Robuuste plaatsbepaling met submeterresolutie steunend op aankomsttijdmetingen rond 2.4 GHz: haalbaarheidsstudie en realisatie van een CMOS-ontvanger met laag vermogen

A Robust 2.4 GHz Time-of-Arrival Based Ranging System with Sub-Meter Accuracy: Feasibility Study and Realization of Low Power CMOS Receiver

**Guy Torfs**

Promotoren: prof. dr. ir. J. Vandewege, prof. dr. ir. J. Bauwelinck Proefschrift ingediend tot het behalen van de graad van Doctor in de Ingenieurswetenschappen: Elektrotechniek

Vakgroep Informatietechnologie Voorzitter: prof. dr. ir. D. De Zutter Faculteit Ingenieurswetenschappen en Architectuur Academiejaar 2011 - 2012

ISBN 978-90-8578-524-8 NUR 959

Wettelijk depot: D/2012/10.500/50

#### Dankwoord

Dit proefschrift is het resultaat van bijna 5 jaar onderzoek uitgevoerd als medewerker van het labo INTEC\_design van de universiteit Gent. Zoals gekend, kleurt het avondrood van de ondergang alles met de bekoring van de nostalgie, wat dit de ideale plaats maakt om een aantal personen die hebben bijgedragen tot het welslagen van dit werk te bedanken.

Zo wens ik prof. dr. ir. Daniël De Zutter, voorzitter van de vakgroep informatie technologie, te bedanken voor de aangeboden faciliteiten en omkadering.

Het onderzoek, beschreven in dit proefstuk, kaderde in het ELOCA en het ALOHA project. Ik wens het IWT-Vlaanderen (Instituut voor de aanmoediging van Innovatie door Wetenschap en Technologie in Vlaanderen) te bedanken voor hun steun. Verder wens ik ook de andere onderzoekspartner, Essensium n.v., te bedanken en meer in het bijzonder ir. Frederic Stubbe, dr. ir. Huub Tubbax en ir. Peter Spiessens voor de nauwe samenwerking en nuttige discussies op zowel architecturaal vlak als in de gedetailleerde transistor implementaties.

Het INTEC\_design laboratorium biedt jonge doctoraatsstudenten de mogelijkheid om zich te vervolmaken in het ontwerpvak. Door nauw samen te werken met verschillende industriële partners wordt een breed gamma van onderzoeksonderwerpen aangeboord en krijgt de student de mogelijkheid om een zee van kennis te vergaren, hoewel er hier en daar nog gebaggerd kan worden. Prof. dr. ir. Jan Vandewege en prof. dr. ir. Johan Bauwelinck, beide promotoren van dit proefschrift, leiden dit labo en ik wens hen te danken voor het vertrouwen en de verschillende ideeën die zij aangereikt hebben alsmede voor het nalezen van deze tekst.

Voorts wens ik mijn collega's van de INTEC\_designgroup te bedanken voor de aangename en prettige samenwerking gedurende de laatste jaren. In het bijzonder dank ik dr. ir. Xin Yin en ir. Zhisheng Li voor hun bijdrage aan de ontwikkelde borden en chips, Ing. Jan Gillis voor het frezen van test borden

en ontwikkelen van test software, ir. Jochen Verbrugghe voor zijn inzichten in transitor ontwerp en ir. Christophe Van Praet voor het uitgebreid en kritisch nalezen van deze tekst.

Ik dank mijn ouders om mij de mogelijkheid te bieden dit ingenieursavontuur aan te vangen, wat uiteindelijk geleid heeft tot dit werk en mijn vriendin Charlotte, die in het zicht van een nakende tape-out vele nachten alleen thuis om mij gewacht heeft.

Tot slot wens ik alle mensen, die mij op een of andere manier geholpen of gesteund hebben, te danken.

Gent, mei 2012

Guy Torfs

# Table of Contents

| Da | ankw           | oord     |                                        | i    |

|----|----------------|----------|----------------------------------------|------|

| Ne | ederla         | ındstali | ge samenvatting                        | xiii |

| Er | nglish         | summa    | ary                                    | xvii |

| Li | st of <b>j</b> | publica  | tions                                  | xxi  |

| 1  | Intr           | oductio  | on                                     | 1    |

|    | 1.1            | Backg    | ground                                 | 1    |

|    | 1.2            | Overv    | iew of the work                        | 3    |

|    | 1.3            | Outlin   | ne of the dissertation                 | 4    |

| 2  | Ran            | ging Sy  | vstem                                  | 9    |

|    | 2.1            | Introd   | uction                                 | 9    |

|    |                | 2.1.1    | RF-based Ranging                       | 9    |

|    |                | 2.1.2    | Non-RF-based Ranging                   | 13   |

|    |                | 2.1.3    | Conclusions                            | 15   |

|    | 2.2            | Syster   | m architecture                         | 16   |

|    |                | 2.2.1    | Ranging Transmitter                    | 16   |

|    |                | 2.2.2    | Ranging Receiver                       | 20   |

|    |                | 2.2.3    | Bandwidth requirements                 | 22   |

|    |                | 2.2.4    | Frequency selection and path loss      | 22   |

|    |                | 2.2.5    | Signal to noise ratio versus bandwidth | 24   |

|    |                | 2.2.6    | Signal to noise ratio versus distance  | 25   |

|    | 2.3            | Proof-   | -of-concept                            | 25   |

|    |                | 2.3.1    | Ranging Transmitter                    | 27   |

|    |                | 2.3.2    | Ranging Receiver                       | 28   |

|    |                | 2.3.3    | Clock synthesis                        | 30   |

|    |                | 2.3.4    | Power supplies                         | 31   |

|    |                | 2.3.5    | Ranging FPGA                           | 31   |

|   | 2.4          | Measurements                                   |

|---|--------------|------------------------------------------------|

|   |              | 2.4.1 Transmitter                              |

|   |              | 2.4.2 Receiver                                 |

|   |              | 2.4.3 Ranging Functionality                    |

|   | 2.5          | Conclusion                                     |

| _ | <b>D D D</b> |                                                |

| 3 |              | Front-end 45                                   |

|   | 3.1          | Introduction                                   |

|   | 3.2          | Derivation of the circuit-level specifications |

|   |              | 3.2.1 Technology selection                     |

|   | 3.3          | Low Noise Amplifier                            |

|   |              | 3.3.1 Introduction                             |

|   |              | 3.3.2 Topology overview                        |

|   |              | 3.3.3 Implementation                           |

|   |              | 3.3.4 Measurements                             |

|   |              | 3.3.5 Conclusion                               |

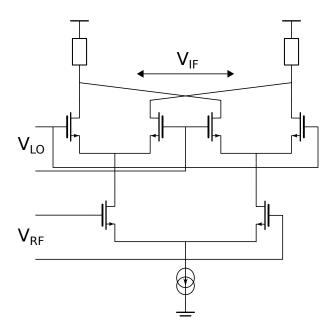

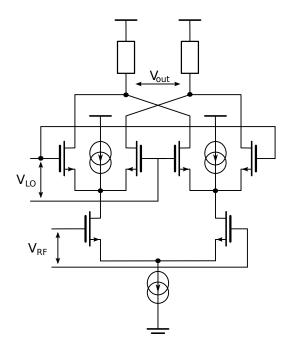

|   | 3.4          | Mixer                                          |

|   |              | 3.4.1 Introduction                             |

|   |              | 3.4.2 Topology overview                        |

|   |              | 3.4.3 Topology selection                       |

|   |              | 3.4.4 Implementation                           |

|   |              | 3.4.5 Measurements                             |

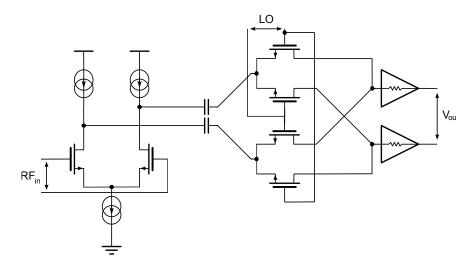

|   | 3.5          | Integrated receiver                            |

|   |              | 3.5.1 Input Matching                           |

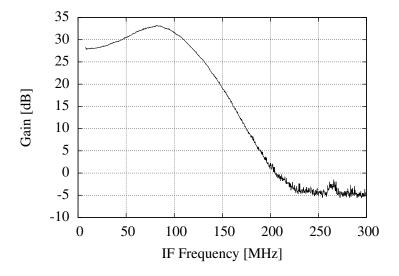

|   |              | 3.5.2 Gain                                     |

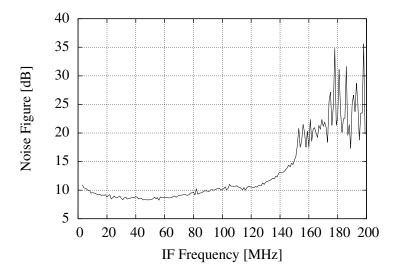

|   |              | 3.5.3 Noise                                    |

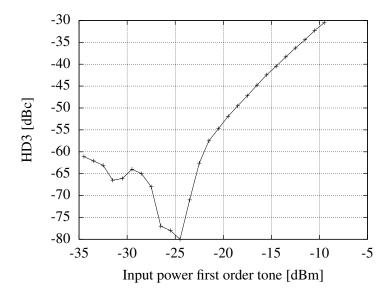

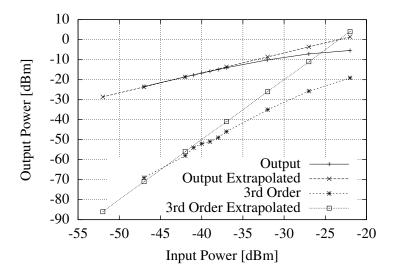

|   |              | 3.5.4 Linearity                                |

|   | 3.6          | Conclusion                                     |

| 4 | Dage         | eband section 95                               |

| 4 | 4.1          |                                                |

|   |              |                                                |

|   | 4.2          | Baseband Filter                                |

|   |              | 4.2.1 Specifications                           |

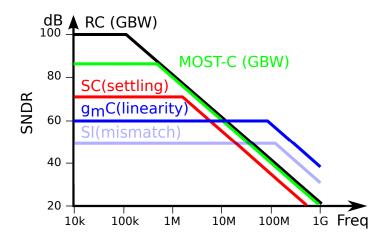

|   |              | 4.2.2 Topologies                               |

|   |              | 4.2.3 Implementation                           |

|   |              | 4.2.4 Measurements                             |

|   |              | 4.2.5 Integrated receiver                      |

|   | 4.3          | Analog-to-Digital Converter                    |

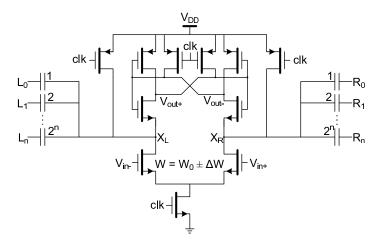

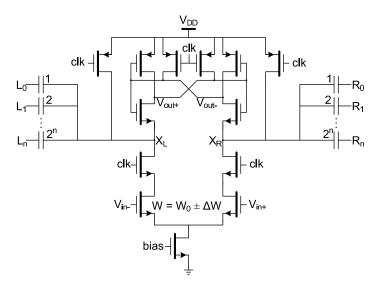

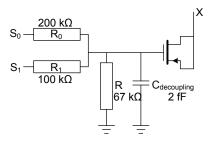

|   |              | 4.3.1 A reduced kickback noise comparator      |

|   |              | 4.3.2 PMOS capacitor                           |

|   |      | 4.3.3 Simulation results                         | 122 |

|---|------|--------------------------------------------------|-----|

|   |      | 4.3.4 Implementation and measurements            | 125 |

| 5 | Ante | enna                                             | 135 |

|   | 5.1  | Introduction                                     | 135 |

|   | 5.2  | Exploration of various antenna types             | 135 |

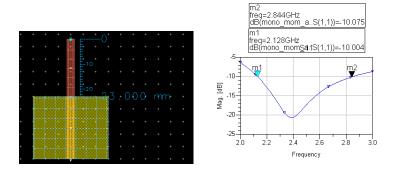

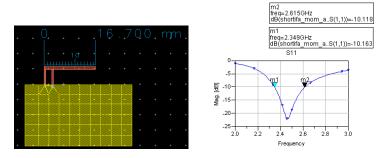

|   |      | 5.2.1 Dipole and monopole antennas               | 136 |

|   |      | 5.2.2 Loop antennas                              | 138 |

|   |      | 5.2.3 Conclusion                                 | 140 |

|   | 5.3  | Available substrates for on-board antennas       | 140 |

|   | 5.4  | Derivation of an efficient co-design methodology | 141 |

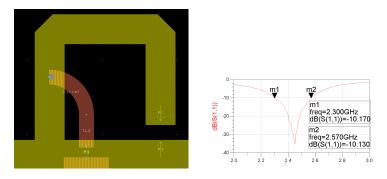

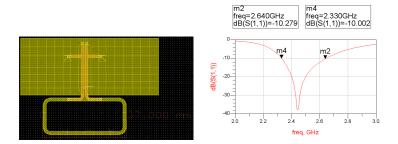

|   | 5.5  | Antenna Implementation and Measurements          | 143 |

|   |      | 5.5.1 Impedance Matching                         | 144 |

|   |      |                                                  | 144 |

|   | 5.6  | Conclusion                                       | 145 |

| 6 | Con  | clusion                                          | 149 |

|   | 6.1  | Summary of the results                           | 149 |

|   | 6.2  | •                                                | 151 |

# Glossary

#### A

**AC** Alternating Current

ADC Analog to Digital Converter

ADS Advanced Design System

AGC Automatic Gain Control

**AOA** Angle Of Arrival

**ASIC** Application Specific Integrated Circuit

#### $\mathbf{C}$

**CMOS** Complementary Metal Oxide Semiconductor

#### D

**DAC** Digital to Analog Converter

**DC** Direct Current

DIP Dual In-line PackageDNL Differential Non-LinearityDSP Digital Signal Processing

#### $\mathbf{E}$

**EM** Electro-Magnetic

**ENOB** Effective Number Of Bits **ENR** Excess Noise Ratio

**ESD** Electrostatic Discharge

$\mathbf{F}$

FCC Federal Communications Commission

FEM Front End Module

FIB Focussed Ion Beam

FOM Figure Of Merrit

**FPGA** Field-Programmable Gate Array

**FR4** Flame Retardant 4

$\mathbf{G}$

GPIO General Purpose Input Output

GPS Global Positioning System

I

IC Inversion Coefficient

**ID** Drain current

**IEEE** Institute of Electrical and Electronics Engineers

**IF** Intermediate Frequency

**IIP3** Input-referred 3rd order Intercept Point

IM3 3rd order intermodulationINL Integral Non-LinearityIQ In phase – Quadrature

**ISM** Industrial, Scientific and Medical

IWT Agentschap voor Innovatie door Wetenschap en

Technologie - Agency for Innovation by Science

and Technology

L

LNA Low Noise Amplifier

LO Local Oscillator

LOS Line Of Sight

LPC Low Pin Count interface LSB Least Significant Bit

LVDS Low Voltage Differential Signaling

#### M

MIM Metal-Insulator-Metal

MIT Massachusetts Institute of Technology

MOS Metal-Oxide-Semiconductor

MOSFET Metal-Oxide-Semiconductor Field-Effect Tran-

sistor

#### N

NF Noise Figure

NLOS Non-Line Of Sight

NMOS N-type MOSFET

NRE Non-Recurring Engineering

#### O

OFDM Orthogonal Frequency-Division Multiplexing

OTA Operational Transconductance Amplifier

#### P

PA Power Amplifier

PCB Printed Circuit Board

PLL Phase Locked Loop

PMOS P-type MOSFET

R

**RF** Radio Frequency

**RFID** Radio Frequency IDentification

ROM Read-Only Memory

RSS Received Signal Strength

**RSSI** Received Signal Strength Indication

**RX** Receiver

#### S

**SAW** Surface Acoustic Wave

**SNDR** Signal to Noise and Distortion Ratio

SNR Signal to Noise Ratio SoC System on Chip

**SPI** Serial Peripheral Interface bus

#### $\mathbf{T}$

**TDOA** Time Difference of Arrival

**TE** Transverse Electric

TIA TransImpedance Amplifier

TM Transverse Magnetic

TOA Time Of Arrival

TWR Two Way Ranging

TX Transmitter

#### U

UMTS Universal Mobile Telecommunications SystemUNII Unlicensed National Information Infrastructure

**UWB** Ultra Wide Band

#### V

VGA Variable Gain Amplifier VNA Vector Network Analyzer W

WLAN Wireless Local Area Network

# Nederlandstalige samenvatting –Dutch Summary–

Recente draadloze sensor netwerken, bestaande uit een aantal onderling verbonden nodes, verzamelen verschillende soorten informatie. Voorbeelden hiervan omvatten meteorologische parameters zoals de temperatuur of de status van machines in een industriële omgeving. Naast de gemeten parameter is de locatie, waar de informatie verzameld is, een belangerijk onderdeel van de informatie zelf. Voor sommige toepassingen, zoals het volgen van personen of goederen, is de plaatsinformatie zelfs de meest belangrijke en mogelijkmakende factor.

De basistechnologie, die nodig is om de positie van een sensor te bepalen, is de meettechnologie die de afstand tot een gekend referentiepunt schat. Door verschillende van deze afstandsmetingen te combineren, is het mogelijk de absolute locatie van de node te berekenen. Er bestaan reeds verschillende technieken die toelaten de positie van een apparaat te bepalen, maar deze hebben elk een aantal onvolkomenheden. GPS werkt bijvoorbeeld enkel buitenshuis en werkt niet wanneer te veel multipad reflecties aanwezig zijn, wat een gevolg is van de kleine bandbreedte en de lange correlatietijden. Andere technieken die het ontvangen zendvermogen meten, zijn slechts in staat een ruwe schatting te geven en hangen sterk af van een vooraf opgestelde blauwdruk. Een meer belovende techniek voor positiebepaling binnenshuis maakt gebruik van ultra-breedbandige (UWB) signalen. De grote bandbreedte van deze signalen vertaalt zich in korte pulsen in het tijdsdomein, die gebruikt kunnen worden voor een aankomsttijd (TOA) gebaseerde meetmethode. Deze korte tijdspulsen zijn immuun voor multipad reflecties maar er is enkel een beperkt zendvermogen beschikbaar, bepaald door de spectrale regelgeving. Wanneer dit gecombineerd wordt met de hoge werkfrequentie, resulteert dit in een korte werkafstand. Verder veroorzaakt de hoge bandbreedte een stijging van de ingangsruis wat dan weer nadelig is voor het linkbudget.

Door een relatief lage radiofrequentie (RF) (2.4 GHz) en een hoge bandbreedte (≈200 MHz) te gebruiken, wordt robuuste, mulitipad resistente, TOA gebaseerd afstandsbepaling mogelijk over een afstand van 300 meter met submeter nauwkeurigheid. De lage frequentie zorgt voor een hoog linkbudget terwijl de hoge bandbreedte voldoende nauwkeurigheid verzekert bij de afstandsbepaling, sinds de te verwachten fout in eerste benadering omgekeerd evenredig is met de bandbreedte. In een eerste fase werd dit innovatieve systeem geëvalueerd met behulp van met commerciële componenten, en van een aangepaste 2.4 GHz draadloze, lokale netwerk (WLAN) zendontvanger (TX/RX). De start van het WLAN pakket wordt vervormd tot een steile flank, wat resulteert in een puls met hoge bandbreedte aan de start van elk pakket. Sinds enkel de start van het pakket de steile flank vertoont, wordt de spectrale regelgeving niet geschonden zolang de herhalingsfrequentie laag genoeg is. De steile flank werd gemaakt door een GaAs schakelaar voor de WLAN vermogensversterker (PA) te plaatsen, wat resulteert in een stijgtijd van 3.25 ns aan het begin van elk pakket. Dit afstandsbepalingspakket wordt vervolgens verzonden naar een referentie node, die de informatie ontvangt door middel van een voortrap met grote bandbreedte. Deze ontvanger bestaat uit twee lage-ruisversterkers, een I/Q menger, basisband filters en versterkers en een snelle 8 bit 500 Msps analoog naar digitaal omvormer (ADC). De bemonsterde informatie wordt vervolgens verder verwerkt in het digitale domein. Deze demonstrator toont de mogelijkheid van nauwkeurige afstandsbepaling aan: een submeter nauwkeurigheid met één enkele meting die verbeterd kan worden door uitmiddeling zodat de fout nadert tot de golflengte van de draaggolf (ongeveer 12.5 cm @ 2.4 GHz). Niettegenstaande de goede nauwkeurigheid die behaald wordt, is het getoonde prototype enkel bruikbaar in een beperkt aantal toepassingen. Dit door de hoge kost van de componenten en het hoge energieverbruik (10 Watt). Om het energieverbruik en de kost van de componenten te verminderen, wordt het gedemonstreerde systeem als startpunt gekozen voor verdere integratie van het systeem op silicium.

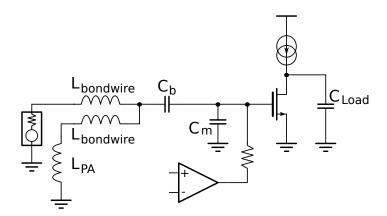

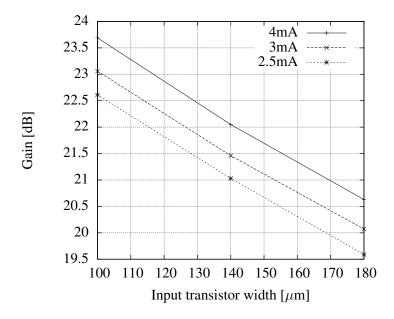

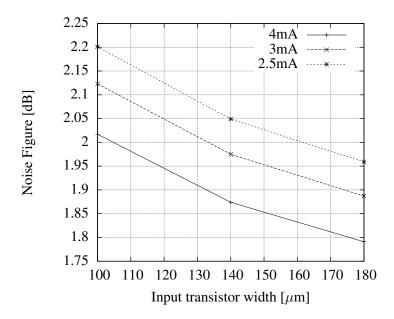

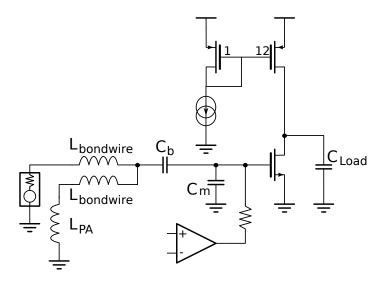

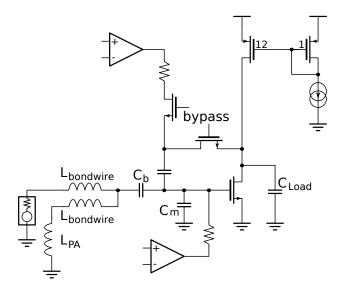

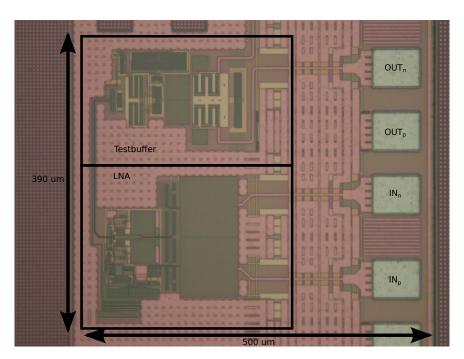

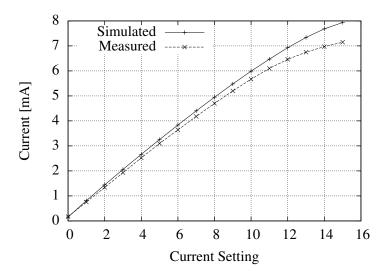

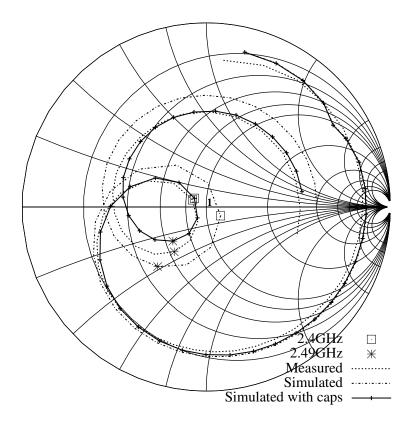

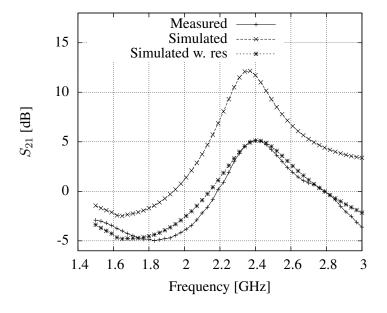

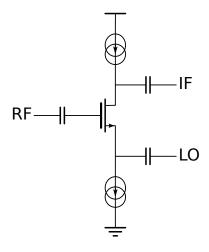

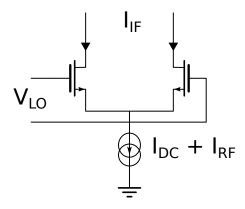

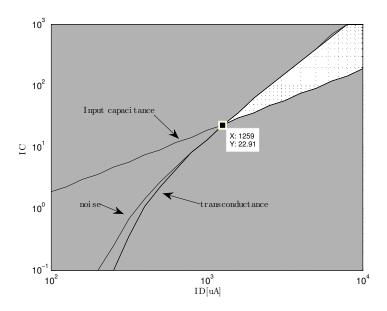

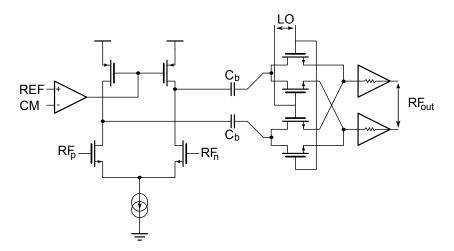

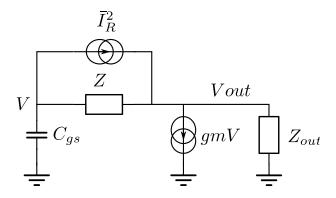

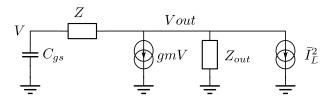

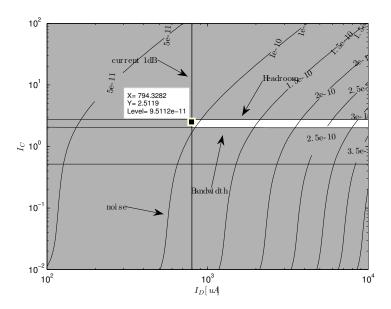

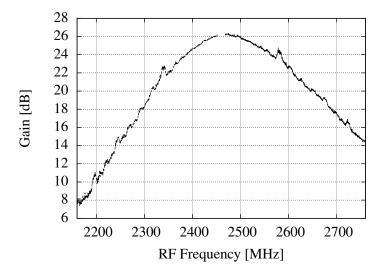

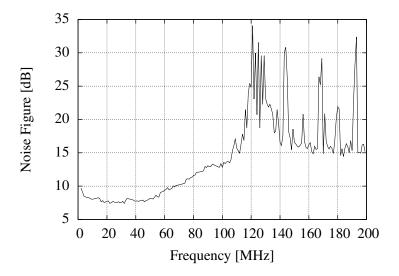

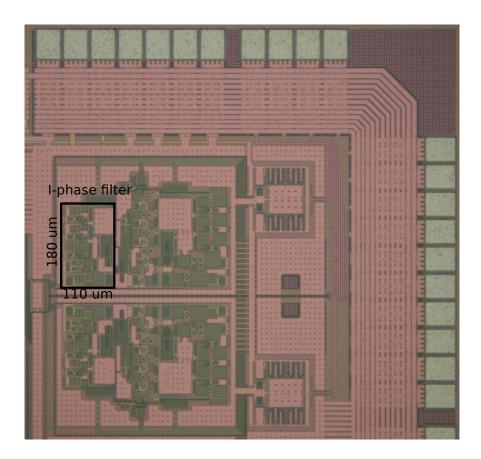

In het volgende deel van dit proefstuk wordt de integratie van de CMOS voortrap beschreven, één van de delen met het hoogste energieverbruik. Het ontwerp wordt geïmplementeerd in een  $0.13~\mu m$  CMOS technologie en is opgedeeld in twee delen: de hoogfrequente lage-ruisversterker (LNA) en de I/Q menger, en de basisband filters en de ADC. De LNA en de menger zijn ontworpen met behulp van een gestructureerde ontwerpsmethodologie. Dit resulteerde in een compact en laagvermogen ontwerp, gerealiseerd in een korte ontwerpstijd. Slimme technieken op architecturaal niveau maak-

DUTCH SUMMARY XV

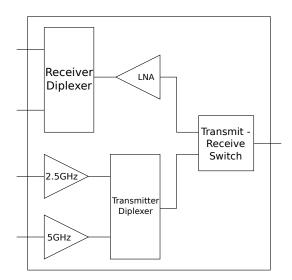

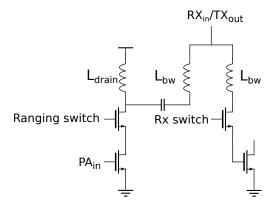

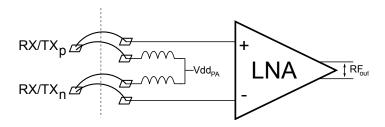

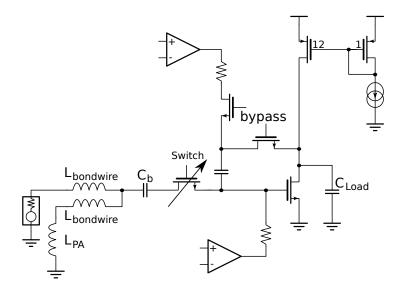

ten het mogelijk om de TX/RX schakelaar en extra spoelen van het LNA ingangsaanpassingsnetwerk te verwijderen door de drainuitgangsspoel van de vermogensversterker te hergebruiken. De cascade van de LNA en de menger resulteerde in een ruisgetal van  $7.5~\mathrm{dB},~28~\mathrm{dB}$  versterking en een bandbreedte van  $250~\mathrm{MHz}.$  Dit alles verbruikt slechts  $10~\mathrm{mW}.$

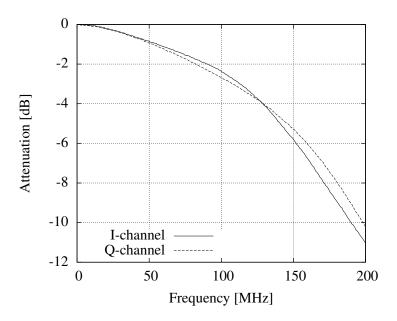

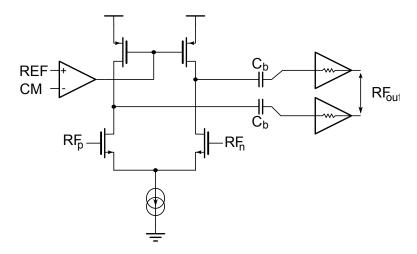

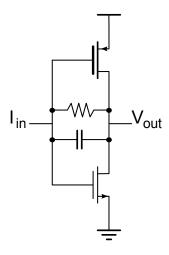

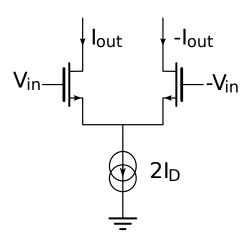

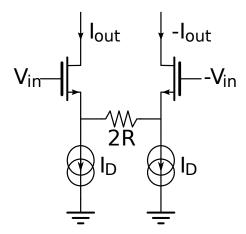

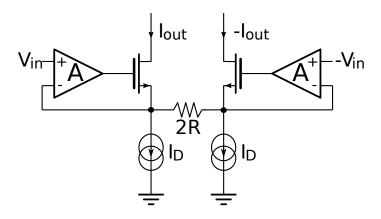

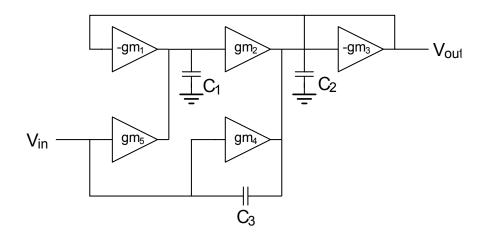

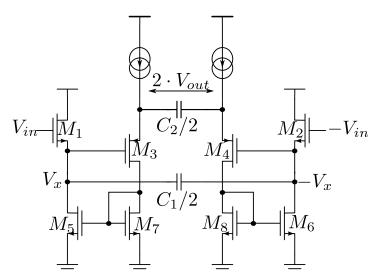

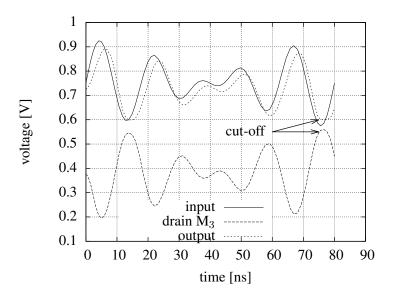

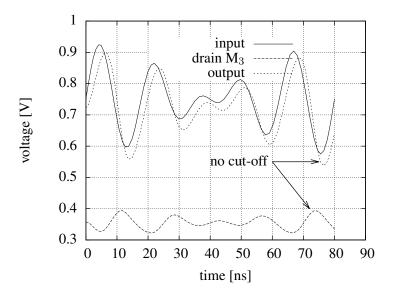

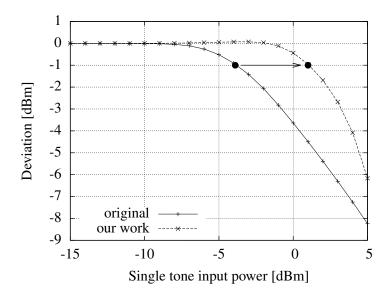

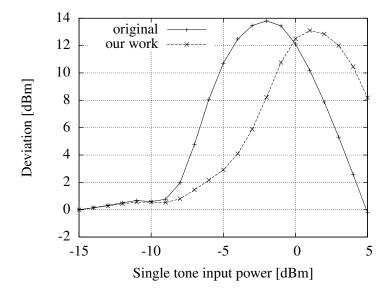

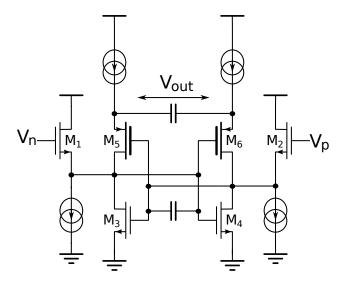

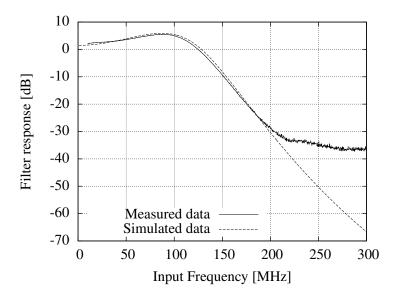

Door de grote bandbreedte van de ontvanger wordt sterke interferentie van nabijgelegen UMTS zenders verwacht. Om deze stoorsignalen uit het basisband spectrum te verwijderen en de robuustheid van de ontvanger te garanderen, zonder de nauwkeurigheid van de afstandsbepaling te schaden (dus door voldoende bandbreedte te garanderen), werd een scherp 10e orde sourcevolger gebaseerd filter ontworpen. Source-volger gebaseerde filters zijn inherent lineair door de ingebouwde terugkoppeling tussen gate en source wat een laagvermogen realizatie toelaat. Een minpunt van een sourcevolger is zijn beperkte spanningsversterking (typisch 0.7). Door kruiselingsgekoppelde transistoren toe te voegen, kan de versterking verhoogd worden, wat dan weer de ruisbijdrage van volgende secties vermindert. In de zoektocht naar lineaire sourcevolger gebaseerde filters bleek dat harde afknijpingsverschijnselen voorkwamen wanneer het filter aangestuurd werd met sterke signalen. Een alternatief terugkoppelingsmechanisme werd voorgesteld om het lineair ingangsgebied van het filter uit te breiden en om de sterke afknijpingsverschijnselen te onderdrukken. Het voorgestelde I/Q basisbandfilter verbruikt 2 mW, heeft een bandbreedte van 130 MHz en een onderdrukking van 33 dB op 225 MHz.

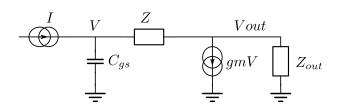

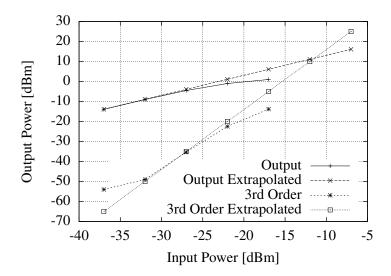

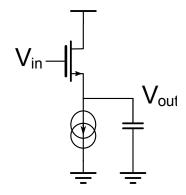

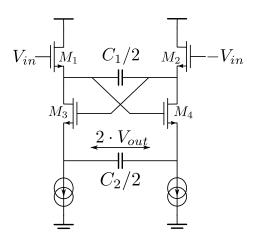

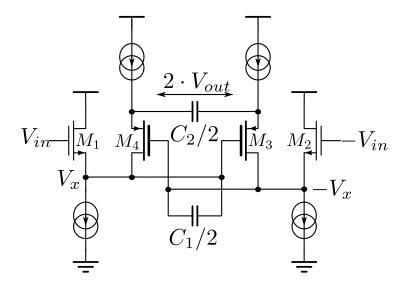

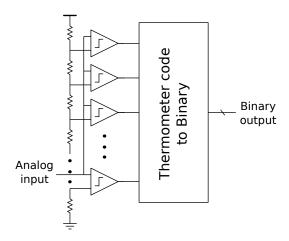

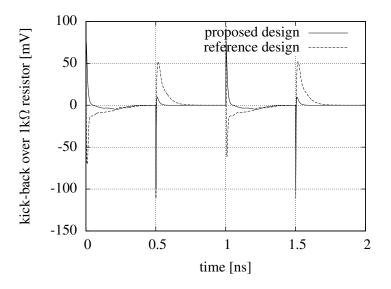

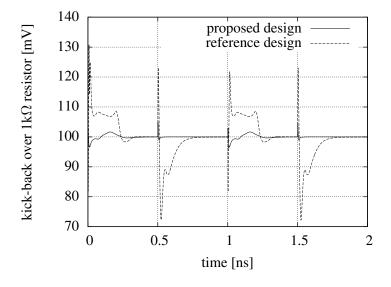

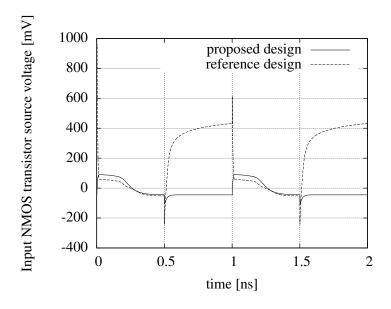

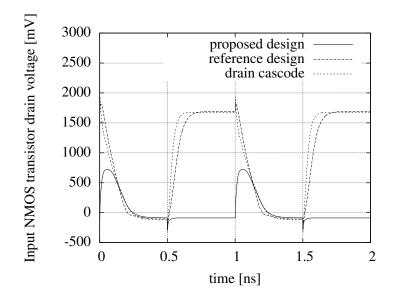

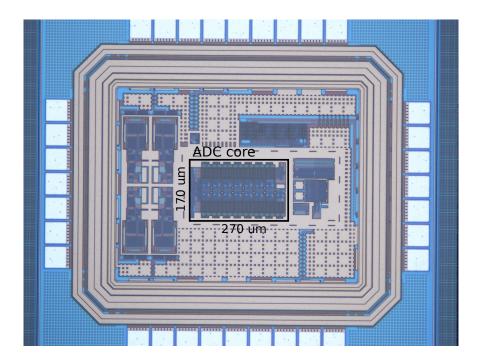

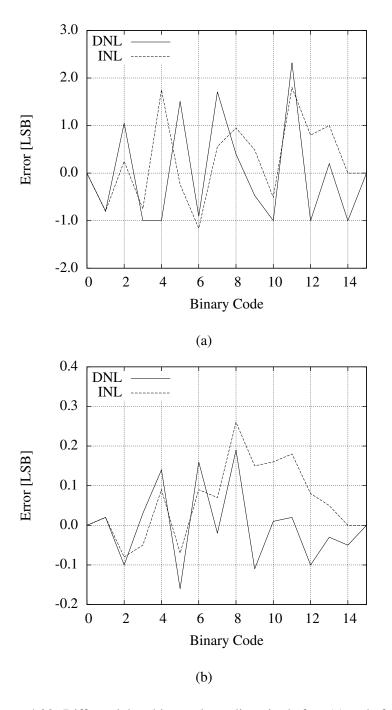

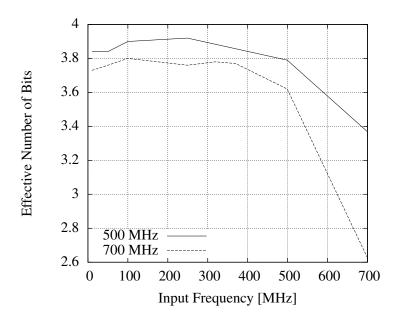

De snelle ADC is het onderdeel dat het meeste energie verbruikt in de voortrap gebouwd met discrete componenten. Om dit vermogen drastisch te doen dalen werd een 4 bit flits ADC ontwikkeld. Voorgaande ontwerpen toonden aan dat vergelijkers met ingebouwde drempelspanning leden onder terugslagruis. Deze terugslagruis veroorzaakt geheugeneffecten als het signaal wordt aangestuurd vanuit een bron met een te hoge uitgangsimpedantie zodat een breedbandige buffer met lage uitgangsimpedantie, die veel vermogen verbruikt, noodzakelijk is. Om de terugslagruis te verminderen is een nieuwe vergelijker voorgesteld, die door het verminderen van de terugslagruis een meer nauwkeurige kalibrering toelaat. Door 15 van deze vergelijkers samen te voegen tot een 4 bit ADC, werd een ontwerp bekomen dat slechts 4.3 mW verbruikte op een werkfrequentie van 700 Msps met een performantiemaat (FOM) van slechts 0.57 pJ per monster en per effictieve bit.

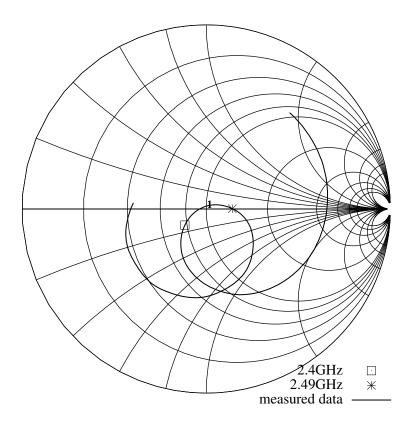

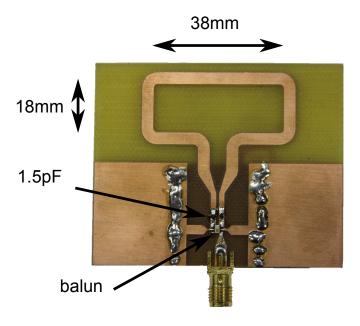

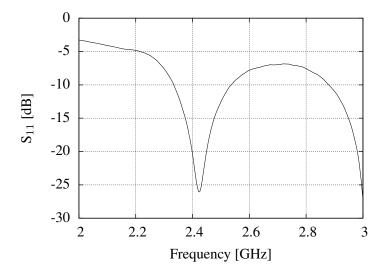

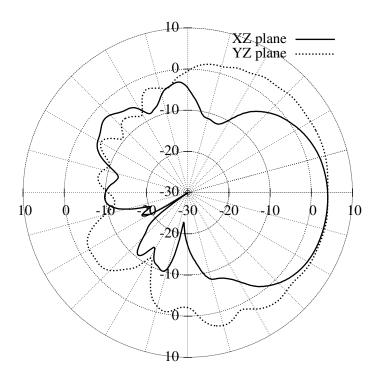

Om de ontvangersketen te vervolledigen, wordt in het laatste hoofdstuk

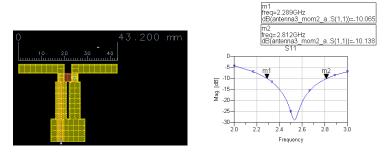

van dit proefschrif het ontwerp en de implementatie van een differentiële, volle golflengte lusantenne beschreven. De bandbreedte van de antenne is voldoende groot gemaakt om de ontvangst van afstandsbepalingssignalen mogelijk te maken en door zijn magnetische eigenschappen wordt de invloed van storingen in het nabije veld gereduceerd. Door de differentiële opbouw van de antenne wordt de nood aan extra omzettingen van gebalanceerde naar ongebalanceerde signalen vermeden. Dit resulteert in een hogere versterking en lagere ruis van de gehele zendontvanger.

De combinatie van al deze bouwblokken maakt het mogelijk een volledige voortrap voor een afstandsbepalingsontvanger te bouwen. Dit geheel brengt de initiële demonstrator een stap dichter bij een implementatie met laag vermogen en een beperkte prijs.

## **English summary**

Nowadays, wireless sensor networks, consisting of multiple interconnected nodes, gather different kinds of information, for example meteorological parameters such as temperature or machine health status parameters in an industrial setup. Besides the measured parameter, the location where the information is gathered, is a crucial part of the information itself. For some applications, such as people and asset tracking systems, location information is even the most important and enabling factor.

The basic technology needed to determine the position of a sensor is the ranging technology, which estimates the distance to known reference points. By combining several distance measurements, the absolute location of the node can be calculated. There already exist different technologies to determine the position of a device, but all of these have certain limitations. The GPS, for example, only works in outdoor scenarios and isn't capable of handling multipath reflections due to low signal bandwidth and long correlation times. Other techniques make use of received signal strength measurements, which can only providing a rough estimate, and rely on extensive fingerprinting. A more promising technique for indoor applications makes use of UWB signals. The wide bandwidth translates to short pulses in time domain, and allows for a time-of-arrival (TOA) based ranging method that makes the ranging signals immune for multipath reflections. However, due to spectral regulations, only limited transmit power is allowed. Combined with the high operating frequency, this results in a relatively short operating range. Furthermore, the high bandwidth increases the input noise which is a disadvantage for the link budget.

By using a relatively low (2.4 GHz) RF frequency and a high ( $\approx$ 200 MHz) bandwidth, a sub-meter accurate, multipath reflection robust, TOA based ranging system is shown to operate over 300 meter. The low frequency offers a high link budget while the high bandwidth ensures the ranging accuracy, since, in first order, the expected error is inversely proportional to the bandwidth. This system, prototyped on a PCB with off-the-shelf com-

xviii English summary

ponents, makes use of a modified 2.4 GHz WLAN transceiver. The onset of a WLAN packet is modified to produce a steep edge, generating a high bandwidth pulse at the start of each packet. Since only the start of the packet has a steep edge, spectral regulations aren't violated as long as the repetition rate is low. The steep edge is generated by a fast GaAs switch placed in front of the WLAN PA, which offers rise times of 3.25 ns at the beginning of the packet. This ranging packet is transmitted to a reference node, capturing the information with a high bandwidth front-end, consisting of two LNA's, a I/Q mixer, baseband filters and amplifiers and a fast 8 bit 500 Msps ADC. The sampled information is further processed in the digital domain. This first prototype yielded a single shot accuracy of less than one meter. After averaging, the error could be minimized downto the carrier wavelength (about 12.5 cm @ 2.4 GHz). Although good ranging accuracy is achieved, the demonstrated prototype is only practical in a limited number of situations due to the high component cost and high power consumption (10 Watt). To lower the power consumption and component count, the proof-of-concept is used as starting point for silicon integration of the system.

Further on, the CMOS integration of the front-end, one of the most power consuming parts, is described. A 0.13  $\mu m$  CMOS technology is used to implement the design, which is divided into two parts: the high frequency LNA and I/Q mixer, and the baseband filters and ADC. The LNA and mixer are designed via a structured design methodology and resulted in a compact low power design achieved via a short design cycle. Clever architectural techniques made it possible to remove a full TX/RX switch and extra inductors from the LNA input matching network, by reusing the drain output inductor of the PA. The cascade of LNA and mixer resulted in a NF of 7.5 dB, 28 dB gain and a bandwidth of 250 MHz while only consuming  $10~\rm mW$ .

Due to the high receiver bandwidth, high interference of nearby UMTS transmitters is expected. To remove these signals from the baseband spectrum and thus, to ensure the robustness of the receiver, while still enabling accurate ranging (thus preserving enough bandwidth), a steep 10th order source-follower based filter is implemented.

Source-follower filters are inherently linear devices due to the built-in feed-back between gate and source, allowing low power linear operation. A downside of a source follower is its limited voltage gain (0.7 typical). By adding an extra crosscoupling transistor, the gain can be increased, reducing the noise contribution of the subsequent stages. The search for a linear

ENGLISH SUMMARY xix

source-follower based filter showed that hard clipping occurs when the filter is driven with strong signals. An alternative feedback structure is proposed to extend the linear input range and to reduce the hard clipping effects of the source follower filter. The proposed I/Q baseband filters consume  $2~\mathrm{mW}$ , have a bandwidth of  $130~\mathrm{MHz}$  and an attenuation of  $33~\mathrm{dB}$  at  $225~\mathrm{MHz}$ .

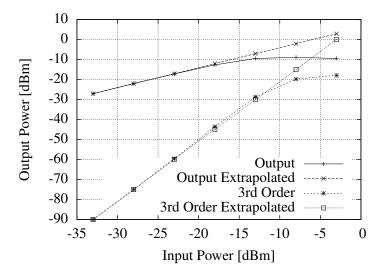

The high-speed ADC is the most power consuming block of the proof-of-concept PCB. To reduce the power consumption dramatically, a low power 4 bit flash ADC is developed. Previous designs showed the use of comparators with built-in threshold voltages but suffered from severe kickback noise. This kickback noise can result in memory effects when the signal source output impedance is too high, requiring a high power broadband input buffer. To reduce the kickback noise, a novel comparator is proposed, which due to the reduced kickback noise, enabled a finer calibration. Combining 15 of such comparators in a 4 bit ADC, led to a 4.3 mW design working at 700 Msps with a FOM of 0.57 pJ.

To complete the receiver chain, the last chapter of this dissertation presents the design and implementation of a differential full wave loop antenna. The antenna is made sufficiently broadband to allow reception of ranging signals and makes use of its magnetic properties to reduce the influence of disturbances in its near field. The differential nature of the antenna removes the need for on or off-chip baluns, allowing higher gain and lower noise of the overall TRX.

The combination of all these building blocks realizes a complete ranging receiver front-end, bringing the initial proof-of-concept PCB one step closer towards a low power and low cost implementation.

## List of publications

#### **Publications in international journals**

- G. Colman, G. Torfs, J. Bauwelinck, and J. Vandewege. Low-cost circuit incorporates mixing and amplifying functions. *EDN*, 53(14):77, JUL 10 2008

- X. Yin, J. Bauwelinck, G. Torfs, P. Demuytere, J. Vandewege, H. Tubbax, J. Wouters, P. Debacker, J. Olbrechts, P. Spiessens, F. Stubbe, and J. Danneels. Embedded ranging system in ISM band. *Electronics Letters*, 44(17):1043–1044, AUG 14 2008

- 3. J. Bauwelinck, E. De Backer, C. Melange, G. Torfs, P. Ossieur, Xing-Zhi Qiu, J. Vandewege, and S. Horvath. A 1024-QAM Analog Front-End for Broadband Powerline Communication Up to 60 MHz. *IEEE Journal of Solid-State Circuits*, 44(5):1477 –1485, May 2009

- 4. G. Torfs, Z. Li, J. Bauwelinck, X. Yin, J. Vandewege, and G. Van Der Plas. A Low-Power Reduced Kick-Back Comparator with Improved Calibration for High-Speed Flash ADCs. *IEICE Transactions on Electronics*, E92C(10):1328–1330, OCT 2009

- 5. G. Torfs, Z. Li, J. Bauwelinck, X. Yin, G. Van der Plas, and J. Vandewege. Low-power 4-bit flash analogue to digital converter for ranging applications. *Electronics Letters*, 47(1):20–21, JAN 6 2011

- 6. G. Torfs, Z. Li, J. Bauwelinck, J. Vandewege, and P. Spiessens. A novel large input range source-follower based filter architecture. *IE-ICE Electronics Express*, 8(24):2025–2028, 2011

- 7. R. Pierco, Z. Li, G. Torfs, X. Yin, J. Bauwelinck, and X.Z. Qiu. Diode string with reduced clamping-voltage for ESD-protection of RF-circuits. *Electronics Letters*, 48(6):317 –318, 2012

xxii Overview

Z. Li, G. Torfs, J. Bauwelinck, X. Yin, J. Vandewege, C. Van Praet, P. Spiessens, H. Tubbax, and F. Stubbe. A 2.45-GHz + 20-dBm Fast Switching Class-E Power Amplifier With 43% PAE and a 18-dB-Wide Power Range in 0.18- μm CMOS. *IEEE Transactions on Circuits and Systems II: Express Briefs*, PP(99):1 –5, 2012

Z. Li, J. Bauwelinck, G. Torfs, X. Yin, and J. Vandewege. A New Common-Mode Stabilization Method for a CMOS Cascode Class-E Power Amplifier with Driver Stage. *IEICE Transactions on Electronics*, E95C(4):765–767, APRIL 2012

#### **Publications in international conferences**

- H. Tubbax, J. Wouters, J. Olbrechts, P. Debacker, P. Spiessens, F. Stubbe, J. Danneels, J. Bauwelinck, X. Yin, G. Torfs, and J. Vandewege. A Novel Ranging Technique for 2.4GHz ISM Band. In *The IASTED International Conference on Sensor Networks*, Sept.-Oct. 2008

- H. Tubbax, J. Wouters, J. Olbrechts, P. Debacker, P. Spiessens, F. Stubbe, J. Danneels, J. Bauwelinck, Xin Yin, G. Torfs, and J. Vandewege. A novel positioning technique for 2.4GHz ISM band. In *IEEE Radio* and Wireless Symposium, pages 667–70, 2009

#### **Publications in national conferences**

- G. Torfs, X. Yin, Z. Li, J. Bauwelinck, and J. Vandewege. Embedded indoor ranging system with decimeter accuracy in the 2.4 GHz ISM band. In 9e UGent-FirW Doctoraatssymposium, pages 208–209, 2008

- 2. G. Torfs, J. Vandewege, and J. Bauwelinck. Integrated subblocks for RF ranging applications. In *11e UGent-FirW Doctoraatssymposium*, page 160, 2010

#### **Patents**

G. Van der plas, P. Nuzzo, F. De Bernardinis, J. Bauwelinck, Z. Li, G. Torfs, J. Vandewege, and X. Yin. A/D Converter Comprising a Voltage Comparator Device. Continuation in part of WO2007088175, US7652600 (B2), granted on 26 Jan. 2010 Overview xxiii

2. J. Bauwelinck, Z. Li, G. Torfs, J. Vandewege, and X. Yin. Amplifier Circuit for a Ranging Transceiver. EP 2 429 075 (A1), published on 14 Mar. 2012

# Introduction

#### 1.1 Background

In wireless sensor networks, sensors convert physical parameters like pressure and temperature to electrical information and transfer this wirelessly to an application server where it can be further processed for the benefit of its users. Besides the sensor information, the accurate location where this information is generated, adds extra value to the sensor read-out. In some applications, it can even be the most valuable information communicated (e.g. all asset and people tracking applications). So far, most of the activity in the domain of wireless sensor networking has focused on the aspect of (low power) communication of sensor information while the requirements for the sensor to acquire accurate position information were neglected. Positioning is considered to be an afterthought and hence the performance, i.e. position accuracy is useless for most applications.

One of the basic technologies for the sensor to accurately determine its position is the ranging technology. Ranging technology estimates the distance between two points, one being the sensor node, the other being a node with a known location. Combining several ranging measurements provides several distances to known, fixed devices, from which positioning algorithms provide a good estimation of the most likely absolute coordinates of the sensor.

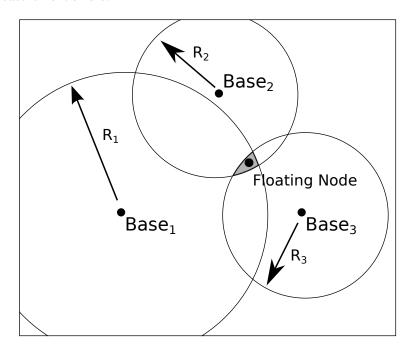

Figure 1.1 shows a classical setup to determine the location of a floating

2 Chapter 1

node. Three basestations use a ranging method to measure the distance to the floating node, yielding the distances  $R_1$ ,  $R_2$  and  $R_3$ . These allow to determine a region in which the floating node is likely to be found. To determine the position in a plane, two base stations are insufficient, yielding 2 different intersect points on 2 circles. A third one solves the ambiguity problem and gives extra redundancy, used to estimated and to compensate measurement errors.

Figure 1.1: Ranging based location determination.

Well-established technologies for position determination are mostly addressing outdoor scenarios, the Global Positioning System (GPS) being the most widespread and well known example. While these techniques have adequate performance outdoors when sufficiently strong line-of-sight signals are available, they suffer from low accuracy in indoor environments. The key reason for this performance degradation is that received signals consist of multiple superimposed, attenuated, delayed and phase rotated copies of the line-of-sight signals caused by reflections [1]. Especially due to the narrow-band nature of the transmitted signals, these copies have a wide span in the time-domain and hence tend to overlap. As a result, copies having travelled several meters more typically can not be distin-

Introduction 3

guished from the line-of-sight path by the receiver, thus introduce errors in the position estimation of the same order of magnitude.

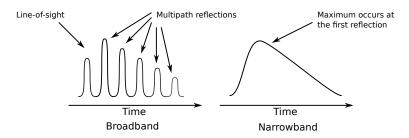

Figure 1.2 shows the effect of multipath reflections on a narrowband ranging system. If a weak line-of-sight signal is followed by a strong reflected signal, the narrowband filtering will result in a signal of which the maximum is aligned with the reflected signal. This time shift in signal will result in ranging errors.

Figure 1.2: Effect on the ranging accuracy due to multipath reflections.

#### 1.2 Overview of the work

This dissertation describes the research the author has conducted during the past 4 years at the INTEC\_design laboratory of the department of information technology (INTEC) at Ghent University.

The INTEC\_design group offers young engineers the opportunity to skill themselves in the design of electronical systems at the PhD level. By collaborating with industrial partners, there is an opportunity to solve real-world problems. In this way the training is not limited to a pure theoretical study but comprises the system study, integration and realization of first prototypes, and concludes with the final testing and demonstration of the new system concepts.

This work in particular is based on the research performed in the framework of the IWT ELOCA (Embedded LOCation Awareness in wireless modules) and IWT ALOHA (Advanced LOcation with High Accuracy) project. Both projects were financed by the Agentschap voor Innovatie door Wetenschap en Technologie – Agency for Innovation by Science and Technology (IWT) and have been conducted in close cooperation with IMEC spin-off Essensium. Essensium is a fabless chip company, situated in Leuven and specialized in system-on-chip Application Specific Integrated Circuit (ASIC) design, for low power solutions and wireless communications.

4 Chapter 1

The IWT project ELOCA focused on the basic technology for accurate ranging in indoor environments. The proof-of-concept ranging transceiver, developed using commercially available components, showed a significant improvement in precision (< 1 m resolution) compared to existing technologies, thanks to the high dynamic range of the transceiver and accurate real-time positioning algorithms. Besides the realization of the transceiver, coexistence with very low mutual interference with ongoing data traffic in the same frequency band was demonstrated. In this project, it was also shown that it is feasible to integrate the functionality on chip, paving the way for a follow-up project, ALOHA.

The IWT ALOHA project is a continuation of the ELOCA project. ALOHA targeted the low cost and low power silicon integration of the ranging transceiver functions, together with data communication functions, in a single front-end. This is mostly driven by the demands for autonomy (so low power) and miniaturization (portability). Our research in this project was mainly focused on the Radio Frequency (RF) building blocks of the transmitter and the receiver, including the antenna design and the co-optimization of the antenna with the RF circuits. The transmitter design will be discussed in detail in the PhD of our colleague Zhisheng Li.

#### 1.3 Outline of the dissertation

This dissertation is organized as follows. Chapter 2 provides an overview of existing ranging technologies and discusses their advantages and disadvantages with respect to accurate indoor ranging. Based on these insights a new ranging technique, patented by Essensium, is presented. This new concept combines the advantages of both broadband and narrowband signals to achieve a high ranging accuracy in presence of strong multipath reflections, to achieve a good link budget and to be compliant with the spectral regulations. The fundamental idea is that also relatively narrowband radios such as those used in Wireless Local Area Network (WLAN) products exhibit and/or can be stimulated to generate wideband transient signals. And these wideband signals can then be leveraged for improved positioning accuracy at the receiver, by processing them with a higher bandwidth than required for the narrowband communication signal. A system level study and a Printed Circuit Board (PCB) demonstrator were developed to prove this new concept in various field trials.

This PCB demonstrator allowed to identify the circuit-level trade-offs (e.g. ranging accuracy vs. power consumption) and to derive the integrated circuit specifications for the integration of the ranging transceiver. The re-

INTRODUCTION 5

mainder of this work focuses on the integration of the RF and analog ranging receiver functions. Chapter 3 describes the design methodologies and measurement results of the high-dynamic range low noise amplifier and mixer. Chapter 4 describes the integration of a highly linear baseband filter and a high-speed 4-bit analog to digital converter. To complete the receiver functionality, chapter 5 described the design of a broadband PCB antenna, and its co-design with the ranging transceiver. This dissertation ends with chapter 6. This chapter concludes with a summary of the main findings of this work and highlights potential areas of related future research.

6 Chapter 1

# Bibliography

[1] S. Gezici, Z. Tian, G.B. Giannakis, H. Kobayashi, A.F. Molisch, H.V. Poor, and Z. Sahinoglu. Localization via ultra-wideband radios: a look at positioning aspects for future sensor networks. *IEEE Signal Processing Magazine*, 22(4):70 – 84, Jul. 2005.

# Ranging System

# 2.1 Introduction

To enable accurate ranging, different techniques have been proposed, each one of them showing both advantages and disadvantages for use in indoor environments.

## 2.1.1 RF-based Ranging

Numerous techniques that perform ranging by means of RF signals exist. Each technique measures some characteristic of the RF signal that can be related to the distance the signal has travelled. The choice of characteristic determines the properties of the obtained ranging technique. In this overview, received signal strength indication, time of arrival, angle of arrival and proximity detection will be discussed.

#### **RSSI**

Received Signal Strength Indication (RSSI) measures the incoming power exploiting the principle that the power decreases with the distance. In free space, signal power decays proportionally with  $d^n$ , with d representing the transmitter-receiver distance and n=2 the path-loss coefficient. However, in real-world channels, multipath fading causes the RSSI to correlate poorly with distance, resulting in inaccurate distance measurements.

Deviations from the general model will occur on both small (looking like noise on top of the model) and large scale (the model parameters seem different). The small scale fading can be somewhat mitigated through averaging. The large scale fading can be addressed by so-called fingerprinting: the environment is characterized before the actual operation, such that the model parameters can be fitted to optimize the ranging accuracy.

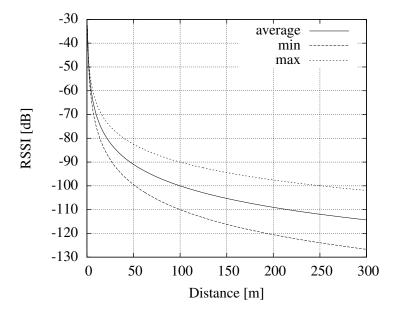

The drawback is that the accuracy degrades if the environment changes, requiring the cumbersome fingerprint procedure to be repeated for every significant deviation. In optimal conditions RSSI can reach about 1 m accuracy, though only over a small range as shown in figure 2.1, as the error with respect to the average distance estimate increases dramatically with distance.

Figure 2.1: Relation between RSSI and distance.

RSSI measurements are relatively inexpensive and simple to implement in hardware, as the RSSI of radio signals can be measured by each receiver during normal data communication without additional bandwidth or energy consumption. Only minimal additional hardware is needed since most communication protocols require that an RSSI measurement is made available upon request by an application. RSSI is often used in combination with WLAN [1] or Zigbee [2]. In summary, RSSI is attractive because of its low

complexity and compatibility with most standards, but it is a very rough measure of distance at its best.

#### Time of Arrival

Time Of Arrival (TOA) measures the travel time of the radio signal between two nodes. This timing information can be translated into distance information in a number of ways. If two wireless nodes have a synchronized clock, the node receiving the signal can determine the TOA of the incoming signal that is time-stamped by the transmit node. The transmitter-receiver distance can then be derived by multiplying the time-of-flight (i.e., TOA minus time-of-transmission) with the propagation velocity, i.e. the speed of light for RF ranging systems.

When there is no time synchronization between a given node and the reference nodes, but the reference nodes are synchronized, then the Time Difference of Arrival (TDOA) technique can be employed. In this case, the TDOA of two signals travelling between the given node and two reference nodes is estimated, which determines the location of the node on a hyperbole, with foci at the two reference nodes.

In the absence of a common clock between the nodes, the round-trip time between two nodes can be measured to estimate the distance between two nodes, which is also referred to as Two Way Ranging (TWR). This results in two TOA detections and eliminates the need of tight synchronization between the nodes, but still limits the amount of clock drift that can be tolerated between the two nodes. To eliminate the clock drift constraint, double-side two-way ranging can be employed [3]: each node initiates a two-way ranging event, effectively resulting in 4 TOA detections. In such a setup, the clock drift will impact the timing estimations, once positively and once negatively, nilling the impact (assuming the clock remains constant during the packets exchange).

The timing can be extracted from the RF signal in a number of ways. The most direct way to derive the timing information of an RF signal is to detect the leading edge of the packet, such as in traditional radar systems [4]. Despite the low emission power, this principle can be used for Ultra Wide Band (UWB) when keeping the distances limited [5]. To fight noise and interference, the receiver typically correlates with a large portion of the signal to determine the TOA. In the GPS system [6] for instance, the receiver correlates over the 1 ms long Coarse/Acquisition code which allows to get good accuracy out of a narrowband signal. In other systems such as

Nanotron [7], an inherently wideband signal is used (60 MHz chirp) to get a relatively good accuracy out of a single measurement.

For an ideal single-path channel, it can be shown that the accuracy of a one-shot TOA estimate depends on the signal bandwidth (which defines the time-resolution) and Signal to Noise Ratio (SNR) [8]. Thus, the accuracy of TOA-based ranging can be improved by increasing the SNR or the signal bandwidth. These two parameters allow to make an initial estimate on the performance of different systems: UWB uses a bandwidth of at least 500 MHz and can thus obtain very good accuracy (down to about 15 cm), but due to the low emission levels the coverage is quite poor (<60 m in LOS and <20 m indoors); Nanotron uses a 20 MHz to 60 MHz chirp, resulting in best case 2 m accuracy over a few 100 meters; WLAN uses a 20 MHz bandwidth, yielding an accuracy of 8 m over a few 100 meters. In practice, the quality of TOA measurements depends also on the receivers ability to accurately estimate the arrival time of the Line Of Sight (LOS) signal. This estimation is mainly hindered by multipath propagation that creates the following error sources:

- Early arriving multipath. Many multipath signals arrive shortly after the LOS signal, and their contribution obscures the real time-of-flight information given by the LOS signal. This is the case if the processing bandwidth is too small to discern between the different paths or if the signal used for locking is too long. This is for instance the case for GPS and chirp signals.

- Non-Line Of Sight (NLOS) propagation results in large positive errors in the TOA estimates. Obstacles such as walls and buildings block the LOS path and, as such, the signal arrives at the receiver via reflections on other surfaces. For each individual measurement, it is very hard to distinguish between a LOS and NLOS measurement. The distinction can e.g. be made using statistics on a large amount of measurements: the spread on NLOS measurements is typically larger than on LOS measurements. Another way is to track the distance measurements: when an object moves behind a wall, a sudden jump in measured distance can occur, which is not physically possible considering the limited speed of the object.

#### **Angle of Arrival**

Angle Of Arrival (AOA) measurement systems provide the direction to neighboring sensors. The most common method to measure the AOA is to use a sensor array and apply array signal processing techniques to estimate

the AOA by determining the differences in arrival time for a transmitted signal at each element of the array. Therefore, AOA measurements need a large array to realize a sufficient angular resolution and the signal processing should be multipath tolerant. Many systems use AOA to augment basic ranging information, e.g. Ubisense [9].

#### **Proximity detection**

A very rough measure of distance is simple proximity detection. If the signal from a known reference source is detected, then the mobile node is within the operational range of that reference point. This operational range can be very short, e.g. in case of Radio Frequency IDentification (RFID) systems [10], resulting in good accuracy, but requiring a huge amount of reference points to get good coverage. Or the range can be very large, e.g. in WLANs, resulting in poor accuracy, but excellent coverage. Several proximity detection mechanisms with different ranges can be combined to make an accuracy/coverage trade-off.

# 2.1.2 Non-RF-based Ranging

A number of systems try to estimate the distances by detecting or measuring non-RF signals. A variety of techniques are shown to give an overview of their benefits and limitations.

#### (Ultra)Sound

An alternative carrier is a sound wave. The Cricket system (see figure 2.2) as developed by Massachusetts Institute of Technology (MIT) uses a 40 KHz ultrasound signal. Ultrasound is a pressure wave, just like sound waves, but with a frequency above the range of human hearing.

Figure 2.2: Cricket System from MIT.

Because of the significantly lower propagation speed of sound compared to RF signals, it requires simpler processing to obtain good accuracy. Cricket can reach 5 cm accuracy [11]. On the other hand, there are a few disadvantages associated with the use of ultrasound: ultrasound does not propagate through walls and diffracts even worse than audible sound through doors and windows [11]. Therefore, ultrasound positioning is confined within rooms and thus mostly suited for large open areas. Moreover, the use of speakers make small scale integration harder.

# Laser

Laser-based ranging systems often feature very impressive accuracy/range combinations: most systems offer accuracies down to  $2\ \mathrm{mm}$  over a range of  $500\ \mathrm{m}$  or more, both indoor and outdoor. Therefore, laser is used intensively for distance measurements. As the laser needs to be pointed on the target, this technique is not really suitable for positioning. Moreover, a clear LOS is required, which reduces the usability to outdoor and open indoor environments.

#### Camera

The position of an object in a camera image can be directly related to the real position in the physical world, yielding immediately the position instead of combining several distance measurements. As a clear LOS is required, camera-based positioning does not handle obstacles well; this can be somewhat mitigated by combining several cameras with different positions and angles in order to completely cover an area.

#### Infra-red

Infra-red propagates well within a confined area, but not through walls. This makes the technique ideally suited for in-room detection. Infra-red transmitters and receivers are inexpensive, making infra-red positioning systems cheap and well suited for a number of specific applications but hard to implement as a generic system.

#### 2.1.3 Conclusions

Based on the overiew of different ranging techniques, the following conclusions can be drawn. To devise a positioning system that offers a good – one-shot – accuracy indoors, one needs to use:

- RF signals, because these propagate well indoor, compared to other signals such as light, ultrasound and infra-red and present a good path to silicon integration.

- TOA: which allows to get good accuracy if a wideband signal is used. In the presence of strong reflections which is typical for indoor environments there is no strong correlation between the Received Signal Strength (RSS) [12] and the distance. This requires to determine and use sophisticated path loss models in combination with an accurate characterization of the environment.

- Broadband signals: By measuring the propagation delay of narrowband signals such as WLAN packets [13]. The achieved accuracy is only 8 m, which is not sufficient for most indoor applications. If more broadband signals are used such as UWB signals [14], a higher accuracy can be achieved. The broadband nature of the signal comes from the very short span used in the time domain and hence provides improved resolution to separate the line-of-sight propagated signal from the reflected copies. However, UWB signalling has serious disadvantages with respect to narrowband communication in terms of link budget. When also taking into account the high frequency at which UWB communication usually takes place, it is not surprising the operation range of such systems tends to be significantly lower than that of classical narrowband systems. Since the UWB approach offers superior ranging capacities and the narrowband approach offers superior communication properties due to the higher link budget, the two techniques should be united to combine the benefits and get rid of the drawbacks.

# 2.2 System architecture

To add low cost location awareness to sensor networks, the communication radio should be reused. As concluded in section 2.1.3, to add ranging capabilities to the existing narrowband radio used for communication, the transmitter should be able to transmit a broadband signal. To limit the cost, and to reuse existing transceivers, a fast amplitude modulation technique is proposed. This way the signal will exceed the narrowband communication channel and a broadband signal is formed, which has superior ranging properties. To obtain a spacial resolution of less than 1 m, a steep edge with a rise time of less than 3.3 ns (the spatial resolution divided by the speed of light) is required. The proposed method and the design requirements are described in this section.

# 2.2.1 Ranging Transmitter

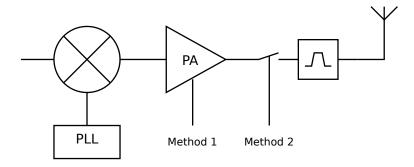

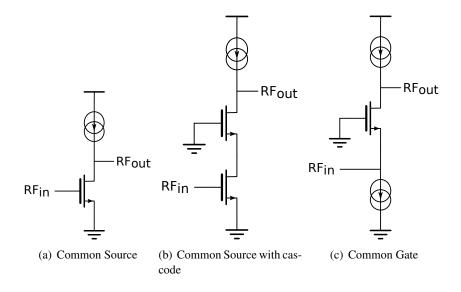

The RF ranging pulse can be generated from a narrow band WLAN signal by forcing a very steep edge at the beginning of the packet. Two different ways of modifying a standard WLAN transmitter are illustrated in figure 2.3.

Figure 2.3: Different methods to generate a ranging pulse.

- 1. Quickly enabling and disabling the Power Amplifier (PA), which varies the generated output power.

- 2. Gating the generated RF power by using RF switches with a fast control interface. The switch can be placed before or after the PA.

To estimate the effect on the performance, the different pulse generation techniques were experimentally evaluated.

#### Method 1: Pulse generation using PA activation

One method to generate steep RF pulses, consists of fast enabling and disabling the PA inside the transmitter chain (by disabling its bias current). The benefit of this approach is that it requires absolutely no additional RF hardware, reducing the implementation cost. The drawback is that the interfacing and even the possibility to quickly change the PA bias depend on the properties of the PA, which differ from product to product. Anyhow, to test the feasibility of the approach, a WLAN Front End Module (FEM) was selected that contains a biasing interface that can be used for generating RF pulses with fast rising edge. The block diagram of the Epic Communications FM7704 FEM [15] is presented in fig. 2.4 showing two PAs, one for the 2.45 GHz Industrial, Scientific and Medical (ISM) and Unlicensed National Information Infrastructure (UNII) band respectively.

Figure 2.4: Block diagram of the FM7704 WLAN front-end module.

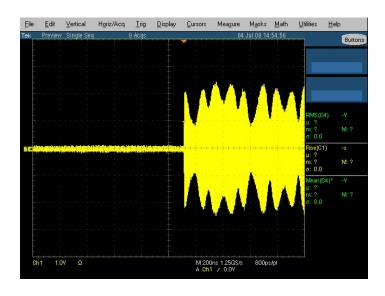

The PA bias interface needs a fixed 2.8~V to operate. To disable the PA this signal was pulled down to 2~V. If the bias is pulled down to as low as 0~V the resulting rise time is lower. The resulting 10~%-90~% rise time was measured to be 2.81~ns. The resulting isolation was 64~dB.

#### Method 2: Pulse generation with a RF switch

The ranging transmitter should generate pulses with rise and fall times that exceed the values typically used for the communication channel. The simplest method to enable a narrowband transmitter to generate wideband RF pulses is to add a RF switch in the main transmitter chain that can toggle fast between its on and off state. The requirements for such a switch are:

- low RF insertion loss

- adequate bandwidth that allows the RF signal to pass

- high switching speeds

To test this concept the Hittite Microwave HMC427LP3 GaAs MMIC positive control transfer switch [16] was selected. Its datasheet states that the switch is able to generate pulses with typical rise and fall times of 2 ns, which is definitely better than what is required. Moreover, the switch can change state with simple 5 V logic interfaces. As the control signals are single ended, a Low Voltage Differential Signaling (LVDS) buffer was required that interfaces from a fast differential LVDS signal and generates a single ended signal with adequately steep rising edges. This Hittite switch can be placed, as explained before, before and after the PA.

The switching was performed on a  $2.45~\mathrm{GHz}$  carrier. The resulting 10~% - 90~% rise time of the generated pulse is  $3.25~\mathrm{ns}$  which is sufficient to perform ranging with adequate accuracy. The position of the switch inside the transmitter chain is arbitrary. The two positions, right before and right after the output PA, were tested. The linearity of the switch is adequate for both locations. The switch itself has limited isolation between the on and off state. During the off-state the transmitted signal should be small enough, so that the first rising edge can be detected without problems. The switch before the PA of the FEM had an isolation of  $54~\mathrm{dB}$  and the switch after the PA of the FEM resulted in  $45~\mathrm{dB}$  isolation. This number is certainly adequate to distinguish the first rising edge of the detected RF pulse.

#### **Bandwidth requirements for Ranging**

Taking the assumption of a first order system, the rise time of the system can be expressed as:

$$t_{r10\% \to 90\%} = 0.35/bandwidth$$

(2.1)

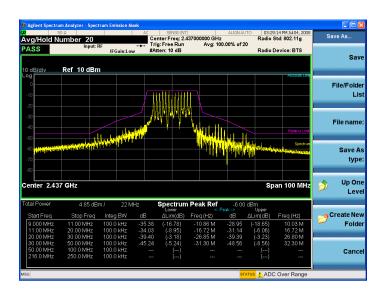

This results in a minimum bandwidth of the pulse generator of at least 100 MHz and preferably more to reach 1 m accuracy. The transmitter should fulfill Federal Communications Commission (FCC) spectral regulations. Normally, the spectrum should be very pure for continuously transmitting equipment, in case the transmission only happens from time to time (e.g. a hundred times per second), as is the case for a ranging transmitter, the average transmitted power is considerably lower and therefore, the spectral congestion will be minimized. This allows to generate a broadband signal which fits in the narrowband spectral mask defined by the FCC regulations. Moreover, the RF pulse generation methods that were discussed before do not offer a very well defined modulation bandwidth. When compared to a WLAN quadrature modulator for example, this bandwidth is very well defined and restricted to the 20 MHz WLAN channels. For the RF pulse generation it is "best effort". Yet previous remarks showed that a wider bandwidth is not a problem as long as the repetition rate is low and the full signal travels through the RF filter without severe deformation. So in conclusion the transmitter bandwidth is chosen large enough not to compromise the measurement accuracy, but not too large to prevent that part of the RF pulse spectrum is filtered by the WLAN RF filter.

#### **Spectral content**

The spectral content of the most simple ranging pulse signal, a gated sine wave, was evaluated experimentally. The power of the ranging signal depends on the repetition rate of the ranging pulse. Considering the maximal packet transmission rate is once every  $80~\mu s$ . The spectrum of the aforementioned pulse generation methods was measured with a spectrum analyser, and with the parameters described in section 17.3.9.2 of the Institute of Electrical and Electronics Engineers (IEEE) 802.11a standard [17]. The pulse width was chosen at 11 ns, which is appreciably higher than the rise and fall times after the receiver filtering so the ranging pulse can be detected at maximum power. The chosen center frequency equals  $5.15~\rm GHz$ , but similar conclusions could be made when modulating a carrier from the ISM band.

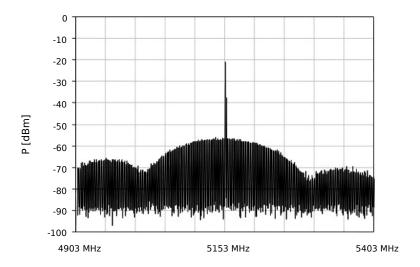

Figure 2.5: Spectrum of a ranging pulse.

Figure 2.5 shows the measured spectrum of the signal with  $10~\mathrm{dBm}$  peak output power. The plot is worth a closer look: the RF carrier clearly stands out. When transmitting an output signal of  $17~\mathrm{dBm}$  with a duty cycle of  $11~\mathrm{ns}$  each  $80~\mu\mathrm{s}$ , the resulting output power is  $17+10\cdot\log11/80000=-22~\mathrm{dBm}$ . The repetition rate can be measured via the spacing of the notches of the resulting sync spectrum,  $80~\mu\mathrm{s}$  corresponds with  $6~\mathrm{MHz}$ . The isolation is estimated to be close to  $30~\mathrm{dB}$ , a typical value for GaAs switches.

## 2.2.2 Ranging Receiver

The ranging transmitter is a narrowband system with a minimum of modifications to realize the broadband ranging pulse. On the receiver side the broadband modulated RF pulses need to be detected. Broadband detection is needed to achieve adequate accuracy for the ranging event. Different solutions exists:

- threshold detection with a RF power detector,

- downconversion with a baseband threshold detector,

- downconversion with a fast Analog to Digital Converter (ADC) and threshold detection in the digital domain.

#### RF power detector

A RF power detector extracts the RF signal after the antenna or after the Low Noise Amplifier (LNA) in case its bandwidth is adequate, and performs threshold detection on this signal. This approach is really simple, and requires very little hardware.

Therefore this approach was selected at first to test the feasibility of pulse transmission and reception after propagation through a warehouse-like environment with very little interfering signals. The RF detector was implemented by using a fast oscilloscope which was able to digitize the RF signal in real time. The threshold detection was performed offline by means of software processing.

On the downside, the feasiblity is questionable because:

- Building an RF detector with more than 100 MHz bandwidth which works up to 2.5 GHz is very hard, since it would require a selective filter (very high Q-factor) to attenuate interferers.

- This solution suffers from limited sensitivity and interference rejection. The only bandwidth limitation in the system is the RF band selection filter (ISM/UNII) which is not adequate. Out-of-band blockers can distort the measurement tremendously due to the high detector bandwidth.

#### Downconversion with a baseband threshold detector

If the RF signal is first downconverted, adequate filtering can be implemented before the threshold detection. Moreover, it is much more feasible to design a fast baseband threshold detector rather than an RF threshold detector. The downside of this approach is that an additional wideband demodulator is required after which the baseband detector can perform the ranging. Moreover a quadrature downconversion is required which doubles the amount of detection electronics.

#### Downconversion with a fast ADC

A threshold detector is in fact nothing more than a 1 bit ADC. To have more accuracy, an ADC with more bits can be used. This is only possible after downconversion because ADCs which sample at RF are very expensive and consume a lot of power. A bonus to having more bits is that other offline processing techniques can be used in order to improve the signal to noise ratio. Specifically correlation techniques could prove very useful to reach

higher distances with a similar bandwidth. The downside of this approach is that the ADC adds quite some additional hardware to the system and increases the cost of the transceiver.

# 2.2.3 Bandwidth requirements

Setting forward an accuracy of 1 meter in 95% of the cases and given the speed of light in air, the uncertainty on the arrival of the pulse in a one-dimensional positioning system is limited to 3.33 ns. In the three dimensional case, three of four delay measurements should be combined to achieve X, Y and Z coordinates. This triangulation process is a research topic covered by the VUB and Essensium in a closely related IWT project.

In case of threshold detection, the threshold will be fixed  $10\ dB$  above the noise floor not to trigger too many false alerts. On the other hand, the power of the received pulses varies as the channel changes due to environment changes and distance variations. Therefore the trigger moment in the rising edge of the pulse will be different from case to case.

It is safe to assume that this jitter – and hence the measurement accuracy – will be smaller than the 10-90~% rise time. In case a very strong pulse arrives the ranging pulse will cross the threshold already at its 10~% level, while a pulse at the edge of sensitivity will cross the threshold at its 90~% level.

$$t_r = \frac{0.35}{bandwidth} \tag{2.2}$$

By means of equation 2.2, which expresses the  $10-90\,\%$  rise time of a first order system, the acceptable inaccuracy of  $3.33\,\mathrm{ns}$  on the delay estimation can now be expressed in terms of a minimum receiver bandwidth of  $100\,\mathrm{MHz}$ . On the other hand, a bandwidth limitation is mandatory to obtain a good receiver SNR, since in case the received pulse power is very small, noise will contribute to the estimation errors. In practice, the receiver bandwidth will be of higher order, since multiple poles of different building blocks will be present. In order to maintain sufficient rise time, the minimum required system bandwidth needs to be increased.

#### 2.2.4 Frequency selection and path loss

An important specification of the system consists of the description of the frequency bands to be used. Different unlicensed frequency ranges exist among which the ones used for WLAN, UWB, Zigbee, ... To make a well-founded decision on the frequency range, path loss and signal to noise ratio

are compared. Frequency bands lower than the 2.4 GHz ISM band don't offer sufficient bandwidth which would result in interference issues.

ADS Ptolemy simulations were performed to asses the influence of different channel models, both urban and suburban, which take large scaling effects (reflections via the ground, buildings, and other obstacles) into account and a simpler path loss based channel with a loss of  $1/r^{3.3}$ , thus independent of frequency. Both the urban and suburban models in the simulator are based on the classical Hata model [18].

| Pathloss model | Pathloss (dB) | Received Power (dBm) | SNR (dB) |

|----------------|---------------|----------------------|----------|

| urban          | 105           | -89                  | -4.0     |

| suburban       | 89.3          | -73.3                | 11.5     |

| $1/r^{3.3}$    | 96            | -80                  | 4.9      |

Table 2.1: Simulation results for a carrier frequency of 5.25 GHz.

| Pathloss model | Pathloss (dB) | Received Power (dBm) | SNR (dB) |

|----------------|---------------|----------------------|----------|

| urban          | 96.5          | -80.5                | 4.5      |

| suburban       | 83.6          | -67.6                | 17.4     |

| $1/r^{3.3}$    | 96            | -80                  | 4.9      |

Table 2.2: Simulation results for a carrier frequency of 2.45 GHz.

The simulation results for a  $16~\mathrm{dBm}$  transmitter at  $5.25~\mathrm{GHz}$  and a receiver with bandwidth of  $200~\mathrm{MHz}$  and a noise figure of  $6~\mathrm{dB}$ , modeled as additive white noise at the receiver input with spectral density of  $-168~\mathrm{dBm/Hz}$  resulting in a total received noise of  $-85~\mathrm{dBm}$  at  $50~\mathrm{m}$  are summerized in table 2.1. The results for a  $2.45~\mathrm{GHz}$  transmitter-receiver combination are shown in table 2.2.

To obtain a high ranging accuracy of up to  $50~\mathrm{m}$ , the  $2.45~\mathrm{GHz}$  frequency band is the obvious choice, since it offers the highest SNR in all cases.

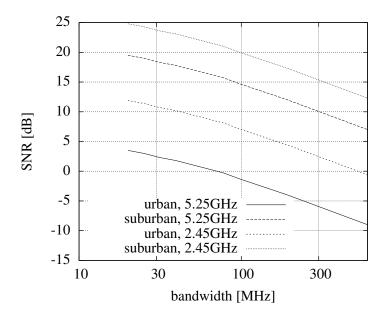

# 2.2.5 Signal to noise ratio versus bandwidth

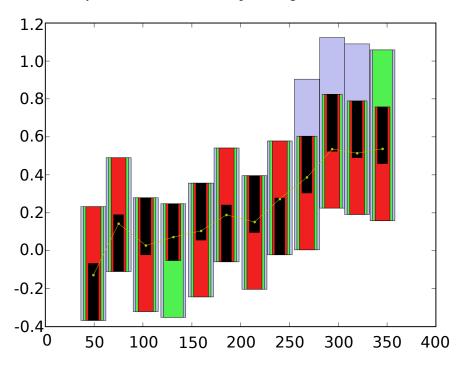

To investigate the effect of the receiver bandwidth on the SNR of the detected signal, the bandwidth is swept from 20 MHz to 600 MHz in a system level Advanced Design System (ADS) model, and the corresponding SNRs are plotted in figure 2.6. It reveals that the SNR of the received pulse depends on the receiver bandwidth. Indeed reducing the receiver bandwidth reduces the noise bandwidth and results in a lower effective integrated noise. Of course caution must be taken that the bandwidth reduction does not compromise the spatial accuracy of the ranging estimation process.

The limited rise time also decreases the accuracy of the detected delay in case the received pulse power is varied from the maximum to the minimum. In case the bandwidth is equal to  $125~\mathrm{MHz}$ , the rise time equals  $2.8~\mathrm{ns}$ , which corresponds to a maximum distance error under  $1~\mathrm{m}$ . Therefore a  $125~\mathrm{MHz}$  bandwidth is certainly adequate, but results in a little worse SNR. Note that the definition of this bandwidth is done in base band. A  $125~\mathrm{MHz}$  bandwidth would result in a  $\pm 125~\mathrm{MHz}$  or  $250~\mathrm{MHz}$  pass band centered on the RF carrier of  $2.45~\mathrm{GHz}$  or  $5.25~\mathrm{GHz}$ .

Figure 2.6: Variation of SNR with respect to receiver bandwidth.

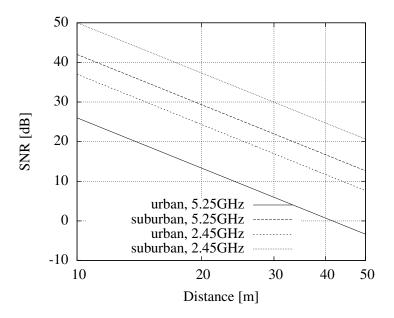

# 2.2.6 Signal to noise ratio versus distance

To analyse the effect of the ranging distance on the SNR at the receiver side, the distance is swept from  $10~\mathrm{m}$  to  $50~\mathrm{m}$  and the corresponding SNRs are plotted in figure 2.7. All four cases, as expected, clearly show that the SNR at receiver side is a logarithmic function of the ranging distance.

Figure 2.7: Variation of SNR with respect to the distance between RX and TX.

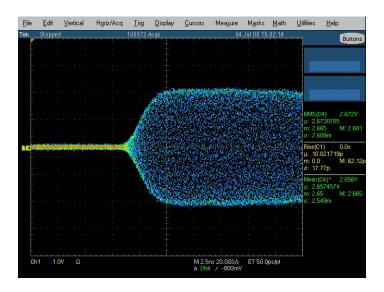

# 2.3 Proof-of-concept

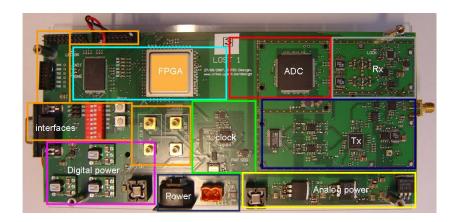

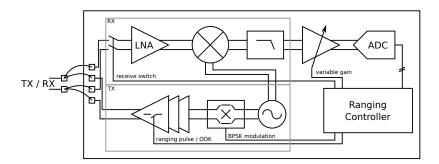

To prove the concept of indoor ranging with sub-meter accuracy in the 2.45 GHz ISM band, a ranging transceiver has been developed, by making use of off-the-shelf components. The architecture of the prototype is shown in figure 2.8. A picture of the resulting PCB design is shown in figure 2.9. It is an 8 layer board made of standard Flame Retardant 4 (FR4) material, containing a total of 593 components including passives. The board includes all functions needed for ranging: the RF front-end, baseband ADC, filtering, a high-speed Field-Programmable Gate Array (FPGA), etc. While designing the board, special care was taken to ensure a proper power supply distribution, maximize signal integrity and reduce crosstalk, etc.

The operation of the board can be configured in various ways:

- with Dual In-line Package (DIP) switches,

- via push buttons,

- and via standard interfaces such as: serial port, Serial Peripheral Interface bus (SPI), Low Pin Count interface (LPC) and General Purpose Input Output (GPIO).

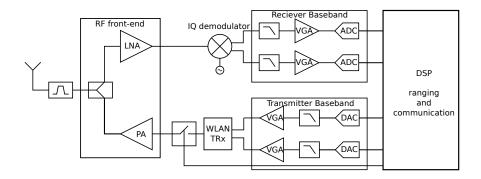

Figure 2.8: Functional block diagram of the ranging transceiver.

Figure 2.9: Ranging transceiver PCB.

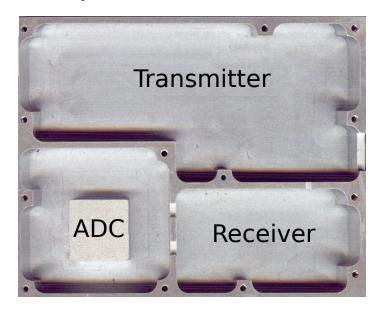

An aluminum cover, shown in figure 2.10, was milled to shield the RF part. Measurements confirm a  $0.5~\mathrm{dB}$  improvement of the Receiver (RX)

noise figure. Since the performance is sufficient without shielding, most experiments were performed without.

Figure 2.10: Metal enclosure to shield the sensitive PCB parts.

# 2.3.1 Ranging Transmitter

The transmitter design offers 3 possibilities to generate the ranging pulse: by switching the bias of the PA or by using an RF switch before or after the PA (see figure 2.3).

- The fast enabling of the PA bias provides the shortest rise time but relies on the specific (GaAs) PA component used. Implementation in Complementary Metal Oxide Semiconductor (CMOS) technology may not be feasible.

- From a ranging point of view, both locations of the RF switch provide sufficient isolation and rise time. As this is a more general solution, this will be preferred. Both locations of the RF switch result in a similar rise time. Since the signals in front of the PA are much smaller, this is the most obvious location to place the switch. This will result in higher isolation and lower distortion.

To demonstrate that communication signals can indeed accommodate the proposed ranging technique, a modified WLAN packet is used, contain-

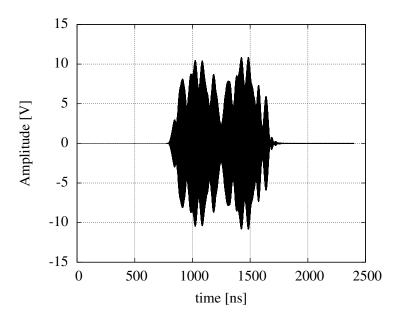

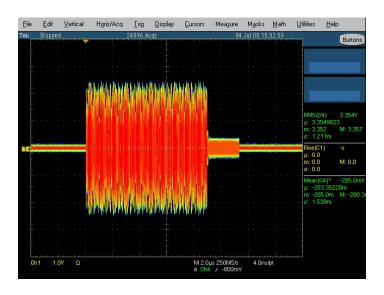

ing only a short preamble to be used for Automatic Gain Control (AGC), timing synchronization, frequency offset estimation, ... The first symbol of the short preamble will be switched to generate the fast edge. These ranging packets are generated using a Digital to Analog Converter (DAC) and upconverted to 2.45 GHz by a WLAN transceiver chip. In between the WLAN transceiver and the PA, a high speed switch is used to generate a fast rising edge at the beginning of the ranging packet. The standard short preamble waveform duration is 8  $\mu s$  (10 "short training sequences", 800 ns long, shown in figure 2.11 ) and contains only 12 (out of 52) carriers. Due to the Orthogonal Frequency-Division Multiplexing (OFDM) multicarrier modulation, the burst envelope is not constant, but has a certain peak-to-average ratio.

Figure 2.11: WLAN short preamble.

#### 2.3.2 Ranging Receiver

The ranging receiver has a zero-Intermediate Frequency (IF) architecture, as most wireless transceivers nowadays. The baseband system contains a variable gain amplifier which can be used to compress the dynamic range of the received signals. If required the gain setting can be fixed for a given ranging distance, while saturating the amplifier annex ADC at short dis-

tances. The required gain range is approximately 40 dB, and the RF bandwidth is up to 200 MHz (2 times the 100 MHz baseband bandwidth).

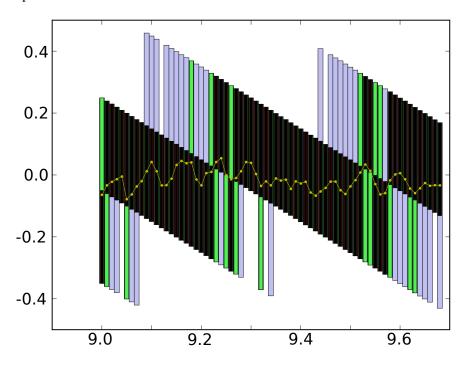

To limit the receiver's bandwidth a differential 5th order Bessel filter (for minimal pulse distortion) with following specifications is implemented: baseband bandwidth of 100 MHz and improved coupling between in- and output (to reduce the attenuation at high frequencies). Care was taken to match the impedance of the In phase – Quadrature (IQ) demodulator which is 65  $\Omega$  in parallel with 5 pF to the input impedance of the AD8369 (Variable Gain Amplifier (VGA)) which is 200  $\Omega$ .

According to Nyquist, the ADC will require a sampling speed of at least 400 Msps, and preferably not much higher as this might cause problems with the high-speed interfacing of the data lines to the FPGA. The National Semiconductor ADC08D500 8-bit ADC is able to sample at speeds up to 500 Msps, and contains two ADCs per package. The ADC output contains demultiplexers, yielding 32 LVDS signals at 250 Msps.

The analysis of the Noise Figure (NF) of the receive path is shown in table 2.3. A legend with the stage numbers can be found in table 2.4. The NF of a cascade of building blocks depends on both the individual noise figures as well as their respective gains. This analysis shows that the RX path requires a second LNA in front of the LT5575 IQ demodulator to achieve a low noise figure (4.65 dB). The latter is dominated by the first LNA (3.0 dB), however, increased by the loss of the band pass filter (1.5 dB) giving 4.5 dB. Without the second LNA, the NF of the IQ demodulator will augment the total receiver NF.

The AD8369 VGA can vary the gain over  $40~\mathrm{dB}$  and the HMC605LP3 LNA offers a bypass mode to decrease the gain by  $20~\mathrm{dB}$ . This high dynamic range is adequate for ranging up to  $500~\mathrm{m}$ .

| stage nr  |     | 1    | 2    | 3    | 4     | 5     | 6     | 7     |

|-----------|-----|------|------|------|-------|-------|-------|-------|

| Gain (dB) | min | -1.5 | 10.0 | -1.9 | 2.0   | -0.5  | -10.0 | -3.0  |

|           | max | -1.5 | 10.0 | 20.0 | 2.0   | -0.5  | 35.0  | -3.0  |

| Cascade   | min | -1.5 | 8.5  | 6.6  | 8.6   | 8.1   | -1.9  | -4.9  |

| Gain (dB) | max | -1.5 | 8.5  | 28.5 | 30.5  | 30.0  | 65.0  | 62.0  |

| NF (dB)   | min | 1.5  | 3.0  | 1.1  | 15.7  | 0.5   | 49.2  | 6.0   |

|           | max | 1.5  | 3.0  | 1.1  | 15.7  | 0.5   | 7.2   | 6.0   |

| Cascade   | min | 1.50 | 4.50 | 4.56 | 10.32 | 10.33 | 41.10 | 41.11 |

| NF (dB)   | max | 1.50 | 4.50 | 4.56 | 4.64  | 4.64  | 4.65  | 4.65  |

Table 2.3: Noise figure analysis of the receive path.

| stage 1 | bandpass filter                                          |

|---------|----------------------------------------------------------|

| stage 2 | LNA of the RF Front-end module                           |

| stage 3 | 2nd LNA                                                  |

| stage 4 | Demodulator                                              |

| stage 5 | Low pass filter                                          |

| stage 6 | VGA                                                      |

| stage 7 | resistor divider (due to the input impedance of the ADC) |

Table 2.4: Description of the receiver stages.

#### 2.3.3 Clock synthesis

The RF modulator and demodulator and especially the fast ADC require a good and dedicated high speed clock. The ADC's clock could be generated directly by a  $450~\mathrm{MHz}$  Surface Acoustic Wave (SAW) oscillator and could be divided down for the other components. However, this solution is expensive and not flexible. An alternative is to use a clock synthesis IC that converts a low-frequency crystal oscillator clock up to the value required for the ADC. The resulting clock jitter is higher but still adequate for our application ( $<10~\mathrm{ps}$ ). An example is the NBC12439 family from On Semi, which allows clock synthesis between  $50~\mathrm{MHz}$  and  $800~\mathrm{MHz}$ . Other clock synthesizers use external Voltage Controlled Oscillators (VCOs) with lower phase noise, which result in lower jitter on the synthesized clock, but provide a lower frequency flexibility and a higher cost.

The ADCs and the FPGA require a coherent differential clock. There are, however, other components which require other clock frequencies. The RF synthesizer can accept clocks from 10 up to 250 MHz. The WLAN transmitter requires a clock between 20 and 44 MHz. The NBC12439 requires a clock between 10 and 20 MHz. The logic conclusion is to select 20 MHz as reference oscillator. The 20 MHz CMOS clock will be distributed over the different components by a 1:4 clock buffer, after which it is applied to the NBC12439 (which generates a 500 MHz clock for the ADC), the RF synthesizer, the FPGA and the WLAN transmitter. The multiplied 500 MHz clock which drives the ADCs will be split and routed to the ADC and FPGA. This will require an additional differential clock splitter. All clock generation/distribution components are in the digital supply domain, except the Phase Locked Loop (PLL) RF synthesizer, which uses the 3.3 V analog supply.

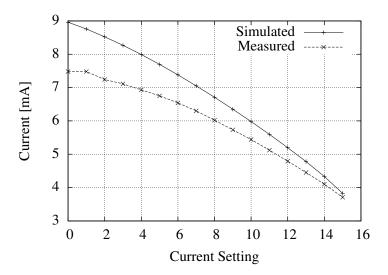

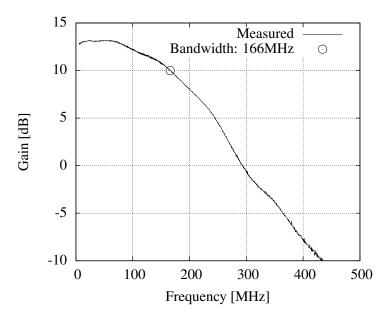

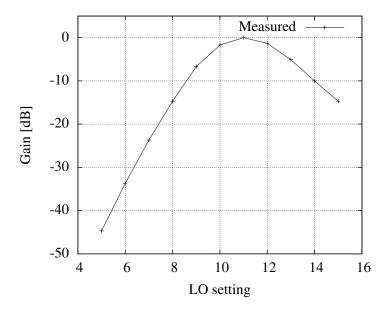

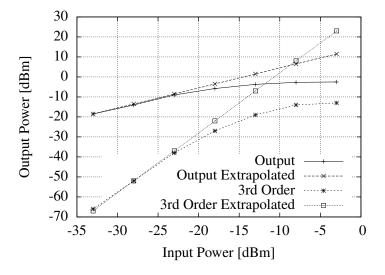

#### 2.3.4 Power supplies