Hybride monolithische integratie van hoogvermogen-DC-DC-convertoren in een hoogspanningstechnologie

Hybrid Monolithic Integration of High-Power DC-DC Converters in a High-Voltage Technology

Jindrich Windels

Promotoren: prof. dr. ir. J. Doutreloigne, dr. ir. A. Monté Proefschrift ingediend tot het behalen van de graad van Doctor in de Ingenieurswetenschappen: Elektrotechniek

Vakgroep Elektronica en Informatiesystemen Voorzitter: prof. dr. ir. J. Van Campenhout Faculteit Ingenieurswetenschappen en Architectuur Academiejaar 2013 - 2014

ISBN 978-90-8578-673-3 NUR 959

Wettelijk depot: D/2014/10.500/19

Universiteit Gent Faculteit Ingenieurswetenschappen en Architectuur Vakgroep Elektronica en Informatiesystemen Centre for Microsystems Technology (CMST) Technologiepark 914A B-9052 Zwijnaarde, België

Tel.: +32-9-264 53 50 Fax.: +32-9-264 53 74

Promotoren: Prof. Dr. ir. Jan Doutreloigne

Dr. ir. Ann Monté

Examencommissie: Prof. Dr. ir. Hendrik Van Landeghem - Voorzitter

Dr. ir. Herbert De Pauw - Secretaris Prof. Dr. ir. Johan Bauwelinck Prof. Dr. ir. Marnix Botte Prof. Dr. ir. Johan Driesen ir. Edmond Op de Beeck

Dit werk kwam tot stand in het kader van een specialisatiebeurs van het Agentschap voor Innovatie door Wetenschap en Technologie (IWT).

Proefschrift ingediend tot het behalen van de graad van Doctor in de Ingenieurswetenschappen: Elektrotechniek Academiejaar 2013-2014

#### Dankwoord

Er was eens, heel lang geleden: mijn eerste dag bij CMST, waarbij het de bedoeling was om onderzoek te doen rond schakelende convertoren met geïntegreerde hoogspanningstransistoren en daar na verloop van tijd een doctoraat over te schrijven. Een goeie vijf jaar na deze eerste dag was het zover: de eerste ruwe versie van dit boek was er. Zowel het boek als het werk ernaartoe zijn iets heel anders geworden dan ik mij indertijd had kunnen inbeelden, maar ik kan met veel plezier terugkijken op de afgelopen jaren. Het onderzoek en dit boek waren er nooit gekomen zonder de hulp, medewerking en gezelschap van een groot aantal mensen, en deze wil ik hierbij graag even vermelden.

Werk-gerelateerd denk ik hierbij in de eerste plaats aan André, om in het verleden de veelzijdige en inspirerende groep mensen die samen CMST vormen samen te brengen en mij daar ook een plekje bij te bieden. Zijn plaats als dagelijkse leider van de groep is ondertussen ingenomen door het CMST management team, bestaande uit Jan, Jan, Herbert, Geert en Johan, die ik wil bedanken om de ingeslagen weg verder te bewandelen.

Mijn promotoren, Jan en Ann wil ik bedanken om mij tijdens het onderzoek steeds zoveel mogelijk mijn eigen weg te laten kiezen, voor het niet aflatende optimisme en om altijd te blijven geloven dat het werk van de afgelopen jaren uiteindelijk tot dit boek zou kunnen leiden. Tijdens het eigenlijke schrijven kwam vooral de directe feedback van Ann op de ruwe versies goed van pas om op tijd bij te kunnen sturen. De collega's uit het smart-power team die geen promotor waren hebben dankzij de (bijna) wekelijkse design-babbel elk op hun eigen wijze bijgedragen met hun ervaring en min of meer gerelateerd werk, dus bij deze ook bedankt aan Stefaan, Vincent, Benoît, Herbert, Jodie, Pieter, Dries en Benoit. Deze laatste verdient een speciale vermelding om met handen en voeten de fijne details over werking en opbouw van vermogenstransistoren duidelijk te maken. Graag wil ik ook van de gelegenheid gebruik te maken om alle leden van de examencommissie te bedanken voor hun bereidheid om in de jury te zetelen en voor hun opmerkingen en correcties bij de ingediende versie van het proefschrift.

Aan de praktische kant van het verhaal moet ik Peter en Bjorn bedanken voor het geduldig blijven uitleggen waarom mijn zoveelste creatieve wirebond-strategie toch niet zo vanzelfsprekend was en uiteraard ook voor de uitvoering van de iets realistischere ontwerpen. Bedankt aan Filip voor de kleine en grote werkjes in het atelier en daarbuiten, en Peter, Ronny en Michiel om de hardware, software

en het netwerk zoveel mogelijk in goeie banen te leiden. Nadine en Dieter verdienen hier hun plekje door hun vele inspanningen om CMST zowel op gebied van mensen als van toestellen veilig en operationeel te houden. Katrien en Ilse wil ik graag bedanken voor het afhandelen van de bergen administratie en bestellingen. Uiteraard mag ik ik bij het bedanken van de mensen die dit werk mogelijk gemaakt hebben Alcatel-Lucent niet vergeten, vooral Eddy om af en toe een blik te gunnen in een aantal aspecten van convertor-ontwerp voor toepassingen in de echte wereld, en Marnix om de financiële kant van het verhaal rond te helpen krijgen.

Naast de technische kant is er ook het sociale aspect van CMST, met naast de etentjes en pizza-events een jaarlijks hoogtepunt in de CMST BBQ. Dankzij Tom, Bram en Jelle, die ongeveer tegelijk met mij bij CMST begonnen zijn en waarmee ik een aantal jaar samen de BBQ georganiseerd heb waren de voorbereidende vergaderingen even leuk als het eigenlijke event. De gezellige gesprekken aan tafel over de middag hadden diverse onderwerpen, maar ik wil Steven, Bram en Kristof in het bijzonder bedanken om mij (of ik het nu wilde of niet) op de hoogte te houden over de koers, voetbal en boer zoekt vrouw.

Uiteraard horen hier ook mijn bureaugenootjes uit de periode voor ik vergroeide met het elektronicalabo thuis: Rik, Jeroen, Benoît, Jan, Tom, Sheila, David, Luigi, Enkhbold, Sandeep, Amir en Sanjeev. Bedankt voor de gezellige sfeer! Ann wil ik bij deze nog eens extra in de bloemetjes zetten voor de aangename momenten, zowel bij de samenwerking op het werk als in de vrije tijd. And of course, I shouldn't forget the people from the occasional international after-work movies and drinks, so thanks to Pankaj, Tom, Kamal, Bram, Sandeep, Jeroen, Filip, Rik and Nuria for the nice times.

Uiteraard is er nog een leven buiten CMST, en hierbij wil ik Christophe bedanken voor de vele aangename avonden en om de link te vormen naar de kennismaking met zijn collega's van INTEC\_design. De vrienden uit het verre West-Vlaanderen (met enclave in Antwerpen) mogen uiteraard ook niet vergeten worden: Metjew, Yannick, Pieter, Thibaut, Yann, Mathieu, Jelle, Seba, Mathias en Boris. We zien elkaar minder vaak dan vroeger, maar dat maakt het niet minder aangenaam als we elkaar nog eens terug zien. Ook jullie zijn bedankt voor de leuke reizen, weekends en avondjes uit!

En uiteraard, last but not least: bedankt aan mijn ouders en zus om er gedurende de afgelopen 30 jaar altijd te zijn wanneer het nodig was.

Gent, 14 maart 2014 Jindrich Windels

# Table of contents

| Та  | ble o                    | f conte                                                                            | ents                                                            | Vii                                                 |

|-----|--------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------|

| Lis | st of                    | figures                                                                            | <b>5</b>                                                        | хi                                                  |

| Lis | st of                    | tables                                                                             |                                                                 | χV                                                  |

| Sa  | men                      | vatting                                                                            | J                                                               | xix                                                 |

| Su  | mma                      | ary                                                                                |                                                                 | xxiii                                               |

| 1   | 1.1<br>1.2<br>1.3<br>1.4 | Outlin<br>Resea<br>Resea<br>1.4.1                                                  | uction                                                          | . 3<br>. 4<br>. 4<br>. 5                            |

| 2   | 2.1<br>2.2<br>2.3<br>2.4 | Introd<br>Efficie<br>The ri<br>Select<br>2.4.1<br>2.4.2<br>2.4.3<br>2.4.4<br>Concl | efficient energy distribution through voltage conversion uction | . 8<br>. 10<br>. 12<br>. 12<br>. 13<br>. 14<br>. 15 |

| 3   | 3.1                      | Introd                                                                             | optimization for smart-power converters uction                  |                                                     |

viii Table of contents

|   |      | 3.2.1 Zero size                                                 |

|---|------|-----------------------------------------------------------------|

|   |      | 3.2.2 Zero cost                                                 |

|   |      | <b>3.2.3</b> Zero dissipation                                   |

|   |      | 3.2.4 Additional properties                                     |

|   |      | <b>3.2.5</b> Conclusions                                        |

|   | 3.3  | Semiconductor devices                                           |

|   |      | <b>3.3.1</b> Transistors                                        |

|   |      | 3.3.2 Diodes and synchronous rectifiers                         |

|   | 3.4  | Smart-power technologies                                        |

|   | 3.5  | Cost function for ASIC implementation                           |

|   |      | 3.5.1 Silicon area vs. expected dissipation                     |

|   |      | 3.5.2 N type vs. P type                                         |

|   | 3.6  | Linear voltage regulators                                       |

|   |      | 3.6.1 Shunt linear regulator                                    |

|   |      | 3.6.2 Series linear regulator                                   |

|   |      | 3.6.3 Discussion                                                |

|   | 3.7  | Switching voltage converter topologies                          |

|   |      | 3.7.1 Switched capacitor                                        |

|   |      | 3.7.2 Non-isolated switched inductor                            |

|   |      | 3.7.3 Transformer-isolated switched inductor converters 57      |

|   | 3.8  | Optimal topology for the telecom reference applications 71      |

|   |      | 3.8.1 48 Volt to 12 Volt                                        |

|   |      | 3.8.2 48 Volt to 5 Volt                                         |

|   | 3.9  | Conclusions                                                     |

|   | Refe | rences                                                          |

| 4 | Fnal | bling efficient smart-power integration 83                      |

| • | 4.1  | Introduction                                                    |

|   | 4.2  | From the ideal circuit to the real world                        |

|   | ¬.∠  | 4.2.1 A more realistic inductor and transformer                 |

|   |      | 4.2.2 A more realistic capacitor                                |

|   |      | 4.2.3 A more realistic switch                                   |

|   |      | 4.2.4 Realistic switches need drivers                           |

|   |      | 4.2.5 Inductive parasitics                                      |

|   | 4.3  | Handling the voltage overshoot                                  |

|   |      | 4.3.1 Increasing the device voltage rating                      |

|   |      | 4.3.2 Clamp circuits                                            |

|   |      | 4.3.3 Efficiency of energy recovering voltage clamp circuits 90 |

|   | 4.4  | The asynchronous active voltage clamp                           |

|   |      | 4.4.1 Concept                                                   |

|   |      | 4.4.2 Discussion                                                |

|   | 4.5  | Proof-of-concept                                                |

|   | 4.6  |                                                                 |

| Table of contents | ix |

|-------------------|----|

|-------------------|----|

|   |      | 4.6.1   | Preliminary design considerations          | 98  |

|---|------|---------|--------------------------------------------|-----|

|   |      | 4.6.2   | System partitioning                        | 100 |

|   |      | 4.6.3   | Control block                              | 101 |

|   |      | 4.6.4   | Comparison with dissipative clamp circuits | 102 |

|   | 4.7  | Conclu  | usions                                     | 113 |

|   | Refe | rences  |                                            | 114 |

| 5 | Loa  | d-dene  | ndent efficiency optimization              | 117 |

| • | 5.1  |         | uction                                     | 117 |

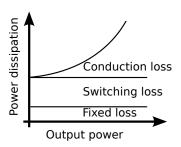

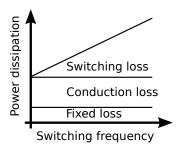

|   | 5.2  |         | erms in switching converters               | 118 |

|   | 5.3  |         | sing the switching converter               | 121 |

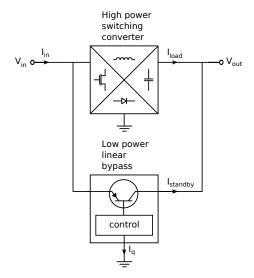

|   | 5.5  | 5.3.1   | Linear regulator bypass                    | 121 |

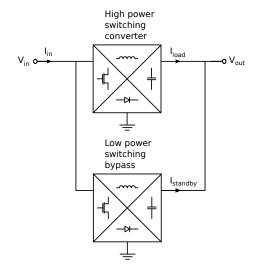

|   |      | 5.3.2   | Switching converter bypass                 | 121 |

|   | 5.4  |         | ring the switching converter               | 123 |

|   | 5.4  | 5.4.1   | Effective switching frequency reduction    | 125 |

|   |      | 5.4.1   |                                            | 123 |

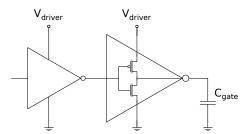

|   |      | 5.4.2   | Dynamic gate drive voltage optimization    | 127 |

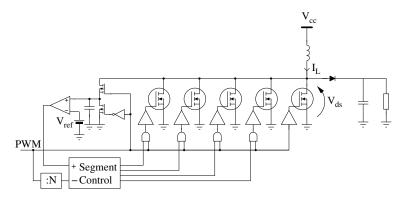

|   | 5.5  | 00      | MOSFET segmentation                        | 131 |

|   | 5.5  |         | natic adaptive MOSFET segmentation         |     |

|   | F 0  | 5.5.1   | Current estimation                         | 131 |

|   | 5.6  |         | of-concept                                 | 134 |

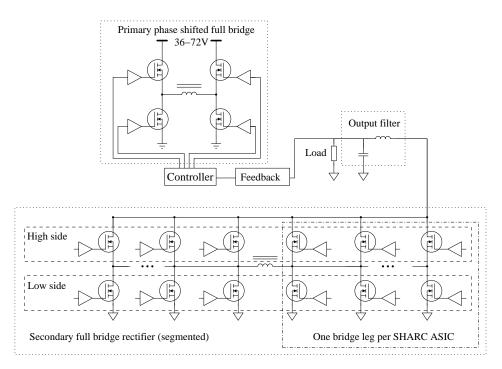

|   | 5.7  |         | implementation                             | 137 |

|   |      | 5.7.1   | Power stage dimensioning                   | 139 |

|   |      | 5.7.2   | Optimal segmentation                       | 140 |

|   |      | 5.7.3   | Optimized driver size and gate voltage     | 142 |

|   |      | 5.7.4   | High-voltage driver for external MOSFET    | 146 |

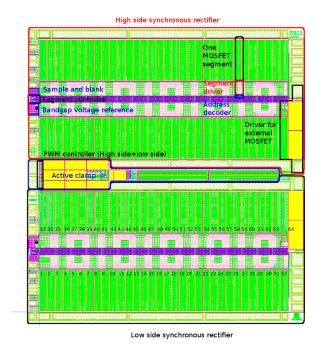

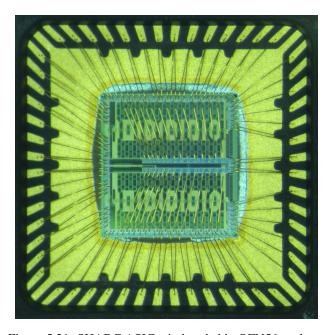

|   |      | 5.7.5   | ASIC layout                                | 147 |

|   |      | 5.7.6   | ASIC packaging and test-board              | 148 |

|   |      | 5.7.7   | ASIC characterization                      | 150 |

|   | 5.8  |         | usions                                     | 150 |

|   | Refe | rences  |                                            | 153 |

| 6 | Con  | clusior | ns and final remarks                       | 157 |

| • | 6.1  |         | achievements                               | 157 |

|   | 6.2  |         | work                                       | 159 |

|   | J    |         |                                            | 10) |

# List of Figures

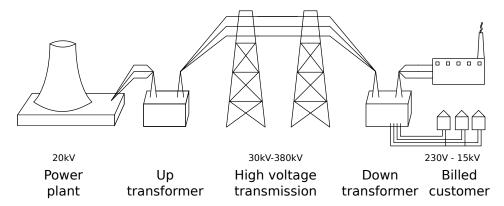

| 2.1  | Schematic overview of a distribution network for electrical energy .                        | 8  |

|------|---------------------------------------------------------------------------------------------|----|

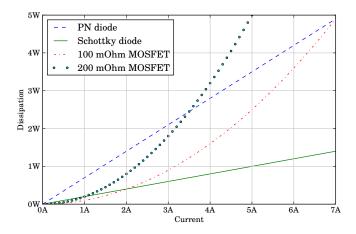

| 3.1  | Conduction loss with PN diode, Schottky diode, and synchronous rectification versus current | 27 |

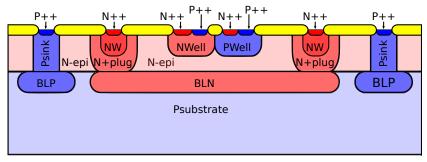

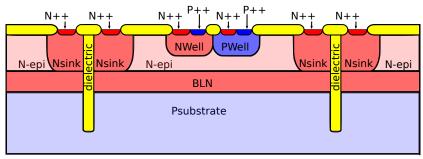

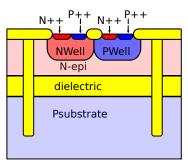

| 3.2  | Cross section of isolation structures in smart-power technologies .                         | 30 |

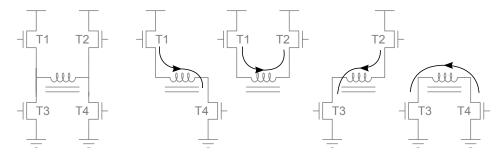

| 3.3  | Current paths in the primary side of a full bridge                                          | 33 |

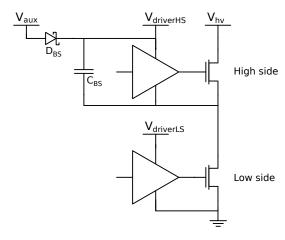

| 3.4  | Bootstrap power supply for generating a floating supply voltage to                          |    |

| ۰.   | drive an N-type high-side switch                                                            | 34 |

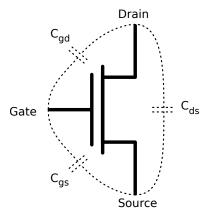

| 3.5  | Parasitic capacitors indicated on an N-channel MOSFET                                       | 36 |

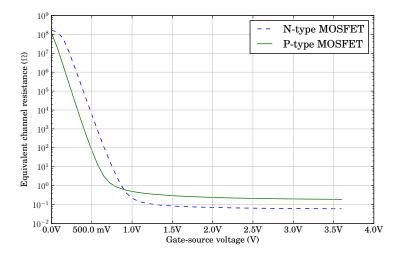

| 3.6  | Channel resistance in function of gate-source voltage for 1 mm <sup>2</sup>                 | 20 |

|      | N-type and P-type DMOS devices in the I3T50 Technology                                      | 39 |

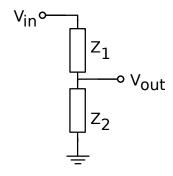

| 3.7  | Voltage divider                                                                             | 41 |

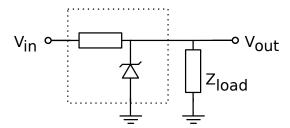

| 3.8  | Shunt voltage regulator                                                                     | 42 |

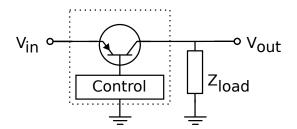

| 3.9  | Series linear regulator                                                                     | 43 |

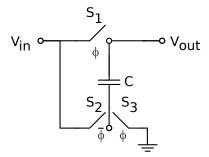

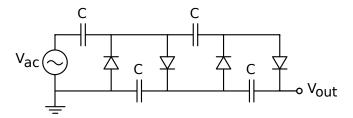

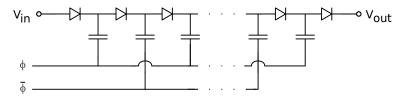

|      | Basic voltage doubler                                                                       | 46 |

|      | The Greinacher voltage doubler                                                              | 47 |

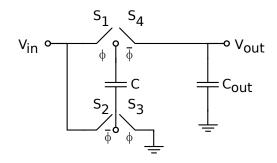

|      | A 2-stage Greinacher/C-W voltage multiplier                                                 | 47 |

| 3.13 | A clocked 2-stage Greinacher/C-W voltage multiplier, showing the                            |    |

|      | stray capacitors to ground                                                                  | 48 |

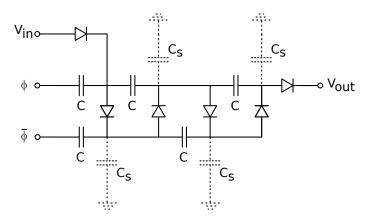

|      | Dickson charge pump                                                                         | 49 |

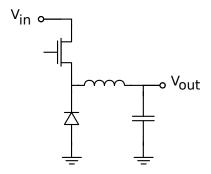

|      | Buck converter circuit                                                                      | 53 |

| 3.16 | Boost converter circuit                                                                     | 55 |

| 3.17 | Buck-boost converter circuit                                                                | 57 |

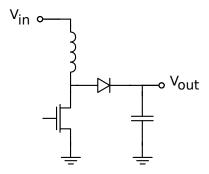

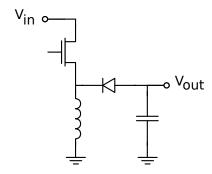

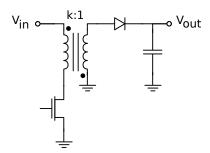

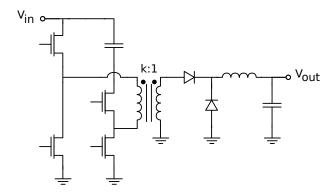

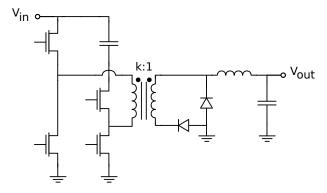

| 3.18 | Flyback converter circuit                                                                   | 58 |

| 3.19 | 1-Transistor forward converter circuit with a transformer reset winding                     | 60 |

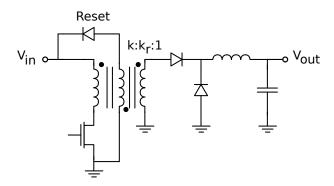

| 3.20 | 2-Transistor Series forward converter circuit                                               | 61 |

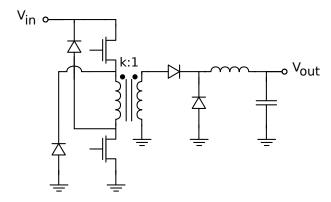

| 3.21 | 2-Transistor active clamp forward converter circuit                                         | 62 |

| 3.22 | Optimized 4-Transistor active clamp forward converter circuit                               | 62 |

| 3.23 | Optimized 4-Transistor active clamp forward converter circuit with                          |    |

|      | secondary side rectifiers optimized for integration                                         | 63 |

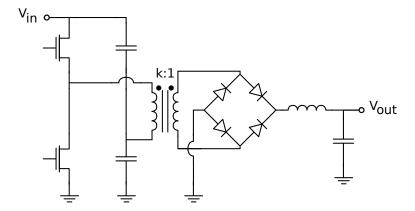

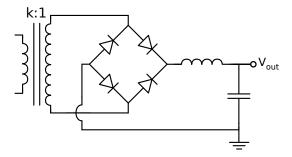

| 3.24 | Half bridge converter with a full bridge secondary side rectifier                           | 64 |

| 3.25 | Full bridge rectifier for double ended topologies                                           | 65 |

| 3.26 | Centre tap secondary for double ended topologies                                            | 67 |

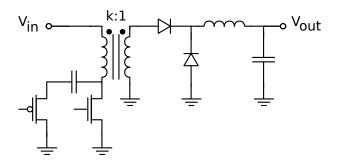

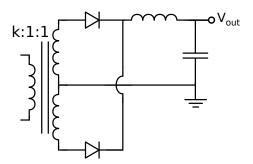

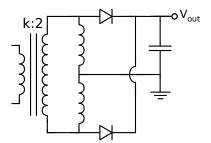

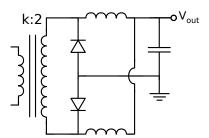

| 3.27 | Current doubler secondary for double ended topologies                                                                                                                                                                                                                                  | 67  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.28 | Current doubler secondary for double ended topologies with recti-<br>fier placement optimized for smart-power                                                                                                                                                                          | 68  |

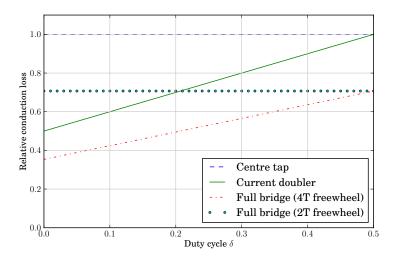

| 3.29 | Relative conduction loss in double ended secondary side rectifiers in function of the duty cycle                                                                                                                                                                                       | 69  |

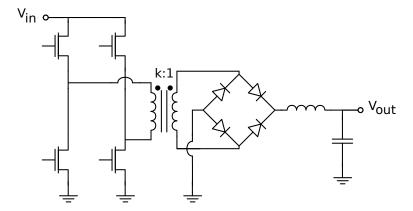

| 3.30 | Full bridge converter with a full bridge secondary side rectifier                                                                                                                                                                                                                      | 70  |

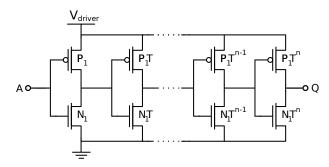

| 4.1  | Tapered buffer                                                                                                                                                                                                                                                                         | 87  |

| 4.2  | A typical dissipative secondary side RCD (Resistor, Capacitor, and Diode) voltage clamp                                                                                                                                                                                                | 89  |

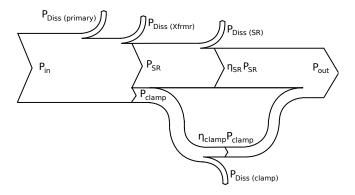

| 4.3  | Sankey diagram of power in converter and clamp circuit with the clamp circuit recovering the absorbed energy to the output of the converter                                                                                                                                            | 91  |

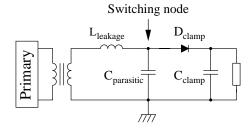

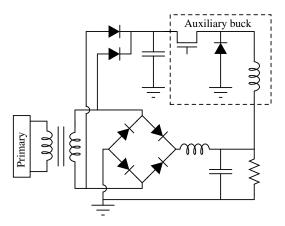

| 4.4  | Basic schematic of the converter secondary with an asynchronous active clamp circuit                                                                                                                                                                                                   | 91  |

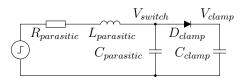

| 4.5  | Equivalent schematic of the clamped switching node                                                                                                                                                                                                                                     | 92  |

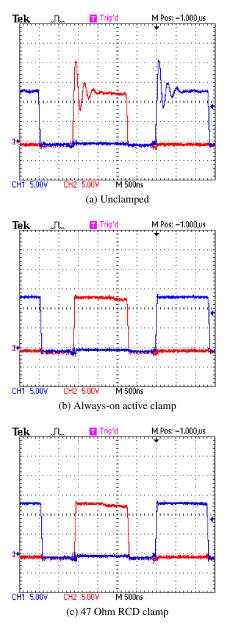

| 4.6  | Secondary side voltages for 14 V input voltage with proof-of-concept converter                                                                                                                                                                                                         | 97  |

| 4.7  | The complete asynchronous active clamp circuit. The components that are not integrated on the smart-power IC are shown outside the dashed rectangle                                                                                                                                    | 100 |

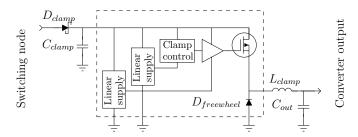

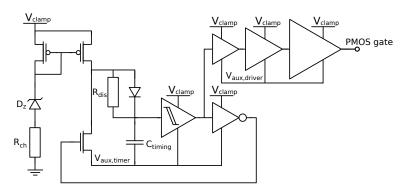

| 4.8  | Control block for the active clamp circuit on the SHARC ASIC                                                                                                                                                                                                                           | 102 |

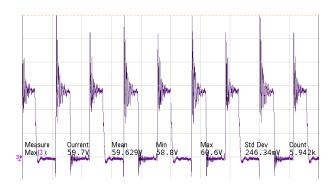

| 4.9  | Secondary side waveforms for the maximum input voltages for the converter without any clamp circuit (10 V/division) for 30 W output power                                                                                                                                              | 103 |

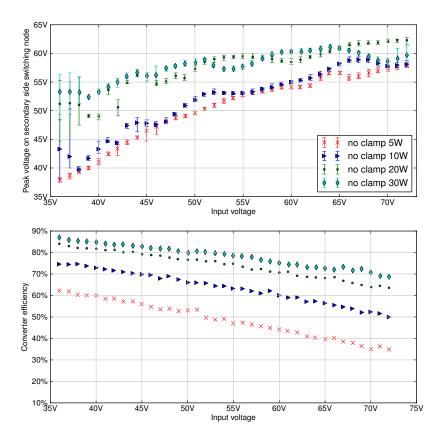

| 4.10 | Average per-cycle peak secondary side voltages versus converter input voltage for different output loads without any clamp circuit, error bars indicate minimum and maximum value over a 10 s observation window (top), converter efficiency for the same measurements (bottom)        | 106 |

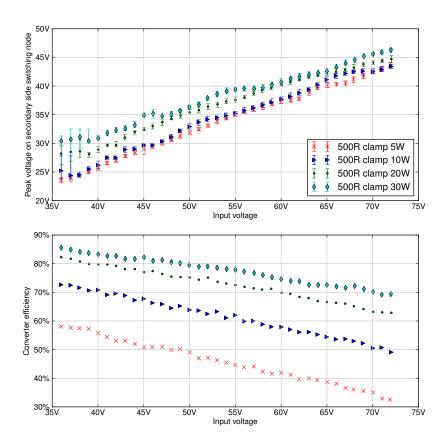

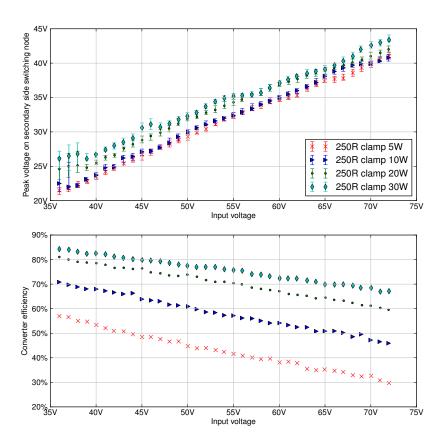

| 4.11 | Average per-cycle peak secondary side voltages versus converter input voltage for different output loads with a 500 Ohm RCD clamp circuit, error bars indicate minimum and maximum value over a 10 s observation window (top), converter efficiency for the same measurements (bottom) | 107 |

| 4.12 | Average per-cycle peak secondary side voltages versus converter input voltage for different output loads with a 250 Ohm RCD clamp circuit, error bars indicate minimum and maximum value over a 10 s observation window (top), converter efficiency for the same                       | 100 |

|      | measurements (bottom)                                                                                                                                                                                                                                                                  | 108 |

List of Figures xiii

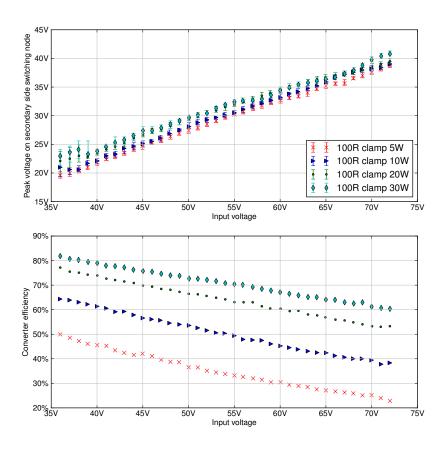

| 4.13       | Average per-cycle peak secondary side voltages versus converter input voltage for different output loads with a 100 Ohm RCD clamp circuit, error bars indicate minimum and maximum value over a 10 s observation window (top), converter efficiency for the same                                                         |            |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 4.14       | measurements (bottom)                                                                                                                                                                                                                                                                                                    | 109        |

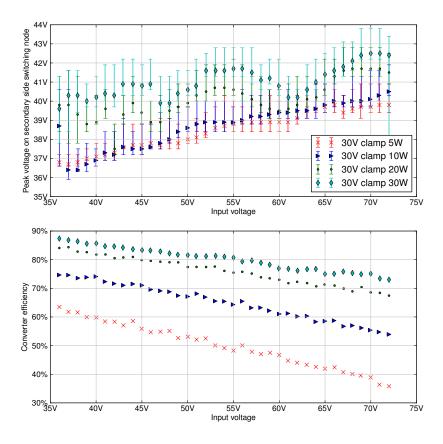

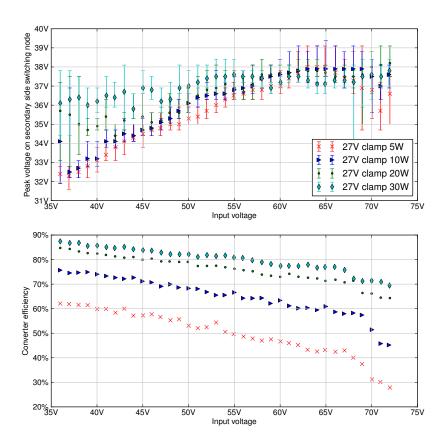

| 4.15       | verter efficiency for the same measurements (bottom) Average per-cycle peak secondary side voltages versus converter input voltage for different output loads with a energy recovering active clamp circuit using a 27 V Zener, error bars indicate minimum and maximum value over a 10 s observation window (top), con- | 110        |

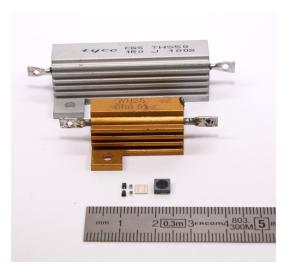

| 4.16       | verter efficiency for the same measurements (bottom) Size comparison of the components used in the asynchronous active clamp capacitor reset mechanism (bottom) and a Welwyn                                                                                                                                             | 111        |

| 4.17       | WH25 series (middle) and a Tyco THS50 series (top) resistor Layout plot of the SHARC ASIC                                                                                                                                                                                                                                | 112<br>112 |

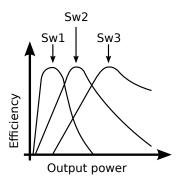

| 5.1        | Power loss distribution in function of load power                                                                                                                                                                                                                                                                        | 119        |

| 5.2        | Power loss distribution in function of switching frequency                                                                                                                                                                                                                                                               | 119        |

| 5.3<br>5.4 | Efficiency of several switching power converters over the load range<br>Linear regulator bypass of a high-power switching converter to op-                                                                                                                                                                               | 120        |

|            | timize the low-load efficiency                                                                                                                                                                                                                                                                                           | 122        |

| 5.5        | Low-power switching converter bypass of a high-power switching                                                                                                                                                                                                                                                           |            |

|            | converter to optimize the low-load efficiency                                                                                                                                                                                                                                                                            | 123        |

| 5.6        | A 2-stage complementary MOSFET driver charging the gate ca-                                                                                                                                                                                                                                                              |            |

|            | pacitor of a switching power device                                                                                                                                                                                                                                                                                      | 124        |

| 5.7        | Illustration of the clock signal and output ripple when using pulse                                                                                                                                                                                                                                                      |            |

|            | skipping and burst mode to optimize the low-load efficiency                                                                                                                                                                                                                                                              | 126        |

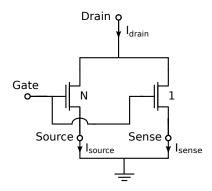

| 5.8        | SenseFET equivalent circuit                                                                                                                                                                                                                                                                                              | 132        |

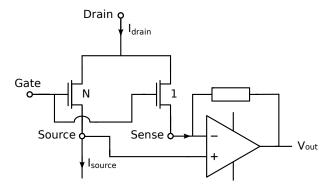

| 5.9        | SenseFET current sensing circuit with amplifier                                                                                                                                                                                                                                                                          | 133        |

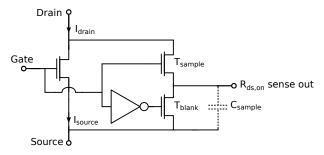

| 5.10       | Sensing current by observing the MOSFET drain-source voltage                                                                                                                                                                                                                                                             |            |

|            | drop over the channel resistance $R_{ds,on}$                                                                                                                                                                                                                                                                             | 133        |

|            | Schematic of a boost converter with segmented power stage                                                                                                                                                                                                                                                                | 135        |

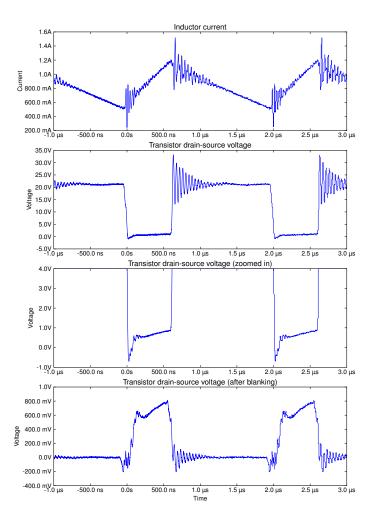

| 5.12       | Some key waveforms in the $R_{ds,on}$ current sense technique for a simple boost converter                                                                                                                                                                                                                               | 136        |

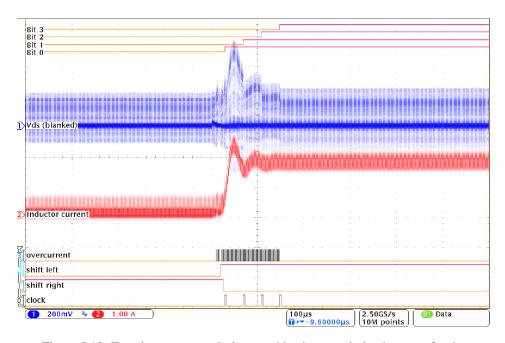

| 5.13       | Transient response during a sudden increase in load current for<br>the proof-of-concept boost converter with segmented power stage.                                                                                                                                                                                      |            |

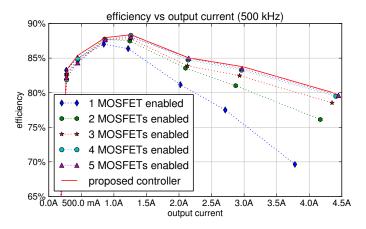

|            | Each Bit $x$ represents one activated MOSFET segment                                                                                                                                                                                                                                                                     | 138        |

| 5.14       | Efficiency of a prototype boost converter with a fixed number of MOSFET segments and with the automatic segment selector                                                                                                                                                                                                 | 138        |

| 5.15 | Schematic for a phase shifted full bridge converter with a synchronous full bridge rectifier | 140 |

|------|----------------------------------------------------------------------------------------------|-----|

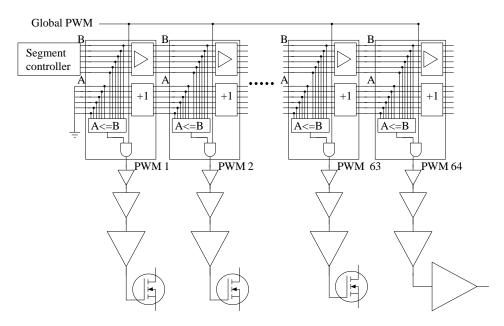

| 5.16 | Segment addressing: PWM1 to PWM63 control integrated MOS-                                    |     |

|      | FET segments, PWM64 controls a high-voltage driver for an external MOSFET                    | 142 |

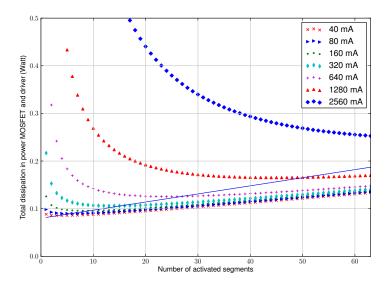

| 5.17 | Power dissipation in MOSFET and drivers in function of the number                            |     |

|      | of activated segments for different load currents                                            | 145 |

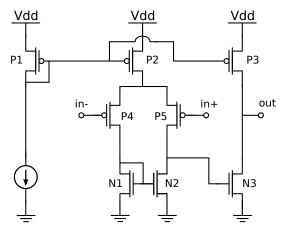

| 5.18 | Comparator circuit for the smart-power implementation of $R_{ds,on}$                         |     |

|      | based current sensing                                                                        | 145 |

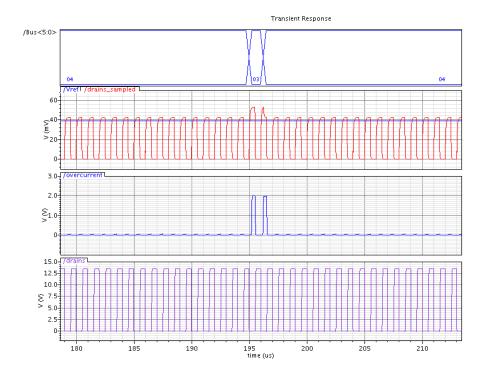

| 5.19 | At t = 195 $\mu$ s, the segment controller deactivates a segment to                          |     |

|      | detect a possible decrease in current, the comparator triggers and                           |     |

|      | the segment controller immediately reactivates the segment                                   | 146 |

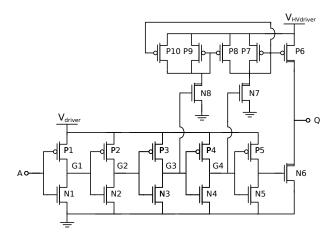

| 5.20 | High-voltage driver for external power MOSFET                                                | 148 |

| 5.21 | SHARC ASIC wirebonded in QFN56 package                                                       | 151 |

| 5.22 | Test-platform for SHARC ASIC                                                                 | 151 |

# List of Tables

| 3.1<br>3.2 | Characteristic values for various smart-power technologies Typical topology choice in discrete converters depending on output                                                                                                                                               | 31  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.3        | Nominal charge per $\operatorname{mm}^2$ for the MIMC capacitor at different voltages compared with charge required to reach final gate-source voltage $V_{gs,final}$ per $\operatorname{mm}^2$ for N-type DMOS at different initial drain-source voltages $V_{ds,initial}$ | 31  |

| 3.4        | Voltage stress $V_{stress}$ and RMS current $I_{RMS}$ in different topologies                                                                                                                                                                                               | 76  |

| 4.1        | Peak voltage stress and converter efficiency for several dissipative and energy recovering clamping configurations on the discrete proof-of-concept converter for several input voltages                                                                                    | 96  |

| 4.2        | Some combinations of capacitor values, clamp regulation voltages and power handling requirements for the clamp circuit that result in staying within the 25 year safe operating area for the I3T50 technology, assuming an ideal diode and estimations of the parasitic     |     |

|            | elements                                                                                                                                                                                                                                                                    | 99  |

| 5.1        | Dimensions of optimized tapered buffer for 1 MOSFET segment (W=10000 $\mu$ m) in the ASIC synchronous rectifier                                                                                                                                                             | 144 |

| 5.2<br>5.3 | Dimensions of transistors in comparator                                                                                                                                                                                                                                     | 144 |

| 5.4        | Estimated dissipation in package and bondwires for a number of packages available through Europractice assuming a 3 A load current in the SHARC ASIC and excluding dissipation in the ASIC                                                                                  | 149 |

## List of Acronyms

AC Alternating Current

ASIC Application Specific Integrated Circuit

BT Bipolar Transistor

CR Conversion Ratio

C-W Cockcroft-Walton

DC Direct Current

DCR Direct Current Resistance

DTI Deep Trench Isolation

EN/UVLO Enable/Undervoltage-Lockout ESR Equivalent Series Resistance

FIB Focused Ion Beam

GaN GalliumNitride

HVDC High Voltage Direct Current

IC Integrated Circuit

IGBT Insulated Gate Bipolar Transistor

I/Os Inputs/Outputs

IP Intellectual Property

LCD Liquid Crystal Display

LDO Low-dropout

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MIMC Metal Insulator Metal Capacitor

PCB Printed Circuit Board

PFC Power Factor Correction

POL Point Of Load

PWM Pulse Width Modulation

RCD Resistor, Capacitor, and Diode

RESURF Reduced Surface Field

SiC SiliconCarbide

SOI Silicon On Insulator

SR Synchronous Rectifier

### Samenvatting

Elektrische energie is niet meer weg te denken uit het dagelijkse leven, zowel thuis, in ondernemingen als in de industrie. Hoewel bijna alle elektronische applicaties steeds efficiënter worden, blijft de wereldwijde vraag naar energie steeds toenemen, aangezien het aantal gebruikers en applicaties sneller stijgt dan de technologische vooruitgang kan compenseren. Teneinde de totale productie van energie toch haalbaar en betaalbaar te houden, is het essentieel dat de distributie van de geproduceerde elektrische energie zo efficiënt mogelijk gebeurt, of met andere woorden dat de verliezen in de distributie zoveel mogelijk beperkt worden. Door het transport van elektrische energie op de hoogst mogelijke veilige spanning uit te voeren blijven de stromen en de daarmee samenhangende Joule-verliezen beperkt. Om het totale rendement te optimaliseren dient de spanning zo dicht mogelijk bij de eindgebruiker omgezet te worden naar een geschikte lagere spanning, en deze omzetting dient uiteraard ook zo efficiënt, goedkoop en compact mogelijk te gebeuren.

Dankzij een doorgedreven integratie van elektronische systemen, waarbij steeds meer functionaliteit gecombineerd wordt in monolitisch geïntegreerde circuits, kan de kostprijs, het vermogenverbruik en het formaat van deze elektronische systemen sterk beperkt worden. Deze doorgedreven integratie van elektronische systemen is niet beperkt tot de eindgebruikers van de elektrische energie, maar kan ook toegepast worden op de spanningsomzetting. De spanningsomzetting is in de meeste hedendaagse applicaties een efficiënte, schakelende DC-DC-convertor, waarbij energie tijdelijk in een of meerdere reactieve elementen, zoals spoelen en condensatoren, wordt opgeslagen. Hierbij laat een hoge schakelsnelheid toe om de DC-DC-converter compact te houden.

Voor lage vermogens, typisch minder dan 1 Watt, is het mogelijk om deze spanningsomzetting volledig monolitisch te integreren. In sommige gevallen kan dit zelfs samen met het geïntegreerde elektronische circuit dat de eindgebruiker is van de energie, om zo een systeem met minimale afmetingen te realizeren. Voor hogere vermogens voldoen de volledig monolitisch geïntegreerde componenten niet om de gewenste efficiëntie te bereiken en blijken een aantal externe componenten noodzakelijk. Doorgaans zijn de reactieve componenten de meest beperkende factor en worden deze bij stijgende vermogens als eerste buiten het geïntegreerde circuit gebracht. Halfgeleidercomponenten, inclusief de vermogenstransistoren blijven daarentegen deel uitmaken van het geïntegreerde circuit, om zo een hybride geïntegreerde convertor te bekomen. Dankzij deze hybride aanpak is het in de huidige hybride geïntegreerde convertor-toepassingen haalbaar om maximaal ongeveer 60 Watt te verwerken, zij het enkel voor spanningen tot een paar Volt. Voor spanningen xx Samenvatting

van enkele tientallen Volt is het uitgangsvermogen van deze hybride geïntegreerde convertoren beperkt tot een tiental Watt. Voor nog hogere vermogens worden de geïntegreerde vermogenstransistoren eveneens een beperkende factor en worden deze vervangen door discrete vermogenstransistoren. In deze discrete convertoren is de omzetting van veel hogere vermogens mogelijk, maar de omvang van het systeem neemt snel toe. In dit werk worden de grenzen van de hybride aanpak onderzocht bij het gebruiken van zogenaamde *smart-power* technologieën, een generieke term voor betaalbare sub-micron CMOS technologieën met enkele uitbreidingen voor de integratie van hoogspanningscomponenten. Afhankelijk van de applicatie is het mogelijk om beter te presteren dan de huidige "beste" convertoren op het gebied van efficiëntie, formaat en kostprijs, door het combineren van de gepaste smart-power technologie en de juiste topologie.

Voor het bepalen van de mogelijkheden van smart-power DC-DC-convertoren worden eerst algemeen de belangrijkste parameters besproken voor een efficiënte energiedistributie en bekijken we de rol die spanningsomzetting speelt in de energiedistributie. Aansluitend kiezen we uit de mogelijke toepassingen een tweetal applicaties uit de wereld van de telecommunicatie waarvoor we de hybride monolitische integratie in een smartpower technologie wensen te optimaliseren. Daarna bekijken we de eigenschappen van een ideale convertor en de relevante specifieke kenmerken van de betaalbare smart-power technologieën voor de implementatie van DC-DC-convertoren. Rekening houdend met de beperkingen die aanwezig zijn in deze technologieën bepalen we een kostfunctie die toelaat om systematisch de verschillende topologieën voor convertoren te kunnen vergelijken zonder het volledige ontwerpproces te doorlopen. Vanuit deze kostfunctie valt het op dat de de facto standaard keuze voor de topologie in discrete convertoren, die gebasseerd is op het uitgangsvermogen, niet optimaal is voor convertoren met geïntegreerde vermogenstransistoren. Op basis van deze kostfunctie en de randvoorwaarden die gesteld worden aan onze concrete applicaties bepalen we de optimale topologie voor een smart-power implementatie voor de eerder gekozen applicaties.

Vervolgens gaan we een stap dichter bij de realiteit en bekijken we de gevolgen van parasitaire elementen in een smart-power implementatie van schakelende convertoren. De spanningspieken veroorzaakt door de lekinductantie aan de secundaire van transformatorgeïsoleerde convertoren blijken daarbij een groot struikelblok voor een efficiënte implementatie. Aangezien de gebruikelijke aanpak van deze spanningspieken in discrete convertoren niet voldoet voor smart-power convertoren omwille van technologische beperkingen wordt een alternatieve aanpak aangetoond en geïmplementeerd, waarbij de energie uit de spanningspieken wordt geabsorbeerd en hierbij gerecycleerd naar de uitgang van de convertor. Hierdoor is het mogelijk om de spanningspieken sterk te reduceren en tegelijk het rendement vrijwel constant te houden. Zo bekomen we een efficiënte, compacte en betaalbare implementatie. De correcte werking van deze aanpak werd uitgetest en aangetoond, zowel in een versie gebruik makend van een commercieel verkrijgbaar geïntegreerd circuit, als in een eigen smart-power implementatie.

Uiteindelijk bekijken we ook de optimalisatie van schakelende convertoren over de volledige lastkarakteristiek door de mogelijkheden van een sterk geïntegreerde convertor uit te buiten. Alhoewel het maximale uitgangsvermogen nog steeds een van de karakteristieke

Samenvatting xxi

eigenschappen is van een convertor blijkt dat de meeste convertoren een belangrijk deel van hun levensduur significant lagere vermogens omzetten. Hierdoor is het wenselijk om ook bij een lagere uitgangsstroom en uitgangsvermogen het rendement te optimaliseren. Door de vermogenstransistoren op te splitsen in verschillende onafhankelijke segmenten, die in functie van de stroom al dan niet aangestuurd worden, kan het rendement bij lage stromen sterk verhoogd worden. Dit alles zonder de introductie van ongewenste frequentiecomponenten in de uitgangsspanning en zonder dat dit ten koste gaat van het rendement bij hogere stromen. Deze eigenschappen laten toe om deze optimalisatietechniek in vrijwel alle applicaties van hybride monolithische DC-DC-convertoren toe te passen, zonder grote impact op de complexiteit en de kost van het systeem. Deze aanpak werd uitgetest en aangetoond in een versie met discrete vermogenstransistoren, maar kon wegens een probleem met een digitaal controleblok enkel in simulatie aangetoond worden voor de eigen smart-power implementatie.

Tenslotte worden eveneens een aantal algemene conclusies geformuleerd en halen we de mogelijkheden voor toekomstig werk in het verlengde van dit onderzoek aan.

### Summary

The supply of electrical energy to home, commercial, and industrial users has become ubiquitous, and it is hard to imagine a world without the facilities provided by electrical energy. Despite the ever increasing efficiency of nearly every electrical application, the worldwide demand for electrical power continues to increase, since the number of users and applications more than compensates for these technological improvements. In order to maintain the affordability and feasibility of the total production, it is essential for the distribution of the produced electrical energy to be as efficient as possible. In other words the loss in the power distribution is to be minimized. By transporting electrical energy at the maximum safe voltage, the current in the conductors, and the associated conduction loss can remain as low as possible. In order to optimize the total efficiency, the high transportation voltage needs to be converted to the appropriate lower voltage as close as possible to the end user. Obviously, this conversion also needs to be as efficient, affordable, and compact as possible.

Because of the ever increasing integration of electronic systems, where more and more functionality is combined in monolithically integrated circuits, the cost, the power consumption, and the size of these electronic systems can be greatly reduced. This thorough integration is not limited to the electronic systems that are the end users of the electrical energy, but can also be applied to the power conversion itself. In most modern applications, the voltage conversion is implemented as a switching DC-DC converter, in which electrical energy is temporarily stored in reactive elements, i.e. inductors or capacitors. High switching speeds are used to allow for a compact and efficient implementation.

For low power levels, typically below 1 Watt, it is possible to monolithically implement the voltage conversion on an integrated circuit. In some cases, this is even done on the same integrated circuit that is the end user of the electrical energy to minimize the system dimensions. For higher power levels, it is no longer feasible to achieve the desired efficiency with monolithically integrated components, and some external components prove indispensable. Usually, the reactive components are the main limiting factor, and are the first components to be moved away from the integrated circuit for increasing power levels. The semiconductor components, including the power transistors, remain part of the integrated circuit. Using this hybrid approach, it is possible in modern converter-applications to process around 60 Watt, albeit limited to voltages of a few Volt. For hybrid integrated converters with an output voltage of tens of Volt, the power is limited to approximately 10 Watt. For even higher power levels, the integrated power transistors also become a limiting factor, and are replaced with discrete power devices. In these

xxiv Summary

discrete converters, greatly increased power levels become possible, although the system size rapidly increases. In this work, the limits of the hybrid approach are explored when using so-called *smart-power* technologies. Smart-power technologies are standard low-cost submicron CMOS technologies that are complemented with a number of integrated high-voltage devices. By using an appropriate combination of smart-power technologies and circuit topologies, it is possible to improve on the current state-of-the-art converters, by optimizing the size, the cost, and the efficiency.

To determine the limits of smart-power DC-DC converters, we first discuss the major contributing factors for an efficient energy distribution, and take a look at the role of voltage conversion in the energy distribution. Considering the limitations of the technologies and the potential application areas, we define two test-cases in the telecommunications sector for which we want to optimize the hybrid monolithic integration in a smart-power technology. Subsequently, we explore the specifications of an ideal converter, and the relevant properties of the affordable smart-power technologies for the implementation of DC-DC converters. Taking into account the limitations of these technologies, we define a cost function that allows to systematically evaluate the different potential converter topologies, without having to perform a full design cycle for each topology. From this cost function, we notice that the de facto default topology selection in discrete converters, which is typically based on output power, is not optimal for converters with integrated power transistors. Based on the cost function and the boundary conditions of our test-cases, we determine the optimal topology for a smart-power implementation of these applications. Then, we take another step towards the real world and evaluate the influence of parasitic elements in a smart-power implementation of switching converters. It is noticed that the voltage overshoot caused by the transformer secondary side leakage inductance is a major roadblock for an efficient implementation. Since the usual approach to this voltage overshoot in discrete converters is not applicable in smart-power converters due to technological limitations, an alternative approach is shown and implemented. The energy from the voltage overshoot is absorbed and transferred to the output of the converter. This allows for a significant reduction in the voltage overshoot, while maintaining a high efficiency, leading to an efficient, compact, and low-cost implementation. The effectiveness of this approach was tested and demonstrated in both a version using a commercially available integrated circuit, and our own implementation in a smart-power integrated circuit.

Finally, we also take a look at the optimization of switching converters over the load range by exploiting the capabilities of highly integrated converters. Although the maximum output power remains one of the defining characteristics of converters, it has been shown that most converters spend a majority of their lifetime delivering significantly lower output power. Therefore, it is also desirable to optimize the efficiency of the converter at reduced output current and output power. By splitting the power transistors in multiple independent segments, which are turned on or off in function of the current, the efficiency at low currents can be significantly improved, without introducing undesirable frequency components in the output voltage, and without harming the efficiency at higher currents. These properties allow a near universal application of the optimization technique in hybrid monolithic DC-DC converter applications, without significant impact on the complexity

Summary xxv

and the cost of the system. This approach for the optimization of switching converters over the load range was demonstrated using a boost converter with discrete power transistors. The demonstration of our smart-power implementation was limited to simulations due to an issue with a digital control block.

On a finishing note, we formulate the general conclusions and provide an outlook on potential future work based on this research.

# Introduction

#### 1.1 Introduction

The electrification of the world has been called the greatest engineering achievement of the 20th century, and if we see what can be achieved nowadays by merely flicking a switch this is no exaggeration. Since the end of the 19th century, when the first commercial implementations of electrical power plants began to distribute electrical energy to a region of customers, these customers have realized the advantages of using electrical energy for powering mechanical equipment, lighting, and heat sources, and the availability of electrical power has played a significant part in the development of the world as we know it today, with a notable highlight in the form of today's information technology. The ubiquitous nature of electrical energy in everyday life is mainly obvious when the electrical power distribution is temporarily interrupted, and everything we take for granted suddenly grinds to a halt.

Because of the multitude of applications in which electrical energy can be used, the world-wide hunger for electrical power has seen a steady increase ever since the beginning of the electrification. To make this possible at a reasonable cost, the efficiency of bringing electrical power from where it is generated to where it is used needs to be optimized as much as possible, which includes every aspect from generation over transportation to use of electrical energy.

The transportation of electrical energy is most efficient at high voltages and lower currents, while applications at the end of the line run at lower voltages, with a trend for electronic equipment to operate at ever decreasing voltages. This requires multiple conversions of energy from a high transportation voltage towards a lower utilization voltage.

2 Introduction

To optimize the benefits of the high transportation voltage, this conversion also needs to be optimized in the aspects of size, cost, and efficiency, otherwise the gains in the distribution by using an increased voltage are lost again in the conversion.

Electrical energy conversion is an enormously broad field, ranging from gigawatt to nanowatt, so obviously there is no single solution that is optimal for all applications.

In this work we aim to optimize highly – but not fully – integrated converters, where most components, including the power transistors, are integrated on a single chip using affordable smart-power technologies, which are high-voltage extensions of standard semiconductor processes, but still allowing the use of discrete components when integrated components become impractical to integrate from a cost or performance perspective. Because of the integrated character and the associated limitations, these highly integrated converters are limited in power and voltage compared to converters that use discrete power devices. However, the voltage and power is at the high end of the capabilities of integrated technologies and we feel that hybrid monolithic integrated high-voltage high-power converters is an adequate description of the converters that we want to optimize. Even though in absolute numbers the individual gain in efficiency for an optimized relatively low-power converter is small, their large number implies that significant energy saving in the generation and distribution stage can be achieved by optimizing these converters.

First, we will show that voltage conversion is the key to efficient distribution of electrical energy, and that throughout the history of voltage conversion the increasing degree of integration of functionality in a single chip has been an enabling factor for affordable and widespread implementation of efficient converters. Nowadays, thanks to the smart-power technologies it is possible to implement all power devices and controlling logic on a single chip, and by allowing the use of some external components in a hybrid monolithic integrated converter, the power can be increased compared to fully integrated converters, where all components are on the chip.

To optimize these hybrid monolithic integrated high-voltage high-power converters, we first need to be familiar with the properties of the available high-voltage technologies and the impact this has on the potential applications. After this, we can select an optimal combination of application and converter topology, based on an estimation of the efficiency and the required silicon area.

Then, we see that – once we leave the idealized world of textbooks and basic simulations and enter the real world with non-ideal components – voltage overshoot on the secondary side of transformer-isolated converters is a major roadblock for efficient smart-power implementation. To minimize the effects of the secondary side voltage overshoot, we show a new and highly integrated approach that can arbitrarily reduce the overshoot while maintaining a high efficiency, which is not possible using the conventional approach known from discrete converters.

Finally, we take a closer look at how the efficiency of the hybrid integrated power converters over the load range can be optimized by taking advantage of the properties of integrated converters.

1.2 Outline 3

#### 1.2 Outline

In the Introduction chapter, which you are reading right now, a short and abstract background to the work is sketched, followed by the outline of the work. Then we briefly highlight the research context, and give an overview of the dissemination that has resulted from the research.

In Chapter 2, a more in depth introduction to efficient energy distribution and the potential applications of hybrid monolithic integrated converters is discussed. Additionally, we select two converter specifications for telecommunications applications as a reference case for hybrid monolithic integrated converters, based on the properties of the available smart-power technologies, the specifications of these converters, and the global relevance of the applications.

In Chapter 3, we begin our search for an a optimal converter topology for integration in affordable smart-power technologies, starting form the definition of an ideal converter, introducing some semiconductor device basics and the relevant properties for smart-power technologies. Then we define a cost function for the monolithic integration of converters in these smart-power technologies and discuss the advantages and disadvantages of several approaches for voltage conversion. To end Chapter 3, we conclude on an optimum converter topology for hybrid monolithic integration of high-power converters in a high-voltage technology.

In Chapter 4, we introduce some parasitic elements in the converters that were not relevant in the discussion of the relative merits of different topologies for integration in a smart-power technology from the previous chapter, but are very much relevant for an efficient implementation of a smart-power converter. We will find out that the voltage overshoot caused by the inductive parasitics in transformer-isolated converters is a major roadblock for an efficient smart-power implementation, and discuss the possibilities to reduce the impact of the voltage overshoot. This discussion leads to an asynchronous active voltage clamp approach, that is significantly different than is common in discrete converters at this power level. We show a discrete prototype confirming the potential benefits of this proposed clamping circuit, and highlight the relevant design aspects for a monolithic version that is integrated with the synchronous rectifier of a smart-power converter. Measurements on the clamping circuit confirm a reduced voltage stress, improved efficiency, and reduced size compared to dissipative clamping circuits, which are the common solution for converters at this power level.

In Chapter 5, we discuss the possibilities for optimizing the efficiency of hybrid monolithic integrated converters over the load range. We take a look at the loss mechanisms that are present in switching converters, and systematically discuss the impact on the efficiency over the load range for a number of modifications to the textbook converters. We see that an approach where the dimensions of the power devices are dynamically adjusted in function of the load based on a non-invasive current estimation is well suited for implementation in hybrid monolithic integrated converters. Therefore, this approach is discussed in more detail, followed by a proof of concept on a discrete implementation with measurements confirming the optimization of efficiency, and a discussion of

4 Introduction

the design aspects for a monolithic implementation. Unfortunately, no measurements are available on this monolithic implementation, due to an issue with a digital control block. In Chapter 6, we arrive at the conclusions, where the main achievements are highlighted and an outlook for future work is presented.

#### 1.3 Research context

In modern times, the days of lone researchers working in a vacuum and emerging after a couple of years to present their work are long gone. Instead, researchers continue to build on the framework built by their predecessors and peers in order to advance the state-of-the-art. This work was situated at the CMST (Centre for Microsystems Technology), formerly known as *TFCG Microsystems Lab* in Zwijnaarde (Gent), a research group in the ELIS (Electronics and Information Systems) Department of the Faculty of Engineering and Architecture of Ghent University, and also an associated lab of imec. Under the lead of em. Prof. André Van Calster, CMST has grown from a small research group working on thin-film displays to a multidisciplinary research group working on smart microsystems integration, focusing on both design and technology in a number of domains: advanced packaging, stretchable interconnects, polymer structuring and microfluidics, optical interconnect and laser technology, display technology, and smart-power. This is a diverse range of domains, with target applications in ambient intelligence, telecom, energy, displays & lighting, and biomedical & health.

The research presented in this work is situated in the smart-power subgroup – specialized in the design of high-voltage integrated circuits – under the lead of Prof. Jan Doutreloigne. Originally, these high-voltage integrated circuits were used for driving thin-film displays, although through the years the applications have diversified to intelligent drivers for bistable, modular, and emissive displays, drivers and splitters for xDSL applications, TCAD simulations of power devices, switching converters for (O)LED applications and telecommunications, smart switches for PV applications, and design of MEMS devices and drivers. The research on telecommunications applications, including the switching converters, is in the framework of a bilateral research agreement with Alcatel-Lucent, a global manufacturer of telecommunications equipment.

This work was initially funded by Ghent University in the form of a *Dehousse* scholarship, followed by an IWT post-graduate *specialisatiebeurs* grant, and finalized as an imec payroll employee. Additional funding was provided by the bilateral research agreement with Alcatel-Lucent.

#### 1.4 Research dissemination

#### 1.4.1 Papers published in an SCI-journal

• **Jindrich Windels** and Jan Doutreloigne, "Active asynchronous secondary side voltage clamping", *Electronics Letters*, *IEE*, **2011**, 47, 512-514

# 1.4.2 Papers presented at international conferences listed as P1-publications

- Ann Monté, Jan Doutreloigne, Jindrich Windels, Pieter Bauwens, "Driving electronics for OLED lighting", SID-ME Spring 2013 Meeting. Ghent, Belgium, April 15-16, 2013

- Jan Doutreloigne, Ann Monté and Jindrich Windels, "Design of an Integrated OLED Driver for a Modular Large-Area Lighting System", 7th International Conference on Circuits, Systems and Signals (CSS '13), Cambridge, MA, USA, January 30- Februari 1, 2013

- **Jindrich Windels**, Ann Monté and Jan Doutreloigne, "Monolithic integration of an active asynchronous voltage clamp with a 12V3A full bridge synchronous rectifier", Proceedings of the 2012 IEEE International conference on Power Electronics, Drives and Energy Systems (2012), Bengaluru, India, December 16-19, 2012

- Jan Doutreloigne, Ann Monté, Benoit Bakeroot and Jindrich Windels, "Monolithic Integration of an Active Clamping H-Bridge for Isolated Forward DC-DC Converters", Proceedings of the 11th WSEAS International Conference on Instrumentation, Measurements, Circuits and Systems (IMCAS'12), Rovaniemi, Finland, April 18-20, 2012

- Jan Doutreloigne, Benoit Bakeroot, Ann Monté and Jindrich Windels, "Monolithic Integration of the Synchronous Rectifier in Isolated Forward DC-DC Converters", Proceedings of the 11th WSEAS International Conference on Instrumentation, Measurements, Circuits and Systems (IMCAS'12), Rovaniemi, Finland, April 18-20, 2012

- Jindrich Windels, Christophe Van Praet, Herbert De Pauw and Jan Doutreloigne, "Comparative study on the effects of PVT variations between a novel all-MOS current reference and alternative CMOS solutions" Midwest Symposium on Circuits and Systems Conference Proceedings (2009), Cancun, Mexico, August 2-5, 2009

#### 1.4.3 Papers presented at national conferences

• **Jindrich Windels**, Analysis and design of high power monolithically integrated switching DCDC converters, UGent-FirW Doctoraatssymposium, 11e (2010)

# 2

# Enabling efficient energy distribution through voltage conversion

#### 2.1 Introduction

In this chapter we will take a look at the design considerations for an energy efficient distribution network for electrical energy. Typically, energy distribution is considered as everything coming from the electrical power plant, where the electrical energy is converted from other energy sources to electricity, and ending at the industrial, commercial, or home user, which is billed for the energy consumption on-site. However, the same considerations for energy distribution are valid over an even wider range: coming from the power plant, over the billed customer down to individual systems, modules, and subsystems, the same design considerations are in effect for efficient energy distribution, only at a different scale, and therefore leading to different optimal solutions.

After discussing the underlying principles for efficient energy distribution, we will situate where our hybrid monolithic high-power converters are located in the distribution process of electrical energy and identify where our work can improve on the state-of-the-art. We will highlight a number of potential applications for a hybrid monolithic integrated high-voltage high-power DC-DC converter, and select two test-cases where we expect the advantages of hybrid monolithic integrated power converters using affordable high-voltage technologies will be the most relevant.

Figure 2.1: Schematic overview of a distribution network for electrical energy

#### 2.2 Efficient energy distribution

In any energy distribution system, it is important to optimize the cost of the energy distribution and the efficiency of the energy distribution. Obviously, every Watt that is generated at the power plant has an associated cost, be it in fossil fuels, nuclear fuel mining and disposal, or simply the resources that are used in the construction of a renewable energy plant with a finite life time. Therefore, it is in the best interest of anyone involved in the generation and distribution of power to ensure the delivery to the end user is as optimal as possible, and reduce the losses to a minimum. A conflicting interest however is the cost of building and maintaining the distribution network, since the resistance of the conductors needs to be as low as possible to achieve low losses in the electrical distribution network. All good electrical conductors, such as copper and aluminum, that can transport large amounts of power without requiring excessive material and space are also finite resources, and can quickly become expensive if large currents need to be transported over large distances. It is estimated that worldwide in 2011 approximately 8 percent of all generated electrical energy was lost in transmission and distribution, i.e. between the power plant and the billed customer [1] [2].

Because electrical power is the product of current and voltage, it is possible to minimize the amount of required conductor material by performing the transport of electrical energy at the highest possible safe and practical voltage, thereby reducing the current through the conductor. Because of the quadratic dependence on current of the Joule loss in a conductor  $(P=RI^2)$ , the loss in identical resistive conductors is reduced by a factor 4 with doubling the voltage, which reduces the current in half.

Regional voltages exist in voltages used for generation, transmission, distribution, and delivery to the end users. In Figure 2.1, a more-or-less typical distribution system is shown with the voltage ranges as used in Belgium [3]. Here, the Alternating Current (AC) voltage as generated by the power plant is converted using a transformer to a higher voltage, typically tens to hundreds of kV to optimize the distribution efficiency. For

safety reasons, these high-voltage lines are either placed overhead on pylons or buried underground. Near the end user, the voltage is transformed down again using another transformer to a voltage that is appropriate for the amount of power that the customer is using, for residential electrical installations and small scale commercial installations, this is typically 230 V, but can be increased for larger commercial and industrial customers up to tens of kV.

Ever since the beginning of the construction of the distribution network, an AC system running at a few tens of Hertz has been the most convenient way to distribute electrical energy. The choice for the mains frequency was a historical compromise between losses over long transmission lines, which increase with frequency, the properties of some rotating machines that do not operate well on high frequencies, and the size of transformers, that become smaller and lighter with increased frequency [4].

The use of AC leads to a less than optimal use of the conductor and isolation material. For the isolation material, this is caused by the peak voltages in AC being  $\sqrt{2}$  times the nominal voltage, whereas in DC the nominal and peak voltage are identical. For the conductor material, this is caused by the skin effect in conductors carrying AC which reduces the effective conductor cross-section, and thus the need to use a somewhat larger conductor compared to DC for an identical equivalent resistance. However, the ability to use transformers to increase or decrease the voltage in a simple, relatively low-cost and efficient way has historically compensated for the less than perfect conductor utilization. Typically, only in specialty applications like underseas cables, very long interconnect distances, and to connect asynchronous AC networks, the additional cost of implementing a High Voltage DC (HVDC) distribution link is warranted [5].

However, the power distribution story is not limited to centralized production in a power plant with delivery of the electrical power to the end user, as only a limited number of appliances, such as heaters, electrical motors and incandescent lighting actually use the electrical energy at the voltage at which it is delivered by the distribution grid. Both applications where the electrical energy from the grid is used in other appliances inside the end user facility that operate at other voltages, and applications that are not necessarily connected to the distribution grid, such as battery-powered and battery-backed-up equipment need to be optimized for an efficient energy distribution to reduce the loss to a minimum.

Within the premises of the end user, the same considerations apply as in the distribution network, but at reduced power levels and typically also at reduced voltages to improve the safety when users of the electrical energy can come into proximity of live conductors.

Until relatively recently, almost all power conversion was performed with transformers operating at mains frequency, often followed by rectification and one or more linear regulators to provide a stable DC voltage. This classical approach leads to a bulky power supply, because of the use of physically large and heavy transformers and the need to provide adequate heat-sinking for the linear regulators but is simple and relatively low-cost.

#### 2.3 The rise of the semiconductor

Ever since the first commercial release of an integrated circuit (IC) in 1960, when Texas Instruments announced their TI #502 multivibrator IC [6], the number of components on a single IC has increased exponentially. This trend was first described by Gordon E. Moore in 1965, when he predicted that by 1975 as many as 65000 components on a single chip would not only be possible, but would provide a minimum cost per component [7], based on the then-short history of the integrated circuit and a then-state-of-the art optimum of 50 components per IC. This prediction corresponded with a doubling of the number of transistors in an integrated circuit every 12 months, and when 1975 rolled around, Moore's prediction was confirmed. Based on the additional insights in the production process that were available ten years after his initial observation of the trend, he then revised his prediction to a doubling every 24 months [8], and his prediction of exponential growth has proven to be uncannily accurate until the present day. This is in part because his prediction became a self-fulfilling prophecy, considering it is used by the semiconductor industry to define their long term road-map, and the trend he observed in the 1960's is still referred to as Moore's law.

To achieve this increased density, the dimensions of semiconductor devices also decreased dramatically since the first integrated circuit. Because of the physical limitations in the materials used in the semiconductor manufacturing, such as maximum field strength in semiconductors and dielectrics, this increase in density has corresponded with ever decreasing supply voltages. Although the reduction in size and supply voltage results in a reduction in power consumption per transistor, the exponentially increasing number of transistors leads to an ever increasing current consumption for integrated circuits.

As we have seen in the previous section on efficient energy distribution, the losses in a system are minimized by transferring electrical energy at the maximum possible voltage at low currents, and reducing the voltage and increasing the current as close to the end user as possible. Although the scale in an electronic system composed of integrated circuits is significantly different from the distribution grid, where thousands of Ampere at hundreds of kV can be transported, the same principle still applies, as the conductor cross section is also much smaller.

With the increasing power demands of integrated circuits, the classic voltage conversion approach with transformers operating at the mains frequency followed by a linear regulator became increasingly impractical. Since this approach is limited by thermal considerations in the heat-sinks and transformers, the increasing power demands of the shrinking electronic systems imply increasingly large transformers and heat-sinks.

By 1947, when the first transistor was demonstrated in a laboratory setting [9], switching power supplies were already commercially available using electromechanical switches or *vibrators* operating at a few tens to a few hundred Hertz [10]. Because of the noise and mechanical wear associated with electromechanical switches, these switching power supplies were typically used in battery-powered applications requiring voltages in excess of the battery voltage. Since these electromechanical switching converters operated in the same frequency range as the electrical mains, the potential reduction in size

for the transformer by choosing an increased frequency was relatively limited. Together with the increasing use of semiconductor devices in analog and digital circuits, discrete semiconductor power devices that could be used as switches also became available, and switching power supplies operating at frequencies above the mains frequency gradually became more practical. The first patent for a transistor based power converter was filed in 1959 [11], allowing for an increase in switching speed compared to electromechanical switches. The initial development of these switching converters was mainly driven by aerospace applications, where the reduced weight and size and the improved efficiency made up for the high cost [12]. Gradually, improved power transistors with fast switching speeds and increased voltage ratings became available, and switching converter technology began to trickle down to consumer applications.