Ontwerp van gebeurtenisgebaseerde automatische versterkingsregeling en hogesnelheidsdatapad voor optische ontvangers met meerdere kanalen

Design of Event-Driven Automatic Gain Control and High-Speed Data Path for Multichannel Optical Receiver Arrays

Jochen Verbrugghe

Promotoren: prof. dr. ir. X. Yin, prof. dr. ir. J. Bauwelinck Proefschrift ingediend tot het behalen van de graad van Doctor in de Ingenieurswetenschappen: Elektrotechniek

Vakgroep Informatietechnologie Voorzitter: prof. dr. ir. D. De Zutter Faculteit Ingenieurswetenschappen en Architectuur Academiejaar 2014 - 2015

ISBN 978-90-8578-787-7 NUR 959

Wettelijk depot: D/2015/10.500/30

### Universiteit Gent Faculteit Ingenieurswetenschappen en Architectuur Vakgroep Informatietechnologie

Promotoren: prof. dr. ir. Xin Yin

prof. dr. ir. Johan Bauwelinck

Universiteit Gent Faculteit Ingenieurswetenschappen en Architectuur

Vakgroep Informatietechnologie Sint-Pietersnieuwstraat 41, B-9000 Gent, België

Tel.: +32 (9) 264 33 46 Fax.: +32 (9) 264 35 93

Dit werk werd financieel gesteund door een specialisatiebeurs van het IWT-Vlaanderen (agentschap voor Innovatie door Wetenschap en Technologie).

Proefschrift tot het behalen van de graad van Doctor in de Ingenieurswetenschappen: Elektrotechniek Academiejaar 2014-2015

## Voorwoord

Dit proefschrift kwam tot stand binnen de vakgroep Informatietechnologie van de Universiteit Gent en is het resultaat van een aantal jaren studie en onderzoek als medewerker van het Intec Design laboratorium. Ik wens dan ook uitdrukkelijk de vakgroepvoorzitter prof. dr. ir. Daniël De Zutter te bedanken voor de aangeboden infrastructuur en omkadering.

Ik wens zowel het oude als het nieuwe hoofd van het labo, prof. dr. ir. Jan Vandewege en prof. dr. ir. Johan Bauwelinck, laatstgenoemde tevens ook copromotor van dit werk, te bedanken voor de geboden kansen en het gestelde vertrouwen. Een woord van dank gaat verder uit naar prof. dr. ir. Xin Yin, promotor van dit werk, en dr. ir. Guy Torfs voor de leerrijke discussies en het nauwgezet nalezen. Ik ben prof. dr. ir. Xing-Zhi Qiu erkentelijk voor het onderhouden van contacten met de technologische industrie alsook het agentschap voor Innovatie door Wetenschap en Technologie (IWT) voor de toegekende beurs.

In het bijzonder ben ik ir. Bart Moeneclaey dankbaar voor zijn bijdrage in de ontwikkelde chips en de gemeenschappelijke interesse in snelle analytische technieken, waarbij de vele discussies leidden tot diepere inzichten of zelfs ontspoorden tot heuse zijprojecten.

Verder wens ik mijn ex-collega's en collega's van de Intec Design groep te bedanken voor de samenwerking tijdens deze jaren. Bovenal was ing. Jan Gillis onmisbaar voor de technische ondersteuning, PCB's, layout of gewoon zomaar. Ook denk ik met name aan dr. ir. Christophe Van Praet, dr. ir. Guy Torfs, dr. ir. Jasmien Put en ir. Wouter Soenen voor de uitgebreide discussies, aangename koffiepauzes en het gezelschap.

Een speciaal woord van dank gaat ook uit naar dr. ir. Renato Vaernewyck en ir. Xiao Li voor hun bijdrage in het PCB ontwerp en naar dr. ir Bart Baekelandt voor de hulp bij de beursaanvraag.

Mijn ouders verdienen ook zeker een plaats in dit dankwoord. Niet in het minst voor het sponseren van een Elektuurabonnement tijdens mijn jeugd en om mij de kans te geven om me verder te verdiepen in elektronica.

Tenslotte bedank ik mijn vriendin, die mijn voortdurend groeiende verzameling antieke meetapparatuur moet tolereren.

Gent, December 2014 Jochen Verbrugghe

# **Contents**

| Co             | nten  | s                                         | ix   |  |  |

|----------------|-------|-------------------------------------------|------|--|--|

| Gl             | ossar | 7                                         | xiii |  |  |

| Νe             | derla | ndstalige Samenvatting                    | xv   |  |  |

| En             | glish | Summary                                   | xix  |  |  |

| 1 Introduction |       |                                           |      |  |  |

|                | 1.1   | Background                                | . 1  |  |  |

|                |       | 1.1.1 Data Centers                        | . 2  |  |  |

|                |       | 1.1.2 The Metro Network                   | . 4  |  |  |

|                | 1.2   | Aspects of Analog Circuit Design          |      |  |  |

|                |       | 1.2.1 Design Flow                         |      |  |  |

|                |       | 1.2.2 Transistor Hand Calculation Models  | . 7  |  |  |

|                |       | 1.2.2.1 MOSFETs                           | . 8  |  |  |

|                |       | 1.2.2.2 Bipolar Junction Transistors      |      |  |  |

|                |       | 1.2.3 Tools                               | . 8  |  |  |

|                | 1.3   | Technology                                | . 11 |  |  |

|                | 1.4   | Outline of the Dissertation               |      |  |  |

| 2              | Opti  | cal Receiver Concepts                     | 15   |  |  |

|                | 2.1   | Overview                                  | . 15 |  |  |

|                | 2.2   | Transmission Mode                         |      |  |  |

|                | 2.3   | Data Format                               |      |  |  |

|                |       | 2.3.1 Modulation                          | . 16 |  |  |

|                |       | 2.3.2 Line Coding                         | . 16 |  |  |

|                | 2.4   | Dynamic Range                             |      |  |  |

|                |       | 2.4.1 Sensitivity                         | . 17 |  |  |

|                |       | 2.4.2 Overload Limit                      | . 17 |  |  |

|                | 2.5   | Power Penalties and Non-idealities        | . 18 |  |  |

|                |       | 2.5.1 Extinction Ratio                    | . 18 |  |  |

|                |       | 2.5.2 Bandwidth                           | . 18 |  |  |

|                |       | 2.5.3 High-pass Behavior                  |      |  |  |

|                |       | 2.5.4 Crosstalk in Multichannel Receivers |      |  |  |

|                | 2.6   | Detector: P-I-N Photo Diode               | . 20 |  |  |

|                |       | 2.6.1 Responsivity                        | 21   |  |  |

#### x CONTENTS

|   |     | 2.6.2   | Linear Model                 | 21 |

|---|-----|---------|------------------------------|----|

| 3 | Eve | nt-driv | en AGC Concepts              | 23 |

|   | 3.1 |         |                              | 24 |

|   |     | 3.1.1   | Continuous-time Feedback AGC | 24 |

|   |     | 3.1.2   |                              | 24 |

|   |     | 3.1.3   |                              | 25 |

|   |     | 3.1.4   |                              | 30 |

|   | 3.2 | Event-  |                              | 31 |

|   |     | 3.2.1   | • .                          | 32 |

|   |     | 3.2.2   |                              | 32 |

|   |     | 0.2.2   |                              | 34 |

|   |     |         | ·                            | 34 |

|   |     | 3.2.3   | •                            | 35 |

|   |     | 3.2.4   | ~                            | 38 |

|   |     | 3.2.4   |                              | 39 |

|   |     |         | •                            | 40 |

|   |     | 3.2.5   | ·                            | 40 |

|   |     | 3.4.3   |                              | 41 |

|   |     | 3.2.6   |                              | 43 |

|   |     | 3.2.7   | 1.                           | 43 |

|   |     | 3.4.7   | 7 1                          |    |

|   |     |         | 8 1                          | 43 |

|   |     |         |                              | 44 |

|   |     |         | 1 0                          | 44 |

|   |     | 2.0.0   | , 1                          | 44 |

|   |     | 3.2.8   | Conclusion                   | 45 |

| 4 |     |         |                              | 47 |

|   | 4.1 |         |                              | 47 |

|   | 4.2 |         | 6 3                          | 49 |

|   | 4.3 |         |                              | 50 |

|   | 4.4 |         |                              | 51 |

|   | 4.5 |         |                              | 52 |

|   | 4.6 |         |                              | 53 |

|   | 4.7 | Concl   | asion                        | 53 |

| 5 | Eve | nt-driv | en AGC Implementation        | 55 |

|   | 5.1 |         | •                            | 55 |

|   |     | 5.1.1   |                              | 56 |

|   |     |         |                              | 56 |

|   |     |         |                              | 58 |

|   |     | 5.1.2   |                              | 59 |

|   |     | 5.1.3   |                              | 60 |

|   |     |         |                              | 61 |

|   |     |         | 1 11                         | 61 |

|   |     |         |                              | 61 |

|   |     | 5.1.4   |                              | 62 |

|   |     | 0.1.1   |                              | 63 |

|   |     |         |                              | 64 |

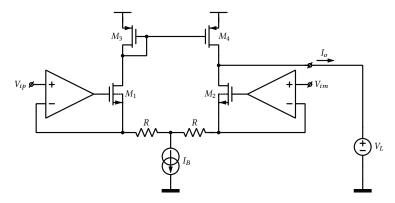

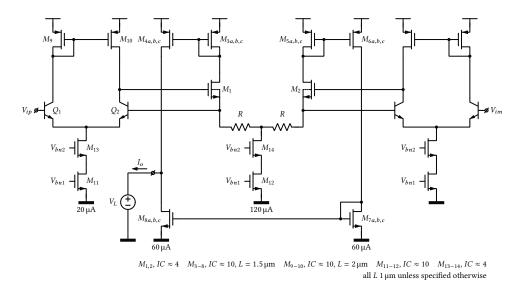

|   | 5.2  | Transc     | conductor                                                | <br> |  | . 64  |

|---|------|------------|----------------------------------------------------------|------|--|-------|

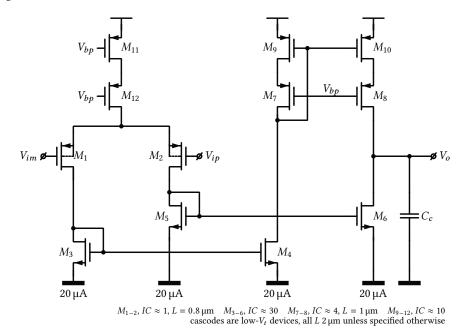

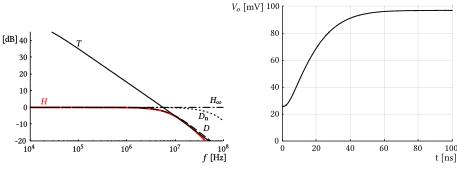

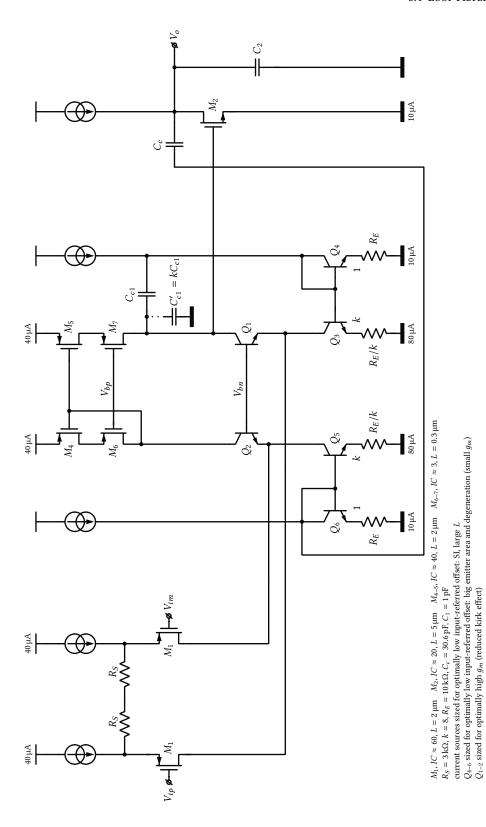

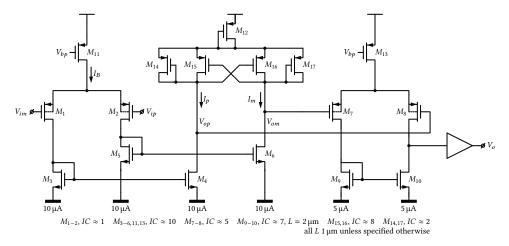

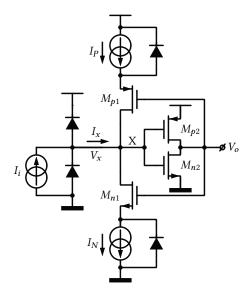

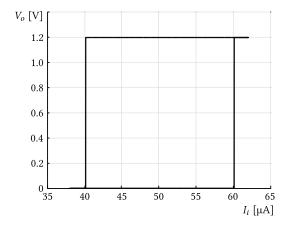

|   |      | 5.2.1      | Circuit                                                  | <br> |  | . 65  |

|   | 5.3  | Logarit    | thmic Amplifier                                          | <br> |  | . 67  |

|   |      | 5.3.1      | Working Principle                                        |      |  |       |

|   |      | 5.3.2      | Circuit                                                  |      |  |       |

|   |      | 5.3.3      | Simulation Results                                       |      |  |       |

|   | 5.4  | Loop F     | Filter                                                   |      |  |       |

|   |      | 5.4.1      | Circuit                                                  |      |  |       |

|   |      | 5.4.2      | Design Considerations                                    |      |  |       |

|   |      | 5.4.3      | Transient Restart Behavior                               |      |  |       |

|   |      | 5.4.4      | Simulation Results                                       |      |  |       |

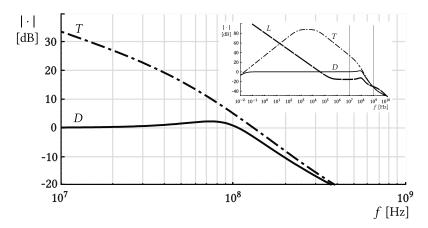

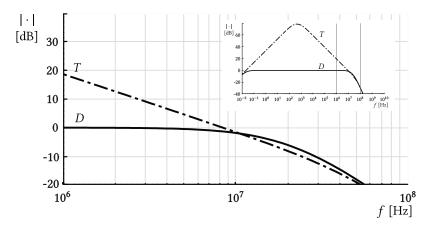

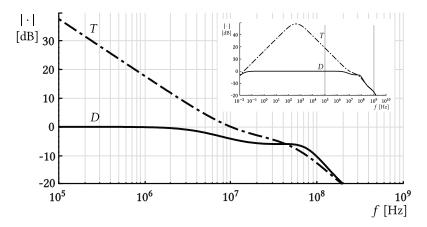

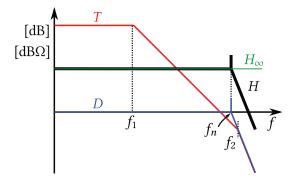

|   |      |            | 5.4.4.1 Decomposition of the External Loop Gain <i>L</i> |      |  |       |

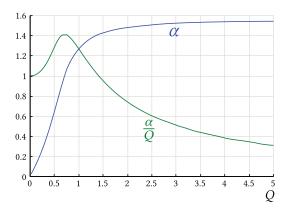

|   |      |            | 5.4.4.2 Step Response of the External Closed-Loop G      |      |  |       |

|   | 5.5  | Quanti     | izer                                                     |      |  |       |

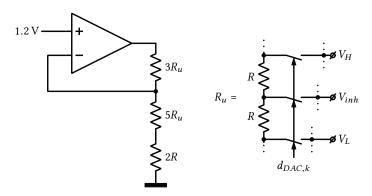

|   |      | ~<br>5.5.1 | DAC and Full-scale Voltage Generator                     |      |  |       |

|   |      | 5.5.2      | Comparator                                               |      |  |       |

|   |      |            | 5.5.2.1 Preamplifier                                     |      |  |       |

|   |      |            | 5.5.2.2 Latch                                            |      |  |       |

|   |      |            | 5.5.2.3 Analog and CMOS Buffer                           |      |  |       |

|   |      | 5.5.3      | Monoflop                                                 |      |  |       |

|   |      | 5.5.4      | Counter and Digital Control                              |      |  |       |

|   |      | 5.5.5      | Simulation Results                                       |      |  |       |

|   | 5.6  | Windo      | ow Comparator                                            |      |  |       |

|   |      | 5.6.1      | Current Comparator                                       |      |  |       |

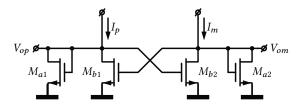

|   |      |            | 5.6.1.1 Input Stage                                      |      |  |       |

|   |      |            | 5.6.1.2 Decision Stage                                   |      |  |       |

|   |      |            | 5.6.1.3 Simulation Results                               |      |  |       |

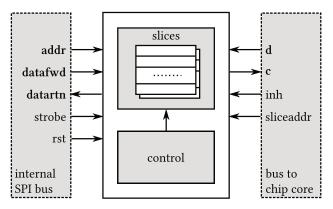

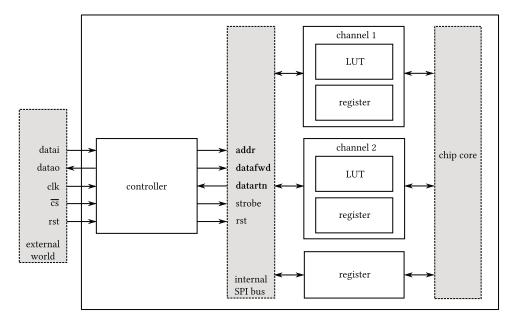

|   | 5.7  | Look-u     | pp Table                                                 |      |  |       |

|   | 5.8  |            | eral Circuits                                            |      |  |       |

|   | 5.9  | _          | mental Results                                           |      |  |       |

|   |      | 5.9.1      | Low-Speed Electrical Tests                               |      |  |       |

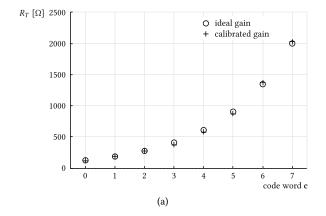

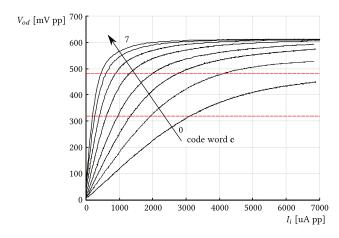

|   |      | 0.7.1      | 5.9.1.1 Calibration and Input-output Characteristics     |      |  |       |

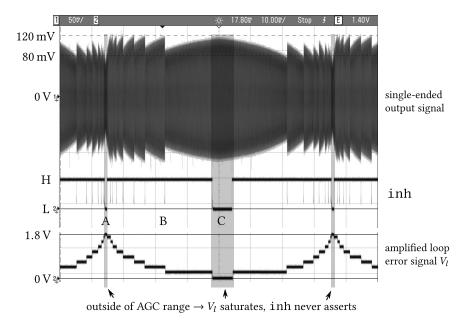

|   |      |            | 5.9.1.2 Functional Test                                  |      |  |       |

|   |      |            | 5.9.1.3 Limit Cycling                                    |      |  |       |

|   |      |            | 5.9.1.4 Step Response                                    |      |  |       |

|   |      |            | 5.9.1.5 Small-signal AGC Loop Filter Step Response       |      |  |       |

|   |      | 5.9.2      | High-Speed Optical Tests                                 |      |  |       |

|   |      | 0.7.2      | 5.9.2.1 Detector                                         |      |  |       |

|   |      |            | 5.9.2.2 Functional Test                                  |      |  |       |

|   | 5.10 | Conclu     | ision                                                    |      |  |       |

| 6 | Mult | tichanr    | nel Optical Receiver                                     |      |  | 105   |

|   | 6.1  |            | Objectives                                               | <br> |  | . 105 |

|   | 6.2  |            | er Array Architecture                                    |      |  |       |

|   |      | 6.2.1      | Channel Architecture                                     |      |  |       |

|   | 6.3  |            | mpedance Amplifier                                       |      |  |       |

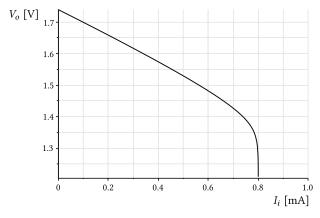

|   |      | 6.3.1      | Large-signal Behavior                                    |      |  |       |

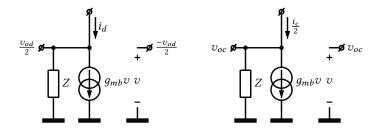

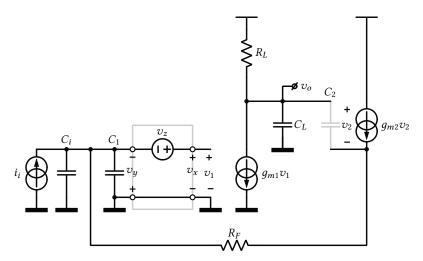

|   |      | 6.3.2      | Linear Model                                             |      |  |       |

|   |      |            |                                                          |      |  |       |

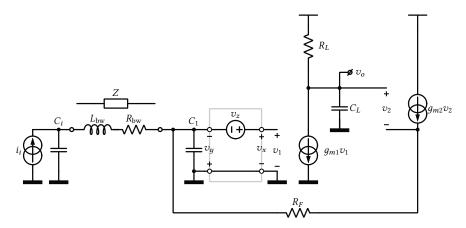

|   |      | 6.3.2.1 Input/output Transfer Function                | 1 |

|---|------|-------------------------------------------------------|---|

|   |      | 6.3.2.2 Terminal Impedances                           | 4 |

|   |      | 6.3.2.3 Input-referred Noise                          | 5 |

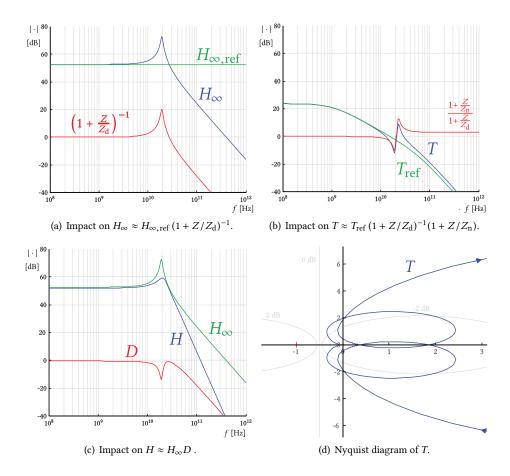

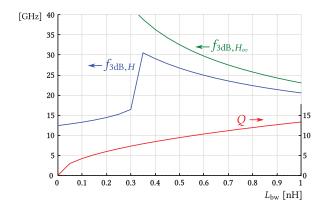

|   |      | 6.3.3 Bandwidth Enhancement Through Inductive Peaking | 7 |

|   |      | 6.3.4 Extending Dynamic Range By Adaptive Biasing     | 1 |

|   | 6.4  | Main Amplifier and Output Buffer                      | 4 |

|   |      | 6.4.1 Large-signal and Small-signal Behavior          | 7 |

|   |      | 6.4.2 Simulation Results                              | 8 |

|   |      | 6.4.3 Output Buffer                                   | 8 |

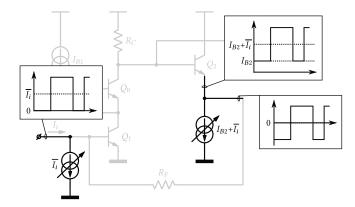

|   | 6.5  | Balancing Loop                                        | 8 |

|   |      | 6.5.1 Principle of Operation                          | 9 |

|   |      | 6.5.1.1 Clipping Nature of the Main Amplifier         | 0 |

|   |      | 6.5.2 Implementation                                  | 0 |

|   | 6.6  | Peripheral Circuits                                   | 2 |

|   | 6.7  | Experimental Results                                  |   |

|   |      | 6.7.1 Impact of Bondwire Inductance                   |   |

|   |      | 6.7.2 Adaptive Biasing                                | 4 |

|   |      | 6.7.3 Sensitivity                                     | 5 |

|   | 6.8  | Conclusion                                            | 8 |

| 7 | Con  | clusion 13                                            | 9 |

| • | 7.1  | Event-driven AGC for Linear Optical Receiver          |   |

|   | 7.2  | Multichannel Optical Receiver                         |   |

|   |      | Col. Co. 157 d. 1771                                  | _ |

| A |      | amary of the General Network Theorem                  |   |

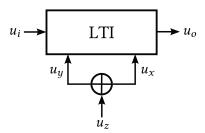

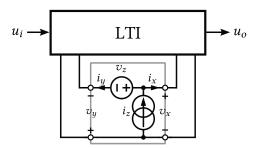

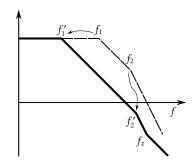

|   | A.1  |                                                       |   |

|   |      | A.1.1 The General Feedback Theorem                    |   |

|   |      | A.1.1.1 Calculation                                   |   |

|   |      | A.1.1.2 Ideal injection points                        |   |

|   |      | A.1.1.3 Discussion                                    |   |

|   |      | A.1.2 The Extra Element Theorem                       |   |

|   | A.2  | Implementation in Cadence Virtuoso                    |   |

|   | Λ.Δ  | implementation in Cadence virtuoso                    | 1 |

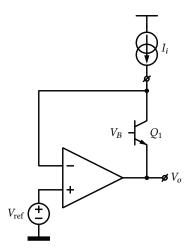

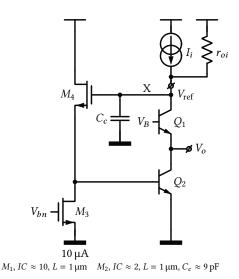

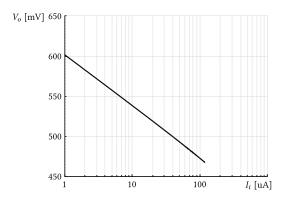

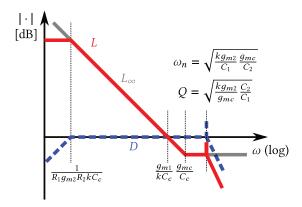

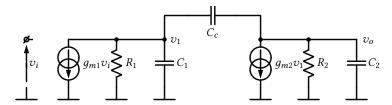

| В | Mill | er Compensation with Capacitance Multipliers 15       |   |

|   | B.1  | 1                                                     |   |

|   | B.2  | Avoiding the RHP Zero: Current Buffer                 | 8 |

|   |      | B.2.1 Ideal Current Buffer                            | 8 |

|   |      | B.2.2 Ideal Current Amplifier                         | 9 |

|   | B.3  | Current Amplifier with Non-zero Input Resistance      |   |

|   |      | B.3.1 Complete Model                                  |   |

|   |      | B.3.2 Internal Loop Compensation                      |   |

|   | B.4  | Conclusion                                            | 6 |

|   | List | of Publications 16                                    | 9 |

# Glossary

ADC analog to digital converter

AGC automatic gain control

AGM asymptotic gain model

AOC active optical cable

APD avalanche photodetector

AWG arrayed waveguide grating

BER bit-error ratio

BNG broadband network gateway

CDN content delivery network

CDR clock-and-data recovery

CID consecutive identical digits

CML current-mode logic CT chain theorem CW continuous-wave

CWDM coarse wavelength division multiplexing

D-OA design-oriented analysis DAC digital to analog converter DIDF dual-input describing function DNL differential non-linearity dnti double-null triple-injection DSP digital signal processing DT dissection theorem DUT device under test

DWDM dense wavelength division multiplexing

EDFA erbium doped fiber amplifier EET extra element theorem

ER extinction ratio

FP7 Seventh Framework Programme

GBW gain-bandwidth product GFT general feedback theorem

#### xiv Glossary

| GNT | general network theorem | n |

|-----|-------------------------|---|

|-----|-------------------------|---|

HDL hardware description language

IIDF incremental-input describing function

INL integral non-linearity

ISI inter-symbol interference

ISP internet service provider

LCA lightwave component analyzer

LHP left hand-side plane LTI linear time-invariant

LUT look-up table

MA main amplifier

MIM metal-insulator-metal

ndi null double-injection NRZ non-return-to-zero

ODB optical duobinary OOK on-off keying

PAM pulse-amplitude modulation PON passive optical network

PP power penalty

PRBS pseudo-random bit sequence PSD power spectral density pss periodic steady-state

PVT process, supply and temperature

RHP right hand-side plane

S2D single-ended to differential

SI strong inversion

si single-injection

SNR signal-to-noise ratio

SOI silicon-on-insulator

SPI serial peripheral interface

TIA transimpedance amplifier

VGA variable gain amplifier

WDM wavelength division multiplexing

WI weak inversion

## Nederlandstalige Samenvatting

Het internet heeft zonder enige twijfel ons leven ingrijpend veranderd. Het stijgend aanbod aan nieuwe online toepassingen, binnen sectoren zoals amusement, handel, industrie en gezondheidszorg vraagt steeds meer bandbreedte en stelt steeds grotere eisen aan de kwaliteit van de netwerk- en ICT-infrastructuur. Vooral de explosieve groei van online video en sociale media vereist grotere datasnelheden. Het net levert inhoud voor consumptie aan, in plaats van louter in connectiviteit tussen machines te voorzien. Het efficiënt schalen van netwerken en datacentra met beperkte kost vormt hierbij een grote uitdaging. Daarbij mag het vermogenverbruik maar beperkt stijgen met de bandbreedte, om extra kosten te vermijden en om de uitstoot van broeikasgassen te beperken. Hierbij moet er wel voor gezorgd worden dat de kwaliteit van de aangeboden diensten niet afneemt.

In de huidige architectuur van het internet zijn eindgebruikers verbonden met het openbare netwerk via het toegangsnetwerk van de lokale internetaanbieder. Traditioneel zijn deze toegangsnetwerken gebaseerd op de bestaande koper- of coaxiale verbindingen, maar tegenwoordig worden er nieuwe passieve optische netwerken (PONs) ontplooid. Deze PONs maken gebruik van optische vezel waardoor ze veel hogere datasnelheden kunnen aanbieden, voor een fractie van het vermogenverbruik. Het dataverkeer van de toegangsnetwerken wordt via Ethernetswitches en breedbandnetwerkgateways doorgesluist naar het ruggengraatnetwerk. Het geheel van deze regionale verbindingen is het metronetwerk. Datacentra zijn via een eigen router verbonden met het ruggengraatnetwerk.

Er zijn verschillende initiatieven in het leven geroepen om een oplossing voor het probleem van de vraag naar stijgende datasnelheden te vinden, met aandacht voor de ecologische en economische impact. Het werk beschreven in deze thesis werd uitgevoerd in de context van twee projecten in het kader van het Europese FP7 programma. Het doel van beide projecten is het ontwikkelen van hooggeïntegreerde opto-elektronische componenten die hogere datasnelheden ondersteunen met laag vermogenverbruik, maar elk concentreert zich op een ander aspect van de netwerkarchitectuur. Mirage focust zich op datacentra, terwijl C3PO zich toelegt op middellange-afstandsnetwerken, zoals het metronetwerk. In het bijzonder besteedt dit werk aandacht aan twee aspecten van de optische ontvangers: ten eerste het vergroten van het dynamisch bereik van een lineaire ontvanger voor modulatieformaten met meerdere niveaus; ten tweede de integratie van meerdere kanalen op eenzelfde chip met beperkte oppervlakte.

Datacentra bieden de eindgebruiker opslagruimte, rekenkracht en software aan op afstand. Ze bestaan uit gateway routers, een lokaal netwerk, servers en opslag, waarbij tot 100 000 apparaten geïntegreerd worden in standaardrekken. Ook hier is schaalbaarheid een groot probleem. Er zijn ingrijpende veranderingen nodig op het vlak van interconnectie en vermogenverbruik om tot een duurzame oplossing te komen. In het bijzonder

leidt een lager vermogenverbruik ook tot een reductie in koelkosten. De verschillende rekken zijn onderling verbonden met actieve optische kabels (AOCs), die op dit moment snelheden tot 25 Gb/s met aan-uitmodulatie (NRZ) ondersteunen. Om hogere datasnelheden over langere kabels te ondersteunen, kunnen een aantal verbeteringen doorgevoerd worden. Daarbij is vooral het gebruik van modulatieformaten met meerdere niveaus interessant. Zo'n modulatieformaten gebruiken de beschikbare bandbreedte efficiënter dan NRZ, maar vereisen wel een lineaire voorversterker in de ontvanger. Het grootste deel van deze dissertatie beschrijft het ontwerp en implementatie van een gebeurtenisgebaseerde automatische versterkingsregeling (AGC) voor het datapad van een lineaire transimpedantieversterker voor hoge snelheden.

Binnen de topologie van het internet bevindt het metronetwerk zich tussen de toegangsnetwerken en het ruggengraatnetwerk. Het strekt zich uit over afstanden tot 500 km. Studies geven aan dat het metro-dataverkeer in de nabije toekomst sterk zal verhogen. Dit is vooral te wijten aan het toenemende verkeer, vooral videostreaming, van content delivery netwerken en bijhorende datacentra die rechtstreeks op de lokale metronetwerken worden aangesloten. Deze evolutie gaat gepaard met een vraag naar hogere datasnelheden. De meest voor de hand liggende oplossing is het gebruik van golflengtemultiplexering met hoge dichtheid (DWDM), waardoor een enkele glasvezel veel hogere datasnelheden kan ondersteunen. Aan de ontvangerkant wordt elke golflengte van het gedemultiplexeerde invallende licht gekoppeld in een fotodiode van een fotodioderooster, die op zijn beurt verbonden is met een kanaal van een meerkanaals ontvanger. Om veel kanalen te ondersteunen moet de fysieke oppervlakte van de kanalen klein zijn. Bovendien dient het vermogenverbruik per kanaal beperkt te zijn om de temperatuur laag genoeg te houden zonder koeling. In het tweede deel van dit werk wordt dan ook dieper ingegaan op de implementatie van een vierkanaals ontvanger, voor een datasnelheid van 4 × 25 Gb/s, met laag vermogenverbruik en beperkte oppervlakte. De afstand tussen de kanalen is gelijk aan die van een standaard fotodioderooster, 250 μm.

Hoofdstuk 1 beschrijft de impact van de stijgende vraag naar bandbreedte in combinatie met lager vermogenverbruik op het ontwerp van de optische ontvanger, zowel in de context van middellange verbindingen (metronetwerken) als van korte verbindingen (datacentra). Daarnaast wordt een korte beschrijving gegeven van een aantal aspecten van geïntegreerd analoog ontwerp: de ontwerpsmethodiek, de modellen voor handberekeningen van de transistoren en een hulpprogramma. Ook wordt een overzicht van de gebruikte technologie gegeven.

Hoofdstuk 2 definieert een aantal essentiële concepten in verband met optische ontvangers. Die zijn nodig voor een goed begrip van de verdere tekst.

De basisprincipes van tegengekoppelde AGC systemen worden aangebracht in het eerste deel van Hoofdstuk 3. Een basismodel in continuë tijd is beschreven, waarbij de instelbare versterker (VGA) het datapad van een lineaire optische ontvanger is. Om modulatieformaten met meerdere niveaus goed te kunnen ontvangen, moet de VGA een goed gecontroleerde frequentiekarakteristiek hebben. In het bijzonder moet doorschot in het tijdsdomein beperkt worden, en dit voor het volledige instelbereik. Er wordt betoogd dat dit moeilijk volledig analoog te implementeren valt. Daarom wordt een gebeurtenisgebaseerde uitbreiding van het continuëtijdsmodel voorgesteld, waarbij zowel de structurele aspecten als het dynamisch gedrag besproken worden. Het resultaat is een systeemmodel van een gekwantiseerde AGC lus, dat als basis dient voor het ontwerp op systeemniveau in Hoofdstuk 4. De gedetailleerde implementatie op circuitniveau wordt verder uitgewerkt in Hoofdstuk 5, waarbij experimentele resultaten de haalbaarheid van de voorgestelde

structuur bevestigen.

Hoofdstuk 6 beschrijft het ontwerp en de implementatie van een  $4 \times 25 \, \mathrm{Gb/s}$  optische ontvanger met meerdere kanalen, voor NRZ modulatie met kleine chipoppervlakte. Er wordt vooral aandacht besteed aan de ingangstrap, waarbij technieken worden beschreven die de bandbreedte en het dynamisch bereik vergroten. Meetresultaten voor NRZ en optische duobinary modulatie worden voorgelegd, alsook de invloed van overspraak op de prestaties.

Het laatste hoofdstuk 7 geeft een overzicht van de belangrijkste conclusies en suggereert een aantal onderwerpen voor verder onderzoek.

Op het einde van het werk zijn twee appendices opgenomen. Appendix A geeft een overzicht van het general network theorem, een theorema dat vaak gebruikt wordt in dit werk en ook numeriek werd geïmplementeerd. De resultaten van Appendix B, een analyse van een tweetrapsopamp, gecompenseerd met capaciteitsvermenigvuldiger, zijn gebruikt bij het ontwerp van een bouwblok in het AGC systeem.

## **English Summary**

The internet has become the ubiquitous tool that has transformed the lives of all of us. New broadband applications in the field of entertainment, commerce, industry, healthcare and social interactions demand increasingly higher data rates and quality of the networks and ICT infrastructure. In addition, high definition video streaming and cloud services will continue to push the demand for bandwidth. These applications are reshaping the internet into a content-centric network. The challenge is to transform the telecom optical networks and data centers such that they can be scaled efficiently, at low cost. Furthermore, from both an environmental and economic perspective, this scaling should go hand in hand with reduced power consumption. This stems from the desire to reduce  $CO_2$  emission and to reduce network operating costs while offering the same service level as today.

In the current architecture of the internet, end-users connect to the public network using the access network of an internet service provider (ISP). Today, this access network either reuses the legacy copper or coaxial network or uses passive optical network (PON) technologies, among which the PON is the most energy efficient and provides the highest data rates. Traffic from the access network is aggregated with Ethernet switches and routed to the core network through the provider edge routers, with broadband network gateways (BNGs) to regulate access and usage. These regional links are collectively called the metro network. Data centers connect to the core network using their own dedicated gateway router.

The problem of increasing data rates, while reducing the economic and environmental impact, has attracted considerable attention. The research described in this work has been performed in the context of two projects part of the European Union Seventh Framework Programme (FP7), which both aim for higher data rates and tight integration while keeping power consumption low. Mirage targets data center applications while C3PO focuses on medium-reach networks, such as the metro network. Specifically, this research considers two aspects of the high-speed optical receivers used in the communication networks: increasing dynamic range of a linear receiver for multilevel modulation through automatic gain control (AGC) and integration of multiple channels on a single chip with a small area footprint.

The data centers of today are high-density computing facilities that provide storage, processing and software as a service to the end-user. They are comprised of gateway routers, a local area network, servers and storage. All of this is organized in racks. The largest units contain over 100 000 servers. The major challenges regarding data centers are scalability and keeping up with increasing amounts of traffic while reducing power consumption (of the devices as well as the associated cooling) and keeping cost minimal. Presently, racks are primarily interconnected with active optical cables (AOCs) which

employ signal rates up to 25 Gb/s per lane with non-return-to-zero (NRZ) modulation. A number of technological developments can be employed in AOCs of the future to provide terabit-capacity optical interconnects over longer distances. One such innovation is the use of multilevel modulation formats, which are more bandwidth-efficient than traditional NRZ modulation. Multilevel modulation requires a linear amplifier as front-end of the optical receiver. The greater part of this dissertation discusses the design and implementation of an AGC system for the data path of a linear transimpedance amplifier (TIA).

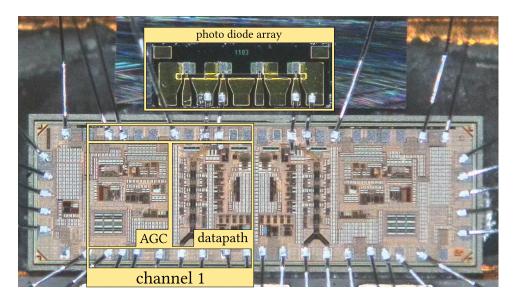

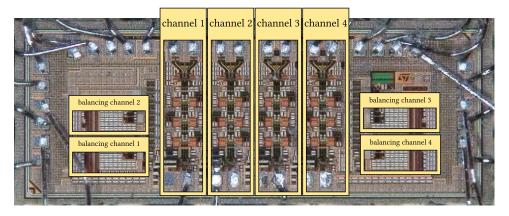

The metro network is the intermediate regional network between the access and core network of the internet architecture, with link lengths up to 500 km. It is estimated that in the near future metro-traffic will increase massively. This growth is attributed mainly to increasing traffic from content delivery networks (CDNs) and data centers, which bypass the core network and directly connect to the metro network. Internet video growth is the major reason for traffic increase. This evolution demands increasingly higher data rates. Today, dense wavelength division multiplexing (DWDM) is widely recognized as being necessary to provide data capacity scalability for future optical networks, as it allows for much higher combined data rates over a single fiber. At the receiver, each wavelength of the demultiplexed incoming light is coupled to a photo diode in a photo diode array which is connected to a dedicated lane of a multichannel receiver. The high number of channels requires small physical channel spacing and tight integration of the diode array with the receiver. In addition, active cooling should be avoided, such that power consumption per receiver lane must be kept low in order not to exceed thermal operation limits. The second component of this work presents the development of an integrated four-channel receiver, targeting 4 × 25 Gb/s data rate, with low power consumption and small footprint to support tight integration with a p-i-n photo diode array with a 250 µm channel pitch.

Chapter 1 discusses the impact of increasing data rates and the desire to reduce power consumption on the design of the optical receiver component, in wide metropolitan area networks as well as in short-reach point-to-point links in data centers. In addition, some aspects of integrated analog circuit design are highlighted: the design flow, transistor hand models, a software design tool. Also, an overview of the process technology is given.

Chapter 2 provides essential optical receiver concepts, which are required to understand the remainder of the work.

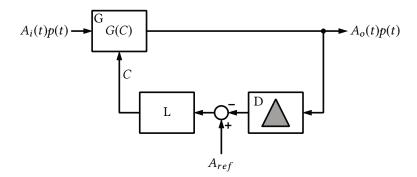

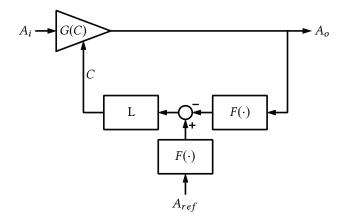

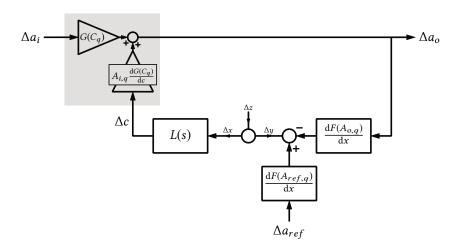

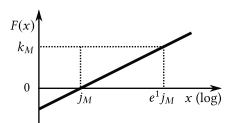

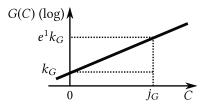

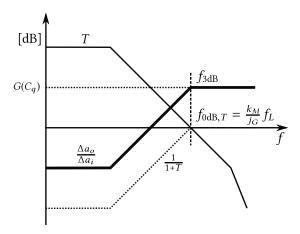

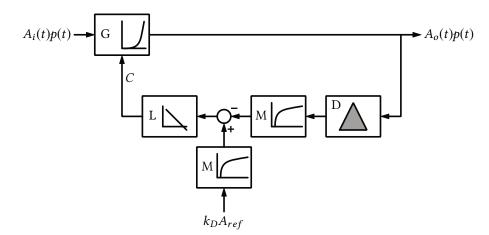

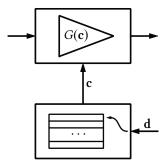

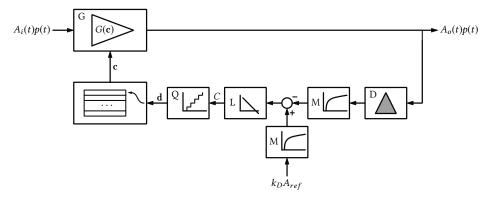

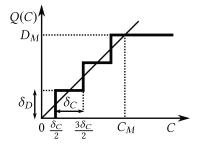

Fundamentals of feedback AGC systems are discussed in the first part of Chapter 3. A basic system model is presented in the continuous-time domain, in which the variable gain amplifier (VGA) constitutes the multistage datapath of a linear optical receiver. To enable reliable reception of multilevel modulation formats, the VGA requires controlled frequency response and in particular limited time-domain overshoot across the gain range. It is argued that this control is hard to achieve with fully analog building blocks. Therefore, an event-driven approach is proposed as an extension of the continuous-time system. Both the structural and behavioral aspects are discussed. The result is a system model of a quantized AGC loop, upon which the system-level design, presented in Chapter 4, is based. In turn, Chapter 5 discusses the detailed implementation of the various building blocks on the circuit level and presents experimental results that confirm the feasibility of the proposed approach.

Chapter 6 discusses the design and implementation of a  $4 \times 25\,\text{Gb/s}$  optical receiver array for NRZ modulation with a small area footprint. The focus lies on the input stages and techniques to extend bandwidth and dynamic range are presented. Measurement results for NRZ and optical duobinary (ODB) modulation are presented, as well as the

influence of crosstalk on the performance.

Finally, Chapter 7 provides an overview of the foremost conclusions of the presented research and includes suggestions for future research.

Two appendices are included. Appendix A gives an overview of the general network theorem (GNT), which is used throughout this work and which has been implemented numerically. The results from Appendix B, the analysis of a two-stage opamp compensated with capacitance multipliers, were used to design a building block for the AGC system.

xxii English Summary

## Chapter 1

## Introduction

This introductory chapter provides the background against which the research described in this work is performed. An overview of today's network topology and its challenges are given. In particular, in Section 1.1, the impact of increasing data rates and the desire to reduce power consumption on the design of the optical receiver component, in wide metropolitan area networks, as well as in short-reach point-to-point links in data centers, is discussed. In Section 1.2, some aspects of the analog design flow used throughout this work are discussed, while the used process technology is shortly described in Section 1.3. Finally, an outline of this dissertation is given in Section 1.4.

### 1.1 Background

The internet has become the ubiquitous tool that has transformed the lives of all of us. New broadband applications in the field of entertainment, commerce, industry, healthcare and social interactions demand increasingly higher data rates and quality of the networks and ICT infrastructure. In addition, high definition video streaming and cloud services will continue to push the demand for bandwidth [1]. These applications are reshaping the internet into a content-centric network. The challenge is to transform the telecom optical networks and data centers such that they can be scaled efficiently, at low cost. Furthermore, from both an environmental and an economic perspective, this scaling should go hand in hand with reduced power consumption. This stems from the desire to reduce  $CO_2$  emission and to reduce network operating costs while offering the same service level as today [2,3].

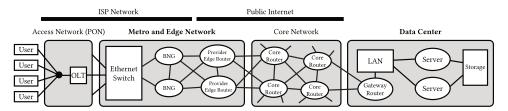

**Figure 1.1:** Architecture of the internet as it is today [4].

In the current architecture of the internet (Fig. 1.1), end-users connect to the public

network using the access network of an internet service provider (ISP) [4]. Today this access network either reuses the legacy copper or coaxial network or uses passive optical network (PON) technologies, among which the PON is the most energy efficient and provides the highest data rates [3,5]. Traffic from the access network is aggregated with Ethernet switches and routed to the core network through the provider edge routers, with broadband network gateways (BNGs) to regulate access and usage. These regional links are collectively called the metro network. The core network comprises high-capacity transport networks and core routers, mainly using optical wavelength division multiplexing (WDM) fiber links. Data centers connect to the core network using their own dedicated gateway router. They are comprised of server and networking infrastructure: servers, storage, local area network and gateway routers. The services offered to the enduser include remote storage, remote software and remote processing [6].

In 2011, the internet was estimated to consume between 170 GW and 307 GW. Although this is a small fraction of the global power consumption,  $1.1\,\%$  to  $1.9\,\%$ , its relative importance will only increase as the internet will continue to provide substitutes for other functions of society that use much more energy [7]. An estimated  $2\,\%$  to  $10\,\%$  of the human carbon emission comes from ICT, of which  $37\,\%$  is due the production of the energy required to operate the telecom infrastructure and devices. The metro/access networks are responsible for  $60\,\%$  of the total power consumption of the communication networks [8].

In 2013, data centers in the U.S. consumed an estimated  $91 \times 10^9$  kW h of energy, equivalent to an average power consumption of 10.5 GW and is expected to increase to roughly 16 GW in 2020 [9]. The SMARTer 2020 report, a widely recognized study, projects the global data center emissions until 2020 and expects these will grow 7 % year-on-year [10].

The problem of increasing data rates, while reducing the economic and environmental impact, has attracted considerable attention. The research described in this work has been performed in the context of two projects part of the European Union Seventh Framework Programme (FP7), which both aim for higher data rates and tight integration while keeping power consumption low. Mirage targets data center applications while C3PO focuses on medium-reach networks, such as the metro network.

#### 1.1.1 Data Centers

In the content-centric internet of today, millions of users demand instant access to vast amounts of data. Data centers are high-density computing facilities that provide storage, processing and software as a service to the end-user [4]. In recent years, they have received significant attention due to the migration to cloud computing. They serve as hosting sites for multi-billion services such as video content distribution, social networking and large-scale computations [11].

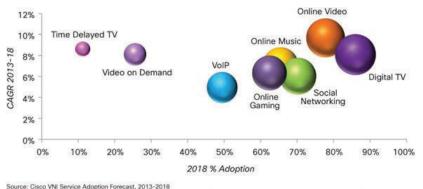

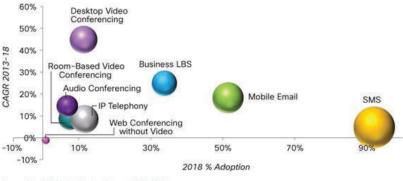

Data centers are comprised of gateway routers, a local area network, servers and storage. The devices are organized in racks, spanning up to 2 km distance (short-reach), and are interconnected with fast optical links. Today's largest data centers contain over 100 000 servers [12]. Cisco predicts that global data center traffic will increase by 2.8 times by 2018, reaching 715 exabytes per month [13]. By then, 78 % of all workloads will be processed in the cloud, nearly double compared to 2013. This is mainly attributed to increased use of cloud services. Figures 1.2 and 1.3 show the projected adoption of residential and business services and growth of online services worldwide in 2018. These figures indicate that online video streaming has a major impact on IP traffic.

Data centers consume enormous amounts of power, with associated cost and envi-

Figure 1.2: Residential services adoption and growth [14]

Source: Cisco VNI Service Adoption Forecast, 2013-2018 Il be 2.1 billion; the number of business mobile users will be 582 million

**Figure 1.3:** Business services adoption and growth [14]

ronmental impact. In 2005, data centers worldwide consumed 0.8 % of the total electricity consumption, amounting to \$7.2 billion per year [15]. Typically, 50 % to 60 % of the energy is consumed in cooling and other overhead [4,16]. In 2010, it was estimated that data center electricity usage likely accounted for between 1.1 % and 1.5 % of the total electricity use, with associated emissions equivalent to 70 to 90 500 MW coal-fired power plants [17]. While a reduction in the pace of growth from previous estimates can be observed, the continued expansion of the industry means that the energy consumption and emission of greenhouse gasses will continue to grow [9].

The major challenges regarding data centers are scalability and keeping up with increasing amounts of traffic while reducing power consumption (of the devices as well as associated cooling) and keeping cost minimal. In order to offer a fast, reliable service, data centers are often geographically distributed with high-capacity optical links between the locations. As cloud services become more widespread and data rates increase, the energy consumption of the cloud devices and network will grow.

In today's data centers, racks are primarily interconnected with active optical cables (AOCs), used to carry hundreds of gigabits through hundreds of meters. Current standards (100G Ethernet, InfiniBand EDR, 32G Fibre Channel, PSM4) employ signal rates up to 25 Gb/s per lane with non-return-to-zero (NRZ) modulation. A number of technological developments can be employed in AOCs of the future to provide terabit-capacity optical interconnects over longer distances:

**Long wavelengths** Wavelengths of 1310 nm or 1550 nm suffer less attenuation than the traditionally used 850 nm, enabling longer-reach networks [18].

**Single-mode fiber** Multi-mode fiber suffers more from limited bandwidth-distance product than single-mode fiber [5].

Wavelength division multiplexing (WDM) and space-multiplexing Combining parallel strands of single-mode fiber with WDM allows for much higher combined data rates [19].

**Space-multiplexing in multi-core fibers** As high-quality glass fiber are becoming broadly available, prices will drop and application in AOCs becomes feasible. This can lead to cost savings as the transceivers require less separate interfaces. Furthermore, in comparison with fiber bundles, fiber management and ventilation issues are mitigated in large data centers.

**Multilevel modulation** Instead of using traditional NRZ modulation, the effective bit rate can be increased by using bandwidth-efficient multilevel modulation. When lower-order modulation formats such as 4-pulse-amplitude modulation (PAM) are used, the increase of the complexity of the electronics is limited [20].

#### Mirage

The project Mirage (Multi-coRe, multilevel, WDM-enAbled embedded optical enGine for Terabit board-to-board and rack-to-rack parallel optics) aims to raise the bar of optical interconnect technology currently used in data centers. The ambition of the project is to increase the optical interconnect speed, which currently tops at around 140 Gb/s per link, to terabit per second numbers. The project introduces several techniques to increase data center scalability and introduce new degrees of parallelism into the optical interconnects of AOCs: data transmission in multicore single-mode fiber and development of the required chip-to-fiber interfaces; introduction of multilevel modulation schemes (4-PAM); introduction of wavelength multiplexing in AOCs.

In this context, the author was involved in the realization of a multichannel high-dynamic range linear transimpedance amplifier (TIA) for multilevel modulation formats. In particular, the author was responsible for the automatic gain control (AGC) system, which was implemented as an event-driven control loop around the linear high-speed datapath, targeting 20 GBd 4-PAM or 26 Gb/s NRZ data.

#### 1.1.2 The Metro Network

The metro network is the intermediate regional network between the access and core network of the internet architecture, with link lengths up to  $500\,\mathrm{km}$ .

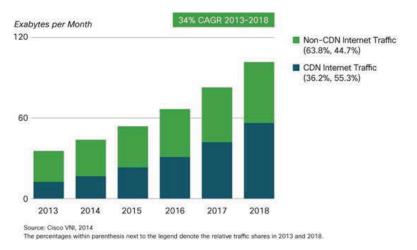

Cisco estimates that metro-only traffic will surpass long-haul traffic (traffic in the core network) in 2015 and will account for 62 % of the total IP traffic in 2018, 2.6 times higher than long-haul (Fig. 1.4). This growth is attributed mainly to increasing traffic from content delivery networks (CDNs) and data centers, which bypass the core network and directly connect to the metro network. These CDNs will carry 55 % of the total internet traffic by 2018. As long-haul traffic is routed through the metro networks, total metro traffic already exceeds long-haul traffic. Internet video growth, including video-on-demand,

videoconferencing and video file sharing, is the major reason for traffic increase and will account for 79 % of the total traffic in 2018 [14].

**Figure 1.4:** Estimated increase of CDN traffic by 2018 [14].

Metro networks consist mainly of electronic BNGs and edge routers, which are the gateway to the access network and core network, respectively. Traditionally, metropolitan area networks were based on switched synchronous optical network/synchronous digital hierarchy (SONET/SDH) architectures. To increase flexibility, scalability and cost-effectiveness, ISPs shifted to Ethernet-based networks. However, this still required optical-electronic-optical conversion at each intermediate node, with associated high cost and power consumption [21]. These redundant conversions were eliminated by assigning a dedicated wavelength channel (colors of light) to each connection between an intermediate node and a hub node. The latter connects the metro network to the core or access network. Furthermore, this technique enables higher data rates on a single fiber due to simultaneously transmitting multiple wavelengths of light. In addition exploiting spatial diversity using parallel fibers can further increase the data rates. Although optical technology is energy efficient, the aggregation of access network traffic can only be performed electronically. Therefore, proper optimization of both the optical and electronic devices is important [8].

Two types of WDM exist. Coarse wavelength division multiplexing (CWDM) is a WDM technology, where the available bandwidth is divided in a coarse grid of up to 20 wavelengths. The relatively high distance between the wavelengths or channels makes optical component performance, such as wavelength stability of the laser, less critical and hence enables lower cost. However, total capacity is limited which implies scalability issues. Still, the small number of channels makes equipment compact.

Today, using dense wavelength division multiplexing (DWDM) across core, metro and access network is widely recognized as being necessary to provide data capacity scalability for future optical networks. The denser wavelength grid allows more frequency diversity. The channel spacing in today's DWDM systems is 100 GHz, 50 GHz or 25 GHz (around 0.8 nm, 0.4 nm or 0.25 nm), which allows up to 160 channels in one fiber [22]. The dense packing of the wavelengths imposes additional constraints on the equipment: highselectivity optical (de)multiplexers (arrayed waveguide gratings (AWGs)) are required to aggregate the wavelengths at the transmitting end and to split the combined signal into separate channels at the receiving end. Moreover, high-precision, temperature-stable expensive lasers must keep the channels exactly on target as almost no frequency drift is allowed. Currently, this means keeping the laser at a constant temperature which implies additional cooling costs. At the receiving end, each wavelength of the demultiplexed incoming light is coupled to a photo diode in a photo diode array which is connected to a dedicated lane of a multichannel receiver. The high number of channels requires small physical channel spacing and tight integration of the diode array with the receiver. In addition, as active cooling should be avoided, power consumption per receiver lane must be kept low in order not to exceed thermal operation limits.

#### C<sub>3</sub>PO

C3PO (Colorless and Coolerless Components for low Power Optical Networks) focuses on reducing power consumption on multiple levels of the physical network architecture, while enabling bandwidth increase and constraining cost. The project develops colorless (non-wavelength specific) devices for use in DWDM systems. This allows to use the technology in various contexts, from low-cost, reconfigurable router interface for metro networks to the optical modem of the end-user in access networks. Coolerless components operate without active cooling, hence reducing operating costs and allowing tighter integration of photonic and electronic components. This reduction of thermal management requires lower power consumption of the active components, such as laser, modulator, driver and receiver. The project targets four lanes/wavelengths of 25 Gb/s each, resulting in 100 Gb/s total line rate. Since the envisioned system has to support distances up to 500 km, the components have to support optical duobinary (ODB) modulation, next to conventional NRZ, for its greater dispersion tolerance. The ODB signals are directly decoded by the same direct detection receiver.

The author was responsible for the development of the integrated four-channel receiver, targeting  $4\times25\,\text{Gb/s}$  data rate, with low power consumption and small footprint to support tight integration with a p-i-n photo diode array with a 250 µm channel pitch.

### 1.2 Aspects of Analog Circuit Design

This section shortly presents the design flow, active device models for hand design, analytical tools and a software design tool used during the course of this work.

### 1.2.1 Design Flow

Although it is impossible to devise a general recipe for the design of analog circuits, it is useful to describe, from a high-level point of view, the design flow that is used for most blocks in this works. Even though presented in an idealized linear fashion, inevitably some (hopefully limited) iterations or even a full restart are required. Also, it may be possible to skip some steps. Sometimes, a specific circuit requires a completely different approach.

The starting point is the main block specifications, which may be derived using any combination of system level modeling, rules of thumb, good design practices or experience. The flow is based on the 3-sigma flow described in [23].

- **Topology selection** A candidate topology is selected that could satisfy the block specifications.

- **Design equations** A circuit model is set up and analytical expressions that express the main block specifications, as a function of device parameters and the topology, are derived. Care must be taken that the model is not overly complicated or simplified. The expressions should be useful for design (see also Appendix A) [24]. A simulator can be used to develop and/or validate the model.

- **Initial sizing** Based on the design equations, knowledge of device operation and its trade-offs, rules of thumb, good practices and experience, an initial set of device parameters is chosen. Note that the set of design equations is invariably underdetermined which explains the aspect of 'choice'. This initial sizing is verified with a simulator.

- (Partial) 3-sigma corner extraction To cope with process, supply and temperature (PVT) variations, operating corners and local mismatch, partial 3-sigma corners are extracted for each block specification, based on a Monte Carlo simulation run with limited number of samples (e.g. 100). The block specifications need to be formalized to allow numerical validation. Their probability density function is estimated. Software tool support is a must. In this work Cadence's Virtuoso ADE XL is fit for the purpose.

- Resizing If necessary, the initial sizing is adapted such that all the specifications are satisfied across the extracted partial 3-sigma corners.

- **Monte Carlo run with auto stop** A Monte Carlo simulation run is executed to verify the circuit under PVT, operating corners and mismatch variations. The simulator automatically stops the run when the yield estimates for the specifications are met with a certain confidence for a given target yield. This ensures an optimum number of samples. It can be shown that, on average, at least 1400 samples are needed to predict 3-sigma yield with 95 % statistical confidence.

- Layout and post-layout verification The circuit is converted to a physical layout. Parasitics and layout dependent effects (e.g. well proximity effect, electromigration effects) are extracted and back-annotated. Another Monte Carlo run with auto stop verifies the post-layout circuit behavior.

For parasitic- and layout-sensitive circuits, specialized tools such as Cadence's Electrically-Aware Design suite can reduce the iteration time by allowing to include parasitics and layout dependent effects early on in the flow. They can be estimated or even extracted from a partial layout. In addition, tools such as worst-case corner extraction, high-sigma yield, global and local optimization, sensitivity and reliability analyses...help the designer in the sizing and verification process and shorten design time.

#### 1.2.2 **Transistor Hand Calculation Models**

This section concisely introduces the transistor models used for hand design. The active devices offered in the process technology used for the designs in this work (Section 1.3) are enhancement mode MOSFETs and bipolar junction transistors.

#### 1.2.2.1 MOSFETs

A MOS transistor can be operated anywhere in the continuum between weak inversion (WI), strong inversion (SI) and SI with velocity saturation. The inversion level can, a.o., be expressed as inversion coefficient IC, transconductance efficiency  $g_m/I_D$  or effective gatesource voltage  $V_{EFF}$ . For hand calculations and as a general MOSFET design approach, this work follows [25,26], which is based on the EKV model [27]. The inversion coefficient is a primary design parameter, along with channel length and drain current. Drain current is given by:

$$I_D = I_o \frac{W}{I} IC \tag{1.1}$$

in which  $I_o=2n_0\mu_0C'_{ox}U_t^2$  is the technology current, with  $n_0$ ,  $\mu_0$ ,  $C'_{ox}$  and  $U_t$  the substrate factor, mobility, gate-oxide capacitance and thermal voltage, respectively. The selection of inversion coefficient IC, drain current  $I_D$  and channel length L is governed by the circuit design equations (e.g. which impose a certain  $g_m$ ) and permits different tradeoffs in bandwidth, gain, matching, noise, etc. Channel width W follows from Eq. (1.1). Velocity saturation can be included by replacing IC by a modified value. For example, in the  $g_m/I_D$  curve (see Fig. 1.6(a)), replace IC by  $IC(1+IC/IC_{CRIT})$ , in which  $IC_{CRIT}$  denotes the transition point between the SI  $g_m/I_D$  without velocity saturation and the velocity saturated value. While  $I_o$  is relatively independent of the channel length (and certainly fulfills the needs for a hand calculation model),  $IC_{CRIT}$  is dependent on the electrical field strength and should be extracted for different channel lengths. The reader is referred to [26] for further parameters, expressions and relations.

This design methodology based on inversion level allows to fully exploit the potential of MOS transistors and can also be used with modern process technologies (45 nm and below). The partnership between the BSIM6 and EKV modeling group, an effort to replace the older BSIM3, BSIM4 and PSP compact models for bulk CMOS processes [28], and emerging publications on methodologies in processes with very small channel lengths [29,30], indicate the increased importance of both accurate modeling and hand design in all regions of operations.

#### 1.2.2.2 Bipolar Junction Transistors

The collector current of a bipolar transistor is exponentially dependent on the base-emitter voltage, over decades of collector current. A simple version of the Gummel-Poon model, which has the Ebers-Moll equations at its core, augmented with junction capacitances, is sufficient as a hand calculation model [31]. Effects such as emitter crowding, Kirk-effect and self-heating are assessed graphically (Section 1.2.3) and with the simulator.

#### **1.2.3** Tools

During the course of this work, various analytical techniques, collectively referred to as methods of design-oriented analysis [24, 32, 33] were acquired and applied consciously. These methods make it easier to analyze a circuit, and aim for resulting expressions that are useful to achieve the design objectives. These techniques range from simple, such as the notion of inverted poles and zeros and doing algebra on the graph, to more advanced. An example of the latter is the general network theorem (GNT) and its descendants, the general feedback theorem (GFT), extra element theorem (EET) and chain theorem (CT),

that allow to decompose a transfer function such that its constituent parts have a specific meaning to the circuit. In order to be able to apply these theorems numerically to real designs, they were integrated as a new analysis in Cadence Virtuoso during this work. Appendix A presents a summary.

A software tool was developed to aid the designer in visualizing and exploring the various trade-offs inherent to a single device, i.e. a bipolar transistor, MOSFET or even a passive. This tool allows to plot single parameters or expressions governing device behavior as a function of operating point, temperature and physical parameters. It helps the designer in sizing a device and choosing quiescent currents, based on the graphical representation. This graphical design method was used extensively in the vacuum tube and early transistor era [34,35] and is complementary to equation-based design. A lot of principal design equations that describe the behavior of a circuit are a function of operating point parameters of active devices: inversion coefficient, transconductance, output conductance... A major design task involves translating these parameters to bias current, emitter area, gate area (see Section 1.2.1). The effect of a given choice on the design equations as well as on other, perhaps overlooked parameters, is quickly made clear by the various plots. This leads to less iterations and more efficient design.

**Figure 1.5:** Main interface of the design tool.

It is the author's experience that the different trade-offs and optimal operating region for a certain parameter are identified with increasingly less effort as the shape of a graph (including some key numbers) is 'automatically' memorized over time. Then, dependence on the software gradually reduces. This may be of higher interest than trying to remember a bunch of potentially complex equations. Case in point is the MOS transistor, whose properties change widely over inversion level, drain current and gate length (already ignoring all the higher-order effects).

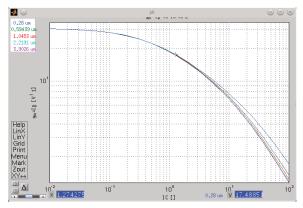

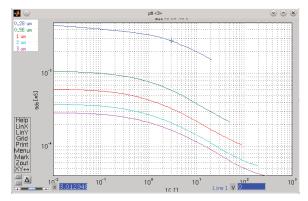

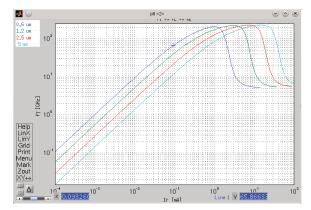

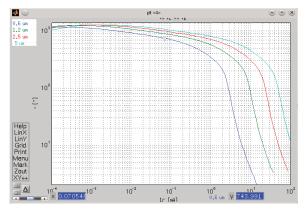

Figure 1.5 depicts the main interface of the software tool. Example plots for the technology used in this work (Section 1.3) are shown in Figs. 1.6 and 1.7: the transconductance efficiency  $g_m/I_D$  curve of a typical NMOS transistor (Fig. 1.6(a)), for various channel lengths; the output conductance  $g_{ds}$  of a NMOS transistor, for various channel lengths, at a fixed drain current (Fig. 1.6(b)); the transition frequency  $f_T$  of a bipolar transistor, for various emitter widths (Fig. 1.7(a)); the forward current gain  $\beta$  of an NPN bipolar transistor, for various emitter widths (Fig. 1.7(b)).

(a) Transconductance efficiency  $g_m/I_D$  of a MOS transistor, for various channel lengths, versus inversion coefficient IC.

(b) Output conductance  $g_{ds}$  of a MOS transistor, for various channel lengths, at fixed drain current, versus inversion coefficient IC.

**Figure 1.6:** Illustration of plots generated by the design tool for a double-oxide NMOS transistor.

(a) Transition frequency  $f_T$  of a bipolar transistor, for various emitter widths, versus collector current  $I_C$

(b) Forward current gain  $\beta$  of a bipolar transistor, for various emitter widths, versus collector current  $I_C$ .

Figure 1.7: Illustration of plots generated by the design tool for a high-speed bipolar NPN transistor.

#### 1.3 **Technology**

Both the optical multichannel NRZ receiver and the optical linear receiver with AGC system were implemented in a 0.13 µm SiGe BiCMOS process [36]. A BiCMOS technology allows integration of high performance analog blocks with low-density logic. It combines the high-speed, high current capability and low noise of bipolar devices with the low-power MOS transistor (for logic) [37]. For the implementation of the high-speed datapaths, the bipolar transistor is a better choice as it is faster, has higher current capability, has better transconductance than a MOS transistor at equal current, offers better inputreferred voltage matching and is optimized for low noise. The MOS transistors are used in CMOS logic circuits and whenever e.g. their infinite input resistance is advantageous, a complementary topology is useful, smaller input voltages are needed (in WI)...

For a given BiCMOS node, a comparable CMOS technology would be scaled by two generations. Hence, 65 nm CMOS offers similar speed as 0.13 µm BiCMOS (bipolar transistors). However, analog circuits show less benefit from CMOS scaling than their digital counterparts as the passive components do not scale as fast (if at all) and the supply voltage decreases, which limits dynamic range and headroom in general. In addition, the cost per unit of area for a design in a BiCMOS process in a multiproject wafer run is lower than in a comparable CMOS process. Also, compared to bulk CMOS, the BiCMOS process has a high-ohmic P- substrate, which is beneficial to reduce crosstalk (Section 2.5.4).

In the front-end, the technology offers high-speed vertical NPN bipolar transistors with transition frequency  $f_T$  up to 220 GHz, as shown in Fig. 1.7(a). The (open base) collector-emitter breakdown voltage is 1.2 V. Figure 1.7(b) indicates that the forward current gain  $\beta$  easily exceeds 500, at typical bias currents. Therefore, in all small-signal equivalent circuit,  $\beta$  will be assumed infinite if not otherwise noted. Also available are lower speed ( $f_T = 120 \text{ GHz}$ ) NPN transistors with higher breakdown voltage (1.6 V). Low-speed, low- $\beta$  lateral PNP devices are available for band gap references.

Single-oxide (1.2 V, 0.13 μm) and dual-oxide (2.5 V, 0.28 μm) NMOS and PMOS transistors are offered. Each type is available in a natural-, low- or high- $V_T$  version. The low- $V_T$  devices can be used as self-cascode devices. The relevant technology currents  $I_o$ (Section 1.2.2) are listed in Table 1.1. As expected, due to lower carrier mobility, PMOS devices have a 3 to 5 times lower  $I_o$  than NMOS devices.

|              | Device | $L_{\min}$ [ $\mu$ m] | <i>I</i> <sub>o</sub> [μA] |

|--------------|--------|-----------------------|----------------------------|

| double-oxide |        |                       |                            |

|              | NMOS   | 0.28                  | 0.34                       |

|              | PMOS   | 0.28                  | 0.07                       |

| single-oxide |        |                       |                            |

|              | NMOS   | 0.13                  | 0.55                       |

|              | PMOS   | 0.13                  | 0.13                       |

Table 1.1: Technology currents of the MOS transistors in the given 0.13 µm BiCMOS technology (at 300 K).

As for passive devices, the technology offers capacitors, resistors and inductors. The capacitors are either of the poly-well (MOS-capacitors) or the metal-insulator-metal (MIM) type. The latter offers much greater linearity and stability over PVT variations, but has less capacitance per unit area. The resistors are of the diffusion-, metal- or poly-type, the latter with various doping levels. A high-sheet resistance poly resistor is also available.

In the back-end, 6 metal layers plus one aluminium top layer are available for routing. The upper two metal layers are much ticker than the lower metals.

#### **Outline of the Dissertation** 1.4

This chapter has presented the background against which the research in this work is performed. Furthermore, some aspects of integrated analog circuit design have been highlighted: the design flow, transistor hand models and a software tool. In addition, the technology in which the integrated circuits described in this work have been implemented, has been presented.

The remainder of this dissertation is composed of two major parts: the design and implementation of an event-driven AGC system for a high-speed linear optical receiver and the development of a limiting  $4 \times 25$  Gb/s receiver array. It should be mentioned that, although the AGC system is presented first, the real chronology was in reverse order. Hence, the wealth of experience gathered from developing the 4 × 25 Gb/s receiver was applied to the design of the datapath in the linear receiver.

In Chapter 2, basic optical receiver concepts, necessary to understand the material in the subsequent chapters are reviewed, in particular the requirements and their implications on the design of the receiver array and the datapath of the linear receiver.

Chapters 3 to 5 constitute the bulk of this work: the event-driven AGC system embedded in a high-speed linear optical receiver. In the first part of Chapter 3, the fundamentals of feedback AGC systems are introduced. In the second part, an event-driven approach is proposed and developed. Basic limitations and design relations are derived and further built upon in Chapter 4, in which the AGC system is designed on the system level. Chapter 5 presents the detailed design of the building blocks on the circuit level, along with experimental results, which underline the successful implementation of the proposed

Chapter 6 presents the design of the  $4 \times 25$  Gb/s receiver array, focusing on the TIA input stage and discussing techniques to improve bandwidth and dynamic range. Measurement results are presented.

Finally, Chapter 7 gives general conclusive remarks and suggests some topics for further research.

Two appendices are included. Appendix A gives a short introduction to the general network theorem (GNT) and its derived theorems. These theorems provide fast analytical techniques to analyze linear systems and are used throughout this book. Appendix B presents an analysis of a two-stage opamp compensated with capacitance multipliers. This topology was used for a building block in the AGC system.

# **Chapter 2**

# **Optical Receiver Concepts**

This chapter introduces essential optical receiver concepts which are relevant for the remainder of this work.

The basic structure of an optical receiver is presented in Section 2.1. Transmission modes and data formats are described in Sections 2.2 and 2.3, respectively. The dynamic range, determined by the sensitivity and overload limit, is discussed in Section 2.4. The concept of power penalty and the impact of several non-idealities, in particular the problem of crosstalk in a multichannel receivers, is presented in Section 2.5. Finally, an overview of the p-i-n photo diode is given in Section 2.6. Note that this work is only concerned with direct detection of the optical input signal. As such, coherent receivers are beyond the scope of this text.

# 2.1 Overview

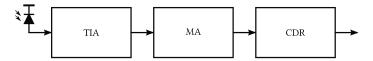

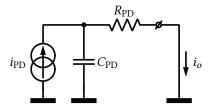

An optical receiver for baseband modulation is generally composed of four building blocks (Fig. 2.1): a detector, transimpedance amplifier (TIA), main amplifier (MA) and clock-and-data recovery (CDR) block [18]. Information is transmitted on an optical carrier in a certain modulation format. The function of the receiver is to recover the information embedded in the received signal.

Figure 2.1: Conceptual block diagram of a optical receiver.

The detector linearly converts the incident optical power to a current, which is amplified and converted to a voltage by the TIA. The MA provides further amplification and can be limiting or linear, depending on the modulation format. The MA and CDR jointly recover amplitude and timing information and act as a decision block. These functional building blocks can be combined in the physical implementation.

In this work, the focus lies on the TIA and MA, which will be integrated on one chip. Although no CDR is included, the system is still denoted as a 'receiver'. Chapter 6 de-

scribes a multichannel limiting receiver, while Chapter 5 presents the design of an automatic gain control (AGC) system embedded in a linear receiver.

# 2.2 Transmission Mode

In continuous-wave (CW) transmission, data packets are transmitted in a continuous, uninterrupted stream of bits or symbols. The incident optical power is relatively constant once reception has started. In burst-mode transmission, data arrives in bursts with strongly varying power levels. This requires a different approach for the design of a burst-mode receiver [38, 39]. This work only considers CW transmission, in which data arrives in a continuous fashion and not in individual bursts.

# 2.3 Data Format

The data format of an optical information stream is given by the modulation format and type of line coding. The data format typically used with limiting receivers (Chapter 6) is non-return-to-zero (NRZ) or optical duobinary (ODB), while the linear receiver (Chapter 5) is made for multilevel modulation such as pulse-amplitude modulation (PAM).

# 2.3.1 Modulation

Information can be conveyed in a single-mode optical fiber by modulation of three physical attributes of the optical field: intensity, phase and polarization. Among the multitude of existing optical modulation formats, the simplest one is NRZ or on-off keying (OOK), in which information appears as two intensity levels: the optical signal is on for a one bit and off for a zero bit. This format puts the least constraints on the receiver linearity. Given a bit rate of  $R_b$  bits/s, it can be shown that most of the power is confined in a bandwidth of  $R_b$  Hz [40].

Spectral efficiency can be increased by adding more intensity levels, as in PAM. This also alleviates inter-symbol interference (ISI) induced by chromatic dispersion as, for a given bit-rate, the required bandwidth is lower compared to NRZ. However, it makes the design of the receiver more difficult as a linear datapath is required with controlled overshoot. In addition, a higher signal-to-noise ratio is needed for reliable detection.

A compromise between the chromatic dispersion tolerance of multilevel schemes and simplicity and low-cost of direct detection receivers is found in ODB modulation. The electrical three-level output of a precoder is mapped into three optical states: low and high optical intensity, of which the phase of the optical field can be inverting or non-inverting [41–43]. The precoded ODB signal can be demodulated into a NRZ-like signal by a conventional direct detection receiver.

Many more complex modulation schemes also embed information in the phase and polarization of the optical field, a discussion which is beyond the scope of this work [44].

# 2.3.2 Line Coding

Line coding is usually applied to a data stream to provide the following properties: dc balance, short run lengths and high transition density. The time-average of a dc balanced signal is centered between the extreme values and carries no information. This allows

for ac coupling or functionally equivalent operations, such as offset compensation. However, in order to limit the power penalty (Section 2.5.3) due to baseline wander or droop, the low-frequency content of the data should be limited. Hence, a maximum number of consecutive identical bits or symbols (run-length) is usually imposed. A high transition density is desired for the clock recovery. Well-known types of line coding include pseudorandom bit sequence (PRBS) scrambling and block coding (e.g. 8B/10B, 64B/66B) [45].

#### 2.4 **Dynamic Range**

The dynamic range of an optical receiver is defined as the input (optical power or electrical current) range where a specified signal quality is achieved. Dynamic range is lower bounded by the sensitivity limit and upper bounded by the overload limit. Signal quality is usually expressed as a bit-error ratio (BER), although sometimes signal-to-noise ratio (SNR) or SNR per bit  $(E_b/N_0)$  is used. The BER associated with 'error-free' reception depends on the context. In this work, the target is  $10^{-12}$ . Visually, received signal quality is sometimes evaluated on the eye diagram. Note that error-correcting codes can be used to obtain a lower BER at the expense of some overhead.

#### 2.4.1 Sensitivity

The sensitivity limit equals the smallest input signal that can still be received with a certain quality. For NRZ modulation, free of ISI and only Gaussian signal-independent noise, the average optical sensitivity can be expressed as:

$$\overline{P}_{\rm sens} = Q \frac{i_n^{\rm rms}}{\mathcal{R}} \tag{2.1}$$

with  $i_n^{\rm rms}$  the total rms input-referred noise current of the receiver and  $\mathcal{R}$  the photo diode responsivity (Section 2.6). The Personick-Q Q expresses how much larger the optical signal needs to be, compared to the noise, to obtain a given BER. Formally, the threshold of the decision circuit should be at least Q standard deviations (of the noise) above or below the mean high or low level to ensure a desired error rate [46]. For a BER of 10<sup>-12</sup>, Q = 7.035.

Equation (2.1) can also be expressed in the electrical domain as follows, assuming infinite extinction ratio (ER):

$$i_{\rm sens}^{\rm pp} = 2 \, Q \, i_n^{\rm rms} \tag{2.2}$$

in which  $i_{\text{sens}}^{\text{pp}}$  is the minimum *peak-to-peak* input current.

In this work, this simple model will be used as p-i-n photo diode noise is largely signalindependent.

#### 2.4.2 **Overload Limit**

As the input signal increases beyond the sensitivity limit, the BER continues to decrease, typically until a BER-floor is observed. At a given input level, signal quality degrades again as large-signal effects such as pulse-width modulation, jitter and asymmetric clipping distort the output eye. The overload limit,  $\overline{P}_{ovl}$  or  $i_{ovl}^{pp}$ , equals the maximum input level where a specified signal quality is still obtained. No general formula exists as the overload limit is highly topology-dependent.

The design described in Chapter 5 includes AGC to increase the overload limit and hence increase the dynamic range.

# 2.5 Power Penalties and Non-idealities

Several non-idealities in the receiver degrade the performance or quality of the received signal. A concept that allows to quantify these impairments is power penalty (PP). Formally, a PP related to an impairment is the increase in average optical transmit power necessary to achieve the same BER as in the absence of the impairment. The relevant PP's in the context of this work are described concisely in this section. Several other power penalties are covered in literature [18].

### 2.5.1 Extinction Ratio

When an optical transmitter transmits a zero, the light is not completely shut off. The ratio of the (time-average) power of a logical '1' to the (time-average) power of logical '0' is called ER:

$$ER = \frac{P_1}{P_0} \tag{2.3}$$

Ideally ER is infinite. It can be shown that, for unamplified p-i-n receivers, the PP due to finite ER is [18]:

$$PP = \frac{ER + 1}{ER - 1} \tag{2.4}$$

For  $ER = 10 \, dB$ ,  $PP = 0.87 \, dB$ .

# 2.5.2 Bandwidth

Limited bandwidth of a receiver introduces ISI and limits the output swing of certain bit sequences (those with higher frequency content). As a result, the vertical eye opening is reduced from  $V_h$  to  $V_h'$ . In order to restore the vertical eye opening and original BER, the output swing needs to increase to  $PP \cdot V_h$ , such that:

$$PP = \frac{V_h}{V_h'} \tag{2.5}$$

# 2.5.3 High-pass Behavior

Certain circuit topologies, such as balancing, feedback offset compensation or ac coupling, introduce a high-pass pole in the small-signal gain of the datapath. This introduces drift, droop or baseline wander in the output signal when the input signal remains at the same level for a long period of time, e.g. when receiving a long string of consecutive identical digits (CID). This causes a degradation of signal quality (BER).

It can be shown that the PP, for NRZ modulation, associated with a single high-pass pole  $f_{pL}$  is [18]:

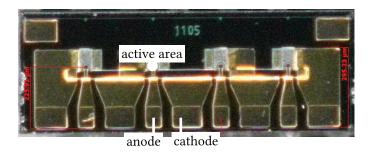

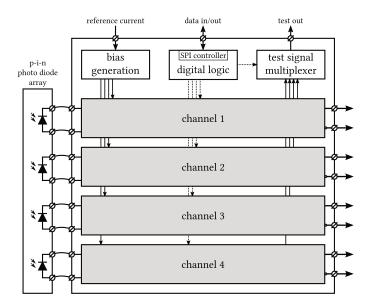

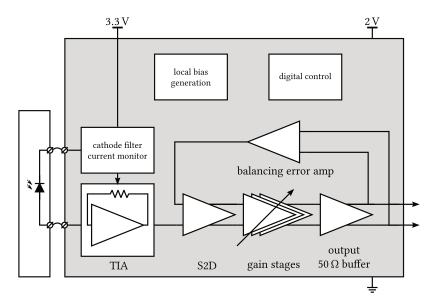

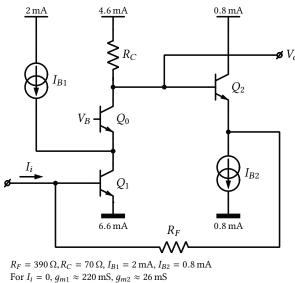

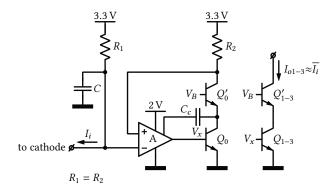

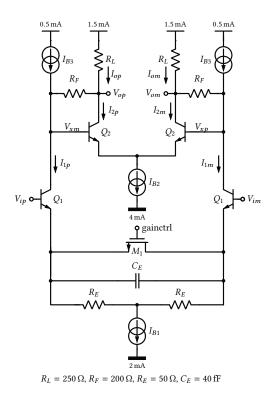

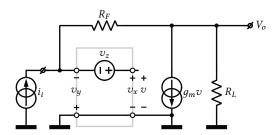

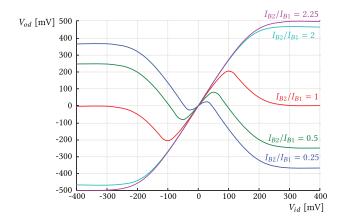

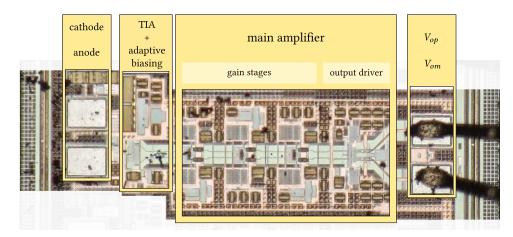

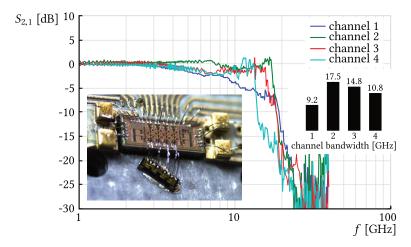

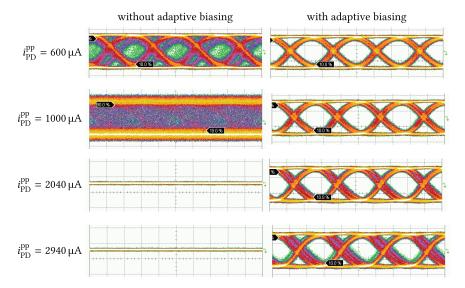

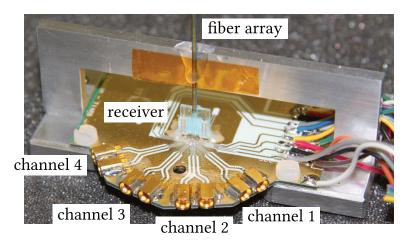

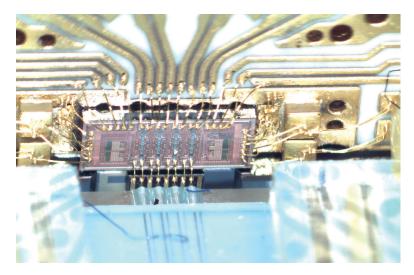

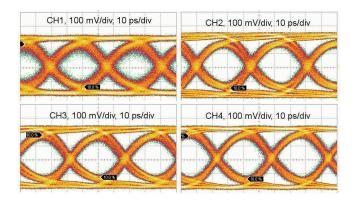

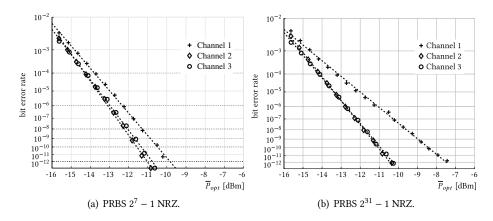

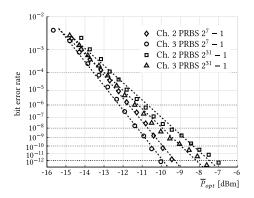

$$PP = 1 + \frac{2\pi f_{pL}r}{R_h} \tag{2.6}$$