Efficiente exploratie van de ontwerpruimte van ingebedde microprocessors

Efficient Design Space Exploration of Embedded Microprocessors

Maximilien Breughe

Promotoren: prof. dr. ir. L. Eeckhout, dr. ir. S. Eyerman Proefschrift ingediend tot het behalen van de graad van Doctor in de Ingenieurswetenschappen: Computerwetenschappen

Vakgroep Elektronica en Informatiesystemen Voorzitter: prof. dr. ir. R. Van de Walle Faculteit Ingenieurswetenschappen en Architectuur Academiejaar 2014 - 2015

ISBN 978-90-8578-747-1 NUR 980, 950

Wettelijk depot: D/2014/10.500/93

#### Dankwoord

Dat ik na vijf jaar ijverig experimenteel onderzoek in mijn doctoraal examen aan de universiteit Gent geslaagd ben, stemt mij fier en gelukkig. Maar evenzeer realiseer ik mij dat dit succes de resultante is van een reeks ontmoetingen met wetenschappers van topniveau. En die mensen wil ik hier oprecht bedanken voor wat zij voor mij betekend hebben.

Vooreerst mijn twee promotoren: prof. Lieven Eeckhout en dr. Stijn Eyerman. Aan Lieven heb ik te danken dat ik een doctorale graad bekomen heb. Hij heeft mijn carrière vorm gegeven. Hij is mij onder de studenten lichting 2009 komen opzoeken met de vraag om in zijn dienst experimenteel werk te verrichten op het gebied van computerarchitectuur. Hij heeft mij gevormd in zijn lab en mij geholpen bij het uitwerken van mijn projecten. Hij heeft mij geleerd hoe publicaties op te stellen en me aangezet tussendoor op internationale topconferenties en in internationale tijdschriften vier artikelen te publiceren. Hij was het die mij in de juiste richting duwde en mij in het buitenland stage liet lopen. Ik ben trots een leerling geweest te zijn van deze professor met internationale faam.

Aan Stijn, mijn tweede promotor, eveneens mijn dank. Die heeft mij zeer intens begeleid bij mijn experimenten. Met zijn ongeëvenaarde expertise en scherp inzicht heeft mij telkens weer de juiste richting doen inslaan. Ook hij was enthousiast over de mogelijkheden die mij in Amerika ter beschikking werden gesteld. Samen met Lieven heeft hij ervoor gezorgd dat mijn onderzoek in Gent en Austin vloeiend verliepen en voor deze harmonieuze samenwerking wil ik ze allebei nog eens extra bedanken.

De tweede groep wetenschappers die mij geleid hebben zijn mijn Amerikaanse medewerkers. I hereby would like to thank Nasr Ullah, Wichaya Top Changwatchai, Brian Grayson and Tim Snyder for making this internship happen. These four persons were key in introducing me into Samsung Austin R&D Center and I don't have enough words to express my thanks. The internship has been invaluable for my PhD. A special word of thanks goes to David Eklöv, for sharing his experience as a PhD student and for his willingness to listen to my research topic. Another special word of thanks goes to Shen, for her patience, support, wise advice and motivating words, especially during the months I wrote the dissertation. I would also like to thank Kshitij and Zheng Li for their wise practical advice.

Tot nu toe heb ik de wetenschappers bedankt die mij in de opbouw van mijn werk geholpen hebben. Ik wil echter evenzeer mijn dank richten tot diegenen die de zware opdracht aanvaard hebben in de examencommissie te zetelen. Deze bestond, naast Lieven en Stijn, uit zes leden, zijnde vier binnenlandse leden, nl. prof. Koen De Bosschere, prof. Filip De Turck, dr. Philippe Manet en prof. Luc Taerwe, en twee buitenlandse professoren, nl. Prof. Roy Jenevein en Prof. Erik Hagersten. Ik bedank ze allen één voor één voor het extra werk dat zij op zich genomen hebben met mijn scriptie door te lezen, wat suggesties naar bijschaving naar voren te brengen en uiteindelijk een oordeel te vellen. En voor de twee buitenlandse professoren komt daar nog de zware trip naar Gent bij. Many thanks go to Prof. Erik Hagersten and Prof. Roy Jenevein for their effort to evaluate this thesis, their suggestions and their willingness to travel to Ghent, despite their busy schedules.

Verder wil ik enkele zaken uit de persoonlijke sfeer niet onvermeld laten. Vooreerst, de sfeer van het thuisfront zal ik nooit vergeten. Kristof en Klaas, mijn beide "bureaugenoten" tijdens mijn doctoraatsjaren, hebben mij, naast wetenschappelijk advies, veel morele steun geboden en voor de nodige afleiding gezorgd. Ook de overige bureaugenoten, nl. Cecilia, Sam, Sander en Shoaib hebben meegeholpen aan het creëren van een aangename stimulerende werksfeer. Daarnaast wil ik niet vergeten, omwille van hun professionele ondersteuning, Marnix, Michiel, Ronny en Pieterjan evenals het personeel van het Vlaams Supercomputer Center (VSC). Vervolgens – zo hoort het – een woordje van dank aan mijn familie. Daarbij denk ik in het bijzonder aan: mama, papa en bonpa die mij de kans gegeven hebben om te geraken waar ik nu sta; en mijn zus Laétitia die er altijd de vrolijke noot wist in te houden. Wie ik echter tot slot nog in herinnering wil brengen is mijn studiegenoot en vriend Geert, die op het moment van schrijven voor een bekende Belgische firma ergens in Australië aan het baggeren is.

Maximilien Breughe Gent, 25 november 2014

### **Examencommissie**

Prof. Luc Taerwe, voorzitter

Prodecaan Faculteit Ingenieurswetenschappen en Architectuur

Universiteit Gent

Prof. Koen De Bosschere, secretaris

Vakgroep ELIS

Faculteit Ingenieurswetenschappen en Architectuur

Universiteit Gent

Prof. Lieven Eeckhout, promotor

Vakgroep ELIS

Faculteit Ingenieurswetenschappen en Architectuur

Universiteit Gent

Dr. Stijn Eyerman, promotor

Vakgroep ELIS

Faculteit Ingenieurswetenschappen en Architectuur

Universiteit Gent

Prof. Filip De Turck

Vakgroep Informatietechnologie

Faculteit Ingenieurswetenschappen en Architectuur

Universiteit Gent

Prof. Erik Hagersten

Uppsala University

Sweden

Prof. Roy Jenevein

The University of Texas at Austin

**USA**

Dr. Philippe Manet

**Embedded Computing Specialists**

Brussel

## Leescommissie

Prof. Filip De Turck

Vakgroep Informatietechnologie

Faculteit Ingenieurswetenschappen en Architectuur

Universiteit Gent

Prof. Lieven Eeckhout

Vakgroep ELIS

Faculteit Ingenieurswetenschappen en Architectuur

Universiteit Gent

Prof. Erik Hagersten

Uppsala University

Sweden

Prof. Roy Jenevein

The University of Texas at Austin

**USA**

Dr. Philippe Manet

**Embedded Computing Specialists**

Brussel

# Samenvatting

Ondanks hun sterke vertegenwoordiging in het alledaagse leven is het ontwerpen van microprocessors bijzonder complex. Het vereist het werk van honderden mensen gedurende enkele jaren. Dit komt door de strenge eisen die worden opgelegd aan het ontwerp: processors moeten snel zijn om de steeds complexere software te kunnen uitvoeren, maar ook vermogenefficiënt om een lange batterijduur te garanderen. Om deze criteria te kunnen bereiken kunnen we gebruik maken van de revolutionaire vooruitgang op gebied van technologie. Dit laat ons toe om miljarden transistors te plaatsen op een kleine oppervlakte. Deze transistors bouwen de verschillende componenten van de microprocessor op. De vele componenten waaruit de microprocessor bestaat hebben verschillende parameters die moeten worden gekozen om ontwerpcriteria zoals uitvoeringstijd en vermogen-efficiëntie te bereiken. Het vinden van de juiste parameters voor iedere component om deze ontwerpcriteria te bereiken is het onderwerp van ontwerpruimte-exploratie (Eng.: design space exploration).

Traditionele cyclus-getrouwe simulators zijn niet geschikt om grote ontwerpruimtes volledig te exploreren door de lage simulatiesnelheid. Trage simulaties leiden namelijk tot twee grote problemen. Ten eerste worden computerarchitecten verplicht om slechts enkele gebieden in de grote ontwerpruimte te simuleren. Hierdoor bestaat de kans dat interessante alternatieve ontwerpen nooit gesimuleerd worden. Ten tweede limiteert de lage simulatiesnelheid de werklasten die gebruikt worden tijdens de exploratie van de ontwerpruimte. Dit kan ertoe leiden dat het gekozen ontwerp suboptimaal zal presteren voor werklasten die niet tijdens het ontwikkelingsprocess gebruikt werden.

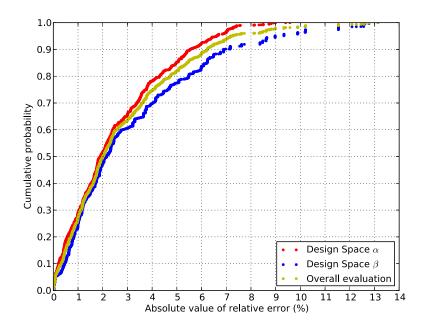

Om computerarchitecten te helpen bij de selectie van de gebieden die ze wensen te simuleren, introduceren we een snel analytisch prestatiemodel dat voorafgaand aan de cyclus-getrouwe simulaties gebruikt kan worden. De constructie van het model is gebaseerd op de interne werking van de microprocessors. We valideren de nauwkeurigheid zowel ten opzichte van cyclus-getrouwe simulatie als ten opzichte van echte hardware. Door het model te vergelijken ten opzichte van meer dan 6,000 cyclus-getrouwe simulaties (een combinatie van programma-applicaties en microarchitecturale configuraties), tonen we aan dat het model het aantal cycli per in-

viii SAMENVATTING

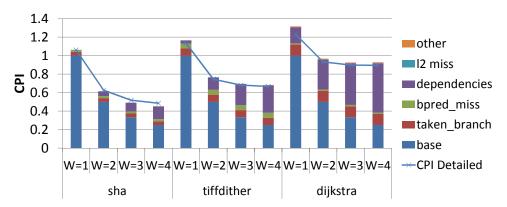

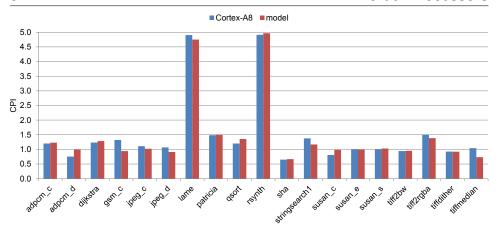

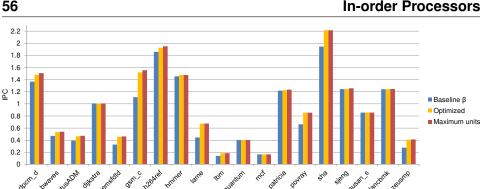

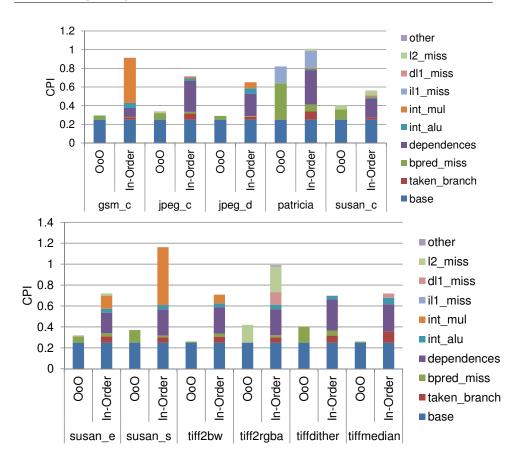

structie (CPI) kan voorspellen met een gemiddelde absolute voorspellingsfout van slechts 2.8% en een standaardafwijking van 0.024. Wanneer we het model inzetten om de prestatie te voorspellen van 19 applicaties voor ingebedde systemen op de ARM Cortex-A8 op een hardware-platform, tonen we aan dat het een gemiddelde absolute nauwkeurigheidsfout in CPI heeft van slechts 10%, met een standaardafwijking van 0.10. Het eigenlijke model bestaat uit een som van verschillende termen die de uitvoeringstijd op een verschillende manier beïnvloeden, zoals bijvoorbeeld foutief voorspelde sprongen, cache missers, afhankelijkheden tussen instructies, maar ook het onbeschikbaar zijn van functionele eenheden. De invoer voor het model bestaat uit de configuratie van de hardware waarvoor een prestatieschatting gewenst is, een aantal programmakarakteristieken die onafhankelijk zijn van de microarchitectuur, en programmakarakteristieken die gedeeltelijk afhankelijk zijn van de microarchitectuur. Het voordeel om de totale prestatie onder te verdelen in aparte termen is dat op die manier de interactie van een programma met de microarchitectuur gevisualiseerd kan worden. We gebruiken het model voor het oplossen van een aantal ontwerpproblemen. We tonen aan dat we het model kunnen inzetten om het aantal functionele eenheden te minimaliseren voor een gegeven prestatiedoel. Verder zetten we het model in om de microarchitectuur te optimaliseren voor zowel prestatie als energie. Naast deze ontwerpproblemen geven we ook een aantal interessante inzichten mee door de interactie tussen programma's en de microarchitectuur te visualiseren aan de hand van het model. We tonen aan dat programma's met een gelijke instructie-mix sterk verschillend kunnen reageren op het schalen van microarchitecturale componenten. Wanneer we de interactie tussen een programma en de microarchitectuur visualiseren voor uitvoerbare bestanden gegenereerd met verschillende compiler-instellingen, kunnen we aantonen hoe deze instellingen de prestatie beïnvloeden.

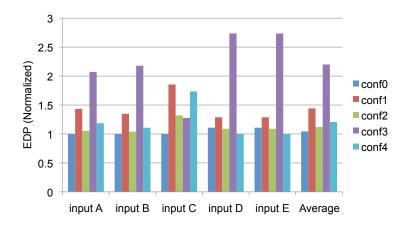

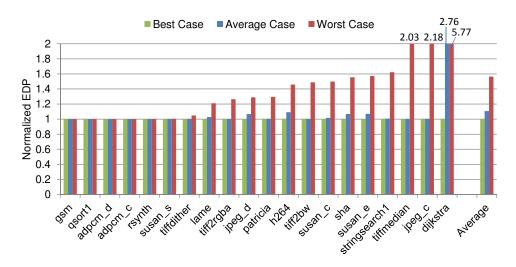

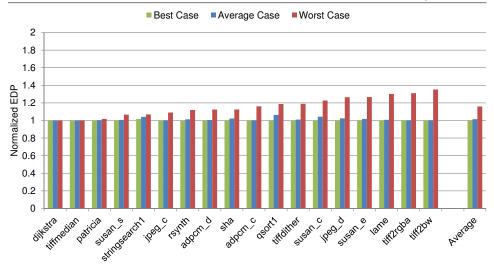

Het kiezen van de juiste werklasten die tijdens het ontwerp van microprocessors gebruikt worden is van groot belang om robuste beslissingen te maken en te vermijden dat het ontwerp slecht presteert op nieuwe werklasten. Tot op vandaag hebben voorafgaande studies vooral gefocust op het vinden van representatieve programma's en representatieve regio's binnen deze programma's. Er zijn echter twee impliciete parameters die gekoppeld gaan met de gekozen werklast die slechts weinig bestudeerd zijn: de programma-invoer en de compileroptimalisatievlaggen die gebruikt werden om een uitvoerbaar bestand te genereren. Met een grootschalig onderzoek tonen we aan dat slecht gekozen programma-invoerbestanden kunnen leiden tot een ontwerp met een energie-efficiëntie dat 57% lager ligt dan het ontwerp met de hoogste energie-efficiëntie. Een slecht gekozen uitvoerbaar bestand kan resulteren in een energie-efficiëntie dat 16% lager ligt dan het ontwerp met de hoogste energie-efficiëntie.

Gezien de potentieel sterk negatieve impact van slecht gekozen pro-

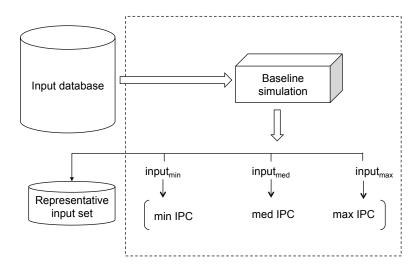

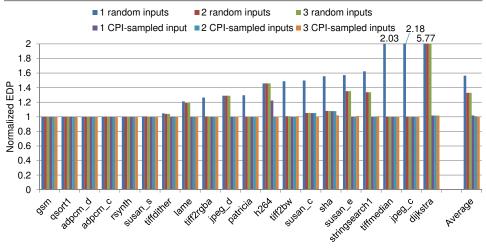

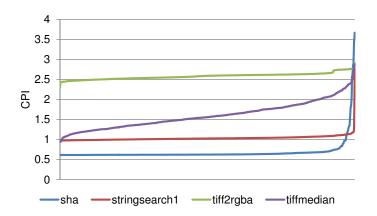

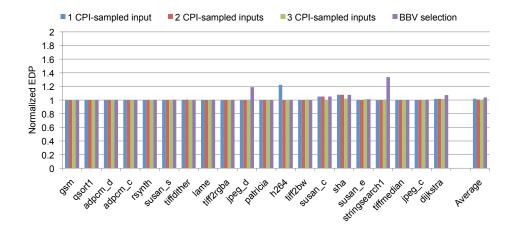

gramma-invoerbestanden introduceren we drie verschillende karakterisatietechnieken om de kans op een nadelige energie-efficiëntie in te perken. Deze technieken hebben als grote voordeel dat, eens de invoerbestanden gekarakteriseerd zijn, de simulatietijd niet stijgt ten opzichte van willekeurig geselecteerde invoerbestanden: onze experimenten tonen aan dat ten hoogste drie representatieve invoerbestanden voldoende zijn om een ontwerp te vinden dat nagenoeg de hoogste energie-efficiëntie heeft. De eerste techniek maakt gebruik van kleine regio's in de ontwerpruimte om de invoerbestanden te filteren, wat tot een energie-efficiëntie leidt die slechts 7% onder het maximum ligt wanneer drie invoerbestanden gebruikt worden. Deze techniek vereist een aantal simulaties, evenredig aan de grootte van de regio's en het beschikbaar aantal invoerbestanden, voorafgaand aan de eigenlijke ontwerpruimte-exploratie om de invoerbestanden te karakteriseren. De tweede techniek karakteriseert de invoerbestanden onafhankelijk van de onderliggende microarchitectuur, op basis van basic-block-vectoren (BBV's). Deze techniek heeft de kortste karakterisatietijd en leidt tot een energie-efficiëntie die slechts 4% onder het maximum ligt wanneer twee invoerbestanden gebruikt worden. De derde en laatste techniek maakt het mogelijk om met drie invoerbestanden het ontwerp te vinden met de hoogste energie-efficiëntie. Hiervoor maakt de techniek gebruik van simulatiestatistieken zoals het gemiddeld aantal cycli per instructie (CPI). De karakterisatietijd komt overeen met een enkele simulatie voor ieder invoerbestand.

Als besluit geloven we dat deze twee bijdragen, het analytisch prestatiemodel en de karakterisatietechnieken voor programma-invoer, een belangrijk deel moeten vormen van de ontwerpcyclus voor microprocessors. Het prestatiemodel laat ons toe om prestatieschattingen te maken in enkele seconden, in plaats van uren cyclus-getrouwe simulatietijd. Deze snelle prestatieschattingen zijn van groot belang om interessante regio's te ontdekken in de grote ontwerpruimte. Met de karakterisatietechnieken voor programma-invoer kunnen we representatieve programma-invoerbestanden selecteren tijdens het ontwerp van de microprocessor. Dit zorgt ervoor dat het uiteindelijke ontwerp voldoende robuust is voor het uiteenlopende dynamisch gedrag van computerprogramma's.

x SAMENVATTING

# **Summary**

Despite their ubiquitous presence in everyday life, designing a microprocessor is a complicated process, involving the work of hundreds of people for several years. Not only should new microprocessors keep up with the performance demands of new software applications, they also need to be power efficient. To achieve these design goals we can rely on spectacular advances in technology that provide the ability of placing billions of transistors on a very small area. These transistors are hierarchically organized into a number of components that all require the appropriate scaling and tuning to meet the design goals. The large number of these components together with the many parameters they bring along build up a large design space for the computer architect to explore.

Traditional cycle-level simulators are not suitable to explore these large design spaces because of their low simulation speed. The low simulation speed introduces two important problems. First, slow simulation forces computer architects to carefully select small regions in the design space they wish to simulate, potentially leaving out interesting design alternatives. Second, the low simulation speed further limits the amount and sizes of workloads that are used during design space exploration, possibly resulting in designs that are suboptimal for workloads that were not simulated during the development.

To guide architects in selecting interesting regions in the typically large design spaces, we propose a fast analytical performance model that can be used in the early stages of the design. We construct the model based of the internal mechanics of the microarchitecture, and compare it against both detailed cycle-level simulation and hardware. For over 6,000 cycle-level simulations (a combination of workloads and microarchitectural configurations), we show that the model's predicted number of cycles per instructions (CPI) has an absolute error of 2.8% on average, with a standard deviation of 0.024. For a set of 19 embedded benchmarks, executed on a hardware platform with the ARM Cortex-A8 processor, we report an absolute average prediction error in CPI of 10% on average, with a standard deviation of 0.10. The final model consists of the sum of a number of penalty terms that reflect the impact of miss events (i.e., branch mispredictions, cache misses, etc.), inter-instruction dependences and functional

xii SUMMARY

unit contention. The inputs to provide to the model are a number of machine parameters for which a performance estimate is desired, a number of program characteristics independent on the microarchitecture, and a number of mixed program-machine characteristics. The advantage of having separate terms that reflect a penalty is that they can be used to visualize the interaction of an application with the microarchitecture. We use the model for a number of design space exploration studies: we are able to find the minimum number of functional units to achieve a predefined performance target using the model, as well as to find the microarchitecture with an energy-delay-product within 1% of the microarchitecure with the lowest energy-delay-product as found by detailed cycle-level simulation. We further reveal a number of interesting insights by using the model to visualize the application-microarchitecture interaction. We show that applications with a similar instruction mix can react very differently on microarchitectural enhancements. By visualizing the application-microarchitecture interaction on a number of different optimized binaries for the same application, we show how compiler optimization flags can impact the performance of an application.

Selecting representative workloads to use throughout design space exploration is of extreme importance in order to assure that design decisions are robust across previously unseen workloads. Before, workload selection has mainly focused on finding representative applications and finding representative samples within these applications. There are however two implicit parameters tied to the workload that have been given only little attention until now: the application's input data sets and the compiler optimization flags used to generate the application binary. We show that poorly chosen application inputs could guide design space exploration to a design with an energy-delay-product (EDP) 57% higher than the design with the lowest EDP. A poorly chosen application binary could result in an EDP increase of 16% over the design with the lowest EDP.

Given the potentially high impact of poorly chosen application inputs we introduce three input selection techniques to reduce the EDP deficiency, without drastically increasing the simulation time: in our experimental setup, we find one to three inputs to be sufficient to find a nearly optimal design. Filtering the inputs by performing design space exploration on a very small region of the original design space reduces the worst case scenario to an EDP deficiency of 7% by using three inputs. This technique requires a number of simulations, proportional to the number of inputs available and the size of the selected region, prior to design space exploration to profile the inputs. With basic block vector (BBV) selection we characterize inputs in a microarchitecture-independent way. This technique has the lowest input characterization overhead and is able to reduce the worst case scenario to an EDP deficiency of 4% with as few as two inputs. The third technique is able to completely eliminate the EDP deficiency in our

setup by using three inputs during design space exploration. It therefore characterizes inputs by using simulation statistics, such as CPI (cycles per instruction), from a single cycle-level simulation per input.

We believe that the two main contributions of this dissertation, namely the analytical performance model and benchmark input selection techniques, are key additions into the microarchitectural design cycle. With the proposed mechanistic model, we are able to estimate microprocessor performance in seconds, compared to hours of cycle-level simulation, which helps guiding us into interesting regions of the typically large design space. The proposed input selection techniques allow us to use representative benchmark inputs during design space exploration, leading to design decisions that are optimal across inputs.

xiv SUMMARY

# **Contents**

|   | Ned  | lerlandse samenvatting                                       | vii |

|---|------|--------------------------------------------------------------|-----|

|   | Eng  | lish Summary                                                 | xi  |

| 1 | Intr | oduction                                                     | 1   |

|   | 1.1  | Motivation and focus                                         | 2   |

|   | 1.2  | The Contributions of this Thesis                             | 4   |

|   |      | bottleneck visualization                                     | 4   |

|   |      | 7.7                                                          | 5   |

|   | 1.3  | tative benchmark inputs                                      | 7   |

|   |      |                                                              |     |

| 2 | Bac  | kground                                                      | 9   |

|   | 2.1  | Superscalar Processors                                       | 9   |

|   |      | 2.1.1 Superscalar in-order processors                        | 10  |

|   |      | 2.1.2 Superscalar out-of-order processors                    | 13  |

|   | 2.2  | Analytical Performance Modeling                              | 15  |

|   |      | 2.2.1 Mechanistic Modeling                                   | 16  |

|   |      | 2.2.2 Empirical Modeling                                     | 18  |

|   |      | 2.2.3 Hybrid mechanistic-empirical modeling                  | 18  |

|   | 2.3  | Workload selection techniques                                | 18  |

|   |      | 2.3.1 Benchmark Selection                                    | 19  |

|   |      | 2.3.2 Sample Selection                                       | 20  |

|   |      | 2.3.3 Input Selection                                        | 20  |

|   |      | 2.3.4 Summary                                                | 21  |

| 3 | Med  | chanistic Analytical Performance Modeling of Superscalar In- |     |

|   |      | er Processors                                                | 23  |

|   | 3.1  | Modeling context                                             | 24  |

|   |      | 3.1.1 General overview                                       | 24  |

|   |      | 3.1.2 Microarchitecture description                          | 25  |

|   | 3.2  | Overall formula                                              | 26  |

|   | 3.3  | Miss events                                                  | 27  |

xvi CONTENTS

|   |      | 3.3.1   | J                                                      | 27  |

|---|------|---------|--------------------------------------------------------|-----|

|   |      | 3.3.2   | J 1                                                    | 28  |

|   | 3.4  |         | instruction dependences and functional unit contention |     |

|   |      | 3.4.1   | Inter-Instruction Dependences                          | 31  |

|   |      | 3.4.2   | Functional Unit Contention                             | 36  |

|   | 3.5  |         | imental setup                                          | 44  |

|   | 3.6  |         | l Validation                                           | 50  |

|   |      | 3.6.1   | Validation Against Detailed Simulation                 | 50  |

|   |      | 3.6.2   | 0                                                      | 54  |

|   | 3.7  |         | ng design space exploration                            | 55  |

|   |      | 3.7.1   | Minimizing Number of Functional Units for a Given      |     |

|   |      |         | Performance Target                                     | 55  |

|   |      | 3.7.2   | Minimizing the Energy Delay Product                    | 56  |

|   | 3.8  | Gaini   | ng insights                                            | 60  |

|   |      | 3.8.1   | Revealing Performance Bottlenecks                      | 60  |

|   |      | 3.8.2   | Compiler Optimizations                                 | 62  |

|   |      | 3.8.3   | In-order versus out-of-order performance               | 65  |

|   | 3.9  | Sumn    | nary                                                   | 66  |

| 4 | Sele | cting I | Representative Benchmark Inputs for Design Space Ex    | (-  |

|   | ploi | ation   |                                                        | 69  |

|   | 4.1  | Poten   | tial pitfall of current practice                       | 70  |

|   | 4.2  | Exper   | imental Setup                                          | 72  |

|   |      | 4.2.1   | Design Space                                           | 72  |

|   |      | 4.2.2   | Workloads                                              | 73  |

|   |      | 4.2.3   | Modeling Infrastructure                                | 75  |

|   |      | 4.2.4   | Optimization Criterion                                 | 76  |

|   | 4.3  | Quan    | tifying the impact of implicit parameters on micropro- |     |

|   |      | cessor  | design space exploration                               | 77  |

|   |      | 4.3.1   | Sensitivity to Benchmark Inputs                        | 78  |

|   |      | 4.3.2   | Sensitivity to Compiler Optimization Flags             | 80  |

|   |      | 4.3.3   | The impact of the microarchitecture on compiler op-    |     |

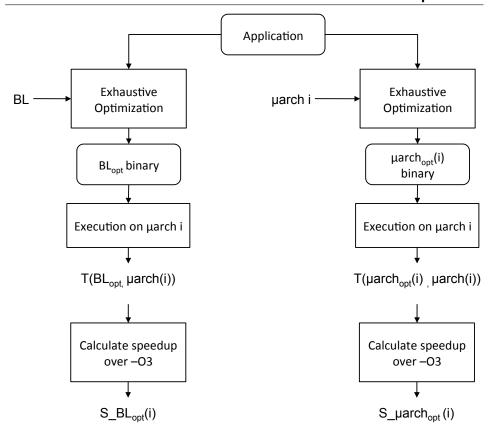

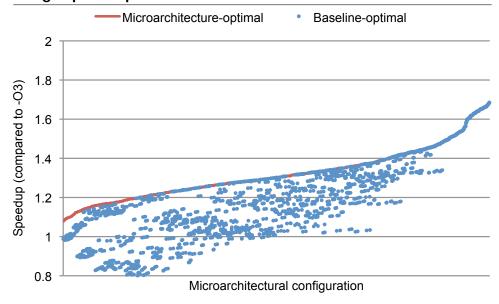

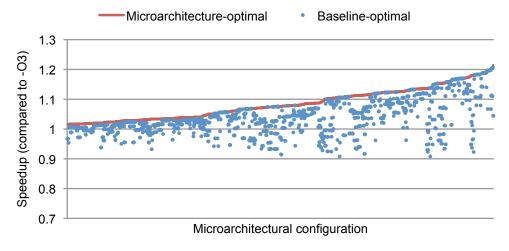

|   |      |         | timization flags                                       | 81  |

|   | 4.4  | Repre   | sentative Benchmark Input Selection                    | 84  |

|   |      | 4.4.1   | Random Selection                                       | 85  |

|   |      | 4.4.2   | Microarchitecture-Independent Selection                | 87  |

|   |      | 4.4.3   | Filtered Selection                                     | 92  |

|   |      | 4.4.4   | CPI-Sampled Selection                                  | 96  |

|   |      | 4.4.5   | Overview and Discussion                                | 98  |

|   | 4.5  |         | nary                                                   | 101 |

| 5 | Con  | clusion | n                                                      | 103 |

| - | 5.1  |         | nary                                                   | 104 |

|   |      |         | Analytical performance modeling                        | 104 |

| СО | NTE  | NTENTS XV |                                                      |     |

|----|------|-----------|------------------------------------------------------|-----|

|    |      | 5.1.2     | Selecting representative benchmark inputs            | 105 |

|    | 5.2  | Future    | ework                                                | 106 |

|    |      | 5.2.1     | Mechanistic performance modeling of superscalar in-  |     |

|    |      |           | order processors                                     | 106 |

|    |      | 5.2.2     | Quantification of compiler optimization flags on de- |     |

|    |      |           | sign space exploration                               | 107 |

|    |      | 5.2.3     | Selecting representative benchmark inputs            | 107 |

| A  | Inst | ruction   | Profiler                                             | 109 |

| В  | Rep  | resenta   | tive Benchmark inputs                                | 115 |

|    |      |           |                                                      |     |

xviii CONTENTS

# **List of Tables**

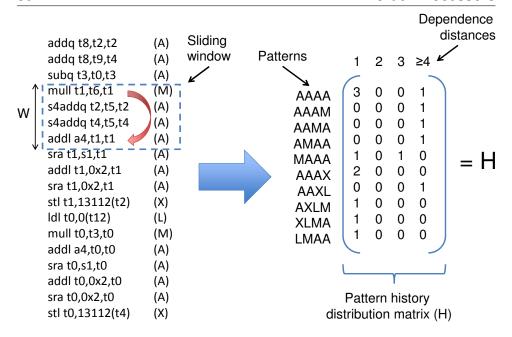

| 3.1  | H-matrix for the instruction stream in Figure 3.6               | 40  |

|------|-----------------------------------------------------------------|-----|

| 3.2  | Penalties for the patterns of the H-matrix in Table 3.1 in the  |     |

|      | case of two non-pipelined multiply units                        | 41  |

| 3.3  | Penalties for the patterns of the H-matrix in Table 3.1 in the  |     |

|      | case of two pipelined multiply units                            | 43  |

| 3.4  | Overview of MiBench benchmarks                                  | 45  |

| 3.5  | Overview of SPEC CPU 2006 benchmarks                            | 46  |

| 3.6  | Design Space $\alpha$                                           | 48  |

| 3.7  | Design Space $\beta$                                            | 49  |

| 3.8  | Cortex-A8 microarchitectural parameters                         | 50  |

| 3.9  | Benchmark-optimal configurations achieving at least 98% of      |     |

|      | maximum performance with a minimum number of units              | 57  |

| 3.10 | Configuration used to compare in-order with out-of-order        |     |

|      | CPI stacks                                                      | 64  |

| 4.1  | Design space for detailed simulation                            | 71  |

| 4.2  | Design space considered in this study                           | 72  |

| 4.3  | Overview of benchmarks                                          | 74  |

| 4.4  | Resulting microarchitectural optimizations for jpeg_d, depend-  |     |

|      | ing on the used input during design space exploration           | 87  |

| 4.5  | Summary of input selection methods. ( <i>N</i> is the number of |     |

|      | inputs in the database, $M$ the number of microarchitectures,   |     |

|      | s the simulation time overhead and the $p$ instrumentation      |     |

|      | overhead.)                                                      | 99  |

| B.1  | Representative inputs for MiBench, characterized with the       |     |

|      | <u>.</u>                                                        | 116 |

| B.2  | Representative inputs for MiBench, characterized with the       |     |

|      | ± ±                                                             | 117 |

# **List of Figures**

| 1.1  | Schematic view of the main steps involved in microprocessor design                                                                                                  | 2  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | The contributions of this thesis (mechanistic model and input selection) and how they affect processor design                                                       | 3  |

| 2.1  | Block diagram of a superscalar in-order pipeline                                                                                                                    | 10 |

| 2.2  | Block diagram of a superscalar out-of-order pipeline                                                                                                                | 13 |

| 2.3  | Interval analysis analyzes processor performance on an interval basis determined by disruptive miss events: (a) out-of-order processors and (b) in-order processors | 17 |

|      | of-order processors and (b) in-order processors                                                                                                                     | 17 |

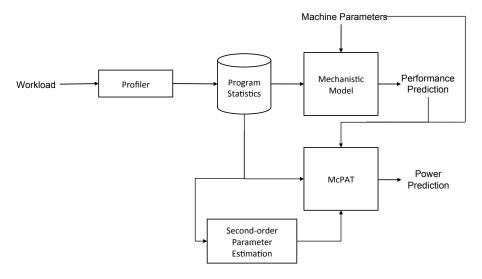

| 3.1  | Overview of the mechanistic modeling framework                                                                                                                      | 24 |

| 3.2  | Schematic view of the assumed superscalar in-order processor. Here, W=4 and D=2                                                                                     | 25 |

| 3.3  | Construction of the pattern distribution matrix for part of the dct_chroma routine of the h264 benchmark                                                            | 30 |

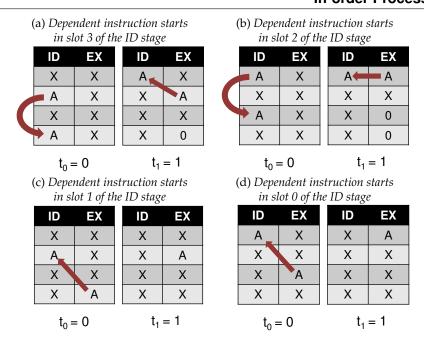

| 3.4  | Four possible instruction flows for an instruction dependent on an ALU instruction at distance $d = 2, \ldots, \ldots$                                              | 32 |

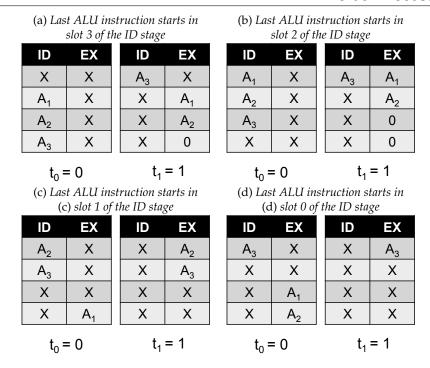

| 3.5  | Four possible instruction flows of the pattern "XAAA"                                                                                                               | 38 |

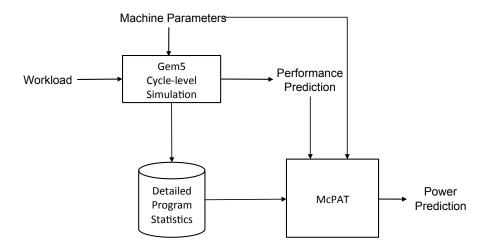

| 3.6  | An example instruction stream with multiply instructions                                                                                                            | 39 |

| 3.7  | Instruction flow of the example instruction stream in Figure                                                                                                        |    |

|      | 3.6 through a superscalar processor with two multiply units.                                                                                                        | 40 |

| 3.8  | Simulation framework when evaluation is driven by cycle-                                                                                                            |    |

| •    | level simulation                                                                                                                                                    | 47 |

| 3.9  | Simulation framework when evaluation is driven by the mechanistic model                                                                                             | 47 |

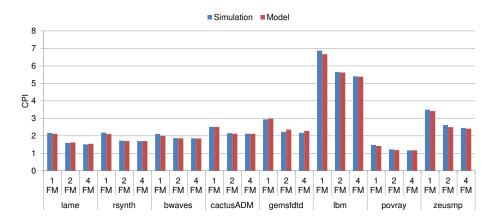

| 3.10 | Model validation while varying the number of floating-point multiply units (FM), for the floating-point benchmarks of MiBench and SPEC CPU2006                      | 51 |

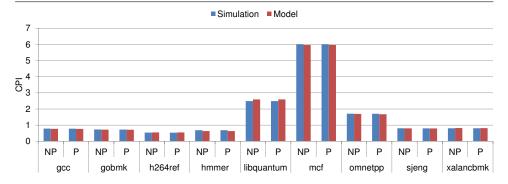

| 3.11 | Evaluation of the model compared to detailed simulation for pipelined (P) and non-pipelined (NP) functional units, on the integer benchmarks of SPEC CPU 2006       | 52 |

|      | die niteger beneimment of bribe er o 2000                                                                                                                           | 02 |

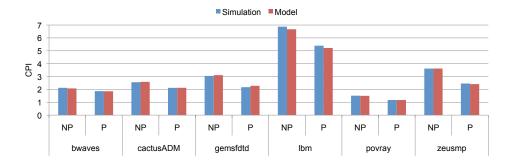

| 3.12 | Evaluation of the model compared to detailed simulation for pipelined (P) and non-pipelined (NP) functional units, on the floating-point benchmarks of SPEC CPU 2006                                                                                             | 52 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.13 | Cumulative probability distribution of error for design spaces $\alpha$ and $\beta$ on all evaluated points                                                                                                                                                      | 53 |

| 3.14 | Model accuracy for estimating relative performance as a function of superscalar width.                                                                                                                                                                           | 53 |

| 3.15 | Evaluation of the model compared to the Cortex-A8 microarchitecture.                                                                                                                                                                                             | 54 |

| 3.16 | Baseline performance, performance of the configuration with 4 units of each type (Maximum units) and the performance of the configuration picked by the model with a minimum number of functional units within 98% of the optimum (Optimized)                    | 56 |

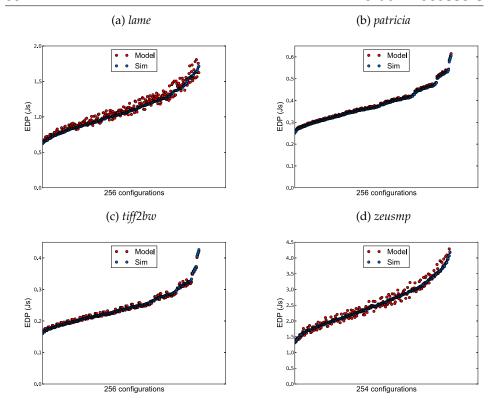

| 3.17 | Using the model versus detailed simulation when optimizing for EDP, for four benchmarks and 256 configurations                                                                                                                                                   | 58 |

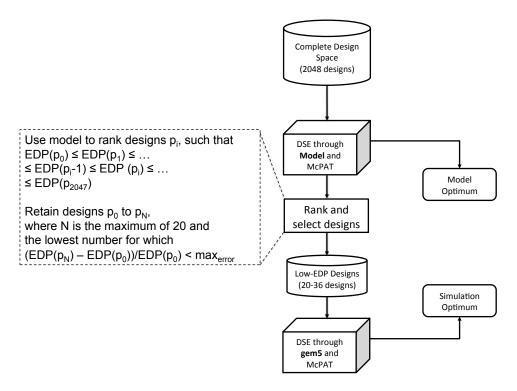

| 3.18 | Framework to filter the designs used in the second experiment of Section 3.7.2, to limit the number of designs to evaluate with detailed cycle-level simulation                                                                                                  | 59 |

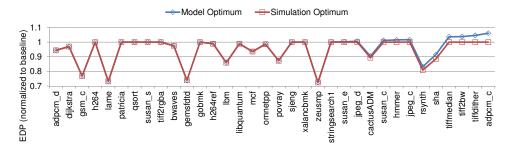

| 3.19 | EDP (normalized by the EDP of Baseline $\beta$ ) for the lowest EDP configuration discovered by simulation and by the model.                                                                                                                                     | 59 |

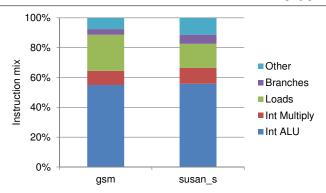

| 3.20 | The instruction mix of benchmarks gsm_c and susan_s are similar: Many integer ALU instructions and over 10% integer multiply instructions                                                                                                                        | 60 |

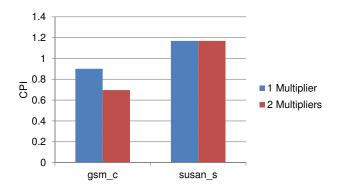

| 3.21 | Adding an additional multiply unit increases performance significantly for one benchmark, but not for the other, while the instruction mixes of Figure 3.20 are similar                                                                                          | 61 |

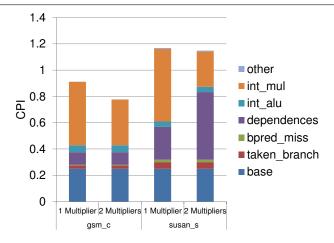

| 3.22 | CPI stacks reveal that inter-instruction dependences between multiply instructions are the underlying bottleneck that is preventing performance improvement for susan_s. The 'other' component are all other terms in the model that only have a small component | 62 |

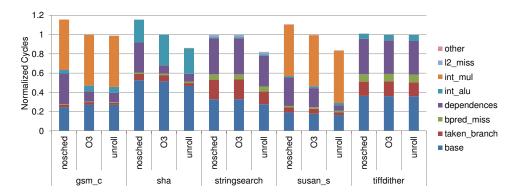

| 3.23 | Normalized cycle stacks for five benchmarks across different compiler optimizations.                                                                                                                                                                             | 63 |

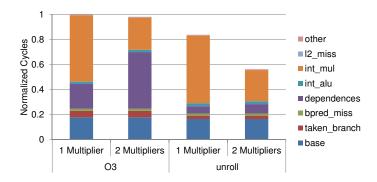

| 3.24 | Normalized cycle stacks for susan_s with and without loop unrolling, and on two different architectures (one and two multiply units).                                                                                                                            | 63 |

| 3.25 | Comparing in-order versus out-of-order performance using CPI stacks obtained through mechanistic modeling                                                                                                                                                        | 65 |

| 4.1  | Normalized EDP for sha for five different processor configurations and five different inputs                                                                                                                                                                     | 71 |

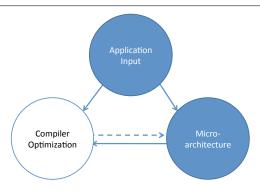

| 4.2  | Relationships between parameters that are quantified in Sec-                                       |    |

|------|----------------------------------------------------------------------------------------------------|----|

|      | tion 4.3. The strong impact from benchmark inputs on mi-                                           |    |

|      | croarchitectural design decisions is the main focus of this                                        |    |

|      | chapter, and is quantified in Section 4.3.1. In addition, the                                      |    |

|      | other relationships are quantified in the remainder of Section                                     |    |

|      | 4.3                                                                                                | 78 |

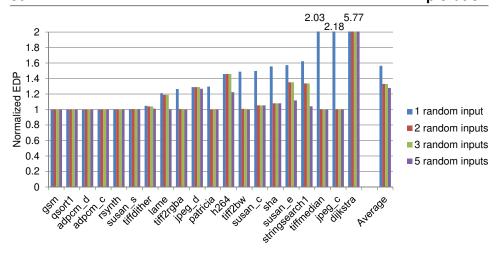

| 4.3  | Quantifying the impact of selected benchmark inputs for iden-                                      |    |

|      | tifying the optimum processor configuration                                                        | 78 |

| 4.4  | Quantifying the impact of compiler optimization flags on the                                       |    |

|      | identification of the optimum processor configuration                                              | 80 |

| 4.5  | Framework to calculate the speedups of the baseline-optimal                                        |    |

|      | (BL <sub>opt</sub> ) binary and the microarchitecture-optimal ( $\mu$ arch <sub>opt</sub> ( $i$ )) |    |

|      | binary for microarchitecture $i$                                                                   | 82 |

| 4.6  | Speedups over -03 for lame when the binary is optimized                                            |    |

|      | for the target architecture (red curve) and when it is opti-                                       |    |

|      | mized by a baseline architecture (blue data points). The ex-                                       |    |

|      | periment is repeated for different microarchitectures on the                                       |    |

|      | X-axis, but the baseline is kept the same                                                          | 83 |

| 4.7  | Speedups over -03 for sha when the binary is optimized for                                         |    |

|      | the target architecture (red curve) and when it is optimized                                       |    |

|      | by a baseline architecture (blue data points). The experiment                                      |    |

|      | is repeated for different microarchitectures on the X-axis, but                                    |    |

|      | the baseline is kept the same                                                                      | 83 |

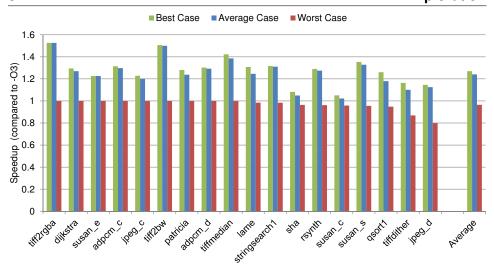

| 4.8  | Harmonic average of speedups over 1728 microarchitectures,                                         |    |

|      | when the baseline to generate the application binary is (1)                                        |    |

|      | the microarchitecture resulting in the best speedup (i.e., the                                     |    |

|      | binary is generated by the microarchitecture we measure speed                                      | up |

|      | on and hence is the best case.), (2) the microarchitecture re-                                     |    |

|      | sulting in an average speedup (average case) and (3) the mi-                                       |    |

|      | croarchitecture resulting in the worst speedup (worst case).                                       | 84 |

| 4.9  | Input selection workflow                                                                           | 85 |

| 4.10 | Random input selection: worst case normalized EDP as a                                             |    |

|      | function of number of randomly selected inputs                                                     | 86 |

|      | Input 807 for jpeg_d                                                                               | 88 |

| 4.12 | Input 261 for jpeg_d                                                                               | 88 |

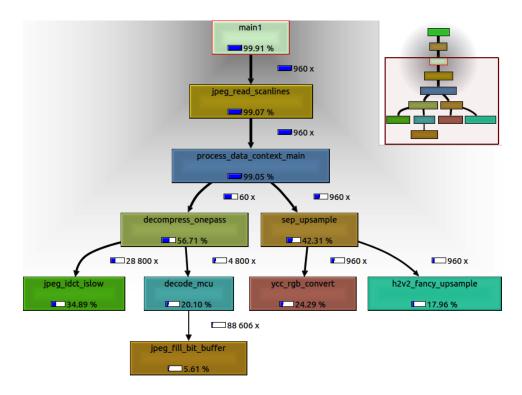

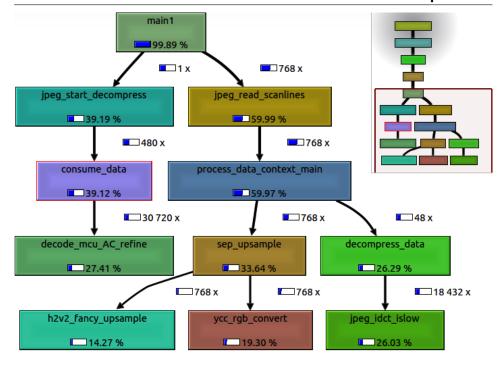

| 4.13 | Call graph of the valgrind analysis for input 807                                                  | 89 |

| 4.14 | Call graph of the valgrind analysis for input 261                                                  | 89 |

| 4.15 | Microarchitecture-independent input selection using Basic                                          |    |

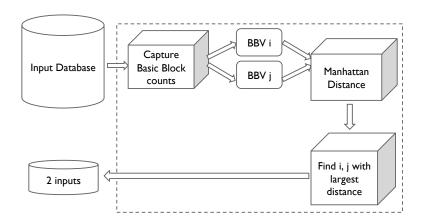

|      | Block Vectors (BBVs)                                                                               | 90 |

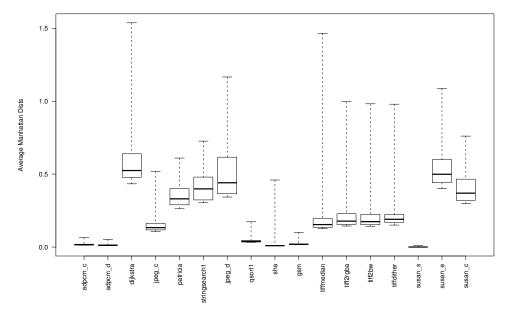

| 4.16 | Boxplot distribution of average Manhattan distances between                                        |    |

|      | each input and all other inputs. The high distances indicate                                       |    |

|      | that there is many different dynamic behavior over different                                       |    |

|      | inputs: e.g., a Manhattan distance of 0.5 indicates that 25%                                       |    |

|      | of the executed code resides in different basic blocks                                             | 91 |

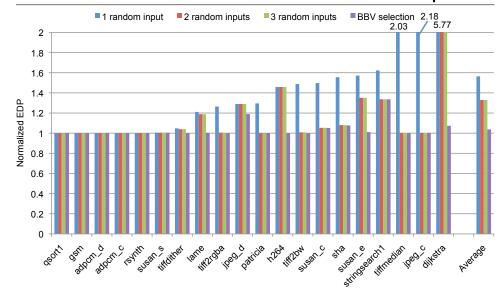

| 4.17 | Normalized EDP for microarchitecture-independent input selection using BBVs versus random selection | 92         |

|------|-----------------------------------------------------------------------------------------------------|------------|

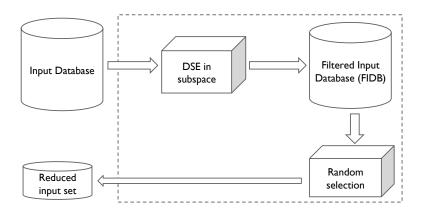

| 4.18 | One-level filtered input selection uses design space explo-                                         | > <b>-</b> |

|      | ration in a limited microarchitectural subspace to filter out                                       |            |

|      | non-representative inputs                                                                           | 93         |

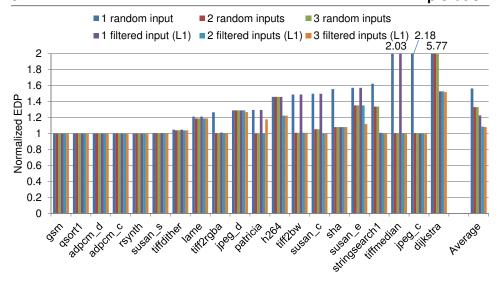

| 4.19 | Normalized EDP through one-level filtered input selection                                           | 94         |

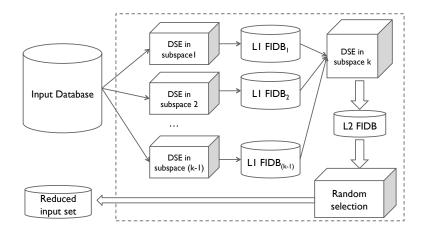

| 4.20 | Two-level filtered input selection uses two levels of design                                        |            |

|      | space exploration in limited subspaces to filter out non-represe                                    | ntative    |

|      | inputs                                                                                              | 95         |

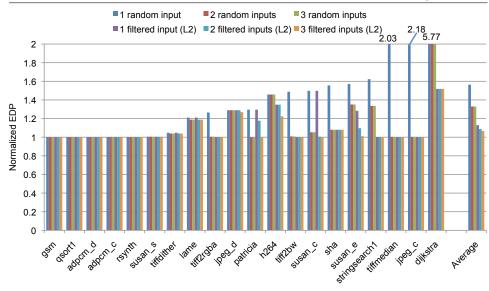

| 4.21 | Normalized EDP through two-level filtered input selection.                                          | 96         |

|      | CPI-sampled selection                                                                               | 96         |

|      | Normalized EDP through CPI-sampled selection                                                        | 98         |

|      | CPI across data sets for a number of benchmarks                                                     | 98         |

| 4.25 | Overview of the best performing two techniques: BBV selec-                                          |            |

|      | tion and CPI-sampling                                                                               | 100        |

### List of Abbreviations

ALU Arithmetic Logic Unit

ASIC Application-Specific Integrated Circuit

BBV Basic Block Vector

CISC Complex Instruction Set Computer

CPI Cycles Per Instruction

DV Design Verification

EDP Energy-Delay Product

EPI Energy Per Instruction

FDTD Finite Difference Time Domain GCC GNU Compiler Collection ILP Instruction-Level parallelism

IPC Instructions Per Cycle

ISA Instruction Set Architecture

L1 I-cache Level one Instrution cache

L1 D-cache Level one Data cache

L2 cache Level two cache LSU Load/Store Unit

MLP Memory-Level Parallelism MSHR Miss Status Handling Register

RAW Read After Write

RTL Register Transfer Level

SHA Secure Hasing Algorithm

TLB Translation Lookaside Buffer

TPI Time Per Instruction

WAR Write After Read

WAW Write After Write

### **Chapter 1**

### Introduction

I think there is a world market for maybe five computers. **Thomas J. Watson, IBM**

Microprocessors take an important role in our everyday life: several billions of microprocessors are distributed in the world in many different devices [1], ranging from smartphones and smart watches to desktop computers, game consoles and server systems in data centers. Despite their ubiquitous presence, building a microprocessor is a very complicated process. Not only does the microprocessor need to keep up with the increasing complexity of software applications, it also needs to be power efficient, both to allow for a long battery lifetime in handheld devices and to keep the energy bill low and cooling costs reasonable in big data centers. To achieve these goals we can rely on spectacular advances in technology that provide the ability of placing billions of transistors on a very small area. The task of organizing these transistors, however, is a very complicated one and involves the work of hundreds of people for several years [12].

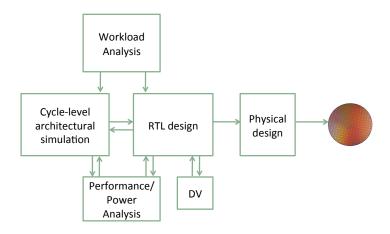

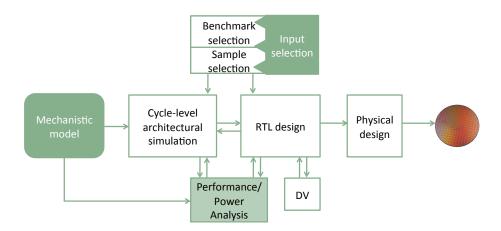

Figure 1.1 shows a high-level view of the main steps during the development of a microprocessor. During every step of the development, performance, power/energy consumption, area, reliability, etc., are the optimization criteria. It is the task of the computer architect to build an RTL design that meets these criteria. Once the RTL design is ready (and functionally verified by the Design Verification teams (DV)), it will go through the physical design steps to create a layout file of the circuit (GDSII-file), which is sent to the fab for wafer manufacturing.

To understand the impact of design decisions, the RTL design can be simulated in software, which gives a very accurate estimate of its performance if it were to be built in silicon. However, there are two main disadvantages. First, only very small workloads can be simulated because of the low simulation speed: typically, simulating an application on RTL is 7 to 8 orders of magnitude slower than executing an application on real

2 Introduction

Figure 1.1: Schematic view of the main steps involved in microprocessor design.

hardware. To make design decisions, however, it is important to be able to estimate the performance of workloads that are sufficiently large. Second, RTL code tends to be inflexible when trying to explore the behavior of new design features. To overcome these disadvantages, cycle-level microarchitectural simulators are built and used by performance and power analysis teams to help RTL designers make design decisions. Cycle-level architectural simulators aim at making performance estimates that are close to those of RTL simulators, but they operate at a higher level of abstraction. Because of this they are 3 to 4 orders of magnitude faster than RTL simulators, and hence more design configurations can be explored and more and larger workloads can be simulated. Unfortunately, these architectural simulators are still up to 4 orders of magnitude slower than execution on real hardware, which forms a hard limit on the number of simulations that can be done. This potentially leads to designs that are suboptimal for workloads that were not simulated during the development and/or limits the number of designs that computer architects can simulate.

#### 1.1 Motivation and focus

Traditional cycle-level simulators are clearly not suitable to explore large design spaces. Because resources are limited, designers are tied to a limited simulation budget and hence are forced to carefully select small regions in the design space they wish to simulate. A second problem is that the low simulation speed further limits the amount and sizes of workloads to be simulated. However, in order to ensure that design decisions are robust, it is important to select the appropriate workloads during design space exploration. Figure 1.2 shows our contributions to the microprocessor development cycle to help solving both these problems.

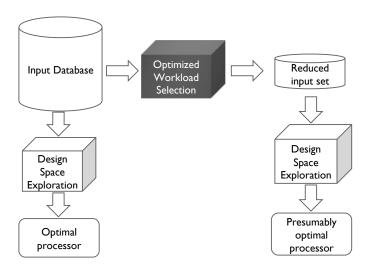

**Figure 1.2:** The contributions of this thesis (mechanistic model and input selection) and how they affect processor design.

We develop an analytical performance model, built from the internal mechanics of a microprocessor, for exploring design spaces in the early design stage, by trading off accuracy for speed. Not only does the model speed up simulation time drastically as it involves evaluating a number of mathematical formulas, it also provides insight into the application-microarchitecture interaction. The main intent of the model is to get quick insight and to prune down the large number of designs to a smaller set that can be simulated with detailed cycle-level simulation.

The challenge in workload selection is to select as few workloads as possible while capturing as much program-behavior as possible. Limiting the number of workloads is important to reduce simulation time, while having a broad coverage reduces the chance that our design has an undesired performance on unseen workloads once the microprocessor is shipped. We contribute to the workload selection process by adding techniques for benchmark input selection to the computer architect's toolbox.

When moving towards application-specific processors, the contributions of this thesis gain even more importance. An application-specific processor is a processor that is tailored for the application or application domain of interest. This specialized processor is optimized to achieve the best possible performance within a given energy envelope, or, vice versa, the processor is optimized to consume the least possible energy while achieving a given performance target <sup>1</sup>. Application-specific processors are more cost-effective than hardware specialization, such as application-specific integrated circuits (ASICs), and in addition benefit from the programmability of a general-purpose processor. In order to find the sweet spot in the typi-

<sup>&</sup>lt;sup>1</sup>Synopsys' DesignWare ARC processors and Cadence Tensilica Xtensa dataplane processors are solutions along this line.

4 Introduction

cally huge design spaces, optimized along multiple design criteria, the design methodology is obviously key. The analytical performance model that we introduce in this thesis can help computer architects guide design space exploration by creating fast performance predictions for large regions in the design space. Further, since these specialized processors are customized for a specific application it is important to capture sufficient dynamic behavior of the application. Therefore, the input selection techniques that we propose allow computer architects to find inputs that are representative for the application.

As stated earlier, a primary design goal for embedded microprocessors is energy-efficiency. While superscalar out-of-order processors deliver high performance, they come at the price of complex logic which makes them power-hungry. Because the performance of a single core is proportional to the square root of its area <sup>2</sup> [5], known as Pollack's rule, and power consumption is roughly proportional to the area, processors that occupy a smaller area are more power-efficient. This is even further motivated by the end of the Dennard scaling [13] where the power density increases when transistor sizes further decrease. We therefore consider superscalar in-order processors throughout the course of this thesis, as they are less complex to design, occupy less area and consume less energy, compared to superscalar out-of-order processors. In-order processors are widely used in today's embedded systems such as in the iPhone 4 and iPad (under the Apple A4 processor), but also in the recently released Galaxy S5 Mini (using the ARM Cortex-A8) and the high-end Samsung Galaxy S5 smartphone (as part of the big.LITTLE core [27]).

#### 1.2 The Contributions of this Thesis

# 1.2.1 Contribution 1: Fast microarchitectual evaluation and bottleneck visualization

The intent of cycle-level microarchitectural simulators is to allow computer architects to make high level decisions of a complicated hardware design. Computer architects build these microarchitectural simulators to be as accurate as possible compared to RTL-simulators or real hardware. Because cycle-level microarchitectural simulators have a higher level of abstraction than RTL-simulators they are 3 to 4 orders of magnitude faster. Therefore computer architects can use them to explore many different potential microarchitectural designs. Unfortunately, applications executed on a simulator are still up to 4 orders of magnitude slower compared to executing

<sup>&</sup>lt;sup>2</sup>The performance of a single core is proportional to the square root of its complexity. Hence, when considering the same feature size, the performance of a single core is proportional to the square root of its area.

these applications on real hardware. Hence, an exhaustive search of all potential microarchitectural designs is impossible, forcing computer architects to carefully select the designs they want to simulate.

To guide architects selecting interesting regions in the typically huge design spaces we extend current practice of design space exploration by constructing a model with a higher level of abstraction. We build a performance model for superscalar in-order processors that eliminates the slow-down from which cycle-level simulation suffers by using analytical formulas.

As a bonus, the model not only reduces simulation time significantly, it also shows how an application interacts with the microarchitecture. This allows computer architects to visualize where an application's cycles are spent. In addition, when applying this visualization technique on multiple binaries of the same application, we are able to visualize how compiler flags impact the interaction between an application and the microarchitecture.

Our results show that the model has an absolute error of only 2.8% on average when compared against cycle-level simulation and 10% when compared against hardware. The evaluation time of the model is less than a second, while the evaluation time of cycle-level simulators typically takes several hours.

A discussion of the model has been peer reviewed by and presented at the 2012 IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS), where it was **nominated for best paper award**:

Maximilien Breughe, Stijn Eyerman, and Lieven Eeckhout, "A mechanistic performance model for superscalar in-order processors", IS-PASS '12: Proceedings of the 2012 IEEE International Symposium on Performance Analysis of Systems and Software.

An extended version of the model is in press for ACM Transactions on Architecture and Code Optimization (TACO):

Maximilien Breughe, Stijn Eyerman, and Lieven Eeckhout, "Mechanistic analytical modeling of superscalar in-order processor performance", TACO '14: ACM Transactions on Architecture and Code Optimization.

# 1.2.2 Contribution 2: Selection methodology for representative benchmark inputs

When performing design space exploration there are two parameters that are implicit to the workloads that are being used: the input to the application and the set of compiler flags that is used to optimize the application's

6 Introduction

binary. Common practice is to use one or a couple of inputs and application binaries, and assume that they capture enough dynamic behavior to be representative for the entire application. These assumptions have never proven to be true and the need to study them is increasing when moving toward application-specific processors.

Therefore, we first conduct an experiment that uses a large database of inputs for a number of applications and show that some inputs could lead to poor results, when used to drive design space exploration. On average, the energy-delay product (EDP) <sup>3</sup> can be 57% or 33% higher than the lowest achievable EDP, when using one, respectively three badly chosen inputs. Second, we set up a similar experiment by using application binaries, compiled with different sets of compiler flags, to drive design space exploration. We show that the choice of compiler flags with which the application binary was generated, has a less significant impact: in the worst case the EDP is 16% higher on average than the lowest achievable EDP.

A discussion on the sensitivity study of benchmark inputs has been peer reviewed by and presented at the 2011 IEEE Symposium on Application Specific Processors (SASP):

Maximilien Breughe, Zheng Li, Yang Chen, Stijn Eyerman, Olivier Temam, Chengyong Wu and Lieven Eeckhout. "How sensitive is processor customization to the workload's input datasets?", SASP '11: Proceedings of the 2011 IEEE 9th Symposium on Application Specific Processors.

Based on these insights we conclude that it is important to perform design space exploration with representative inputs. It is unclear, however, a priori which input is representative for the application. Hence, without a proper selection method we would either run the risk of building a design with diminishing performance by using non-representative inputs, or we would need to perform the exploration with a high number of inputs and increase simulation time drastically. Both options are infeasible in practice. Therefore we build different input selection techniques to reduce the EDP deficiency. With the techniques we propose we are able to reduce the average EDP deficiency to less than 3.7%, without a significant increase in simulation time.

A discussion of these input selection techniques and their trade-offs has been published in ACM Transactions on Architecture and Code Optimization (TACO) and has been presented at the 2014 International Conference on High-Performance and Embedded Architectures and Compilers (HiPEAC):

<sup>&</sup>lt;sup>3</sup>We use EDP as a metric for energy-efficiency.

1.3 Thesis Outline 7

Maximilien Breughe and Lieven Eeckhout. "Selecting representative benchmark inputs for exploring microprocessor design spaces", TACO '13: ACM Transactions on Architecture and Code Optimization, Vol.10, No.37, Dec. 2013.

### 1.3 Thesis Outline

This dissertation is organized as follows. Chapter 2 describes the microarchitecture of modern superscalar in-order and out-of-order processors and describes the current state-of-the-art of analytical performance modeling and workload selection. Chapter 3 describes our analytical performance model for superscalar in-order processors and illustrates its usefulness with a number of case studies. In Chapter 4 we quantify the impact of implicit workload parameters on design space exploration and introduce our novel techniques to select representative benchmark inputs. Finally we present our conclusions in Chapter 5 and provide suggestions for future work.

8 Introduction

## **Chapter 2**

## **Background**

An expert is a person who has made all the mistakes that can be made in a very narrow field.

Niels Bohr

In this chapter we describe important background topics to situate the contributions of this work. We start by describing a high-level view of the architecture of superscalar in-order and out-of-order processors. Next we give an overview of prior work in analytical performance modeling of superscalar processors. The last section of this chapter describes the current state-of-the-art in workload selection.

### 2.1 Superscalar Processors

Microprocessors have been around for several decades, dating back from the 1970s [6]. Their purpose is to execute instructions, as defined by the programmer. Between the start and end of the execution of an instruction on a microprocessor there is a long and complex chain of logic gates. The longer the chain of logic gates, the longer the clock cycle of a single instruction and hence, the longer it takes to execute a software application.

Processing an instruction can be broken up into sequential pipeline stages in an *instruction pipeline*. The chains of logic gates in each of the sequential stages are therefore much smaller and hence the complexity of the work that needs to be done in each clock cycle is drastically reduced and spread over multiple stages. This means the length of the clock cycle can be reduced and instructions can theoretically flow into the pipeline cycle after cycle. Modern pipelines (such as Intel Core i7) use this principle to increase their clock frequency with deeply pipelined processors. The cost of placing buffers (among other logic) between the pipeline stages and the increasing performance penalty of branch mispredictions limit the amount

10 Background

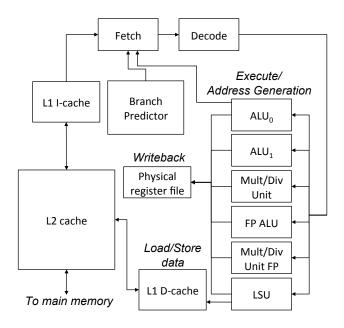

Figure 2.1: Block diagram of a superscalar in-order pipeline.

of pipelining.

A second step in increasing the rate at which instructions are executed is increasing the number of instructions that can be processed by a pipeline stage *concurrently*. Many applications have a certain amount of instruction-level parallelism (ILP): instructions that are independent of each other's results can be executed in parallel. Superscalar processors are built to exploit the instruction-level parallelism of applications. There are basically two kinds of superscalar processors: in-order processors and out-of-order processors. We will discuss both of them in the next subsections.

### 2.1.1 Superscalar in-order processors

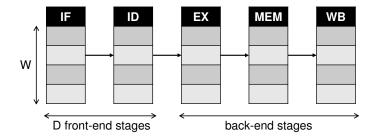

Figure 2.1 shows the block diagram of a superscalar in-order pipeline. Instructions and data are accessed from the memory subsystem, and processed by the other units of the pipeline. The memory subsystem is designed to provide instructions and data to the processor as soon as possible by organizing the data in a hierarchical system. The execution of an instruction can be broken up into five stages: instruction fetch, instruction decode, execute, memory access and writeback. We consider a width W for each of the pipeline stages, meaning that a maximum of W instructions can flow into each pipeline stage every cycle.  $^1$

<sup>&</sup>lt;sup>1</sup>Note that, to ease this discussion, we limit ourselves to a processor of depth 5 and a uniform width for each of the stages. The depth can be chosen arbitrarily and each pipeline

We will now describe the flow of instructions through the pipeline, stage by stage.

**Instruction Fetch** During instruction fetch, the processor fetches new instructions from the level-one instruction cache (L1 I-cache) of the memory subsystem. The fetch unit does this in a sequential way until a control flow instruction (i.e., a branch instruction) redirects the flow of instructions. The result of branch instructions, however, is only known during the execute stage, which means that the processor might fetch too many instructions on the sequential path. Because this has an important impact on performance, modern processors have branch predictors, predicting the outcome of a branch instruction early in the pipeline.

**Instruction Decode** After the instruction is fetched from the memory subsystem it will get decoded by the decode unit/stage which identifies the work that must be done. The decode unit/stage sets up the correct signals in order to process the instruction further: it determines which type of functional unit needs to be accessed based on the instruction type (addition, multiplication, load data, etc.) and which registers need to be accessed from the register file. In addition, depending on the instruction-set architecture (ISA) the processor implements, the decode unit/stage might need to determine the length of the instruction  $^2$ , complicating the logic of the decode unit/stage even further.

For in-order processors, the decode unit/stage also handles the signalling for inter-instruction dependences. When one of the instructions that is decoded, depends on the outcome of an instruction that has not computed its result yet, the decode unit/stage blocks this instruction and all subsequent instructions from going to the next pipeline stage. An instruction in the decode unit/stage can be dependent on instructions in the execute, memory and writeback stages but also on older instructions in the decode unit/stage itself. To avoid waiting on producers to reach the *writeback* stage, forwarding logic is built between the pipeline stages. However, the pipeline will still be blocked until the result is *computed* in the execute stage. As we will see in Chapter 3, stalls due to inter-instruction dependences can be a limit on performance for a large number of applications. This, in addition to the associated hardware cost, limits the maximum width to benefit from instruction-level parallelism.

stage can potentially be designed with different widths.

<sup>&</sup>lt;sup>2</sup>CISC processors (Complex Instruction Set Computer) have instructions of variable length.

12 Background

**Execute** During execute, an instruction is processed by the appropriate functional unit. In Figure 2.1 we distinguish six functional units: two integer Arithmetic Logic Units (ALUs), an integer multiply/divide unit, a floating-point ALU, a floating-point multiply divide unit and a load/store unit (LSU). <sup>3</sup>

Integer ALU instructions, such as integer additions usually take a single clock cycle to execute. This means that each clock cycle a new ALU instruction can get processed by the same ALU. More complex instructions, such as floating-point operations can take multiple clock cycles before the result is calculated. We further refer to these instructions as long-latency instructions. Long-latency instructions not only take multiple cycles to compute their result, they also block the functional unit from processing new instructions for several cycles. To overcome this, functional units for long-latency instructions can have a pipelined design. This means that the computation of e.g., an integer multiply instruction, is further subdivided in smaller steps, allowing several multiply instructions to be in-flight in the same multiply unit. However, this complicates the design more and is not possible for all long-latency instructions.

The number of functional units is another important design parameter. When, for example, the processor pipeline has a width of W=4, and only two ALUs are built in the processor, the processor will stall when more than two ALU instructions are coming out of the decode stage. This is called functional unit contention: the processor stalls because of an insufficient number of functional units. Depending on the target application domain, the number of each type of functional units must be carefully selected. Chapter 3 shows the optimal number of functional units of each type for a large number of applications of the SPEC CPU 2006 and MiBench benchmark suites.

**Memory** Load and store instructions use the LSU to access the memory subsystem in this stage. A load instructions first looks up whether the required data can be found in the fast level-one data cache (L1 D-cache). If the data cannot be loaded from the L1 D-cache, a request is sent out to the level-two cache (L2 cache). If the L2 cache does not have the data either, the request is sent further down the memory subsystem (e.g., L3 cache or directly to main memory).

**Writeback** During the writeback stage, computation results are written to the registers in the physical register file.

<sup>&</sup>lt;sup>3</sup>Note that although the LSU unit is depicted under execute, it is accessed during the memory stage.

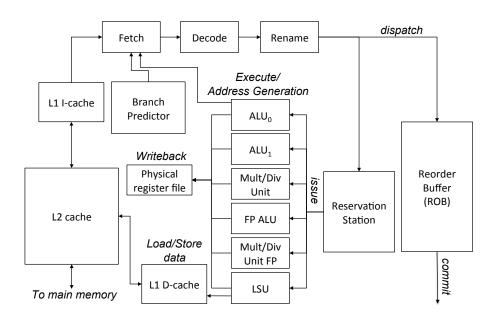

Figure 2.2: Block diagram of a superscalar out-of-order pipeline.

Examples of commercial superscalar in-order microarchitectures are ARM's Cortex-A7, ARM's Cortex-A8, Intel's Bonnell <sup>4</sup> , etc.

### 2.1.2 Superscalar out-of-order processors

Out-of-order processors remove the limit of executing instructions in program order. Instead of blocking the processor whenever an instruction waits for a dependence to resolve or a functional unit to become available, it looks whether it can execute subsequent instructions. Hence, out-of-order processors are capable of exploiting ILP even further. However, this requires additional logic: additional pipeline stages, a rename unit, a re-order buffer (ROB) and (a) reservation station(s). In addition, out-of-order processors improve memory-level parallelism (MLP) by adding miss status handling registers (MSHRs).

While this additional logic improves the ability to exploit the ILP and MLP of an application, the extra out-of-order logic comes at a price. Not only is the design more complex, requiring additional effort throughout the design cycle, out-of-order processors are also power-hungry. This further motivates the popularity of superscalar in-order processors, which are more power-efficient, in embedded systems.

To provide some insight into the differences between out-of-order and in-order processor architectures, we will now describe the flow of an in-

<sup>&</sup>lt;sup>4</sup>The Bonnell microarchitecture is present in the popular Atom Z6 series.

14 Background

struction from fetch to writeback on an out-of-order processor.

**Instruction Fetch** Similar as for in-order processors, instruction fetch loads instructions out of the memory by accessing the L1 instruction cache. It does this sequentially unless the branch predictor or execution unit redirects the fetch unit to fetch from a different address. The branch predictor is typically more complicated for out-of-order processors because more speculative instructions could be in-flight in the processor. Further, the cost of a mispredicted branch is relatively higher for out-of-order processors than for in-order processors, even when the front-end has the same number of pipeline stages. This is caused by the branch resolution time [23]: the time it takes to calculate the outcome of the branch.

**Instruction Decode** As with in-order processors the decode unit/stage identifies the type of work that needs to be done and sets up the signals to process the instruction further. Unlike in-order processors, the detection of inter-instruction dependencies does not happen in this stage but instead happens in the rename unit and the reservation station.

**Instruction Rename** The rename unit is a hardware structure that helps to allow out-of-order execution of instructions. It determines dependencies between instructions and maps the typically small architectural register file to a larger physical register file. This allows instructions that write the same output register (i.e., write-after-write (WAW) dependencies) to be scheduled out-of-order without harming program behavior. It also removes write-after-read (WAR) dependencies. Lastly it performs the necessary bookkeeping when an instruction leaves the ROB.

**Dispatch** The renamed instruction now gets dispatched in the ROB and in the reservation station. Depending on the microarchitecture, there could be multiple reservation stations (e.g., one assigned to each functional unit) and dispatch will need to ensure that the instructions are sent to the correct reservation station. Dispatch is, with the exception of the commit stage, the last stage where instructions flow in program order. The ROB keeps track of this order so that, even if instructions get executed out-of-order beyond dispatch, the microarchitectural state gets updated in-order, i.e., the instructions leave the microarchitecture in program order.

**Issue** In the issue stage, instructions get selected from the reservation station(s) and are sent to the various functional units. This is done by an instruction scheduler. For an instruction to get selected by the scheduler, a

necessary criteria is to have its source registers ready (i.e., all register dependences are resolved) and a functional unit to be available. In addition, more selection criteria, such as the age of the instruction, can be implemented in the scheduler.

**Execute** Similar to in-order processors, this stage starts calculation of the result of an instruction, using the appropriate functional unit. For instructions requiring access to the memory subsystem, an address generator unit (AGU) is often added to calculate memory addresses and detect memory dependencies. As an example, store-to-load forwarding logic could be added to forward results from a store instruction to a dependent load instruction.

**Memory** Memory instructions that have generated an address can access the memory in this stage. Because of the out-of-order nature of executing instructions, additional logic must be available to ensure the correct ordering of memory accesses to the same address. For example, when an instruction reads data from a memory address that is supposed to be written by an earlier instruction (i.e., a read-after-write dependency or RAW dependency) the microprocessor must make sure that the write happens before data gets read.

**Writeback** As mentioned before, instructions update the microarchitecture in program order, despite the fact that they might be executed out-of-order.

**Commit** Instructions leave the ROB in program order.

Examples of out-of-order microarchitectures are AMD's Jaguar, ARM's Cortex-A57, Qualcomm's Krait, Intel's Nehalem, etc.

## 2.2 Analytical Performance Modeling

Before designing the complex RTL code of a superscalar microprocessor, appropriate design decisions need to be made. This is a challenging process and is typically approached by running many cycle-level simulations. As mentioned in Chapter 1, cycle-level simulators execute applications at a speed of up 4 orders of magnitude slower than execution on real hardware. This slows down design space exploration as computer architects need to wait on simulation results. To accommodate for the slow speed, a better approach exists in having a good first-order analytical model which

16 Background

trades off accuracy for speed. There are basically three approaches to analytical performance modeling: mechanistic modeling, empirical modeling and hybrid mechanistic/empirical modeling. In the next subsection we will briefly describe the different types of analytical modeling and give an overview of some of the existing related work.

### 2.2.1 Mechanistic Modeling

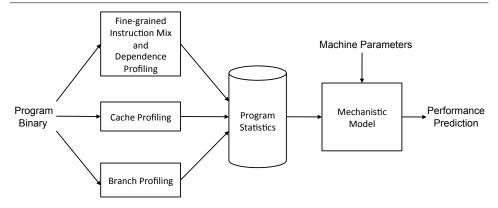

Mechanistic modeling is derived from the actual mechanisms in the processor. A mechanistic model has the advantage of directly displaying the performance effects of individual mechanisms, expressed in terms of program characteristics such as inter-instruction dependence profiles and fine-grained instruction mix; machine parameters such as processor width, number of functional units and pipeline depth; and program-machine interaction characteristics such as cache miss rates and branch misprediction rates.

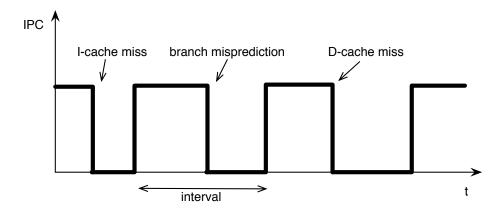

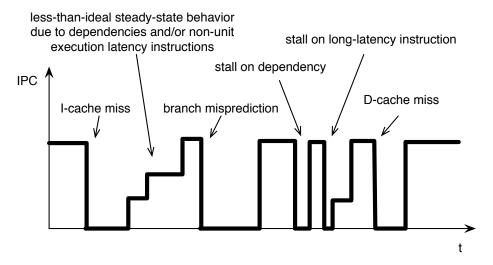

Prior work focused on mechanistic modeling of out-of-order processor performance for the most part. Michaud et al. [48] build a mechanistic model of the instruction window and issue mechanism. Karkhanis and Smith [41] extend this simple mechanistic model to build a complete performance model that assumes sustained steady-state issue performance punctuated by miss events. Chen and Aamodt [8] improve upon this model through more accurate modeling of pending data cache hits, overlaps between computation and memory accesses, and the impact of a limited number of MSHRs. Taha and Wills [59] propose a mechanistic model that breaks up the execution into so-called macro blocks, separated by miss events. Eyerman et al. [24] propose the interval model for superscalar out-of-order processors.