# Influence of Random DC Offsets on Burst-Mode Receiver Sensitivity

Peter Ossieur, *Member, IEEE*, Tine De Ridder, *Student Member, IEEE*, Xing-Zhi Qiu, *Member, IEEE*, and Jan Vandewege, *Member, IEEE*

Abstract—This paper presents the influence of random direct current (dc) offsets on the sensitivity of dc-coupled burst-mode receivers (BMRxs). It is well known that a BMRx exhibits a noisy decision threshold, resulting in a sensitivity penalty. If the BMRx is dc coupled, an additional penalty is incurred by random dc offsets. This penalty can only be determined for a statistically significant number of fabricated BMRx samples. Using Monte Carlo (MC) simulations and a detailed BMRx model, the relationship between the variance of this random dc offset, the resulting sensitivity penalty, and BMRx yield (the fraction of fabricated BMRx samples that meets a given sensitivity specification) is evaluated as a function of various receiver parameters. The obtained curves can be used to trade off BMRx die area against sensitivity for a given yield. It is demonstrated that a thorough understanding of the relationship between BMRx sensitivity, BMRx yield, and the variance of the random dc offsets is needed to optimize a dccoupled BMRx with respect to sensitivity and die area for a given yield. It is shown that compensation of dc offsets with a resolution of 8 bits results in a sensitivity penalty of 1 dB for a wide range of random dc offsets.

*Index Terms*—Avalanche photodiodes, bit error rate (BER), burst-mode receiver (BMRx), optical access network, optical receiver.

#### I. INTRODUCTION

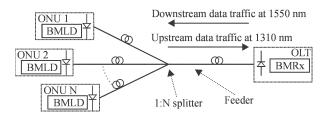

**B** URST-MODE receivers (BMRxs) [1]–[4] are an important component in passive optical networks (PONs). PON is an optical transmission technology intended for use in the access network. In PONs, the capacity of the fiber plant is shared among a group of subscribers (see Fig. 1). The upstream traffic (from the subscribers to the central office) of all these subscribers is typically combined in a time division multiple access (TDMA) scheme. A BMRx is used in the central office of the PON to handle this TDMA upstream communication. A BMRx is needed as the signal arriving at the central office consists of a succession of packets with widely varying amplitudes [1].

The adoption of the ITU-T G.984.2 standard [5] [so-called gigabit-capable passive optical network (GPON)] and the IEEE 802.3ah standard {so-called gigabit-capable Ethernet passive optical network [(G)EPON]} [6] has intensified the research aimed at developing gigabit-capable BMRxs, with an emphasis on achieving high sensitivity and dynamic range [7]–[11]. Indeed, successful and economical deployment of PONs requires

Manuscript received September 21, 2005; revised November 10, 2005.

The authors are with the INTEC\_design Laboratory, Ghent University, Ghent B-9000, Belgium (e-mail: peter.ossieur@intec.ugent.be; tine.deridder@intec.ugent.be; xingzhi.qiu@intec.ugent.be; jan.Vandewege@intec.ugent.be).

Digital Object Identifier 10.1109/JLT.2005.863294

Fig. 1. Overview of a typical passive optical network. OLT = optical line termination, ONU = optical network unit, BMRx = burst-mode receiver, BMLD = burst-mode laser driver.

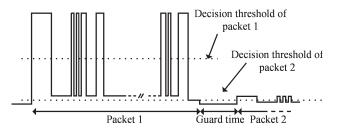

Fig. 2. Typical input signal of a BMRx when employed in the optical line termination of a PON.

large physical reach (distance between the subscriber and the central office) and especially large splitting factors (the number of subscribers served by a single PON) [12]. This physical reach and splitting ratio are largely determined by the dynamic range and sensitivity of the BMRx [12]–[14]. Hence, it is important to maximize the sensitivity and the dynamic range of the BMRx. Therefore, one has to thoroughly understand and quantify all factors that could give rise to sensitivity penalties due to the bursty nature of the optical signal arriving at the optical line termination. This paper investigates the reduction of sensitivity due to random direct current (dc) offsets. Indeed, to the extent of the author's knowledge, the impact of random dc offsets on the sensitivity of BMRxs (and more, in general, optical receivers) has never been reported upon before in open literature.

As mentioned above, the upstream signal over a PON consists of a rapid succession of packets with varying amplitudes. Hence, the decision threshold needed to make a difference between a received 1 and a received 0 differs from one packet to another packet (see Fig. 2). Thus, a BMRx needs to extract a decision threshold from each incoming packet. This is typically done during a few bits (called the preamble) at the beginning of each packet. In this paper, a very short guard time between packets is assumed. This corresponds to the GPON case (e.g., a guard time as short as 25.6 ns is allowed at 1.25 Gb/s) but is unlike the situation for EPON, where long guard times in combination with 8B/10B coding allow for alternating current (ac) coupling [7], [15]. The mentioned very short guard times combined with > 72 consecutive identical digits necessitate the use of a dc-coupled BMRx. As will be explained in Section II, a dc-coupled BMRx that can only use a few bits to extract its decision threshold will exhibit two significant sources of sensitivity penalties when compared to continuous-mode receivers. Indeed, the extracted decision threshold is noisy, giving rise to a first sensitivity penalty. This penalty, which can range from a few tenths of decibels up to a few decibels, has already been extensively studied [16]–[19]. A second sensitivity penalty stems from unintentional but unavoidable dc offsets that are added to the input signal itself and the extracted decision threshold. The penalty due to a fixed dc offset has been studied in [19]. However, a major part of this dc offset is a random variable that depends on the matching properties of the technology in which the BMRx is designed. Such a random dc offset stems from randomness in chip fabrication processes, resulting in small random differences between the characteristics of geometrically identical transistors, such as in differential pairs or current mirrors [20]. In this paper, the sensitivity penalty due to such random dc offsets is studied in detail.

The importance of this study lies with the fact that in order to use optical components in access networks, such components should be low-cost. This necessitates the use of standard packages such as TO-can packages. Use of such packages puts severe restrictions on the maximum die dimensions. On one hand, one would like to keep the sensitivity penalty due to random dc offsets small (requiring limited random dc offsets, hence large transistors and thus requiring large die area), but on the other hand, one would also like to keep the die dimensions within the restrictions imposed by the packaging technology and the cost requirements.

The paper is organized as follows. In Section II, the BMRx operation and several concepts related to random dc offsets are introduced in a qualitative manner. In Section III, a previously developed model [19] for predicting the BMRx sensitivity is extended to include the sensitivity penalty due to random dc offsets. Section IV presents important results and design guide-lines for dc-coupled BMRxs and shows how these guidelines were implemented in a practical design [10].

### II. BMRX OPERATION AND RANDOM DC OFFSETS

## A. BMRx Operation

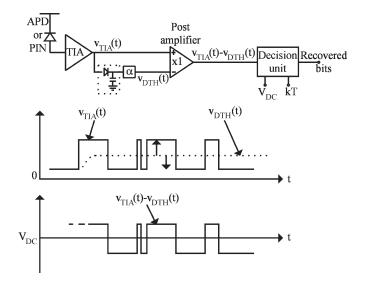

Fig. 3 shows a conceptual block diagram of a dc-coupled BMRx together with the important waveforms. An opticalto-electrical (O/E) converter [typically a p-i-n diode or an avalanche photodiode (APD)] converts the incoming optical power into an electrical current. Using a dc-coupled transimpedance amplifier (TIA), this electrical current is amplified and converted to a voltage signal  $v_{\text{TIA}}(t)$ . Then, typically using fast peak detectors and appropriate scaling with a factor  $\alpha$ , the decision threshold  $v_{\text{DTH}}(t)$  is extracted from the level of incoming 1s and, where applicable, incoming 0s.  $\alpha$  should be chosen such that the noise-free decision threshold (the threshold that would be extracted in case the receiver chain does not exhibit any noise) is located at the intersection of the probability density of the 1 level and the probability density of the 0 level,

Fig. 3. Conceptual block diagram of a BMRx and associated signals. APD = avalanche photodiode, TIA = transimpedance amplifier.

guaranteeing best sensitivity [21]. Note, however, that for many practical receivers,  $\alpha$  equals 1/2. The difference between the output signal  $v_{\text{TIA}}(t)$  of the TIA itself and the extracted decision threshold  $v_{\text{DTH}}(t)$  is then compared to a constant voltage level  $V_{\text{dc}}$  at regular times kT, where k is an integer and T is the bit period. If the signal level  $v_{\text{TIA}}(kT) - v_{\text{DTH}}(kT)$  is higher than  $V_{\text{dc}}$ , then it is said that a 1 was received, otherwise, it is said that a 0 was received. Note that in many practical BMRxs, the bit decision for bit k is made by direct comparison of  $v_{\text{TIA}}(kT)$ with  $v_{\text{DTH}}(kT)$ . This is mathematically equivalent with comparing  $v_{\text{TIA}}(kT) - v_{\text{DTH}}(kT)$  with zero, or in this paper, with  $V_{\text{dc}} = 0$ . The sole purpose of introducing a voltage level  $V_{\text{dc}}$ that may or may not be zero is for convenience of modeling, as will be explained in paragraph Sections II-B and III.

It is well known from classical receiver theory that the optimum decision threshold is situated at the point where the probability density functions of a received 1 and a received 0 intersect [21]. Obviously, any deviation from the optimum decision threshold, for example, due to noise and/or dc offsets, will result in a sensitivity penalty. Therefore, when compared to so-called continuous-mode optical receivers, a BMRx typically shows reduced sensitivity. Indeed, in a continuous-mode optical receiver, the decision threshold is extracted using circuitry that operates with time constants in the range of many thousands of bit periods. Hence, the circuitry that extracts the decision threshold can be very accurate, and the extracted decision threshold is a fixed voltage level, free of any noise (the noise is effectively filtered out). In a BMRx, using many thousands of bits to extract the decision threshold is not an option, as a BMRx needs to handle packets with limited length originating from different subscribers. Indeed, this would lead to an unacceptable reduction in transmission efficiency. Hence, the decision threshold is typically extracted using a limited number of bits, known as the preamble, at the start of each packet. This fast extraction results in two sensitivity penalties. 1) As the extraction is done with a large bandwidth, the extracted decision threshold effectively exhibits noise. The sensitivity penalty due to a noisy decision threshold has already received

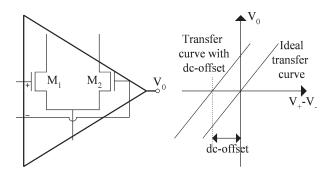

Fig. 4. Input stage of a differential amplifier exhibiting dc offsets.

extensive attention in literature [16]–[19]. 2) The other source of sensitivity penalty arises from the well-known fact that any electronic circuit shows an inherent tradeoff between speed and dc accuracy for a fixed power consumption and a given technology [22], [23]. As the power consumption is limited by packaging concerns, the faster a circuit, the less accurate it will become. For example, for a metal–oxide–semiconductor (MOS) transistor, this relationship can be expressed as

$$\frac{\text{Speed} \times \text{Accuracy}^2}{\text{Power}} = \frac{1}{C_{\text{ox}} A_{Vt}^2}$$

(1)

where  $C_{ox}$  and  $A_{Vt}$  are technology constants [22]. Similar relationships or bounds exist for bipolar transistors [23]. Thus, it is clear that the fast extraction of the decision threshold results in unavoidable dc offsets. Therefore, many dc-coupled BMRxs include extensive circuitry to remove or compensate these dc offsets [2], [4], [10]. In order to properly dimension such dc offset compensation circuitry, it must be thoroughly understood how random dc offsets degrade optical receiver sensitivity.

# B. Qualitative Description of Random DC Offsets, Sensitivity, and Yield

Any dc-coupled circuitry will add random dc offsets to the signals that it processes. These random dc offsets stem from small differences in the characteristics of nominally equal transistors, and in turn, the result of the randomness of the chip fabrication process [20]. For example, the input stage of the amplifier in Fig. 3 that generates the difference between the output signal of the TIA and the extracted decision threshold will typically consist of a differential pair (see Fig. 4). Assuming that both the transistors  $M_1$  and  $M_2$  are ideal (in the sense that the input stage would exhibit no dc offset), then if both inputs of the differential pair are kept at the same potential, the differential output of the amplifier will be zero. However, due to small random fluctuations in the geometry of the transistors  $M_1$  and  $M_2$ , the characteristics (e.g., the threshold voltage) of both transistors will be different, and the differential output of the amplifier will be nonzero, even if both inputs are kept at an equal potential. This dc offset is a random variable, typically Gaussian distributed [20]. The larger the geometrical dimensions of a transistor (e.g., large width and length in the case of an MOS transistor), the less important the random fluctuations of its characteristics [20]. All subblocks of the BMRx as shown in Fig. 3 will exhibit similar random uncorrelated dc offsets. In

Fig. 3, one can easily verify that the accumulated effect of the dc offsets from the various components in the BMRx is mathematically indistinguishable from a shift in the voltage level  $V_{dc}$ . Indeed, assume for simplicity that the only noise source present is the Gaussian additive noise from the preamplifier. Then, the error probability  $P[E_k]$  for bit k can be written as

$$P[E_k] = p_1 P \left[ \overline{v_{\text{TIA}}(kT)} + E_{\text{TIA}} + n_{\text{TIA}}(kT) - \overline{v_{\text{DTH}}(kT)} - E_{\text{PK}} - E_{\text{PA}} < V_{\text{dc}} | 1 \right]$$

+  $p_0 P \left[ \overline{v_{\text{TIA}}(kT)} + E_{\text{TIA}} + n_{\text{TIA}}(kT) - \overline{v_{\text{DTH}}(kT)} - E_{\text{PK}} - E_{\text{PA}} > V_{\text{dc}} | 0 \right]$

=  $p_1 P \left[ \overline{v_{\text{TIA}}(kT)} + n_{\text{TIA}}(kT) - \overline{v_{\text{DTH}}(kT)} < V'_{\text{dc}} | 1 \right]$

+  $p_0 P \left[ \overline{v_{\text{TIA}}(kT)} + n_{\text{TIA}}(kT) - \overline{v_{\text{DTH}}(kT)} > V'_{\text{dc}} | 0 \right]$

(2)

where  $V'_{dc} = V_{dc} - E_{TIA} + E_{PK} + E_{PA}$  is the shifted voltage level,  $E_{TIA}$ ,  $E_{PK}$ , and  $E_{PA}$  are the dc offsets of the TIA, the peak detector, and the postamplifier, respectively, as shown in Fig. 3, and  $n_{TIA}(kT)$  is the noise from the preamplifier and the decision moment kT.  $p_1$  and  $p_0$  are the occurrence probabilities of a transmitted 1 and a transmitted 0, respectively.  $\overline{v_{TIA}(kT)}$ and  $\overline{v_{DTH}(kT)}$  indicate the time averages of  $v_{TIA}(kT)$  and  $v_{DTH}(kT)$ . Hence, the random dc offsets will be modeled by assuming that  $V_{dc}$  exhibits a given probability density. This is explained in detail in Section III.

For the remainder of the paper, it is important to make a clear distinction between a BMRx design and a fabricated BMRx sample. A BMRx design refers to the schematic and layout database of a certain BMRx. A BMRx sample refers to an actually existing chip, fabricated using the layout database of the BMRx design.

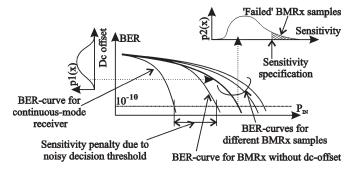

If for a BMRx design, samples are fabricated, this random dc offset will assume a value that differs from one sample to another, according to a probability density p1(x). Hence, the sensitivity will differ from one sample to another. Therefore, the sensitivity of a collection of BMRx samples that exhibit random dc offsets is, in turn, also a random variable. This random variable will exhibit a certain probability density p2(x), whose shape depends upon the probability density p1(x), and the characteristics of the BMRx design. This is further clarified in Fig. 5. In Fig. 5, several bit error rate (BER) curves are shown as a function of the average optical power. A certain BMRx is said to have a sensitivity P if the BER at an optical input power P equals a given number smaller than 1 (e.g.,  $10^{-10}$ ). In Fig. 5, a BER curve is shown of both a continuous-mode optical receiver and an "ideal" BMRx (ideal in the sense that this BMRx does not exhibit any dc offsets). Due to the noise on the decision threshold, for the same optical power, the BER of the "ideal" BMRx will be higher than the BER of the continuous-mode receiver, resulting in a sensitivity penalty, as shown in Fig. 5. Also shown in Fig. 5 are three BER curves of three BMRx samples, each exhibiting a different dc offset. One can again

Fig. 5. BMRx sensitivity penalties and BMRx yield as a result of dc offsets. p1(x) is the probability density function of the random dc offsets, BER = biterror rate, and p2(x) is the resulting distribution of BMRx sensitivities.

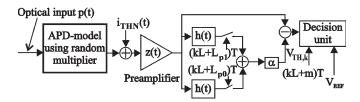

Fig. 6. Model of the BMRx.  $(kL + L_{px})T$ , x = 0, 1 are the times where the decision threshold extraction unit samples its input response for a 1 and a 0, and (kL + m)T is the time where the decision unit samples its input for bit m of packet k.

see that compared to the "ideal" BMRx, a sensitivity penalty is incurred. Furthermore, note that, indeed, the sensitivity of a BMRx sample is now itself a random variable, with a certain probability density p2(x). If a certain sensitivity specification is required, some BMRx samples may fail to meet this specification due to excessive dc offset. Hence, a yield can be defined, as done for many circuits such as analog-to-digital converters [24], [25]. This yield is the fraction of BMRx samples that meets a given sensitivity specification. As seen in Fig. 5, if one knows the sensitivity probability density p2(x) and the sensitivity specification, one can directly calculate the yield. For high yield (e.g., better than 99.7% is a typical requirement [25], [26]), this sensitivity specification can only be worse than the sensitivity of an "ideal" BMRx, which does not exhibit any dc offsets. Indeed, requiring a sensitivity specification better than the "ideal" BMRx would result in a yield of zero, assuming that the decision threshold of the "ideal" BMRx is located at its optimum value (requiring an optimal scaling factor  $\alpha$ ). Hence, an effective sensitivity penalty that can only be measured for a large collection of BMRx samples is incurred. Clearly, if one reduces the dc offset variance, then the yield of the BMRx design will increase for a given sensitivity specification, or the sensitivity can be improved for a given yield. Decreasing the variance of the random dc offset requires increasing the die area (the larger the geometrical area of a transistor, the less important the random fluctuations of its characteristics become) [20], increasing BMRx cost.

#### III. BMRX MODEL

### A. BMRx Model

Fig. 6 gives the model of the BMRx as developed in [19]. Only a brief outline is given here; the derivation of the mathematical equations has been discussed in [19] and will not be repeated here. The current from an APD with gain G is fed to a preamplifier with impulse response z(t). The APD model takes into account the detailed statistics of the avalanche multiplication noise; details can be found in [19] and [27]. G = 1 is equivalent to a p-i-n photodiode. The preamplifier thermal noise  $i_{\text{THN}}(t)$  is assumed to be white and Gaussian. After the preamplifier, the signal is fed to a decision unit and a sample-and-hold (S/H) unit. The S/H unit takes care of the decision threshold extraction, the decision unit takes the actual data decisions. The S/H unit contains two filters with impulse response h(t). To extract the decision threshold, it successively samples the amplitude of a 1 and a 0 within the preamble of each packet. For simplicity, it is assumed that there is an equal number L of successive 1s and 0s (with bit period T) within the preamble. The two samples are added together and a scaling factor  $\alpha$  is applied, which places the threshold  $v_{\text{DTH }k}$ for packet k between the level of a 1 and a 0 [1], [3]. As was done in [13], [17], and [19], z(t) is assumed to be a firstorder resistance–capacitance (RC) filter (with 3-dB bandwidth  $f_{3 \text{ dB}}$ ) as this approximates the frequency domain behavior of many practical receivers. Other impulse responses can be used without significantly altering the conclusions from this study. As in [13] and [17]–[19], it is assumed that the convolution of z(t) with h(t) is a first-order RC filter with time constant  $\tau$ , adapted according to the preamble length 2L and the bit period T as

$$\tau = -LT \ln^{-1}(\delta). \tag{3}$$

$\delta$  is the normalized steady-state error, which is the difference between the output of the S/H filter at a time t = LT and the steady-state output of the S/H filter normalized to this output, assuming continuous 1s (or 0s) starting at t = 0 [18], [19]. The decision unit samples each packet at regular intervals with length T. By comparison of these samples against a constant voltage level  $V_{dc}$ , a decision is made whether a 1 or a 0 is received. As explained in [19], using this model, the BER for given optical power can be calculated by the following N-point Gaussian quadrature formula [27], given as

$$BER = \frac{1}{4} \sum_{x=0,1} \sum_{i=1}^{N} w_{i,x} \operatorname{erfc}\left(\frac{(-1)^{x} V_{dc} - (-1)^{x} s_{x} - a_{i,x}}{\sqrt{2}\sigma_{T}}\right)$$

(4)

where erfc is the complementary error function. In (4),  $\{w_{i,x}, a_{i,x} | i = 1, ..., N\}, x = 0, 1$  form a set of weights and abscissas that incorporate the APD multiplication noise. These weights and abscissas can be computed using the characteristic function of the APD multiplication noise [19], [27].  $\sigma_T$  is the thermal noise from the preamplifier referred to the input of the decision unit. In the case of a BMRx,  $\sigma_T$  contains a direct contribution from the input-referred noise of the preamplifier, and an additional indirect contribution from the noisy decision threshold [19]. Similarly, the set  $\{w_{i,x}, a_{i,x} | i = 1, ..., N\}, x = 0, 1$  of weights and abscissas consists of a direct contribution from the APD multiplication noise, and an additional indirect contribution from the noisy decision threshold.

Detailed formulas to calculate the contributions from a noisy decision threshold to the BER can be found in [19] and are based upon averaging the BER with respect to the distribution of the noisy decision threshold [16], [17], [19].  $s_x$ , x = 0, 1 is the signal strength at the input of the decision unit when a 1 or a 0 was transmitted. To model the random dc offset  $V_{dc}$  is set equal to

$$V_{\rm dc}(\beta) = \beta \mu_1 + (1 - \beta) \mu_0.$$

(5)

$\mu_1$  and  $\mu_0$  are the expected values of the signal at the decision threshold input when a 1 and a 0 is received, respectively, for a BMRx that does not exhibit any random dc offsets. Clearly,  $0 < \beta < 1$  is a normalized constant voltage level used in the decision unit to discriminate between a 1 and a 0 [19]. This normalization allows to compare the sensitivity penalty due to random dc offsets of different BMRx designs with each other. Contrary to [19] where  $\beta$  was fixed, here,  $\beta$  is modeled as a Gaussian random variable with mean  $\mu_{\beta}$  and standard deviation  $\sigma_{\beta}$ . This does not correspond to a noisy decision threshold as it is assumed that each realization of  $\beta$  corresponds to a single sample of a given BMRx design, as has been explained in Section II-B. Furthermore, from (5) and as explained above, the effect of a noisy decision threshold influences the BER via contributions to  $\sigma_T$  and the set of weights  $\{w_{i,x}, a_{i,x} | i =$  $1, \ldots, N$ . Clearly, this is different from the way in which random dc offsets modeled using (5) enters formula (4) for calculating the BER. Note that the BER in (4) corresponds to the BER averaged over the distribution of the noise on the decision threshold [19], which, due to the assumed ergodicity of this distribution, corresponds to the BER obtained from a large number of packets [16]. Hence, as for calculating sensitivity penalties, only these average BERs are used; it is not possible that a BMRx with random dc offsets and noisy decision threshold has better sensitivity than a BMRx without random dc offsets but with a noisy decision threshold. Although this is possible when comparing BERs on a packet-by-packet basis, such comparison does not make sense, as typically packets should be very long to actually measure BERs as low as  $10^{-10}$ .

As explained in Section II, a collection of BMRx samples suffering from random dc offsets will exhibit a sensitivity distribution. As shown in Fig. 5 and explained in Section II-B, this distribution results in a yield, which is the fraction of BMRx samples that meets a given sensitivity specification. To calculate this yield, one must determine the sensitivity distribution. In principle, as one knows, the distribution of  $V_{dc}$ , the sensitivity distribution for a fixed BER can be found using (4). To do this analytically, this requires inversion of (4) with respect to  $V_{dc}$ . Straightforward inversion of (4) is clearly difficult to perform analytically. Therefore, Monte Carlo (MC) simulations are used to obtain a statistical estimate  $\hat{Y}$  of the yield given as

$$\hat{Y} = \frac{1}{N_{\rm MC}} \sum_{i=1}^{N_{\rm MC}} \varphi(P_i) \qquad \varphi(P_i) = \begin{cases} 1, & P_i \le P_{\rm SPEC} \\ 0, & P_i > P_{\rm SPEC} \end{cases}$$

(6)

where  $N_{\rm MC}$  is an amount of MC runs ensuring a statistical confidence interval of  $\pm 1\%$ .  $P_i$  is the sensitivity of BMRx sample *i* and  $P_{\rm SPEC}$  the sensitivity specification. If  $P_{\rm SPEC}$  is

TABLE I BURST-MODE RECEIVER PARAMETERS

| Parameter                                               | Value |

|---------------------------------------------------------|-------|

| 3-dB bandwidth of the preamplifier f <sub>3dB</sub>     | 0.8/T |

| Normalized steady-state error $\delta$                  | 0.01  |

| Scaling factor $\alpha$                                 | 0.5   |

| Noise charges per bit period Nn                         | 1000  |

| Ionization ratio k of electrons and holes of the APD    | 0.35  |

| Ratio of optical power of a 1 to a 0 (extinction ratio) | 10    |

larger than the offset-free BMRx sensitivity, then the collection of BMRx samples exhibits a sensitivity penalty  $P_{\Delta}$  defined as the ratio (in decibels) of  $P_{\rm SPEC}$  to the offset-free BMRx sensitivity.

A single MC run consists of two steps. 1) A random number is drawn from a Gaussian distribution with mean  $\mu_{\beta}$  and standard deviation  $\sigma_{\beta}$ , resulting in a value for  $V_{dc}$  (5). 2) From (4), one can calculate numerically the associated optical power  $P_i$  needed to ensure a given BER (e.g.,  $10^{-10}$ ). By iterating both steps, a collection of sensitivities is obtained, from which one can generate histograms or calculate yields using (6). The required number of iterations is determined by the required confidence interval on, for example, the yield.

#### **B.** Normalizations

To keep the results presented in Section IV widely applicable, a number of frequently used normalizations will be presented. As in [19], the bit period will be normalized to 1. The thermal noise at the preamplifier input has been normalized as [28]

$$qN_n = \sigma_{\text{IN},T}T\tag{7}$$

where  $N_n$  is the number of noise charges per bit period, q is the electronic charge, and  $\sigma_{IN,T}$  is the root mean square (rms) thermal noise at the preamp input [19]. The peak input optical power is expressed as a number N of photoelectrons per bit period [28]

$$qN = I_{\rm pk}T\tag{8}$$

in which  $I_{pk}$  is the primary (i.e., before multiplication) peak APD current and rectangular shaped optical input pulses are assumed [19]. Table I lists the BMRx parameters used in Section IV. A 3-dB bandwidth of 0.8/T was chosen as this corresponds to the experimental results presented in [3]. The bandwidth in this design is slightly higher than the optimum tradeoff of 0.7/T between noise and intersymbol interference to account for process variations. As in [13] and [19], intersymbol interference is assumed to be negligible. If intersymbol interference is present, the presented mathematical model can be used if care is taken to correctly calculate the weights and abscissas  $\{w_{i,x}, a_{i,x} | i = 1, ..., N\}$  [27]. The presented model has been used before with success to calculate the sensitivity of BMRxs [13].

# **IV. RESULTS**

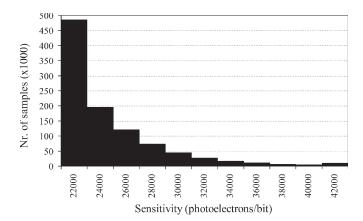

As many optical receivers employ a p-i-n photodiode, special attention is paid to the case where G = 1. Fig. 7 displays a

Fig. 7. Histogram of the sensitivity obtained from 10<sup>6</sup> Monte Carlo runs.

Fig. 8. Yield of the PIN-BMRx.  $\mu_{\beta}$  is fixed to 0.5.

histogram of the sensitivity of a p-i-n BMRx, obtained from  $10^6$  MC runs. Note how the shown histogram is clearly skewed. The sensitivity of the ideal BMRx that does not exhibit random dc offsets is 20 351 photoelectrons/bit. The statistical mean of the histogram is 24 350 photoelectrons/bit. 63% of the MC generated samples have a sensitivity that is better than this statistical mean. However, typically, a yield of only 63% is considered to be a particularly bad design; normally, yields > 99.7% are aimed at. This clearly demonstrates that the sensitivity, averaged over the probability density of the dc offsets, is not a good measure to characterize the sensitivity of a collection of BMRxs that exhibit random dc offsets. This is unlike the situation with noise on the decision threshold, where it does make sense to characterize the BMRx sensitivity using its average over the probability density of the sensitivity.

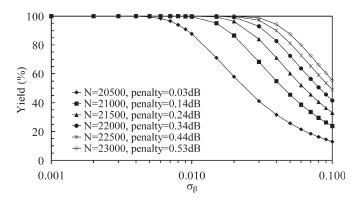

Fig. 8 displays the yield as a function of  $\sigma_{\beta}$ . The decision threshold is extracted from a single 1 and a single 0. The nominal sensitivity for G = 1 of the BMRx with the parameters from Table I is 20 350 photoelectrons/bit period. If  $\sigma_{\beta}$  is smaller than 0.005, then it can be seen that the yield is always greater than 99.7%, with a negligible sensitivity penalty (compared to a BMRx that does not exhibit random dc offsets) of 0.07 dB. If a larger sensitivity penalty can be tolerated, then one can allow a worse dc accuracy or equivalently a bigger dc offset variance  $\sigma_{\beta}$  for a fixed yield. Thus, for a given technology, Fig. 8 can be used to quantify the tradeoff between higher dc accuracy on one hand (which implies higher chip complexity and die area) and reduced sensitivity penalty on the other hand (which

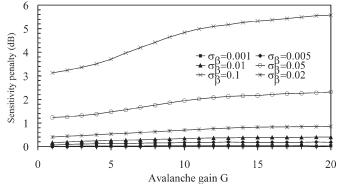

Fig. 9. Sensitivity penalty (decibels) as a function of G.

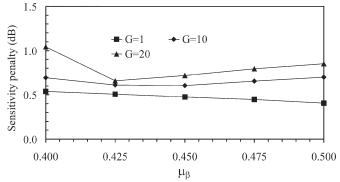

Fig. 10. Sensitivity penalty as a function of  $\mu_{\beta}$  for different G.

implies better sensitivity and dynamic range). For example, in [4], a series of amplifiers is used to improve the signal-to-offset ratio along this chain of amplifiers. The larger the number of amplifiers, the less the influence of random dc offsets, but the higher the circuit complexity. This tradeoff was mentioned (in a qualitative way) in [4]. Another practical way to reduce  $\sigma_{\beta}$  is to increase the geometrical dimensions of the transistors that contribute most to the random dc offsets, for example, the input transistors of differential amplifiers as shown in Fig. 4. Using Fig. 8, this tradeoff between maximum allowable dc offset and circuit complexity can now be quantified.

The yield, if the sensitivity specification  $P_{\text{SPEC}}$  equals the sensitivity averaged with respect to its probability density, ranges between 67% and 60% for  $\sigma_{\beta}$  ranging from 0.1 to 0.001. This proves again that contrary to a noisy decision threshold, one cannot describe the sensitivity of a collection of BMRx samples that exhibit random dc offsets using the expected value of the sensitivities.

To limit the parameter space in case an APD is used, the penalty  $P_{\Delta}$  as defined in Section III-A is determined that results in a yield of 99.7%. Fig. 9 displays this sensitivity penalty as a function of G for different values of  $\sigma_{\beta}$ ;  $\mu_{\beta}$  equals 0.5. With increasing G, the penalty increases. This is due to the fact that the optimum threshold is no longer situated halfway between the level of a 1 and a 0, due to the signal dependent APD multiplication noise. Fig. 10 shows that the penalty can be reduced for higher G by shifting  $V_{dc}$  closer to the 0 level. This is a practical way to control  $\mu_{\beta}$ .

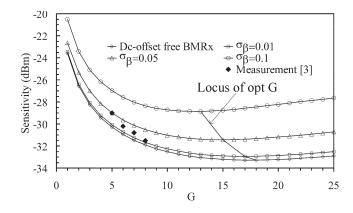

Fig. 11 gives the sensitivity of a 1.25-Gb/s BMRx as a function of G with  $\sigma_{\text{IN},T}$  measured as 250 nA<sub>rms</sub> together

Fig. 11. Sensitivity of a 1.25-Gb/s BMRx as a function of avalanche gain.

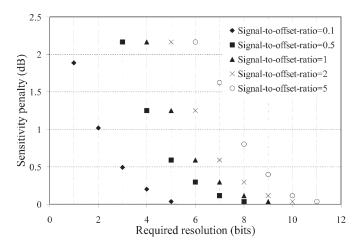

Fig. 12. Sensitivity penalty versus the resolution of D/A converter.

with the results from [12]. Such a BMRx can be used for the upstream transmission over GPONs [11]. With G = 6 and  $\sigma_{\beta}$  equal to 0.05, a sensitivity of -29 dBm is reached for 99.7% of all BMRx samples. These values correspond to experimental results for a BMRx sample presented in [3].

Several BMRx designs employ digital-to-analog (D/A) converters to compensate various dc offsets [2], [3], [10]. Obviously, it is important to know the required resolution of such D/A converters, as increased resolution drastically increases circuit complexity and required die area. Fig. 12 displays the required resolution of a digital-to-analog (D/A) converter as a function of the sensitivity penalty. The curves have been obtained as follows. First, the amplitude of the least significant bit (LSB) is obtained by assuming that the D/A converter succeeds in compensating the dc offset within  $\pm 1$  LSB. The resulting sensitivity penalty due to a worst case remaining dc offset can be easily computed using (3). Then the required fullscale range is obtained as three times the standard deviation of the random dc offset that needs to be compensated. This results in a yield of 99.7%. As the LSB amplitude and the full-scale range are both known, the required resolution can be easily calculated. In Fig. 12, the required resolution is shown together with the resulting worst case sensitivity penalty. This is done for several ratios of the effective signal to the standard deviation of the random dc offsets. Here, the effective signal is the difference between the amplitude of a 1 and a 0 for the ideal (i.e., without any dc offsets) BMRx. Note that for many BMRxs, the magnitude of the random dc offsets can easily exceed the signal amplitude.

In Fig. 12, one can see that an 8-bit D/A converter is sufficient to ensure that the sensitivity penalty is always smaller than 1 dB, even if the dc offsets to be compensated are five times larger than the effective signal amplitude. In [10], 7-bit D/A converters were used to compensate the dc offsets. The magnitude of the random dc offsets was such that this ensured that the worst case sensitivity penalty was always smaller than 0.3 dB. Fig. 12 can be used to dimension the D/A converters of a BMRx once the required sensitivity is given.

#### V. CONCLUSION

In this paper, the sensitivity penalty due to random dc offsets in dc-coupled BMRxs has been studied. The results can be used to trade off dc accuracy against sensitivity and thus allow optimizing the BMRx design with respect to die area and yield, determining the cost of the device.

It is shown that if the dc offset compensation circuitry has a resolution of 8 bits, this results in a sensitivity penalty less than 1 dB, even if the magnitude of the random dc offsets is five times larger than the effective signal amplitude.

### ACKNOWLEDGMENT

The authors thank the anonymous reviewers of this paper for their invaluable comments.

#### REFERENCES

- [1] Y. Ota, R. G. Swartz, V. D. Archer, III, S. K. Korotky, M. Banu, and A. E. Dunlop, "High-speed, burst-mode, packet-capable optical receiver and instantaneous clock recovery for optical bus operation," *J. Lightw. Technol.*, vol. 12, no. 2, pp. 325–331, Feb. 1994.

- [2] S. Brigati, P. Colombara, L. D'Ascoli, U. Gatti, T. Kerekes, and P. Malcovati, "A SiGe BiCMOS burst-mode 155-Mb/s receiver for PON," *IEEE J. Solid-State Circuits*, vol. 37, no. 7, pp. 887–894, Jul. 2002.

- [3] P. Ossieur, Y. C. Yi, J. Bauwelinck, X. Z. Qiu, J. Vandewege, and E. Gilon, "DC-coupled 1.25-Gbit/s burst-mode receiver with automatic offset compensation," *Electron. Lett*, vol. 40, no. 7, pp. 447–448, Apr. 2004.

- [4] M. Nakamura, N. Ishihara, and Y. Akazawa, "A 156-Mb/s CMOS optical receiver for burst-mode transmission," *IEEE J. Solid-State Circuits*, vol. 33, no. 8, pp. 1179–1187, Aug. 1998.

- [5] Gigabit-Capable Passive Optical Networks (GPON): Physical Media Dependent (PMD) Layer Specification, Jan. 2003, ITU-T Recommendation G.984.2.

- [6] Media Access Control Parameters, Physical Layers and Management Parameters for Subscriber Access Networks, Jun. 2003. IEEE Draft P802.3ah.

- [7] S. Han and M.-S. Lee, "AC-coupled burst-mode optical receiver employing 8B/10B coding," *Electron. Lett.*, vol. 39, no. 21, pp. 1527–1528, Oct. 2003.

- [8] J.-W. Kwon, J.-H. Lee, J.-M. Baek, J.-C. Cho, J.-W. Seo, S.-S. Park, J.-K. Lmee, Y.-K. Oh, and D.-H. Jang, "AC-coupled burst-mode OLT SFP transceiver for gigabit Ethernet PON systems," *IEEE Photon. Technol. Lett.*, vol. 17, no. 7, pp. 1519–1521, Jul. 2005.

- [9] S. Vatannia, P. H. Yeung, and C. Lu, "A fast response 155-Mb/s burstmode optical receiver for PON," *IEEE Photon. Technol. Lett*, vol. 17, no. 5, pp. 1067–1069, May 2005.

- [10] P. Ossieur, D. Verhulst, Y. Martens, W. Chen, J. Bauwelinck, X. Z. Qiu, and J. Vandewege, "A 1.25-Gb/s burst-mode receiver for GPON applications," *IEEE J. Solid-State Circuits*, vol. 40, no. 5, pp. 1180–1189, May 2005.

- [11] K. Nishimura, H. Kimura, M. Watanabe, T. Nagai, K. Nojima, K. Gomyo, M. Takata, M. Iwamoto, and H. Asano, "A 1.25-Gb/s CMOS

burst-mode optical transceiver for Ethernet PON system," *IEEE J. Solid-State Circuits*, vol. 40, no. 4, pp. 1027–1034, Apr. 2005.

- [12] X. Z. Qiu, P. Ossieur, J. Bauwelinck, Y. C. Yi, D. Verhulst, J. Vandewege *et al.*, "Development of GPON upstream physical media dependent prototypes, *J. Lightw. Technol.*, vol. 22, no. 11, pp. 2498–2508, Nov. 2004.

- [13] P. Ossieur, X. Z. Qiu, and J. Vandewege, "Analysis of optimum avalanche gain of burst-mode receivers for PON applications," *IEEE Photon. Technol. Lett.*, vol. 17, no. 4, pp. 884–886, Apr. 2005.

- [14] Y. Park, C. Lim, and J. Lung, "ONU power equalization of Ethernet PON systems," *IEEE Photon. Technol. Lett*, vol. 16, no. 8, pp. 1984–1986, Aug. 2004.

- [15] E. Rotem and D. Sadot, "Performance analysis of ac-coupled burst-mode receiver for fiber-optic burst switching networks," *IEEE Trans. Commun.*, vol. 53, no. 5, pp. 899–904, May 2005.

- [16] C. A. Eldering, "Theoretical determination of sensitivity penalty for burst mode fiber optic receivers," J. Lightw. Technol., vol. 11, no. 12, pp. 2145–2149, Dec. 1993.

- [17] P. Menéndez-Valdés, "Performance of optical direct receivers using noise corrupted decision threshold," J. Lightw. Technol., vol. 13, no. 11, pp. 2202–2214, Nov. 1995.

- [18] C. Su, L.-K. Chen, and K. W. Cheung, "Theory of burst-mode receiver and its applications in optical multiaccess networks," J. Lightw. Technol., vol. 15, no. 4, pp. 590–606, Apr. 1997.

- [19] P. Ossieur, X. Z. Qiu, J. Bauwelinck, and J. Vandewege, "Sensitivity penalty calculation for burst-mode receivers using avalanche photodiodes," *J. Lightw. Technol.*, vol. 21, no. 11, pp. 2565–2575, Nov. 2003.

- [20] M. J. M. Pelgrom, A. C. J. Duinmaijer, and A. P. G. Welbers, "Matching properties of MOS transistors," *IEEE J. Solid-State Circuits*, vol. 24, no. 5, pp. 1433–1439, Oct. 1989.

- [21] J. Conradi, "A simplified non-gaussian approach to digital optical receiver design with avalanche photodiodes: Theory," J. Lightw. Technol., vol. 9, no. 8, pp. 1019–1026, Aug. 1991.

- [22] K. Uyttenhove and M. S. J. Steyaert, "Speed-power-accuracy tradeoff in high-speed CMOS ADCs," *IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process.*, vol. 49, no. 4, pp. 280–287, Apr. 2002.

- [23] P. R. Kinget, "Device mismatch and tradeoffs in the design of analog circuits," *IEEE J. Solid-State Circuits*, vol. 40, no. 6, pp. 1212–1224, Jun. 2005.

- [24] M. Pelgrom, J. van Rens, M. Vertregt, and M. Dijkstra, "A 25-Mb/s 8-bit CMOS A/D converter for embedded applications," *IEEE J. Solid-State Circuits*, vol. 29, no. 8, pp. 879–885, Aug. 1994.

- [25] J. Bastos, A. Marques, M. Steyaert, and W. Sansen, "A 12-bit intrinsic accuracy high-speed CMOS DAC," *IEEE J. Solid-State Circuits*, vol. 33, no. 12, pp. 1959–1969, Dec. 1998.

- [26] P. R. Kinget, "Device mismatch and tradeoffs in the design of analog circuits," *IEEE J. Solid-State Circuits*, vol. 40, no. 6, pp. 1212–1224, Jun. 2005.

- [27] R. Dogliotti, A. Luvison, and G. Pirani, "Error probability in optical fiber transmission systems," *IEEE Trans. Inf. Theory*, vol. IT-25, no. 2, pp. 170–179, Mar. 1979.

- [28] J. Conradi, "A simplified non-Gaussian approach to digital optical receiver design with avalanche photodiodes: Theory," J. Lightw. Technol., vol. 9, no. 8, pp. 1019–1026, Aug. 1991.

**Peter Ossieur** (S'02–M'06) was born in Brugge, Belgium, in 1977. He received the M.S. degree in electrical engineering (micro- and optoelectronics) and the Ph.D. degree in applied sciences and electronics from Ghent University, Ghent, Belgium, in 2000 and 2005, respectively.

He has been a Research Assistant in the INTEC\_ design laboratory since 2000. His research is focused on analog integrated circuits for burst-mode laser drivers and receivers in passive optical network (PON) telecommunication systems and modeling of burst-mode communication.

**Tine De Ridder** (S'05) was born in Knokke-Heist, Belgium, in 1982. She received the M.S. degree in electrical engineering (micro- and optoelectronics) from Ghent University, Ghent, Belgium, in 2004. She is currently working toward the Ph.D. degree in applied sciences and electronics at the INTEC\_design laboratory, which she joined in 2004.

Her research is focused on the various aspects of the design of high-performance receiver front-end circuitry for both automotive and telecom applications such as passive optical networks (PONs).

**Xing-Zhi Qiu** (M'03) received the Ph.D. degree in electronics engineering from Ghent University, Ghent, Belgium, in 1993.

Since 1986, she has been with the INTEC\_design laboratory. She is currently managing high-speed mixed analog/digital chip and subsystem design. She accumulated 16 years of R&D experience in the field of hardware design for the physical layer, mostly developing advanced telecommunication systems and optical access network demonstrators. She is the author/coauthor of 70 international publications.

**Jan Vandewege** (M'96) was born in Ghent, Belgium, in 1949. He received the M.S. and Ph.D. degrees in electronics engineering from Ghent University, Ghent, Belgium, in 1972 and 1978, respectively.

In 1985, he founded the INTEC\_design laboratory to train Ph.D.-level electronic engineers in the design of telecom and radio frequency (RF) hardware and embedded software. He (co)authored 134 international publications and ten international patents in the field of telecommunication.