Aansturing van modulatoren met meerdere kanalen aan hoge snelheid en laag vermogenverbruik voor middellange optische verbindingen

High-Speed Low-Power Modulator Driver Arrays for Medium-Reach Optical Networks

Renato Vaernewyck

Promotoren: prof. dr. ir. J. Bauwelinck, prof. dr. ir. X. Yin Proefschrift ingediend tot het behalen van de graad van Doctor in de Ingenieurswetenschappen: Elektrotechniek

Vakgroep Informatietechnologie Voorzitter: prof. dr. ir. D. De Zutter Faculteit Ingenieurswetenschappen en Architectuur Academiejaar 2014 - 2015

ISBN 978-90-8578-746-4 NUR 959 Wettelijk depot: D/2014/10.500/92

Universiteit Gent Faculteit Ingenieurswetenschappen en Architectuur Vakgroep Informatietechnologie

Aansturing van modulatoren met meerdere kanalen aan hoge snelheid en laag vermogenverbruik voor middellange optische verbindingen

High-Speed Low-Power Modulator Driver Arrays for Medium-Reach Optical Networks

Renato Vaernewyck

Proefschrift tot het bekomen van de graad van Doctor in de Ingenieurswetenschappen: Elektrotechniek Academiejaar 2014-2015

Universiteit Gent Faculteit Ingenieurswetenschappen en Architectuur Vakgroep Informatietechnologie

Promotor: Prof. Dr. Ir. Johan Bauwelinck Prof. Dr. Ir. Xin Yin

Universiteit Gent Faculteit Ingenieurswetenschappen en Architectuur

Vakgroep Informatietechnologie Sint-Pietersnieuwstraat 41, B-9000 Gent, België

Tel.: +32-9-264.33.46 Fax.: +32-9-264.35.93

Proefschrift tot het behalen van de graad van Doctor in de Ingenieurswetenschappen: Elektrotechniek Academiejaar 2014-2015

#### Dankwoord

Elk onderzoek steunt op het harde werk van de onderzoeker, maar de inbreng en aanmoedigingen van anderen is onontbeerlijk in het bereiken van het uiteindelijke doel. Dit proefschrift kwam tot stand binnen de vakgroep Informatietechnologie van de Universiteit Gent. Het is het resultaat van 4 jaar onderzoek als medewerker in het labo INTEC Design en kon onmogelijk verwezenlijkt worden zonder de hulp van de volgende mensen, die ik dan ook hartelijk wens te bedanken. In eerste instantie wil ik de vakgroepvoorzitter prof. dr. ir. Daniël De Zutter bedanken voor de aangeboden faciliteiten en voor de verzorgde omkadering die me toelieten mijn onderzoek tot een goed einde te brengen.

Daarnaast wil ik ook het hoofd van de onderzoeksgroep INTEC Design, prof. dr. ir. Jan Vandewege, danken voor de geboden kansen. Ook prof. dr. ir. Xing-Zhi Qiu verdient een woord van dank voor het aanleggen en onderhouden van de vele contacten met de technologische industrie en het nauwkeurig nalezen en verbeteren van deze thesis. Beiden wil ik dan ook het beste toewensen in het leven na hun pensioen.

Mijn bijzondere dank gaat uit naar mijn promotoren, prof. dr. ir. Johan Bauwelinck en prof. dr. ir. Xin Yin. Ze wisten steeds tijd te maken voor een deskundige begeleiding, hulp bij het projectwerk en het nalezen van dit werk.

Verder ben ik ing. Jan Gillis dankbaar voor de technologische ondersteuning en vele tips. Ook Mike Van Puyenbroeck wil ik vermelden voor zijn onmisbare administratieve hulp.

Voorts wil ik mijn collega's en ex-collega's bedanken voor de aangename samenwerking en de plezierige ontspanningsmomenten. Dr. ir. Zhisheng Li wil ik dank betuigen voor zijn uitgebreide hulp bij mijn eerste tape-out. Mijn jaargenoten Arno, Ramses en Timothy wil ik in het bijzonder danken. Niet alleen gaven ze mij een fantastische barbeque, we beleefden ook veel plezante tijden tijdens de vele 'glee-avonden'.

Ik wil ook Deborah bedanken voor haar steun tijdens de jaren van hard labeur. Ten slotte dank ik mijn ouders omdat ze mij de mogelijkheden boden mij in de wetenschap te verdiepen, wat uiteindelijk heeft geleid tot dit werk.

Gent, november 2014

Renato Vaernewyck

## Table of Contents

| Dankwoord i |         |                                                   |       |

|-------------|---------|---------------------------------------------------|-------|

| Ne          | ederla  | andstalige samenvatting                           | xxiii |

| Eı          | ıglish  | summary                                           | xxvii |

| Li          | st of j | publications                                      | xxxi  |

| 1           | Intr    | oduction                                          | 1     |

|             | 1.1     | ICT infrastructure and power consumption          | 1     |

|             | 1.2     | Passive Optical Network                           | 4     |

|             | 1.3     | Data centers                                      | 12    |

|             | 1.4     | Overview of the work                              | 13    |

|             | 1.5     | Outline of the dissertation                       | 15    |

| 2           | Opt     | ical transmitters                                 | 23    |

|             | 2.1     | Introduction                                      | 23    |

|             | 2.2     | Optical light sources                             | 23    |

|             | 2.3     | Direct modulation of a semiconductor light source | 28    |

|             | 2.4     | External modulation                               | 30    |

|             |         | 2.4.1 Electro-optic modulator                     | 30    |

|             |         | 2.4.2 Electroabsorption modulator                 | 34    |

|             | 2.5     | Conclusion                                        | 37    |

| 3           | Moo     | dulator driver topologies and power consumption   | 43    |

|             | 3.1     | Modulator driver circuit                          | 43    |

|             |         | 3.1.1 Output stage                                | 43    |

|             |         | 3.1.2 Back termination                            | 45    |

|             |         | 3.1.3 Bandwidth and parasitics                    | 46    |

|             |         | 3.1.4 Predriver                                   | 46    |

|             |         | 3.1.5 Pulse width control                         | 48    |

|   |      | 8                                                     | 48 |

|---|------|-------------------------------------------------------|----|

|   |      | 1                                                     | 50 |

|   | 3.2  |                                                       | 50 |

|   |      |                                                       | 51 |

|   |      |                                                       | 55 |

|   |      | 1 1                                                   | 57 |

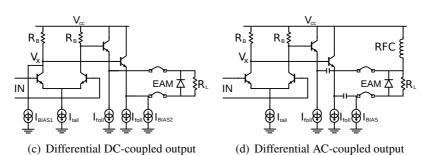

|   |      | 3.2.4 Differential AC-coupled output                  | 60 |

|   |      |                                                       | 61 |

|   | 3.3  | Comparison                                            | 64 |

|   | 3.4  | Conclusion                                            | 66 |

| 4 | 10 c | hannel 11.3 Gb/s/ch low power EAM driver array        | 71 |

|   | 4.1  | Introduction                                          | 71 |

|   | 4.2  | Specifications                                        | 72 |

|   | 4.3  | Technology                                            | 72 |

|   | 4.4  | Driver array architecture                             | 74 |

|   | 4.5  | Predriver stage                                       | 75 |

|   | 4.6  | Current steering driver stage                         | 78 |

|   |      | 4.6.1 Model of the EAM combined with the interconnect | 78 |

|   |      | 4.6.2 Design of the driver stage                      | 79 |

|   |      |                                                       | 81 |

|   | 4.7  |                                                       | 82 |

|   |      | 4.7.1 Chip layout and pinout                          | 82 |

|   |      | 4.7.2 Prototyping of the 10-channel 11.3 Gb/s/ch EAM  |    |

|   |      | driver array                                          | 84 |

|   | 4.8  | 1                                                     | 87 |

|   |      | 1                                                     | 87 |

|   |      | 1                                                     | 87 |

|   |      |                                                       | 90 |

|   |      |                                                       | 91 |

|   | 4.9  | Conclusion                                            | 95 |

| 5 |      |                                                       | 01 |

|   | 5.1  |                                                       | 01 |

|   | 5.2  |                                                       | 02 |

|   | 5.3  |                                                       | 05 |

|   | 5.4  | 1 5                                                   | 07 |

|   | 5.5  |                                                       | 09 |

|   | 5.6  | 1                                                     | 11 |

|   |      | 5.6.1 Precoder implementation                         | 11 |

iv

|   |       | 5.6.2 Encoder implementation                                | 115 |

|---|-------|-------------------------------------------------------------|-----|

|   | 5.7   | Circuits                                                    | 116 |

|   | 5.8   | Conclusion                                                  | 118 |

| 6 | Dual  | channel 28 Gb/s/ch low power optical duobinary EAM          | [   |

|   | drive | er array                                                    | 123 |

|   | 6.1   | Introduction                                                | 123 |

|   | 6.2   | Specifications                                              | 123 |

|   | 6.3   | Driver array architecture                                   | 125 |

|   |       | 6.3.1 Duobinary precoding and encoding                      | 125 |

|   |       | 6.3.2 Top level architecture                                | 126 |

|   | 6.4   | Predriver stage                                             | 127 |

|   | 6.5   | Current steering driver stage                               | 129 |

|   |       | 6.5.1 Model of the EAM combined with the interconnect       | 129 |

|   |       | 6.5.2 Design of the driver stage                            | 130 |

|   | 6.6   | Realization of the dual channel 28 Gb/s/ch EAM driver array | 131 |

|   |       | 6.6.1 Chip layout and pinout                                | 131 |

|   |       | 6.6.2 Prototyping of the 2-channel 28 Gb/s/ch EAM driver    |     |

|   |       | array                                                       | 131 |

|   | 6.7   | Experimental test results                                   | 135 |

|   |       | 6.7.1 Validation of the test setup                          | 135 |

|   |       | 6.7.2 Electrical experiments                                | 136 |

|   | 6.8   | Second generation 2-channel 28 Gb/s/ch EAM driver array     | 136 |

|   |       | 6.8.1 Architecture changes                                  | 137 |

|   |       | 6.8.2 Circuit changes                                       | 137 |

|   | 6.9   | Realization of the second generation 2-channel 28 Gb/s/ch   |     |

|   |       | EAM driver array                                            | 138 |

|   |       | 6.9.1 Chip layout and pinout                                | 138 |

|   | 6.10  | Second generation experimental test results                 | 139 |

|   |       | 6.10.1 Electrical experiments                               | 140 |

|   |       | 6.10.2 Optical experiments using a commercial component     |     |

|   | 6.11  | Conclusion                                                  | 144 |

| 7 | Cone  | clusion                                                     | 149 |

|   | 7.1   | Summary of the results                                      | 149 |

|   | 7.2   | Further research                                            | 151 |

v

## List of Figures

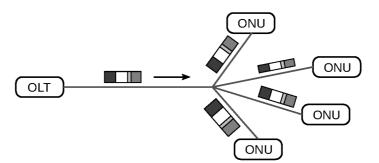

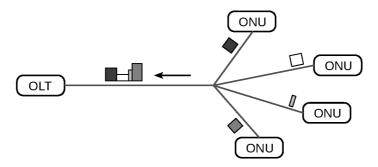

| 1.1  | Geographical overview of the network tiers                     | 4  |

|------|----------------------------------------------------------------|----|

| 1.2  | Performance characteristics of ADSL, ADSL2+, VDSL1             | _  |

|      | and VDSL2 [7, 8]                                               | 5  |

| 1.3  | Schematical representation of TDM-PON downstream trans-        | _  |

|      | mission                                                        | 7  |

| 1.4  | Schematical representation of TDM-PON upstream trans-          | -  |

|      | mission                                                        | 7  |

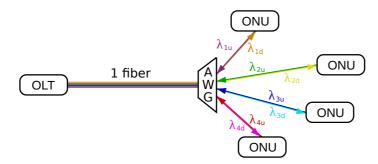

| 1.5  | Schematical representation of WDM-PON                          | 9  |

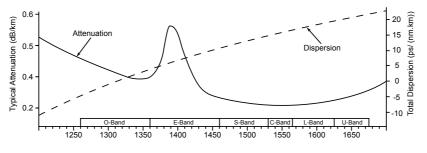

| 1.6  | Attenuation and dispersion in SMF [5, 6]                       | 10 |

| 1.7  | WDM-PON envisioned by C3PO project                             | 14 |

| 2.1  | Fundamental emission processes: (a) spontaneous emis-          |    |

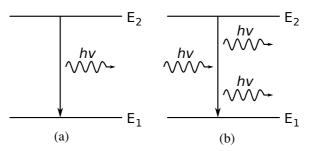

|      | sion (b) stimulated emission                                   | 24 |

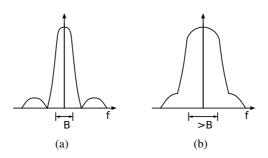

| 2.2  | Optical transmitter spectrum of NRZ: (a) ideally vs. (b)       |    |

|      | chirped                                                        | 26 |

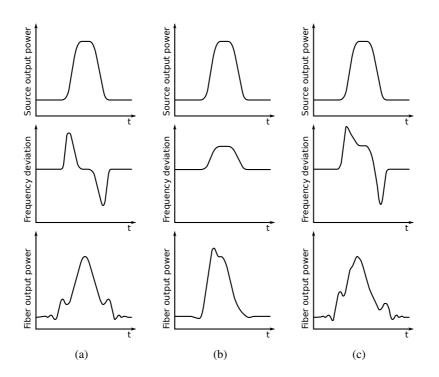

| 2.3  | Illustration of chirp-dispersion induced pulse distortion: (a) |    |

|      | transient, (b) adiabatic, (c) both chirp components            | 27 |

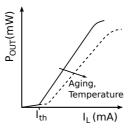

| 2.4  | LED light output power vs. drive current                       | 29 |

| 2.5  | Laser diode light output power vs. drive current               | 29 |

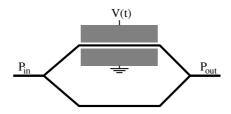

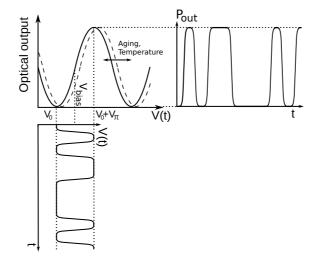

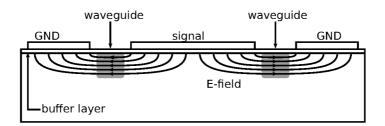

| 2.6  | MZM with electro-optic material in one arm                     | 31 |

| 2.7  | MZM transfer function and output as a function of drive        |    |

|      | voltage                                                        | 32 |

| 2.8  | X-cut MZM                                                      | 33 |

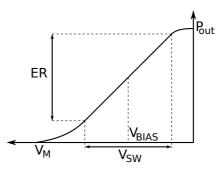

| 2.9  | Typical EAM switching characteristics with ER, voltage         |    |

|      | swing and bias voltage indicated                               | 35 |

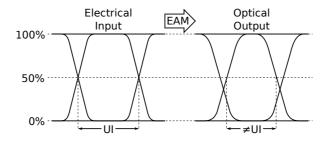

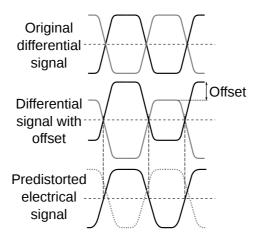

| 2.10 | Example of PWD                                                 | 36 |

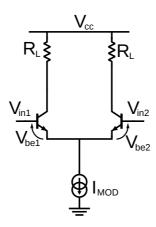

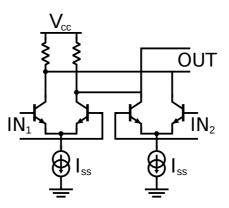

| 3.1  | BJT current steering circuit or differential pair              | 44 |

| 3.2  | A simple predriver circuit                                     | 47 |

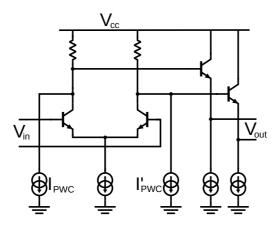

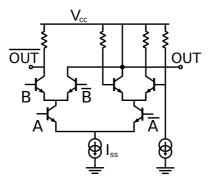

| 3.3  | Operation of PWC                                               | 48 |

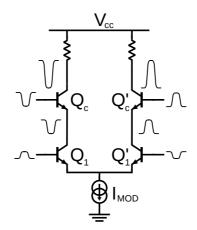

| 3.4  | Breakdown doubler technique                                    | 49 |

| 2    |                                                                | ., |

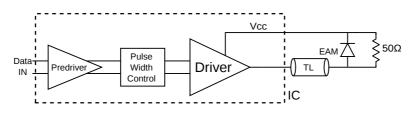

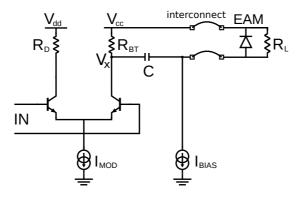

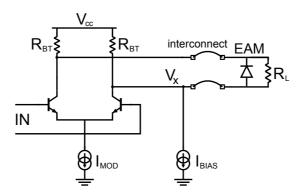

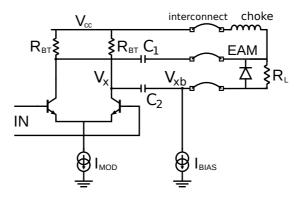

| 3.5  | Simple EAM driver IC top level block diagram                                                                                                | 50 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------|----|

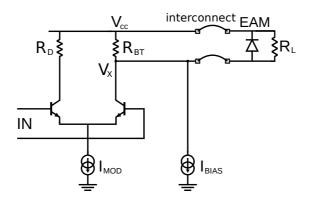

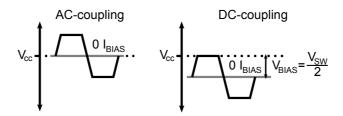

| 3.6  | Typical configuration with a single ended DC-coupled output                                                                                 | 52 |

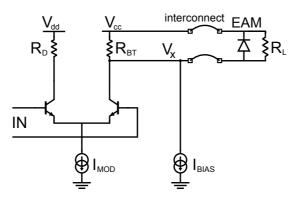

| 3.7  | Typical configuration with a second supply for a single ended                                                                               |    |

|      | DC-coupled output                                                                                                                           | 53 |

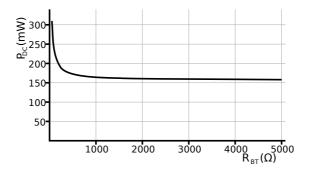

| 3.8  | Power consumption in function of $R_{BT}$ in a configuration                                                                                |    |

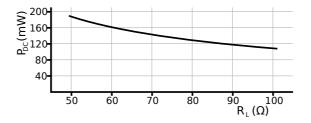

|      | with a single ended DC-coupled output $(R_L = 50 \ \Omega)$                                                                                 | 54 |

| 3.9  | Power consumption in function of $R_L$ for a configuration                                                                                  |    |

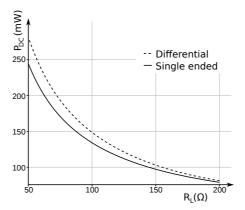

|      | with a single ended DC-coupled output $(R_{BT} = 250 \ \Omega)$ .                                                                           | 54 |

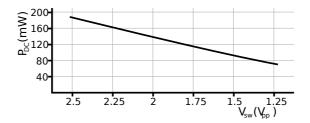

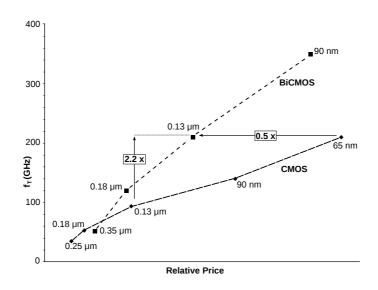

| 3.10 | Power consumption in function of $V_{SW}$ for a configuration                                                                               |    |

|      | with a single ended DC-coupled output ( $R_{BT} = 250 \ \Omega, R_L$                                                                        |    |

|      | $= 50 \Omega) \qquad \dots \qquad $ | 55 |

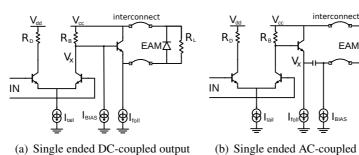

| 3.11 | Typical configuration with a second supply and a single                                                                                     |    |

|      | ended AC-coupled output                                                                                                                     | 55 |

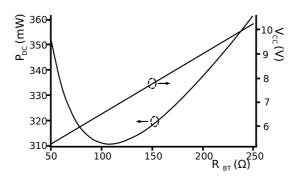

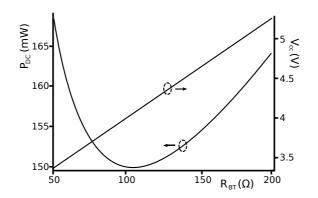

| 3.12 | Power consumption and $V_{cc}$ in function of $R_{BT}$ for a con-                                                                           |    |

|      | figuration with a single ended AC-coupled output ( $R_L = 50$                                                                               |    |

|      | $\begin{array}{c} \Omega \\ \Omega \end{array} $                                                                                            | 57 |

| 3.13 | $V_{BIAS}$ with $I_{BIAS} = 0$ mA for AC- and DC-coupled output                                                                             | 57 |

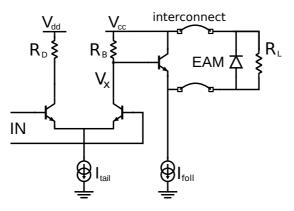

|      | Typical configuration with a differential DC-coupled output                                                                                 | 58 |

|      | Power consumption and $V_{cc}$ in function of $R_{BT}$ for a con-                                                                           |    |

|      | figuration with a differential DC-coupled output ( $R_L = 100$                                                                              |    |

|      | $\Omega)  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                                  | 59 |

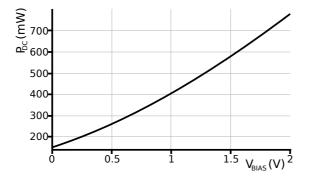

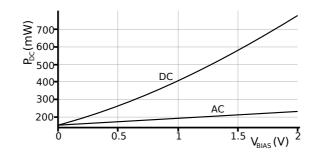

| 3.16 | Power consumption in function of $V_{BIAS}$ for a configura-                                                                                |    |

|      | tion with a differential DC-coupled output ( $R_L = 100 \ \Omega$ ,                                                                         |    |

|      | $R_{BT} = 100 \ \Omega) \dots $       | 59 |

| 3.17 | Typical configuration with a differential AC-coupled output                                                                                 | 60 |

|      | Comparison between AC- and DC-coupled differential con-                                                                                     |    |

|      | figuration of the power consumption in function of $V_{BIAS}$                                                                               | 61 |

| 3.19 | Simple driver circuit with active back termination                                                                                          | 61 |

|      | Different possibilities for the active back termination topol-                                                                              |    |

|      | Ogy                                                                                                                                         | 63 |

| 3.21 | AC-coupled active back termination comparison between                                                                                       | 00 |

| 0.21 | single ended and differential output                                                                                                        | 64 |

| 3 22 | Comparison between single ended DC-coupled output and                                                                                       | 0. |

| 0.22 | differential AC-coupled output for different $V_{SW}$                                                                                       | 65 |

|      |                                                                                                                                             | 05 |

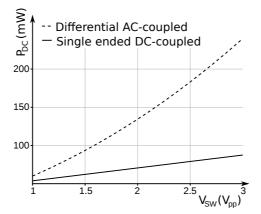

| 4.1  | Comparison of price vs. performance of BiCMOS and CMOS                                                                                      | 73 |

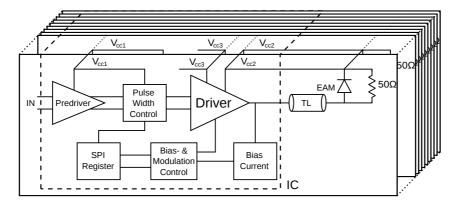

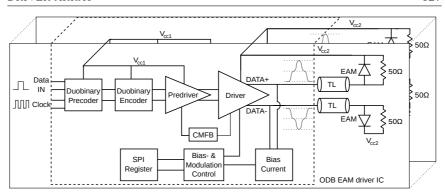

| 4.2  | EAM driver array IC top level block diagram                                                                                                 | 74 |

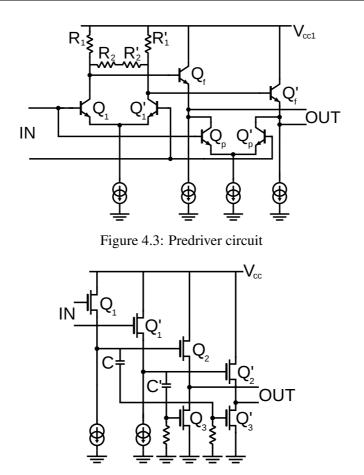

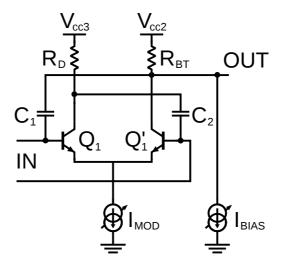

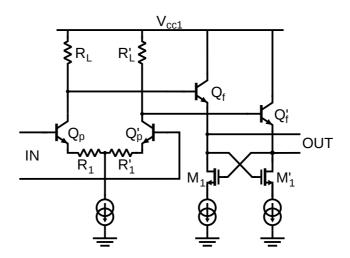

| 4.3  | Predriver circuit                                                                                                                           | 76 |

| 4.4  | Follower cascade with differential active source followers .                                                                                | 76 |

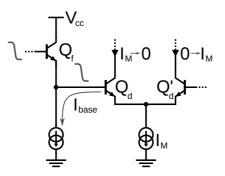

| 4.5  | Base current at falling edge                                                                                                                | 77 |

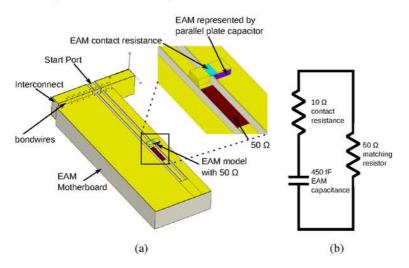

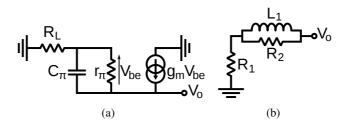

| 4.6        | CST model (a) of a hybrid assembly with (b) the EAM              |     |

|------------|------------------------------------------------------------------|-----|

|            | equivalent circuit                                               | 78  |

| 4.7        | Driver circuit                                                   | 79  |

| 4.8        | Bias current source made of a cascode mirror                     | 81  |

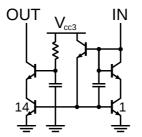

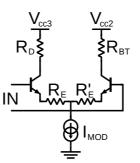

| 4.9        | Degenerated driver circuit                                       | 82  |

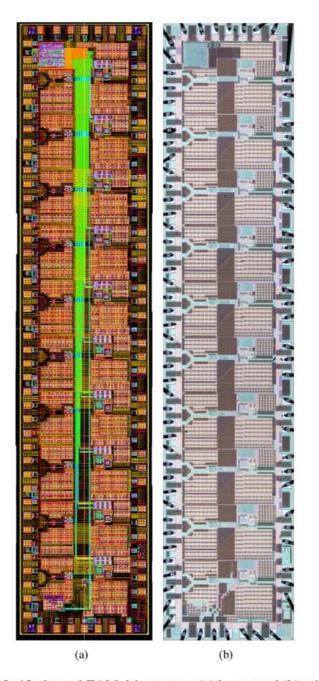

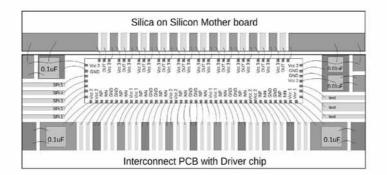

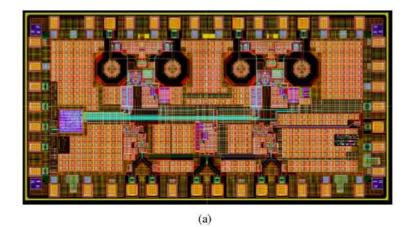

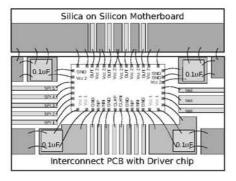

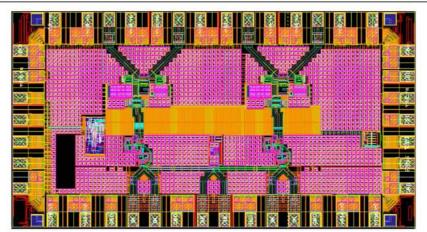

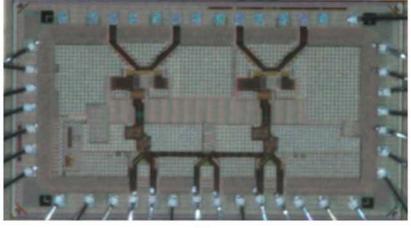

| 4.10       | 10-channel EAM driver array: (a) layout and (b) micrograph       | 83  |

|            | Pinout of the 10-channel EAM driver array with decoupling        | 84  |

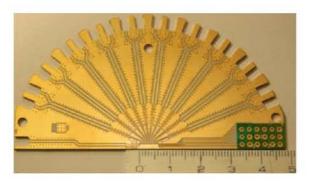

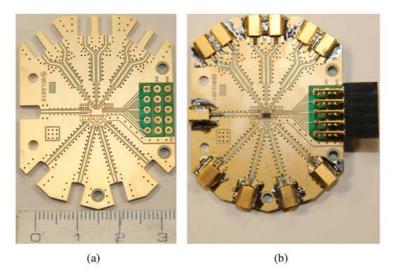

|            | Unassembled optical test PCB board                               | 85  |

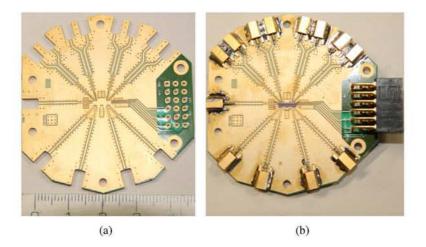

|            | 10-channel EAM driver array electric test board: (a) before      |     |

|            | assembly and (b) after assembly                                  | 85  |

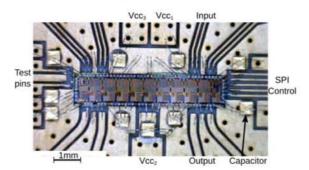

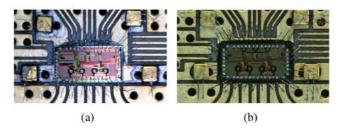

| 4.14       | Bonded die of the 10-channel EAM driver array                    | 85  |

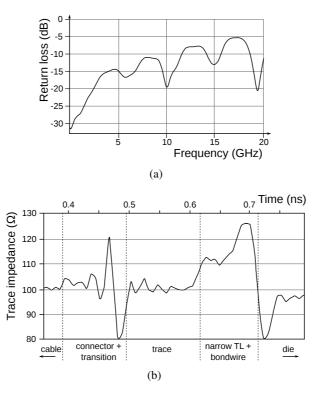

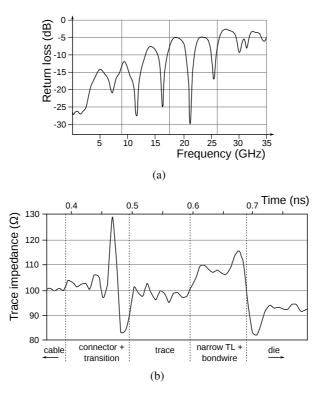

|            | Differential input transmission line measurement with a bonded   | ł   |

|            | die: (a) S11 (b) TDR                                             | 86  |

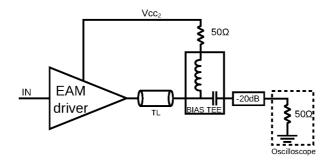

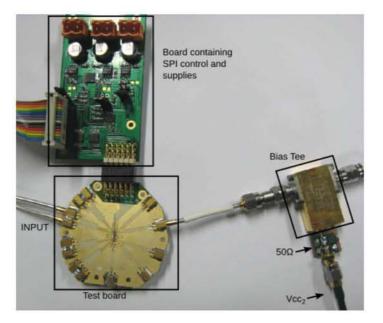

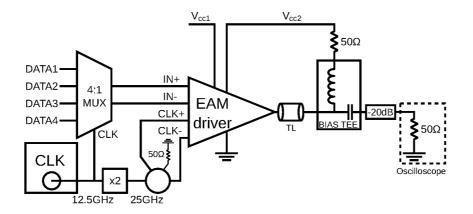

| 4.16       | Experimental setup for the electrical testing                    | 87  |

| 4.17       | Picture of the devices used in the test setup for the electrical |     |

|            | testing                                                          | 88  |

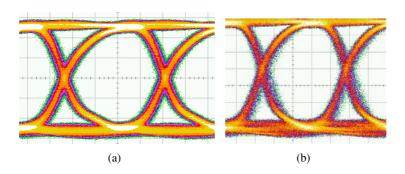

| 4.18       | Output signal at 11.3 Gb/s for a 2.5 $V_{pp}$ (a) output and a 3 |     |

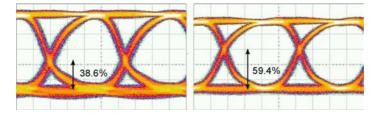

|            | $V_{pp}$ (b) (2 <sup>31</sup> -1 PRBS, 0.5 V/div, 20 ps/div)     | 89  |

| 4.19       | Pulse width control, (a) minimum, (b) maximum $(2^{31}-1)$       |     |

|            | PRBS, 0.5 V/div, 20 ps/div)                                      | 89  |

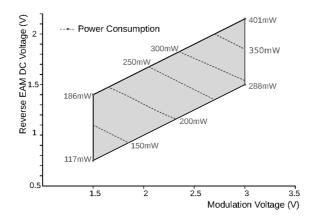

| 4.20       | Reach of the modulation and bias voltage with the corre-         |     |

|            | sponding power consumptions                                      | 90  |

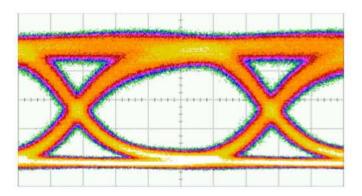

| 4.21       | Optical eye diagram at 10 Gb/s $(2^{31}-1 \text{ PRBS})$         | 91  |

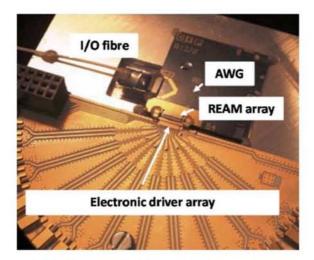

| 4.22       | Photograph of the optical transmitter assembly                   | 91  |

| 4.23       | Testbed at Tyndall National Institute for evaluating the in-     |     |

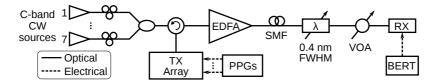

|            | tegrated transmitter array at 11.3 Gb/s                          | 92  |

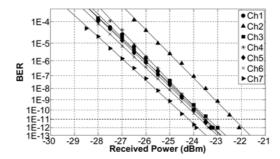

| 4.24       | BER as a function of received power for Ch1-7 in B2B             |     |

|            | single-channel operation                                         | 93  |

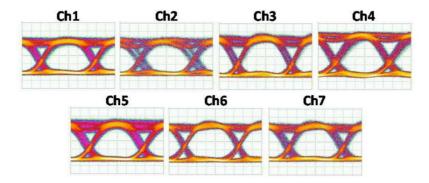

| 4.25       | 11.3 Gb/s optical eye diagrams for Ch 1-7 in B2B single-         |     |

|            | channel operation (15.2 ps/div)                                  | 93  |

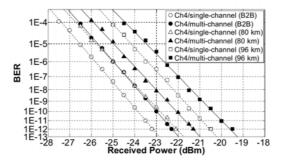

| 4.26       | BER as a function of received power for Ch4 in single- and       |     |

|            | multi-channel operation                                          | 94  |

| <b>-</b> 1 |                                                                  | 100 |

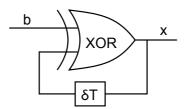

| 5.1        | 1 2                                                              | 103 |

| 5.2        | 1                                                                | 103 |

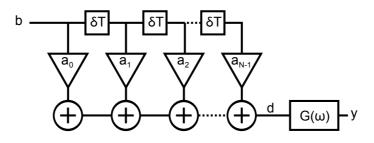

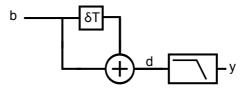

| 5.3        | Spectrum of a delay-and-add filter compared to a 5th order       | 104 |

| E 1        | 1 5                                                              | 104 |

| 5.4        | I E                                                              | 104 |

| 5.5        |                                                                  | 105 |

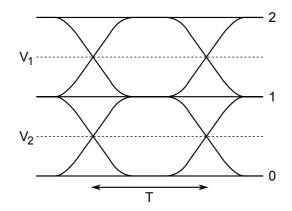

| 5.6        | Duobinary eye diagram with thresholds $V_1$ and $V_2$            | 106 |

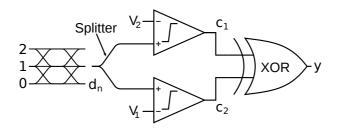

| 5.7                                                                                                                   | Schematic of duobinary to binary conversion               | 107                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

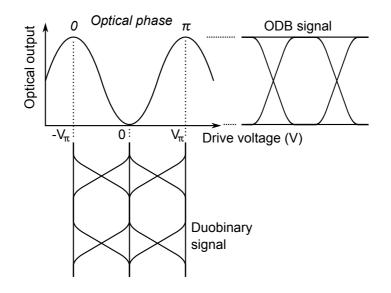

| 5.8                                                                                                                   | Conversion from electric DB into optical DB using an MZM  | 108                                                                                                   |

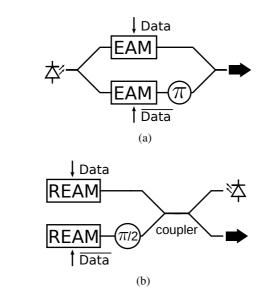

| 5.9                                                                                                                   | (a) EAMs in a MZ configuration and (b) REAMs in a Michel- |                                                                                                       |

|                                                                                                                       | son configuration                                         | 109                                                                                                   |

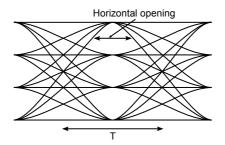

| 5.10                                                                                                                  | PAM4 eye diagram, with horizontal eye opening             | 110                                                                                                   |

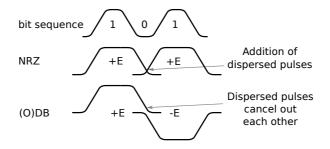

| 5.11                                                                                                                  | Effect of dispersion on NRZ and DB                        | 111                                                                                                   |

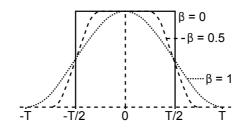

| 5.12                                                                                                                  | Raised cosine pulses with different roll-off $\beta$      | 111                                                                                                   |

| 5.13                                                                                                                  | Spectrum of NRZ and DB with a raised cosine pulse with    |                                                                                                       |

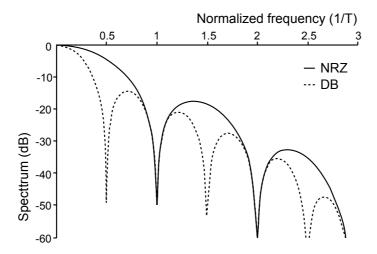

|                                                                                                                       | roll-off $\beta = 0.5$                                    | 112                                                                                                   |

| 5.14                                                                                                                  | Spectrum of NRZ and DB with a raised cosine pulse with    |                                                                                                       |

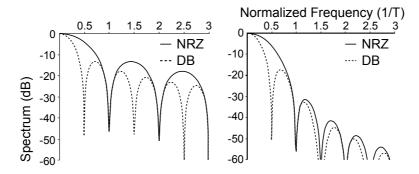

|                                                                                                                       | roll-off $\beta = 0$ (left) and $\beta = 1$ (right)       | 112                                                                                                   |

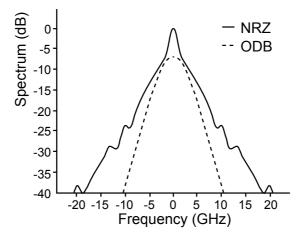

| 5.15                                                                                                                  | Optical spectrum of NRZ and ODB (10 Gb/s) [16]            | 113                                                                                                   |

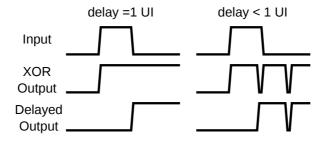

|                                                                                                                       | XOR-precoder output for exact and fast delay              | 113                                                                                                   |

|                                                                                                                       | · · ·                                                     | 114                                                                                                   |

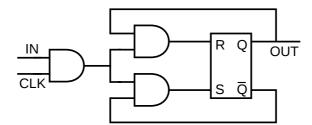

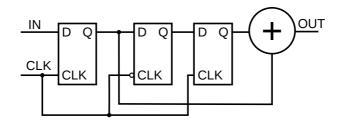

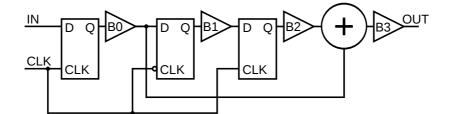

|                                                                                                                       | Frequency divider used as precoder                        | 115                                                                                                   |

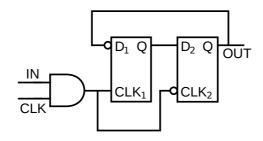

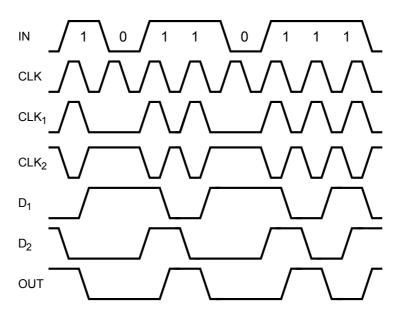

|                                                                                                                       | Frequency divider as precoder bit example                 | 115                                                                                                   |

|                                                                                                                       | Encoder with D-latches                                    | 116                                                                                                   |

| 5.21                                                                                                                  | Example of the simplicity of CML circuit transformation . | 117                                                                                                   |

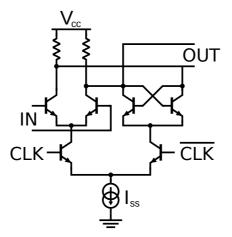

|                                                                                                                       | Conventional CML D-latch circuit                          | 117                                                                                                   |

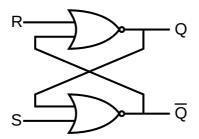

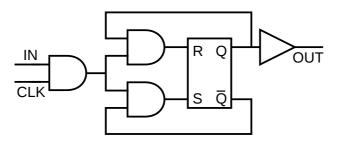

|                                                                                                                       | SR-latch buildup                                          | 118                                                                                                   |

|                                                                                                                       | -                                                         | 118                                                                                                   |

|                                                                                                                       |                                                           |                                                                                                       |

| 6.1                                                                                                                   | 1                                                         | 125                                                                                                   |

| 6.2                                                                                                                   | Implemented precoder as a T-flip-flop                     | 126                                                                                                   |

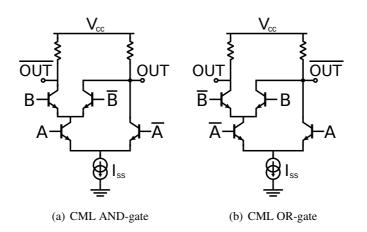

| 6.3                                                                                                                   | Implementation of the first AND-gate                      | 176                                                                                                   |

| 6.4                                                                                                                   |                                                           | 126                                                                                                   |

|                                                                                                                       | IC top level block diagram                                | 127                                                                                                   |

| 6.5                                                                                                                   | IC top level block diagram                                |                                                                                                       |

|                                                                                                                       | IC top level block diagram                                | 127<br>128                                                                                            |

| 6.5<br>6.6                                                                                                            | IC top level block diagram                                | 127<br>128<br>129                                                                                     |

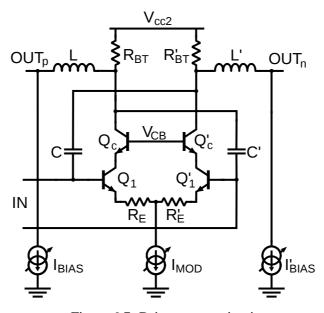

| 6.5<br>6.6<br>6.7                                                                                                     | IC top level block diagram                                | 127<br>128<br>129<br>130                                                                              |

| <ul><li>6.5</li><li>6.6</li><li>6.7</li><li>6.8</li></ul>                                                             | IC top level block diagram                                | 127<br>128<br>129<br>130<br>132                                                                       |

| 6.5<br>6.6<br>6.7                                                                                                     | IC top level block diagram                                | 127<br>128<br>129<br>130                                                                              |

| <ul><li>6.5</li><li>6.6</li><li>6.7</li><li>6.8</li></ul>                                                             | IC top level block diagram                                | 127<br>128<br>129<br>130<br>132<br>132                                                                |

| <ul><li>6.5</li><li>6.6</li><li>6.7</li><li>6.8</li><li>6.9</li></ul>                                                 | IC top level block diagram                                | 127<br>128<br>129<br>130<br>132                                                                       |

| <ul><li>6.5</li><li>6.6</li><li>6.7</li><li>6.8</li><li>6.9</li></ul>                                                 | IC top level block diagram                                | 127<br>128<br>129<br>130<br>132<br>132                                                                |

| <ul> <li>6.5</li> <li>6.6</li> <li>6.7</li> <li>6.8</li> <li>6.9</li> <li>6.10</li> <li>6.11</li> </ul>               | IC top level block diagram                                | <ul> <li>127</li> <li>128</li> <li>129</li> <li>130</li> <li>132</li> <li>133</li> <li>133</li> </ul> |

| <ul> <li>6.5</li> <li>6.6</li> <li>6.7</li> <li>6.8</li> <li>6.9</li> <li>6.10</li> <li>6.11</li> </ul>               | IC top level block diagram                                | <ul> <li>127</li> <li>128</li> <li>129</li> <li>130</li> <li>132</li> <li>133</li> <li>133</li> </ul> |

| <ul> <li>6.5</li> <li>6.6</li> <li>6.7</li> <li>6.8</li> <li>6.9</li> <li>6.10</li> <li>6.11</li> <li>6.12</li> </ul> | IC top level block diagram                                | <ul> <li>127</li> <li>128</li> <li>129</li> <li>130</li> <li>132</li> <li>133</li> <li>133</li> </ul> |

| <ul> <li>6.5</li> <li>6.6</li> <li>6.7</li> <li>6.8</li> <li>6.9</li> <li>6.10</li> <li>6.11</li> <li>6.12</li> </ul> | IC top level block diagram                                | 127<br>128<br>129<br>130<br>132<br>132<br>133<br>133<br>ed                                            |

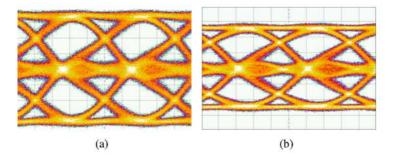

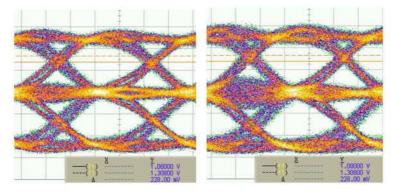

| 6.14 | Output signal at 25 Gb/s with a 4.2 $V_{pp}$ differential output (a) and a 3 $V_{pp}$ differential output (b) (2 <sup>31</sup> -1 PRBS, 0.6 V/- |     |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | div, 10 ps/div)                                                                                                                                 | 136 |

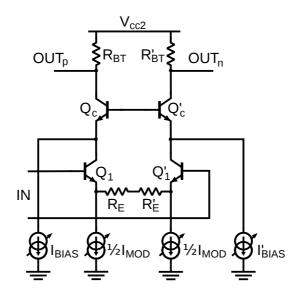

| 6.15 | Second generation driver circuit                                                                                                                | 138 |

| 6.16 | Second generation 2-channel driver array: (a) layout and                                                                                        |     |

|      | (b) micrograph                                                                                                                                  | 139 |

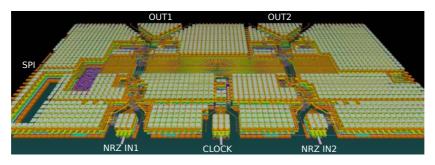

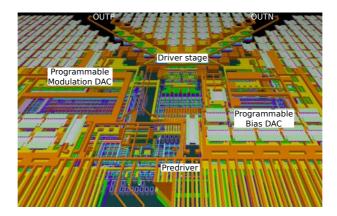

| 6.17 | 3D view of the chip layout                                                                                                                      | 140 |

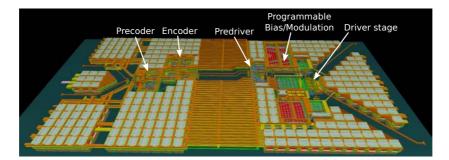

|      | Detailed layout of a single channel                                                                                                             | 140 |

| 6.19 | Detailed layout of the last stages                                                                                                              | 140 |

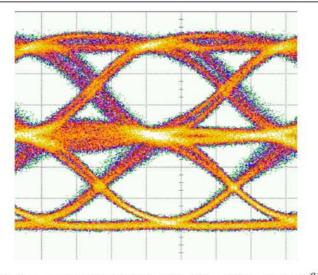

| 6.20 | Output signal at 28 Gb/s with 6 $V_{pp}$ differentially (2 <sup>31</sup> -1                                                                     |     |

|      | PRBS, 1 V/div, 10 ps/div)                                                                                                                       | 141 |

| 6.21 | Output signal with a 3 $V_{pp}$ differential output at 28 Gb/s (a)                                                                              |     |

|      | and at 21 Gb/s (b)( $2^{31}$ -1 PRBS, 0.6 V/div, 10 ps/div)                                                                                     | 142 |

| 6.22 | Crosspoint difference for an output of 4 $V_{pp}$ at 28 Gb/s (0.8                                                                               |     |

|      | V/div, 10 ps/div)                                                                                                                               | 142 |

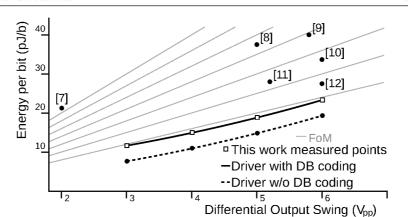

| 6.23 | Energy per bit and output swing comparison                                                                                                      | 143 |

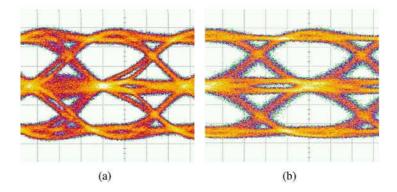

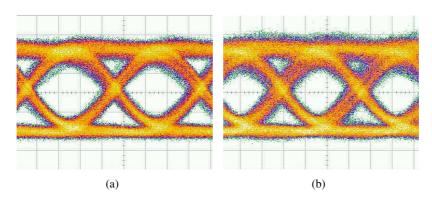

| 6.24 | Optically eye diagram $(2^{31}-1 \text{ PRBS}, 10 \text{ ps/div})$ .: (a) at 25                                                                 |     |

|      | Gb/s and (b) at 28 Gb/s                                                                                                                         | 145 |

xi

## List of Tables

| 1.1<br>1.2 | Advantages of optical fiberDifferent TDM-PON standards.    | 6<br>8 |

|------------|------------------------------------------------------------|--------|

| 4.1        | 10-channel 113 Gb/s EAM driver array chip level design     | 70     |

|            | specifications                                             | 72     |

| 4.2        | Power consumption comparison                               | 89     |

| - 1        |                                                            | 100    |

| 5.1        | Truth table for DB pre- and encoding                       | 106    |

| 5.2        | Truth table for decoding                                   | 107    |

| 5.3        | T-flip-flop truth table                                    | 114    |

| 6.1        | 2-channel 56 Gb/s EAM driver array chip level design spec- |        |

|            | ifications                                                 | 124    |

| 6.2        | Comparison state-of-the-art in low energy consumption      | 143    |

# List of Acronyms

#### A

| AC     | Alternating Current                     |

|--------|-----------------------------------------|

| ADSL   | Asymmetric Digital Subscriber Line      |

| AM     | Amplitude Modulation                    |

| AM-PSK | Amplitude Modulation Phase Shift Keying |

| ASE    | Amplified Spontaneous Emission          |

| ATM    | Asynchronous Transfer Mode              |

| AWG    | Arrayed Waveguide Grating               |

|        |                                         |

#### B

| B2B   | Back-To-Back                       |

|-------|------------------------------------|

| BER   | Bit Error Rate                     |

| BERT  | Bit-Error Rate Tester              |

| BJT   | <b>Bipolar Junction Transistor</b> |

| BPF   | Band Pass Filter                   |

| B-PON | Broadbrand Passive Optical Network |

|       |                                    |

## С

| CFP  | Centum Form-factor Pluggable |

|------|------------------------------|

| CM   | Common Mode                  |

| CMFB | Common Mode Feedback         |

| CML  | Current-Mode Logic                      |

|------|-----------------------------------------|

| CMOS | Complementary Metal Oxide Semiconductor |

| CO   | Central Office                          |

| CPON | Composite Passive Optical Network       |

| CW   | Continuous Wave                         |

| CWDM | Coarse Wavelength Division Multiplexing |

#### D

| DAF  | Delay-and-Add Filter                   |

|------|----------------------------------------|

| DB   | Duobinary                              |

| DBR  | Distributed Bragg Reflector            |

| DC   | Direct Current                         |

| DFB  | Distributed Feedback                   |

| DSF  | Dispersion Shifted Fibers              |

| DS   | Downstream                             |

| DSL  | Digital Subscriber Line                |

| DSP  | Digital Signal Processing              |

| DWDM | Dense Wavelength Division Multiplexing |

|      |                                        |

### E

| EAM  | Electro Absorption Modulator     |

|------|----------------------------------|

| ECL  | Emitter Coupled Logic            |

| EDFA | Erbium Doped Fiber Amplifier     |

| EML  | Electroabsoption Modulated Laser |

| EOM  | Electro Optic Modulator          |

| EPON | Ethernet Passive Optical Network |

| ER   | Extinction Ratio                 |

|      |                                  |

#### F

| FEC | Forward Error Correction  |

|-----|---------------------------|

| 120 | I of mara Biror Conteenon |

#### xvi

| FET  | Field Effect Transistor        |

|------|--------------------------------|

| FIR  | Finite Impulse Response        |

| FKE  | Franz-Keldysh Effect           |

| FoM  | Figure of Merit                |

| FP   | Fabry-Perot                    |

| FTTB | Fibre To The Business/Building |

| FTTC | Fibre To The Cabinet/Curb      |

| FTTH | Fiber To The Home              |

| FWHM | Full-Width Half-Maximum        |

## G

| Gb/s   | Gigabit per second                       |

|--------|------------------------------------------|

| GCPW   | Grounded Coplanar Waveguide              |

| GE-PON | Gigabit Ethernet Passive Optical Network |

| G-PON  | Gigabit-capable Passive Optical Network  |

### H

| HiCuM | High Current Model |

|-------|--------------------|

|       | U                  |

#### I

| IC   | Integrated Circuit                                |

|------|---------------------------------------------------|

| IEEE | Institute of Electrical and Electronics Engineers |

| IM   | Intensity Modulation                              |

| I/O  | Input/Output                                      |

| ISI  | Inter Symbol Interference                         |

| ISP  | Internet Service Provider                         |

| ITU  | International Telecommunications Union            |

#### xvii

| L                 |                                                                                    |

|-------------------|------------------------------------------------------------------------------------|

| LASER<br>LED      | Light Amplification by Stimulated Emission of<br>Radiation<br>Light Emitting Diode |

| LPF<br>M          | Low Pass Filter                                                                    |

|                   |                                                                                    |

| MEMS<br>MLM       | Micro-Electro-Mechanical Systems<br>Multiple-Longitudinal Mode                     |

| MQW<br>MZI        | Multi Quantum Well<br>Mach-Zehnder Interferometer                                  |

| MZM               | Mach-Zehnder Modulator                                                             |

| Ν                 |                                                                                    |

| NG-PON<br>NRZ-OOK | Next Generation Passive Optical Network<br>Non-Return-to-Zero On/Off Keying        |

| 0                 |                                                                                    |

| ODB               | Optical Duobinary                                                                  |

| OLT<br>ONU        | Optical Line Termination<br>Optical Network Unit                                   |

| OSNR              | Optical Signal-to-Noise Ratio                                                      |

#### P

| P2MP | Point-to-MultiPoint         |

|------|-----------------------------|

| P2P  | Point-to-Point              |

| PAM  | Pulse Amplitude Modulation  |

| PCB  | Printed Circuit Board       |

| PDU  | Power Distribution Unit     |

| PIC  | Photonic Integrated Circuit |

| PIN  | Positive-Intrinsic-Negative |

| PON  | Passive Optical Network     |

| PPG  | Pulse Pattern Generator     |

| PRBS | Pseudo Random Bit Sequence  |

| PRS  | Partial Response Signaling  |

| PSK  | Phase Shift Keying          |

| PWC  | Pulse Width Control         |

| PWD  | Pulse-Width Distortion      |

|      |                             |

## Q

| QCSE | Quantum Confined Stark Effect |

|------|-------------------------------|

| QW   | Quantum Well                  |

### R

| REAM    | Reflective Electro Absorption Modulator    |

|---------|--------------------------------------------|

| RF      | Radio Frequency                            |

| RFC     | Radio Frequency Choke                      |

| RITENET | Remote Interrogation of Terminal Network   |

| RN      | Remote Node                                |

| RSOA    | Reflective Semiconductor Optical Amplifier |

| RX      | Receiver                                   |

|         |                                            |

xix

### S

| SG-DBR | Sampled Grating Distributed Bragg Reflector |

|--------|---------------------------------------------|

| SLM    | Single-Longitudinal Mode                    |

| SMF    | Single Mode Fiber                           |

| SNR    | Signal-to-Noise Ratio                       |

| SOA    | Semiconductor Optical Amplifier             |

| SPI    | Serial Peripheral Interface                 |

| SS     | Spectral Slicing                            |

|        |                                             |

#### Т

| TDM  | Time Domain Multiplexing      |

|------|-------------------------------|

| TDMA | Time-Division Multiple Access |

| TDR  | Time Domain Reflectometry     |

| TEC  | Thermo-Electric Cooler        |

| TX   | Transmitter                   |

|      |                               |

#### U

| UI    | Unit Interval                                |

|-------|----------------------------------------------|

| UPS   | Uninterruptable Power Supply                 |

| US    | Upstream                                     |

| UDWDM | Ultra Dense Wavelength Division Multiplexing |

#### V

| VCSEL | Vertical Cavity Surface Emitting Laser    |

|-------|-------------------------------------------|

| VDSL  | Very-high-bitrate Digital Subscriber Line |

| VOA   | Variable Optical Attenuator               |

#### xx

W

WDM

Wavelength Division Multiplexing

xxi

### Nederlandstalige samenvatting –Dutch Summary–

Het internet is de dag van vandaag alomtegenwoordig en heeft het leven van vele burgers over de hele wereld veranderd. Handel, overheid, industrie, gezondheidszorg en sociale interacties gebruiken in toenemende mate internetapplicaties als een verbeterde en makkelijke manier van communiceren. Video applicaties zijn hier het grote voorbeeld van en vragen steeds grotere data snelheden en betere kwaliteit van de netwerken. Hogedefinitietelevisie (HDTV) diensten springen als paddenstoelen uit de grond en eisen nadrukkelijk een uitbouw van wijdverspreide netwerken met steeds grotere bandbreedtes.

De huidige passieve optische netwerken (PONs) gebruiken een enkele golflengte voor stroomafwaartse transmissie en een aparte golflengte voor stroomopwaartse transmissie. Door golflengtemultiplexering (WDM) in een PON toe te passen, kunnen veel grotere bandbreedtes in beide richtingen bereikt worden. Terwijl WDM technologieën al jaren worden gebruikt in lange-afstandsnetwerken, zijn ze slechts beperkt aanwezig in toegangsnetwerken. De hoge kost om complete WDM toegangsnetwerken uit te bouwen is de belangrijkste oorzaak hiervoor. Anderzijds kan het hedendaagse optische netwerk de capaciteit voor de toekomstige gebruikers niet bereiken op een kostenefficiënte manier. Bijgevolg is er een grote nood aan nieuwe WDM toegangscomponenten die zowel compact als kostenefficiënt zijn en in grote volumes kunnen geproduceerd worden.

Een toename van het aantal golflengtes voor WDM-PON leidt automatisch tot meerdere zend-ontvangers voor de verschillende golflengtekanalen, wat de totale fysische plaatsinname aanzienlijk vergroot. Fotonische integratie van zend-ontvangers tot een geïntegreerde reeks zou de kost en fysische plaatsinname gevoelig reduceren. Het totale vermogenverbruik van zo'n geïntegreerde reeks vormt echter een probleem. Om het gebruik van thermoëlektrische koeling te vermijden, is de integratiedichtheid van de componenten streng gelimiteerd door de warmteverspreiding van de componentverpakking. Bijgevolg vereist the WDM-PON visie een vermindering van het vermogenverbruik van de zend-ontvanger.

Dit betoog geeft duidelijk de voornaamste uitdagingen bij de realisatie van toekomstbestendige, optische (toegangs)netwerken weer. Zowel een inperking van de fysische plaatsinname, als een verlaging van de kosten en de reductie van het vermogenverbruik van de actieve componenten zijn problemen die moeten aangepakt worden.

In die zin zou een 100 Gb/s component, dat bestaat uit 10 kanalen aan 11.3 Gb/s per golflengtekanaal, een uitstekende bijdrage zijn bij de uitbreiding van de bandbreedte die klanten ter beschikking krijgen. Vooral optische zenders, die werken aan hoge snelheden, hebben een aanzienlijk vermogenverbruik. De hittegeneratie veroorzaakt door dit vermogenverbruik vormt een vervelende hindernis in de ontwikkeling van 10-kanaalszenders. Dit onderstreept nog eens het belang van het vermogenverbruik.

Naast de invoering van WDM in de toegangsnetwerken, zou een punt-totpunt connectie in datacenteromgevingen ook gebaat zijn met de WDM visie. Aangezien datacenteroperatoren dikwijls lijden aan een tekort aan optische vezels of hun vezelinfrastructuur niet zelf bezitten, zijn WDM technologieën essentieel om hun bereik en capaciteit uit te breiden. Interdatacentercommunicatie heeft ook baat bij kleine, kosten- en energie-efficiënte componenten die werken bij hoge snelheden om hun doorvoercapaciteit te maximaliseren. Bijgevolg zijn geïntegreerde 100 Gb/s zendontvangers, zoals 4 kanalen aan 28 Gb/s, uiterst gewenst.

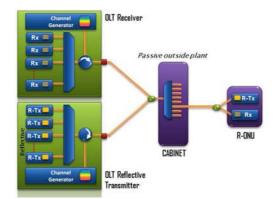

Het werk beschreven in deze thesis werd gedeeltelijk gefinancierd door het Europese FP7 project C3PO (Colourless and Coolerless Components for low Power Optical Networks) en door het UGent bijzonder onderzoeksfonds (BOF). Het C3PO project streefde naar de ontwikkeling van een nieuwe generatie 'groene' Si-fotonische compatibele componenten met een uiterst laag vermogenverbruik en terzelfdertijd wou men een toename in bandbreedte en een afname in kost bereiken. C3PO stelde zich de uitbouw van een toegangsnetwerk met grote capaciteit tot doel, gebruikmakend van reflecterende fotonische componenten. Om dit te bereiken, was het noodzakelijk om kostenefficiënte reflecterende zenders gebaseerd op electroabsorptie modulatoren (EAM) dicht bij elkaar te plaatsen in geïntegreerde reeksen. Een optische bron die meerdere golflengtes produceert voorziet de nodige golflengtekanalen, zowel voor de stroomafwaartse als voor de stroomopwaartse signalen in de WDM-PON. Hoofdstuk 1 geeft een kort overzicht van het PON-netwerk en beschrijft de voornaamste implementaties van een WDM-PON toegangsnetwerk. Het introduceert een geïntegreerde zenderreeks met een laag verbruik te gebruiken in een kostenefficiënte architectuur van WDM-PONs en inter-datacentercommunicatie.

Hoofdstuk 2 vergelijkt verschillende optische zenders en geeft een kort overzicht van hun belangrijkste karakteristieken. Externe modulatie met zowel Mach-Zehnder modulatoren (MZMs) als met EAMs wordt er beschreven. Er wordt aangetoond dat EAMs de beste keuze zijn voor geïntegreerde zender reeksen met laag vermogenverbruik, dankzij hun lage spanningszwaai en kleine afmetingen, in vergelijking met MZMs.

Om een laag verbruik te bereiken, wordt de elektronische driver topologie bestudeerd in hoofdstuk 3. De uitdaging in het ontwerpen van modulator drivers is de noodzaak om zeer grote stromen te leveren in combinatie met een hoge spanningszwaai. Vier verschillende uitgangsconfiguraties worden er vergeleken en technieken om het vermogenverbruik van de modulator drivers te verlagen worden beschreven.

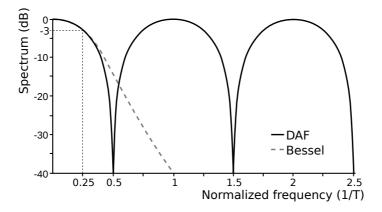

Hoofdstuk 5 beschrijft duobinair (DB), een modulatieschema dat steeds meer gebruikt wordt in de hedendaagse optische communicatie. Aangezien de nodige bandbreedte ongeveer de helft is van NRZ, kunnen de bandbreedtespecificaties van de zender gemilderd worden. Dankzij zijn smalle optische spectrum is DB bovendien minder gevoelig aan chromatische dispersie in lange-afstandsverbindingen en kan het de spectrale efficiëntie verhogen in WDM architecturen. Voor optische DB is er ook precodering nodig om te verzekeren dat het ontvangen signaal gelijk is aan het originele binaire signaal.

Het uitgevoerde onderzoek dat leidde tot deze thesis heeft 2 geïntegreerde modulator driver reeksen voortgebracht:

- Een 10 kanaals 113 Gb/s geïntegreerde modulator driver reeks met ultra-laag vermogenverbruik.

- Een 2 kanaals 56 Gb/s duobinair geïntegreerde modulator driver reeks met een differentiële uitgang.

Beide ontwerpen worden uitgebreid geanalyseerd in hoofdstuk 4 en 6 respectievelijk. Voor zover bekend is de 10 kanaals geïntegreerde modulator driver reeks de eerste in zijn soort, terwijl hij het laagste vermogenverbruik voor een EAM driver haalt, 50% lager dan voorheen gerapporteerd. De 2 kanaals geïntegreerde modulator driver reeks is de snelste modulator driver met op-chip DB encodering en precodering tot nu gerapporteerd.

Het laatste hoofdstuk geeft een overzicht van de belangrijkste conclusies van het gepresenteerde onderzoek en geeft een aantal suggesties voor toekomstig onderzoek.

#### English summary

The internet is becoming the ubiquitous tool that is changing the lives of so many citizens across the world. Commerce, government, industry, healthcare and social interactions are all increasingly using internet applications to improve and facilitate communications. This is especially true for videoenabled applications, which currently demand much higher data rates and quality from data networks. High definition TV streaming services are emerging and these again will significantly push the demand for widely deployed, high-bandwidth services.

The current access passive optical networks (PONs) use a single wavelength for downstream transmission and a separate one for upstream transmission. Incorporating wavelength-division multiplexing (WDM) in a PON allows for much higher bandwidths in both directions. While WDM technologies have been successfully deployed for many years in metro and core networks, in access networks they are not commonly used yet. This is mainly due to the high costs associated with deploying entire WDM access networks. However, the present optical networks cannot be simply and cost-effectively scaled to provide the capacity for tomorrow's users. As an effect there is a strong need for new WDM access components which are compact, cost-competitive and mass-manufacturable.

Increasing the number of wavelengths for WDM-PON automatically leads to an increase in the number of single pluggable transceivers, which brings substantial design challenges and additional costs. The multitude of TXs and RXs for different wavelength channels increases the total footprint considerably. Photonic integration of transceivers into arrays will significantly reduce the footprint and cost. However, the total power consumption of an array device is an issue. To avoid the use of a thermoelectric cooler, the integration density of components is severely limited by the heat dissipating capabilities offered by their package. As a result the WDM-PON philosophy necessitates the reduction of the transceiver's power dissipation.

From this plea it is apparent that the main technology challenges for real-

izing future-proof optical (access) networks are reducing active component power consumption, shrinking form factors and lowering assembly costs.

In this perspective an over 100 Gb/s throughput component, composed of 10 channels at 11.3 Gb/s per wavelength channel would be a great contribution to the expansion of customer bandwidth. It can provide increased line rates to the end users at speeds of 10 Gb/s per wavelength. As RXs typically consume much less power than externally modulated TXs, they can relatively easily be integrated into an array. Mainly high speed optical transmitters have significant power consumptions and the heat generation caused by power dissipation forms a critical obstacle in the development of a 10-channel transmitter, which again underlines the importance of power reduction.

Alongside the introduction of WDM in access networks, also inter-office point-to-point connections in data center environments could benefit from the WDM philosophy. As data center operators often suffer from fiber scarcity or do not own their fiber infrastructure, WDM technologies are essential to deliver reach and capacity extension for these scenarios. Inter-data center communication also benefits from cost-, footprint- and energy-efficient components operating at high speed to maximize the throughput. As an effect integrated over 100 Gb/s transceivers, such as 4 channels at 28 Gb/s, are highly desirable.

The research described in this dissertation was partly funded by the European FP7 ICT project C3PO (Colourless and Coolerless Components for low Power Optical Networks) and the UGent special research fund. The C3PO project aimed to develop a new generation of green Si-photonic compatible components with record low power consumption, that can enable bandwidth growth and constrain the total cost. C3PO envisioned building high-capacity access networks employing reflective photonic components. To achieve this, cost-competitive reflective transmitters based on electroabsorption modulators (EAM) needed to be closely integrated into arrays. A multi-wavelength optical source provides the required wavelength channels for both downstream and upstream signals in the WDM-PON.

Chapter 1 gives a short overview of a PON and describes the main implementations of a WDM-PON access network. It introduces integrated low power transmitter arrays for a cost-effective architecture of WDM-PONs and inter-data center communication.

Chapter 2 compares different optical transmitters and gives a short overview

of their most important characteristics. External modulation through both Mach-Zehnder modulators (MZMs) and EAMs is described. It shows that EAMs are the best choice for low power transmitter array integration, thanks to their lower drive voltage and smaller form factor, compared to MZMs.

To achieve a reduced consumption, the electronic modulator driver topology is studied in chapter 3. The challenge in designing modulator drivers is the need to deliver very large currents in combination with high voltage swings. Four distinct output configurations are compared and techniques to reduce the power consumption of the drivers are described.

Chapter 5 presents duobinary (DB), a modulation scheme that is gaining interest in today's optical transmission. As the required bandwidth is about half that of NRZ, it softens the constraints on the transmitter bandwidth. Thanks to its narrow optical spectrum, it has an improved tolerance to dispersion in long haul single mode links and it can improve the spectral efficiency in WDM architectures. For optical DB a precoder is necessary to assure the received signal is equal to the original binary signal.

The conducted research that resulted in this dissertation produced 2 low power EAM driver arrays:

- A 10-channel 113 Gb/s modulator driver array with state-of-the art ultra-low power consumption.

- A 2-channel 56 Gb/s duobinary driver array with a differential output with low power consumption.

Both designs are elaborately analyzed in chapter 4 and 6 respectively. To the best of our knowledge the 10-channel EAM driver array is the first in its kind, while achieving the lowest power consumption for an EAM driver so far reported, 50% below the state of the art in power consumption. The 2-channel EAM driver array is the fastest modulator driver including on-chip duobinary encoding and precoding reported so far.

The final chapter provides an overview of the foremost conclusions from the presented research. It is concluded with suggestions for further research.

## List of publications

#### **Publications in international journals**

- **R. Vaernewyck**, J. Bauwelinck, X. Yin, R. Pierco, J. Verbrugghe, G. Torfs, Z. Li, X.Z. Qiu, J. Vandewege, R. Cronin, A. Borghesani and D. Moodie, *113 Gb/s (10 x 11.3 Gb/s) Ultra-Low Power EAM Driver Array*, Optics Express, Vol. 21, No. 1, January 14, 2013, pp. 256-262

- **R. Vaernewyck**, X. Yin, J. Verbrugghe, G. Torfs, X.-Z. Qiu, E. Kehayas, and J, Bauwelinck, *A Low Power 2x28 Gb/s Electroabsorption Modulator Driver Array with On-chip Duobinary Encoding*, IEICE Transactions on Communications, Vol. E97-B, No. 8, August, 2014

- J. Verbrugghe, R. Vaernewyck, B. Moeneclaey, X. Yin, G. Maxwell, R. Cronin, G. Torfs, X.Z. Qiu, C.P. Lai, P.D. Townsend and J. Bauwelinck, *Multi-Channel 25 Gb/s Low-Power Driver and Transimpedance Amplifier Integrated Circuits for 100 Gb/s Optical Links*, Journal of Lightwave Technology

#### **Publications in international conferences**

- **R. Vaernewyck**, J. Bauwelinck, X. Yin, R. Pierco, J. Verbrugghe, G. Torfs, Z. Li, X. Z. Qiu, J. Vandewege, R. Cronin, A. Borghesani and D. Moodie, *A 113 Gb/s (10 x 11.3 Gb/s) ultra-low power EAM driver array*, Proceedings of the 38th European Conference and Exhibition on Optical Communication 2012 (ECOC), September 16-20, 2012, Amsterdam, Netherlands, pp. Mo.2.B.2

- **R. Vaernewyck**, J. Verbrugghe, W. Soenen, B. Moeneclaey, G. Torfs, X. Yin and J. Bauwelinck, *High-speed Electronic Integrated Circuits for Metro, Access and Data Center Networks*, EPIC workshop Op-

tical Interconnect in Data Centers, March 18-19, 2014, Berlin, Germany

- C. P. Lai, A. Naughton, P. Ossieur, P. D. Townsend, D. W. Smith, A. Borghesani, D. G. Moodie, G. Maxwell, J. Bauwelinck, R. Vaernewyck, J. Verbrugghe, X. Yin, X.Z. Qiu, M. Eiselt, K. Grobe, N. Parsons, R. Jensen and E. Kehayas, *Energyefficient colourless photonic technologies for nextgeneration DWDM metro and access networks*, Photonics in Switching 2012, September 11-14, 2012, Ajaccio, Corsica, France, pp. We-S11-I01 [Invited]

- J. Bauwelinck, R. Vaernewyck, J. Verbrugghe, W. Soenen, B. Moeneclaey, C. Van Praet, A. Vyncke, G. Torfs, X. Yin, X.Z. Qiu, J. Vandewege, N. Sotiropoulos, H. de Waardt, R. Cronin, G. Maxwell, T. Tekin, P. Bakopoulos, C.P. Lai, P.D. Townsend, *High-speed electronics or short-link communication*, Proceedings of the 39th European Conference and Exhibition on Optical Communication 2013 (ECOC), September 22-26, 2013, London, United Kingdom, pp. Mo.4.F.4 [invited]

- C.P. Lai, R. Vaernewyck, A. Naughton, J. Bauwelinck, X. Yin, X.Z. Qiu, G. Maxwell, D.W. Smith, A. Borghesani, R. Cronin, K. Grobe, N. Parsons, E. Kehayas and P.D. Townsend, *Multi-Channel 11.3-Gb/s Integrated Reflective Transmitter for WDM-PON*, Proceedings of the 39th European Conference and Exhibition on Optical Communication 2013 (ECOC), September 22-26, 2013, London, United Kingdom, pp. Tu.1.B.2

- X. Yin, X. Z. Qiu, G. Torfs, C. Van Praet, R. Vaernewyck, A. Vyncke, J. Verbrugghe, B. Moeneclaey, M. Ruffini, D. B. Payne, and J. Bauwelinck, *Performance evaluation of single carrier 40-Gbit/s downstream for long-reach passive optical network*, 18th International Conference on Optical Network Design and Modeling (ONDM 2014), May 19-22, 2014, Stockholm, Sweden, pp. 162-167

#### **Publications in national conferences**

W. Soenen, R. Vaernewyck, A. Vyncke and J. Bauwelinck, *Evaluation of a discrete 4-PAM optical link for future automotive networks*, Annual Symposium of the IPS Benelux Chapter Mons, November 29-30, 2012, Mons, Belgium, pp. 69-72

• **R** . Vaernewyck, New 100 Gb/s transmitter reduces CO2 emission, 13th FEA PhD symposium, December 5, 2012, Gent, Belgium,

#### Patents

• T. De Keulenaer, **R. Vaernewyck**, J. Bauwelinck, and G. Torfs, *Improvements in or Relating to Signal Processing*, European patent application, EP14161804, filed on 26 March 2014.

# Introduction

The internet becomes the ubiquitous tool that is changing the lives of so many citizens across the world. Commerce, government, industry, healthcare and social interactions are all increasingly using internet applications to improve and facilitate communications. This is especially true for videoenabled applications, which now demand much higher data rates and quality from data networks. High definition TV streaming services are emerging and these again will significantly push the demand for widely deployed, high-bandwidth services. High speed networks are also being installed across Europe, giving end customers access to data rates (over 100 Mb/s) that used to be the preserve of telecom carriers entirely on their own.

#### 1.1 ICT infrastructure and power consumption

With the ever increasing bandwidth demands, the internet needs to grow continuously. In parallel with the rising demand for bandwidth, there is an urgent need to significantly reduce the energy consumption of existing networks. Besides the ecological issues, the interest also stems from economic needs, since both energy costs and electrical requirements for telecom operators and internet service providers (ISPs) show a continuously rising trend. The dramatic increase in network energy consumption essentially depends on new services being offered, as well as on data traffic volume increase, which follows Moore's law, by doubling every 18 months [1].

In 2012 the global communication networks were estimated to consume about 350 TWh or 1.7% of the worldwide electricity consumption [2]. This number excludes data centers and consumer's personal computation devices, such as desktops, laptops, etc.

Passive optical networks (PONs) are considered to be the most energy efficient network architecture for broadband fiber access [3]. A PON basically consists of an optical fiber star topology, where a large number of subscribers are connected to the optical line terminal (OLT) at a central office (CO). The standard PON operates in the "single-wavelength mode" where one wavelength is used for downstream (DS) transmission and a separate one is used for upstream (US) transmission. PONs will be explained in more detail in Section 1.2. Incorporating wavelength-division multiplexing (WDM) in a PON allows one to support much higher bandwidth, since multiple wavelengths are used, both in DS and US directions.

WDM technologies have been successfully deployed for many years in metro and core networks as they provide tremendous system capacity with long distance transmission. In access networks, however, WDM technology is not commonly used yet. This is due to the relatively low required peruser data rates at present and more importantly due to the high costs associated with deploying entire WDM access networks. However, the present optical networks cannot be simply and cost-effectively scaled to provide the capacity for tomorrow's users. As an effect there is a strong need for new WDM access components which are compact, cost-competitive and mass-manufacturable. This is particularly true at the OLT, where a high degree of integration is a must. While a WDM-PON OLT could in principle be built from pluggable transceivers, a cost-, footprint- and energy-optimized solution is not available today, mainly due to the lack of highly integrated multi-channel transceiver arrays [4].

The necessity to increase the number of wavelengths for WDM-PON automatically leads to an increase in the number of single pluggable transceivers, which brings substantial design challenges and additional costs. In traditional PONs an OLT only contains a single DS transmitter (TX) and a single US receiver (RX). However, in WDM-PON the OLT hosts multiple TXs and RXs for different wavelength channels, increasing the total footprint considerably. Photonic integration of OLT transceivers into arrays will significantly reduce the footprint and cost of WDM-PON OLTs. However, the total power consumption of an array device is an issue. A single multichannel integrated photoelectronic component consumes much more power than a discrete component. To avoid the use of a thermoelectric cooler, the integration density of components is severely limited by the heat dissipat-

ing capabilities offered by their package. Every watt of power consumed by the optoelectronics would be multiplied by a factor of 6 if we consider the power needed to drive thermoelectric coolers to maintain 25°C operating temperature and the power used by air conditioning systems to remove the generated heat in a building. As a result the WDM-PON philosophy necessitates the reduction of the transceiver's power dissipation.

While the ultimate solution is to have coolerless components, an interim step would be to design the components to operate semi-cooled, at 40°C, for example. This recent trend of increasing the operating temperature of the electronics on equipment cards aims at reducing rack cooling costs. In this way the cooling requirements are eased and temperature control power dissipation is reduced. This will obviously increase the power load on today's thermoelectric cooled optoelectronic devices, as they will have to work even harder at higher ambient temperatures. From this plea it is apparent that the main technology challenges for realizing future-proof optical (access) networks are reducing active component power consumption, shrinking form factors and lowering assembly costs.

In this perspective a 100 Gb/s throughput component, composed of 10 channels at 11.3 Gb/s per wavelength channel would be a great contribution to the expansion of customer bandwidth. It can provide increased line rates to the end users at speeds of over 10 Gb/s per wavelength. As RXs typically consume much less power than externally modulated TXs, they can relatively easily be integrated into an array. High speed optical TXs, on the other hand, have significant power consumptions, ranging from 0.5 W up to a few Watts. The heat generation caused by power dissipation forms a critical obstacle in the development of a 10-channel transmitter, which again underlines the importance of power reduction.

Alongside the introduction of WDM in PON networks, also inter-office point-to-point connections in data center environments can benefit from the WDM philosophy. As data center operators often suffer from fiber scarcity or do not own their fiber infrastructure, dense wavelength division multiplexing (DWDM) technologies are essential to deliver capacity extension for datacom applications. In Europe distances between data centers do typically not exceed 80 km, with the majority of the links being shorter than 40 km. Inter-data center communication also benefits from cost-, footprint-and energy-efficient components operating at high data rates to maximize the throughput. As an effect integrated >100 Gb/s transceivers, such as 4 channels at 28 Gb/s, are highly desirable.

#### **1.2 Passive Optical Network**

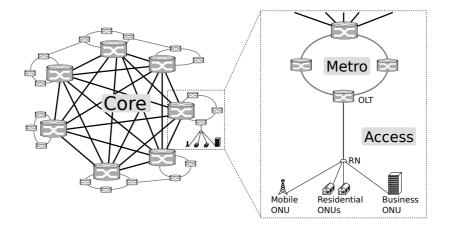

The general structure of a modern telecommunication network can be subdivided in three main sections called *tiers*, as shown in Figure 1.1 [5]. On the highest level, the *backbone* or *core tier* is used for long-distance transport and to interconnect continents and countries across hundreds to thousands of kilometers in a mesh topology. The *metro* networks reside at a lower level and consist of ring topologies that link several COs over tens to hundreds of kilometers. The *access tier* provides end-user connectivity. Access networks typically span several kilometers to tens of kilometers and are deployed in large volumes. They can be configured in bus, star or ring topologies [6].

Figure 1.1: Geographical overview of the network tiers

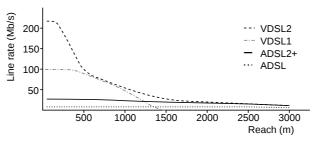

While the core and metro networks incorporate optical fibers, most access networks still consist of copper. However, the bulk, low-speed copper cables can't cope with the increase in speed demanded by the next generation. Even though advanced transmission techniques are being used to augment the data speed towards end-customers, the present, already deployed access infrastructure can't possibly guarantee gigabit rates over distances surpassing 500 m. The copper cables pose a limitation, as they suffer from limited bandwidth, large attenuation and dispersion, added with crosstalk between different lines. Figure 1.2 shows the line rate of the different digital subscriber line (DSL) technologies over distance [7, 8]. Despite their short-distance data rate of over 200 Mb/s, they suffer from a low bandwidth distance product, which results in a mere 50 Mb/s rate after 1 km of transmission. The emerging G.fast standard does reach a top speed of 1.1 Gb/s

over a distance of 70 m, however, after 200 m the data rate quickly drops to 200 Mb/s [9]. A medium that is able to follow the data rate increase is the optical fiber, which can cope with extremely high bandwidths. Compared with copper, optical fibers have many advantages, which are summarized in Table 1.1 [10].

Figure 1.2: Performance characteristics of ADSL, ADSL2+, VDSL1 and VDSL2 [7, 8]

The legacy copper network can be replaced by an optical access network, which has a number of possible topologies. The CO can be connected to subscribers by point-to-point (P2P) fibers. This has the drawback of a high cost due to the huge amount of fibers needed. To reduce the fiber quantity, a star topology is used, in which case there is a splitting point, known as the remote node (RN) close to the end subscribers, which is connected to the CO. This splitting point can be implemented using an active node that incorporates a transceiver per customer which has to be powered and maintained, while future-proofness isn't guaranteed. When the splitter is implemented passively, the network is called a passive optical network. A PON consists of a single mode fiber-based point-to-multipoint (P2MP) topology, where a number of optical network units (ONUs) at subscriber side are connected to the OLT at the CO via passive splitters. The passive infrastructure benefits from a low installation and maintenance cost and reduces the power consumption, since no power supplies are needed at the RN.

To increase the bandwidth of the subscribers, a fiber to the home (FTTH) scenario is preferred. In this topology a high speed fiber is distributed to every subscriber's premise [11]. Even though this strategy is future proof, it hasn't been globally deployed yet due to the economic considerations that come with laying out such a vast network of optical cables. The equipment and fibers needed for the deployment, together with the civil works for installing the fibers are the main contributors to the immense cost. As a midterm solution a hybrid fiber access is provided by routing fiber to a cabinet in the street, so called fiber to the curb (FTTC), or to a building

| Small size                    | The total diameter of the core and the cladding is<br>typically 125 $\mu$ m, although a protection jacket<br>brings the total diameter typically to 400 $\mu$ m.<br>Coaxial cable has a diameter greater than 6 mm.<br>For cramped conduits in buildings and under-<br>ground layout, the advantage of small size is con-<br>siderable. |  |  |