Een 'duobinary' ontvangerchip voor seriële communicatie aan 84 Gb/s

A Duobinary Receiver Chip for 84 Gb/s Serial Data Communication

Timothy De Keulenaer

Promotoren: prof. dr. ir. J. Bauwelinck, dr. ir. G. Torfs Proefschrift ingediend tot het behalen van de graad van Doctor in de Ingenieurswetenschappen: Elektrotechniek

Vakgroep Informatietechnologie Voorzitter: prof. dr. ir. D. De Zutter Faculteit Ingenieurswetenschappen en Architectuur Academiejaar 2014 - 2015

ISBN 978-90-8578-814-0 NUR 959 Wettelijk depot: D/2015/10.500/58

Universiteit Gent Faculteit Ingenieurswetenschappen en Architectuur Vakgroep Informatietechnologie

Promotor: Prof. Dr. Ir. Johan Bauwelinck Dr. Ir. Guy Torfs

Universiteit Gent Faculteit Ingenieurswetenschappen en Architectuur

Vakgroep Informatietechnologie Sint-Pietersnieuwstraat 41, B-9000 Gent, België

Tel.: +32 9 264 3340 Fax.: +32 9 264 3593

Proefschrift tot het behalen van de graad van Doctor in de Ingenieurswetenschappen: Elektrotechniek Academiejaar 2014–2015

# Dankwoord

Of je het nu dankwoord, voorwoord of acknowledgement noemt, het komt allemaal een beetje op hetzelfde neer. De laatste dag voor het indienen, moet het nog geschreven worden en het is de pagina die het meest gelezen zal worden. De stress om niemand te vergeten is dan groot natuurlijk want op die bijna 5 jaar tijd is er veel gebeurd! Ik zal er dan ook voor opteren om niet alles en iedereen bij naam te noemen, je hoeft je dan ook niet ongelukkig te voelen als je hier niet met naam en toenaam vermeld wordt, ik heb alle steun en afleiding zeer zeker geapprecieerd! Onderaan heb ik trouwens een vakje voorzien voor iedereen die graag een gepersonaliseerde, gehandtekende versie wil.

In het voorjaar van 2010 was ik nog rustig samen met Arnaut aan m'n thesis bezig, en nu, voorjaar 2015, ligt de eerste ingebonden versie van m'n doctoraat hier voor mij. Dit was natuurlijk nooit gelukt mocht ik niet mogen beginnen hier in de INTEC Design groep. Hiervoor wil ik natuurlijk mijn promotoren Johan en Guy bedanken, maar ook Jan Vandewege natuurlijk die in 2010 het labo nog in goede banen leidde. Ook van Daniel, de vakgroepvoorzitter, kreeg ik altijd uitleg bij vragen die zich meer in zijn vakgebied situeerden. Daarnaast horen ook de leden van de examencommissie thuis in deze paragraaf, hen wil ik graag bedanken voor het beoordelen van mijn werk en aanreiken van interessante opmerkingen. Uiteraard mag ook het ShortTrack team niet ontbreken, bedankt voor de relevante feedback en mij op het industrieel belang van mijn onderzoek te wijzen.

Nu beginnen we aan het echte werk natuurlijk, ik ga zeker niet iedereen bij naam noemen zoals eerder al aangeven maar onder sommige namen kan ik echt niet onderuit, zoals de collega desingers van afstudeerjaar 2010: Arno, Ramses en Renato bedankt voor de ontspanning, maar ook het delen van de spanning en het samen verder bouwen aan onze grote droom: het starten van een succesvolle multinational ;)! De overige collegas en ex-collegas mogen natuurlijk ook niet vergeten worden met in het bijzonder Jean voor de technische bijstand van het eerste uur en om de deur te openen als ik mijn batch vergeten was en Mike voor de administratieve hulp, bedankt. Van de collega's, last but by far not least natuurlijk Joris en zijn bubbel, hoewel hij hier nog maar een jaartje als collega zit en daarvoor nog een beetje een vreemd thesisstudentje was, is hij nu één van de collega's waar ik de laatste maanden het meest mee samenwerkte. Bedankt Joris, voor al het werk dat we het laatste jaar verricht hebben, als all rounder op DesignCon 2015, tijdens onze demo in Berlijn en de steeds kritische blik op de zaken, veel plezier en succes nog binnen het labo en daarna!

In het Technicum liepen natuurlijk ook nog andere mensen rond zoals de begeleiders van de Werkgroep ELEKtronica (WELEK) met onderandere Bart en Francis, de mensen van de EM groep met natuurlijk thesis partner Arnaut en regelmatige project partner Thomas in het bijzonder, de vrienden bij de Floheacom zoals ondermeer Kathleen en Bernd. Bedankt om de zorgen voor de nodige ontspanning!

Het labo en bij extensie het Technicum is bij deze overlopen, dan zijn er natuurlijk nog alle buiten labo'se activiteiten, niet dat ik zo een ongeloofelijk druk bezet persoon ben, want ik kan best genieten van een rustige avond tv kijken samen met mijn favoriete vriendin allertijden Ellen, maar sommige dingen konden we natuurlijk niet laten voorbijgaan. Om een beetje te beginnen bij het begin zitten we terug in 2010 waarbij we nog wekelijks een goed gevuld en vullend pasta team organiseerden en de zoektocht naar een huis startte! Een jaar later was het dan zover en konden Toon, Bernd, Ellen en ikzelf intrekken in de Ham 54! Merci allemaal! Tijdens het werken werd het al snel duidelijk dat ontspanning niet te onderschatten is! Bij deze: Wieland, Quinten, Stijn, Joris en de hele bende bedankt voor het mede entertainen, boeken, plannen en rijden tijdens onze zomeren wintervakanties! Stijn en Bernd, bedankt voor het organiseren van de jaarlijkse bbqs.

Onder een apparte vermelding van Bernd kan ik natuurlijk niet onderuit als mede-burgie, mede-eigenaar van Ham 54, en zoveel meer: je stond altijd paraat met raad en daad! Bedankt!

En dan komen we natuurlijk tot bij de familie, in het begin de harde kern: de mams, de paps en de zussen (ons Julie en ons Amelie) en natuurlijk 'mijn' Ellentje. Later werd de groep dan nog wat groter en kwamen daar ook nog Günther en Sarah bij. Hen allen wil ik niet enkel bedanken voor het nalezen en tonen van oprechte interesse, maar ook voor de steun, ontspanning onder de vorm van kubb, bbqs en molteams en het maken van mij tot hoe ik ben geworden :) De familie is natuurlijk meer dan enkel het gezinnetje De Keulenaer, daar horen ook oma en opa bij, die regelmatig eens belden om op de hoogte te blijven, of was het om een technisch probleem op te lossen? En de nonkels en tantes, bedankt!

Nu volgt natuurlijk nog de belangrijkste bedanking, die voor Ellen, ik mocht niet teveel koosnaampjes gebruiken en heb dat dan ook proberen vermijden. Bedankt voor alle steun, het nalezen, de interesse, het luisteren, het zorgen voor de plantjes en nog zoveel meer!

> Gent, mei 2015 Timothy De Keulenaer

iv

If two people always agree, one of them is useless. If they always disagree, both are useless.

MARK TWAIN

# Table of Contents

| Dankwoord i                                              |                    |                                            |                            |     |  |  |  |  |

|----------------------------------------------------------|--------------------|--------------------------------------------|----------------------------|-----|--|--|--|--|

| Nederlandse samenvatting                                 |                    |                                            |                            |     |  |  |  |  |

| Er                                                       | English summary xv |                                            |                            |     |  |  |  |  |

| Li                                                       | st of l            | Publicat                                   | ions                       | xxi |  |  |  |  |

| 1                                                        | Introduction       |                                            |                            |     |  |  |  |  |

|                                                          | 1.1                | Backgi                                     | round                      | 1   |  |  |  |  |

|                                                          |                    | 1.1.1                                      | Backplane configurations   | 2   |  |  |  |  |

|                                                          |                    | 1.1.2                                      | Modulation formats         | 6   |  |  |  |  |

|                                                          |                    | 1.1.3                                      | Duobinary system           | 10  |  |  |  |  |

|                                                          | 1.2                | Overvi                                     | ew of the work             | 13  |  |  |  |  |

|                                                          |                    | 1.2.1                                      | Chip design and analysis   | 13  |  |  |  |  |

|                                                          |                    | 1.2.2                                      | Measurements and results   | 14  |  |  |  |  |

|                                                          | 1.3                | Outline                                    | e of the dissertation      | 14  |  |  |  |  |

| I                                                        | Des                | ign and                                    | l analysis                 | 19  |  |  |  |  |

| 2                                                        | Rec                | eiver de                                   | sign                       | 21  |  |  |  |  |

|                                                          | 2.1                | Introdu                                    | iction and design overview | 22  |  |  |  |  |

| 2.2 Design of a 80 Gbit/s SiGe BiCMOS fully differential |                    |                                            |                            |     |  |  |  |  |

|                                                          |                    | buffer for serial electrical communication |                            |     |  |  |  |  |

|                                                          |                    | 2.2.1                                      | Introduction               | 24  |  |  |  |  |

|                                                          |                    | 2.2.2                                      | Block diagram              | 24  |  |  |  |  |

|                                                          |                    | 2.2.3                                      | Circuit description        | 25  |  |  |  |  |

|                                                          |                    |                                            | 2.2.3.1 Input buffer       | 25  |  |  |  |  |

|                                                          |                    |                                            | 2.2.3.2 Output buffer      | 25  |  |  |  |  |

|                                                          |                    | 2.2.4                                      | EM modeling                | 25  |  |  |  |  |

|                                                          |                    |                                            |                            |     |  |  |  |  |

|     | 2.2.5   | Simulation results                                     | 26        |

|-----|---------|--------------------------------------------------------|-----------|

|     |         | 2.2.5.1 Small-signal simulations                       | 27        |

|     |         | 2.2.5.2 Time-domain simulations                        | 27        |

|     | 2.2.6   | Comparison                                             | 28        |

|     | 2.2.7   | Conclusion                                             | 29        |

| 2.3 | A Dig   | itally Controlled Threshold Adjustment Circuit in a    |           |

|     | 0.13 µ  | m SiGe BiCMOS Technology for Receiving Multi-          |           |

|     | level S | Signals up to 80 Gb/s                                  | 32        |

|     | 2.3.1   | Introduction                                           | 32        |

|     | 2.3.2   | Non-clocked duobinary receiver                         | 32        |

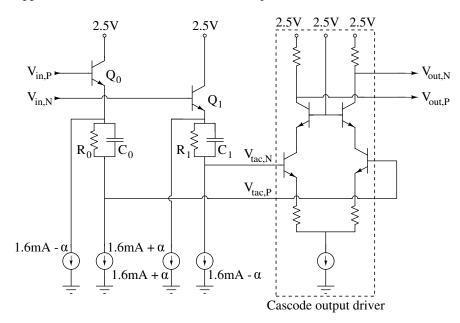

|     | 2.3.3   | Emitter follower threshold adjustment circuit          | 33        |

|     |         | 2.3.3.1 Emitter follower threshold adjustment .        | 33        |

|     |         | 2.3.3.2 Cascoded output driver                         | 36        |

|     |         | 2.3.3.3 Bandwidth and linearity                        | 36        |

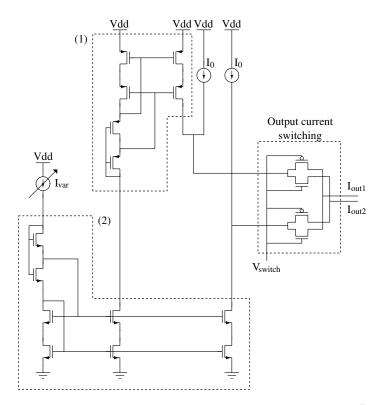

|     | 2.3.4   | Digitally controlled current DACs                      | 36        |

|     | 2.3.5   | Fabrication and further Work                           | 37        |

|     | 2.3.6   | Conclusion and results                                 | 39        |

| 2.4 | Additi  | onal high-speed subblocks                              | 39        |

|     | 2.4.1   | Combining the level shifters into the LSLA             | 39        |

|     | 2.4.2   | Sampling stages                                        | 40        |

|     | 2.4.3   | Half rate XOR gate                                     | 41        |

|     | 2.4.4   | Quarter rate output buffers                            | 42        |

|     | 2.4.5   | Clock chain                                            | 43        |

| 2.5 | Power   | consumption overview                                   | 44        |

| 2.6 | Conclu  | usions                                                 | 45        |

|     |         |                                                        |           |

|     |         | ents of millimeter wave test structures for high-speed |           |

| -   | testing |                                                        | <b>49</b> |

| 3.1 |         | uction                                                 | 50        |

| 3.2 |         | n of millimeter wave test structures                   | 51        |

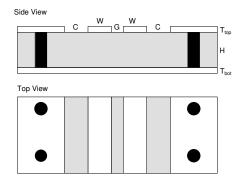

|     | 3.2.1   | Coupled GCPW                                           | 51        |

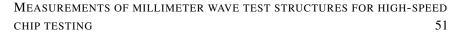

|     | 3.2.2   | Coupled to uncoupled GCPW splitter                     | 52        |

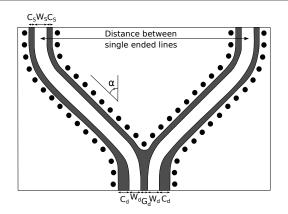

|     | 3.2.3   | Connector footprint                                    | 53        |

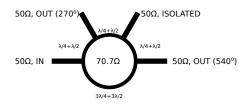

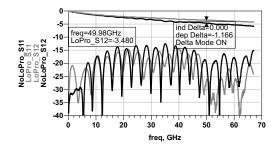

|     | 3.2.4   | Rat-race coupler                                       | 55        |

| 3.3 |         | rements of high-speed test boards                      | 56        |

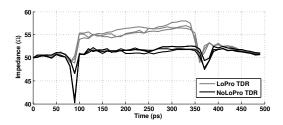

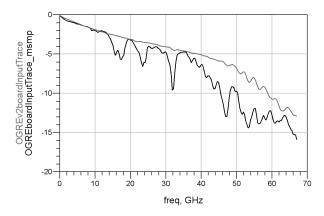

|     | 3.3.1   | Material characteristics                               | 56        |

|     | 3.3.2   | Connector characteristics                              | 58        |

|     | 3.3.3   | Bandwidth of differential lines                        | 58        |

|     | 3.3.4   | Rat-race coupler                                       | 59        |

3

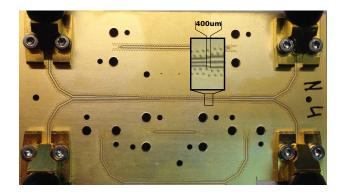

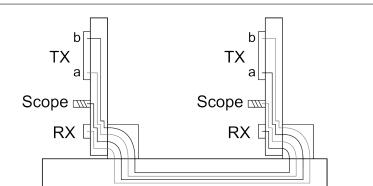

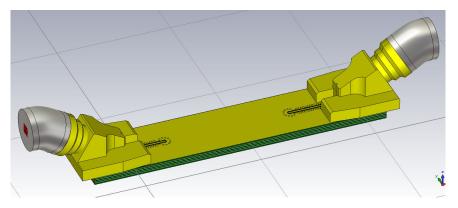

|    | 3.4<br>3.5<br>3.6                                                                                            | Flip chip mounting of the receiver chip              | 60<br>65<br>68 |  |  |

|----|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------|--|--|

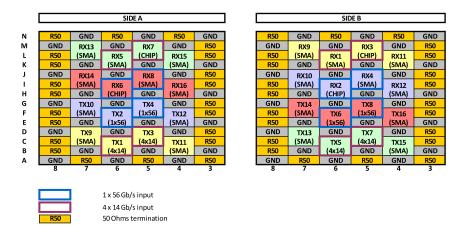

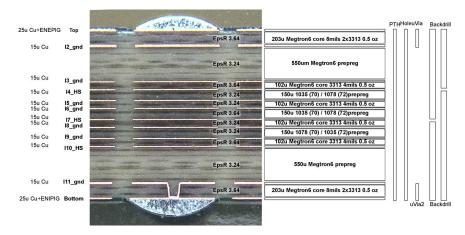

|    |                                                                                                              | 3.6.1 Board stack up                                 | 68             |  |  |

|    |                                                                                                              | 3.6.2 Routing                                        | 72             |  |  |

|    |                                                                                                              | 3.6.3 Mounting order                                 | 74             |  |  |

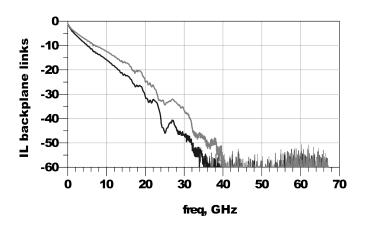

|    | . –                                                                                                          | 3.6.4 Board performance                              | 75             |  |  |

|    | 3.7                                                                                                          | Conclusion                                           | 77             |  |  |

| II | Me                                                                                                           | easurements and results                              | 81             |  |  |

| 4  | 84 Gb/s SiGe BiCMOS duobinary serial data link including Se-<br>rialiser/Deserialiser (SERDES) and 5-tap FFE |                                                      |                |  |  |

|    | 4.1                                                                                                          | Introduction                                         | 84             |  |  |

|    | 4.2                                                                                                          | Transmitter                                          | 85             |  |  |

|    | 4.3                                                                                                          | Receiver                                             | 86             |  |  |

|    | 4.4                                                                                                          | Measurements and conclusion                          | 89             |  |  |

| 5  | 56+                                                                                                          | + Gb/s serial transmission using duobinary signaling |                |  |  |

|    | 5.1                                                                                                          | Introduction                                         | 94             |  |  |

|    | 5.2                                                                                                          | Duobinary signaling                                  |                |  |  |

|    | 5.3                                                                                                          | Custom ASIC design for 50+ Gb/s duobinary link       | 100            |  |  |

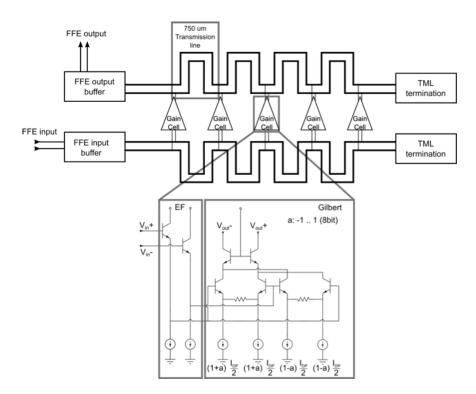

|    |                                                                                                              | 5.3.1 Feed-forward equalizer                         | 100            |  |  |

|    |                                                                                                              | 5.3.1.1 Introduction to feed-forward equalization    | 100            |  |  |

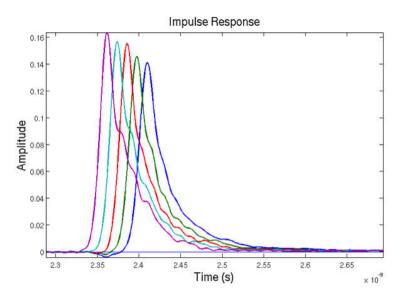

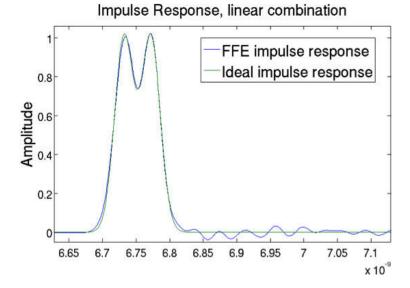

|    |                                                                                                              | 5.3.1.2 Implementation 12.4 ps spaced 5-tap FFE      | 100            |  |  |

|    |                                                                                                              | 5.3.1.3 Parameter optimization                       | 102            |  |  |

|    |                                                                                                              | 5.3.2 Duobinary receiver                             | 103            |  |  |

|    |                                                                                                              | 5.3.2.1 Introduction to duobinary receivers          | 103            |  |  |

|    | 5.4                                                                                                          | Eye-pattern and BER measurements                     | 106            |  |  |

|    |                                                                                                              | 5.4.1 Measurement setup                              | 106            |  |  |

|    |                                                                                                              | 5.4.2 Measurements on ExaMAX® demonstrator           | 107            |  |  |

|    | 5.5                                                                                                          | Measurements on active daughter cards                | 111            |  |  |

|    | 5.6                                                                                                          | Conclusions                                          | 114            |  |  |

| 6  | Con                                                                                                          | clusions and future research                         | 121            |  |  |

|    | 6.1                                                                                                          | Summary of the results                               | 121            |  |  |

|    | 6.2                                                                                                          | Valorisation opportunities                           | 123            |  |  |

|    | 6.3                                                                                                          | Future research                                      | 124            |  |  |

ix

# Nederlandse samenvatting –Summary in Dutch–

De laatste jaren is er een enorme groei van het dataverkeer in de telecom-, datacom- en supercomputersector. Gebruikers verwachten hoge-kwaliteit, bandbreedte verslindende, 4K-video conferenties met meerdere gebruikers. Ze verwachten dat Google in één milliseconde door zijn honderden terabytes grote database kan zoeken en dat een supercomputer pi kan berekenen tot 10 miljoen getallen na de komma in minder dan een microseconde. Om al deze verwachtingen te kunnen inlossen, zal de communicatiesnelheid in server racks drastisch moeten opgeschaald worden. Typisch gebruiken deze racks een architectuur waarbij verschillende kaarten in een backplane geplugd worden. Dit kunnen lijnkaarten zijn voor telecom, opslagmodules voor data centers, verwerkingseenheden voor supercomputers, ... Hogesnelheidscommunicatie over deze backplanes is zeer uitdagend omwille van hun zeer hoge frequentieafhankelijke verliezen. Om dit euvel op te lossen kan men afstappen van de typische on-off keying non-return-to-zero modulatie en in de plaats daarvan gebruik maken van meer bandbreedteefficiënte modulatieformaten zoals een 4-niveaus puls amplitude gemoduleerd signaal (PAM4) of een 'duobinary' gemoduleerd signaal.

De interesse om over te stappen op andere, meer bandbreedte-efficiënte, modulatieformaten is er niet enkel voor backplane communicatie, ook bij korte-afstands optische netwerken is hier veel onderzoek naar. De INTEC Design onderzoeksgroep van de Universiteit Gent is al verschillende jaren bezig met onderzoek naar PAM4 en 'duobinary' modulatie, voor zowel elektrische als korte-afstands optische netwerken. Dit om efficiënter gebruik te maken van de kanaalbandbreedte en zo de gewenste datasnelheden te bereiken. In dit werk is gekozen voor 'duobinary' modulatie omwille van de afweging tussen bandbreedte-efficiëntie, implementatiecomplexiteit en vermogenverbruik.

Duobinary werd voorgesteld in 1963 door A. Lender in zijn paper 'The

duobinary technique for high-speed data transmission'. Hij toonde aan dat een beperkte hoeveelheid toegevoegde complexiteit kan leiden tot een veel efficiënter gebruik van de kanaalbandbreedte. Dit zou vooral van belang zijn bij bedrade en hoogfrequente radiocommunicatie. Meer dan 40 jaar later beschreef J. Sinsky dat 'duobinary' modulatie ook interessant kan zijn bij backplane communicatie. In zijn artikel toont hij een vernieuwende techniek voor het decoderen van een 'duobinary' gemoduleerd signaal tot een traditoneel digitaal signaal door gebruik te maken van een XOR poort in plaats van een gelijkrichter (zoals voorgesteld door A. Lender). Deze techniek zorgde ervoor dat 'duobinary' terug kan concurreren met PAM4 voor hogesnelheidscommunicatiekanalen. Duobinary is verschillend van de meer courante modulatieformaten omdat het gebruik maakt van intersymboolinterferentie en zo de kanaalverliezen benut in plaats van ze volledig te proberen compenseren. Duobinary is een speciale vorm van partial response signaling met een specifiek decodeeralgoritme: het 'duobinary' gemoduleerd signaal wordt gevormd aan de uitgang van het totale kanaal (aan de ingang van de ontvanger). Dit kanaal wordt op zijn beurt gevormd door een combinatie van het predistorsie filter, by. geïmplementeerd als een feedforward equalizer, en het transmissiekanaal.

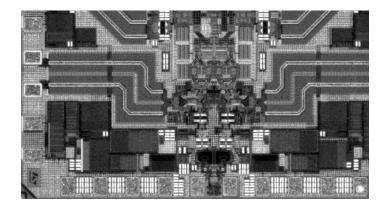

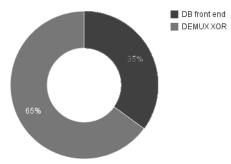

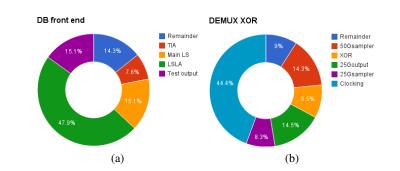

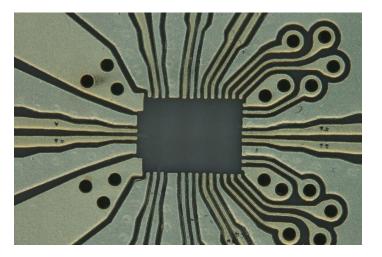

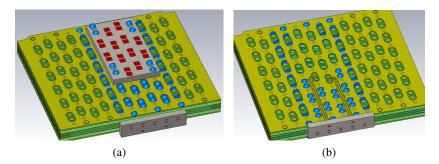

Het werk voorgesteld in deze thesis is gebaseerd op het ontwerp en het testen van een hogesnelheids-duobinary-ontvanger. Het ontwerp en de analyse van de chip en bijbehorende testborden worden grondig beschreven. De chip bestaat uit twee delen: een eerste deel waarin de 'duobinary' gemoduleerde data ontvangen wordt en een tweede deel waarin de ontvangen data gedecodeerd wordt. Verschillende onderdelen van het eerste gedeelte werden door mezelf gepresenteerd op internationale conferenties. Het belangrijkste onderdeel, de ingangsbuffer, is geïmplementeerd als een transimpedantieversterker aangepast aan een  $100 \Omega$  differentiële impedantie en werkt als een zeer efficiënte breedbandige lageruisversterker. Deze heeft een gesimuleerde bandbreedte van 50 GHz, een ruisgetal lager dan 5 dB en een versterking van 12 dB. Verder zijn er twee niveau-verschuivende begrenzende versterkers verbonden met deze ingangsbuffer. Elke versterker bestaat uit twee niveau-verschuivende elementen met enkele versterkende elementen er tussenin. Door verschillende niveau-verschuivende elementen te gebruiken, kan zowel de bandbreedte als het bereik waarover het niveau verschoven kan worden, nodig om het onderste en het bovenste oog van een 'duobinary' signaal te ontvangen, gemaximaliseerd worden. Het tweede deel van de chip bestaat uit een demultiplexer en decodeer-structuur. Eerst wordt het signaal gesplitst in vier signalen, elk aan de halve snelheid. Deze worden dan gedecodeerd door twee XOR poorten die werken aan halve snelheid. Hierna worden deze twee datastromen verder gesplitst tot vier datastromen aan een kwart van de snelheid, die dan naar de uitgangsbuffers gestuurd worden. De technieken die in de complete chipset geïmplementeerd zijn, zijn het onderwerp van 3 patentaanvragen.

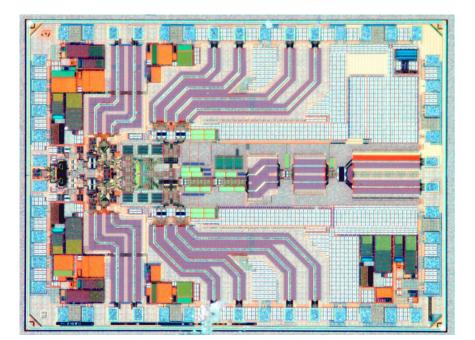

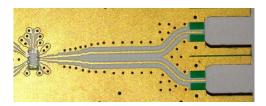

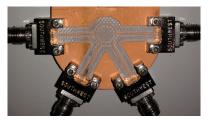

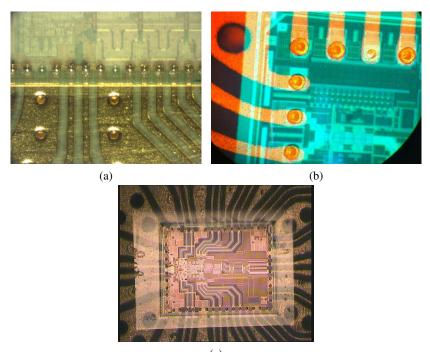

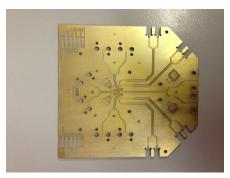

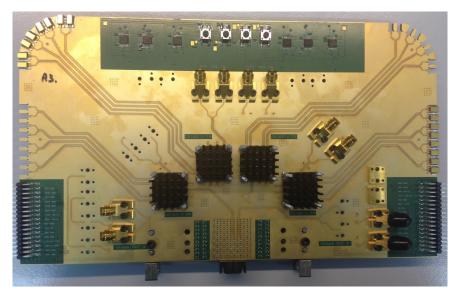

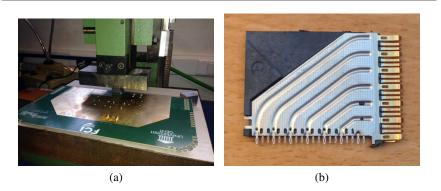

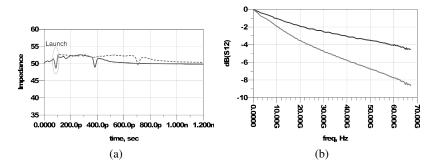

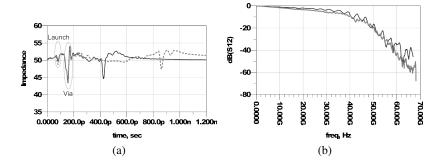

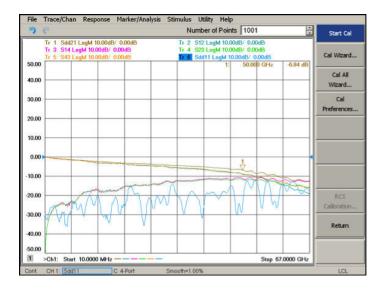

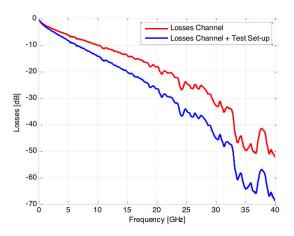

Om systeemtesten met de ontworpen chipset mogelijk te maken, is er nood aan een testbord dat de prestaties van de chips niet beperkt. Hiervoor werden verschillende connectoren, bordmaterialen en routeertechnieken onderzocht en vergeleken. De resultaten hiervan werden door mezelf gepresenteerd op de IEEE Workshop on Signal and Power Integrity in 2014. Gebruik makend van 1.85 mm Rosenberger connectoren werden er verbindingen getoond met een vlakke verlieskarakteristiek tot 67 GHz, inclusief het veranderen van de lijnbreedte, tussen de connector en de chip voetafdruk, en de overgang van ongekoppelde naar gekoppelde transmissielijnen. Deze techniek samen met het thermosonisch flip-chip monteren van de chip op het bord, leidde tot meerdere succesvolle testborden, gaande van een klein 4 laags Rogers RO4003C bord met maar één chip op, tot een groot 24 cm x 30 cm 12 laags Megtron 6 bord met twee ontvanger- en twee zenderchips.

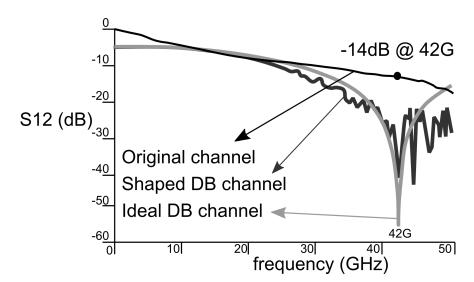

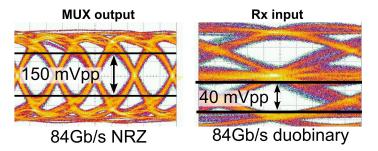

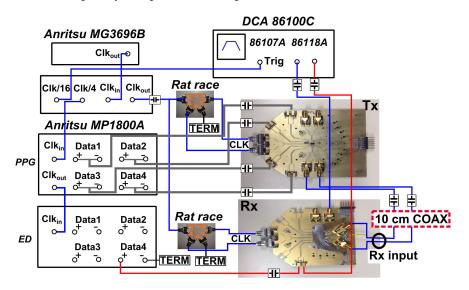

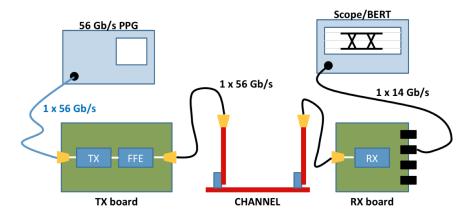

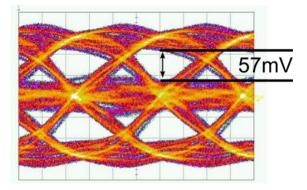

Het combineren van de ontworpen chip met het vier lagen testbord leidde tot een 84 Gb/s transmissielink over 20 cm coax-kabel verbonden tussen de twee testborden met minder dan één bitfout per 100 miljard bits (BER  $< 10^{-11}$ ). Het kanaalverlies bij 42 GHz was ongeveer 14 dB en werd gevormd tot een 'duobinary' kanaal door een 5 taps feedforward equalizer aan de zendkant. Tot nu toe is dit de snelste seriële 'duobinary' gemoduleerde link. Dit was dan ook de aanleiding van een journal paper gepubliceerd in Electronic Letters.

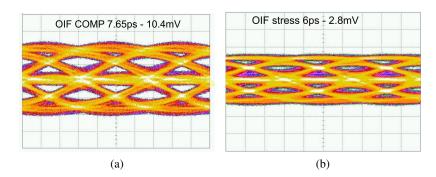

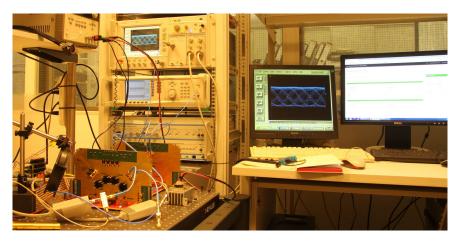

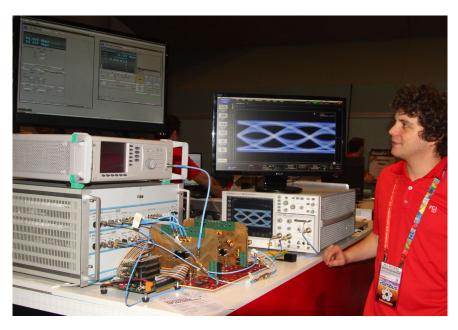

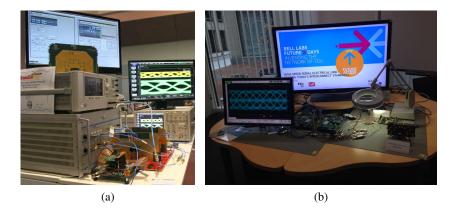

Tot slot werd er ook een compleet backplane testplatform gemaakt, om de performantie van de chip op 56 Gb/s te demonstreren over grotere afstanden. Het testplatform bestaat uit twee borden met elk vier chips die op een Megtron 6 FCI ExaMAX® backplane demonstrator geplugged kunnen worden. Foutvrije (BER <  $10^{-13}$ ) communicatie werd aangetoond bij link lengtes tot 50 cm met verliezen boven de 40 dB bij 28 GHz. Een 56 Gb/s link met 33 dB verlies op 28 GHz werd live gedemonsteerd op DesignCon 2015 in Santa Clara (USA) op de stand van FCI. Dit met een 28 Gb/s cross-talk stoorbron. Samen met Jan De Geest presenteerde ik een paper hierover op DesignCon 2015 die beloond werd met een best paper award.

Het werk voorgesteld in deze thesis kreeg veel aandacht van de industrie tijdens een demo op de Bell Labs Future X dagen en op DesignCon 2015. De ontworpen chipset en bordontwerptechnieken kunnen gebruikt worden voor verschillende doeleinden, zoals: het aansturen van korte-afstands hoge-snelheids optische kanalen, communiceren over complexe backplane kanalen met veel frequentieafhankelijk verlies of voor korte chip-to-module toepassingen.

Samen met drie andere onderzoekers van de INTEC Design groep hebben we recent financiering verkregen van het IOF UGent fonds om de technologie ontworpen tijdens deze thesis verder te ontwikkelen en klaar te maken voor industrieel gebruik.

# English summary

During the last decades, the data traffic in telecom, datacom and high performance computers (HPC) is skyrocketing. Users expect high quality, bandwidth devouring, 4K multi-user video conferencing; they expect Google to query their hundreds of Terabytes database in milliseconds and expect supercomputers to calculate 10 million digits of Pi in a microsecond. To keep up with these expectations, the communication speed within server racks needs to increase dramatically. Typical rack systems use an architecture where multiple cards are plugged into a big backplane. These can be, among others, line cards for telecom, storage blades for datacom, blade servers for HPCs. High-speed communication across these backplanes is very challenging, due to the high amount of frequency dependent loss. To overcome these challenges, one can look at trading in the typical on-off keying non-return-to-zero communication methods for more bandwidthefficient formats such as 4 level pulse amplitude modulated signals (PAM4) or duobinary modulated signals.

The interest in moving towards more spectrally efficient modulation schemes is not only coming from backplane communication, also in short reach optics numerous studies are ongoing regarding this topic. The INTEC Design research group of Ghent University has been investigating PAM4 and duobinary for a couple of years, for use in electrical as well as short reach optical interconnections, to make more efficient use of the total available channel bandwidth and achieve the desired increase in data rate. The selection of duobinary in this work is based on the trade off between spectral efficiency, implementation complexity and power consumption.

Duobinary was first introduced by A. Lender in 1963 in his paper 'The duobinary technique for high-speed data transmission'. He showed that a low degree of added complexity could result in a significantly more efficient use of the channel bandwidth. This would mainly be beneficial for wireline and high-frequency radio communications. More than 40 years later, J. Sinsky wrote about using duobinary signaling for electrical back-

plane systems. He described a novel technique of decoding a duobinary modulated signal to a traditional binary signal using an XOR gate instead of a full wave rectifier (as proposed by A. Lender). This technique allowed duobinary signaling to compete on record breaking rates with its main rival PAM4. Duobinary signaling differs from the other more commonly known modulation formats: it is based on intersymbol interference and in this way embraces the channel loss in contrast to fighting it. It can be thought of as a special case of partial response signaling with a specific decoding structure. A duobinary modulated signal is generated at the receiver by combining the channel loss and a predistortion filter, such as a feed forward equalizer, to shape the channel.

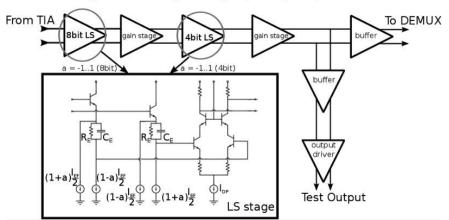

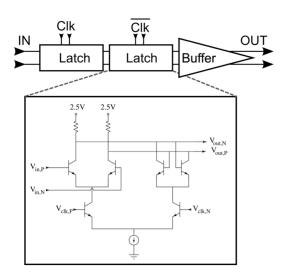

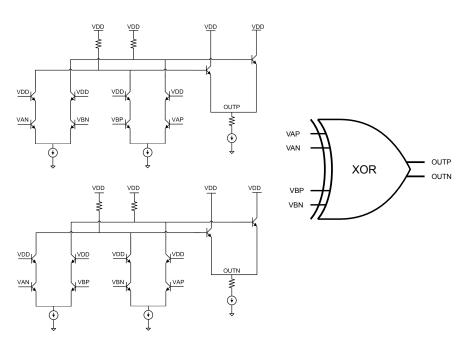

The work presented in this dissertation is based on the design and testing of a high-speed duobinary receiver. The design and analysis of the chip and the accompanying test boards are thoroughly discussed. The chip consists of two main parts: a duobinary front end and a DEMUX/XOR back end. Multiple blocks of the duobinary front end were published and presented at international conferences by myself. The main block of the front end is the input buffer which is implemented as a transimpedance amplifier matched to a  $100 \Omega$  differential impedance and operates as a very effective wideband low noise input buffer. In simulations, the input buffer has a bandwidth of 50 GHz, a noise figure below 5 dB and a gain of 12 dB. Subsequently, two level shifting limiting amplifiers are connected to the output of the input buffer. Each consists of two level shifting stages and different amplifying stages. Using multiple level shifting stages allows the designer to maximize the bandwidth and level shifting range necessary to convert the upper and lower duobinary eves to traditional NRZ eves. The back end of this chip consists of a DEMUX/XOR structure. First, the signal is deserialized to four half rate signals, which are then decoded using two half rate XOR gates. Afterwards, these two streams are further deserialized and provided to the four quarter rate output buffers. The techniques used in this chipset led to three patent applications on the chip implementation.

To perform system tests with the designed chipset, a test board that does not limit the chip's performance is required. To this end, several connector footprints and routing techniques were developed and compared. The results were presented at the IEEE Workshop on Signal and Power Integrity (SPI) 2014. Using 1.85 mm Rosenberger connectors, traces with smooth frequency response up to 67 GHz are shown, including tapering down to the chip inputs and transitioning from coupled to uncoupled transmission lines. This technique, together with thermosonic flip chip mounting of the chips on the board, led to multiple successful test boards, ranging from a small 4 layer Rogers RO4003C board with only one high speed chip, to a large 24 cm x 30 cm 12 layer Megtron 6 board with two receiver and two transmitter chips.

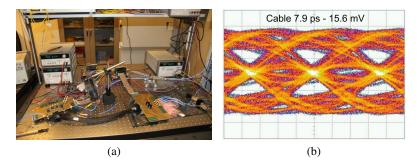

Combining the designed receiver chip and the four layer test board, an 84 Gb/s transmission link is achieved across 20 cm of coax cable connected in between the receiver and transmitter test boards with a BER  $< 10^{-11}$  without any form of forward error correction. The total channel loss at 42 GHz is approximately 14 dB with the channel equalized to the duobinary shape by the 5 tap 12.4 ps spaced feedforward equalizer available at the transmitter. Up to now, this is the fastest duobinary modulated serial communication link which subsequently led to a journal paper published in Electronic Letters.

Finally, a complete backplane test bed was built to show the chip's performance at 56 Gb/s. The test bed contains two active daughter cards, each with 4 chips, and a Megtron 6 ExaMAX backplane. Error free (BER  $< 10^{-13}$ ) transmission was shown across backplane links up to 50 cm with more than 40 dB loss at 28 GHz. Transmission across a channel with 33 dB of loss at 28 GHz was demonstrated live at DesignCon 2015 in Santa Clara (USA), in the booth of FCI with a 28 Gb/s cross talk aggressor. A paper on this work was presented at DesignCon 2015 and won a best paper award.

The work presented in this dissertation gained a lot of attention from the industry during the Bell Labs Future X days, and during DesignCon 2015. The developed chipset and board design techniques can be used for many different applications, such as: driving short high-speed optical channels, transmission across complex high-loss backplane channels or short-range chip-to-module applications.

Together with three other researchers from the INTEC Design group, we aquired project funding from the Industrial Research Fund of Ghent University to further refine the technology developed during this work and prepare it for commercialization.

# List of Publications

## **Publications in International Journals**

T. De Keulenaer, G. Torfs, Y. Ban, R. Pierco, R. Vaernewyck, A. Vyncke, Z. Li, J.H. Sinsky, B. Kozicki, X. Yin, and J. Bauwelinck. 84 Gb/s SiGe BiCMOS duobinary serial data link including serialiser/deserialiser (serdes) and 5-tap FFE. *Electronics Letters*, 51(4):343–345, 2015

Y. Ban, T. De Keulenaer, G. Torfs, J.H. Sinsksy, B. Kozicki and J. Bauwelinck. Experimental evaluation of NRZ and duobinary up to 48 Gb/s for electrical backplanes. *Electronics Letters*, 51(8):617–619, 2015

R. Pierco, G. Torfs, T. De Keulenaer, B. Vandecasteele, J. Missinne, and J. Bauwelinck. A ka-band SiGe BiCMOS power amplifier with 24 dBm output power. *Microwave and Optical Technology Letters*, 57(3):718–722, 2015

K. De Kerpel, T. De Keulenaer, S. De Schampheleire, and M. De Paepe. Capacitance sensor measurements of upward and downward two-phase flow in vertical return bends. *International Journal of Multiphase Flow*, 64:1– 10, 2014

## **Publications in International Conferences**

T. De Keulenaer, J. De Geest, G. Torfs, J. Bauwelinck, Y. Ban, J.H. Sinsky, and B. Kozicki. 56+ Gb/s serial transmission using duobinary signaling. *Proc. IEC DesignCon (Santa Clara, CA, 2015)*, 2015

T. De Keulenaer, G. Torfs, R. Pierco, and J. Bauwelinck. A digitally controlled threshold adjustment circuit in a  $0.13 \mu m$  SiGe BiCMOS technology for receiving multilevel signals up to 80 Gb/s. In 2014 10th Conference on *Ph. D. Research in Microelectronics and Electronics (PRIME)*, pages 1–4. IEEE, 2014

T. De Keulenaer, Y. Ban, Z. Li, and J. Bauwelinck. Design of a 80 Gb/s SiGe BiCMOS fully differential input buffer for serial electrical communication. In 2012 19th IEEE International Conference on Electronics, Circuits and Systems (ICECS), pages 237–239. IEEE, 2012

T. De Keulenaer, Y. Ban, G. Torfs, S. Sercu, J. De Geest, and J. Bauwelinck. Measurements of millimeter wave test structures for high speed chip testing. In 2014 IEEE 18th Workshop on Signal and Power Integrity (SPI), pages 1–4. IEEE, 2014

R. Pierco, T. De Keulenaer, G. Torfs, and J. Bauwelinck. Analysis and design of a high power, high gain SiGe BiCMOS output stage for use in a millimeter-wave power amplifier. In 2014 10th Conference on Ph. D. Research in Microelectronics and Electronics (PRIME), pages 1–4. IEEE, 2014

A. Dierck, T. De Keulenaer, F. Declercq, and H. Rogier. A wearable active gps antenna for application in smart textiles. In 32nd ESA Antenna Workshop on Antennas for Space Applications: From technologies to architectures, 2010

K. De Kerpel, T. De Keulenaer, S. De Schampheleire, and M. De Paepe. Two-phase flow behaviour in a smooth hairpin tube: analysis of the disturbance using capacitive measurements. In *10th International Conference on Heat Transfer, Fluid Mechanics and Thermodynamics*, pages 1314–1321, 2014

K. De Kerpel, C. De Groof, M. Dreesen, T. De Keulenaer, and M. De Paepe. Two phase flow behaviour in a smooth hairpin tube. In *4th IIR Confer*ence on Thermophysical Properties and Transfer Processes of Refrigerants, pages 227–234, 2013

K. De Kerpel, C. De Groof, M. Dreesen, T. De Keulenaer, and M. De Paepe. Capacitive sensor measurements on two-phase flow in smooth return bends. In 8th world conference on experimental heat transfer, fluid mechanics and thermodynamics, 2013

## **Publications in National Conferences**

T. De Keulenaer, J. Vandewege, and J. Bauwelinck. 40 Gb/s transceiver design. In *12th FEA PhD Symposium, Interactive poster session*, Ghent, Belgium, December 2011

## **Patents**

J.H. Sinsky, G. De Peuter, G. Torfs, Z. Li, and T. De Keulenaer. Circuitry and method for multi-level signals. European patent application, EP14305284.3, filed in March 2014

J. Bauwelinck, G. Torfs, Y. Ban, and T. De Keulenaer. Improvements in test circuits. European patent application, EP14161772.0, filed in March 2014

T. De Keulenaer, R. Vaernewyck, J. Bauwelinck, and G. Torfs. Improvements in or relating to signal processing. European patent application, EP14161804.1, filed in March 2014

# Introduction

THIS dissertation pertains to high-speed backplane communication technologies. To introduce the basic concepts, this chapter discusses where a backplane can be found in today's telecom and datacom systems and how backplanes are evolving to reach next generation speed requirements. This is done by giving an overview of the different backplane topologies and architectures as well as an overview of the different modulation formats used.

After providing this necessary background, an overview of the work and an outline of the dissertation is presented.

## 1.1 Background

Starting in the late nineties the Internet became increasingly present in people's daily lives. From 2000 onwards more and more people had home access to high-speed broadband internet. In the mean time, they grew so accustomed to it that it became indispensable. Between 2000 and 2010 the broadband speeds grew from around 1 Mb/s to above 100 Mb/s. Only a few years later, mobile internet usage became more and more popular and providers upgraded their systems from 3G to 4G systems, allowing mobile speeds of above 50 Mb/s needed for video streaming, gaming, communication, etc. This impressive evolution in access speeds leads to new bottlenecks deeper in the network. All data coming from millions of users has to be processed and transferred by the service providers or in the data center. The advances in the data rate of modern communication systems has led to the need for an increased speed in inter-chip communication over so-called backplanes.

These inter-chip serial communication links are becoming more ubiquitous in electronic system designs at an astonishing rate. Today's typical backplane systems use multiple daughter cards communicating over a backplane using non return to zero on-off keying (NRZ OOK) with serial links at 25 Gb/s or below. To move forward and use higher serial speeds, system designers will have to deviate from the traditional ways and think about more advanced modulation formats and/or different system architectures [1].

#### **1.1.1 Backplane configurations**

A typical backplane setup, of which a photo is shown in Figure 1.1, consists of two or more daughter cards interconnected via a backplane. Due to the excessive amount of frequency dependent loss found in these kind of structures, alternatives are approaching the market for high-speed backplanes (28+ Gb/s). Such setups are, among others, cable backplanes, midplane systems and direct orthogonal systems. Another alternative is the use of shorter backplane channels to reduce the loss at higher rates.

Figure 1.1: Photo of a typical backplane system, a Cabletron MMAC PLUS network hub.

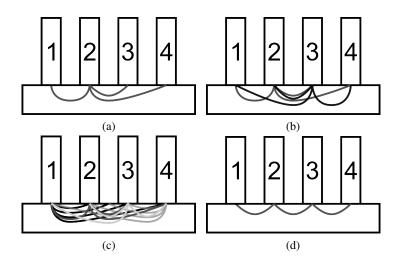

First an overview of the possible backplane topologies, shown in Figure 1.2, will be given.

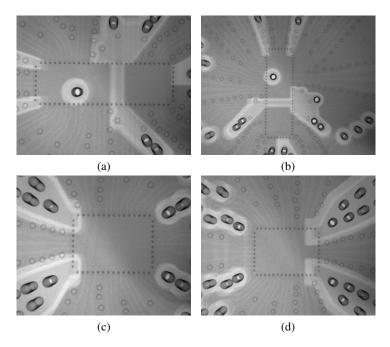

*Figure 1.2: Schematical backplane topologies: Single Star topology (a), Dual Star topology (b), Full Mesh topology (c) and a Chain topology (d).*

#### **Single Star topology**

In network setups today, the star architecture is one of the most common high-speed serial topologies. The advantage is that it reduces the chance of network failure by connecting all the systems to a central node. A failure of a link from any peripheral node to the central node results in the isolation of that peripheral node from all others. As a result, the rest of the system remains unaffected [2].

A basic form of a star topology is shown in Figure 1.2a. In this implementation the central node (node 2) is typically aggregating all traffic from the peripheral nodes (nodes 1, 3 and 4).

The disadvantages of a single star topology are the high dependency on the central node and the large line lengths due to the need to connect to each peripheral node. In case of failure of the central node the system becomes useless.

#### **Dual Star/ Multi-Star topology**

To reduce the dependency on the central node in a single star topology, two or more central nodes can be used, as illustrated in Figure 1.2d. Introducing multiple central nodes provides redundancy in mission critical system applications in case of failure, or allows to upgrade the node hardware.

#### Mesh topology

A fully connected mesh topology, when applied to a backplane application, does not have one or more central nodes as in the case of star topologies, as illustrated in Figure 1.2b. Instead, each node connects with all other nodes forming a mesh. Its major disadvantage is the number of connections, which grows significantly with the number of nodes. This requires additional backplane connector pins and layers to interconnect them. Because of this, it is impractical for large systems and only used when there are a small number of cards that need to be interconnected.

#### **Chain topology**

When moving to higher speeds, line length is sometimes more critical than redundancy. Therefore a chain topology as illustrated in Figure 1.2d can be of interest. Each node is only connected to its neighbors allowing minimal line lengths.

The main drawback of this topology is that the failure of one node leads to the failure of a large part of the system. To reduce this dependency one can utilize a chain topology in which each node is connected to its neighbors and their neighbors. This kind of enhanced chain topology increases the reliability and still allows for a reduction in line length. Now an overview of the possible backplane architectures shown in Figure 1.3 will be given.

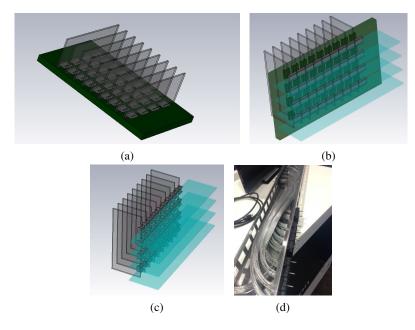

Figure 1.3: Schematical backplane architectures: (a) typical backplane setup, (b) orthogonal setup using midplane, (c) a direct mate orthogonal setup and (d) a cable backplane setup.

#### **Traditional backplane**

In traditional backplane implementations the daughter cards are oriented parallel to each other and mounted on a backplane, as shown in Figure 1.3a.

#### **Orthogonal/midplane/DMO backplane**

One way to reduce the frequency dependent loss is to shorten the link or reduce the amount of connectors and connector footprints. This can typically be seen in orthogonal setups where daughter cards are oriented perpendicular to each other, as shown in Figure 1.3b. In most cases there is a midplane in between, however, one can increase the performance even more by removing this midplane and using direct mate orthogonal connectors (DMO), illustrated in Figure 1.3c.

#### Cable backplane

Another way to reduce the frequency dependent loss without decreasing the physical distance between the daughter cards is using cables instead of a backplane. A photo of a cable backplane is shown in Figure 1.3d. Cables typically consist of a dielectric that has better highfrequency performance. Another benefit of using cables is the routing: since all used cables are shielded twinax cables, one can route in as many layers as needed. Therefore, the routing can be changed after installation without having to replace the complete backplane board.

#### **1.1.2 Modulation formats**

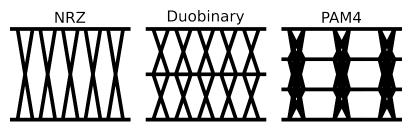

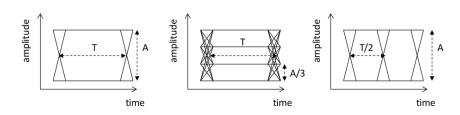

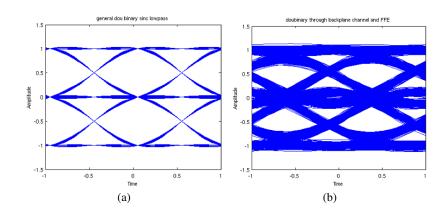

In this subsection the main baseband modulation formats will be discussed: NRZ, 4 level Pulse Amplitude Modulation (PAM4) and duobinary (DB). These are the most realistic formats for high-speed low-cost short-reach wireline and optical systems. Later in this dissertation some other formats will be mentioned and explained. Each of these three formats has its drawbacks and benefits. In Figure 1.4 the three formats are shown next to each other.

*Figure 1.4: Overview of backplane modulation formats, from left to right: NRZ, duobinary and PAM4.*

#### NRZ

NRZ excels in its low complexity and, therefore, native power consumption. However, due to the excessive bandwidth requirement, it needs the strongest equalization of all modulation formats under comparison. NRZ typically needs Forward Error Correction (FEC) to provide reliable communication, which increases power consumption and latency.

#### PAM4

PAM4 combines two bits in each symbol, reducing the symbol rate by a factor of two. This goes hand in hand with the fact that the bandwidth is halved. However, it also adds complexity, increases receiver sensitivity requirements and needs a linear output at the transmitter. Additionally, it adds latency in the decoding and FEC difficulties.

#### **Duobinary**

Duobinary uses known inter-symbol interference to reduce the required channel bandwidth, which makes it a specific form of partial response signaling. This means that two consecutive bits are merged together in a known way. To prevent error propagation, a precoder is added. Merging two consecutive bits together can be done using a feed forward equalizer (FFE). The same equalizer that would be used for NRZ could be used using different parameters to convert the combined response of the FFE and the channel to a duobinary channel instead of a channel without inter-symbol interference (ISI) (as would be the case for NRZ or PAM4 optimization). This means that duobinary can actually embrace part of the loss of the channel and use it to obtain its typical 2-eye duobinary shape. At the receiver side, the sensitivity needs to be higher compared to that of an NRZ receiver and the input needs to be linear. However, the sensitivity requirements are less stringent with respect to a PAM4 receiver since there are two eves instead of three with a PAM4 signal. The decoding of the duobinary stream to an NRZ stream can be done using a rectifier, which in modern designs is typically implemented using the semi-digital approach proposed by Sinsky [3] consisting of an XOR gate combined with two level shifters. An additional advantage of duobinary is that do to the nature of correlative coding, some error detection/correction can be done as explained in [4]. This is however not commonly integrated yet in high speed duobinary receivers.

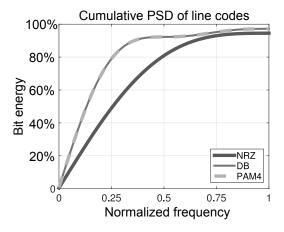

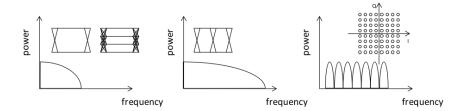

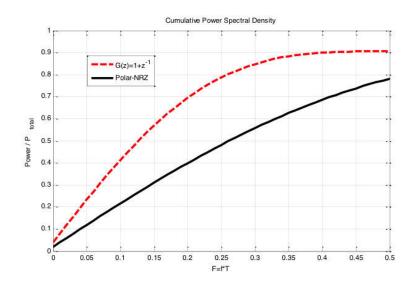

Going into more detail, comparing the bandwidth requirements, we can check the cumulative power spectral density of these modulation schemes. From Figure 1.5 it is clear that PAM4 and duobinary need considerably less bandwidth compared to NRZ. Selecting 90% bit energy (of a square pulsed modulated signal) as the minimum bandwidth necessary results in 35% of the bitrate for PAM4 and duobinary and 66% of the bitrate for NRZ, which clearly indicates the bandwidth reduction obtained by using PAM4 or DB versus NRZ.

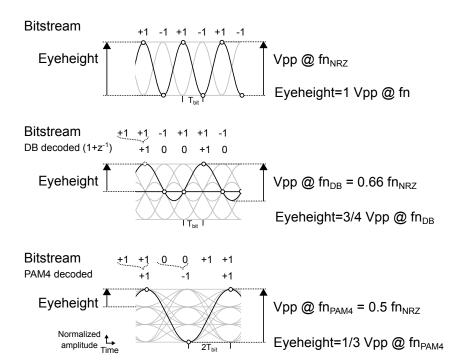

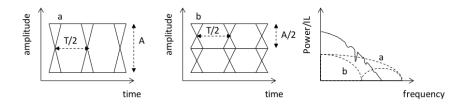

Another more common way for system architects to compare different modulation formats is the Nyquist frequency (fn). Fn is defined as being the highest frequency minimally required to receive the transmitted stream without unwanted ISI. An overview for each modulation format is shown in Figure 1.6. For NRZ and PAM4 these are well known and equal to half and a quarter of the bitrate respectively. For duobinary it is less intuitive but as depicted in Figure 1.6, the Nyquist frequency is at 1/3 of the bitrate. To compare the modulation formats, each format has a penalty with

Figure 1.5: Cumulative power spectral density (PSD) plot comparing NRZ, duobinary modulation and PAM4. The bit energy of PAM4 and duobinary modulation is concentrated in a lower part of the spectrum compared to that of NRZ.

respect to the achieved eye height. This way one can determine which modulation format would have the largest vertical eye opening for a given channel. For PAM4 this signal to noise penalty is well defined at 9.54 dB  $(-20log_{10}(1/3))$  since the eye height is one third of the amplitude at frequency  $fn_{PAM4}$ . For duobinary the eye height is three quarters of the amplitude at  $fn_{DB}$  resulting in a signal to noise penalty of only 2.5 dB  $(-20log_{10}(3/4))$ . Although  $fn_{DB}$  is 33% higher compared to  $fn_{PAM4}$ there is an SNR penalty difference of 7 dB. Which is comparable to the measured 6 dB difference in [5].

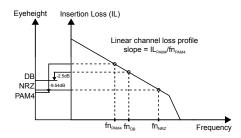

In summary, three situations can be distinguished when comparing channels with a linear loss profile (e.g. a trace on a printed circuit board) and only taking the eye height into account, a typical example is given in Figure 1.7. For this kind of channel that the slope equals  $IL_{PAM4}/fn_{PAM4}$ as well as  $IL_{DB}/fn_{DB}$  and  $IL_{NRZ}/fn_{NRZ}$ . Taking into account the SNR penalty one can calculte that as long as the channel loss is less than 3.75 dB at the quarter bit rate ( $fn_{PAM4}$ ) one should use NRZ for maximal eye opening. Once the loss at  $fn_{PAM4}$  is between 3.75 dB and 21 dB, duobinary is the preferred modulation format and beyond 21 dB loss at  $fn_{PAM4}$  PAM4 will achieve the highest vertical eye opening.

It should be noted that in current systems an insertion loss of 21 dB at  $fn_{PAM4}$  (or for linear channels 42 dB at  $fn_{NRZ}$ ) is very high and only occurs when working with cheap material or at very high bitrates. Also many of the current channels are not linear up to the  $fn_{NRZ}$ . Further in

Figure 1.6: Time domain representation of the Nyquist frequency and the associated eyeheight versus peak ampltude ratio of NRZ (top), Duobinary modulation (middle) and PAM4 (bottom).

this dissertation, the loss of a channel will be specified at the  $fn_{NRZ}$  for easy comparison to other commercial channels (unless noted otherwise).

Another thing that is clarified in Figure 1.6 is the horizontal eye opening, when using minimum bandwidth pulses. It is clear that, although PAM4 has the lowest Nyquist frequency and needs only half the sample rate of NRZ and duobinary, the horizontal eye opening of a PAM4 signal is significantly reduced when reducing the channel bandwidth to  $fn_{PAM4}$ . This results in a comparable jitter tolerance with respect to NRZ and DB, as opposed to what one would expect from halving the baudrate.

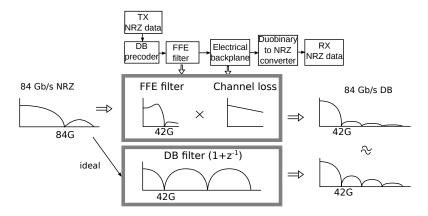

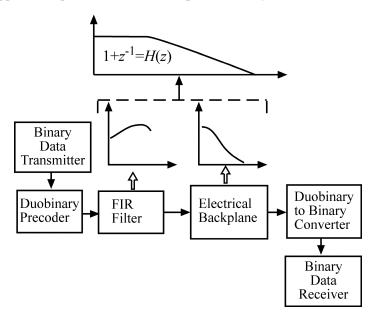

#### 1.1.3 Duobinary system

In Figure 1.8 a typical example of a duobinary system is shown, assuming 84 Gb/s duobinary transmission. Duobinary is a special case of partial response NRZ coding [6] as explained earlier. One of the main advantages is the relatively easy receiver chain, however, the drawback is that you need

*Figure 1.7: Example of determining the largest vertical eye opening for NRZ, duobinary modulation and PAM4 on a channel with a linear loss profile.*

Figure 1.8: Overview of the duobinary signal chain.

a precoder to prevent error propagation. At the transmitter side, a data stream is precoded and shaped to produce the wanted duobinary shape at the output of the channel. Hence, the transmitter contains a precoder and a shaping filter.

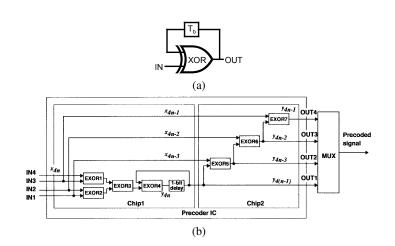

The precoding can be implemented in different ways and can also be done on a sub rate if one decides to use multiple sub rate data streams at the input of the transmitter. On the full rate it can be implemented as a toggle flipflop, which toggles the signal when the input is high and keeps the output when the input signal is low, or using an XOR gate as depicted in Figure 1.9a. On a sub rate a duobinary precoder can be implemented as described in [7] and illustrated in Figure 1.9b.

The shaping filter can also be implemented in different ways e.g. a Continues Time Linear Equalization filter (CTLE) or a Feed Forward Equalizer (FFE). It is intended to shape the signal in such a way that in combination with the channel, a low pass filter is obtained, with transfer function,  $H(z) = 1 + z^{-1}$ . This results in a three level signal at the receiver input.

*Figure 1.9: Example of a duobinary precoder implementation: a typical full rate precoder (a) and a quarter rate precoder (b).*

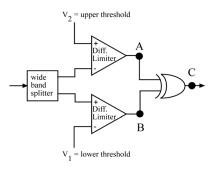

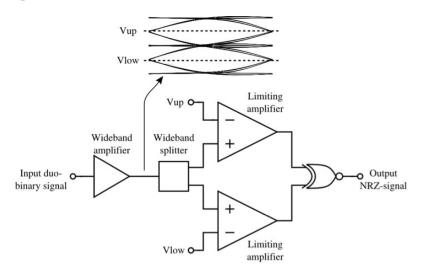

At the receiver side there is a duobinary-to-binary converter, which can be implemented as a rectifier or its semi-digital equivalent, a XOR gate as shown in Figure 1.10 and explained in more detail in [3, 8]. More advanced receiver structures are also possible, making optimal use of duobinary and its error detecting properties. A more in depth overview of how a duobinary receiver can be implemented on-chip can be found in Chapter 2. To

Figure 1.10: Decode duobinary using an XOR gate. (from [8])

implement the use of duobinary signaling in a real-life system the use of a CDR is inevitable. In litrature some topologies are explained implemening a CDR to receive duobinary modulated signals either by using NRZ based techniques after the decoding or by using multilevel techniques [9–11].

## **1.2** Overview of the work

This dissertation is based on the design and testing of a high-speed duobinary receiver I have worked on over the last 5 years at the Design laboratory of the department of information technology (INTEC) at Ghent University.

This work in particular was based on my research performed during his personal IWT grant and in close collaboration with the IWT O&O project ShortTrack together with Alcatel Lucent Bell Labs<sup>1</sup>. His personal IWT grant focusses on design methodologies and new chip architectures to scale to rates above 40 Gb/s for relatively long backplane links (order 0.5 m). During the ShortTrack project an implementation of this architecture was done with the goal of reaching 100 Gb/s across 10 cm backplane links. After the ShortTrack project I was also involved in a follow up collaboration with FCI<sup>2</sup>, a to provide a live demonstrator at their booth during DesignCon 2015 showing error free 56 Gb/s transmission over Megtron 6 backplane links.

My contributions during these projects consisted of the technology explorations, the flip-chip assembly and the optimization methodology for the high-speed transceiver chips, followed by the design of the 100 Gb/s duobinary front end and the design of the high speed test boards for system tests and demonstrations.

#### 1.2.1 Chip design and analysis

During this PhD research, a duobinary receiver was designed. Two chip design cycles were needed to realize a fully functional prototype. The first run was used to test different building blocks such as the input buffer and the duobinary front end. The second tape-out contained an optimized duobinary front end based on the results of the first chip. Also a back end which recovers the original NRZ data out of the two duobinary eyes was added. The back end, consisting of an XOR gate implemented in a deserializer was designed together with our colleague Zisheng Li.

All building blocks were first designed and optimized separately and afterwards combined to larger sub structures. These structures such as a level shifting limiting amplifier consisting of different gain and level shifting stages were then again optimized together to obtain optimal performance.

<sup>&</sup>lt;sup>1</sup>Alcatel Lucent Bell Labs: Inspiring innovation, changing the way you see the world. http://www.alcatel-lucent.com/bell-labs

<sup>&</sup>lt;sup>2</sup>FCI: Setting the Standard for Connectors. http://www.fci.com

Due to the high bitrates and accompanying bandwidths it became clear in the first years of this work that the board design and the connector and mounting methods would have a significant impact on the system performance. One could even say that the test board design becomes equally important as the chip design.

#### 1.2.2 Measurements and results

After the designed duobinary receiver was fabricated and mounted on different test boards, multiple experiments were conducted. The main conclusions and results of these experiments are bundled in chapters 4 and 5 based on publications [12, 13]. Most of the experiments were done in close collaboration with Yu Ban and later also with Joris Van Kerrebrouck.

### **1.3** Outline of the dissertation

The dissertation consists of an introduction in Chapter 1 followed by 2 parts. Part I contains Chapter 2 and Chapter 3 and treats the design and analysis. Part II consists of Chapter 4 and Chapter 5 and focusses on measurement results. The last chapter formulates a conclusion on this topic after almost five years of work. An overview of the content of the succeeding chapters is given below.

#### Chapter 2

The second chapter focusses on the chip design performed during this thesis. In the first part an overview is given of the implemented high-speed duobinary receiver, indicating all high-speed building blocks of the duobinary front end and the DEMUX/XOR. The second part [14] focusses on the input buffer of the receiver chips and how it provides the necessary matching, gain and linearity. It explains how the use of a transimpedance amplifier matched to a 100  $\Omega$  differential impedance can be a very effective wideband low noise input buffer. Subsequently, the level shifter is explained [15]. It shows how the duobinary signal is shifted so that either the upper or the lower eye can be received. To obtain a high shifting resolution a digital current control is implemented. The additional high-speed building blocks are explained afterwards, giving the reader an overview of all main components included in the receiver chip. The chapter concludes with an overview of the power consumption of the chip and an overview of the achieved results.

#### Chapter 3

This chapter (see [16]) deals with the characterization of different millimeter wave structures, and the design of high-speed test boards. It focusses on the importance of connector footprint design as well as trace and via impedance matching. Different connectors are compared and multilayer board buildups are explained. An overview is presented of different commercially available flip chip mounting techniques to allow for broadband interconnection bandwidths above 50 GHz. These were necessary for the successful demonstration of the designed chips.

#### **Chapter 4**

The focus in this chapter is on a 84 Gb/s serial link measurement that was performed [12]. It explains the way the transmitter is able to shape a highbandwidth, lossy channel to a duobinary shape and how the experiment was set up to reach this record breaking rate in serial electrical transmission. Due to the limited availability of the necessary equipment we were only able to set up the 84 Gb/s link across a coaxial link and were time limited to try other interesting channels.

#### Chapter 5

In the penultimate chapter (see [13]) the focus lies on backplane communication links. The first part yields an overview of the current and future standards of backplane communication. This is followed by an introduction to duobinary signaling and an overview of the custom ASIC design. The second part discusses frequency as well as time domain measurements on the test setup and shows how the boards designed in Chapter 3 and the chip designed in Chapter 2 are used. The measurements shown in this chapter were also repeated during a live demo at DesignCon 2015 in the booth of FCI.

#### **Chapter 6**

The final chapter summarizes the progress made in high-speed serial communication links and highlights the most important results. Some suggestions are listed for further research and valorization of the results and knowhow obtained during this PhD.

## References

- W. Beyene, YC. Hahm, D. Secker, and D. Mullen. Design and characterization of interconnects for serial links operating at 56 Gb/s and beyond. *Proc. IEC DesignCon (Santa Clara, CA, 2015)*, 2015.

- [2] B. Simonovich. Backplane architecture and design. 2011.

- [3] J.H. Sinsky, M. Duelk, and A. Adamiecki. High-speed electrical backplane transmission using duobinary signaling. *IEEE Transactions on Microwave Theory and Techniques*, 53(1):152–160, 2005.

- [4] A. Lender. Correlative digital communication techniques. *IEEE Transactions on Communication Technology*, 12(4):128–135, 1964.

- [5] Yamaguchi, K.; Sunaga, K.; Kaeriyama, S.; Nedachi, T.; Takamiya, M.; Nose, K.; Nakagawa, Y.; Sugawara, M.; Fukaishi, M. J. Lee, MS. Chen, and HD. Wang. 12 Gb/s duobinary signaling with x2 oversampled edge equalization. In 2005 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), IEEE, 2005.

- [6] M. Hossain and AC. Carusone. Multi-Gb/s bit-by-bit receiver architectures for 1-d partial-response channels. *IEEE Transactions on Circuits* and Systems I: Regular Papers, 57(1):270–279, 2010.

- [7] M. Yoneyama, K. Yonenaga, Y. Kisaka, and Y. Miyamoto. Differential precoder ic modules for 20-and 40-Gb/s optical duobinary transmission systems. *IEEE Transactions on Microwave Theory and Techniques*, 47(12):2263–2270, 1999.

- [8] J. Lee, MS. Chen, and HD. Wang. Design and comparison of three 20-Gb/s backplane transceivers for duobinary, pam4, and nrz data. *IEEE Journal of Solid-State Circuits*, 43(9):2120–2133, 2008.

- [9] K. Sunaga, H. Sugita, K. Yamaguchi, and K. Suzuki. An 18Gb/s duobinary receiver with a CDR-assisted DFE. In 2009 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), IEEE, 2009.

- [10] L.P. Baskaran, A. Morales, and S. Agili. Transmitter Pre-emphasis and Adaptive Receiver Equalization for Duobinary Signaling in Backplane Channels. In *Digest of Technical Papers. International Conference* on Consumer Electronics (ICCE), 2007.

- [11] M. Hsieh, and G.E. Sobelman. SiGe BiCMOS PAM-4 clock and data recovery circuit for high-speed serial communications. In *Digest* of Technical Papers. IEEE International Systems-on-Chip Conference, 2003.

- [12] T. De Keulenaer, G. Torfs, Y. Ban, R. Pierco, R. Vaernewyck, A. Vyncke, Z Li, J.H. Sinsky, B. Kozicki, X. Yin, and J. Bauwelinck. 84 Gb/s SiGe bicmos duobinary serial data link including serialiser/deserialiser (serdes) and 5-tap ffe. *Electronics Letters*, 51(4):343–345, 2015.

- [13] T. De Keulenaer, J. De Geest, G. Torfs, J. Bauwelinck, Y. Ban, J. Sinsky, and B. Kozicki. 56+ Gb/s serial transmission using duobinary signaling. *Proc. IEC DesignCon (Santa Clara, CA, 2015)*, 2015.

- [14] T. De Keulenaer, Y. Ban, Z. Li, and J. Bauwelinck. Design of a 80 Gb/s SiGe bicmos fully differential input buffer for serial electrical communication. In 2012 19th IEEE International Conference on Electronics, Circuits and Systems (ICECS), pages 237–239. IEEE, 2012.

- [15] T. De Keulenaer, G. Torfs, R. Pierco, and J. Bauwelinck. A digitally controlled threshold adjustment circuit in a 0.13μm SiGe bicmos technology for receiving multilevel signals up to 80 Gb/s. In 2014 10th Conference on Ph. D. Research in Microelectronics and Electronics (PRIME), pages 1–4. IEEE, 2014.

- [16] T. De Keulenaer, Y. Ban, G. Torfs, S. Sercu, J. De Geest, and J. Bauwelinck. Measurements of millimeter wave test structures for high speed chip testing. In 2014 IEEE 18th Workshop on Signal and Power Integrity (SPI), pages 1–4. IEEE, 2014.

## Part I Design and analysis

# 2 Receiver design

#### Timothy De Keulenaer, Ramses Pierco, Yu Ban, Zhisheng Li, Guy Torfs and Johan Bauwelinck

Based on the publications presented by Timothy De Keulenaer at ICECS 2012 and PRIME 2014 extended with an introduction and a description of the remaining subblocks.

Section 2.2 was presented at the 19th IEEE International Conference on Electronics, Circuits and Systems (ICECS 2012) Section 2.3 was presented at the 10th Conference on Ph.D Research in Microelectronics and Electronics (PRIME 2014)

\*\*\*

THE authors would like to thank the Agency for Innovation by Science and Technology in Flanders (IWT) and Integrand Software for access to their EM solver EMX. As well as Ricardo Andres Aroca and Shahriar Shahramian from Alcatel Lucent for the thorough schematic and layout reviews.

## 2.1 Introduction and design overview

In this chapter the chip design activities are discussed. The chip designed in this work was created in close collaboration with the design of a matching transmitter chip described in the dissertation of my colleague Yu Ban. In this section the receiver topology will be explained together with the importance of all subblocks. The main blocks were published on international conferences and a reformatted version of these publications is imported in sections 2.2 and 2.3. Other blocks will briefly be described in the succeeding sections.

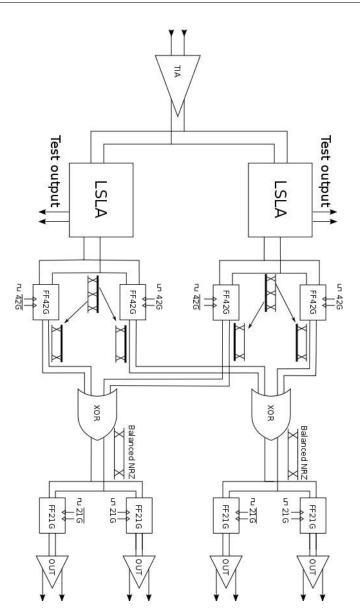

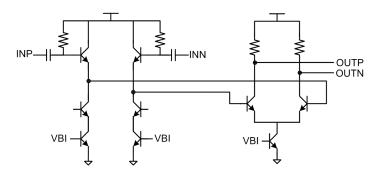

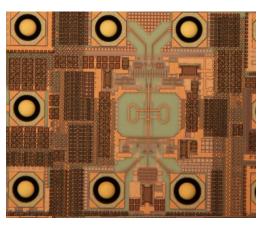

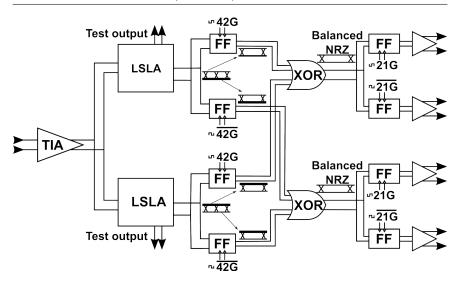

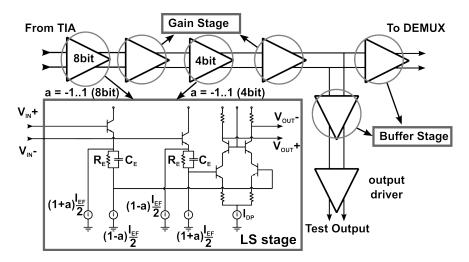

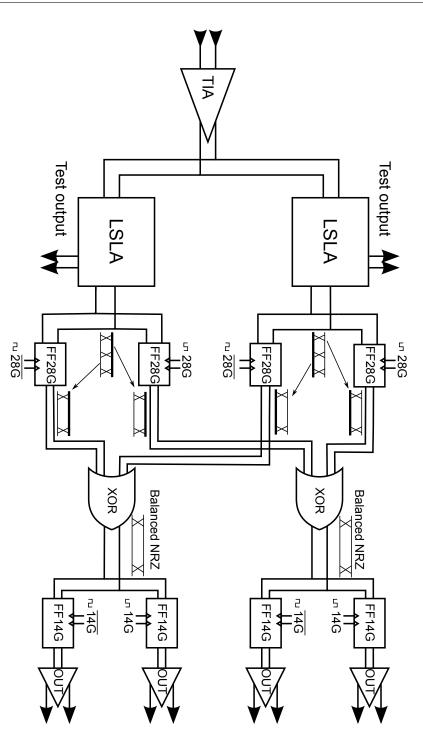

Figure 2.1 shows the receiver topology with at the left a low-noise amplifier (LNA) implemented as a transimpedance amplifier (TIA). The TIA is the first active stage on the chip directly connected to the chip's bump pads and is followed by a set of level shifters, to extract either the upper or the lower eye of the duobinary modulated signal. The level shifters are contained in the level shifting limiting amplifier (LSLA) which amplifies and shifts the upper or the lower eye until a logic-compatible digital swing is obtained. The LSLA outputs are connected to two signal paths: the front end test port and the DEMUX/XOR circuit with the possibility to turn off the test ports via a serial peripheral interface (SPI).

Implementing duobinary signalling at high speeds using the traditional wide band rectifier is not possible using today's technologies. The method proposed by Sinsky in [1] and shown in Chapter 1 is a lot more appropriate for a high-speed implementation. However, each stage adds jitter. At the input of the receiver, the jitter on the duobinary modulated eye is typically 5 to 6 ps. A period of 10 ps for a 100 Gb/s signal severely limits the remaining jitter budget.

To reduce the added jitter, this architecture resamples the signal as soon as possible. This resampling operation reduces the jitter to the clock jitter but can introduce errors if the phase of the clock is misaligned with respect to the data.

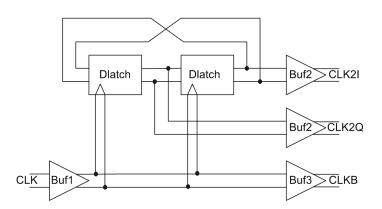

The main block in the proposed receiver architecture that could benefit from a clocked input is the XOR gate. Since full rate sampling beyond 80 Gb/s was not possible in the selected technology, the signal after the LSLA is first down-sampled to a half rate signal and a XOR operation is performed afterwards, as shown in Figure 2.1. This architecture is also the subject of a patent application that has been filed (EP14305284.3).

Implementing the duobinary receiver in this way diminishes the jitter intro-

*Figure 2.1: Implemented receiver architecture for receiving a 84 Gb/s duobinary signal.*

duced by the XOR and runs the XOR at half the channel bit rate. However, a synchronized clock at the receiver side is necessary. This clock can be generated and phase shifted on chip using a CDR circuit, however this is outside of the scope of this dissertation.

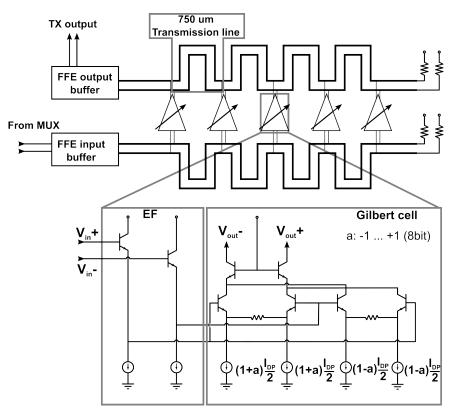

## 2.2 Design of a 80 Gbit/s SiGe BiCMOS fully differential input buffer for serial electrical communication

#### 2.2.1 Introduction

At high data rates, inter-chip electrical communication over PCB traces or long cables becomes challenging due to excessive frequency dependent channel attenuation, which causes large amounts of inter-symbol interference (ISI). Combined with impedance mismatch, this results in a very challenging environment for high-speed and high-bandwidth communication. The input stage of the receiver is optimized for a low noise figure (NF) and good input matching, but without sacrificing area, gain and bandwidth. In this paper, a linear input buffer designed in a 130 nm SiGe BiCMOS process is discussed. The designed buffer has >35 GHz of bandwidth and can be used for a multitude of modulation formats, e.g. NRZ, duobinary modulation, PAM4. Section 2.2.2 introduces the serial communication link and shows the focus of this paper. The topology used to design the matched input buffer is shown in Section 2.2.3, followed by a section on the electromagnetic simulations of long chip interconnections and the peaking inductor using EMX as an EM solver, which is based on the boundary element method [2]. Section 2.2.5 presents the results of the post layout simulations of the wideband input buffer for both AC and transient response. Section 2.2.6 compares the results achieved in this work with similar publications.

#### 2.2.2 Block diagram

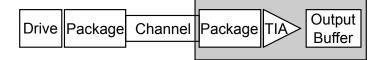

In Figure 2.2 an overview is given of a typical simplified serial communication link.

Figure 2.2: A schematic overview of a simplified link, the grey part is discussed in this paper.

The grey part of this block diagram will be discussed in this paper with emphasis on the TIA as a low noise input buffer for next generation serial electrical communication links.

#### 2.2.3 Circuit description

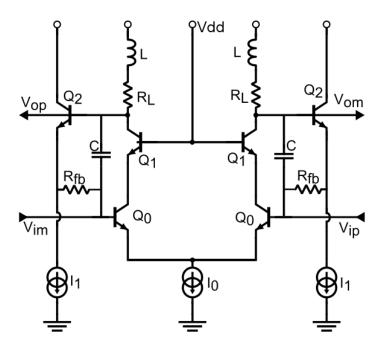

#### 2.2.3.1 Input buffer

A wide range of high-speed bipolar buffer topologies can be found in literature ranging from a simple differential pair or an emitter follower to more elaborate circuits optimized for noise matching or linearity using resistive degeneration [3]. In this work a transimpedance stage is implemented as shown in Figure 2.3. Recently, the use of shunt feedback to lower the optimal noise impedance to  $50 \Omega$  has been considered in low-noise voltage preamplifiers [4]. To obtain optimal broadband impedance matching to the system impedance  $Z_0$ , the open loop gain A and feedback resistor  $R_{fb}$  are chosen by:

$$Z_0 = R_{in} = \frac{R_{fb}}{1+A}.$$

(2.1)

Inductors are used to peak the open loop gain at the higher frequencies without excessively increasing the power dissipation. The design of these custom peaking inductors will be described in Section 2.2.4. When the loop gain reduces at higher frequencies, the input impedance changes. To reduce this effect a capacitor is added between the input and load impedance. The capacitor effectively cuts the loop and connects the input to the 50  $\Omega$  load impedance, this allows to increase the input matching bandwidth beyond the gain bandwidth. The feedback resistor is connected through emitter followers to the input to reduce the capacitive load on the collector resistors.

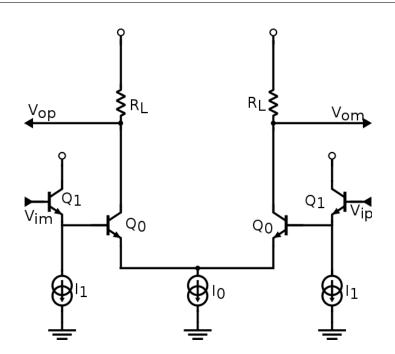

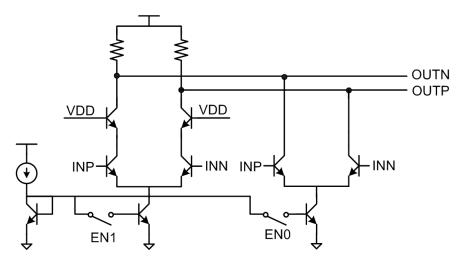

#### 2.2.3.2 Output buffer

To characterize the TIA, a  $50 \Omega$  output buffer was designed using a typical current mode logic (CML) structure. At the input of this CML stage emitter followers were added to increase the input impedance and reduce the input common mode voltage. The schematic is shown in Figure 2.4.

#### 2.2.4 EM modeling

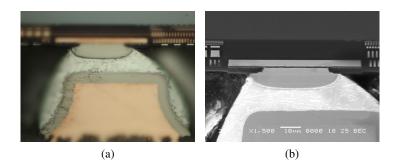

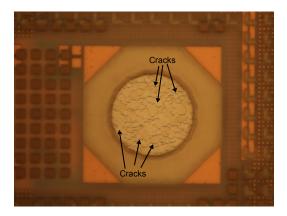

Due to the high bandwidth (>35 GHz), little parasitics can be tolerated at the input. Wirebonding typically introduces 1 nH for each mm of wire and even with short bondwires it is hard to go below 0.3 nH. To solve this, flip chip bumps can be used. Furthermore, flip chip pads are typically smaller, compared to pand intended for wire bonding, which reduces the parasitic capacitance of the pad on the input. In 2002, a thorough study has been done by A. Jentzsch [5] which resulted in an overview table containing

Figure 2.3: Fully differential input buffer. The load impedance  $R_L$  is 50  $\Omega$ , the feedback impedance  $R_{fb}$  is 175  $\Omega$ , the transistors are biased around maximum  $f_T$ .

different pad sizes and bump heights. Both measurements and EM simulation were done and compared in [5]. These results were verified using CST Microwave Studio<sup>1</sup>, a 3D EM simulator, which shows that bandwidths exceeding 50 GHz are possible employing flip chip bumps.

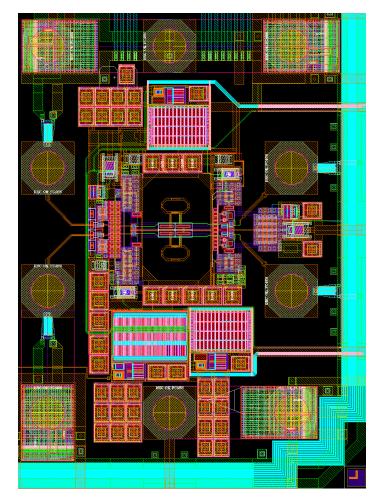

Also due to the high bandwidth, accurate broadband models of long onchip traces and on-chip inductors are required. These inductors were first designed as a separate component and later simulated as part of the TIA to take into account the influence of all parasitic elements. Simulations were performed using the EMX software of Integrand Software. As can be seen in the final layout (Figure 2.7) the size of the custom designed inductors is small compared to the bump pads.

#### 2.2.5 Simulation results

The circuit of the input buffer was simulated including extracted layout parasitics and EM-models for the coils and long traces as well as equivalent models for the flip chip parasitics and ESD protection. The integrated

$<sup>^1\</sup>mbox{CST}$  MWS is a specialist tool for the 3D EM simulation of high frequency. http://www.cst.com

*Figure 2.4: Schematic of the CML output buffer with emitter followers in front. Load impedance*  $R_L$  *is* 50  $\Omega$ *, current*  $I_0$  *is* 6 mA.

circuit is directly flip chipped on a circuit board.

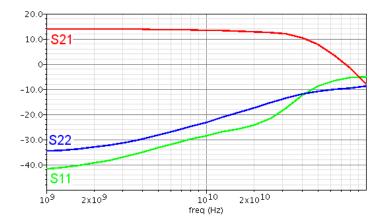

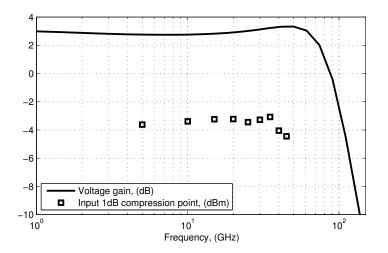

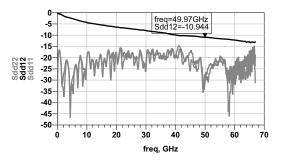

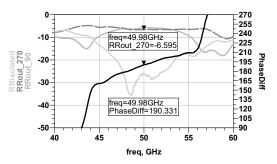

#### 2.2.5.1 Small-signal simulations

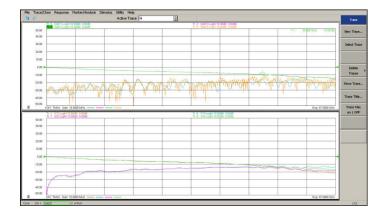

The S-parameters are shown in Figure 2.5. The amplifier has a gain of 14 dB and a 3-dB bandwidth of 37 GHz. The gain-bandwidth product is simulated to be 185 GHz. The simulated input return loss is below 14 dB within the 3-dB bandwidth and the output return loss is below 12.5 dB over the entire 3-dB bandwidth. The maximum noise figure over the 3-dB bandwidth is 8 dB and group delay variation is less than 3 ps.

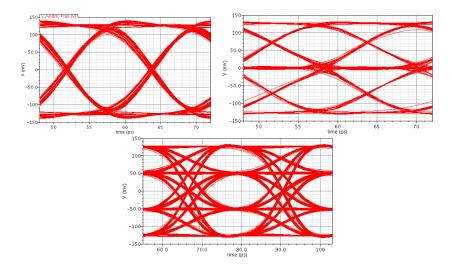

#### 2.2.5.2 Time-domain simulations

A transient simulation of the total circuit including flip chip parasitics, inductors and extracted capacitances is shown in Figure 2.6 with a 60 mVpp input signal at 80 Gb/s (12 ps bit period for NRZ and duobinary, 24 ps for PAM4) at 75 °C. The resulting NRZ eye shows a vertical eye opening of 200 mV and a horizontal eye opening of more than 10 ps with less than 2 ps of jitter. The duobinary simulation obtains a vertical eye opening of

Figure 2.5: Small signal simulation results of the input buffer including parasitics and EM-models, simulated with an input and output impedance of  $100 \Omega$  differential.

100 mV, a horizontal eye opening of 11 ps and less than 1 ps of jitter. The PAM4 eye shows a vertical opening of 70 mV and a horizontal opening of 16 ps.

#### 2.2.6 Comparison

The litrature on input buffers for serial electrical interconnects is limited. For this reason the input buffer is compared to transimpedance amplifiers for 40 Gb/s communication. For this comparison the TIA was simulated with a photodiode input, which results in higher gain and bandwidth compared to a  $100 \Omega$  differential input. An overview can be found in table 2.1. From the table it is clear that the proposed transimpedance amplifier achieves the highest Figure of Merit (FOM), which includes the BW, input matching and power consumption. Since this amplifier is used as an input buffer for electrical communication it will not be linked to a photodiode and silicon area is the main cost contributor. The design presented here is also the smallest (including pads) of the compared transimpedance amplifiers, which is beneficial from the point of view of cost reduction of an electrical communication system.

<sup>&</sup>lt;sup>2</sup>simulated result

Figure 2.6: Transient simulation results of an 80 Gb/s bitstream. NRZ (top left), duobinary modulation (top right) and PAM4 (bottom) modulation are shown. The input amplitude is 60 mVpp from a  $100 \Omega$  differential source for all signals, rise and fall times are half the bit period and the waveform is piecewise linear, chip temperature is set to 75 °C.

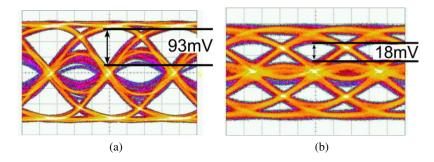

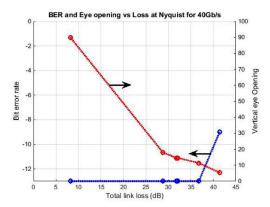

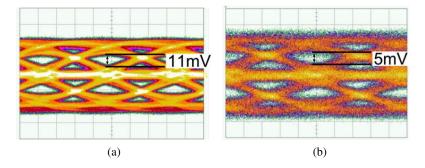

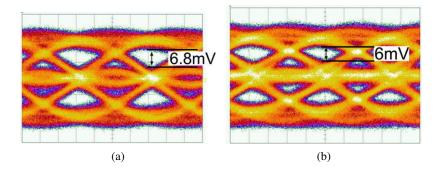

#### 2.2.7 Conclusion