Modellering en taakplanning van heterogene architecturen met meerdere rekenkernen

Modeling and Scheduling Heterogeneous Multi-Core Architectures

### Kenzo Van Craeynest

Promotor:

prof. dr. ir. Lieven Eeckhout

Proefschrift ingediend tot het behalen van de graad van

Doctor in de Ingenieurswetenschappen: Computerwetenschappen

Vakgroep Elektronica en Informatiesystemen Voorzitter: Prof. dr. ir. Jan Van Campenhout Faculteit Ingenieurswetenschappen

## **Examencommissie**

Prof. Rik Van De Walle, voorzitter Decaan, Faculteit Ingenieurswetenschappen en Architectuur Universiteit Gent

Prof. Lieven Eeckhout, promotor Vakgroep ELIS, Faculteit Ingenieurswetenschappen en Architectuur Universiteit Gent

Prof. David Black-Schaffer Uppsala University, Sweden

Prof. Koen De Bosschere, secretaris Vakgroep ELIS, Faculteit Ingenieurswetenschappen en Architectuur Universiteit Gent

Prof. Jan Fostier Vakgroep Informatietechnologie, Faculteit Ingenieurswetenschappen Universiteit Gent

Dr. Jennifer B. Sartor Vakgroep ELIS, Faculteit Ingenieurswetenschappen en Architectuur Universiteit Gent

Dr. Aamer Jaleel Intel, Hudson, MA USA

Dr. Ibrahim Hur Intel, Belgium

## Leescommissie

Prof. Jan Fostier

Vakgroep Informatietechnologie, Faculteit Ingenieurswetenschappen Universiteit Gent

Prof. David Black-Schaffer

Uppsala University,

Sweden

Dr. Jennifer B. Sartor

Vakgroep ELIS, Faculteit Ingenieurswetenschappen en Architectuur Universiteit Gent

Dr. Aamer Jaleel

Intel, Hudson, MA

USA

Dr. Ibrahim Hur

Intel, Belgium

# Samenvatting

In de laatste decennia zijn processors geëvolueerd van relatief eenvoudige scalaire in-order processors tot meerkernige processors met meerdere superscalaire out-of-order rekenkernen. Hierdoor stijgt de complexiteit van de processors en de nood aan hulpmiddelen om te begrijpen waarom de prestatie van een applicatie op een processor is wat ze is. Het beschikken over adequate hulpmiddelen is cruciaal want meer inzicht in het gedrag van de processor zal uiteindelijk leiden naar betere (snellere en/of energieefficiëntere) ontwerpen.

### Simulatie van Meerkernige Processors

Een simulator is een dergelijk hulpmiddel: er wordt een model van een processor in software geïmplementeerd. Zo kunnen ontwerpen geëvalueerd worden alvorens ze effectief te bouwen en kan er meer inzicht verkregen worden in de prestatie van de verschillende onderdelen van de te ontwerpen processor. Het spreekt voor zich dat simulatoren nauwkeurig het gedrag van de processor die ze modelleren moeten nabootsen, maar het is minstens even belangrijk dat de evaluatie voldoende snel kan gebeuren. Hoe sneller de simulatie verloopt, hoe meer parameters, configuraties, werklasten en ontwerpbeslissingen geëvalueerd kunnen worden. Dit probleem wordt exponentieel groter wanneer we meerkernige processors beschouwen: omdat een meerkernige processor meerdere applicaties tegelijk kan uitvoeren, vormt iedere combinatie van programma's een nieuwe potientiële werklast om te evalueren. Gezien simulatie relatief traag is (vaak meerdere grootteordes trager dan de processors die ze modelleren) is het dan ook volledig onhaalbaar om alle (of zelfs maar een fractie van alle) werklasten te evalueren. Er is dus duidelijk nood aan een fundamenteel andere aanpak voor de prestatie-evaluatie en exploratie van de ontwerpruimte van meerkernige processors.

### **Analytisch Modelleren van Meerkernige Processors**

In dit proefschrift onderzoeken we het gebruik van analytische modellen om de prestatie van meerkernige processors te evalueren. Eén van de grootste uitdagingen bij de prestatie-evaluatie van meerkernige processors zijn de gedeelde systeembronnen — wij hebben ons voornamelijk geconcentreerd op de gedeelde caches. Er is een complexe terugkoppellus waarbij de prestatie van de individuele applicaties bepaald wordt door de manier waarop de gedeelde cacheruimte dynamisch toegewezen wordt aan de verschillende applicaties die samen uitvoeren op de meerkernige processor. Maar de verdeling van de cache beïnvloedt dan weer de prestatie van de applicaties, waardoor de toegangspatronen naar de cache veranderen, wat op zijn beurt leidt tot een andere verdeling in de cache. Het is duidelijk dat de prestatie van een meerkernige processor bepaald wordt door de prestatie van de individuele rekenkernen én de manier waarop gedeelde systeembronnen toegewezen worden aan de rekenkernen.

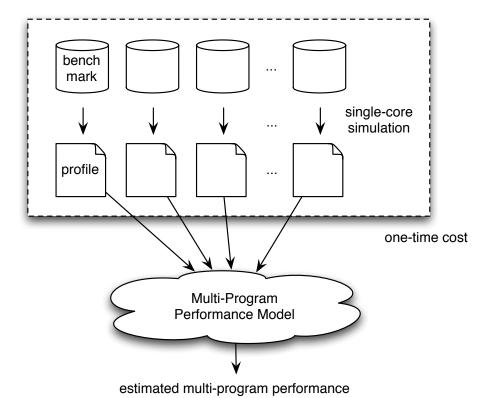

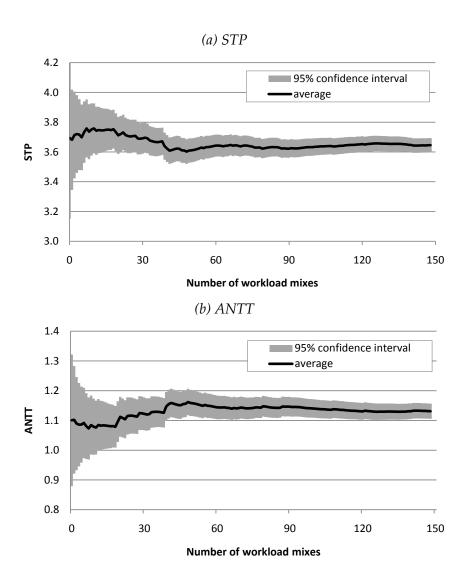

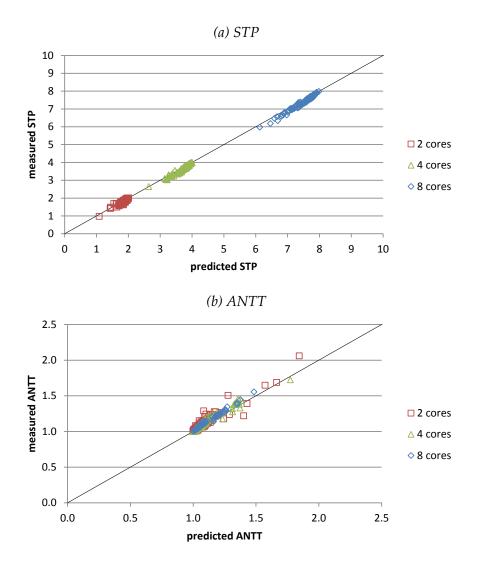

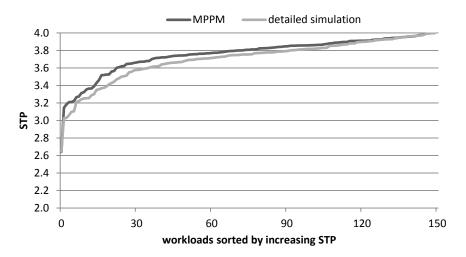

Wij stellen een methodologie, het *Multi-Program Performance Model* (MPPM), voor waarbij we enkel (trage) gedetailleerde simulatie gebruiken voor de prestatie-evaluatie van de rekenkernen en waarbij we gebruik maken van een iteratief analytisch model om de impact van de gedeelde caches te schatten. Omdat we per applicatie slechts één maal gedetailleerd moeten simuleren, is het MPPM-raamwerk lineair in tijdscomplexiteit m.b.t. het aantal te evalueren applicaties. De MPPM-methode voor de prestatie-evaluatie van meerkernige processors is daardoor tot vijf grootteordes sneller dan gedetailleerde simulatie, terwijl de door MPPM geschatte prestatie een fout vertoont van slechts 2.3% voor *system throughput* (STP) en 2.9% voor *average normalized turnaround time* (ANTT) in vergelijking met gedetailleerde simulatie. Bovendien hebben we, gebruik makend van het MPPM-raamwerk hebben we aangetoond dat de gangbare praktijk om slechts een beperkt aantal combinaties van applicaties te evalueren kan leiden tot foutieve ontwerpbeslissingen.

## Exploratie van de Ontwerpruimte van Heterogene Meerkernige Processors

Traditioneel bestaan meerkernige processors uit meerdere identieke kernen (zogenaamde homogene meerkernige processors). Heterogene meerkernige processors bestaan uit verschillende types rekenkernen. Heterogene meerkernige processors kunnen veel energie-efficiënter zijn dan homogene meerkernige processors door taken op een type processorkern die best geschikt is voor de gegeven taak (beste prestatie voor het minste vermogenverbruik) uit te voeren.

Het MPPM-raamwerk stelt ons in staat een uitgebreide exploratie te doen van de heterogene ontwerpruimte van meerkernige processors, om zo inzicht te verschaffen in heterogeen meerkernig ontwerp en een antwoord te geven op een aantal fundamentele ontwerpkeuze vragen. We hebben alle mogelijke configuraties van vijf verschillende types processorkernen beschouwd, met verschillende cache configuraties, off-chip band-

breedtelimieten en taakplanningsalgoritmes. De belangrijkste conclusies uit deze studie luiden als volgt:

- We hebben aangetoond dat twee verschillende types processorkernen voldoende zijn om het grootste deel van de energie-efficiëntie van heterogeniteit te bereiken.

- Heterogeniteit houdt een fundamentele afweging in tussen de prestatie van individuele applicaties en de prestatie van de volledige processor.

- Een beperkt aantal combinaties van types processorkernen bestrijkt het grootste deel van de ontwerpruimte.

- Een goede plaatsing van de applicaties op de types processorkernen is cruciaal voor de efficiëntie van heterogene meerkernige processors.

- Beperken van off-chip bandbreedte heeft een grote impact op een aantal fundamentele ontwerpkeuzes van heterogene meerkernige processors.

### Taakplanning voor Heterogene Meerkernige Processors

Eén van de belangrijkste aspecten van heterogene meerkernige processors is de taakplanning: heterogeniteit kan enkel tot een betere energie-efficiëntie leiden indien er een goede taakplanning is van de applicaties op de processorkernen. Bovendien vertonen programma's vaak tijdsvariërend gedrag, waardoor het cruciaal is dat taakplanningen dynamisch zijn: de optimale planning verandert naarmate het uitvoeringspatronen van de applicaties veranderen.

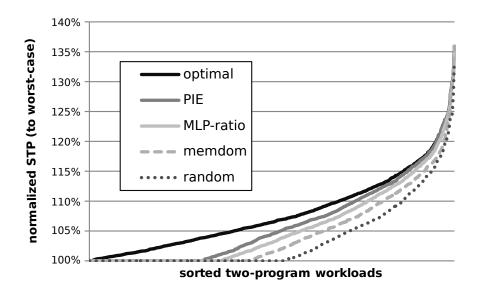

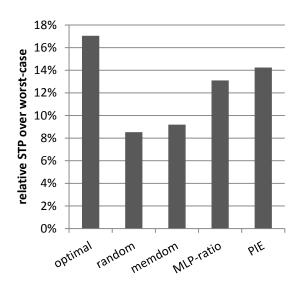

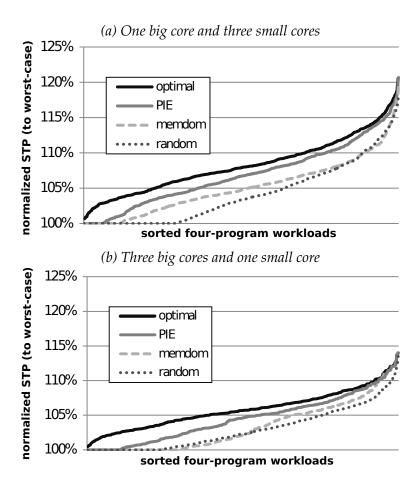

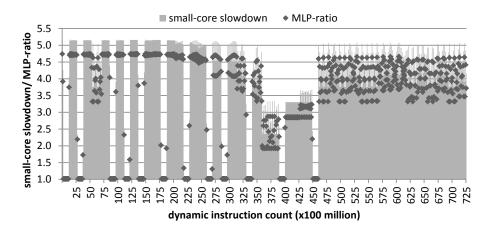

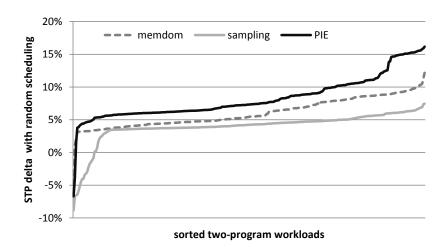

Wij stellen *Performance Impact Estimation* (PIE) voor, een methode waarbij de prestatie van een applicatie op andere types processorkernen geschat wordt met behulp van een analytisch model. Omdat we de prestatie niet hoeven te bemonsteren op alle types processorkernen bekomen we een schaalbaar systeem, zowel in het aantal processorkernen als in het aantal types processorkernen. Bovendien vereist PIE slechts zeer beperkte hardwareondersteuning nodig. We hebben PIE geëvalueerd voor verschillende hardwareconfiguraties: voor een set van werklasten waarvoor taakplanning zeer belangrijk is presteert PIE gemiddeld 5.5% beter dan de conventionele technieken en 8.7% beter dan bemonstering-gebaseerde taakplanning. Tevens hebben we aangetoond dat de logica van de conventionele manier van taakplanning (geheugenintensieve taken worden prioritair op de minder krachtige processorkernen geplaatst) ernstige gebreken vertoont in situaties waarbij parallellisme niet behouden wordt op de minder krachtige types processorkernen.

### Fairness-gebaseerde Taakplanning

Bijna zonder uitzondering wordt er enkel rekening gehouden met *throughput* (of totale prestatie van de processor) wanneer men de taakplanning evalueert voor heterogene meerkernige processors, inclusief de net besproken PIE-techniek. Niettemin is het zeer belangrijk om naast throughput ook fairness in rekening te brengen voor zowel werklasten bestaande uit meerdere onafhankelijke programma's als meerdradige werklasten. Een hoge fairness betekent dat alle draden in het systeem proportioneel dezelfde vooruitgang maken ten opzichte van geïsoleerde uitvoering. Voor werklasten bestaande uit meerdere onafhankelijke programma's is fairness belangrijk als het gaat over eigenschappen zoals quality-of-service. Voor meerdradige werklasten is fairness dan weer belangrijk vanwege de synchronisatie tussen de draden.

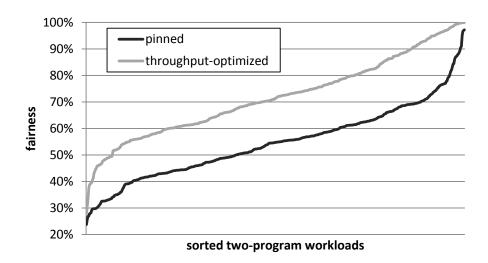

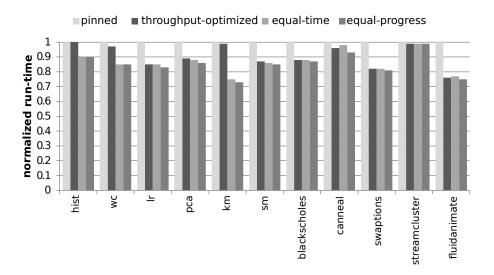

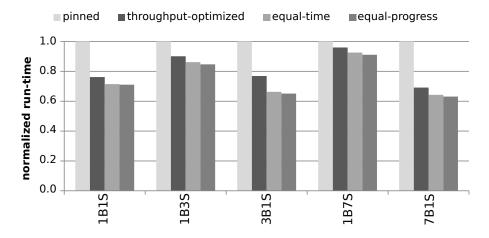

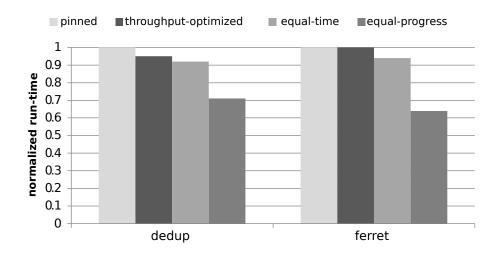

Wij hebben twee manieren van fairness-gebaseerde taakplanning voor heterogene meerkernige processors ontwikkeld en geëvalueerd: equal-time taakplanning en equal-progress taakplanning. Equal-time taakplanning tracht fairness te optimaliseren door alle draden evenveel uitvoeringstijd te geven op elke type processorkern. Wanneer echter de uitvoeringssnelheid van de verschillende draden sterk verschillend is tijdens het uitvoeren op de meest krachtige rekenkern, leidt dit niet noodzakelijkerwijze tot meer fairness. Equal-progress taakplanning gebruikt de effectief gemaakte vooruitgang om de taakplanning aan te sturen, waardoor ook in deze gevallen een hoge fairness kan behaald worden.

Bovendien hebben we aangetoond dat door fairness te optimaliseren, ook de prestatie verbeterd wordt voor meerdradige applicaties. Voor homogene meerdradige applicaties tonen onze resultaten aan dat de prestatie gemiddeld toeneemt met 14% (tot maximaal 25%) ten opzichte van een statische werkverdeling. Voor heterogene meerdradige applicaties neemt de prestatie gemiddeld zelfs toe met 32%.

## Summary

#### **Multi-Cores and Simulation**

Over the past few decades, processors have evolved from relatively simple scalar in-order processors to complex multi-core processors with superscalar out-of-order cores. With increasing transistor counts and increasing core count due to Moore's Law, also comes an increase in complexity. As this trend continues, there emerges a growing need for tools that help the architect understand why a processor is performing the way it is and how design decisions impact performance. A software simulator is a tool that accurately predicts the behavior and performance of a processor: designs can be evaluated using a software model of the hardware which models the behavior and performance of all, or at least, the most important processor components. Obviously, a simulator needs to accurate, but the speed at which an application's performance can be evaluated (relative to native execution speed) is equally important. If simulation is too slow, this might be incompatible with tight time-to-market demands, forcing the architect to evaluate fewer design options, potentially yielding a less-than-optimal design.

This problem gets further compounded when considering representative multi-core workloads: a multi-core processor can execute multiple independent programs concurrently, therefore, any combination of benchmarks forms a potential multi-program workload. We explore the use of analytical modeling to increase multi-core simulation speed. Instead of using slow detailed simulation to evaluate performance for a large number of multi-program workloads and multi-core designs, we propose a methodology (the Multi-Program Performance Model, MPPM) in which detailed simulation is done for single-program workloads only. We then employ an iterative analytical model to estimate the impact of the sharing effects in the last-level caches when co-running programs on the multi-core processor. MPPM is both fast and accurate: we achieve simulation speedups of up to five orders of magnitude, and report an average performance prediction error of 2.3% and 2.9% for system throughput (STP) and average normalized turnaround time (ANTT), respectively. Additionally, we demonstrate that current practice of randomly picking a limited number of multi-program

workloads, can lead to incorrect design decisions in practical design scenarios,, ultimately resulting in sub-optimal designs.

### **Heterogeneous Multi-Core Processors**

Recently, heterogeneous multi-core architectures have been proposed: which integrate multiple core types on a single chip. The idea is that applications have different resource requirements during their execution and by matching the application's requirements to the core capabilities, a much higher level of energy-efficiency may be achieved.

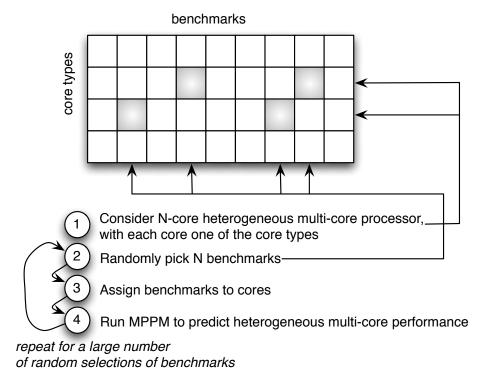

In this work, we aim at understanding how heterogeneity affects both chip throughput and per-program performance; how heterogeneous architectures compare to homogeneous architectures under said performance metrics; and how fundamental design choices, such as core type, cache size and off-chip bandwidth, affect performance. We use the MPPM framework to explore the large heterogeneous multi-core architecture design space. Because MPPM has linear-time complexity in the number of core types and programs of interest, it offers a unique opportunity for exploring the large space of both homogeneous and heterogeneous multi-core processors in limited time. We considered five different core types (ranging from a small scalar in-order core to a large 4-wide out-of-order core). We considered multiple last-level cache sizes and evaluated scenarios of varying off-chip bandwidth limits. Our analysis provides several interesting insights:

- Two core types provide most of the benefits from heterogeneity.

- Heterogeneity fundamentally trades per-program performance for chip throughput.

- Some homogeneous configurations are optimal for particular throughput versus per-program performance trade-offs.

- Job-to-core mapping is both crucial and challenging for heterogeneous multi-core processors to achieve optimum performance.

- Limited off-chip bandwidth alters some of the fundamental design choices in heterogeneous multi-core architectures.

### **Scheduling Heterogeneous Multi-cores**

There exists a fundamental challenge in the design space of heterogeneous multi-core processors, which is how best to schedule workloads on the most appropriate core type. Heterogeneous multi-cores can enable higher performance and reduced energy consumption (within a given power budget) if and only if workloads are executed on the most appropriate core

type. Because a lot of workloads show time-varying behavior, a good scheduling policy needs to be dynamic. Additionally, because processor die size continues to steadily increase, a scheduling policy needs to be scalable with the number cores and the number of core types.

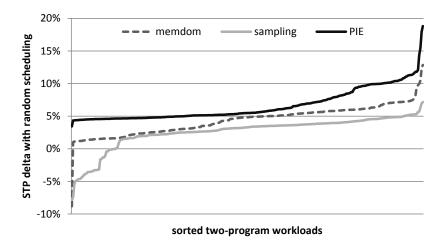

We propose Performance Impact Estimation (PIE), which collects basic characteristics from the application on the core that it is running on, and uses these as inputs to an analytical model to estimate performance of the application on the other core types. PIE uses a dynamic scheduling approach and is a flexible and scalable solution because it scales easily with the number of cores and core types. We evaluate PIE scheduling and report improvements in system performance by 5.5% on average over memory-dominance scheduling (conventional wisdom) and by 8.7% over sampling-based scheduling for a set of scheduling-sensitive workload mixes. Additionally, using insights gained from analytical modeling, we have shown that the state-of-the-art scheduling policy only works as expected when considering core types that do not differ significantly in their capabilities for exploiting parallelism.

### Fairness-Aware Scheduling

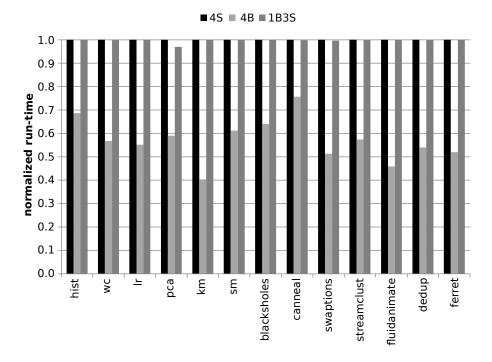

Previously, we focused on optimizing system throughput with PIE scheduling with little attention to fairness. Yet, guaranteeing that all threads make equal progress on heterogeneous multi-cores is important for both multi-threaded and multi-program workloads. Achieving high fairness means that all threads in the system are making equal progress proportional to isolated execution.

For multi-program workloads, fairness is important when it comes to system-level priorities and quality-of-service (QoS) because a heterogeneous system then behaves as a homogeneous one. For a multi-threaded workload, fairness is desirable because of thread synchronization: threads running on a powerful core will typically make faster progress than threads running on a small, low-performance core. When there is need for synchronization, the fast running threads will stall at the barrier until all other threads have reached the barrier.

We propose two techniques to achieve fairness-aware scheduling for heterogeneous multi-cores: equal-time scheduling strives at achieving high fairness by running each thread on each core type for an equal fraction of time. When the threads benefit differently from running on a big core however, equal-time scheduling will not necessarily yield high fairness. Alternatively, equal-progress scheduling can guarantee high fairness for these bases as well: by continuously monitoring progress and by changing the thread-to-core mapping to get equal amounts of work done (instead of time spent) for each thread in the system.

Fairness-aware scheduling improves fairness over pinned scheduling

as done by contemporary operating systems, and it also improves system throughput by enabling threads to run on a big core type for some fraction of time. For homogeneous multi-threaded workloads, we report an average 14% (and up to 25%) performance improvement over pinned scheduling through fairness-aware scheduling. For heterogeneous multi-threaded workloads; equal-progress scheduling improves performance by 32% on average.

# **Contents**

| 1 | Intr | oduction                                       | 1  |

|---|------|------------------------------------------------|----|

|   | 1.1  | Multi-Cores and Simulation                     | 1  |

|   | 1.2  | Multi-Core Analytical Modeling                 | 3  |

|   | 1.3  | Heterogeneous Multi-Core Processors            | 4  |

|   | 1.4  | Fairness-Aware Scheduling                      | 8  |

|   | 1.5  | Overview                                       | 9  |

| 2 | MP   | PM                                             | 11 |

|   | 2.1  | Introduction                                   | 11 |

|   | 2.2  | Multi-Program Performance Model                | 14 |

|   |      | 2.2.1 Single-core Simulation Profiling         | 16 |

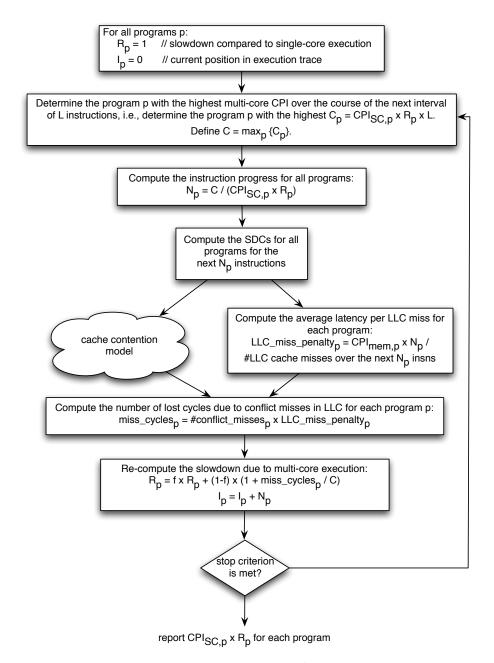

|   |      | 2.2.2 MPPM                                     | 17 |

|   |      | 2.2.3 Discussion                               | 20 |

|   | 2.3  | Experimental Setup                             | 21 |

|   | 2.4  | Model Evaluation                               | 22 |

|   |      | 2.4.1 Variability                              | 22 |

|   |      | 2.4.2 Accuracy                                 | 25 |

|   |      | 2.4.3 Speed                                    | 26 |

|   | 2.5  | Debunking Current Practice                     | 26 |

|   | 2.6  | Identifying Stress Workloads                   | 30 |

|   | 2.7  | Related Work                                   | 32 |

|   | 2.8  | Summary                                        | 35 |

| 3 | Het  | erogeneous Multi-Core Design                   | 37 |

|   | 3.1  | Introduction                                   | 37 |

|   | 3.2  | Multi-core Performance Modeling                | 41 |

|   | 3.3  | Design Space Exploration                       | 42 |

|   |      | 3.3.1 Heterogeneous multi-core design space    | 43 |

|   |      | 3.3.2 Multi-core performance                   | 44 |

|   | 3.4  | Experimental Setup                             | 46 |

|   | 3.5  | Results                                        | 47 |

|   |      | 3.5.1 Homogeneous multi-core processors        | 48 |

|   |      | 3.5.2 Pareto-optimal heterogeneous multi-cores | 48 |

xiv CONTENTS

|   |     | 3.5.3  | Limiting off-chip bandwidth                           | 51  |

|---|-----|--------|-------------------------------------------------------|-----|

|   |     | 3.5.4  | Impact of LLC size                                    | 53  |

|   |     | 3.5.5  | Which core types to employ in a heterogeneous design? | 55  |

|   |     | 3.5.6  | Job-to-core mapping                                   | 57  |

|   |     | 3.5.7  | Workloads                                             | 59  |

|   | 3.6 | Relate | ed Work                                               | 59  |

|   | 3.7 |        | nary                                                  | 61  |

| 4 | Het | erogen | eous Multi-Core Scheduling                            | 65  |

|   | 4.1 |        | luction                                               | 65  |

|   | 4.2 |        | ration                                                | 66  |

|   | 4.3 | Perfo  | rmance Impact Estimation (PIE)                        | 69  |

|   |     | 4.3.1  | Predicting MLP                                        | 72  |

|   |     | 4.3.2  | Predicting ILP                                        | 74  |

|   |     | 4.3.3  | Evaluating the PIE Model                              | 76  |

|   | 4.4 | Dyna   | mic Scheduling                                        | 80  |

|   |     | 4.4.1  | Quantifying migration overhead                        | 80  |

|   |     | 4.4.2  | Dynamic PIE Scheduling                                | 82  |

|   |     | 4.4.3  | Hardware support                                      | 83  |

|   | 4.5 | Exper  | rimental Setup                                        | 84  |

|   | 4.6 |        | ts and Analysis                                       | 85  |

|   |     | 4.6.1  | Private LLCs                                          | 85  |

|   |     | 4.6.2  |                                                       | 86  |

|   |     | 4.6.3  |                                                       | 87  |

|   | 4.7 |        | ed Work                                               | 88  |

|   | 4.8 |        | nary                                                  | 90  |

| _ |     |        | •                                                     |     |

| 5 |     |        | ware Scheduling                                       | 93  |

|   | 5.1 |        | duction                                               | 93  |

|   | 5.2 |        | ration                                                | 95  |

|   |     | 5.2.1  | Fairness                                              | 95  |

|   |     | 5.2.2  |                                                       | 96  |

|   |     | 5.2.3  | 1 0                                                   | 97  |

|   | 5.3 | Fairne | ess-Aware Scheduling                                  | 98  |

|   |     | 5.3.1  | Equal-time scheduling                                 | 99  |

|   |     | 5.3.2  | Equal-progress scheduling                             | 100 |

|   |     | 5.3.3  |                                                       | 102 |

|   |     | 5.3.4  |                                                       | 102 |

|   |     | 5.3.5  |                                                       | 103 |

|   | 5.4 | Exper  |                                                       | 104 |

|   |     | 5.4.1  | ±                                                     | 104 |

|   |     | 5.4.2  |                                                       | 104 |

|   | 5.5 | Evalu  |                                                       | 106 |

|   |     | 5.5.1  |                                                       | 106 |

| CONTENTS | XV |

|----------|----|

| CONTENTS | XV |

| _   |      | 5.5.2 Multi-threaded workloads |    |

|-----|------|--------------------------------|----|

| į   | 5.6  | Related Work                   | 11 |

| į   | 5.7  | Summary                        | 1  |

| 5 ] | Futu | re Work                        | 11 |

|     | 5.1  | Summary                        | 11 |

| (   | J. 1 | Summary                        | 11 |

|     |      | Future Work                    |    |

|     |      |                                | 12 |

xvi CONTENTS

# **List of Tables**

| 2.1 | Baseline processor configuration             | 21  |

|-----|----------------------------------------------|-----|

| 2.2 | Last-level cache (LLC) configurations        | 21  |

| 3.1 | Chip area cost model                         | 44  |

| 5.1 | Multi-threaded benchmarks used in this study | 105 |

# **List of Figures**

| 2.1 | General overview of MPPM                                      | 15  |

|-----|---------------------------------------------------------------|-----|

| 2.2 | The Multi-Program Performance Model                           | 18  |

| 2.3 | Variability in (a) STP and (b) ANTT as a function of the num- |     |

|     | ber of multi-program workload mixes                           | 23  |

| 2.4 | Accuracy of MPPM for predicting (a) STP and (b) ANTT;         |     |

|     | measured STP/ANTT on vertical axis versus predicted STP/AN    | JTT |

|     | on the horizontal axis.                                       | 24  |

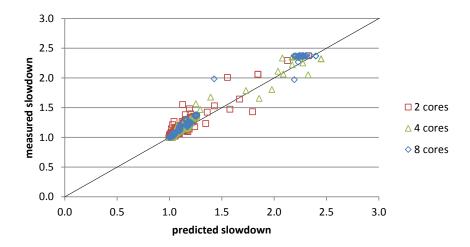

| 2.5 | Measured versus predicted relative per-program slowdown       |     |

|     | due to multi-core execution                                   | 27  |

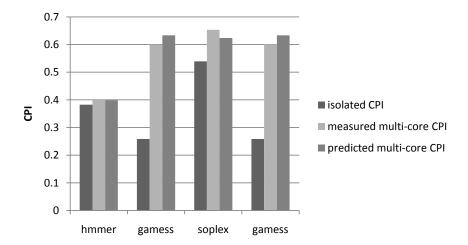

| 2.6 | Tracking the performance of individual programs in a multi-   |     |

|     | program workload consisting of two copies of gamess along     |     |

|     | with hmmer and soplex: isolated execution CPI, measured       |     |

|     | multi-core execution CPI (through simulation), and predicted  |     |

|     | multi-core execution CPI (through MPPM)                       | 27  |

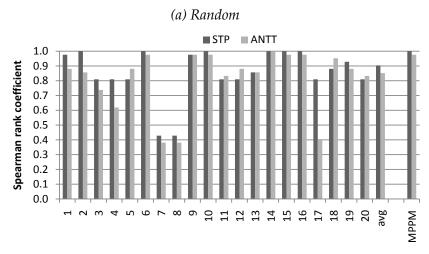

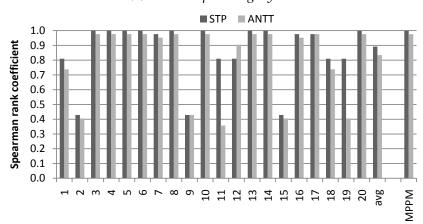

| 2.7 | Evaluating current practice of selecting random workload      |     |

|     | mixes: Rank correlation coefficient for 20 sets of 12-program |     |

|     | workloads versus MPPM. (a) Random selection of programs;      |     |

|     | and (b) Random selection of programs within program cate-     |     |

|     | gories                                                        | 28  |

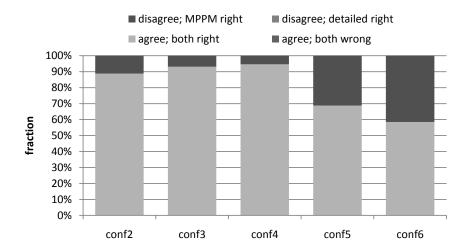

| 2.8 | Fractions of when current practice agrees or disagrees with   |     |

|     | MPPM, and when MPPM is correct and current practice is not.   | 31  |

| 2.9 | Identifying 4-program workloads with the worst STP            | 31  |

|     |                                                               | _   |

| 3.1 | Using MPPM for exploring the heterogeneous multi-core de-     |     |

|     | sign space                                                    | 42  |

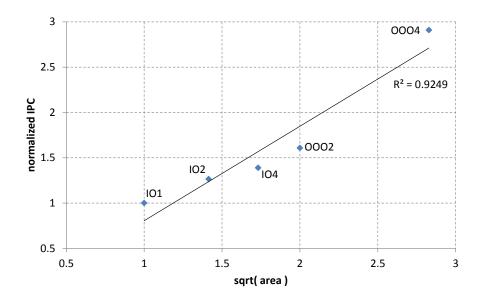

| 3.2 | Average normalized IPC for the five core configurations con-  |     |

|     | sidered in this study as a function of the square root of the |     |

|     | area counted in BCEs                                          | 46  |

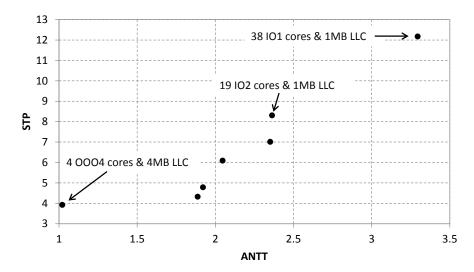

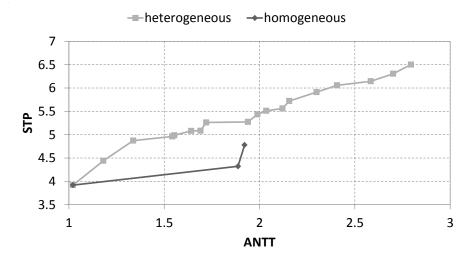

| 3.3 | Pareto-optimal homogeneous multi-core configurations as a     |     |

|     | function of STP (vertical axis) and ANTT (horizontal axis)    | 47  |

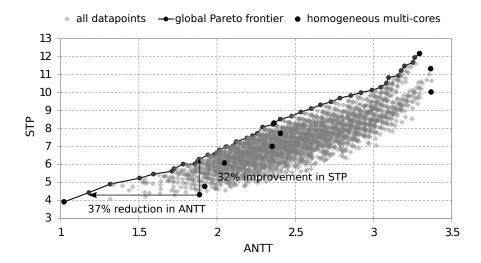

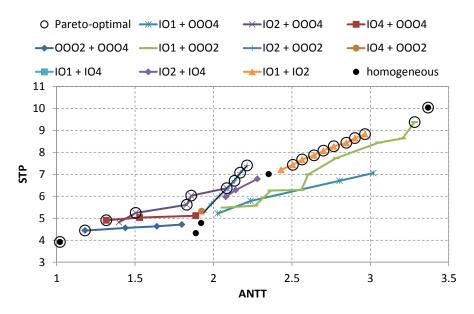

| 3.4 | Pareto frontier of multi-core configurations, along with all  |     |

|     | processor configurations explored including the homogeneous   |     |

|     | design points                                                 | 49  |

xx LIST OF FIGURES

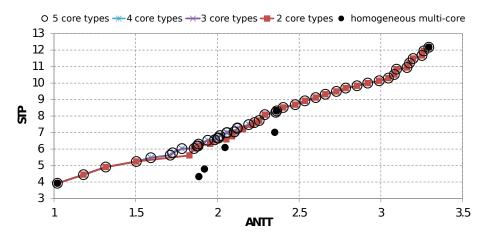

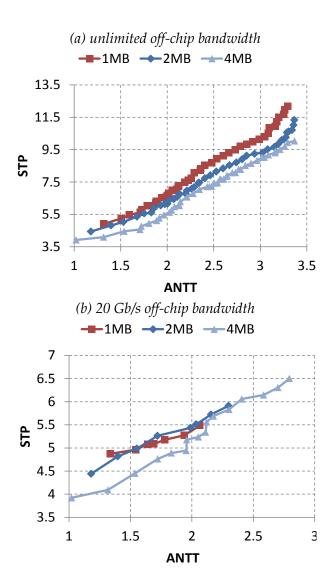

| 3.5  | Pareto frontier for heterogeneous multi-core architectures with |    |

|------|-----------------------------------------------------------------|----|

|      | a varying number of core types                                  | 51 |

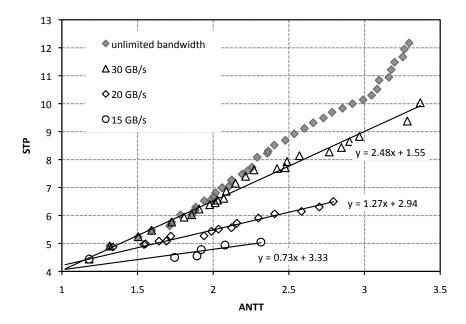

| 3.6  | Evaluating how off-chip bandwidth limitations affect het-       |    |

|      | erogeneous multi-core performance                               | 52 |

| 3.7  | Pareto frontier for heterogeneous and homogeneous multi-        |    |

|      | core designs under 20 GB/s off-chip bandwidth constraints.      | 53 |

| 3.8  | Evaluating how LLC size affects Pareto-optimal heteroge-        |    |

|      | neous multi-core performance under different off-chip band-     |    |

|      | width constraints                                               | 54 |

| 3.9  | Pareto frontiers for heterogeneous multi-cores with two core    |    |

|      | types, assuming 30 GB/s off-chip bandwidth                      | 55 |

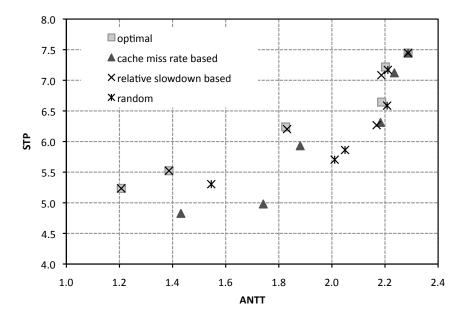

| 3.10 | Evaluating how job-to-core mapping affects heterogeneous        |    |

|      | multi-core performance                                          | 58 |

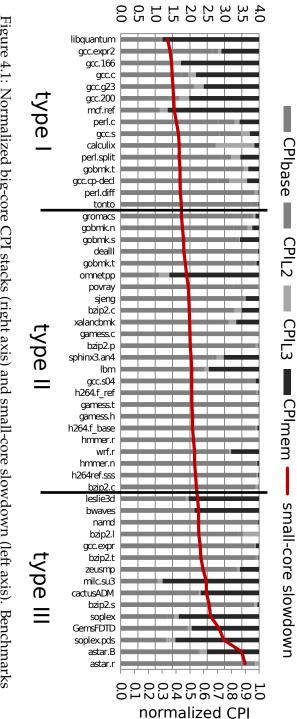

| 4.1  | Normalized big-core CPI stacks (right axis) and small-core      |    |

|      | slowdown (left axis). Benchmarks are sorted by their small-     |    |

|      | versus-big core slowdown                                        | 68 |

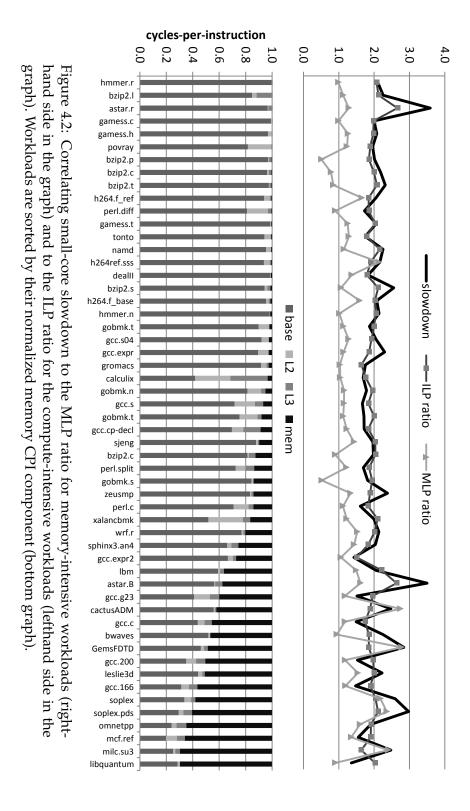

| 4.2  | Correlating small-core slowdown to the MLP ratio for memory-    |    |

|      | intensive workloads (righthand side in the graph) and to        |    |

|      | the ILP ratio for the compute-intensive workloads (lefthand     |    |

|      | side in the graph). Workloads are sorted by their normalized    |    |

|      | memory CPI component (bottom graph)                             | 70 |

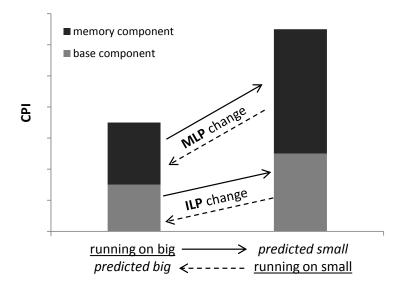

| 4.3  | Illustration of the PIE model                                   | 72 |

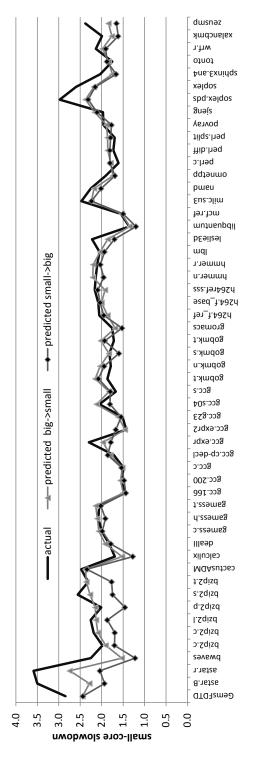

| 4.4  | Evaluating the accuracy of the PIE model                        | 75 |

| 4.5  | Comparing scheduling policies on a two-core heterogeneous       |    |

|      | multi-core                                                      | 77 |

| 4.6  | Comparing different scheduling algorithms for type-I and        |    |

|      | type-III workload mixes assuming a static setup                 | 78 |

| 4.7  | Evaluating PIE for heterogeneous multi-core with one big        |    |

|      | and three small cores (top graph), and three big cores and      |    |

|      | one small core (bottom graph)                                   | 79 |

| 4.8  | Dynamic execution profile of libquantum                         | 80 |

| 4.9  | Migration overhead for a shared LLC                             | 81 |

| 4.10 | Migration overhead for private powered-off LLCs                 | 81 |

| 4.11 | Migration overhead for private powered-on LLCs                  | 83 |

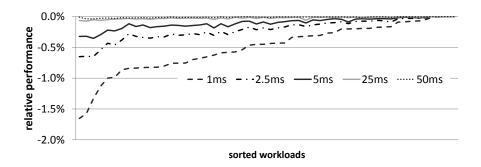

| 4.12 | Relative performance (STP) delta over random scheduling         |    |

|      | for sampling-based, memory-dominance and PIE schedul-           |    |

|      | ing, assuming private LLCs                                      | 86 |

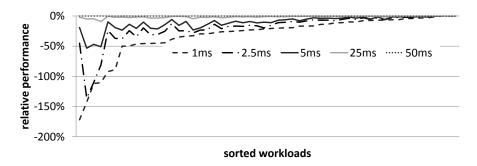

| 4.13 | Relative performance (STP) delta over random scheduling         |    |

|      | for sampling-based, memory-dominance and PIE schedul-           |    |

|      | ing, assuming an LRU-managed shared LLC                         | 87 |

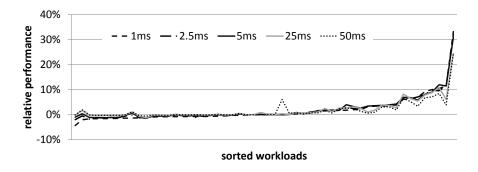

| 4.14 | Relative performance (STP) delta over random scheduling         |    |

|      | for sampling-based, memory-dominance and PIE schedul-           |    |

|      | ing, assuming an RRIP-managed shared LLC                        | 88 |

LIST OF FIGURES xxi

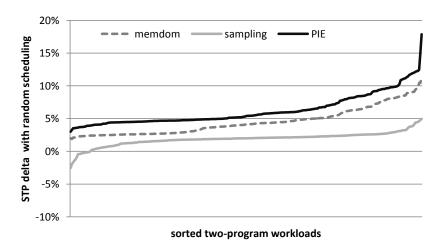

| 5.1        | Normalized run-time on a homogeneous multi-core with 4 small cores (4S), 4 big cores (4B), and a heterogeneous multi-core with one big and three small cores (1B3S) while keeping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|            | threads pinned to cores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 97  |

| 5.2        | Fairness for a 1B1S system for pinned versus throughput-<br>optimized scheduling using PIE for 500 randomly chosen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 00  |

| <b>-</b> 0 | two-job mixes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 98  |

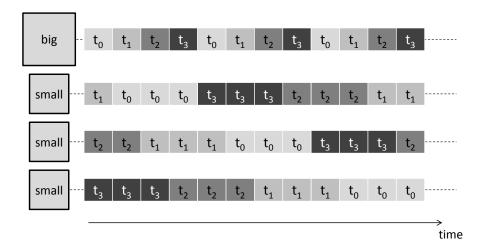

| 5.3        | Equal-time scheduling on a 1B3S heterogeneous multi-core.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 99  |

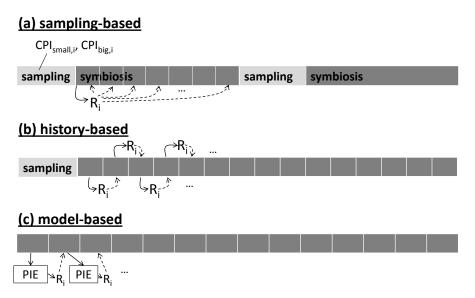

| 5.4        | Equal-progress scheduling: sampling-based, history-based                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 101 |

|            | and model-based                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 101 |

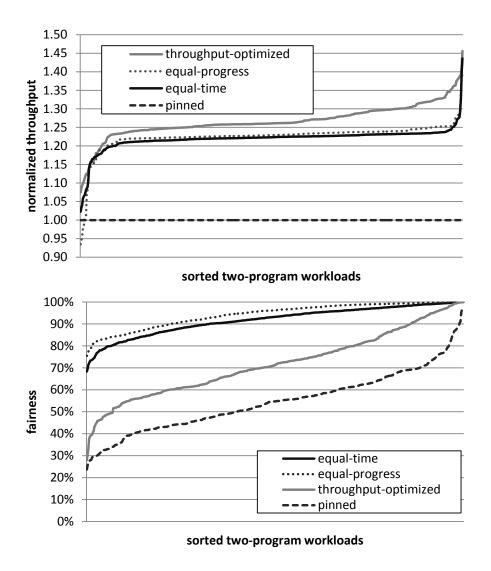

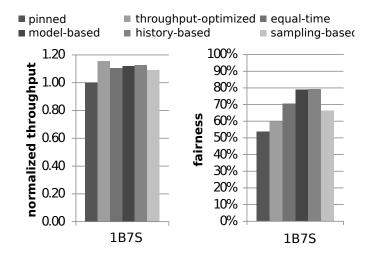

| 5.5        | Comparing scheduling algorithms relative to pinned scheduling in the scheduling algorithms relative to pinned schedulin |     |

|            | ing in terms of throughput (top graph) and fairness (bottom                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|            | graph) for a 1B1S heterogeneous multi-core with one big and one small core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 107 |

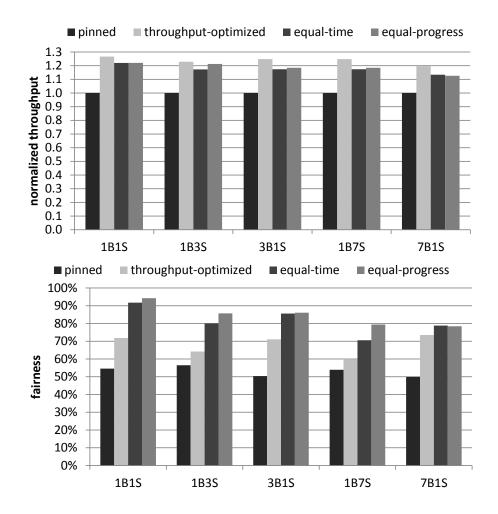

| 5.6        | Fairness-aware scheduling as a function of core count in terms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 107 |

| 5.6        | of throughput (top graph) and fairness (bottom graph)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 109 |

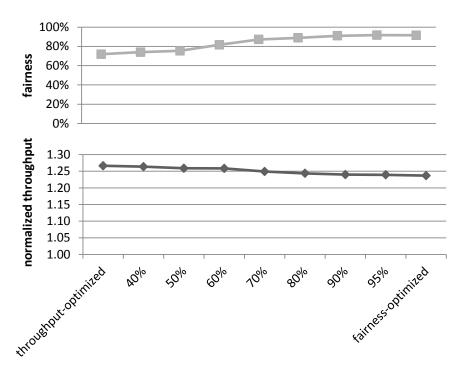

| 5.7        | Evaluating different methods for estimating the big-to-small-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 109 |

| 5.7        | core scaling factor in equal-progress scheduling for a 1B7S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|            | system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 110 |

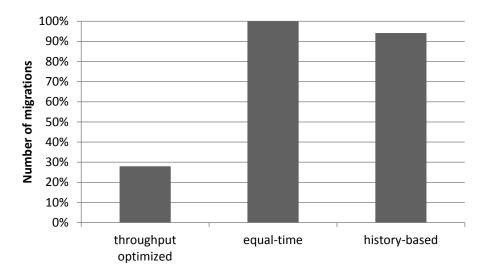

| 5.8        | The number of migrations across core types in a heteroge-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 110 |

| 5.0        | neous multi-core system under various scheduling policies.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 111 |

| 5.9        | Trade-off between fairness and throughput-optimized schedul-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| 0.,        | ing for a 1B1S system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 112 |

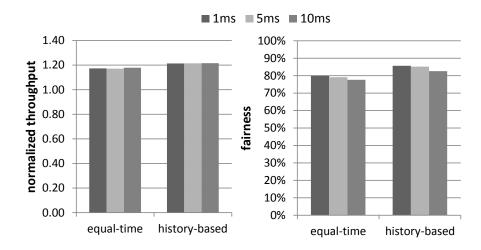

| 5.10       | System throughput and fairness for equal-time and equal-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|            | progress (history-based) scheduling as a function of time slice                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|            | granularity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 113 |