Methodes voor de prestatieanalyse van het schalingsgedrag van meerdradige programma's

Performance Analysis Methods for Understanding Scaling Bottlenecks in Multi-Threaded Applications

Kristof Du Bois

Promotoren: prof. dr. ir. L. Eeckhout, dr. ir. S. Eyerman Proefschrift ingediend tot het behalen van de graad van Doctor in de Ingenieurswetenschappen: Computerwetenschappen

Vakgroep Elektronica en Informatiesystemen Voorzitter: prof. dr. ir. J. Van Campenhout Faculteit Ingenieurswetenschappen en Architectuur Academiejaar 2013 - 2014

ISBN 978-90-8578-703-7 NUR 980

Wettelijk depot: D/2014/10.500/49

### Dankwoord

De weg naar een doctoraat is lang en verloopt over een parcours dat onderweg bezaaid is met verschillende hindernissen. Om deze tocht toch tot een goed einde te brengen, heb ik de afgelopen vier jaar de hulp en steun gekregen van een aantal bijzondere mensen. Daarom, nu de finishlijn van dit doctoraat bereikt is, is het dan ook de hoogste tijd om hier even bij stil te staan.

Allereerst wens ik mijn beide promotors, prof. Lieven Eeckhout en dr. Stijn Eyerman, oprecht te bedanken voor hun onvoorwaardelijke steun, inzichtvolle feedback en actieve hulp bij het schrijven van artikels en als apotheose deze thesis. Dat ik dit doctoraat tot een goed einde heb kunnen brengen, is voor een groot deel dankzij hen. Daarom overdrijf ik niet wanneer ik zeg dat ik mij geen betere begeleiding had kunnen voorstellen.

I would also like to thank dr. Jennifer B. Sartor for all her great help on writing papers, her assistance with Java, and for providing interesting ideas.

Daarnaast wil ik alle leden van mijn examencommissie bedanken, omdat ze de tijd namen om dit proefschrift te lezen, in vraag te stellen en te verbeteren. I would also like to address a special word of thanks to Prof. Margaret Martonosi and Prof. Per Stenström for accepting my invitation to be part of my PhD committee and their willingness to travel to Ghent, despite their busy schedules.

Wat ik bovendien nooit zal vergeten, is de aangename en vriendelijke werksfeer die heerst in onze onderzoeksgroep. Daarom wil ik alle collega's en in het bijzonder mijn bureaugenoten van de afgelopen jaren bedanken: Andy, Cecilia, Frederick, Max, Sam, Sander, Shoaib en Stijn. Ook Marnix, Michiel en Ronny mogen hier zeker niet ontbreken, onder meer omwille van hun zeer geapprecieerde hulp bij praktische problemen. Een heel speciaal woordje van dank heb ik voor Max en Klaas, twee collega's die al snel goede vrienden werden en waarmee ik ook naast het werk tal van onvergetelijke momenten mee heb beleefd.

Het Vlaams Supercomputer Centrum (VSC) voor het beschikbaar stellen van een enorme hoeveelheid rekenkracht en de feilloze technische ondersteuning.

Ten slotte wil ik mijn familie en vrienden bedanken om er steeds te zijn wanneer ik hen nodig heb. In het bijzonder wil ik mama en papa bedanken, eigenlijk kunnen woorden niet beschrijven hoe dankbaar ik jullie ben omwille van alle kansen die jullie mij gaven en me steeds steunen in alles wat ik doe en me vormden tot de persoon die ik nu ben, enz.

Kristof Du Bois Gent, 24 juni 2014

### Examencommissie

Prof. Rik Van de Walle, voorzitter

Decaan Faculteit Ingenieurswetenschappen en Architectuur

Universiteit Gent

Dr. Jennifer B. Sartor, secretaris

Vakgroep ELIS

Faculteit Ingenieurswetenschappen en Architectuur

Universiteit Gent

Prof. Lieven Eeckhout, promotor

Vakgroep ELIS

Faculteit Ingenieurswetenschappen en Architectuur

Universiteit Gent

Dr. Stijn Eyerman, promotor

Vakgroep ELIS

Faculteit Ingenieurswetenschappen en Architectuur

Universiteit Gent

Prof. Filip De Turck

Vakgroep Informatietechnologie

Faculteit Ingenieurswetenschappen en Architectuur

Universiteit Gent

Prof. Wolfgang De Meuter

Vakgroep Computerwetenschappen

Faculteit Wetenschappen

Vrije Universiteit Brussel

Prof. Margaret Martonosi

Princeton University USA

Prof. Per Stenström

Chalmers University

Sweden

### Leescommissie

Dr. Stijn Eyerman Vakgroep ELIS

Faculteit Ingenieurswetenschappen en Architectuur

Universiteit Gent

Prof. Filip De Turck

Vakgroep Informatietechnologie

Faculteit Ingenieurswetenschappen en Architectuur

Universiteit Gent

Prof. Wolfgang De Meuter

Vakgroep Computerwetenschappen

Faculteit Wetenschappen Vrije Universiteit Brussel

Prof. Margaret Martonosi

Princeton University

USA

Prof. Per Stenström

Chalmers University

Sweden

# Samenvatting

Gedurende vele jaren konden processorfabrikanten de prestatie van één enkele rekenkern verhogen. Er was immers een toename in transistordensiteit, als gevolg van de wet van Moore; en de schalingstheorie van Dennard stelde dat het verbruikte vermogen van een transistor schaalde met de grootte ervan. Tijdens deze periode resulteerde de trend van dalende transistorgroottes in een toenemende klokfrequentie en/of pijplijnbreedte van de processor, waarvan de Intel Pentium 4 een goed voorbeeld was. Aan deze trend kwam echter een einde omwille van beperkingen op het verbruikte vermogen en de daaraan gerelateerde koeling. Als reactie hierop introduceerden processorfabrikanten multi-core processors waarbij meerdere rekenkernen op eenzelfde chip geplaatst worden.

De verschillende rekenkernen op een multi-core processor kunnen onafhankelijk van elkaar instructies uitvoeren, maar ze moeten wel een aantal componenten op de chip delen, zoals bijvoorbeeld een cache of een bus. Het delen van deze componenten zorgt ervoor dat ze efficiënter gebruikt worden, maar heeft als nadeel dat de verschillende rekenkernen een invloed hebben op elkaars prestatie. Bijvoorbeeld in het geval van een gedeelde cache kan een rekenkern ervoor zorgen dat data van een andere rekenkern verwijderd wordt, wat leidt tot een toegenomen aantal missers voor de andere rekenkern.

Om ten volle gebruik te kunnen maken van deze meerdere rekenkernen moeten software-ontwikkelaars ook hun programma's aanpassen. Immers waar het vroeger voldoende was één draad te hebben per programma, is het nu interessanter om meerdere draden per programma te hebben zodanig dat de draden parallel kunnen uitvoeren op de verschillende rekenkernen. Meestal kunnen deze verschillende draden echter niet geheel onafhankelijk van elkaar uitvoeren omdat ze gegevens moeten delen of wachten op elkaar. Daarom voorziet software in synchronisatiemethodes. Deze synchronisatie is nodig om een correcte

viii SAMENVATTING

uitvoering van het programma te verzekeren, maar heeft als nadeel dat draden opnieuw een invloed hebben op elkaars uitvoering, net zoals bij de gedeelde hardware componenten.

Deze twee types van interacties tussen draden zijn bepalend voor de prestatie van meerdradige programma's, maar ze maken het tevens ook complex om deze prestatie te analyseren. Daarom introduceren we in dit proefschrift drie nieuwe methodes, genaamd *criticality stacks*, *bottle graphs* en *speedup stacks*, die het eenvoudig maken om de prestatie te analyseren van meerdradige programma's. De methodes tonen op een visuele manier aan software en hardware ontwikkelaars wat er gebeurt tijdens de uitvoering van een parallel programma.

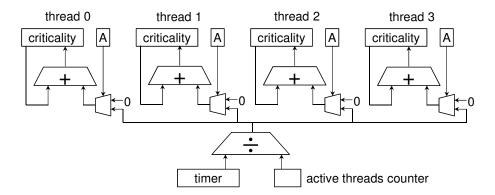

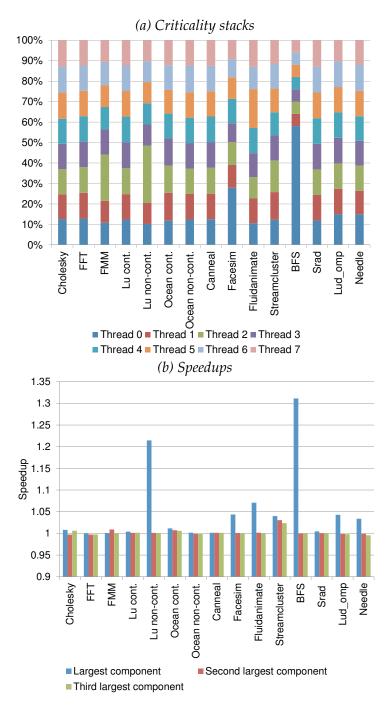

Onze eerste methode, criticality stacks, is bruikbaar voor het analyseren van onevenwicht tussen draden. Om deze stacks te construeren stellen we een nieuwe criticaliteitsmetriek voor, die onafhankelijk is van het type synchronisatie. De metriek wordt berekend aan de hand van de tijd dat een draad actief is, en het aantal andere draden dat tegelijk uitvoert. Gebruik makend van deze metriek splitsen criticality stacks de uitvoeringstijd van een applicatie op in een deel voor iedere draad. Hoe groter dit deel is voor een draad, hoe kritischer deze draad is voor de applicatie. Om deze metriek te berekenen tijdens de uitvoering van een programma stellen we een kleine hardwarecomponent voor. Deze component bevindt zich niet op het kritisch pad van de processor en verbruikt een kleine hoeveelheid aan extra vermogen. In dit werk gebruiken we criticality stacks voor het analyseren van onevenwicht tussen draden voor een verzameling van benchmarks, het sturen van optimalisatie van software, het dynamisch optimaliseren van de prestatie en het reduceren van het energieverbruik van parallelle applicaties.

De tweede methode, bottle graphs, stelt iedere draad van een meerdradig programma voor als een rechthoek in een grafiek. De hoogte van de rechthoek wordt berekend door middel van onze criticaliteitsmetriek, de breedte stelt het parallellisme van een draad voor (hoeveel andere draden er tegelijk met die draad actief zijn). De oppervlakte van de rechthoek is gelijk aan de totale uitvoeringstijd van de draad. De rechthoeken worden dan op elkaar gestapeld in een grafiek en gesorteerd naar gelang hun breedte, met de smalste rechthoeken bovenaan. Dit betekent dat draden met een beperkt parallellisme bovenaan in de grafiek zitten, als het ware in de hals van de fles waardoor we ze beschouwen als "bottlenecks" voor de applicatie. Hoewel bottle graphs geconstrueerd kunnen worden met de hardwarecomponent die we ont-

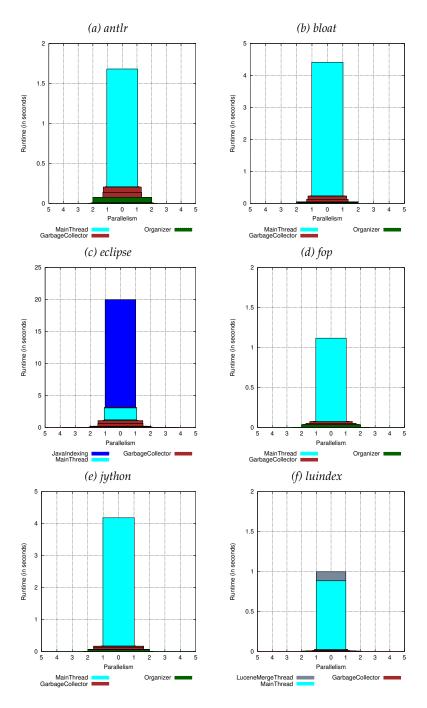

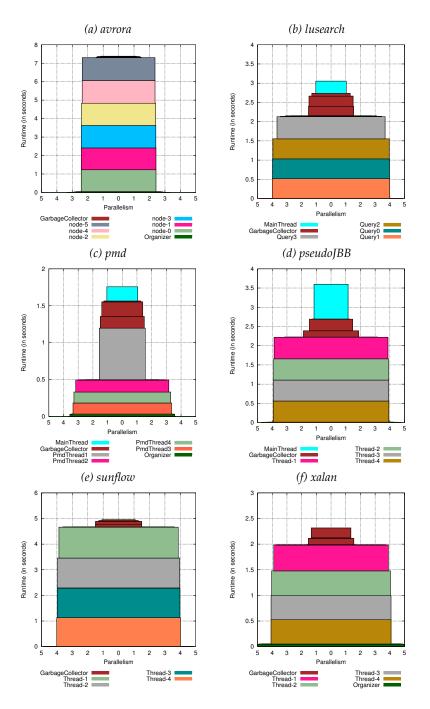

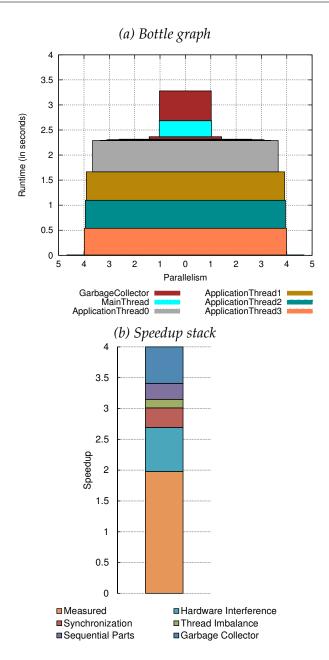

wierpen voor criticality stacks, hebben we een tweede profileringstechniek uitgewerkt volledig in software. Hierdoor kunnen we bottle graphs construeren van ongewijzigde programma's die uitvoeren op hedendaagse processors (en niet op een simulator). In dit werk gebruiken we bottle graphs voor het analyseren van de prestatie van Java programma's uitvoerend op Jikes RVM. We analyseren de prestatie van zowel applicatiedraden (die afkomstig zijn van de programma's), als servicedraden (die afkomstig zijn van de virtuele machine).

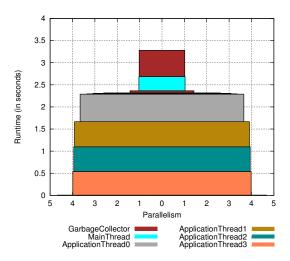

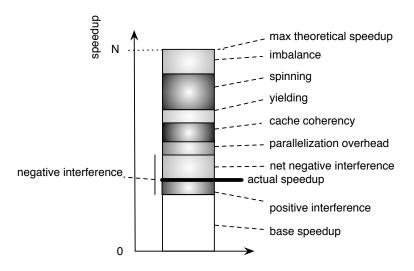

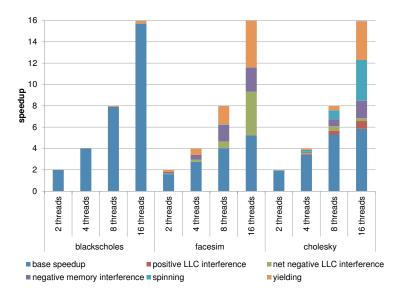

Onze derde methode, speedup stacks, toont de bereikte speedup (versnelling t.o.v. sequentiële uitvoering) van een applicatie en de verschillende componenten die speedup beperken in een gestapelde grafiek. De totale hoogte van de stapel is de maximaal bereikbare speedup; de onderste component in de stapel toont de bereikte speedup. De andere elementen in de stapel tonen de componenten die de speedup beperken en hun relatieve impact op de speedup. De intuïtie achter het concept van een speedup stack is dat door het reduceren van de invloed van een bepaalde component, de speedup van een applicatie proportioneel toeneemt met de grootte van die component in de stapel. In dit werk stellen we twee versies van speedup stacks voor. Onze eerste versie gebruikt extra hardwareondersteuning om speedup stacks te construeren tijdens de uitvoering van een programma. In deze versie bevat de speedup stack de volgende componenten: interferentie in de gedeelde cache en de geheugenhiërarchie, actief spinning, tijd uitgescheduled, en onevenwicht tussen draden. De profileringsmethode gebruikt een speciaal ontwikkelde tellerarchitectuur voor het opmeten van positieve en negatieve interferentie op de prestatie van draden. De extra overhead van deze profileringsmethode is beperkt tot 1,1 KB per rekenkern, dus ongeveer 18 KB voor een processor met 16 rekenkernen. In dit proefschrift gebruiken we deze versie van speedup stacks voor het identificeren van schalingsproblemen, het classificeren van benchmarks gebaseerd op hun schalingsgedrag, en voor het begrijpen van de prestatie van een gedeelde cache. Onze tweede versie van speedup stacks richt zich op Java-programma's. In deze versie bestaat de stapel uit andere componenten, namelijk garbage collection, sequentiële delen, onevenwicht tussen draden, synchronisatie en interferentie in de hardware. Voor het opmeten van deze speedup stacks hergebruiken we de profileringsmethode die we ontwierpen voor het genereren van bottle graphs, maar we passen deze methode aan om onze speedup stacks te kunnen construeren. Deze tweede versie van speedup stacks gebruiken we in dit werk voor het bestuderen van het schalingsgedrag

van Java-applicaties die uitvoeren op Jikes RVM.

Als besluit geloven we dat deze drie methodes inzichtelijk zijn voor zowel software- als hardware-ontwikkelaars voor het begrijpen van het schalingsgedrag, het identificeren van bottlenecks, en het optimaliseren van de prestatie van meerdradige programma's. Dit is geen eenvoudige taak omdat er interacties tussen draden zijn zowel in de hardware, omwille van gedeelde componenten, als in de software door synchronisatie tussen draden.

# Summary

For many years the increase in transistor density coming from Moore's law combined with Dennard's scaling made it possible for chip manufacturers to increase single-core performance. During this period the trend of decreased transistor size resulted in increased clock frequency and pipeline width of the processor, as exemplified by the Intel Pentium 4 design. However, because of power and cooling constraints related to it, this trend came to an end and chip manufacturers went in the direction of multi-core processors, where instead of one core doing all the work, there are multiple cores available on the same chip.

While these multi-core processors contain several cores that are able to work independently from each other, the different cores also share resources on the chip, for example, a last-level cache, an on-chip interconnection network, or a memory bus. Sharing these resources increases the utilization of the components, but comes with a drawback that cores can affect each other's performance. For example, in case of a shared cache, one core can evict data of another core leading to additional misses for the latter.

Also, in order to fully benefit from the available cores, software writers have to change the way they design their programs. Instead of having just one thread per program, it is now more beneficial to have multiple threads in the same application. Typically, those multiple threads can not work completely independently from each other, because at some point in their execution they have to share some data or they have to wait for each other. Therefore, software provides methods for synchronization. While this synchronization is necessary to achieve a correct execution of the program, it also has the disadvantage that – just like resource sharing – threads can affect each other's performance.

These two types of interactions between threads are determinative to the performance of a multi-threaded application, but make it also difficult to analyze the performance of these applications. Therefore we xii SUMMARY

introduce three new methods in this dissertation, called *criticality stacks*, *bottle graphs* and *speedup stacks*, to facilitate multi-threaded application performance analysis. Our methods visually show programmers and hardware designers what is going on during the execution of parallel programs.

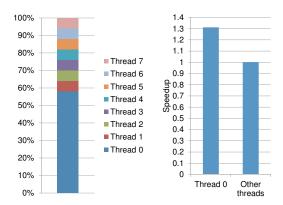

The first method, *criticality stacks*, is useful for visual analysis of parallel imbalance between threads. They are constructed using a novel, intuitive criticality metric that is independent of synchronization primitives, and takes into account both a thread's active running time and the number of co-executing threads. Using this metric, criticality stacks break down the total execution time of an application based on each thread's criticality. The higher the share of a thread in the stack, the more critical the thread is, meaning that the thread is more determinative of execution time. For calculating a thread's criticality value online during the execution of an application, we present a small hardware component. This component is off the processor's critical path and consumes a very small amount of power. We use criticality stacks in this work for analyzing parallel imbalance in a set of applications, guiding software source code optimization, dynamically optimizing the performance, and reducing the energy consumption of parallel programs.

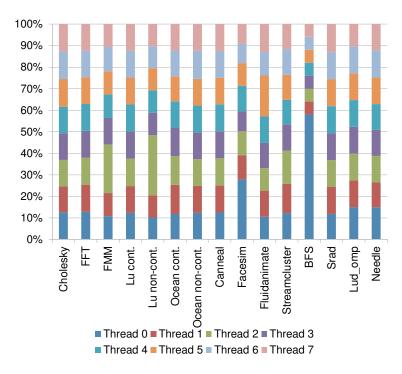

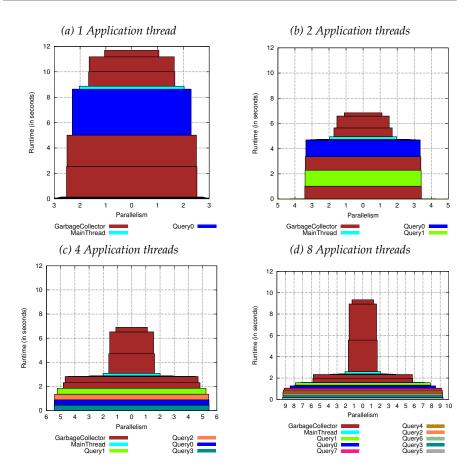

The second method, bottle graphs, shows each thread of a multithreaded application as a box in a stacked bar graph. The height of a box is a thread's execution time share (using our criticality metric) and the width is its parallelism (which is the average number of co-running threads). As a result, the total area of a box is equal to a thread's total running time. We sort boxes according to their width (parallelism) with the narrowest ones at the top, meaning that the threads in the neck of the bottle have low parallelism and therefore reveal themselves as parallel bottlenecks of the application. While we can construct bottle graphs with the hardware component that we designed for constructing criticality stacks, we designed a second profiling tool that is implemented completely in software. This allows us to construct bottle graphs for unmodified applications running on native hardware with minimal overhead. In this work we use bottle graphs to analyze Java applications running on top of Jikes RVM. We do an analysis of the behavior of the application threads (coming from the benchmarks), as well as the additional service threads introduced by the runtime, such as for memory management.

Our third method, *speedup stacks*, visualizes the achieved speedup of an application and the various scaling delimiters as a stacked bar.

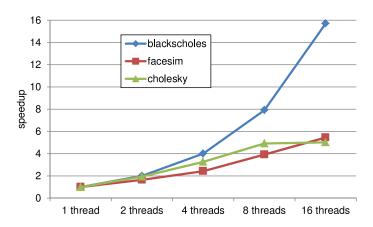

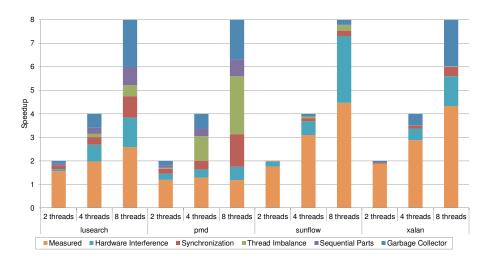

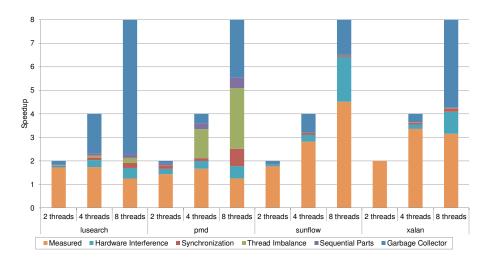

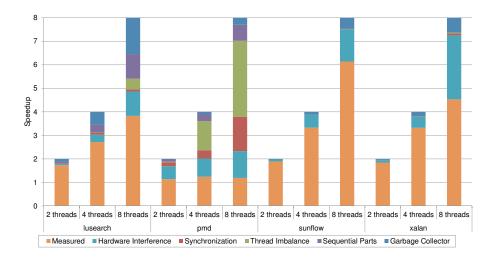

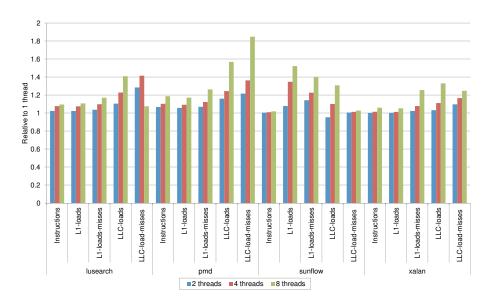

The total height of the stack is equal to the maximum achievable speedup over its single-threaded execution (excluding superlinear scaling), the bottom component in the stack shows the actual speedup, whereas the components on top of it show the various scaling delimiters and their relative impact on speedup. The intuition behind it is that by reducing the impact of a speedup delimiter, speedup improves proportional to the height of the component in the stack. In this disseratation we propose two versions of speedup stacks. The first version uses additional hardware support for computing a speedup stack during the execution of a program, at low overhead. The various speedup delimiters we include in these speedup stacks are: LLC and memory subsystem interference, spinning, yielding, imbalance. The profiling tool uses a dedicated counter architecture to estimate the impact of both negative and positive interference on the performance on threads. Hardware overhead of this tool is limited to 1.1 KB per core, or a total of 18 KB for a 16-core CMP. We use this version of speedup stacks in this work for identifying scaling bottlenecks, classifying benchmarks based on their scaling delimiters, and for understanding LLC performance. The second version of speedup stacks targets managed language applications, like Java programs. For this version of speedup stacks we include a different set of scaling delimiters: garbage collection, sequential parts, thread imbalance, synchronization between threads, and hardware interference. For constructing these speedup stacks, we extend the profiling tool that we designed for generating bottle graphs. This profiling tool is completely implemented in software. We use these speedup stacks for analyzing scaling behavior of Java applications running on Jikes RVM.

We believe the three methods proposed in this dissertation are fundamental to both software and hardware designers for understanding the behavior, identifying scaling bottlenecks, and optimizing the performance of multi-threaded applications. This analysis is not trivial due to threads that interact with each other in software through synchronization in the code and work balance, and in hardware through sharing resources.

xiv SUMMARY

# **Contents**

|   | Nec  | lerland | se samenvatting                 | vii |

|---|------|---------|---------------------------------|-----|

|   | Eng  | lish Su | ımmary                          | xi  |

| 1 | Intr | oductio | on                              | 1   |

|   | 1.1  | Motiv   | vation                          | 1   |

|   | 1.2  | Key C   | Challenges                      | 2   |

|   | 1.3  | •       | ributions in This Dissertation  | 2   |

|   | 1.4  | Other   | Research Activities             | 8   |

|   | 1.5  |         | view of This Dissertation       | 9   |

| 2 | Bac  | kgroun  | ad                              | 11  |

|   | 2.1  | Multi   | -Core Processors                | 11  |

|   |      | 2.1.1   | Resource Sharing                | 12  |

|   |      | 2.1.2   | Sources of Thread Interference  | 13  |

|   |      | 2.1.3   | Quantifying Thread Interference | 15  |

|   | 2.2  | Multi   | -Threaded Applications          | 18  |

|   | 2.3  |         | nary                            | 19  |

| 3 | Per  | forman  | ce Analysis Methods             | 21  |

|   | 3.1  | Introd  | duction                         | 21  |

|   | 3.2  | Critic  | ality Stacks                    | 22  |

|   |      | 3.2.1   | Constructing Criticality Stacks | 23  |

|   |      | 3.2.2   | Example Criticality Stacks      | 26  |

|   | 3.3  | Bottle  | Graphs                          | 27  |

|   |      | 3.3.1   | Constructing Bottle Graphs      | 28  |

|   |      | 3.3.2   |                                 | 30  |

|   | 3.4  | Speed   | lup Stacks                      |     |

|   |      | 3.4.1   | Constructing Speedup Stacks     |     |

|   |      | 342     |                                 | 39  |

xvi CONTENTS

|   |      | 3.4.3 Example Speedup Stacks                   | 41         |

|---|------|------------------------------------------------|------------|

|   | 3.5  | Speedup Stacks for Java                        | 42         |

|   |      | 3.5.1 Scaling Delimiters for Java              | 43         |

|   |      | 3.5.2 Example Speedup Stacks for Java          | 47         |

|   | 3.6  | Related Work                                   | 49         |

|   |      | 3.6.1 Performance Visualization                | 49         |

|   |      | 3.6.2 Criticality Analysis                     | 50         |

|   | 3.7  | Summary                                        | 50         |

| 4 | Crit | icality Stacks: Identifying Critical Threads   | 53         |

|   | 4.1  | Introduction                                   | 53         |

|   | 4.2  | Constructing Criticality Stacks                | 54         |

|   |      | 4.2.1 Identifying Running Threads              | 54         |

|   |      | 4.2.2 Calculating Criticality                  | 55         |

|   | 4.3  | Experimental Setup                             | 57         |

|   | 4.4  | Validation and Analysis                        | 59         |

|   |      | 4.4.1 Validation of Criticality Stacks         | 59         |

|   |      | 4.4.2 Comparison to Prior Criticality Metric   | 61         |

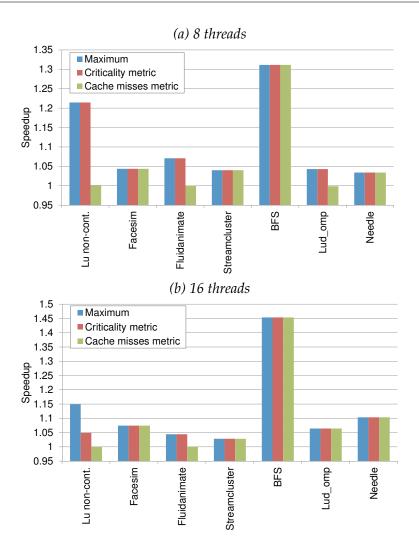

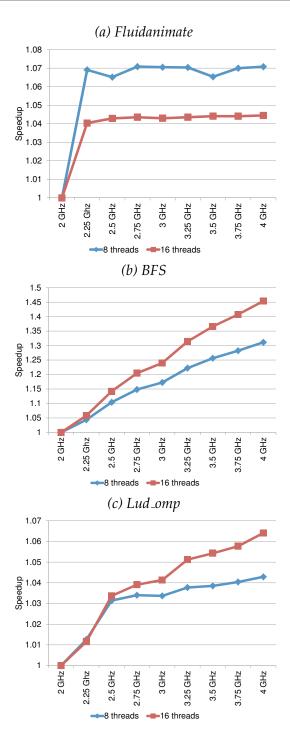

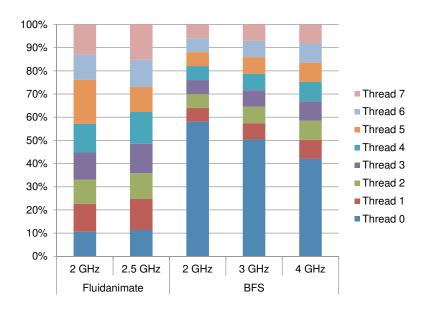

|   |      | 4.4.3 Varying the Amount of Frequency Scaling  | 63         |

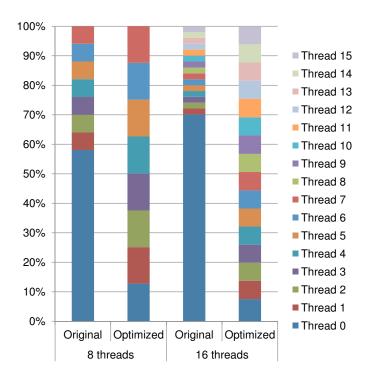

|   |      | 4.4.4 Steering Software Optimization           | 65         |

|   | 4.5  | Summary                                        | 67         |

| 5 | Bott | ele Graphs: Visualizing Per-Thread Performance | 69         |

|   | 5.1  | Introduction                                   | 69         |

|   | 5.2  | Constructing Bottle Graphs                     | 70         |

|   | 5.3  | Experimental Setup                             | <b>7</b> 3 |

|   | 5.4  | Jikes RVM and Benchmark Analysis               | 75         |

|   |      | 5.4.1 Garbage Collection Performance Analysis  | 75         |

|   |      | 5.4.2 Application Performance Analysis         | 81         |

|   |      | 5.4.3 Compiler Performance Analysis            | 82         |

|   |      | 5.4.4 Solving the Poor Scaling of Pmd          | 83         |

|   |      | 5.4.5 Comparing Jikes to OpenJDK               | 87         |

|   | 5.5  | Related Work                                   | 90         |

|   |      | 5.5.1 Comparison to IBM WAIT                   | 91         |

|   |      | 5.5.2 Java Parallelism Analysis                | 92         |

|   | 5.6  | Summary                                        | 93         |

| 6 | Spe  | edup Stacks: Analyzing Application Scaling     | 95         |

|   | 6.1  | Introduction                                   | 95         |

|   | 6.2  | Speedup Stacks Measured in Hardware            | 96         |

|   |      | 62.1 Constructing Speedup Stacks               | 96         |

| CONTENTS xvii |                        |                                   | xvii                                   |

|---------------|------------------------|-----------------------------------|----------------------------------------|

|               | 6.3                    | 6.2.3 Validation                  | 106<br>107<br>115<br>120<br>121<br>123 |

|               | 6.4                    | , 11                              | 124<br>130                             |

| 7             | <b>Dyr</b> 7.1 7.2 7.3 | Introduction                      | 131<br>131<br>132<br>134               |

|               | 7.4<br>7.5<br>7.6      | 7.3.2 Comparison to Previous Work | 137<br>138<br>139<br>141<br>142        |

| 8             | Con                    | nclusions and Future Work         | 143                                    |

|               | 8.1                    | Summary                           |                                        |

|               | 8.2                    | Future Work                       | 146                                    |

xviii CONTENTS

# **List of Figures**

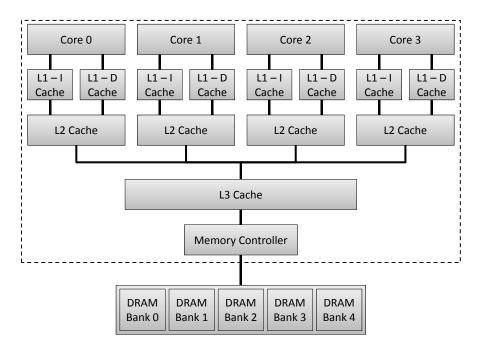

| 2.1  | Example of a multi-core processor along with an off-chip memory component. The dashed line indicates the chip boundary.                        | 12 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------|----|

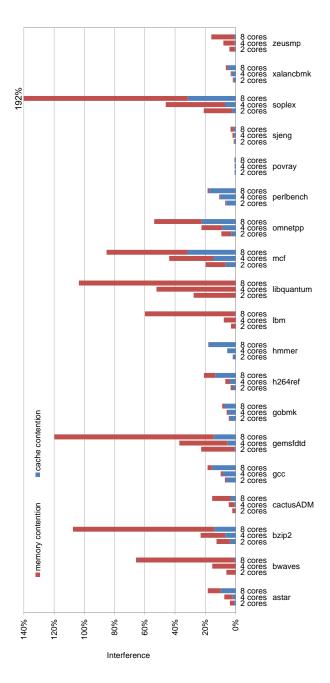

| 2.2  | Impact of inter-thread interference on per-thread performance for 2, 4 and 8 cores, breaking up interference in cache versus memory contention | 16 |

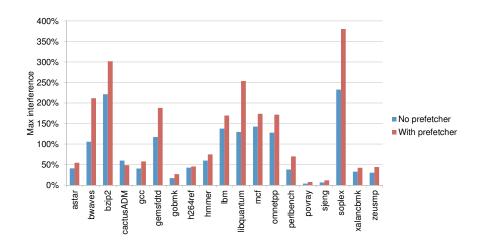

| 2.3  | The impact of prefetching on interference on an eight-<br>core system (maximum interference is reported across 10<br>job mixes per benchmark)  | 17 |

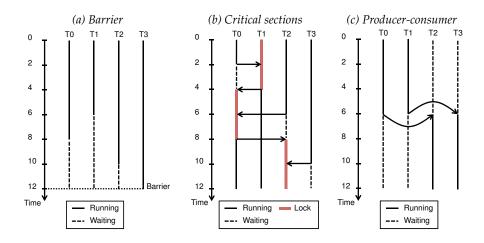

| 2.4  | Examples of synchronization between threads of a multi-<br>threaded application                                                                | 19 |

| 3.1  | BFS's criticality stack and total program speedups from accelerating the identified critical and non-critical threads.                         | 22 |

| 3.2  | Criticality calculation example                                                                                                                | 24 |

| 3.3  | Criticality stacks for all benchmarks with 8 threads                                                                                           | 26 |

| 3.4  | Example of a bottle graph: The lusearch DaCapo benchmark with 4 application threads.                                                           | 28 |

| 3.5  | Bottle graphs for all single-threaded benchmarks with 2 GC threads.                                                                            | 31 |

| 3.6  | Bottle graphs for all multi-threaded benchmarks with 2 GC threads and 4 application threads                                                    | 32 |

| 3.7  | Speedup as a function of the number of cores for blackscholes, facesim (both PARSEC) and cholesky (SPLASH-2).                                  | 34 |

| 3.8  | Illustrative speedup stack                                                                                                                     | 36 |

| 3.9  | Breaking up per-thread performance for computing speedu                                                                                        |    |

|      | stacks                                                                                                                                         | 37 |

| 3.10 | Speedup stacks as a function of the number of threads for blackscholes, facesim and cholesky                                                   | 41 |

| 3.11 | Example of applications threads in a managed language environment                                     | 44 |

|------|-------------------------------------------------------------------------------------------------------|----|

| 3.12 | Example of a bottle graph and speedup stack: The lusearch DaCapo benchmark with 4 application threads | 48 |

| 4.1  | Hardware device for online criticality calculation ('A' is the active bit per thread)                 | 56 |

| 4.3  | corresponding speedups by accelerating one thread Comparison between our and a prior metric, and the  | 60 |

| 1.0  | maximum achievable speedup by accelerating one thread.                                                | 62 |

| 4.4  | Impact of frequency scaling on achieved speedup                                                       | 64 |

| 4.5  | Impact of frequency scaling on criticality stacks                                                     | 65 |

| 4.6  | Example of using criticality stacks as a guide for software optimization (BFS benchmark)              | 66 |

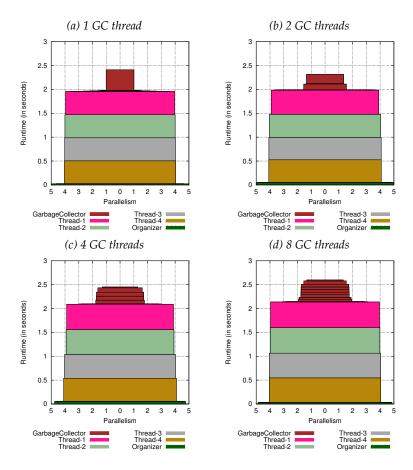

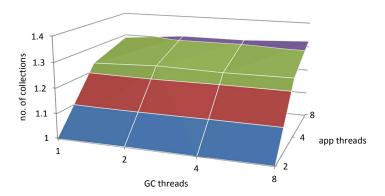

| 5.1  | Xalan: scaling of GC threads with 4 application threads                                               | 76 |

| 5.2  | Xalan: scaling of application threads with 2 GC threads.                                              | 77 |

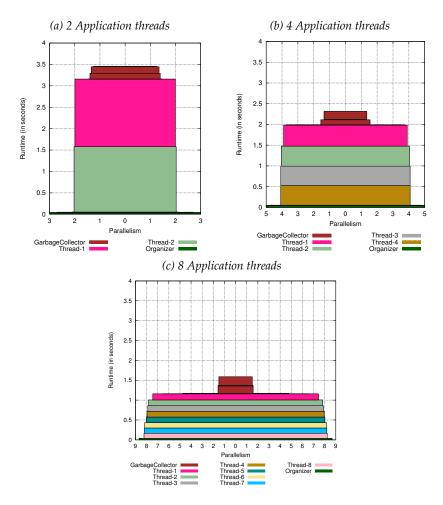

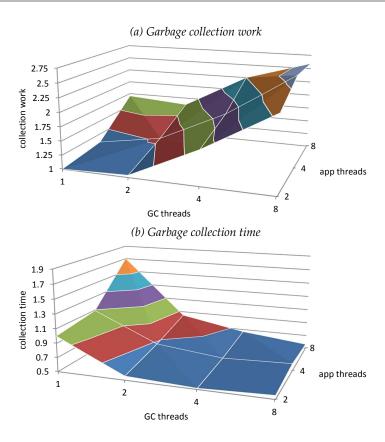

| 5.3  | Average garbage collection work (a) and time (b) as a                                                 | ,, |

| 0.0  | function of application and GC thread count (multi-threa-                                             |    |

|      | ded applications)                                                                                     | 78 |

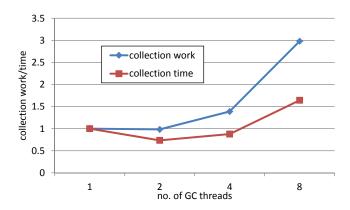

| 5.4  | Average collection work and time as a function of GC                                                  |    |

|      | thread count (single-threaded applications)                                                           | 79 |

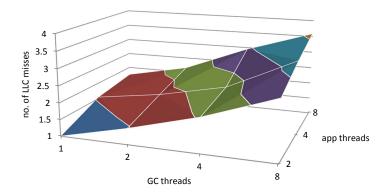

| 5.5  | Average number of LLC misses as a function of applica-                                                |    |

|      | tion and GC thread count (multi-threaded applications).                                               | 79 |

| 5.6  | Average number of collections as a function of applica-                                               |    |

|      | tion and GC thread count (multi-threaded applications).                                               | 80 |

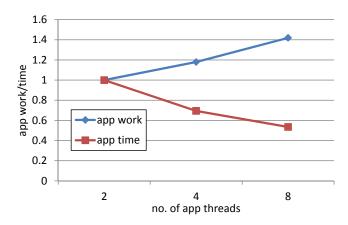

| 5.7  | Average application work and time as a function of ap-                                                |    |

|      | plication thread count (multi-threaded applications)                                                  | 81 |

| 5.8  | Jython: behavior of Organizer thread over different iter-                                             |    |

|      | ations for 4 GC threads                                                                               | 83 |

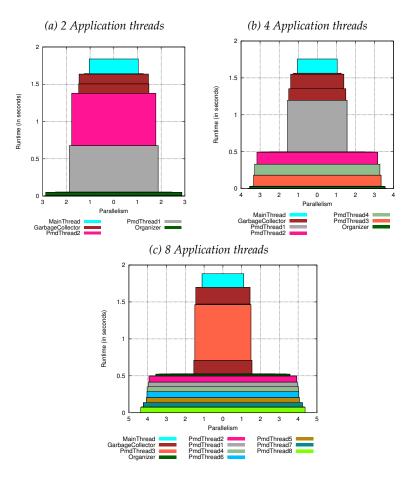

| 5.9  | Pmd: scaling of application threads with 2 GC threads                                                 |    |

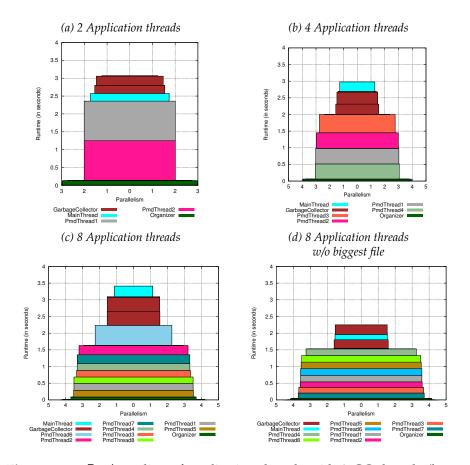

|      | (default input set)                                                                                   | 84 |

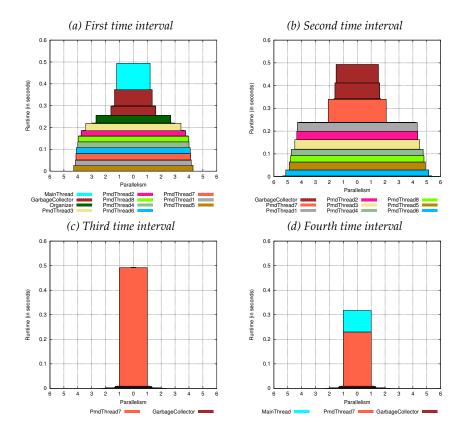

| 5.10 | Pmd: bottle graphs taken every 0.5 seconds with 2 GC                                                  |    |

|      | threads and 8 application threads (default input set)                                                 | 85 |

| 5.11 | Pmd: scaling of application threads with 2 GC threads                                                 |    |

|      | (large input set). For the fourth graph, the biggest source                                           |    |

|      | file is removed from the input set                                                                    | 86 |

| 5.12 | PseudoJBB: scaling of GC threads on OpenJDK, with 4                                                   |    |

|      | application threads                                                                                   | 88 |

| 5.13           | Average OpenJDK garbage collection work (a) and time (b) as a function of application and GC thread count (multi-                                                                                                                         | _                                 |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

|                | threaded applications)                                                                                                                                                                                                                    | 89                                |

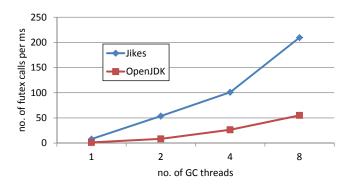

| 5.14           | Average number of futex calls per ms during garbage collection as a function of GC thread count, with 4 application threads (multi-threaded applications)                                                                                 | 90                                |

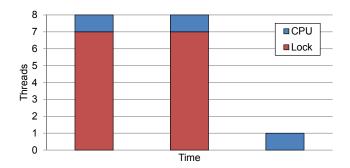

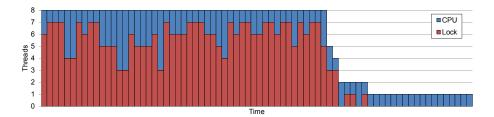

| 5.15           | Output of WAIT for pmd running on OpenJDK with 8 application and 2 GC threads using a 1 second sampling rate                                                                                                                              | 91                                |

| 5.16           | Output of WAIT for pmd running on OpenJDK with 8 application and 2 GC threads using a 50 millisecond sampling rate.                                                                                                                       | 92                                |

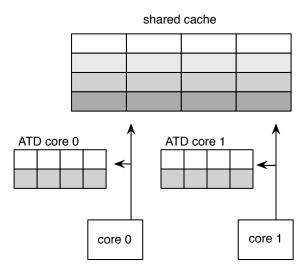

| 6.1            | The ATD samples a number of sets in the shared cache to identify inter-thread misses                                                                                                                                                      | 97                                |

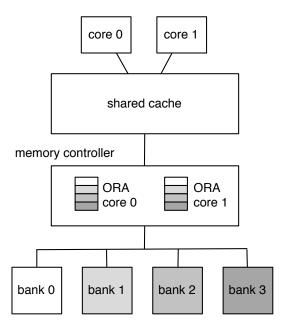

| 6.2            | The ORA keeps track of the most recently accessed row per memory bank per core                                                                                                                                                            | 100                               |

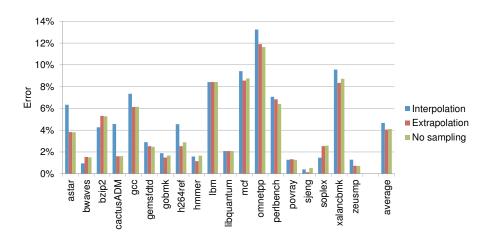

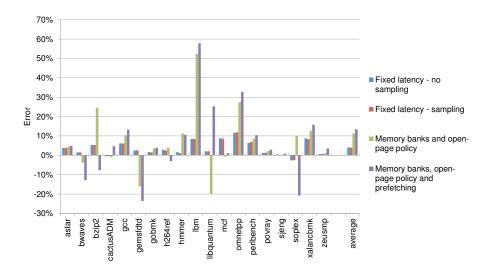

| 6.3            | Average isolated execution time estimation error per benchmark for Equation 6.1 and 6.2 (eight cores, fixed memory                                                                                                                        |                                   |

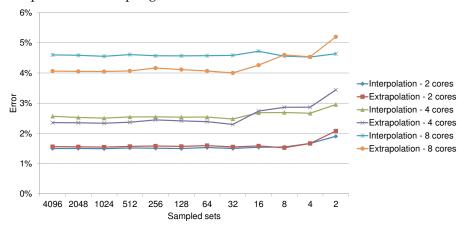

| 6.4            | latency, 32 sampled sets), compared to no sampling Average isolated execution time estimation error for the interpolation and extrapolation approaches as a function of the number of sampled sets; we assume fixed memory access latency | <ul><li>109</li><li>109</li></ul> |

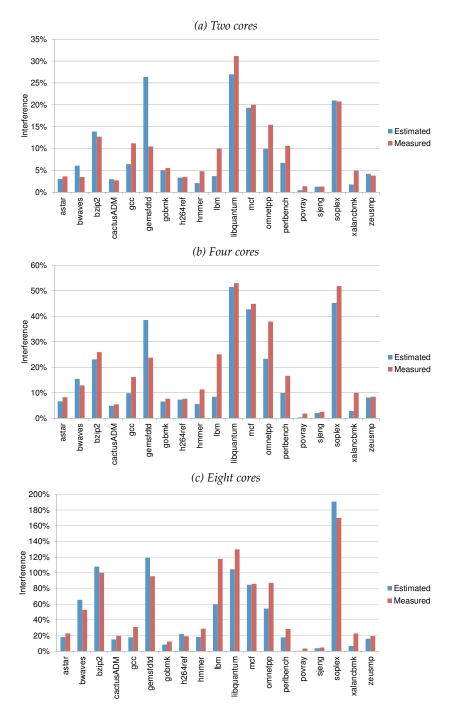

| 6.5            | Estimated versus measured interference for (a) a dual-core, (b) a quad-core, and (c) an eight-core system                                                                                                                                 | 111                               |

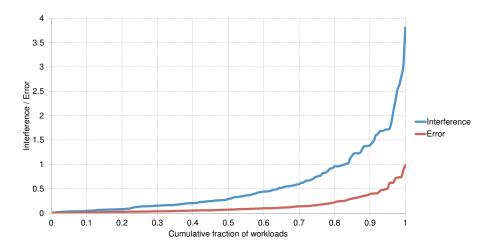

| 6.6            | Interference and error for estimating isolated execution time for an 8-core processor; workloads are sorted along                                                                                                                         |                                   |

| . <del>.</del> | the horizontal axis.                                                                                                                                                                                                                      | 112                               |

| 6.7<br>6.8     | Error analysis per benchmark for an 8-core processor Actual speedup and estimated speedup for all bench-                                                                                                                                  | 113                               |

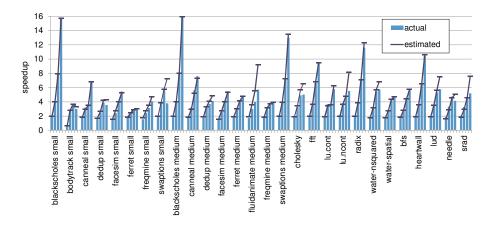

|                | marks for 2, 4, 8 and 16 threads                                                                                                                                                                                                          | 114                               |

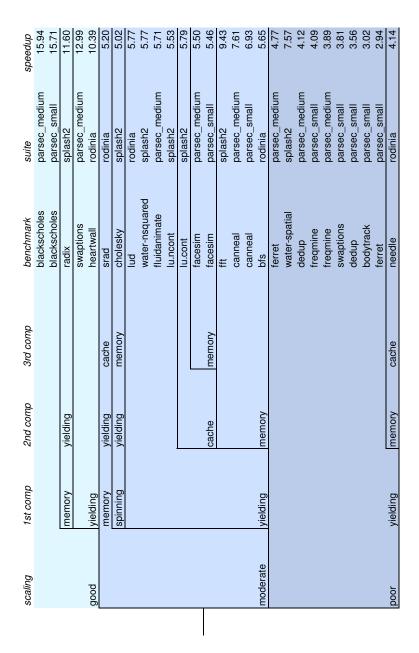

| 6.9            | Tree graph showing main speedup delimiter components for each benchmark for 16 threads                                                                                                                                                    | 117                               |

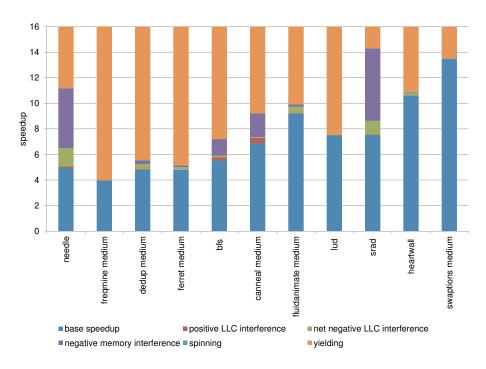

| 6.10           | Speedup stacks for a selection of benchmarks with 16 threads                                                                                                                                                                              | 118                               |

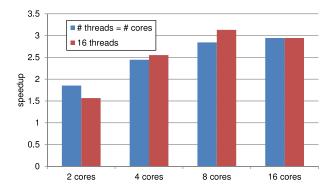

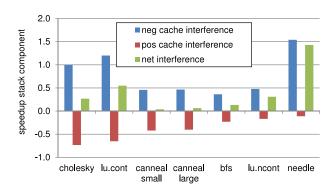

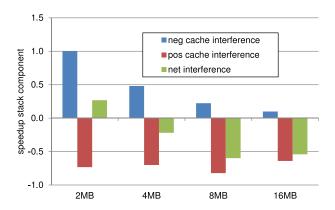

| 6.11           | Speedup numbers for ferret as a function of the number of cores. The number of threads equals the number of cores (left bars) or equals 16 (right bars)                                                                                   | 118                               |

| 6.12           | Negative, positive and net LLC interference components.                                                                                                                                                                                   |                                   |

| Negative, positive and net interference components for      |                                    |

|-------------------------------------------------------------|------------------------------------|

|                                                             | 120                                |

| Speedup stacks for all applications with a stop-the-world   |                                    |

| garbage collector (2×minimum heap size)                     | 124                                |

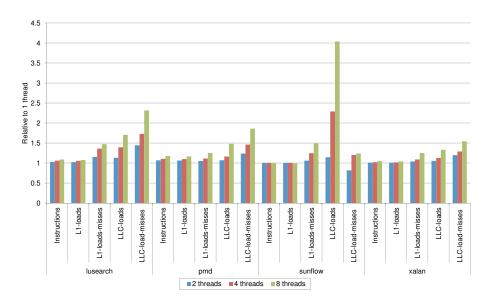

| Data from hardware performance counters for all appli-      |                                    |

| cations using a stop-the-world garbage collector. (Data     |                                    |

| normalized to one application thread.)                      | 125                                |

| Speedup stacks for all applications with a concurrent garba | ge                                 |

|                                                             | _                                  |

|                                                             |                                    |

|                                                             | 127                                |

|                                                             |                                    |

|                                                             |                                    |

|                                                             |                                    |

|                                                             |                                    |

|                                                             | 129                                |

| r                                                           |                                    |

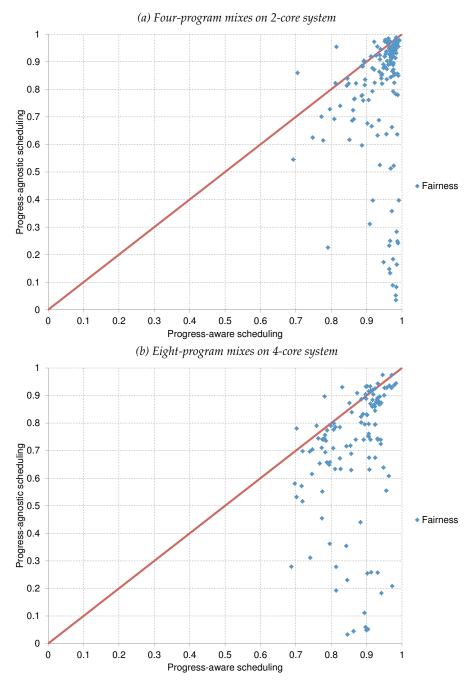

| Fairness results for progress-aware and progress-agnostic   |                                    |

| scheduling for (a) 4-program mixes on 2 cores, and (b) 8-   |                                    |

| program mixes on 4 cores                                    | 133                                |

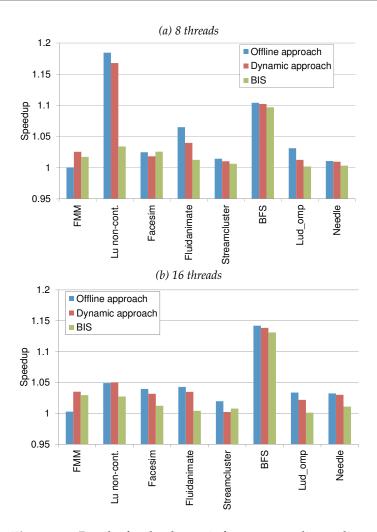

| Results for the dynamic frequency scaling policy            | 137                                |

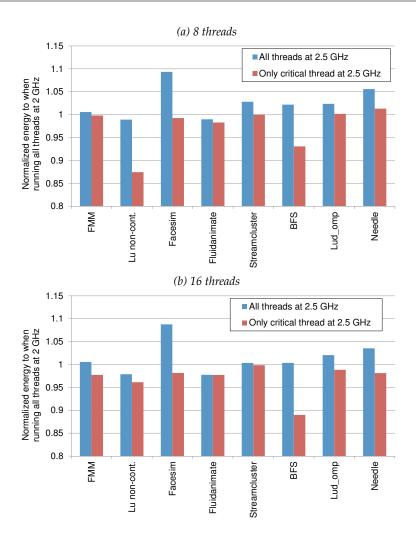

| Comparison of energy consumed when running all threads      |                                    |

| at 2.5 GHz and only the most critical at 2.5 GHz using      |                                    |

| ,                                                           |                                    |

| 2 GHz                                                       | 140                                |

|                                                             | cholesky as a function of LLC size |

# **List of Tables**

| 1.1 | Overview of contributions in this dissertation                                                               |

|-----|--------------------------------------------------------------------------------------------------------------|

| 4.1 | Simulated multi-core processor configurations for criticality stacks                                         |

| 4.2 | Considered benchmarks for criticality stacks                                                                 |

| 5.1 | Considered benchmarks for bottle graphs and kernel module overhead. ST=single-threaded, MT=multi-threaded 74 |

| 6.1 | Considered benchmarks for speedup stacks 106                                                                 |

| 6.2 | Simulated multi-core processor configurations for speedup                                                    |

|     | stacks                                                                                                       |

| 6.3 | Considered benchmarks for speedup stacks measured in                                                         |

|     | software                                                                                                     |

### List of Abbreviations

ATD Auxiliary Tag Directory

CMP Chip-Multiprocessor

CPI Cycles Per Instructions

DTLB Data Translation Lookaside Buffer

GC Garbage Collection

HPC High-Performance Computing

IPC Instructions Per Cycle

JVM Java Virtual Machine

L1 Level 1

L2 Level 2

L3 Level 3

LLC Last-Level Cache

MLP Memory-Level Parallelism

MPI Message Passing Interface

MSHR Miss Status Holding Register

OS Operating System

PARSEC Princeton Application Repository for Shared-Memory Com-

puters

RVM Research Virtual Machine

| xxvi   | LIST OF ABBREVIATIONS                            |

|--------|--------------------------------------------------|

| SMP    | Shared-Memory Processor                          |

| SMT    | Simultaneous Multi-Threading                     |

| SPLASH | Stanford Parallel Applications for Shared-Memory |

Whole-system Analysis of Idle Time

WAIT

### **Chapter 1**

### Introduction

#### 1.1 Motivation

While multi-core processors improve overall chip throughput and utilization, sharing hardware resources among the cores in caches, the on-chip interconnection network, and memory bus, leads to an unpredictable performance of the individual threads running on a multi-core processor. This is because co-executing threads interfere with each other in the shared hardware resources. This interference between threads can either have a negative impact on the performance of an application, meaning that the execution time of the threads becomes longer during multi-core execution compared to an isolated execution of the threads (which is without competing for hardware resources), or it can have a positive impact on performance, meaning that the execution time of threads becomes shorter during multi-core execution.

The advent of multi-core processors also poses new challenges to software designers, because they have to find ways to make use of those multiple available cores. These days, most programmers do this by parallelizing their software, which means that, instead of having one thread doing all the work, the work is now divided between several threads that are each doing a part of the total work. While this idea is simple, the implementation of this concept is often complicated, because the different threads typically have to share data, which means there has to be synchronization between the threads.

2 Introduction

Just like resource sharing, this synchronization between threads leads to threads that affect each other's performance, resulting in a poor scaling of an application. This means that the execution time of a multi-threaded application is not proportional to the number of threads or available cores in the system. Therefore, it is vital for both programmers and processor designers to understand multi-threaded application behavior in order to optimize performance and to design future hardware.

### 1.2 Key Challenges

Analyzing multi-threaded programs and identifying scaling bottlenecks is very challenging, but it is necessary to obtain good parallel performance. The reasons why it is a complicated task, is that threads interact with each other because of resource sharing in the underlying hardware and due to synchronization between the threads. This means that, if we want to analyze the performance of this type of applications, we have to measure and quantify the impact of these interactions across various layers in the computer system stack, including both hardware and software. Apart from measuring, it is also challenging to represent this data into graphs that can be easily interpreted by software developers without having to know the exact details about the underlying hardware platform.

Besides analyzing, it's also challenging to optimize the performance of multi-threaded applications. We will see later in this work that accelerating a particular thread of an application at a certain point in the execution leads to a performance gain, while accelerating other threads does not change performance, but wastes energy. The challenge here is to identify which threads need to be accelerated at which moment during the execution.

#### 1.3 Contributions in This Dissertation

This dissertation presents new methods for analyzing and optimizing the performance of multi-threaded applications running on modern multi-core processors.

## Contribution #1: Per-Thread Cycle Accounting in Multi-Core Processors

This work proposes a hardware-efficient per-thread cycle accounting architecture for multi-core processors. The counter architecture tracks per-thread progress in a multi-core processor, detects how inter-thread interference affects per-thread performance, and predicts the execution time for each thread if run in isolation. The counter architecture captures the effect of interference misses due to cache sharing as well as increased memory access latency due to resource and memory bandwidth sharing in the memory subsystem. The proposed method accounts for 74.3% of the interference cycles, and estimates per-thread progress within 14.2% on average across a large set of multi-program workloads. Hardware cost is limited to 7.44 KB for an 8-core processor — a reduction by almost 10× compared to prior work while being 63.8% more accurate. Chapter 6 details on the implementation of this counter architecture. Making system software progress-aware improves fairness by 22.5% on average over progress-agnostic scheduling, this will be discussed in Chapter 7.

This work has been published in ACM Transactions on Architecture and Code Optimization (TACO) and has been presented at the 2013 International Conference on High-Performance and Embedded Architectures and Compilers (HiPEAC):

K. Du Bois, S. Eyerman, and L. Eeckhout. Per-thread Cycle Accounting in Multicore Processors. *ACM Transactions on Architecture and Code Optimization (TACO)*, 9(4):1–22, Jan. 2013

#### Contribution #2: Speedup Stacks

Multi-threaded workloads typically show sublinear speedup on multi-core hardware, i.e., the achieved speedup is not proportional to the number of cores and threads. Sublinear scaling may have multiple causes, such as poorly scalable synchronization leading to spinning and/or yielding, and interference in shared resources such as the last-level cache (abbreviated as LLC) as well as the main memory subsystem.

In this work, we propose the speedup stack, which quantifies the impact of the various scaling delimiters on multi-threaded application speedup in a single stack. We describe a mechanism for computing

4 Introduction

speedup stacks on a multi-core processor, and we find speedup stacks to be accurate within 5.1% on average for sixteen-threaded applications. We present several use cases: we discuss how speedup stacks can be used to identify scaling bottlenecks, classify benchmarks, optimize performance, and understand LLC performance. We introduce speedup stacks in Chapter 3 and discuss them further in Chapter 6.

Speedup stacks have been presented at the 2012 IEEE International Symposium on Performance Analysis of Systems and Software (IS-PASS):

S. Eyerman, K. Du Bois, and L. Eeckhout. Speedup Stacks: Identifying Scaling Bottlenecks in Multi-Threaded Applications. In *Proceedings of the International Symposium on Performance Analysis of Software and Systems (ISPASS)*, pages 145–155, Apr. 2012

#### Contribution #3: Criticality Stacks

Due to synchronization, certain threads make others wait, because they hold a lock or have yet to reach a barrier. We call these critical threads, i.e., threads whose performance is determinative of program performance as a whole. Identifying these threads can reveal numerous optimization opportunities, for the software developer and for hardware.

In this work, we propose a new metric for assessing thread criticality, which combines both how much time a thread is performing useful work and how many co-running threads are waiting. We show how thread criticality can be calculated online with modest hardware additions and at low overhead. We use our metric to create criticality stacks that break down total execution time into each thread's criticality component, allowing for easy visual analysis of parallel imbalance. We introduce criticality stacks in Chapter 3.

To validate our criticality metric, and demonstrate it is better than previous metrics, we scale up the frequency of the most critical thread and show it achieves the largest performance improvement. We then demonstrate the broad applicability of criticality stacks by using them to perform three types of optimizations: (1) program analysis to remove parallel bottlenecks, (2) dynamically identifying the most critical thread and accelerating it using frequency scaling to improve performance, and (3) showing that accelerating only the most critical thread allows for targeted energy reduction. We discuss this in Chapter 4 and 7.

This work has been presented at the 2013 International Symposium on Computer Architecture (ISCA):

K. Du Bois, S. Eyerman, J. B. Sartor, and L. Eeckhout. Criticality Stacks: Identifying Critical Threads in Parallel Programs Using Synchronization Behavior. In *Proceedings of the International Symposium on Computer Architecture (ISCA)*, pages 511–522, June 2013

#### Contribution #4: Bottle Graphs

In our fourth contribution, we present bottle graphs, a powerful analysis tool that visualizes multi-threaded program performance, in regards to both per-thread parallelism and execution time. Each thread is represented as a box, with its height equal to the share of that thread in the total program execution time, its width equal to its parallelism, and its area equal to to the thread's total execution time. The boxes of all threads are stacked upon each other, leading to a stack with height equal to the total program execution time. Bottle graphs show exactly how scalable each thread is, and thus guide optimization towards those threads that have a smaller parallel component (narrower), and a larger share of the total execution time (taller), i.e., towards the 'neck' of the bottle.

Using light-weight OS modules, we calculate bottle graphs for unmodified multi-threaded programs running on real processors with an average overhead of 0.68%. To demonstrate their utility, we do an extensive analysis of 12 Java benchmarks running on top of Jikes RVM, which introduces many virtual machine service threads. We not only reveal and explain scalability limitations of several well-known Java benchmarks; we also analyze the reasons why the garbage collector itself does not scale, and in fact performs optimally with two collector threads for all benchmarks, regardless of the number of application threads. Finally, we compare the scalability of Jikes versus the Open-JDK JVM. We demonstrate how useful and intuitive bottle graphs are as a tool to analyze scalability and help optimize multi-threaded applications. We introduce bottle graphs in Chapter 3 and discuss them further in Chapter 5.

Bottle graphs have been presented at the 2013 ACM SIGPLAN International Conference on Object Oriented Programming, Systems Languages and Applications (OOPSLA):

6 Introduction

K. Du Bois, J. B. Sartor, S. Eyerman, and L. Eeckhout. Bottle Graphs: Visualizing Scalability Bottlenecks in Multi-threaded Applications. In *Proceedings of the ACM SIGPLAN International Conference on Object Oriented Programming, Systems Languages and Applications (OOPSLA)*, pages 355–372, Oct. 2013

# Contribution #5: Extension on Bottle Graphs and Speedup Stacks

In our fifth contribution, we provide an extension to our previous bottle graphs and speedup stacks papers. We use bottle graphs for analyzing per-thread performance of Java applications running on Jikes RVM. Because it is hard to analyze how the applications themselves scale using bottle graphs, we extend our previously proposed speedup stacks to make them suitable for managed language programs like Java applications. We include the following scaling delimiters to more accurately analyze the scalability of the service threads of managed language programs: garbage collection, sequential parts of the application, thread imbalance, synchronization between threads and hardware interference. For constructing these new speedup stacks, we extend our previously proposed light-weight OS modules that we used for generating bottle graphs. We thus generate speedup stacks for unmodified Java applications running on native hardware at very low overhead. The speedup stacks lead to a better understanding of the causes and contributions of limited speedup of multi-threaded Java programs. We discuss these speedup stacks in Chapter 3 and 6.

This work is submitted to ACM Transactions on Programming Languages and Systems (TOPLAS):

K. Du Bois, S. Eyerman, J. B. Sartor, and L. Eeckhout. Analyzing Scaling Behavior of Managed Runtime Applications. *ACM Transactions on Programming Languages and Systems (TOPLAS)*, 2014. Under review

#### How the Contributions Tie Together

Table 1.1 gives an overview of the different contributions in this dissertation. The first contribution, the per-thread cycle accounting architecture, uses a dedicated hardware component for measuring the impact of interference between threads, due to hardware resource sharing.

|                                                    | Per-Thread<br>Cycle<br>Accounting | Speedup<br>Stacks      | Criticality<br>Stacks | Bottle<br>Graphs |

|----------------------------------------------------|-----------------------------------|------------------------|-----------------------|------------------|

| Implemented with: - hardware - software support    | contr. #1                         | contr. #2<br>contr. #5 | contr. #3             | contr. #4        |

| Used for: - native - managed language applications | contr. #1<br>—                    | contr. #2<br>contr. #5 | contr. #3<br>—        | <br>contr. #4    |

| Visualization tool                                 | ×                                 | V                      | V                     | ~                |

**Table 1.1:** Overview of contributions in this dissertation.

We evaluate our counter architecture on multi-programmed workload mixes, consisting of SPEC CPU2006 benchmarks.

In this dissertation we have two versions of speedup stacks. The first version, found in contribution #2, uses an extended version of the cycle accounting architecture from the first contribution for generating speedup stacks. We use this version of speedup stacks for evaluating the performance of applications from the PARSEC, SPLASH-2 and Rodinia benchmark suites. Our second version of speedup stacks, from contribution #5, is constructed using a software implementation. For this second version, we extend our original speedup stacks to be able to analyze Java applications. We use these speedup stacks for analyzing the performance of multi-threaded Java benchmarks that come from the DaCapo suite, running on Jikes RVM.

In contribution #3, we propose criticality stacks, and a corresponding profiling tool that uses hardware support to generate those stacks. We consider a set of benchmarks from the PARSEC, SPLASH-2 and Rodinia suites for our study with criticality stacks. Contribution #4 presents bottle graphs, which we generate using a profiling tool implemented in software. We use bottle graphs for performance analysis of Java applications (both single- and multi-threaded applications) running on Jikes RVM.

8 Introduction

Speedup stacks, criticality stacks and bottle graphs all provide a visual representation that facilitates an intuitive analysis of the performance of multi-threaded applications.

#### 1.4 Other Research Activities

Besides the contributions mentioned above, we also performed research on evaluating the energy efficiency of computer systems. These results are not discussed in this dissertation, but we refer the interested reader to the respective publication.

#### **Evaluating Computer System Energy Efficiency**

Energy efficiency is a key design concern in contemporary processor and system design, in the embedded domain as well as in the enterprise domain. The focus on energy efficiency has led to a number of power benchmarking methods recently. For example, EEMBC released EnergyBench, and SPEC released SPECpower to quantify a system's energy efficiency; also academics have proposed power benchmarks, such as JouleSort. A major limitation for each of these proposals is that they are tied to a specific benchmark, and hence, they provide limited insight with respect to why one system is more energy-efficient than another.

In this contribution we propose SWEEP, Synthetic Workloads for Energy Efficiency and Performance evaluation, a framework for generating synthetic workloads with specific behavioral characteristics. We employ SWEEP to generate a wide range of synthetic workloads while varying the instruction mix, ILP, memory access patterns, and I/O-intensiveness; and we use SWEEP to evaluate the energy efficiency of commercial computer systems across the workload space and learn about how the energy efficiency of a computer system is tied to workload characteristics.

This work also presents the Energy-Delay Diagram (EDD), a novel method for visualizing energy efficiency. The EDD clearly illustrates the energy versus performance trade-off, and provides more intuitive insight than the traditionally used EDP and ED<sup>2</sup>P metrics.

We refer the interested reader to the following paper that was presented at the 2011 International Conference on High-Performance and

Embedded Architectures and Compilers (HiPEAC):

K. Du Bois, T. Schaeps, S. Polfliet, F. Ryckbosch, and L. Eeckhout. SWEEP: Evaluating Computer System Energy Efficiency Using Synthetic Workloads. In *Proceedings of the International Conference on High Performance and Embedded Architectures and Compilers (HiPEAC)*, pages 159–166, Jan. 2011

#### 1.5 Overview of This Dissertation

This dissertation is organized as follows. In Chapter 2, we provide background on resource sharing between threads in a multi-core processor and discuss synchronization in multi-threaded applications. In Chapter 3, we introduce our three new methods for analyzing the performance and identifying scaling bottlenecks of multi-threaded applications. We further discuss criticality stacks, bottle graphs and speedup stacks in Chapter 4, 5, and 6 respectively. These chapters explain how the new methods are constructed, the experimental setup we used, and results about performance analysis of applications. We show how application performance can be optimized in Chapter 7. Finally we present our conclusions and talk about future work in Chapter 8.

10 Introduction

# **Chapter 2**

# **Background**

In this chapter we provide a background about contemporary multi-core processors, how threads interfere with each other in the shared hardware resources, and discuss synchronization in multi-threaded applications.

#### 2.1 Multi-Core Processors

Moore's law says that the number of transistors on a single chip doubles every two years [48]. As a result of this increase in transistor density, chip manufacturers today are able to put multiple cores on a single chip. Those designs are called multi-core processors or chip-multiprocessors (CMPs) [50]. Examples of contemporary multi-core processors are the Intel Core i7, AMD Opteron, IBM POWER8, etc. These general-purpose processors employ a limited number of cores, typically in the range of 4 to 8 cores, but given the continuous transistor density improvements, it is expected that this number will increase in the coming years, as exemplified by Intel's Xeon Phi with 62 cores on a single chip.

Figure 2.1 shows a high-level overview of a modern multi-core processor, together with an off-chip memory component. In this example the processor contains 4 cores. The cores are connected to their private L1 caches, which are typically separate for instructions and data. Besides a private L1, each core also has a private L2 cache in this example. The cores are connected to a shared last-level cache, which is the L3 cache, by making use of an interconnection network. In case a core wants to access data that cannot be found in one of the caches, the core

12 Background

**Figure 2.1:** Example of a multi-core processor along with an off-chip memory component. The dashed line indicates the chip boundary.

sends a request to the memory controller, which fetches the data from main memory. Main memory is normally placed off-chip and is connected to the chip using a memory bus. Main memory itself exists of several memory banks, which can handle memory accesses in parallel, thereby enabling memory-level parallelism (MLP).

#### 2.1.1 Resource Sharing

As illustrated in Figure 2.1, multi-core processors share resources among the cores, such as caches, on-chip interconnection network, memory controllers, off-chip bandwidth, memory banks, etc. Resource sharing increases hardware utilization, adds flexibility for a processor to adapt to varying workload demands (e.g., a thread with a large working set can allocate a large fraction of the shared cache), and can improve performance (e.g., fast communication between cores through the on-chip interconnection network and shared cache).

However, resource sharing also comes with a significant drawback: co-executing hardware threads may affect each other's performance.

For example, a thread allocating a large fraction of the shared cache may introduce additional interference misses for other threads [45, 64]; likewise, memory accesses by a thread may close open pages in memory, thereby increasing memory access time for other threads.

These inter-thread interferences may or may not have an effect on per-thread performance depending on whether memory accesses can be hidden by doing other useful work. As a result, hardware resource sharing may affect the performance of a multi-threaded application in unpredictable ways and may possibly lead to undesirable properties such as an unbalanced performance across co-executing threads of a parallel workload, thread starvation, etc. Besides that, the impact of resource sharing on application performance is proportional to the number of co-running threads in the application. As a result, the parallel speedup of applications executing on multi-core processors does not scale linearly in the number of threads, but is limited by the impact of resource sharing on per-thread performance.

Therefore, when analyzing the scaling behavior of multi-threaded applications, it is vital to accurately quantify this impact on the performance of an application.

#### 2.1.2 Sources of Thread Interference

Co-executing threads on a multi-core processor interfere with each other in each of the shared resources, which leads to different interference effects. We will now discuss how this interference affects the performance of threads. For now, we assume a single thread per core, hence we use the terms 'thread' and 'core' interchangeably.

#### Last-level cache

Sharing the last-level cache (the L3 cache in Figure 2.1) between threads leads to extra interference misses due to threads evicting each other's data. We refer to these interference misses as *inter-thread misses*. In contrast, we define *intra-thread misses* as misses that also occur during isolated execution, i.e., when the thread runs alone on the processor. Inter-thread misses do not occur during isolated execution and hence, their performance impact is potentially detrimental to per-thread performance: these memory references would be serviced by the LLC in isolated execution but turn into long-latency memory accesses during

14 Background

multi-core execution.

In case of a multi-threaded application, sharing the last-level cache can also have a positive impact on performance. This happens when a thread loads data into the cache that later can be used by other threads. We define an *inter-thread hit* as a hit that would be a miss during isolated execution but becomes a hit during multi-core execution.

#### Interconnection network

The on-chip interconnection network connects the cores to the shared cache (and to each other). A request of one core can be delayed due to a request by another core. Conflicts in the interconnection network thus prolong both the LLC hit and miss latency compared to isolated execution. Prolonging the LLC hit time due to conflicts in the interconnection network is unlikely to significantly affect per-thread performance, because the LLC hit latency (even with the additional conflict latency) is small enough so that it is effectively hidden on superscalar processor cores through out-of-order execution in a balanced design [25]. For LLC misses, the additional conflict latency may have a significant effect (i.e., the additional penalty can not be hidden) because the processor cannot make progress while handling the LLC miss because of its long latency.

#### Memory bus

As with the interconnection network, a memory request issued by a core can hold the bus between the LLC and main memory, possibly delaying requests by other cores. This causes memory accesses to take longer, which may have a significant impact on performance.

#### Memory bank effects

While main memory typically consists of a number of memory banks that can handle memory accesses in parallel, each bank can handle only one access at a time. This implies that while a bank is busy processing an access of a core, no other requests to that bank from other cores can be serviced. This increases the memory access time for the other cores.

An additional effect occurs in case of an open-page policy. Consider an example in which a thread accesses the same page twice and there are no intervening memory accesses to another page in the same bank, i.e., the page is loaded in the row buffer and both accesses are serviced from the row buffer. Now, another thread may interfere and may initiate a memory access to that same bank (but a different page) between the two memory requests by the first thread. This memory access will cause the row buffer to be written back to the memory bank, and a new page to be loaded in the row buffer. The second memory access by the first thread will now see a row miss (instead of a row hit) and will need to load the page again into the row buffer. In other words, this second memory access will see a longer latency during multi-core execution than it would see during isolated execution.

#### Prefetcher

A hardware prefetcher tries to fetch data from a higher memory level into a lower memory level before a core sends a request for accessing the data. This way, hardware tries to anticipate future accesses to both instructions and data, and thereby improve the hit rate of a memory level. Typically there is a prefetcher between the last-level cache and main memory.

Prefetch requests in a memory system usually have a lower priority than read or write requests. Therefore, interference in this component happens when prefetch requests that would be timely in isolated execution are delayed during multi-core execution because of requests from the other cores, and as a result now become a miss for the core. Secondly, despite the lower priority of prefetch requests, they may still congest the memory subsystem because they occupy the memory bus, pollute caches, etc.

#### 2.1.3 Quantifying Thread Interference

In this section we show that interference between threads in shared resources has a significant impact on performance. We do this by running experiments using the gem5 simulator [6], and simulating processors with 1, 2, 4 and 8 cores running multiple single-threaded SPEC CPU2006 workloads (more information about our simulated configurations can be found in Table 6.2 on page 107). We then quantify the impact of this interference on per-thread performance, and we identify the contribution of different sources of interference.

We define interference as the relative increase in execution time be-

16 Background

**Figure 2.2:** Impact of inter-thread interference on per-thread performance for 2, 4 and 8 cores, breaking up interference in cache versus memory contention (average interference is reported across a set of job mixes per benchmark and assuming hardware prefetching).

**Figure 2.3:** The impact of prefetching on interference on an eight-core system (maximum interference is reported across 10 job mixes per benchmark).

tween multi-core and isolated execution:

$$Interference = \frac{T_{multi-core} - T_{isolated}}{T_{isolated}}.$$

(2.1)

Interference thus quantifies the increase in execution time on a multi-core processor due to interference relative to isolated single-core execution. Through detailed simulation we find that interference is significant, and that it increases with the number of cores: 9.3% on average for 2 cores, 19.5% for 4 cores, and 55.4% for 8 cores. The reason why interference increases with core count is that an increasing number of cores put increasingly more pressure on the shared resources, and hence, per-thread performance is affected more significantly.

To understand the relative contributions of the different sources of interference, Figure 2.2 makes a distinction between the interference due to inter-thread misses in the shared cache versus resource and bandwidth sharing in the memory subsystem (memory bus, memory banks and open row policy). Some benchmarks seem to suffer more from cache sharing, whereas other benchmarks suffer more from sharing the memory subsystem. These interference numbers illustrate that the shared resources have substantial impact on per-thread performance, and by consequence, estimating interference is non-trivial (i.e., the null predictor would be highly inaccurate).

Figure 2.3 quantifies the impact of hardware prefetching on inter-

18 Background

ference. We model a stride prefetching scheme that prefetches the next four cache blocks if a stride is detected. Now the maximum interference level observed increases from  $2.3\times$  without prefetching to up to  $3.8\times$  with prefetching. The reason is that hardware prefetching puts even more pressure on the memory system's shared resources, which in its turn affects per-thread progress. In particular, a core that issues many prefetch requests may congest the memory subsystem and thereby degrade other cores' performance.

#### 2.2 Multi-Threaded Applications

In order to take advantage of multi-core processors, software has to provide enough parallel work to make use of the available resources in order to continue the trend of ever-improving performance. Multi-threaded programs that try to use these resources, inherently introduce synchronization to ensure correct execution, for example because they share data among the threads.

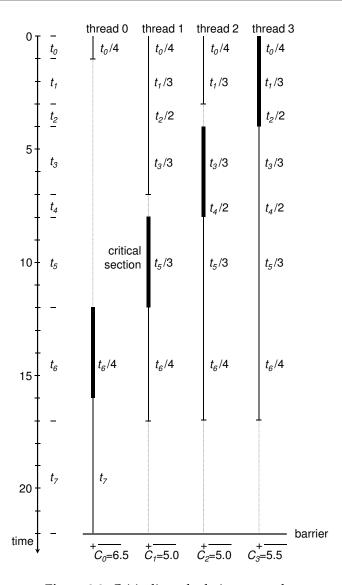

Figure 2.4 shows three common examples of synchronization. In Figure 2.4(a) we show a barrier. A barrier is a synchronization primitive that imposes ordering and denotes a point in the execution beyond which a thread is only allowed to go after all other threads have reached that point. The result of a barrier is that the execution of a thread is halted until all threads have reached the barrier. A barrier can be shared across all threads, or between a subset of threads.

Figure 2.4(b) illustrates the use of critical sections. Critical sections are typically implemented using locks to guarantee atomicity when modifying shared data. Critical sections do not impose a particular ordering of execution, but they prevent threads from reading and modifying the same data concurrently. An alternative to using locks for guaranteeing atomicity in critical sections is transactional memory.

Figure 2.4(c) shows the use of producer-consumer synchronization. In this case threads can only proceed with their calculation after the needed data is produced by other threads. (In the example T2 and T3 have to wait until T0 and T1 finished their calculation.)

When threads are waiting due to synchronization, they can either be in a spinning or yielding state. Spinning means a thread is continuously checking the state of a synchronization variable inside a loop, which is very compute-intensive. Therefore, there is a second state, 2.3 Summary 19

**Figure 2.4:** Examples of synchronization between threads of a multi-threaded application.

called yielding in this work, which means that the operating system schedules out the thread. In this state the thread does no longer occupy the core. However, this approach has the disadvantage of having a larger performance penalty compared to spinning (because the operating system has to schedule the threads in and out).

While synchronization is necessary, it also results in threads waiting for each other, limiting performance and scalability, and wasting energy. This means that threads in a multi-threaded application have an impact on each other's performance, just like they do due to resource sharing in the underlying hardware of a multi-core processor.

# 2.3 Summary

In this chapter, we identified two reasons why threads have an impact on each other's execution, and consequently limit parallel speedup of a multi-threaded application. First, they share resources in the hardware of a multi-core processor. This leads to interference among co-executing threads because of contention effects in the shared resources, such as caches, off-chip bandwidth, memory banks, etc. We quantified that this interference is significant and increases with the number of cores.

Secondly, while synchronization is necessary for achieving correct execution of a multi-threaded application, it also causes threads to wait 20 Background

for each other. This waiting of threads results in certain threads making faster progress than others, leading to an imbalance between the different threads, and some threads that are more critical to performance than others.

We conclude this chapter by saying that apart from the level of the hardware, threads also affect each other's performance on the level of the application. This implies that if we want to analyze the performance and scalability of a multi-threaded application, we have to take into account both levels of interference (both in hardware and in software).

# **Chapter 3**

# Performance Analysis Methods

*In this chapter we introduce three new performance analysis methods for evaluating the performance and scalability of multi-threaded applications.*

#### 3.1 Introduction

Analyzing the performance and scalability of a multi-threaded application is not trivial. As we discussed in the previous chapter, threads interact with each other due to synchronization and resource sharing in the hardware. These complicated interactions make it difficult to analyze performance. However, one of the key needs to efficient parallel programming is to have the appropriate tools to analyze parallel performance. In particular, a software developer needs analysis tools to identify the performance scaling bottlenecks, not only on current hardware but also on future hardware with many more cores than are available today; likewise, computer architects need analysis tools to understand the behavioral characteristics of workloads to design and optimize future hardware.

Therefore, we propose three new methods for analyzing parallel program performance in this chapter. The first method, called *criticality stacks*, is useful for understanding parallel (im)balance between threads of a multi-threaded application. The second method, *bottle graphs*, visualizes parallel performance bottlenecks by quantifying both execution time and parallelism for each thread. Finally, we present *speedup stacks*,

**Figure 3.1:** BFS's criticality stack and total program speedups from accelerating the identified critical and non-critical threads.

which is a tool for providing insights into an application's scaling behavior on multi-core hardware.

In the remainder of this chapter, we discuss those three new methods, explain how they are constructed, and show examples. Criticality stacks are discussed in Section 3.2, bottle graphs in Section 3.3, and speedup stacks in Section 3.4 and 3.5. Finally, we discuss related work in Section 3.6.

### 3.2 Criticality Stacks