The second half of the chessboard Raymond Kurzweil <u>ii \_\_\_\_\_\_</u>

## Dankwoord

Vooraleer je tot het schrijven van een doctoraat komt, heb je reeds een hele levensweg afgelegd. Onderweg is het niet altijd even gemakkelijk om niet verloren te lopen: soms kom je aan een splitsing, een obstakel of een doodlopend eind. Maar steeds was er wel iemand om mij te helpen mijn weg verder te zoeken. Ik ben dan ook veel dank verschuldigd aan heel wat mensen.

In de eerste plaats aan prof. Koen De Bosschere en prof. Lieven Eeckhout, mijn promotoren, voor de mogelijkheid om mijn doctoraatsonderzoek te verrichten in hun onderzoeksgroep. Ik wens hen ook te bedanken voor de begeleiding van mijn onderzoek, voor de vele stimuli en steun en voor de goede raad en inzichten die zij mij bijbrachten.

Verder wil ik ook de andere leden binnen de Paris-onderzoeksgroep bedanken voor de goede onderzoekssfeer die er heerst. Met in het bijzonder de andere professoren, prof. Jan Van Campenhout, prof. Erik D'Hollander en prof. Dirk Stroobandt, voor het geven van constructieve opmerkingen en tips.

Mijn collega-onderzoekers Dries, Andy, Davy, Tom, Jonas, Michiel en Marc, waarmee ik ooit een bureau deelde, zou ik willen bedanken voor de aangename tijd samen, voor hun hulp en collegialiteit. Ook al mijn andere collega's zou ik graag bedanken omdat ik bij hen altijd terecht kon met vragen allerhande.

Verder zou ik ook Dr. David Bacon willen bedanken, die voor mij nieuwe onderzoekswegen opende door mij de kans de geven 2 maanden onderzoek te verrichten in het prestigieuze IBM T.J. Watson Research Center te New York.

I would also like to thank Dr. David Bacon because he opened up new research opportunities for me by giving me the opportunity to do a 2 month internship at the prestigious IBM T.J. Watson Research Center in New York.

Natuurlijk wil ik de leden van mijn examencommissie niet verge-

ten, die ik wil bedanken voor de interesse in mijn werk, het grondig lezen van mijn thesis, het geven van opmerkingen en voor de beoordeling van mijn werk.

Furthermore, I would like to thank the members of my PhD commission for the interest in my work, for reading my thesis carefully, for delivering comments and for evaluating my work.

Ook aan de Universiteit Gent ben ik dank verschuldigd, omdat deze het voor mij financieel mogelijk maakte een doctoraatsmandaat van 4 jaar op te nemen via het Bijzonder OnderzoeksFonds (BOF).

Graag zou ik ook nog een heleboel andere mensen willen bedanken die mij ook buiten mijn doctoraatsonderzoek gesteund hebben en/of mij nauw aan het hart liggen, zoals mijn ouders, mijn zus, mijn vriendin Ilse en alle andere vrienden. Met in het heel bijzonder mijn ouders, die mij al heel mijn leven lang gesteund hebben en mij zoveel gegeven hebben. Bedankt om dit alles mogelijk te maken.

> Kris Venstermans Gent, 29 mei 2007

## Examencommissie

- Prof. Ronny Verhoeven, voorzitter Onderwijsdirecteur Faculteit Ingenieurswetenschappen Universiteit Gent

- Prof. Jan Van Campenhout, secretaris Vakgroep ELIS, Faculteit Ingenieurswetenschappen Universiteit Gent

- Prof. Koen De Bosschere, promotor Vakgroep ELIS, Faculteit Ingenieurswetenschappen Universiteit Gent

- Prof. Lieven Eeckhout, promotor Vakgroep ELIS, Faculteit Ingenieurswetenschappen Universiteit Gent

- Prof. Bart Dhoedt Vakgroep INTEC, Faculteit Ingenieurswetenschappen Universiteit Gent

- Prof. Theo D'Hondt Vakgroep Computerwetenschappen, Faculteit Wetenschappen Vrije Universiteit Brussel

- Prof. Matthew Hertz Department of Computer Science Canisius College, Buffalo, NY, USA

- Dr. Bilha Mendelson Code Optimization Technologies Department IBM Research Lab, Haifa, Israel

vi

## Samenvatting

Computerprogramma's worden complexer telkens als er nieuwe, krachtigere computerchips op de markt komen. Bij elke nieuwe generatie computerchips tasten programma-ontwikkelaars altijd opnieuw de grenzen van die generatie af. Tegelijk met het complexer worden van computerprogramma's, vereisen deze programma's ook steeds meer computergeheugen. Door die stijgende geheugenvraag werd het aantal adresseringsbits in de loop der jaren aangepast. Hedendaagse desktop systemen op de consumentenmarkt zijn allemaal uitgerust met een 64bit CPU (Central Processing Unit), terwijl enkele jaren geleden dergelijke systemen nog bijna uitsluitend van 32-bit processoren waren voorzien. De 64-bit adresseerruimte is gigantisch groot in vergelijking met de 32-bit adresseerruimte.

Groter betekent echter niet steeds beter: als we 32-bit en 64-bit computersystemen vergelijken, merken we dat beide zowel voor- als nadelen hebben. Het meest effectieve prestatievoordeel van 64-bit systemen ligt in het aanwezig zijn van extra 64-bit instructies in de ISA (Instruction Set Architecture). Het belangrijkste nadeel van 64-bit computersystemen is dat zij meer geheugen gebruiken omdat verwijzingen (pointers) tussen verschillende objecten nu met 64 bits voorgesteld worden. De extra 64-bit instructies geven enkel een prestatievoordeel voor programma's die bewerkingen doen op grote gehele getallen, terwijl het nadeel van het grotere geheugengebruik bijna steeds zal optreden omdat objectverwijzingen heel frequent gebruikt worden in moderne programmeertalen.

In deze thesis zullen we twee technieken introduceren die het geheugengebruik van 64-bit programma's zullen verbeteren in het kader van een Java Virtuele Machine (JVM). We kiezen een omgeving die objectgeoriënteerd is, omdat objectgeoriënteerd programmeren heden ten dage een heel populair programmeerparadigma is, en omdat er veel objectverwijzingen voorkomen in een dergelijke omgeving. Vooraleer we de nieuwe technieken introduceren, zullen we eerst een karakterisering maken van de impact van de transitie van 32-bit naar 64-bit systemen op het geheugengebruik en op de prestatie. Deze karakterisering omvat o.a. het opmeten en vergelijken van de objectgrootte van zowel array als niet-array objecten voor 32-bit en 64-bit systemen. We stellen vast dat de gemiddelde objectgrootte met 45.3% toeneemt in een 64-bit systeem ten opzichte van een 32-bit systeem. We zullen de belangrijkste redenen voor deze toename identificeren en bestuderen voor verschillende geheugenbeheersystemen. We bestuderen verder ook het groeien en inkrimpen van de heap, en we bemeten het verschil in aantal geheugensaneringen tussen 32-bit en 64-bit systemen voor een vaste grootte van de heap. Uit deze karakterisering leiden we af dat objectverwijzingen zowel in de objectdata als in de objecthoofding bestaan, en dat ze beide verantwoordelijk zijn voor een groot deel van de totale geheugenomvang van objecten in 64-bit systemen.

De eerste techniek die we voorstellen om het geheugengebruik van 64-bit systemen te reduceren, spitst zich toe op de objectdata. We comprimeren objectverwijzingen die voorkomen in de datavelden. Om deze objectverwijzingen te kunnen comprimeren, zullen we een aantal zaken moeten onderzoeken: (i) decomprimeren moet steeds correct kunnen gebeuren en dus zal er een opvangnet moeten voorzien worden voor in het geval een objectverwijzing niet comprimeerbaar is; (ii) speciale waarden voor objectverwijzingen, zoals de null verwijzing, moeten gedefinieerd worden in gecomprimeerde vorm; (iii) als het geheugenbeheersysteem objecten verplaatst, dan moet het mechanisme dat de objectverwijzingen tijdens het verplaatsen up-to-date brengt, aangepast worden om met gecomprimeerde objectverwijzingen te kunnen functioneren. Verder zullen we ook steeds rekening houden met de efficiëntie bij het implementeren van bovenstaande bemerkingen en stellen we optimalisaties voor om de overhead van onze techniek verder te beperken.

De tweede techniek die we voorstellen ter reductie van het geheugengebruik van 64-bit systemen, focust op de objecthoofding. We onderzoeken welke componenten er zich allemaal bevinden in de objecthoofding en, op basis van hun functie of gebruik, zullen we voor elke component een alternatieve voorstellingswijze introduceren die ons toelaat om die specifieke component uit de objecthoofding te verwijderen. Op deze manier verminderen we de grootte van de objecthoofding initieel van 16 naar 4 bytes en vervolgens elimineren we ook de laatste 4 bytes. Om deze geheugenreducerende techniek toe te passen, hebben we in eerste instantie profielinformatie nodig. Deze profielinformatie wordt verzameld tijdens een offline uitvoering van het programma. Doordat offline technieken niet altijd handig zijn om te gebruiken in een virtuele uitvoeringsomgeving, stellen we ook een volledige online variant van de techniek voor.

Ter conclusie kunnen we stellen dat we in deze thesis het geheugengedrag van 64-bit Java Virtuele Machines bestuderen en optimaliseren. De belangrijkste bijdragen van dit werk kunnen als volgt samengevat worden: een gedetailleerde karakterisering van het geheugengebruik en van de prestaties van 32-bit en 64-bit Java programma's; twee technieken die het geheugengebruik van 64-bit programma's reduceren: één techniek die zich toespitst op de datavelden in objecten en een andere techniek die zich toespitst op de objecthoofding.

## Summary

Modern computer programs increase in complexity each time more powerful computer chips are constructed. And with each generation faster and more efficient computer chips, program developers design applications that search the limits of that system. As computer programs get more and more complex, they also tend to demand more memory. Due to the increasing memory demands, the number of address bits were increased over the years. Currently most consumer market desktop systems are equipped with 64-bit CPUs, while a few years ago most such systems still had a 32-bit microprocessor. The 64bit address space is enormous compared to the 32-bit address space.

But bigger is not always better: if we compare 32-bit with 64-bit computer systems, both have their advantages and disadvantages. The most prominent advantage of 64-bit computer systems in terms of performance is the availability of extra 64-bit integer instructions. The most important disadvantage is that applications tend to use more memory because of the 64-bit representation of pointers. While the extra integer instructions will only give benefit to applications that perform computation on such large integers, the increased memory usage disadvantage will certainly affect most programs since pointers are very heavily used in modern programming languages.

In this dissertation we will propose two techniques that improve the memory usage of 64-bit applications in the context of a Java Virtual Machine. We choose an Object Oriented environment because Object Oriented Programming is a very popular program paradigm these days and because many pointers exist in such an environment. Before we start optimizing the memory behavior of 64-bit applications, we first characterize the memory usage and overall performance impact of the transition from 32-bit to 64-bit computing for Java applications. Our characterization of the memory usage includes a measurement and comparison of the average object sizes of array and non-array objects for 64-bit and 32-bit computing. We observe that the average object size increases by 45.3% in 64-bit mode compared to 32-bit mode. We identify the main causes for this size increase and study them for different memory managers. We also study the heap growth and measure the difference in the number of garbage collections between 64-bit and 32-bit computing systems for a fixed heap size. From our characterization, we observe that pointers exist in the object data as well as in the object header, and that both are responsible for a major part of the object's size in 64-bit systems.

The first memory reduction technique that we propose, focuses on the object data. It compresses pointers inside object data fields. In order to compress pointers, a number of issues needs to be investigated: (i) decompression needs to be correct at all times, so some kind of saveguard needs to be implemented in case a pointer can not be compressed. (ii) a good compressed representation of special pointer values, like the null pointer, has to be constructed and (iii) if the memory manager moves objects, its pointer update mechanism needs to be adapted so that it can handle compressed pointers. When solving these above issues, we will also take efficiency into account and propose optimizations to reduce the overhead of the compression technique.

Our second memory reduction technique concentrates on the object header. We investigate all the object header components and based on their usage/functionality, we propose for each a different alternative representation that allows us to remove that component from the object header. This way we first reduce the size of the object header from 16 to 4 bytes and next we also remove the remaining 4 bytes. Initially this memory reduction technique requires an offline profiling run to collect information about the allocation behavior of the application. However, since offline techniques are sometimes less appealing for a Virtual Execution Environment, we will also propose a variant that is entirely online.

In conclusion, this research studied the memory management of 64bit Java virtual machines. The main contributions described in this dissertation can be summarized as follows: a detailed memory usage and overall performance characterization study of 32-bit and 64-bit Java workloads; two techniques for reducing the memory usage of 64-bit applications: one technique that focuses on the object data fields and one technique that focuses on the object header.

# Contents

|   | Ned  | erlandse samenvatting                                 | vii |

|---|------|-------------------------------------------------------|-----|

|   | Eng  | lish Summary                                          | xi  |

| 1 | Intr | oduction                                              | 1   |

|   | 1.1  | Towards 64-bit computing                              | 2   |

|   | 1.2  | The pros and cons of 64-bit computing                 | 3   |

|   |      | 1.2.1 The pros of 64-bit computing                    | 3   |

|   |      | 1.2.2 The cons of 64-bit computing                    | 4   |

|   | 1.3  | Assessment: 64-bit computing or not?                  | 7   |

|   |      | 1.3.1 32-bit computing systems versus 32-bit compati- |     |

|   |      | bility mode on 64-bit computing systems               | 8   |

|   |      | 1.3.2 32-bit compatibility mode versus 64-bit mode    | 9   |

|   |      | 1.3.3 64-bit mode: the all-around solution?           | 10  |

|   |      | 1.3.4 Conclusions                                     | 12  |

|   | 1.4  | Goal and contributions of this thesis                 | 13  |

|   | 1.5  | Publications                                          | 15  |

|   | 1.6  | Overview                                              | 17  |

| 2 | 64-b | it versus 32-bit computing: a characterization        | 19  |

|   | 2.1  | Introduction                                          | 19  |

|   | 2.2  | Experimental setup                                    | 21  |

|   |      | 2.2.1 Virtual machine                                 | 21  |

|   |      | 2.2.2 PowerPC platform                                | 22  |

|   |      | 2.2.3 Statistical analysis                            | 23  |

|   |      | 2.2.4 Benchmarks                                      | 24  |

|   | 2.3  | 32-bit versus 64-bit VM                               | 27  |

|   |      | 2.3.1 64-bit ISA                                      | 27  |

|   |      | 2.3.2 Increased stack size                            | 27  |

|   |      | 2.3.3 Argument passing                                | 28  |

|   |      |                                                       |     |

|   |     | 2.3.4 In   | ncreased object size                                    | 28 |

|---|-----|------------|---------------------------------------------------------|----|

|   | 2.4 | Memory     | behavior                                                | 30 |

|   |     |            | Average object size                                     | 30 |

|   |     | 2.4.2 R    | Run time behavior of the heap                           | 40 |

|   | 2.5 | Overall    | Performance                                             | 44 |

|   |     | 2.5.1 E    | Execution time                                          | 44 |

|   |     | 2.5.2 N    | Number of instructions executed                         | 45 |

|   |     | 2.5.3 D    | Data cache misses                                       | 45 |

|   |     | 2.5.4 D    | D-TLB performance                                       | 48 |

|   | 2.6 | Related    | work                                                    | 49 |

|   | 2.7 | Conclus    | ion                                                     | 50 |

| 3 | Obj | ect-Relati | ve Addressing                                           | 53 |

|   | 3.1 |            | tion                                                    | 53 |

|   | 3.2 |            | elative Addressing                                      | 54 |

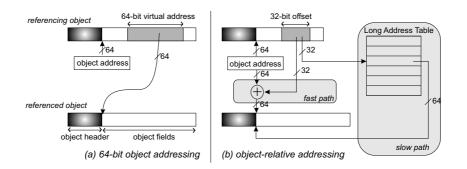

|   |     |            | Basic idea                                              | 55 |

|   |     | 3.2.2 D    | Decompressing pointers                                  | 56 |

|   |     | 3.2.3 C    | Compressing pointers                                    | 59 |

|   |     | 3.2.4 N    | Jull pointer representation                             | 60 |

|   |     | 3.2.5 N    | Ianaging the LAT                                        | 61 |

|   |     | 3.2.6 In   | mplications to copying garbage collectors               | 62 |

|   |     | 3.2.7 L    | Discussion                                              | 62 |

|   |     | 3.2.8 In   | mplications for memory management                       | 64 |

|   | 3.3 |            | ental setup                                             | 65 |

|   | 3.4 | Memory     | usage and impact on GC                                  | 65 |

|   | 3.5 |            | performance evaluation                                  | 70 |

|   |     |            | Execution time                                          | 70 |

|   |     | 3.5.2 C    | Overhead evaluation                                     | 74 |

|   |     |            | Number of instructions executed                         | 75 |

|   |     |            | Cache hierarchy performance                             | 75 |

|   |     |            | D-TLB performance                                       | 78 |

|   | 3.6 | Related    | work                                                    | 78 |

|   | 3.7 | Conclus    | ion                                                     | 81 |

| 4 |     |            | ed Virtual Addressing                                   | 83 |

|   | 4.1 |            | tion                                                    | 83 |

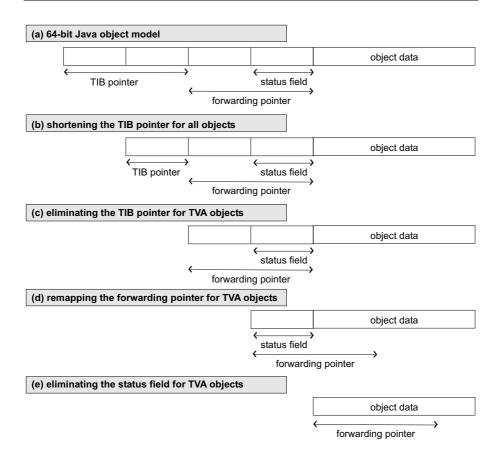

|   | 4.2 |            | it Java object model                                    | 85 |

|   | 4.3 |            | ing the header in the 64-bit Java object model $\ldots$ | 87 |

|   | 4.4 | TIB poin   | ter compression                                         | 88 |

|   | 4.5 | Selective  | e Typed Virtual Addressing                              | 88 |

5

|      | 4.5.1   | The non-array TVA object model          |

|------|---------|-----------------------------------------|

|      | 4.5.2   | The array TVA object model              |

|      | 4.5.3   | Implications of the TVA object model 91 |

| 4.6  | STVA    | type selection                          |

|      | 4.6.1   | Offline STVA type selection             |

|      | 4.6.2   | Online STVA type selection              |

| 4.7  | Exper   | imental setup                           |

| 4.8  |         | ation                                   |

|      | 4.8.1   | Feasibility study of STVA 100           |

|      | 4.8.2   | Memory usage and impact on GC 102       |

|      | 4.8.3   | Performance                             |

|      | 4.8.4   | Cache and TLB performance               |

|      | 4.8.5   | STVA versus TVA                         |

| 4.9  | Relate  | d work                                  |

| 4.10 | Concl   | usion                                   |

| -    |         |                                         |

| Con  | clusior | n 121                                   |

| 5.1  | Summ    | nary                                    |

| 5.2  | Future  | e work, a perspective                   |

|      | 5.2.1   | Embedded systems                        |

|      | 5.2.2   | Creating ORA regions                    |

|      | 5.2.3   | Combining ORA and STVA                  |

\_\_\_\_\_

# List of Tables

| 1.1   | Resources required to first load two 64-bit integers, mul-<br>tiply them, and finally store the lowest 64-bit integer result.                                   | 4  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2   | Dynamic memory increase between 32-bit and 64-bit C programs.                                                                                                   | 5  |

| 1.3   | Overview advantages/disadvantages of 32-bit/64-bit computing.                                                                                                   | 8  |

| 1.4   | Dynamic memory increase between 32-bit and 64-bit Java programs.                                                                                                | 11 |

| 2.1   | Cache hierarchy of the IBM POWER4                                                                                                                               | 22 |

| 2.2   | Benchmarks used from the SPECjvm98 suite                                                                                                                        | 24 |

| 2.3   | The PseudoJBB benchmark                                                                                                                                         | 25 |

| 2.4   | Benchmarks used from the Java Grande Forum suite                                                                                                                | 25 |

| 2.5   | Benchmarks used from the DaCapo benchmark suite                                                                                                                 | 26 |

| 2.6   | Java types and their sizes measured in the number of bits<br>when used on the heap ('field size' column) and when<br>used on the stack ('size on stack' column) | 28 |

| 2.7   | Average object size (in bytes) in 32-bit and 64-bit VM mode for all objects, array objects and non-array objects.                                               | 31 |

| 2.8   | Average object size (in bytes) in the collector-specific spaces<br>in 32-bit and 64-bit VM mode for all objects, array objects<br>and non-array objects.        | 33 |

| 2.9   | Average Application object size (in bytes) in 32-bit and 64-bit VM mode for all objects, array objects and non-                                                 |    |

| 0.4.0 | array objects.                                                                                                                                                  | 35 |

| 2.10  | bit VM mode for all objects, array objects and non-array                                                                                                        |    |

|       | objects                                                                                                                                                         | 36 |

| 2.11 | Raw object size, object size after inter-object alignment<br>and total object heap size in 32-bit and 64-bit mode for<br>the MarkSweep collector.                                          | 38  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.12 | Number of minor and major GCs under the GenMS and GenCopy collection scheme for the 32-bit and 64-bit scenario.                                                                            | 41  |

| 3.1  | Number of minor and major GCs under the GenMS and GenCopy collection scheme for the base 64-bit scenario and ORA                                                                           | 69  |

| 4.1  | Number of TVA-enabled object types for offline STVA type selection, online STVA type selection and the number of object types in common between offline and online type selection.         | 104 |

| 4.2  | Number of minor and major GCs under the GenMS col-<br>lection scheme for the base 64-bit VM and for the small                                                                              |     |

| 4.3  | header and the no-header STVA-aware VMs Number of minor and major GCs under the GenCopy collection scheme for the base 64-bit VM and for the small header and the no-header STVA-aware VMs |     |

# **List of Figures**

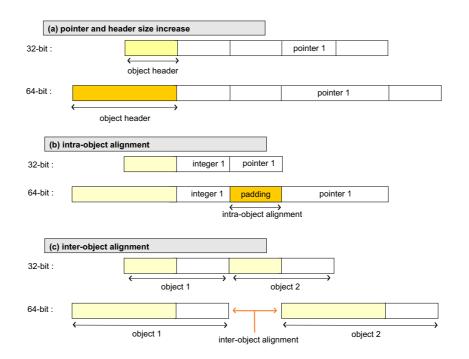

| 2.1  | Causes for object size increase when going from the 32-<br>bit VM to the 64-bit VM.                                                                            | 29       |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

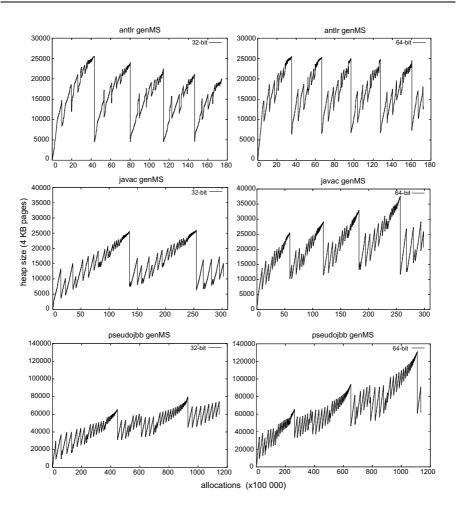

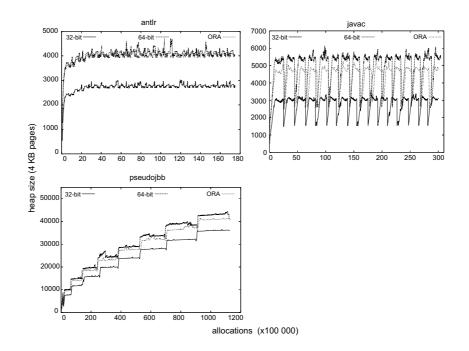

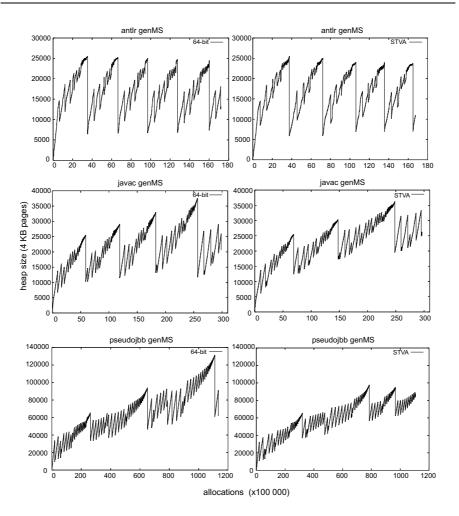

| 2.2  | Heap growth for GenMS collector as a function of time for 32-bit processing and 64-bit processing.                                                             | 40       |

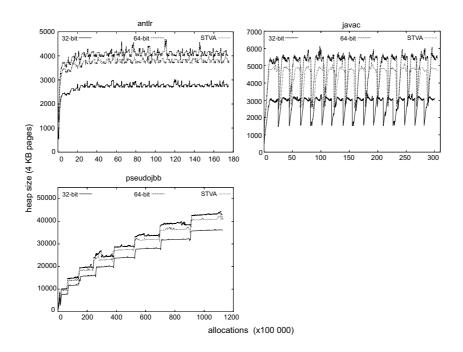

| 2.3  | Garbage collection performance: 64-bit mode versus 32-<br>bit mode                                                                                             | 42       |

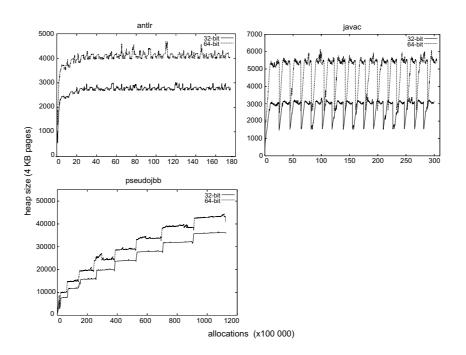

| 2.4  | Maximum reachable bytes as a function of time for 32-bit and 64-bit processing.                                                                                | 43       |

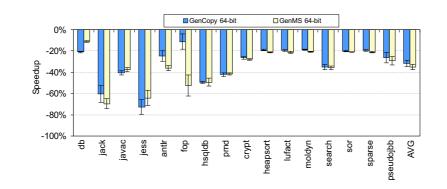

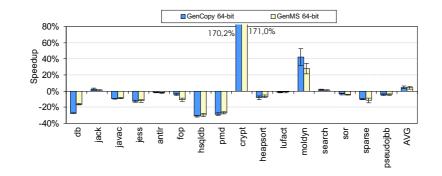

| 2.5  | Overall speedup for 64-bit mode compared to 32-bit mode.                                                                                                       | 44       |

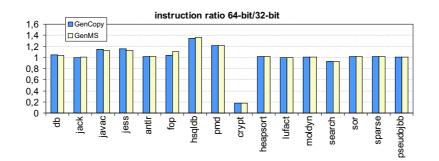

| 2.6  | Ratio of the number of executed instructions of 64-bit to 32-bit mode.                                                                                         | 45       |

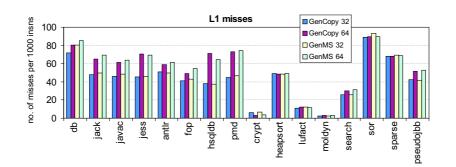

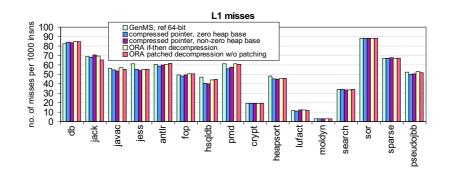

| 2.7  | The number of L1 D-cache misses for 64-bit and 32-bit                                                                                                          | 10       |

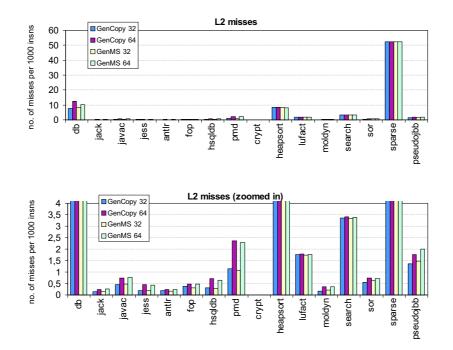

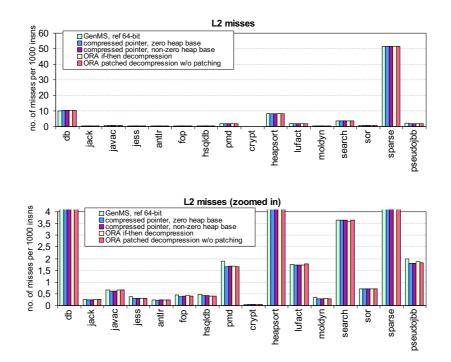

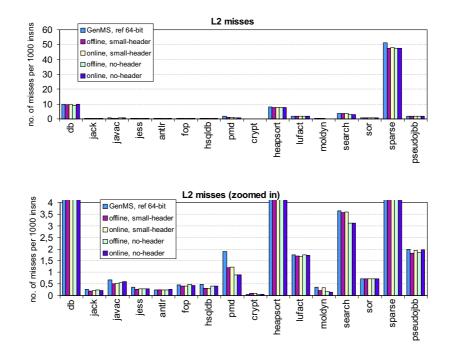

| 2.8  | mode, per 1000 executed instructions in 32-bit mode The number of L2 D-cache misses for 64-bit and 32-bit mode. per 1000 executed instructions in 22 bit mode. | 46<br>46 |

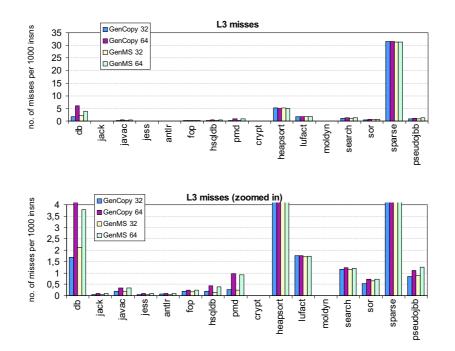

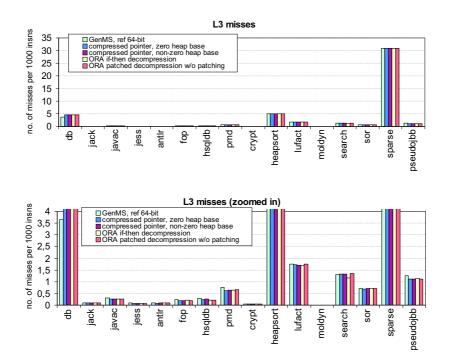

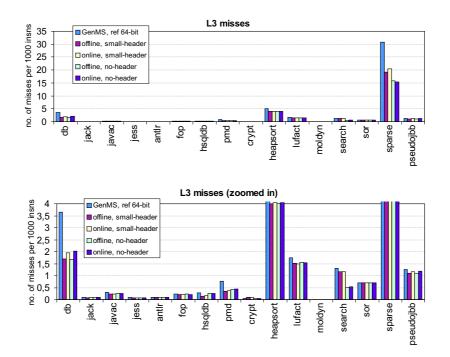

| 2.9  | mode, per 1000 executed instructions in 32-bit mode The number of L3 D-cache misses for 64-bit and 32-bit                                                      |          |

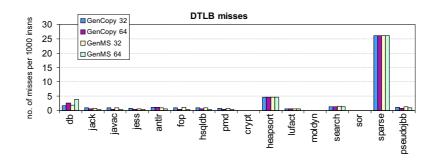

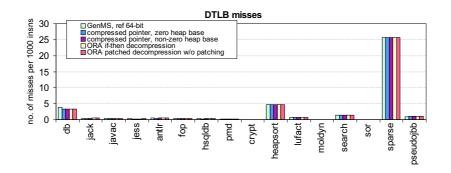

| 2.10 | mode, per 1000 executed instructions in 32-bit mode Number of D-TLB misses for 64-bit and 32-bit mode, per                                                     | 47       |

|      | 1000 executed instructions in 32-bit mode                                                                                                                      | 48       |

| 3.1  | Illustrating the basic idea of object-relative addressing compared to the traditional 64-bit addressing.                                                       | 55       |

| 3.2  | High-level pseudocode for decompressing 32-bit object references.                                                                                              | 56       |

| 3.3  | Low-level pseudocode for decompressing 32-bit object references: the if-then decompression approach.                                                           | 57       |

| 3.4  | Low-level pseudocode for decompressing 32-bit object<br>references: the patched decompression approach before                                                  |          |

|      | code patching is applied                                                                                                                                       | 58       |

| 3.5  | Low-level pseudocode for decompressing 32-bit object<br>references: the patched decompression approach after<br>code patching is applied                                         | 59  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.6  | High-level pseudocode for compressing 64-bit object references.                                                                                                                  | 60  |

| 3.7  | Reduction in the number of allocated bytes through ORA.                                                                                                                          | 66  |

| 3.8  | ORA's reduction of the memory usage overhead of 64-bit                                                                                                                           | 00  |

| 5.0  | mode compared to 32-bit mode                                                                                                                                                     | 66  |

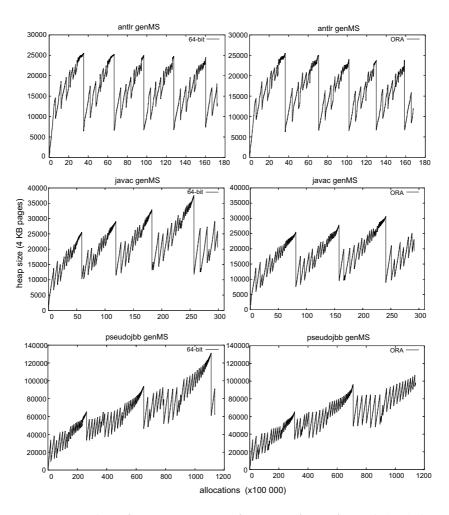

| 3.9  | Number of pages in use as a function of time with the                                                                                                                            | 00  |

| 0.17 | GenMS collector: the base case versus ORA                                                                                                                                        | 67  |

| 3.10 | Maximum reachable bytes as a function of time for 32-bit                                                                                                                         |     |

|      | and 64-bit processing and for ORA                                                                                                                                                | 68  |

| 3.11 | Speedup of the garbage collector through ORA                                                                                                                                     | 69  |

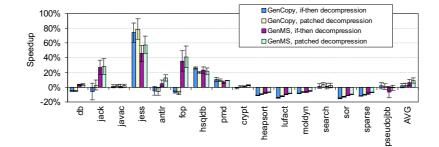

| 3.12 | Evaluating object-relative addressing in terms of perfor-                                                                                                                        |     |

|      | mance                                                                                                                                                                            | 71  |

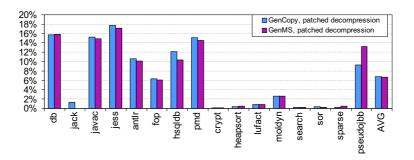

| 3.13 | Evaluating the overhead of different decompression scheme                                                                                                                        |     |

|      | for object-relative addressing in terms of performance.                                                                                                                          | 73  |

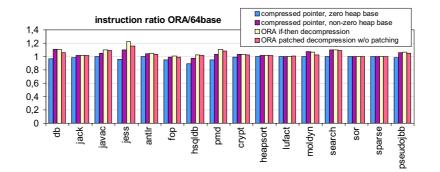

| 3.14 | Ratio of the number of executed instructions of ORA in relation to the 64-bit base case for the GenMS collector.                                                                 | 75  |

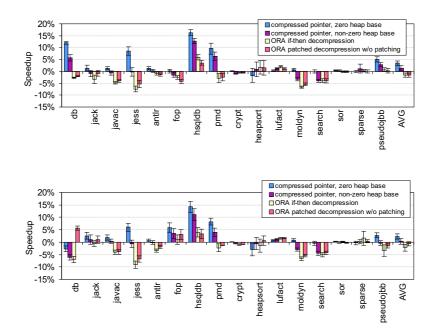

| 3.15 | The number of L1 D-cache misses per 1000 instructions of the base run for the GenMS collector.                                                                                   | 76  |

| 3.16 | The number of L2 D-cache misses per 1000 instructions of the base run for the GenMS collector.                                                                                   | 76  |

| 3.17 | The number of L3 D-cache misses per 1000 instructions of the base run for the GenMS collector.                                                                                   | 77  |

| 3.18 | The number of D-TLB misses for the GenMS collector, per 1000 instructions of the base run                                                                                        | 78  |

| 4.1  | The Java (non-array) object models studied in this chapter.                                                                                                                      | 85  |

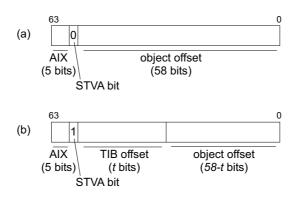

| 4.2  | The 64-bit virtual address for a TVA-disabled object (a) and for a TVA-enabled object (b).                                                                                       | 92  |

| 4.3  | Computing an object's TIB pointer in an STVA-enabled VM implementation.                                                                                                          | 94  |

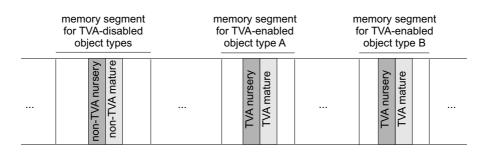

| 4.4  | Mapping the nursery and mature spaces in the virtual address space in a TVA-aware VM                                                                                             | 96  |

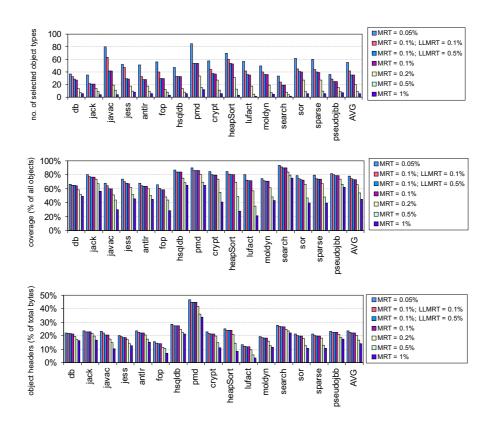

| 4.5  | Feasibility study: The number of selected object types,<br>the coverage by the selected objects and the number of<br>allocated bytes in the headers of the selected object types | 101 |

|      | allocated bytes in the headers of the selected object types.                                                                                                                     | 101 |

| 4.6  | Reduction in the number of allocated bytes for the offline<br>header reduction techniques with MRT and LLMRT set |     |

|------|------------------------------------------------------------------------------------------------------------------|-----|

|      | to $0.1\%$ .                                                                                                     | 103 |

| 4.7  | Reduction in the number of allocated bytes for the online                                                        |     |

|      | header reduction techniques.                                                                                     | 103 |

| 4.8  | STVA's reduction of the memory usage overhead of 64-                                                             |     |

|      | bit mode compared to 32-bit mode.                                                                                | 105 |

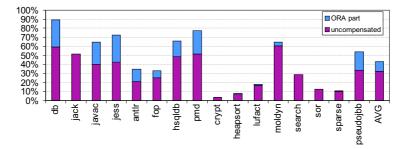

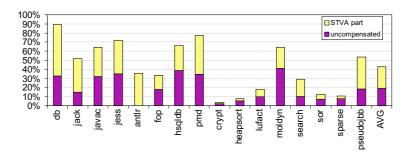

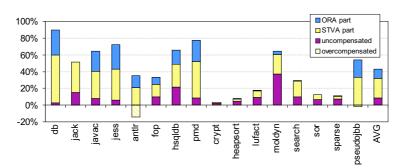

| 4.9  | The reduction in allocated bytes partitioned by TIB pointer                                                      |     |

|      | compression and online no-header STVA for the GenMS                                                              |     |

|      | collector.                                                                                                       | 105 |

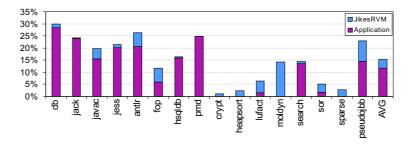

| 4.10 | Accounting the overall memory reduction to application                                                           |     |

|      | and VM objects; this graph assumes the GenMS garbage                                                             |     |

|      | collector and the online no-header STVA object model                                                             | 106 |

| 4.11 | Heap growth for GenMS collector as a function of time.                                                           | 107 |

| 4.12 | Maximum reachable bytes as a function of time for 32-bit                                                         |     |

|      | and 64-bit processing and for STVA                                                                               | 108 |

| 4.13 | Speedup of the garbage collector for offline and online                                                          |     |

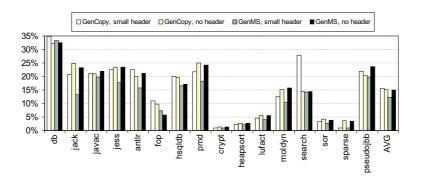

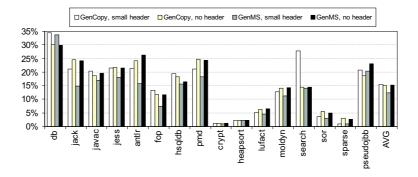

|      | header reduction.                                                                                                | 111 |

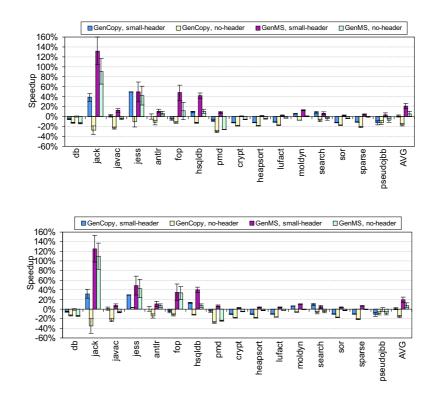

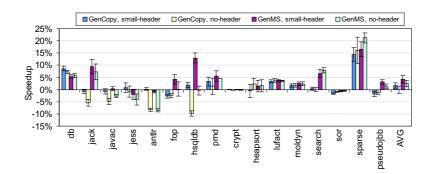

| 4.14 | Speedups along with the 95% confidence intervals for of-                                                         |     |

|      | fline header reduction. The MRT and LLMRT thresholds                                                             |     |

|      | are set to 0.1%                                                                                                  | 112 |

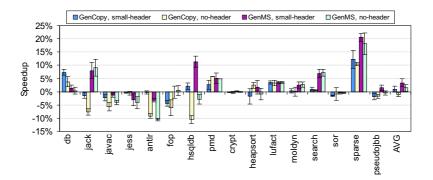

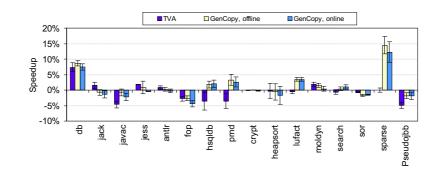

| 4.15 | Speedups along with the 95% confidence intervals for                                                             |     |

|      | online header reduction                                                                                          | 112 |

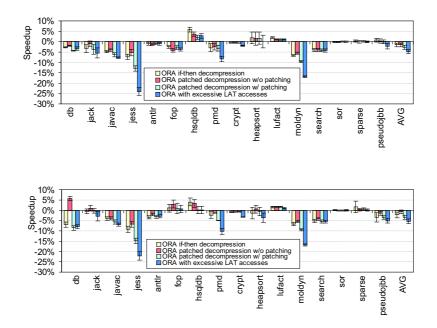

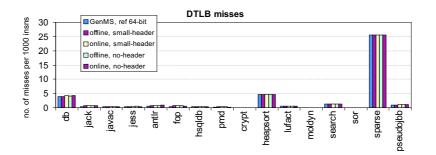

| 4.16 | The number of D-TLB misses per 1000 instructions in the                                                          |     |

|      | reference run for the GenMS garbage collector                                                                    | 112 |

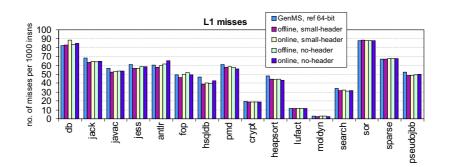

| 4.17 | 1                                                                                                                |     |

|      | in the reference run for the GenMS garbage collector                                                             | 113 |

| 4.18 | 1                                                                                                                |     |

|      | the reference run for the GenMS garbage collector                                                                | 113 |

| 4.19 | The number L3 D-cache misses per 1000 instructions in                                                            |     |

|      | the reference run for the GenMS garbage collector                                                                | 114 |

| 4.20 | Comparing STVA to TVA in terms of speedup for the                                                                |     |

|      | GenCopy garbage collector.                                                                                       | 116 |

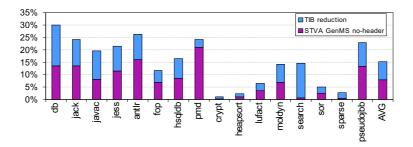

| 5.1  | ORA's and STVA's combined reduction of the memory                                                                |     |

| 0.1  | usage overhead of 64-bit mode compared to 32-bit mode.                                                           | 128 |

|      | ange et enteur et et meue computer to ez ent moue.                                                               | 0   |

# List of Abbreviations

| BiBOP | Big Bag Of Pages                   |

|-------|------------------------------------|

| D-TLB | Data Translation Lookaside Buffer  |

| DCX   | Data Compression eXtensions        |

| EB    | Exa-Byte                           |

| EM64T | Extended Memory 64 Technology      |

| FCP   | Favorable Collection Point         |

| GB    | Giga-Byte                          |

| GC    | Garbage Collection                 |

| ISA   | Instruction Set Architecture       |

| JDK   | Java Development Kit               |

| JGF   | Java Grande Forum                  |

| JIT   | Just-In-Time                       |

| JVM   | Java Virtual Machine               |

| KB    | Kilo-Byte                          |

| LAT   | Long Address Table                 |

| LLMRT | Long-Lived Memory Threshold        |

| LOS   | Large Object Space                 |

| LSB   | Least Significant Bit              |

| MB    | Mega-Byte                          |

| MRT   | Memory Reduction Threshold         |

| 00    | Object Oriented                    |

| ORA   | Object-Relative Addressing         |

| OS    | Operating System                   |

| RVM   | Research Virtual Machine           |

| STVA  | Selective Typed Virtual Addressing |

| TIB   | Type Information Block             |

| TLB   | Translation Lookaside Buffer       |

| TVA   | Typed Virtual Addressing           |

| VEE   | Virtual Execution Environment      |

| VМ    | Virtual Machine                    |

VM Virtual Machine

xxiv

## **Chapter 1**

## Introduction

The second half of the chessboard Raymond Kurzweil

The phrase "The second half of the chessboard" is derived from the fable of an ancient Chinese mathematician, who did a great deed for the emperor of China. As a reward for the great deed, the emperor promised the mathematician anything in his empire he could wish for. The mathematician replied he'd wish every day an amount of rice being placed on a square of his chessboard. The first square should contain one grain, and each successive square would have to contain the double amount of the prior, and so until all 64 squares were filled. The Emperor quickly granted this seemingly humble request.

After the first half of the chessboard was filled, the total number of grains of rice became (1 + 2 + 4 + 8 + 16 + 32 + 64 + 128 + 256 + 512 + 1024 + ... + 2.147.483.648), or  $2^{32} - 1$ . This amount corresponds to about one field of rice and is considered economically insignificant to the emperor of China. It was as they progressed through the second half of the chessboard that the situation quickly deteriorated. The second half should contain  $(4.294.967.296 + ... + 9.223.372.036.854.775.808) = (2^{64} - 2^{32})$ . That is more rice than could ever be grown on the planet in the lifetime of the emperor. One version of the story claims the emperor going bankrupt, another version says the mathematician lost his head.

### **1.1** Towards 64-bit computing

When people use the term 64-bit computing, it's not always clear what they mean. Most often, the width of the instructions, registers and/or addresses is meant. For the purposes of this text, it means executing applications on a processor with 64-bit registers and 64-bit virtual addresses.

Although we are currently in the transition from 32-bit to 64-bit computing in general-purpose systems, 64-bit technology is not new. A variety of high-end servers and applications like supercomputing and database management systems, have been using 64-bit hardware for over fifteen years. Companies that need to process huge amounts of data use 64-bit servers, because these servers can support both a large amount of data as well as large files.

Today, the market for consumer applications is making the transition towards 64-bit computing. The reason why it was running behind, is that this market was dominated by IA-32 instruction set architecture (ISA) based hardware. Motorola produced a 64-bit microprocessor in 1998: the PowerPC 620 processor. However, it was not until AMD extended the IA-32 ISA to the x86-64 ISA in its Athlon64 [32] and Opteron [47] microprocessors, that the market for consumer applications has been quickly catching up. Intel also followed with 64-bit x86 processors; they call their extension of the IA-32 ISA the Intel Extended Memory 64 Technology (EM64T) [35].

This currently widespread use of 64-bit technology is such a hype at the moment that computer system vendors have no trouble convincing consumers that the advantages of 64-bit computer systems are worth switching from 32-bit to 64-bit technology. There are still many 32-bit applications, but thanks to the backward compatibility of most 64-bit systems, these 32-bit applications can run unmodified on these new 64bit systems.

Unfortunately, there are a few drawbacks to 64-bit systems supporting backward compatibility. First, there is the inconvenience for users that applications compiled in 32-bit mode and applications compiled in 64-bit mode can not be linked together. Second, since mixedmode applications can not be linked together, each library needs to be kept twice. And third, special precautions need to be taken to support both 32-bit and 64-bit modes together: either a hardware compatibility mode—the processors support an older 32-bit ISA as well as the new 64-bit ISA—(e.g., AMD64 [1], EM64T [31], PowerPC64 [58]) or software emulation (e.g., IA-32 Execution Layer [10]), or an actual implementation of a 32-bit processor core within the 64-bit processor die (e.g., Intel Itanium [2]). The actual implementation of a 32-bit core occupies precious space on the processor die, while software emulation may face the disadvantage of being slower, due to the extra software layer. While it is not a prerequisite for the latter two cases, the support for a compatibility mode does require the 64-bit ISA to be a superset of the 32-bit ISA.

### **1.2** The pros and cons of 64-bit computing

We now discuss the advantages and disadvantages of 64-bit computing. We identify two advantages and two disadvantages that have a potentially serious impact on performance.

#### **1.2.1** The pros of 64-bit computing

Obviously, the major advantage of 64-bit computing is its very **large address space**. A 32-bit machine is limited by a 4 GB address space, this is because the machine's word size is 32 bit and addresses are typically stored as one machine word. By switching to 64-bit machines, the machine word doubles in size, while the associated address space gets squared, i.e., a 64-bit machine can theoretically address 16 EB (exabyte). This is astronomically large compared to the current usage of memory. If we presume that current systems are equipped with 16 GB, and that we would double the amount of memory usage every two years, even then it would take about 60 years before we hit the new limit.

The second advantage is the availability of 64-bit wide registers and the **extension of the Instruction Set Architecture** (ISA) with extra 64bit integer instructions. Applications that use 64-bit integer numbers can benefit a lot. A large 64-bit integer value now fits in one general purpose register, relinquishing the need for extra instructions to process intermediate results. With fewer instructions executed, execution time is expected to improve. Table 1.1 illustrates this for the multiplication of two 64-bit integer values. The last two columns show the number of instructions needed on a 32-bit processor and a 64-bit processor, respectively. This table shows that a 32-bit machine requires 6 times

| operation           | on 32-bit processor     | on 64-bit processor    |  |

|---------------------|-------------------------|------------------------|--|

| Load two 64-bit     | 4 32-bit registers      | 2 64-bit registers     |  |

| integers            | 4 load instructions     | 2 load instructions    |  |

| Multiply two 64-bit | 4 multiply instructions | 1 multiply instruction |  |

| integers            | 2 addition instructions |                        |  |

| Store one 64-bit    | 2 32-bit registers      | 1 64-bit register      |  |

| result integer      | 2 store instructions    | 1 store instruction    |  |

**Table 1.1:** Resources required to first load two 64-bit integers, multiply them, and finally store the lowest 64-bit integer result.

more instructions than a 64-bit machine to perform a multiplication of two 64-bit integers.

We would like to note that the transition to 64-bit computing triggered some ISAs to be extended even further. Since 64-bit support requires new compilers and new operating systems, it was a great opportunity to make changes that would otherwise also require new tool chains. For example in the x86-64 ISA, 8 extra general purpose registers were added in 64-bit mode (the number of registers is doubled). This of course has a serious impact on performance, since registers are the fastest form of memory available in current processors. As reported in [44], applications execute about 25% faster on average when running in 64-bit mode on the AMD Athlon 64 3800+. However, since these extra registers are not part of the 32-bit to 64-bit address space transition, we believe that such comparison is not entirely fair if one is only interested in the impact of the transition of a 32-bit to a 64-bit address space. We prefer not to take these additional 64-bit ISA extensions into account. This thesis will focus on the impact of 64-bit addresses on performance, rather than the additional ISA extensions.

#### **1.2.2** The cons of 64-bit computing

On the negative side, the most important disadvantage of 64-bit computing is the **increased memory footprint**. By doubling the machine word, every address requires twice the number of bits in memory. Table 1.2 shows the number of dynamically allocated data structures and their size increase when using 64-bit mode instead of 32-bit mode for 15 C benchmarks. The benchmarks are compiled using the gcc 3.3.2 compiler on an IBM Power 4 machine. All data types, except point-

| suite                 | benchmark | #structs | increase (%) |

|-----------------------|-----------|----------|--------------|

| Grande <sup>1</sup>   | heapsort  | 1        | 0.00         |

|                       | lufact    | 2,004    | 0.03         |

|                       | moldyn    | 3        | 0.00         |

|                       | sor       | 2,001    | 0.07         |

|                       | sparse    | 5        | 0.00         |

| PtrDist <sup>2</sup>  | ptrdist   | 32,880   | 4.74         |

|                       | anagram   | 315      | 2.95         |

|                       | ft        | 6,628    | 99.89        |

|                       | ks        | 661      | 98.68        |

| Richards <sup>3</sup> | bench100  | 14       | 48.15        |

| BioPerf <sup>4</sup>  | ce        | 19,011   | 1.51         |

|                       | glimmer   | 135      | 59.74        |

|                       | clustalw  | 4        | 60.00        |

|                       | phylip    | 5        | 60.00        |

|                       | predator  | 64,177   | 47.48        |

| AVG                   |           | 8,523    | 32.22        |

Table 1.2: Dynamic memory increase between 32-bit and 64-bit C programs.

ers, have the same size in 32-bit mode as in 64-bit mode. We observe a wide variety in the number of allocated data structures across the benchmarks. A low number means fewer dynamic structures are created, and this often corresponds to a small increase in memory usage, indicating that the program is doing merely arithmetic computations on a few data structures. For example, the *Grande* applications perform arithmetic operations on large matrices. Large memory increase numbers indicate that there are a lot of pointers between dynamic structures, e.g., the benchmarks *ft* and *ks* show a close to 100% memory increase because these benchmarks almost exclusively perform operations on linked data structures.

Increased memory usage both incurs a cost component and a performance degradation component. We first discuss the cost component. One way of dealing with excessive memory usage is to provide more physical memory in the machine, however, this is costly as physical memory is a significant cost factor in today's computer systems. While in high-end servers extra memory can be installed at a greater cost,

<sup>&</sup>lt;sup>1</sup>http://www.epcc.ed.ac.uk/javagrande/langcomp.html

<sup>&</sup>lt;sup>2</sup>http://www.cs.wisc.edu/ austin/ptr-dist.html

<sup>&</sup>lt;sup>3</sup>http://www.cl.cam.ac.uk/ mr10/

<sup>&</sup>lt;sup>4</sup>http://www.bioperf.org/

there are systems that have strict space constraints, e.g., embedded systems. Designers of embedded systems are always looking for ways to shrink the hardware dimensions and to scale down the cost of their product. For these systems, increasing the amount of physical memory in the system may not be an option.

The increased memory usage may also lead to performance degradation. Although main memory access latency is typically mitigated by a hierarchy of caches, these caches are relatively small in comparison to main memory. The working set of 64-bit applications increases in size with regard to the working set of their 32-bit counterparts, without the injection of extra information (i.e., the same amount of information occupies more memory), and hence caches are more sparsely filled with useful data. This leads to more cache and translation lookaside buffer (TLB) misses, extra pressure on main memory (i.e. bandwith) and hence to overall performance degradation. This is especially of concern on heavily-loaded machines with many simultaneously running programs that are memory-intensive; overall system performance quickly deteriorates once physical memory is exhausted.

Main memory accesses tend to dominate more and more an application's execution time. This can be explained by Moore's law, which states that advances in semiconductor technology double the transistor density of integrated circuits every 18 months. Although processor performance has roughly followed this law and doubled every 18 months for the past decades, memory access time on the other hand did not follow the same speedup rate (only 7% improvement every year [37]), leading to a continuously widening of the *gap* between processor speed and memory speed. Since the *gap* is widening, the number of memory accesses — each main memory access typically takes hundreds of processor cycles — have more and more impact on the performance of the system. Next to performance degradation, the increased memory usage may potentially also increase power consumption because fewer memory banks can be shut off, there is more bus traffic, etc.

The second disadvantage of 64-bit computing is related to **address translation**. If address translation is done through the means of page tables, more levels of indirection need to be traversed in order to translate the virtual address into a physical address. In the x86 ISA family for example, a 2-level page table is used, while on the x86-64 architecture there exists a 4-level page table [1]. Because each entry in a page table is now 64 bit wide, only half of the entries can be stored in an equally

sized page. With the 4-level page scheme, only 48 bits of the virtual address space can be supported. In order to support the entire 64-bit address space, extra levels are needed. All these extra indirections of course slow down the retrieval of a page from memory and thus slows down TLB miss handling. In fact, the x86-64 Linux port already tries to limit the overhead by currently only using three of the four levels, providing only a 39-bit address space for user processes [46]. The PowerPC microprocessor family does not use a hierarchical page table, but instead uses a reversed page table system [56], needing a hashing scheme to find the corresponding physical address of a virtual address. The Intel Itanium processor provides both a linear and a hashed mechanism for hardware page walking [18].

### **1.3** Assessment: 64-bit computing or not?

We outlined the transition of 32-bit technology to 64-bit technology and the existence of different modes on the latter and we listed a number of advantages and disadvantages related to 64-bit technology. Now we will reason about these technologies and modes and make an assessment about 64-bit technology.

If an application requires a 64-bit virtual address space, it is obvious there is only one path to walk. Otherwise, if there is no such requirement, a choice can be made to run it either on a 32-bit system, or on a 64-bit computer system in 64-bit mode, or on a 64-bit computer system in 32-bit mode (if available). For the rest of this discussion we will presume the existence of a 32-bit compatibility mode on a 64-bit computer system which does not introduce an extra performance penalty compared to running on a 32-bit computer system<sup>5</sup>.

We will now discuss the choice between the three options just presented, using Table 1.3. This table gives an overview of the advantages and disadvantages of 64-bit computing, applied to each choice. First, the choice between a 32-bit computer system versus a 64-bit computer system in 32-bit compatibility mode will be elucidated, followed by a discussion of 32-bit mode versus 64-bit mode on a 64-bit computer system. We will argue why 64-bit computing is not always better, explain

<sup>&</sup>lt;sup>5</sup>We will not take into account performance penalties caused by running 32-bit mode on 64-bit systems. Some 64-bit architectures such as the AMD64 [25] do not incur additional overhead when running 32-bit programs in 32-bit compatibility compared to an equivalent 32-bit architecture.

|                     | 32-bit hardware | 64-bit hardv       | 64-bit hardware |  |

|---------------------|-----------------|--------------------|-----------------|--|

|                     | 32-bit mode     | compatibility mode | 64-bit mode     |  |

| Address Space       | -               | +                  | +               |  |

| Extended ISA        | -               | -                  | +               |  |

| Memory footprint    | +               | +                  | -               |  |

| Address translation | +               | -                  | -               |  |

Table 1.3: Overview advantages/disadvantages of 32-bit/64-bit computing.

the main cause of why this is the case, and throw light on the circumstances in which this cause is most likely problematic.

# 1.3.1 32-bit computing systems versus 32-bit compatibility mode on 64-bit computing systems

At first it might look as if there is no difference at all between a 32bit computing system and a(n) (equivalent) 64-bit computing system in compatibility mode, because we stated earlier that no extra performance overhead is incurred to run 32-bit compatibility mode on 64-bit computer systems. But some subtle differences do exist. We will now discuss each of the advantages/disadvantages of Table 1.3:

- The first advantage on the 64-bit system (Table 1.3) is related to the virtual address space. The address space on a 32-bit machine is limited to less than 4 GB in practice, since a large part of the 4 GB address space is already reserved by the operating system (OS) for kernel code and shared libraries, leaving only 2 to 3 GB for user purposes. Although in compatibility mode, the virtual address space of a 64-bit machine is limited to 4 GB, the application can now use the entire 4 GB because compatibility mode on a 64-bit machine is running a 64-bit OS. The OS sees the entire 64-bit address space, and can map the 4 GB virtual address space of the 32-bit application to a different 4 GB segment from the first 4 GB segment which is typically partially used by the OS.

- The second item of Table 1.3, the extended ISA on 64-bit systems, does not apply in compatibility mode nor on 32-bit systems, since these extensions are simply not available.

- A 32-bit application run in compatibility mode will not suffer

from the third item either, an increased memory footprint, because it was compiled as a 32-bit application, and, by consequence, it will use the same amount of memory as running it on a 32-bit system.

• The fourth item related to address translation might apply since the 64-bit system is running a 64-bit OS that has access to the entire virtual address space. However, since there are systems that use hashing schemes (e.g., PowerPC, Itanium), which are similar for both systems, this disadvantage can be bypassed.

In conclusion, there are only subtle differences between a 32-bit computer system and a 64-bit computer system running in 32-bit compatibility mode. However, there is some slight advantage to the 64-bit machine running in compatibility mode.

### 1.3.2 32-bit compatibility mode versus 64-bit mode

Now we compare the 32-bit compatibility mode with the 64-bit mode on a 64-bit computer system. We will do this once again by discussing each of the four advantages/disadvantages listed in Table 1.3:

- Because we are discussing applications that have no need for a 64-bit address space, the first item of Table 1.3 does not apply. Both modes provide at least 4 GB virtual address space to the application.

- The second item about the extended ISA, on the contrary, is only available in 64-bit mode, so applications can only benefit when compiled for 64-bit mode.

- The third item of Table 1.3, concerning the memory footprint, applies also. There is a clear disadvantage for 64-bit mode, having an increased memory usage.

- The last item about address translation does also not apply in this discussion, since both modes run on the same machine with the same 64-bit OS.

To conclude, we can say that for applications requiring less than 4 GB virtual address space, running in 32-bit mode will benefit from

a smaller memory footprint, while running in 64-bit mode might improve performance due to the extended ISA. As there are always pointers in real-life applications, the overhead of the increased memory usage will always occur, while the extended ISA advantage will only be exploitable for applications using large integers.

#### 1.3.3 64-bit mode: the all-around solution?

Although 64-bit computing is the future trend, the previous discussion suggested that many applications that do not require more than 4 GB of memory, will still perform best in 32-bit mode. This is a little inconvenient as two modes might need to be supported for a long time to come. We already summarized some drawbacks of supporting two modes in section 1.1, namely that object files compiled in different modes can not be linked together, and that therefore two copies of each programming library are needed. It would be better to have to support only one mode. One mode would simplify the computer hardware and the operating system. Having only the 64-bit mode would however lead to a substantial increase in memory usage, as discussed above. This increased memory usage is the obstacle that keeps us from switching *en masse* to 64-bit computing.

**Implications on Object-Oriented Languages.** The inflated pointer size is the major cause of increased memory usage when transferring from 32-bit computing to 64-bit computing. The *pointer* concept did not exist in the early fortran77 language, but is widely used in C programs to access and manipulate data structures. Object-Oriented (OO) programming languages go one step further and add extra functionality to the data structures, which are now called *objects*. Each object may receive messages, may process data, and may send messages to other objects. Objects often contain pointers to other objects, and, as such, when messages are passed between objects, chains of pointers are chased in the process.

If we go yet one step further in the chain of software development, we see that in modern software development technology next to the language, an environment gets created in which an application resides. A Virtual Execution Environment (VEE) shields off the application from the underlying platform, by presenting a virtual machine (VM) that provides platform independence to the application. VEEs are very

| suite                  | benchmark | #structs    | increase (%) |

|------------------------|-----------|-------------|--------------|

| Grande <sup>6</sup>    | heapsort  | 82          | 0.00         |

|                        | lufact    | 2,086       | 0.03         |

|                        | moldyn    | 9,063       | 15.15        |

|                        | sor       | 2,084       | 0.03         |

|                        | sparse    | 90          | 0.00         |

|                        | search    | 34,517,857  | 27.18        |

| SPECjvm98 <sup>7</sup> | jess      | 32,178,443  | 71.74        |

|                        | db        | 13,267,280  | 91.19        |

|                        | javac     | 23,501,089  | 60.01        |

|                        | jack      | 35,490,673  | 55.26        |

| DaCapo <sup>8</sup>    | antlr     | 12,966,988  | 29.17        |

| -                      | fop       | 1,180,024   | 47.20        |

|                        | hsqldb    | 11,813,470  | 87.26        |

|                        | pmd       | 154,355,087 | 78.88        |

| SPECjbb20009           | pseudojbb | 74,902,214  | 49.20        |

| AVG                    |           | 26,279,102  | 40.82        |

Table 1.4:

Dynamic memory increase between 32-bit and 64-bit Java programs.

popular nowadays, see for example the Java Virtual Machine and the .NET environment. Virtual execution environments provide benefits in terms of portability, improved security and better resource management. For example, the Java Virtual Machine (JVM) manages its own object allocation and deallocation: reclamation of dead objects from the heap is done by a garbage collector. In order to support garbage collection and some other object functionality like virtual method dispatching, locking and hashing, the JVM needs to be able to keep track of object-specific information. This information is typically stored in a header attached to each object.

With regard to memory management, OO-languages tend to use more dynamic memory than non-object-oriented languages like C. Calder et al. [17] compare C to C++ applications and observed that C++ applications allocate 4x more dynamic memory than C applications, on average. A first reason is obviously the extra object headers

<sup>&</sup>lt;sup>6</sup>http://www.javagrande.org

<sup>&</sup>lt;sup>7</sup>http://www.spec.org/jvm98

<sup>&</sup>lt;sup>8</sup>http://www.spec.org/jbb2000

<sup>&</sup>lt;sup>9</sup>http://dacapobench.org/

which require memory chunks to be larger, and second, since everything is an object in an OO-language like Java, more chunks of memory are likely to be allocated [33]. Table 1.4 shows the number of objects allocated for 15 Java benchmarks and the increase in dynamic memory utilization when making the transition from 32-bit to 64-bit pointer representation. Comparing Table 1.4 to Table 1.2 clearly shows that Java applications typically allocate more dynamic data structures. The added object headers typically contain pointers, and hence make the total memory increase in an OO-language like Java even more drastic (e.g., Table 1.4 shows a 40.82% increase on average, compared to a 32.22% increase in Table 1.2). The low increase in dynamic memory utilization for most of the *Grande* applications can be explained by the nature of these applications—they operate on large arrays and do not manipulate pointers frequently.

### 1.3.4 Conclusions

As a general conclusion of whether it is worth adapting to 64-bit computing or not, we can make a few statements.

First, **64-bit technology cannot be stopped.** All major manufacturers on the general-purpose consumer market have integrated 64-bit technology in all of their products. As 64-bit computer systems with a 32-bit compatibility mode seem to have a slight advantage over pure 32-bit computer systems, the current hype on the consumer market might make sense. Consumers who buy 64-bit technology do not have to give up performance for applications that can run in 32-bit mode. In addition, having a 64-bit computer makes them ready for future applications which might need the extended virtual address space. Moreover, manufacturers can produce only one architecture (that supports both 32-bit and 64-bit applications) instead of two. Due to the economy of scale, production costs decrease, which is again favorable for the consumers.

Second, **64-bit computing is not always better than 32-bit computing.** The statement that consumers would not have to give up performance on 64-bit computer systems is only valid assuming compatibility mode. In 64-bit mode, the real benefit depends on the application. If the application cannot benefit from the address space increase or the 64-bit operations, it will probably suffer from the increased memory footprint. Third, **OO-languages and VEEs suffer more from the disadvantages of 64-bit computing.** If 64-bit mode is used, the increased memory size is the largest cost. The memory increase effect is the largest for applications with many strongly connected objects, but since this effect is even intensified by OO-languages and execution environments with memory management, 64-bit computing is expected to be worse in such an environment.

In general, without space saving techniques specifically targeted at 64-bit platforms, good judgement is in order whether to compile an application in 32-bit mode or in 64-bit mode. If each bit of the 64 bit of an address corresponds to a square of the mathematician's chessboard in the Chinese fable, one should be careful not to make the same mistake as the emperor, entering the second half of the chessboard unadvised.

# **1.4** Goal and contributions of this thesis

Ideally, applications should only take advantage of 64-bit computing without its associated cost. In reality though, these two factors are connected, and a trade-off has to be made between extra addressability and extra memory usage. In this dissertation we make such a trade-off and search for a way in between: use the advantages of 64-bit computing while avoiding paying the penalties, or in other words, provide a 64-bit address space for applications that need it, while minimizing excessive memory usage because of 64-bit pointers for applications that do not require a 64-bit address space. This thesis makes three major contributions:

• A detailed 64-bit memory usage characterization study. Our first contribution [69] is to characterize the impact of the transition from 32-bit to 64-bit computing on memory usage and overall performance for Java workloads. We found that objects grow on average with about 45.3% when going from a 32-bit to a 64-bit Java Virtual Machine. We identified the inflated pointer size of 64-bit pointers as the major cause of this increased object size. From this characterization, we observe that pointers exist in the object data as well as in the object header and that both are responsible for a major part of this increased object size. We also study the memory usage of applications through time, and compare heap growth behaviors of a 32-bit VM and a 64-bit VM. We perform a

detailed performance analysis including cache and TLB miss rate characterization.

• **Object-Relative Addressing.** The cost of 64-bit computing, i.e., the increased memory usage, can be reduced by space saving techniques specifically targeted at 64-bit platforms. In order to achieve a smaller memory footprint, we reduce the size of each/most of the dynamically allocated memory chunks. In Java, each object is dynamically allocated. An object consists of a header and a body and both can contain references. This thesis addresses the excessive memory usage in both the header and the body.

Our first technique concentrates on the object body. References inside the body of an object are used to create links between objects. As linked objects tend to form clusters [60], it is possible to lay out objects on the heap so that many linked objects are in close proximity [39]. If objects are known to be in close proximity, the reference can be encoded in less than 64 bit. Recall that a reference is an abstraction of a pointer, and hence its physical representation can be chosen freely. We propose a technique, called Object-Relative Addressing (ORA), which stores an inter-object reference as a 32-bit offset relative to the referencing object's virtual address. ORA results in more than 10% reduction in allocated bytes for many benchmarks while enabling applications to allocate more than 4 GB, unlike prior work in this area [3]. ORA is published in [72].

• Selective Virtual Typed Addressing. Our third contribution is a technique that reduces the excessive memory usage in the object header. Each object typically has a header attached for the VM to perform internal functionality such as virtual method dispatching, garbage collection, hashing, locking, etc. The object header typically contains a reference that (indirectly) reveals an object's type. In contrast to the references in the body, the purpose of this reference is not to link objects, but to identify the object's run time type. A first observation is that in real-life applications there are only several thousands of types, so using 64 bit in order to distinguish object types is likely to be excessive. Second, the 64-bit virtual address space is so huge, that it is extremely unlikely that this entire space is going to be used in the next few decade(s). Hence we could give each object type its own parti-

tion of the virtual address space, i.e., we allocate all objects of a given type in a particular memory segment. Object type identification can then be done by looking at the address of the object itself, rather than loading a reference from its header. We call this technique Typed Virtual Addressing (TVA). By doing so, the type information in the header gets redundant and hence can be removed. In order not to create excessive fragmentation due to all object types being allocated in different regions in memory, we apply TVA to a selection of objects only, hence the name Selective Typed Virtual Addressing (STVA). Next to applying STVA, we also propose techniques to remove the remaining header fields. In [70] we describe how the selection criterion of STVA can be performed offline and how we reduce the object header from 16 bytes to 4 bytes. Next, [71] extends the former paper by removing the entire object header and by proposing an online TVA selection technique. This reduces memory demands by 15% on average.

# 1.5 Publications

This thesis has three contributions: a characterization study of the memory usage and overall performance of 32-bit and 64-bit applications, a pointer compression technique and a header removal technique. These contributions are published in the following papers.

• The characterization study is published in the paper:

[69] Kris Venstermans, Lieven Eeckhout, and Koen De Bosschere. 64-bit versus 32-bit Virtual Machines for Java. In Software-Practice and Experience (SPE), 36(1): pages 1-26, Jan 2006.

• The ORA pointer compression technique is further detailed in:

[72] Kris Venstermans, Lieven Eeckhout, and Koen De Bosschere. **Object-Relative Addressing: Towards Compressed Pointers in 64-bit Java Virtual Machines**. In Proceedings of the 21st European Conference on Object-Oriented Programming (ECOOP'07), to be published. July 2007.

• The next publications describe the Typed Virtual Addressing

(TVA) and Selective Typed Virtual Addressing (STVA) techniques:

[71] Kris Venstermans, Lieven Eeckhout, and Koen De Bosschere. Java Object Header Elimination for Reduced Memory Consumption in 64-bit Virtual Machines. In ACM Transactions on Architecture and Code Optimization, to be published, 2007.

[70] Kris Venstermans, Lieven Eeckhout, and Koen De Bosschere. Space-Efficient 64-bit Java Objects through Selective Typed Virtual Addressing. In proceedings of the 4th Annual International Symposium on Code Generation and Optimization (CGO), pages 76-86, Mar. 2006.

Besides the contributions described in this dissertation, we also performed research on garbage collection.

• Garbage Collection Hints. Current garbage collection (GC) techniques typically trigger when either the heap, or a part thereof, is full. In between two runs no objects get deallocated, i.e., dead objects need to wait for the next GC to be discovered and freed. The right time to collect is a balance between freeing up unused memory as soon as possible and freeing up as much memory as possible at once. GC algorithms can be made smarter when provided with liveness information from the application [41]. We present a technique, that during the execution of a program feeds back the amount of live data of a training run of that program. From this live data information, execution points can be identified, where the amount of live data reaches a local minimum. We call these execution points favorable collection points (FCPs). In particular, less dead objects occupy the heap if collections are triggered at points in time where the amount of live data is low. The proposed Garbage Collection Hints mechanism helps the VM to decide when and how to collect at these FCPs. This fourth contribution is not included in this thesis, but is published in:

[15] Dries Buytaert, Kris Venstermans, Lieven Eeckhout, and Koen De Bosschere. **GCH: Hints for Triggering Garbage Collections**. In Transactions on High-Performance Embedded Architectures and Compilers, 1(1):pages 52-72, Jun. 2006.

[14] Dries Buytaert, Kris Venstermans, Lieven Eeckhout, and

Koen De Bosschere. **Garbage Collection Hints**. In Proceedings of High-Performance Embedded Architectures and Compilers 2005 (HiPEAC'05), LNCS 3793, pages 233-348, Nov. 2005.

# 1.6 Overview

This dissertation is organized as follows. First, chapter 2 quantifies the increased memory usage of 64-bit computing versus 32-bit computing for Java workloads. In addition, it identifies the major causes of this increase and evaluates the impact on performance.

Since inflated references can cause a significant memory usage increase in 64-bit virtual machines, we investigate memory saving techniques in chapters 3 and 4. Chapter 3 describes the Object-Relative Addressing technique to reduce pointer sizes, while Chapter 4 describes (Selective) Typed Virtual Addressing.

Finally, Chapter 5 summarizes the main conclusions and results from this dissertation and finishes with some perspectives at future work. \_\_\_\_\_

# **Chapter 2**

# 64-bit versus 32-bit computing: a characterization

A lie told often enough becomes the truth. Nikolai Vladimir Ilyich Lenin

In this chapter we are interested in 32-bit versus 64-bit Java processing and its impact on performance. Many speculations have been made about the impact on performance of 64-bit versus 32-bit computing, however, few quantitative results are available. The speculations being made typically concern the impact on memory usage and the impact on execution speed. To the best of our knowledge, this thesis is the first to investigate the impact of 32-bit versus 64-bit computing in the context of Java workloads. In this chapter, we study and quantify both the increased memory requirements due to 64-bit computing and its impact on overall performance in Java.

# 2.1 Introduction