# Wim Bogaerts<sup>123</sup>, Martin Fiers<sup>1</sup>, Massimo Sivilotti <sup>4</sup>, Pieter Dumon<sup>1</sup>,

<sup>1</sup>Luceda Photonics, Noordlaan 21, 9200 Dendermonde, Belgium.

<sup>2</sup>Ghent University-IMEC, Photonics Research Group, Department of Information Technology, Gent, Belgium.

<sup>3</sup>Center of Nano- and Biophotonics (NB Photonics), Gent, Belgium.

<sup>4</sup>Mentor Graphics, Fremont, CA, USA.

wim@lucedaphotonics.com

**Abstract:** We present the IPKISS photonic design framework, which integrates tightly with the L-Edit layout tool. This close link between connectivity and layout allows automatic waveguide generation, adjust connectivity in layout, and verify with post-layout simulations.

**OCIS codes:** (250.5300) Photonic integrated circuits; (130.0130) Integrated optics

#### 1. Introduction

Silicon photonics is rapidly becoming an industrial technology, and this is rapidly changing the requirements for the design of *photonic integrated circuits* (PIC). It is the first true *large-scale integration* technology for photonics, with fabrication requirements that require similar *design for manufacturability* (DfM) as advanced CMOS electronics [1]. In addition, PICs require electronic control, which drives photonic design towards *electronic design automation* (EDA).

Photonics and electronics are both based on planar semiconductor processes and can both be treated as circuits. That is why photonic designers are gruadually adopting a design flow similar to that for analog ICs. Starting from a component library a *schematic* circuit is constructed, which is then used as the basis for the physical *layout*. Such *schematic driven layout* (SDL) can be done manually, but only shows it true potential when supported by design automation software. Most importantly, at the end of the design process, the layout has to be verified against the original circuit schematic [2].

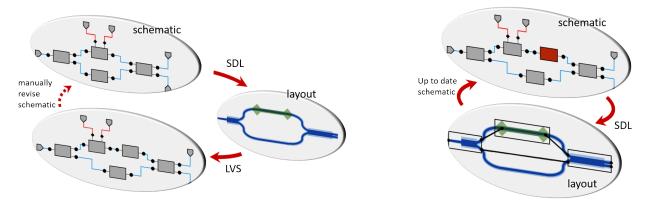

This flow has been well established for analog IC design, but it cannot always be directly applied to photonics design, for the same reason that analog IC design is challenging for advanced CMOS nodes. The key practical obstacle is that in photonics the layout and circuit behavior are very tightly linked, requiring several design iterations to obtain the desired functionality. Traditionally, these iterations require the designer to take one or two steps back in the flow and manually adjust the schematic design. However, such iterations can become numerous, non-trivial and therefore costly. This is especially true if every step involves the transfer of design data between different design tools or even different designers. Photonic design will benefit from a flow where the impact of the layout on the circuit design is more immediate and the integrity of design data exchange is structurally built into the circuit design flow.

Fig. 1. Photonic circuit design flows (a) Open-loop SDL flow. Modifications after verification need to restart from the original schematic (b) Closed-loop design flow, where functional and layout design are tightly coupled.

In photonics, the same can be applied for physical component design. A significant part of photonic design activities is still focused on geometric optimization of existing and new functional building blocks. Here again, the interaction between the fabrication layout and the component behavior is very strong. Design data exchange of parametric cells between different design tools dramatically facilitates the design process of individual components. Given that photonic components can have very irregular geometries, it is also important that this data exchange is not limited to electronic concepts (e.g. Manhattan geometries).

In this paper, we discuss recent improvements in IPKISS, a parametric design framework for integrated photonics that addresses these concerns [3]. Schematic design and layout are intricately connected, and the integration with EDA data exchange standards enables tight interaction within an existing EDA environment. We illustrate how we facilitate iterations between layout and circuit on a small example circuit, without having to leave the layout tool.

#### 2. The IPKISS Framework

IPKISS is a design framework for photonic integrated circuits. At the core are powerful definitions of *parametric cells* (PCell) that integrate all representations of a component or (sub)circuit. Each PCell has multiple *views* that describe a part of the design (a *netlist*, mask layout, circuit models, a physical simulation, etc.). The user interacts with each view by setting parameters and retrieving the resulting data, and views can also interact with one another. For instance, for SDL the layout can automatically extract the connectivity from the netlist to generate waveguides. When a circuit is layed out, the model will be updated with the actual waveguide lengths. IPKISS coordinates this interaction, avoiding duplicate or conflicting information, making design iteration less error prone.

The core of IPKISS is a Python scripting engine. Pcells are simple script files, that can be combined into larger libraries. Python is an industry-standard scripting language with a large ecosystem of scientific and engineering libraries. Python is also very easy for interaction with third-party design and simulation tools.

## 3. EDA Integration

IPKISS PCells integrate directly into an EDA design flow through *OpenAccess* (OA), an industry standard for the exchange of design data between EDA tools, and supported by multiple vendors. Through OA, we have interfaced IPKISS with *L-Edit* to enable a photonic design flow. L-Edit, a full-custom electronic Layout tool by Mentor Graphics (originally by Tanner EDA), supports an SDL flow through integration with schematic editors (e.g. S-Edit) and verification tools (e.g. HiPerVerify or Calibre).

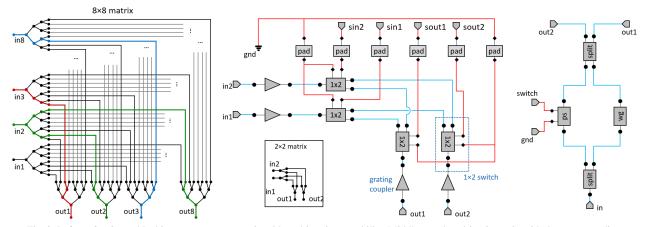

Fig. 2. Left: an  $8\times 8$  non-blocking crossconnect matrix with multicasting capability. Middle: a reduced  $2\times 2$  matrix with the corresponding photonic-electronic circuit. Note that the topology of this circuit requires at least one crossing. Right: The subcircuit schematic of the  $1\times 2$  switch.

However, as discussed, back-and-forth transitions between separate schematic and layout design tools can complicate a photonic design flow, given the strong impact of layout on circuit behavior. Therefore, the optical connectivity can be defined directly in L-Edit (or import from another tool). L-Edit's routing functions can then be used to define the physical connections, from which IPKISS generates the actual waveguide layouts with bends. Because photonic circuits are usually implement in a single routing layer, the immediate visual feedback on the circuit topology in the layout (e.g. unwanted crossings) reduces both the design time and the potential errors. At any time, the layout can be simulated to verify the circuit performance.

## 4. An example

We illustrate this flow while constructing a  $2 \times 2$  optical crossbar switch. When scaled up, this  $2 \times 2$  switch becomes a full  $N \times N$  crossconnect matrix [4]. Figure 2 shows the full crossconnect matrix, and the reduced  $2 \times 2$  circuit. The circuit is both electrical and optical, using thermo-optic  $1 \times 2$  switches with a tunable split ratio to allow multicasting.

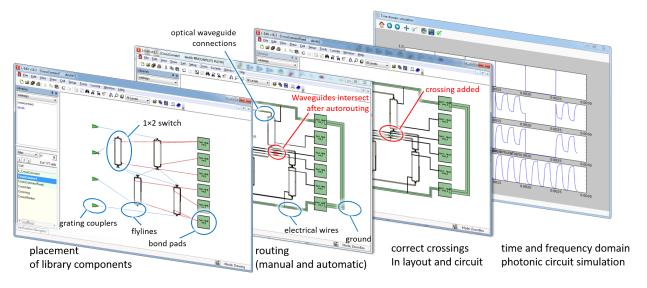

To design this circuit in a silicon photonics technology, we start from building blocks from a *process design kit* (PDK). Figure 3 illustrates our design procedure. We can pick, place and parametrize the IPKISS PCells directly in the L-Edit layout tool, and define the connections with *flylines*. Alternatively, we can import a circuit description (e.g. as a SPICE or VerilogA netlist, or from the OA database) from which the components will be selected and connected automatically. For the electrical connections to the Pads, we use L-Edit's wiring tools. For the waveguides, we let IPKISS determine a first routing solution, which takes care of bends and transitions between different types of waveguides. This identifies a waveguide crossing that needs correction. To correct this, we manually insert a crossing component and reconnect it to the corresponding switches. From this new connectivity, IPKISS generates new waveguides. At any stage of the construction of the layout we can perform a simulation of the circuit using the *Caphe* optical circuit simulator, which allows us to verify whether the corrections (e.g. inserting the crossing) affect the functional behavior.

Fig. 3. Constructing the  $2 \times 2$  crossbar switch of Fig. 2. Left to right: placing and logically connecting the library components; generating waveguides and electrical wires; correction of the waveguides by introducing a crossing; Time-domain simulation of the switching behavior.

### 5. Conclusion

The IPKISS design framework enables a tight integration of the circuit and layout design flow of photonic integrated circuits. The integration with the L-Edit Layout tools facilitates the definition and reiteration of both the connectivity as the physical layout, and allows direct post-layout simulation and verification from the same design environment.

### References

- 1. W. Bogaerts, M. Fiers, and P. Dumon, "Design challenges in silicon photonics," J. Sel. Top. Quantum Electron. **20**, 1–8 (2014).

- R. Cao, J. Billoudet, J. Ferguson, L. Couder, J. Cayo, A. Arriordaz, and I. O'Connor, "LVS check for photonic integrated circuits: Curvilinear feature extraction and validation," in "Proceedings of the 2015 Design, Automation & Test in Europe Conference & Exhibition," (EDA Consortium, San Jose, CA, USA, 2015), DATE '15, pp. 1253–1256.

- 3. M. Fiers, E. Lambert, S. Pathak, P. Dumon, B. Maes, P. Bienstman, and W. Bogaerts, "Improving the design cycle for nanophotonic components," J. Comp. Sci. 4, 313 324 (2013).

- 4. L. Chen and Y. kai Chen, "Compact, low-loss and low-power 8×8 broadband silicon optical switch," Opt. Express **20**, 18,977–18,985 (2012).