#### Universidade do Minho

Alves, Ricardo

#### Distributed shared memory on heterogeneous CPUs+GPUs platforms

http://hdl.handle.net/1822/27975

#### Metadados

Data de Publicação2012-12-19ResumoDeveloping for heterogeneous platforms can significantly complicate<br/>the coding process, since different processing devices mean different<br/>architectures, programming and memory models, disjoint address spaces<br/>and so on. This document proposes that the development process can be<br/>eased by virtualizing a traditional shared memory environment on top<br/>of the heterogeneous distributed system and exposing a unified memory<br/>model to the developer. The memory system frees the developer from<br/>having to manual...TipomasterThesis

Esta página foi gerada automaticamente em 2015-03-23T15:38:51Z com informação proveniente do RepositóriUM

**Universidade do Minho** Escola de Engenharia

Ricardo Daniel Queirós Alves Distributed Shared Memory on Heterogeneous CPUs+GPUs Platforms

Universidade do Minho Escola de Engenharia Departamento de Informática

# Ricardo Daniel Queirós Alves Distributed Shared Memory on Heterogeneous CPUs+GPUs Platforms

Dissertação de Mestrado Mestrado em Engenharia Informática

Trabalho realizado sob orientação de Professor Luís Paulo Santos Professor Donald Fussell

# Acknowledgements/Agradecimentos

Apesar do processo de elaboração de uma tese de mestrado seja algo solitário por natureza, esta dissertação reúne contribuições de várias pessoas. Durante o meu mestrado contei com o apoio e confiança de imensas pessoas, sem as quais este projeto não teria sido possível.

Ao meu orientador, professor Luís Paulo Santos, agradeço a sua paciência, disponibilidade e as diversas discussões e contribuições que foram muito valiosas para este trabalho. *I would also like to thank my co-advisor, professor Donald Fussell, for the opportunity and trust invested in me.* Quero também estender este agradecimento aos professores Alberto Proença e José Nuno Oliveira que, apesar de terem contribuído de uma forma mais indireta nesta dissertação, assumiram um papel de destaque na minha formação ao longo de todo o meu percurso académico na universidade do Minho.

Aos meu colegas do *LabCG* agradeço o apoio e a disponibilidade para debater e trocar ideias. Mas acima de tudo, agradeço a amizade e o ambiente que criaram no laboratório que tornou todo o processo de elaboração desta dissertação muito mais agradável. Em especial, agradeço o contributo e apoio do engenheiro João Barbosa, que foram essenciais para a conclusão deste projeto.

Por último, agradeço aos meus pais, familiares e amigos o apoio e incentivo que me deram, não só neste último ano, mas ao longo de todo o meu percurso académico e pessoal. Um humilde obrigado para amortizar uma dívida que nunca vou conseguir pagar.

### Resumo

Desenvolver aplicações para plataformas heterogéneas pode dificultar significativamente o processo de codificação, visto que o uso de dispositivos de computação diferentes significa ter que lidar com arquiteturas diferentes, modelos de programação e organização de memória diversos, espaços de endereçamento de memória disjuntos, etc. Este documento propõe que o processo de desenvolvimento pode ser simplificado ao virtualizar um ambiente de memória partilhada tradicional em cima de um sistema de memoria heterogéneo distribuído e expondo um modelo de memória unificado ao programador. O sistema de memória liberta o programador da gestão manual dos dados e permite o uso de memória dinâmica acessível por todos os dispositivos.

O sistema de memória proposto foi implementado e validado na *frame-work GAMA* usando três algoritmos para testar o sistema: SAXPY, simulação N-Body "all-pairs" e Barnes-Hut. Estes algoritmos foram usados para avaliar o desempenho e a escalabilidade da *framework* quando equipada com o sistema de memória proposto.

Os resultados mostram que, de uma forma geral, o sistema de memória melhorou o desempenho de todos os algoritmos. O sistema de memória provou ser mais útil em algoritmos com uma alta razão de computação sobre acessos a memória e especialmente em algoritmos irregulares ao melhorar também a escalabilidade. O alocador de memória paralelo mostrou óptimos resultados quando usado apenas no CPU, mas teve problemas na velocidade de alocação quando foram adicionados GPUs ao sistema.

#### Abstract

Developing applications for heterogeneous platforms can significantly complicate the coding process, since different processing devices mean different architectures, programming and memory models, disjoint address spaces and so on. This document proposes that the development process can be eased by virtualizing a traditional shared memory environment on top of the heterogeneous distributed system and exposing a unified memory model to the developer. The memory system frees the developer from having to manually manage data movements and allows the use of dynamic memory, accessible by all the devices.

The proposed memory system was implemented and validated on the *GAMA* framework using three algorithms to benchmark the system: SAXPY, all-pairs N-Body simulation and Barnes-Hut N-Body simulation. These algorithms were used to evaluate the framework's performance and scalability when equipped with the proposed memory system.

The results show that, overall, the memory system improved performance on all algorithms. The memory system proved most useful on algorithms with high ratio of computation over memory accesses by improving execution times and especially useful on irregular algorithms by improving scalability as well. The parallel memory allocator showed great results when used only on CPU, but had speed issues when GPUs were added the system.

# Contents

| $\mathbf{C}$  | onter  | $\mathbf{nts}$ |                                            | iv   |

|---------------|--------|----------------|--------------------------------------------|------|

| $\mathbf{Li}$ | ist of | Figur          | es                                         | vi   |

| $\mathbf{Li}$ | ist of | Table          | s                                          | viii |

| N             | omer   | nclatur        | re                                         | ix   |

| 1             | Intr   | oduct          | ion                                        | 1    |

|               | 1.1    | Distri         | buted shared memory systems                | 2    |

|               | 1.2    | Dynai          | mic memory allocators                      | 4    |

|               | 1.3    | Motiv          | ation and goals                            | 4    |

|               | 1.4    | Docur          | ment organization                          | 6    |

| <b>2</b>      | Bac    | kgrou          | nd and related work                        | 7    |

|               | 2.1    | Parall         | lel architectures                          | 7    |

|               |        | 2.1.1          | CPU multi-core architecture                | 8    |

|               |        | 2.1.2          | GPU many-core architecture                 | 10   |

|               | 2.2    | Distri         | buted shared memory                        | 13   |

|               |        | 2.2.1          | Structure and Granularity                  | 14   |

|               |        | 2.2.2          | Coherence protocols and Consistency models | 14   |

|               |        | 2.2.3          | Scalability                                | 15   |

|               |        | 2.2.4          | Heterogeneity                              | 16   |

|               |        | 2.2.5          | Data location                              | 16   |

|               |        | 2.2.6          | Replacement strategy                       | 17   |

|               |        | 2.2.7          | Trashing                                   |      |

#### CONTENTS

|          | 2.3                                                       | Dynamic memory on parallel architectures                                                                       | 18                                                                                                                                 |

|----------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

|          | 2.4                                                       | Heterogeneous frameworks memory systems                                                                        | 19                                                                                                                                 |

|          | 2.5                                                       | GAMA framework                                                                                                 | 20                                                                                                                                 |

| 3        | Pro                                                       | blem Statement and Thesis                                                                                      | 22                                                                                                                                 |

|          | 3.1                                                       | Problem                                                                                                        | 22                                                                                                                                 |

|          | 3.2                                                       | Thesis                                                                                                         | 24                                                                                                                                 |

| 4        | $\mathbf{Des}$                                            | gn and Implementation                                                                                          | 26                                                                                                                                 |

|          | 4.1                                                       | Programming and memory model                                                                                   | 26                                                                                                                                 |

|          | 4.2                                                       | Distributed shared memory system                                                                               | 29                                                                                                                                 |

|          |                                                           | 4.2.1 Conceptual model                                                                                         | 29                                                                                                                                 |

|          |                                                           | 4.2.2 Implementation $\ldots$ | 32                                                                                                                                 |

|          | 4.3                                                       | Dynamic memory manager                                                                                         | 36                                                                                                                                 |

|          |                                                           | 4.3.1 Conceptual model                                                                                         | 36                                                                                                                                 |

|          |                                                           | 4.3.2 Implementation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                   | 38                                                                                                                                 |

|          |                                                           |                                                                                                                |                                                                                                                                    |

| <b>5</b> | Vali                                                      | dation                                                                                                         | 43                                                                                                                                 |

| 5        | <b>Val</b> i<br>5.1                                       |                                                                                                                | <b>43</b><br>43                                                                                                                    |

| 5        |                                                           | Experimental setup                                                                                             |                                                                                                                                    |

| 5        | 5.1                                                       | Experimental setup                                                                                             | 43                                                                                                                                 |

| 5        | 5.1                                                       | Experimental setupCase studies5.2.1SAXPY                                                                       | 43<br>44                                                                                                                           |

| 5        | 5.1                                                       | Experimental setup                                                                                             | 43<br>44<br>45                                                                                                                     |

| 5        | 5.1                                                       | Experimental setup                                                                                             | 43<br>44<br>45<br>45                                                                                                               |

| 5        | 5.1<br>5.2                                                | Experimental setup                                                                                             | 43<br>44<br>45<br>45<br>46                                                                                                         |

| 5        | 5.1<br>5.2                                                | Experimental setup                                                                                             | 43<br>44<br>45<br>45<br>46<br>48                                                                                                   |

| 5        | 5.1<br>5.2                                                | Experimental setup                                                                                             | 43<br>44<br>45<br>45<br>46<br>48<br>48                                                                                             |

| 5        | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>             | Experimental setup                                                                                             | 43<br>44<br>45<br>45<br>46<br>48<br>48<br>53                                                                                       |

|          | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>             | Experimental setup                                                                                             | <ul> <li>43</li> <li>44</li> <li>45</li> <li>45</li> <li>46</li> <li>48</li> <li>48</li> <li>53</li> <li>55</li> </ul>             |

|          | <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>Con</li></ul> | Experimental setup                                                                                             | <ul> <li>43</li> <li>44</li> <li>45</li> <li>45</li> <li>46</li> <li>48</li> <li>48</li> <li>53</li> <li>55</li> <li>56</li> </ul> |

# List of Figures

| 2.1 | NUMA architecture in a four multi-core processor topology. Each                                           |    |

|-----|-----------------------------------------------------------------------------------------------------------|----|

|     | processor package has a dedicated channel to its local memory and                                         |    |

|     | communicates with other CPUs through QPI/HT to access non                                                 |    |

|     | local memory                                                                                              | 10 |

| 2.2 | Nvidia Fermi GF100/GF110 architecture. Chip diagram on the                                                |    |

|     | left and SM diagram on the right. (Source Nvidia)                                                         | 12 |

| 2.3 | Intuitive definitions of memory coherence. The arrows point from                                          |    |

|     | stricter to weaker consistencies (Remastered version of original in                                       |    |

|     | [29])                                                                                                     | 15 |

| 4.1 | Simple example on how to execute a kernel in a single CUDA GPU                                            | 27 |

| 4.2 | Simple example on how to execute a job in $GAMA$ regardless of                                            |    |

|     | the number of accelerators $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 28 |

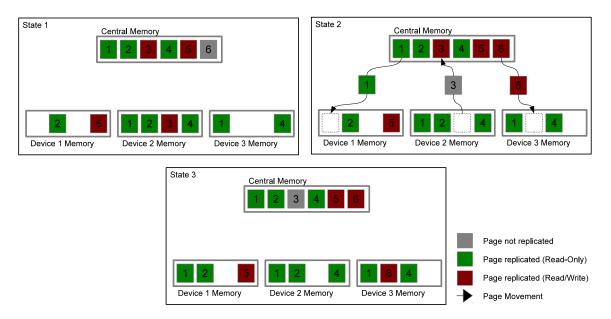

| 4.3 | Diagram of the DSM mechanism of data replication between cen-                                             |    |

|     | tral memory and all the computing devices. The diagram shows                                              |    |

|     | the Device 1 receiving a Read-Only page from central memory; De-                                          |    |

|     | vice 2 returning a Read/Write page to central memory; and Device                                          |    |

|     | 3 receiving a Read/Write page from central memory. $\ldots$                                               | 30 |

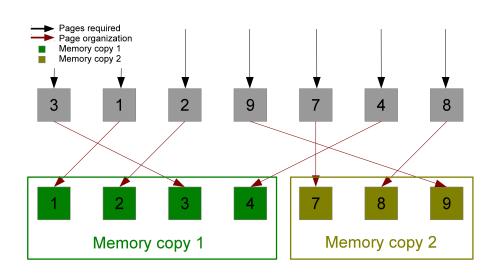

| 4.4 | Diagram of the of a coalescing process of seven pages into two                                            |    |

|     | memory data movement operations $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                        | 34 |

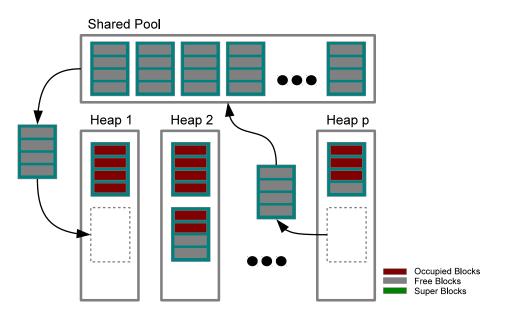

| 4.5 | Diagram of the memory allocator showing one heap returning a                                              |    |

|     | free super-block to the shared pool and another heap fetching a                                           |    |

|     | new super-block from the shared pool                                                                      | 37 |

#### LIST OF FIGURES

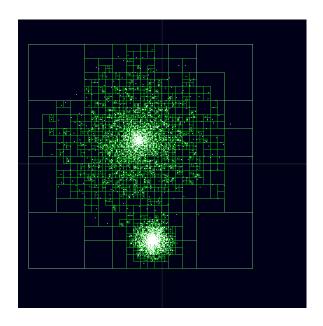

| 5.1  | Complete Barnes-Hut tree decomposition of a distribution of 5000                                                           |    |

|------|----------------------------------------------------------------------------------------------------------------------------|----|

|      | particles in 2D space (source Wikimedia).                                                                                  | 47 |

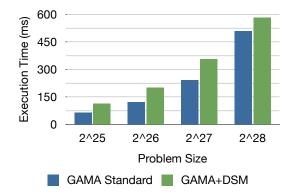

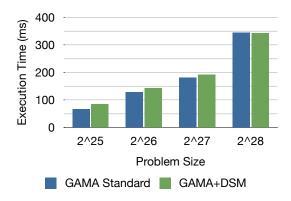

| 5.2  | SAXPY algorithm results running on a single CPU/single GPU                                                                 |    |

|      | configuration, with and without DSM for for different problem                                                              |    |

|      | sizes (from $2^{25}$ to $2^{28}$ elements) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                | 49 |

| 5.3  | SAXPY algorithm results running on a single CPU/two GPU con-                                                               |    |

|      | figuration, with and without DSM for for different problem sizes                                                           |    |

|      | (from $2^{25}$ to $2^{28}$ elements) $\ldots \ldots \ldots$ | 49 |

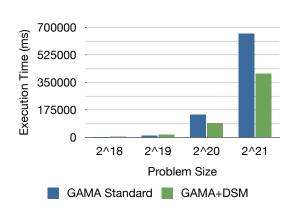

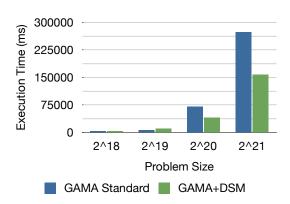

| 5.4  | N-Body (all-pairs) algorithm results running on a single $CPU/single$                                                      |    |

|      | GPU configuration, with and without DSM for for different prob-                                                            |    |

|      | lem sizes (from $2^{17}$ to $2^{20}$ bodies) $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                  | 51 |

| 5.5  | N-Body (all-pairs) algorithm results running on a single $\mathrm{CPU}/\mathrm{two}$                                       |    |

|      | GPU configuration, with and without DSM for for different prob-                                                            |    |

|      | lem sizes (from $2^{17}$ to $2^{20}$ bodies) $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                  | 51 |

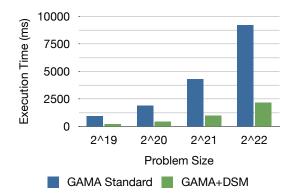

| 5.6  | N-Body (Barnes-Hut) algorithm results running on a single $CPU/single$                                                     | е  |

|      | GPU configuration, with and without DSM for for different prob-                                                            |    |

|      | lem sizes (from $2^{19}$ to $2^{22}$ bodies) $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                  | 52 |

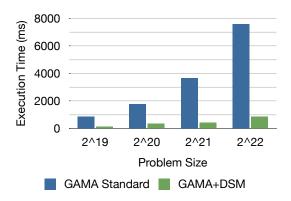

| 5.7  | N-Body (Barnes-Hut) algorithm results running on a single $\mathrm{CPU}/\mathrm{two}$                                      |    |

|      | GPU configuration, with and without DSM for for different prob-                                                            |    |

|      | lem sizes (from $2^{19}$ to $2^{22}$ bodies) $\ldots$                                                                      | 52 |

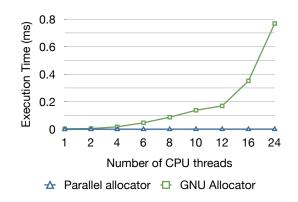

| 5.8  | Scalability results of the proposed memory allocator and the GNU                                                           |    |

|      | malloc                                                                                                                     | 54 |

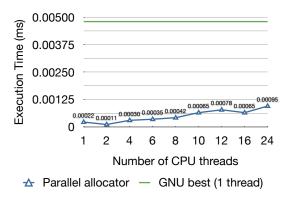

| 5.9  | Scalability results for the proposed memory allocator vs the best                                                          |    |

|      | result achieved with the GNU allocator                                                                                     | 54 |

| 5.10 | Scalability results for the proposed memory allocator when using                                                           |    |

|      | GPUs together with CPU                                                                                                     | 55 |

# List of Tables

| 4.1 | Low level memory API                                                          | 29 |

|-----|-------------------------------------------------------------------------------|----|

| 5.1 | Test machine details                                                          | 44 |

| 5.2 | Test machine's processors details                                             | 44 |

| 5.3 | Speed up of all algorithms when using the DSM vs not using,                   |    |

|     | for the different accelerators configurations. The speedups were              |    |

|     | calculated using the biggest problem size for each algorithm, i.e.            |    |

|     | $2^{28}$ , $2^{21}$ and $2^{22}$ for the SAXPY, N-Body (All-Pairs) and N-Body |    |

|     | (Barnes-Hut) respectively                                                     | 53 |

|     |                                                                               |    |

# Nomenclatur

Cg

CMP

CUDA

DMA

DSM

DSP

FPGA

GAMA

$\operatorname{GCN}$

|                                                      | GLSL   | OpenGL Shading Language                                                |

|------------------------------------------------------|--------|------------------------------------------------------------------------|

|                                                      | HT     | HyperTransport                                                         |

|                                                      | ILP    | Instruction Level Parallelism                                          |

| nenclature                                           | IXP    | Intel family of network processors<br>based on ARM micro-architectures |

|                                                      | MIMD   | Multiple Instruction Multiple Data                                     |

| C for Graphics                                       | NUMA   | Non-Uniform Memory Access                                              |

| Chip Multi-Processors                                | OpenCL | Open Computing Language                                                |

| Compute Unified Device Architec-<br>ture             | QPI    | Quick Path Interconnect                                                |

| Direct Memory Access                                 | SIMD   | Single Instruction Multiple Data                                       |

| Distributed Shared Memory                            | SIMT   | Single Instruction Multiple Thread                                     |

| Digital Signal Processor                             | SMP    | Symmetric multiprocessing                                              |

| Field-Programmable Gate Array                        | SMT    | Simultaneous Multi-Thread                                              |

| GPU And Multicore Aware hetero-<br>geneous framework | TBB    | Thread Building Blocks                                                 |

| AMD's Graphics Core Next GPU architecture            | VLIW   | Very Long Instruction Word                                             |

| ٠ |   |

|---|---|

| 1 | Х |

# Chapter 1

# Introduction

Discontent is the first necessity of progress.

- Thomas A. Edison

Graphics processors (GPUs) were developed to accelerate the creation and manipulation of computer graphics. With the increasing popularity of video games these processors became quite common and powerful, enclosing great computation capability[28]. Recent architecture improvements on the pipeline programability and the introduction of general purpose programming languages like CUDA[30] (Compute Unified Device Architecture) and OpenCL[37] (Open Computing Language), made the GPU a popular processor in a vast array of areas varying from scientific simulation on high end super computer clusters to simple video decoding on common desktop computers.

The CPU (Central Processing Unit) was designed with a more generalist purpose in mind and was oriented to the execution of sequential code. For many years the strategy for improving CPU performance was based on increasing chip clock rates, but due to physical limitations, that is no longer a viable solution[38]. With this limitation and Moore's law[27] still in effect, the alternative was to increase the number of processing cores in a single die. This is a dramatic change in CPU architecture since one can no longer expect to see performance improving in sequential code by simply upgrading the CPU, the algorithms have to be rethought and recoded in order to take advantage of the new parallel nature of the CPU.

With the new parallel orientation of the CPU and performance scalability no longer being transparent to the programmer, the algorithms must explicitly explore parallelism in order to take advantage of the new CPU parallel architectures. This presents an unique opportunity to broaden horizons and explore other parallel processors to implement the new algorithms. The GPU is an excellent candidate because, not only it is almost ubiquitous in modern consumer computers, but it also encloses great computational potential, with a peak arithmetic performance that far exceeds its CPU counterpart. Many state of the art super computers are also equipped with gpus as seen on the top500<sup>1</sup> list (June 2012).

However, one should not focus on which processor to use (CPU or GPU) but on how to use both simultaneously and fully take advantage of the machine potential. This is not always an easy task since, despite the new found parallel nature of modern CPUs, GPUs and CPUs are still very different (architectures, instruction sets, memory hierarchies, programming languages, etc.) and developing for these systems can be very challenging. To improve productivity when programing for heterogeneous CPUs+GPUs systems, new development tools are a fundamental requirement.

### 1.1 Distributed shared memory systems

In parallel programming two main programming models exist – shared memory and message passing. The shared memory programming model is the more straightforward of the two because it is a natural extension of the single processor programing model: the data resides in a memory pool that can be directly accessed by any thread at any given time. This model is generally common on tightly coupled processor machines, where all processor chips and processor cores share a common interface to the memory. This shared interface to the memory is however a serialization point and thus a scalability bottleneck.

In distributed memory systems, each processor (or group of processors) has its private memory and is connected to others processors by a high speed (low

<sup>&</sup>lt;sup>1</sup>Top500 http://www.top500.org/lists/2012/06

latency high bandwidth) network. These systems do not have the same scalability problems as a shared-memory machine, since there are dedicated interfaces to memory and with a well designed interconnection network topology between processors or group of processors, this type of system can scale virtually indefinitely. The tradeoff for scalability is the increase in programming complexity. These systems generally support a message passing programing model where each thread can access data in its private memory directly, but has to request nonlocal data explicitly before accessing it. This requires the programmer to have a deeper knowledge of his program data requirements and to design the algorithms to minimise remote data accesses.

Since discrete GPUs have dedicated memory, general purpose computing languages such as CUDA or OpenCL require the programmer to explicitly move data between the (CPU) host memory and the (GPU) device dedicated memory, similarly to distributed memory systems. Recent improvements on GPU architectures and programming languages allow the programmer to access host memory from the GPU directly, so explicitly memory movements are no longer compulsory. This eases the programming effort, but sacrifies scalability because, much like shared memory system, serializes memory accesses with other devices on the machine. So in an heterogeneous system with GPUs, we are faced with the same problem as with a multi processor system – programming simplicity vs scalability – with the added complexity of the asymmetric nature of host memory and device memory, that have different sizes, bandwidths, clock frequencies, etc.

A way to circumvent the additional programming complexity of distributed memory systems is to use a shared memory abstraction layer on top of the message passing system – distributed shared memory (DSM) system. With the DSM, the physical disjoint memory spaces can be addressed as a single, logically shared, memory space. A software distributed shared memory system can be interpreted as an extension to the underlying operating system virtual memory. Similarly to the operating system virtual memory mechanism, the software DSM is completely transparent to the programmer.

### **1.2** Dynamic memory allocators

Another important step in bringing a familiar multi-core homogeneous environment to an heterogeneous CPU+GPU computing system is to enable the use of dynamic memory on these heterogenous systems as in a shared memory environment. Dynamic memory allocators are used in a variety of applications. The inability to use dynamic memory, poses a barrier to porting existing shared memory programs (that rely on dynamic memory) to heterogeneous systems.

Dynamic memory is already possible on accelerators like modern GPUs, but the data allocated dynamically by GPU threads are only accessible by those GPU's threads. The data is not visible by other GPUs' and CPUs' threads. The same happens with dynamically allocated memory by CPU threads. An heterogeneous dynamic memory allocator on an heterogeneous system should behave as a traditional memory allocator on a traditional system, all dynamic memory allocated by the system's threads should be accessible by any other thread.

## **1.3** Motivation and goals

The new found general purpose side of the GPU, started a new era in software development. This opened a lot of possibilities, but also introduced software developers to new challenges – new architectures, programming models, programming languages, etc. New parallel CPU architectures already put a hard strain on programing complexity and the introduction of GPU many-core architectures only increased the problem. The use of both CPU and GPU simultaneously only adds to the already existing intrinsic difficulties of parallel programming of both families of processors with disjoint memory spaces and different memory models, with different consistency models and synchronization primitives.

This document proposes that the programming burden of heterogenous platforms can be eased by delegating data management to a runtime memory system. This system should unify the disjoint memory address spaces and expose to the programmer a single memory model. This frees the programmer from having to explicitly deal with data transfers and use architecture specific data management primitives. By charging the memory runtime system with these tasks, also enables the opportunity of the memory manager to work with the runtime scheduler and dynamically optimize data transfers. The heterogeneous memory subsystem should not only improve programing productivity but also improve code portability with the minimum negative impact in performance.

The memory runtime system should also allow the programmer to reserve and free memory dynamically. Not only traditional multi-core systems allow the use of dynamic memory but several algorithms and applications rely on the use of dynamic memory. The necessity of enabling the use of dynamic memory is further confirmed by the recent efforts of bringing dynamic memory to GPUs [17][30]. Constructing a familiar and flexible memory environment on heterogeneous systems must include a dynamic memory manager.

The proposed heterogeneous runtime memory system allows: (1) The programmer to be data location agnostic – no explicit data movement requirement by the programmer or even be aware of whether the accelerators have dedicated memory or not. (2) Improve code portability – the systems exposes a unified architecture independent memory model and memory operations. (3) Runtime data management optimizations – by optimizing data movement at runtime, the system can adapt to the system characteristics at real time. (4) The use of dynamic memory – any thread on a system can allocate and free memory visible by the whole system, independently of the device where the threads reside. The dynamic memory manager also has the same four characteristics that other modern memory allocators have: fast alloc/free operations, thread scalability, false share avoidance and low fragmentation.

The focus of this work is set on CPU(s) and GPU(s) heterogeneous systems, but the model should be flexible enough to suport other systems with aditional classes of acelarators, like FPGAs, DSPs, etc. The heterogeneous memory runtime system was implemented and tested on the *GPU And Multicore Aware* (*GAMA*) heterogeneous framework.

### **1.4** Document organization

Chapter 1 gives a brief introduction to heterogenous programing, the problems software developers face and possible solutions. Chapter 2 presents an overview of the modern CPU multi-core architectures and GPU many-core architectures; and gives some background on existing programing models, distributed shared memory systems, parallel memory allocators and heterogeneous frameworks. Chapter 3 specifies in detail the problem and the proposed approach on how to tackle it. Chapter 4 details the proposed heterogeneous runtime memory system – the memory model, heterogeneous distributed shared memory and heterogeneous parallel memory allocator. Chapter 5 contais the experimental validation of the proposed memory system on the *GAMA* heterogeneous framework. Chapter 6 gives a final overview on the project, summarizing and criticizing the project and commenting on future work.

# Chapter 2

# Background and related work

If I have seen further it is by standing on ye sholders of Giants.

- Isaac Newton

Heterogeneous systems can be very diversified and include a great variety of accelerators. The focus of this project however resides solely on CPUs and GPUs only heterogeneous systems. In this chapter some background is given on the multi-core CPU architectures and many-core GPU architectures. The history and characteristics of software distributed memory systems and parallel memory allocators is described as well. The chapter ends with an overview and critical analysis of existing heterogeneous frameworks' memory systems.

### 2.1 Parallel architectures

Different problems and objectives spawned several types of processor architectures. Given the broad nature of problems that processors need to target, two general approaches are taken – producing an all-purpose processor capable of addressing all problem domains by sacrificing some performance over flexibility; or producing domain specific processors, capable of tackling only a set of problems but being very efficient at it. Modern machines are normally equipped with a general purpose processor (CPU) and one or more domain specific processors (accelerators). One of the most popular and ubiquitous accelerator is the one designed to tackle real time computer graphics (GPU).

#### 2.1.1 CPU multi-core architecture

For many years the center of a computing device was a single-core architecture processor, responsible for executing instructions sequentially one at a time. Moore's law predicted that the number of transistors in an integrated circuit could be doubled inexpensively every two years [27] and that dictated the evolution of the CPU, resulting in higher clock speeds. However, constraints in the current processor manufacturing technology made this evolution path unsustainable. Due to power consumption and heat dissipation restraints [38], the CPU clock rates would eventually stagnate and alternatives were explored to complement (and eventually replace) the increase in clock rates as the main improvement on newer CPUs.

With power limitations and Moore's Law still in effect manufacturers used the extra transistors to increase the number of functional units by placing redundant arithmetic and control units in a single die. In order to explore these units new techniques were explored to extract parallelism at the instruction level (ILP - Instruction Level Parallelism). Depending on manufacturer and processor class different sets of ILP techniques are implemented – Pipelining, Very Long Instruction Word (VLIW), Single Instruction Multiple Data (SIMD), etc.

The ILP techniques have the advantage of being used with little to no change in the sequential source code written for traditional sequential processors, since the processor will explore parallelism automatically and new parallel instructions will be introduced in the program by the compiler simply by activating compilation options. But the slow increase on main memory clock speeds when compared to the CPU [40], made memory accesses increasingly costly and optimizations introduced by ILP techniques produce poor results even with larger and faster caches.

The solution to this problem could no longer pass through transparent parallelism introduced by ILP techniques but through explicit parallelism. By dividing an operation into several parallel tasks (computational threads) the processor could hide a thread's memory access latencies by executing instructions of another thread until the data of the previous thread is available, thus keeping functional units occupied – this technique is called Simultaneous Multi-Thread (SMT). SMT efficiently helps hide memory accesses latencies but also introduces complexity for the programmer since parallelism must be expressed in the algorithm/code explicitly.

One way of increasing performance is to multiply the number of computational units. This can be done on a single computational node by increasing the number of CPUs per node – this technique is know as Symmetric Multiprocessor (SMP). SMP is an old technique used when the technology does not mach the computational requirements of the task. Chip Multiprocessors (CMP) derive directly from SMP but places the processors (cores) in a single die (processor package) – multi-core architecture. CMP improves on SMP since communications between processor cores are done inside the chip, which is faster, more energy efficient and through the use of shared caches, it's easier to keep the memory coherent. This shift to paralel architectures stimulated the creation of new tools like OpenMP[11], TBB[32] and Cilk[8] to help the software developers better explore the processor potencial.

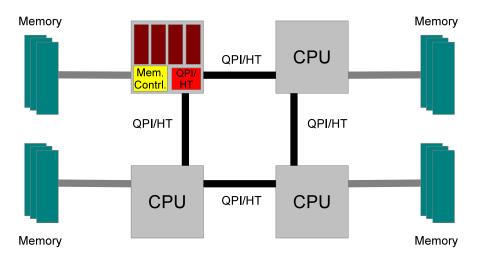

With the new tendency of placing multiple cores/processors in a single computational node the traditional communication mechanism between processors and main memory had to be rethought. Since the communication channel to the memory is shared by all cores/processors, by increasing the number of cores/processors in a node, the number of bus conflicts also increases. With few cores or processors this problem is neglectable, but with the new tendency in increasing the number of cores per processor, this communication model is unsustainable. The alternative comes in the form of NUMA (Non-Uniform Memory Access) architectures. In a NUMA architecture, groups of processors/cores have a local memory and a dedicated communication channel to it. In order for a processor to access non local memory addresses it has to request the data from other processor's local memory.

The communication between processors/cores in the case of Intel processors is done using QPI[19] (Quick Path Interconnect) or HT[18] (Hyper Transport) in the case of AMD. Depending on the processor communication network topology,

a processor might not have a direct communication channel between all the other processors and a remote memory access might have to send its request through several processors before it reaches the desired one. This adds latency to data requests since the farther away (request wise) the data is, the slowest it is to reach. NUMA architecture solves the scalability problem but introduces a new one: memory access times are not uniform anymore, local memory access times are faster than a non local access. A diagram of a NUMA architecture system with four processors can be viewed in figure 2.1.

Figure 2.1: NUMA architecture in a four multi-core processor topology. Each processor package has a dedicated channel to its local memory and communicates with other CPUs through QPI/HT to access non local memory.

#### 2.1.2 GPU many-core architecture

CPU architectures target a variety of different problems and so evolved with this objective in mind, spawning very versatile architectures. More specific domains produced different processors with very specific orientation architectures. One of these domains was computer graphics and the class of processors produced for this specific domain was the GPU.

GPUs are optimized for throughput instead of speed. A GPU architecture sacrifices complex control logic (instruction prefetching, branching prediction, etc.) and large caches (to hide latency) in order to obtain a simpler computing core using less transistors, allowing more cores to be packed in a single die. By having lower clock rates, it reduces the energy consumption of the chip, making heat dissipation easier, which in turn allows more cores per chip.

This type of architecture appeared to solve the realtime rasterization problem. Since rasterization is an intrinsically parallel task, the GPU architecture had (and still has) the same parallel nature. From early on, these types of processors enclosure great computational capability, but they were used exclusively for computer graphics acceleration. It wasn't until the late 90's that the first GPUs with programable pipelines appeared. Initial attempts to use GPUs as general purpose used languages borrowed from computer graphics such as Cg[25] (C for Graphics) or GLSL[34] (OpenGL Shading Language). But with still low programmable capacity and no floating-point arithmetic capability, the use of the GPU for general purpose computing was limited.

Floating point arithmetic capability emerged in these processors in the form of floating-point color buffers in 2002[28]. The purpose of this was to produce richer and more complex computer graphics but it opened the door for general purpose computing on the GPU. Market competitiveness and demand for better graphics stimulated further improvements and modern GPU architectures introduced more programability on the previously fixed pipeline and improved floating point support each time closer to IEEE754 specification.

The introduction of Nvidia's Compute Unified Device Architecture (CUDA)[23] marked an important step in GPGPU (General Purpose GPU), introducing a general purpose language for GPU programming (C for CUDA), and replacing industry specific terms like shaders, texels, pixels, etc. with more conventional terms like cores, threads, cache, etc. Other GPGPU programming languages emerged like the Khronos Group OpenCL[37] or Microsoft's DirectCompute[9].

Nvidia Fermi's architecture<sup>[41]</sup> (and it's recent iteration, Kepler's architecture) is composed of simple computing cores called Stream Processors (SPs) or CUDA cores. Each CUDA core is a pipelined scalar processor capable of single precision integer or floating point operations. Double precision arithmetic is achieved pairing two single precision cores. The SPs are grouped into Stream Multi-Processors (SMs). High end versions of Nvidia Fermi processors have 32 SPs per SM. Like the SPs, the number of SMs per chip varies, generally high end versions have more SMs than lower versions of Fermi processors (GF110 GeForce GTX 580 has 16 SMs). Each SM has load/store units (16 on GF110) and special functional units (4 on GF110) that allow transcendental operations. An individual SM also has register memory and fast memory. This fast memory is used as L1 cache and as an explicitly addressable memory (referred to as shared memory). This memory is shared by all CUDA cores within an SM. The chip also has L2 cache, that is shared by all SMs on the chip and serves as the interface to the chip outside memory be it device or host memory. The details are illustrated in Figure 2.2

Figure 2.2: Nvidia Fermi GF100/GF110 architecture. Chip diagram on the left and SM diagram on the right. (Source Nvidia)

The execution model of each SM can be viewed as a 32-wide SIMD processor. The threads are grouped into blocks (thread block) and the blocks are assigned to SMs for execution. The execution model is not truly SIMD, since SMs deal with conditions differently than an SIMD processor would. A SM does allow divergence between threads (but with a considerable penalty). The model is called SIMT (Single Instruction Multiple Thread). Threads can only be synchronized with other threads from the same thread block, even if two blocks are assigned to the same SM. However, CUDA has cache L2 atomic operations that can be used for synchronization between threads of different blocks.

# 2.2 Distributed shared memory

There are several design considerations that have to be taken into account when developing and implementing a distributed shared memory system [29] [12] [33]. These considerations can be divided into the following groups:

- Structure and Granularity Structure refers to the layout of the data in memory (linear array of words, data objects, language types, etc.) and granularity refers to the size of the unit of sharing (byte, word, page, etc.).

- Coherence protocols and Consistency models When there is data replication, a coherence protocol guarantees that all nodes view all memory positions in the same way. A consistency model determines the conditions under which memory updates will be propagated through the system.

- Scalability Distributed Shared Memory systems can have their scalability limited by central bottlenecks (e.g sharing the same communication bus) and global operations (e.g. synchronization operations).

- Heterogeneity DSMs over heterogeneous systems are intrinsically more complex. An heterogeneous DSM system might include subtle differences (e.g. different memory size or cache levels) to more technical challenging differences, like different processor architectures, instruction set architectures (ISA), memory hierarchies, etc.

- **Data location** When a thread requests data that is not in its local memory, the DSM must support mechanisms to find and retrieve the requested data.

- **Replacement strategy** When a cache is full, replacement strategies are required to decide which cache lines should be replaced to free up space for the new incoming data.

• **Trashing** – Trashing happens when data that cannot be replicated is needed by more than one device at a time or the data is being often written by one device and read by other.

#### 2.2.1 Structure and Granularity

Both these aspects of DSMs are closely related. Most DSMs do not structure their memory[29] and use a simple memory pool. This way the DSM is faster (since it introduces less computational overhead) and more flexible (since it has a lower level view of the memory). Programs that use shared memory typically explore data locality, i.e. a thread is likely to address spatially close address spaces in the near future, so the use of bigger sharing units might reduce communication overhead. On the other hand, a large "page" increases the probability that more than one thread might need the same page at the same time and so increases the probability of false sharing. Having the memory structured can help reduce these problems but also introduces complexity. There isn't a common page size on DSMs with unstructured memories, implementations have the page sizes varying from 16Bytes (Dash[20]) to 8KBytes (Mermaid[43]). Examples of DSMs with structured memories are Munin[6] which structures memory into objects (integers, arrays, structures, etc.) and Linda[1] that uses a database like type of structure.

#### 2.2.2 Coherence protocols and Consistency models

"A memory consistency model is the logical sum of the ordering of events in each processor and the coherence protocol" [35]. There are two kinds of coherence protocols: write-invalidate and write-update[36]. 1) Write-invalidate – after a piece of data is written locally, all copies of the same data on other nodes are marked as invalid; 2) Write-update – after a piece of data is written locally, all other copies of the same data are updated before any access to it is allowed. The write-invalidate protocol allows data writes to be made locally (local update) but data accesses by other nodes to the same data will always result in a cache miss. The write-update protocol on the other hand will not produce cache misses but each data write will always be a global update. Due to the cost of communication, most DSMs implement a write-invalidate coherence protocol. The most natural

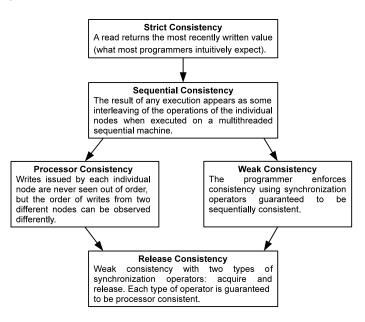

and intuitive model is the Strict consistency model in which the programmer can expect the most recently written value after a read operation. However, such a strict model can have a severe impact in performance. Because of performance considerations distributed shared memory systems implement more relaxed memory consistency models. Figure 2.3 represents several consistency models in an hierarchical way.

Figure 2.3: Intuitive definitions of memory coherence. The arrows point from stricter to weaker consistencies (Remastered version of original in [29])

#### 2.2.3 Scalability

Most work about software DSMs and implementations rely on outdated architectures (single-core processors and a single shared bus across processor packages). Modern architectures have dedicated communication channels for different processors with integrated memory controllers (NUMA architecture) in a structure where each processor has its own private bus for its "local memory". This reduces the scalability bottleneck but introduces complexity since memory accesses latency times are no longer constant. Moreover, despite each GPU device having its local memory, it's not possible to directly access memory of a device from a different one, i.e, all communication between devices must pass through main memory. Depending on the architecture, a GPU device might have to share a memory communication channel with some or all other GPU devices.

#### 2.2.4 Heterogeneity

Distributed memory systems over heterogeneous systems are intrinsically more complex than homogeneous ones. A heterogeneous system might include subtle differences (e.g. different memory size or cache levels) to more technical challenging differences, like different processor architectures, instruction set architectures (ISA), memory hierarchies, etc. Some of these problems do not apply to CPU-GPU computing. Using a common combination of CUDA GPUs and IA-32 CPUs as an example, the CPU-GPU heterogenous system share the same programing language (with small differences), same data representation (e. g. endianness), etc. But other heterogeneous problems are still relevant: (1) Disjoint address memory spaces; (2) Different ISAs and therefore different execution binaries; (3) Computational capability, for example, limited support for conditional branching and no support for recursion on the GPU; (4) Different Memory hierarchy, with the introduction of CPU alien concepts such as explicit cache (shared memory) or local memory; (5) Different memory interfaces with unique capabilities to lower access latencies such as memory coalescing. There aren't many implementations of DSMs that support heterogeneous environments and most do not support modern heterogeneous architectures like multicore and many-core heterogeneous machines.

#### 2.2.5 Data location

When a thread requests data that is not in its local memory, the DSM must support mechanisms to find and retrieve the requested data. Systems where there is no data migration or replication this can be trivially done, since data resides only and always in the same centralized location. However, if data is allowed to migrate and there is replication, the solution its not so easily achieved and several approaches to the problem can be considered. These solutions can be divided into to two groups[21]: Centralized approaches and Distributed manager approaches. The Centralized approaches are simpler, but can overload the node with data accesses and slow down the entire system. Distributed approaches scale better but are significantly more complex.

#### 2.2.6 Replacement strategy

Replacement strategies used in most DSMs are similar to the ones used in caching mechanisms. There are several replacement strategies but the more common are the least recently used (LRU) (or some approximation) or random replacement (RR). Distributed shared memory systems can also have additional information for each page that classifies them by type (e.g. shared, read-only, private, etc.) and in turn are used in the replacement policy. A distributed caching system would give evict priority to a shared read-only page over a privately owned page, since the later would have to be written back in main memory in opposition to a shared read-only page that could simply be erased. These page types cannot be the only factor when deciding which page to replace, because a read-only page, despite being easy to replace, could be accessed several times by that thread and not having it in cache means that it needs to be fetched from main memory.

#### 2.2.7 Trashing

Trashing is a common problem among DSMs and strategies to reduce trashing generally revolve around some form of data replication. Munin allows the programmer to associate types to the shared data (private, migratory, read-only, etc.). But not only is this only possible on a DSM with a structured memory but also requires the programmer to specify the type of data (it's not a transparent process). Mirage[15] uses a dynamically tuned parameter on the coherence protocol that determines the minimum amount of time a page stays at a node ( $\Delta$ ). When a node writes on a shared page, that page remains writable on that node for a minimum of  $\Delta$  time. Mirage dynamically analyses access patterns to tune the  $\Delta$  value.

## 2.3 Dynamic memory on parallel architectures

One of the recurring concerns when dealing with parallel architectures is scalability and traditional memory allocators, designed to work on sequential machines, tend to under perform and scale bad on parallel architectures. Modern memory allocators were designed to address this problem. Several work exists on parallel memory allocators like Hoard[7], Ptmalloc[42] and Michael's allocator[26]. All these memory allocators use different lock or almost lock free algorithms to deal with the scalability problem.

Hoard[7] uses multiple processor heaps in addition to a global heap. Each heap contains zero or more superblocks. Each superblock contains one or more blocks of the same size. Statistics are maintained individually for each superblock as well as collectively for the superblocks of each heap. When a processor heap is found to have too much available space, one of its superblocks is moved to the global heap. When a thread finds that its processor heap does not have available blocks of the desired size, it checks if any superblocks of the desired size are available in the global heap. Threads use their thread ids to decide which processor heap to use for malloc. For free, a thread must return the block to its original superblock and update the fullness statistics for the superblock as well as the heap that owns it. Typically, malloc and free require one and two lock acquisitions, respectively.

Michael's allocator<sup>[26]</sup> recicles some of Hoard's high level structures (heaps, blocks and superblocks), reorganizes them slightly and replaces any locking mechanism with atomic operations (atomic CAS). This makes the allocator completely lock free. Each heap contains superblocks and each superblock is divided into same size blocks. Superblocks are classified and grouped into different size classes depending on their block size and each size class contains several processor heaps. XMalloc<sup>[17]</sup> ports the models introduced by both CPU exclusive Hoard and Michael's allocators to the GPU. XMalloc is a GPU parallel memory allocator implemented in CUDA. It follows a similar data structure to Hoard's superblocks and borrows the atomic CAS based lock-free idea from Michael's allocator.

### 2.4 Heterogeneous frameworks memory systems

With the popularity of the GPU for general purpose computing increasing recently also did the interest in developing tools to aid developers to use not only the GPU but both GPU and CPU. In an effort to ease the software development process in heterogeneous architectures, some frameworks arose (including the GAMA framework). These heterogeneous frameworks have different approaches and propose different programming and memory models. Of the several existing heterogeneous frameworks three stand out by their different approaches to data management: Harmony[13], Merge[22] and StarPU[4].

Harmony is a runtime system that offers a programing and execution model for heterogeneous systems. The objective is to simplify the programing of auxiliary accelerators like GPUs, FPGAs (Field-Programmable Gate Array) and Intel IXPs<sup>1</sup> without sacrificing performance. The programmer writes a collection of compute kernels that are dynamically assigned to available computing resources. The execution model is similar to out-of-order scheduling and execution of instructions on a superscalar processor – kernels are scheduled for execution depending on availability of data (data dependencies) and resources (accelerators). Each kernel only computes data on its own address space, which means that the same kernel cannot run simultaneously on different processors.

Merge is a framework for multi-core heterogeneous systems. The framework offers a programing language (Merge high level language) that uses the mapreduce patterns. The map-reduce enables automatic parallelization of the code and allows the framework to create independent work units to be assigned to processor cores. Merge uses EXOCHI [39] to implement the API for the various heterogeneous processors. EXOCHI can also be used by the programmer to extend Merge to others heterogeneous architectures. This framework is one of the most similar to a SMP (Symmetric multiprocessing) system in terms of memory operations, but the drawback is that it needs all the devices to share the same memory pool. This narrows the type of devices it supports and excludes the dedicated GPUs, the most popular accelerators today.

StarPU is a runtime system with dynamic task scheduling. A task is a set

$<sup>^1 \</sup>mathrm{Intel}$  family of network processors based on ARM micro-architectures.

of architecture specific implementations of the same computational kernel. Each task is then assigned to the available heterogeneous processors by the scheduler. StarPU implements a virtual shared memory with a relaxed consistency model with caching capability[3]. This framework is the more complete in terms of data management. It allows the access of data by any device on the system as in a shared memory environment and it moves data and keeps memory consistency automatically[2]. The framework uses the GMAC[16] system to manage data.

The GMAC system has similar characteristics as the proposed DSM – reduced programming effort and improved code portability by freeing the developer from having to deal with data movements explicitly. However, it has some shortcomings: Despite the CPU being able to access any program variable, (1) code running in the GPU cannot access variables hosted in CPU memory and (2) code running in the GPU cannot access variables hosted in other GPUs. Also, it does not support dynamic allocation and deallocation of memory (visible by all computing devices) by code running on GPUs.

### 2.5 GAMA framework

The *GPU And Multicore Aware (GAMA)* framework is a framework designed to extract performance and simplify the coding process of heterogenous computing environments with GPUs and other classes of accelerators. The framework unifies the independent programming, execution, and memory models of the different computing devices into a single one. This not only simplifies the coding process but also makes the source code independent of the underlying hardware, improving both coding productivity and portability. The framework is still in development and currently only supports systems with x86-64 processors and CUDA capable GPUs.

To implementing an algorithm, the programmer has to code at least two methods – the kernel and the dice method. This is identified as a job. The GAMA kernel works in a similar way as a CUDA or OpenCL kernel, it defines which data each thread will manipulate and how that data will be handled. The dice method defines how the data input domain will be divided across the parallel tasks and how many tasks will be generated from the kernel. It is similar to the way we can define the number of threads and the granularity of each thread in OpenMP or the thread organization topology (grid and block sizes) in CUDA, but more flexible.

The framework builds individual binaries from the kernel targeted at the different computing device's architectures in the system and generates tasks from the dicing method. The runtime scheduler then dynamically assigns the tasks to different computing devices and executes the appropriate binary automatically. The programmer can implement an algorithm as a collection of jobs and tasks from different jobs can run in parallel or can be explicitly sequentialized by a synchronization primitive. The primitive guarantees that all tasks from the previous job have finished by the time tasks from the next job start.

# Chapter 3

# **Problem Statement and Thesis**

Simple things should be simple; complex things should be possible.

- Alan Kay

Heterogeneous systems introduced new programming challenges and aggravated existing ones. In this chapter, some of the problems with an asymmetric distributed memory system typical of heterogeneous environments will be presented and analyzed. In the end a solution for these problems is proposed and justified.

### 3.1 Problem

Data management is a significant and difficult problem when programming heterogeneous systems since correct data placement is crucial for achieving fast execution times. When dealing with these kind of systems the programmer is faced with several problems regarding data and memory:

• Explicit data movement – Accelerators have dedicated memory and, since generally the device cannot access host memory and vice versa, the programmer has to explicitly move the data to and from the devices. This requires the programmer to have a deep knowledge of his program data requirements and to explicitly code his algorithm in an effort to accommodate those data requirements with a minimum impact in performance due to memory copy latencies.

- Poor code portability With a specific accelerator comes a specific memory model and set of primitives to manage data movement and synchronization (intra and inter devices). If the program has to be ported to another architecture, the algorithm has to be recoded to incorporate the new architecture specific memory model and primitives.

- No opportunity for runtime optimizations By programming a device directly, the data movement operations are fixed and hardcoded to the program upon compilation. This leaves no room to dynamically "measure" the state of the system and decide the best option regarding data management. With no runtime help, the user is confined to a "trial and error" approach to determine the best way to move data around with the least performance impact. This also poses a potencial problem when adding new devices since it requires the programmer to repeat the "trial and error" process to find the best option on the new system with additional computing devices.

- Use of dynamic memory Regardless of the programming model, accelerator code follows a simple pattern: copy data to the device; execute the device code on the that data; copy data back from device. The use of dynamic memory is generally not included in the model. Recent improvements on GPU architectures and programming models allow the programmer to allocate and free memory inside of the device, but this memory is not accessible by all cores/threads on the device and certainly not by other devices or CPU.

All these problems increase coding complexity and require the programmer to be familiar with the architecture and its primitives. This can have a significant impact in coding time and decrease productivity. This can even be more problematic if the code has to be ported to other architectures, which generally requires the algorithm to be recoded to incorporate the new architecture specific memory models and primitives. Existing heterogeneous frameworks try to tackle some of these problems, but assume an easy and static data division (no data dependencies between devices and no dynamic memory required) or avoid the issue altogether by requiring the use of accelerators that don't have dedicated memory and share the host memory. StarPU stands out as an exception in this regard by acknowledging the importance of data management in code performance and offers automatic data movement and dynamic management of data dependencies. Unfortunately GMAC, StarPU's DSM, does not offer support for remote data access by the GPU threads, nor the use of dynamic memory.

## 3.2 Thesis

We propose a novel software memory system model for heterogeneous parallel machines that (1) unifies the disjoint address spaces of host main memory (CPU address space) and accelerator dedicated memory (GPU address space); and (2) allows the use and allocation of dynamic memory by all devices, i.e. each device can reserve and free memory visible by all devices on the system.

We argue that to simplify the programming effort and improve code portability on heterogeneous computing systems, the use of a distributed shared memory system with suport for dynamic memory is an important step. The heterogeneous memory system also follows a unified, architecture independent memory model. This essentially virtualizes a more familiar shared memory system on top of an asymmetric distributed memory system. The heterogeneous memory system allows:

- The programmer to be data location agnostic No explicit data movement necessary. The runtime memory system will detect memory dependencies and move the data accordingly. The programmer manages and accesses data in the same way as in a shared memory system.

- Better code portability The system unifies the different devices memory models into a single architecture independent memory model. The system also exposes a single set of data management and synchronization operations. The programmer will not have to know or use any of the underlying

architecture specific data management primitives. This allows the code to be ported without any modifications.

- Runtime data management optimizations By delegating the data movement operations to the runtime system, it is possible for the memory system to dynamically optimize data movement for the current system characteristics and coordinate with the runtime scheduler to improve data reutilization and minimize data movement.

- Use of dynamic memory The memory system allows any thread by any device to allocate memory, visible and accessible by any other thread on the system, at any given time. This helps bring the capabilities of heterogeneous systems closer to the ones of a traditional shared memory (CPU only) system.

The heterogeneous dynamic memory allocator follows the same four characteristics as a modern parallel memory allocator:

- Speed An allocation/free operation should perform as fast as a sequential memory allocator. In the case of the heterogeneous memory allocator, these operations should be as fast as the (CPU only) parallel allocator.

- Scalability The memory operations (alloc/free) should scale with the number of processors on the system i.e. the alloc and free operations execution time should remain constant, independently of the number of processors.

- False share avoidance The allocator should avoid the sharing of memory pages in which different processors have data in the same memory page.

- Low Fragmentation Heavy fragmentation can lead to under use of total available free memory and a significant decrease in performance of allocation and free operations.

# Chapter 4

# **Design and Implementation**

Software is not limited by physics, like buildings are. It is limited by imagination, by design, by organization. In short, it is limited by properties of people, not by properties of the world.

- Ralph Johnson

The proposed heterogeneous memory system can be divided into two main components – a DSM and a dynamic memory manager. The DSM maintains a virtual memory pool, shared across all computing devices, and the dynamic memory manager allows the dynamic allocation and deallocation of memory in this pool. In this chapter, the proposed memory and programming model will be presented together with the design of the heterogeneous DSM and memory manager.

# 4.1 Programming and memory model

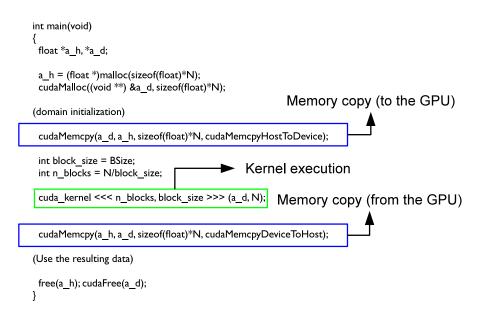

Traditionally when using accelerators, the programmer declares data objects that are associated with a co-processor. The data is then moved to the specific coprocessors and one or more kernels are executed on that data. An example of this model can be viewed in Figure 4.1. The memory space must be allocated in both the host and the device. Then the data is copied to the device, the kernel is executed and after the execution, the data is copied back to the host. If using multiple devices, this process must be repeated for each device.

Figure 4.1: Simple example on how to execute a kernel in a single CUDA GPU

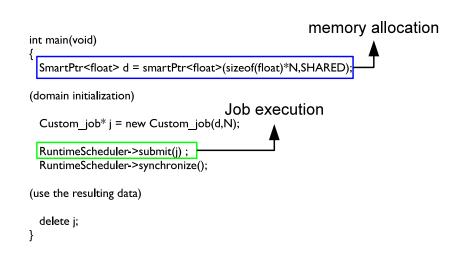

With a DSM there is no need to explicitly request memory on the different devices. Programmers have only to allocate data and run a single kernel (a job in GAMA terminology). The runtime system assigns the processor specific kernels (generated from the user's architecture independent kernel) to the respective devices and manages data transfers automatically. Figure 4.2 shows an example of running a job in the GAMA framework with the DSM system. The programmer only has to allocate the necessary data and execute the job. Since the execution is done asynchronously, the programmer must also use a synchronization barrier if needed.

The system exposes a simple API for allocating/freeing memory – an alloc and dealloc methods (Table 4.1). The programmer only has to specify memory size and the memory properties required – HOST, DEVICE or SHARED. Memory allocated with the HOST property will only be accessible by the host. Memory allocated with the DEVICE property will only be accessible by the computing device that allocated it. Finally, memory allocated with the SHARED property

Figure 4.2: Simple example on how to execute a job in GAMA regardless of the number of accelerators

will be accessible by all computing devices on the system. This distinction can be useful since some data might only be necessary in the current thread/device scope, and specifying this fact explicitly allows the memory runtime system to avoid unnecessary data tracking, improving performance.

When coding the algorithm, aside from the kernel and the dice method required by the *GAMA* framework, the programmer has to specify two additional data methods. These methods allow the memory runtime system to identify the different tasks' data requirements and manage data coherence accordingly. One of the methods identifies the read-only data (ReadOnlyElems(void)) and the other the read/write data (ReadWriteElems(void)) for each thread. These methods must return a list of the elements that will not be modified and the ones that will (respectively). Since the only requirement of the methods is for the output to be a list of elements, the body of the methods (i.e how the list is created) can be as complex as the programmer needs them to be.

The DSM follows a weak consistency model and tasks generated from a job are scheduled arbitrarily. Order between jobs can be enforced by using the synchronization primitive "synchronize()". The programmer can also manage access to shared resources within a job using atomic operations such as "atomicCAS", "atomicAdd" and "atomicSub". The full list and description of all primitives can be consulted in Table 4.1.

| API methods                | Description                                     |  |

|----------------------------|-------------------------------------------------|--|

| alloc(s, mem_type)         | Allocates Memory with size "s" with differ-     |  |

|                            | ent visibilities depending on "mem_type". If    |  |

|                            | "mem_type" is HOST, the memory is only          |  |

|                            | visible by the host. If DEVICE, the mem-        |  |

|                            | ory is only visible by the computing device     |  |

|                            | that allocated it. If SHARED, the memory        |  |

|                            | is visible by all computing devices.            |  |

| dealloc(ptr, mem_type)     | Frees the memory in "ptr" pointer allocated     |  |

|                            | with type "mem_type".                           |  |

| atomicCAS(var, cval, nval) | Atomically tests if the variable "var" has the  |  |

|                            | "cval" value. If successful, "var" is updated   |  |

|                            | with "nval"                                     |  |

| atomicAdd(var,val)         | Atomically adds the value "val" to the cur-     |  |

|                            | rent value of "var"                             |  |

| atomicSub(var,val)         | Atomically subtracts the value "val" to the     |  |

|                            | current value of "var"                          |  |

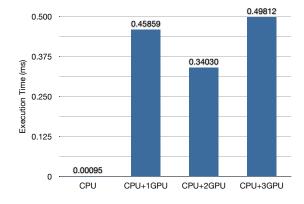

| synchronize()              | Acts as a barrier for all the currently execut- |  |