### Novel TCAD-based Signal-Flow Graph Approaches for the Stability Analysis of Power Semiconductor Devices

| 著者     | 河野 洋志                            |

|--------|----------------------------------|

| year   | 2022-02                          |

| 学位授与年度 | 令和3年度                            |

| 学位授与番号 | 17104甲工第542号                     |

| URL    | http://doi.org/10.18997/00009099 |

## Novel TCAD-based Signal-Flow Graph Approaches for the Stability Analysis of Power Semiconductor Devices

#### Hiroshi Kono

Graduate School of Engineering Kyushu Institute of Technology

This dissertation is submitted for the degree of Doctor of Philosophy in Engineering

February 2022

#### Acknowledgements

First of all, I would like to thank my supervisors. Prof. Ichiro Omura provided me with the opportunity to study at a doctor of engineering course. I would like to thank him for giving me the opportunity to learn electronics systematically through profound discussions on power devices and power electronics on various topics, including not only silicon carbide MOSFETs but also silicon IGBTs, simulations, and current issues for power electronics applications. I would also like to express my gratitude for the meetings that lasted at late night, which may have reduced his sleeping hours. In addition, I would like to apologize for extending the duration of the doctoral program to six years.

I would also like to thank Prof. Satoshi Matsumoto for his generous support and encouragement during my doctoral program and research. I am grateful to Prof. Kazuhiro Toyoda and Prof. Masayuki Watanabe for valuable comments at the examination of this dissertation.

I would also like to thank Ms. Miyo Iwahori for her generous support in writing papers, conducting experiments, and other research activities. Without her support, I could not have continued my research for six years, thank you very much.

I would like to express my gratitude to Kohei Morizuka. He encouraged me to enter a doctoral course and supported my awareness of the need to construct a theoretically supported method for oscillation phenomena in power devices, rather than just trial and error by simulation.

I would like to thank Dr. Masahiro Tanaka, Dr. Satoshi Torimi and Dr. Kenya Kobayashi. They gave me useful advice for my doctor course study and encouraged me. I also would like to thank Dr. He Du for the thoughtful comments on this dissertation.

I would like to thank Mr. Masakazu Yamaguchi for his advice on the development history and device physics of Si-IGBTs.

I would like to thank Hisashi Suzuki and Hideyuki Hayakawa for allowing me to attend the graduate school as a working doctoral student.

Finally, I would like to thank my wife and two sons for their strong support and encouragement over the past six years of my research, which has enabled me to complete this research.

#### Abstract

Technological innovation in power electronics is desired to realize the social demand for the spread of renewable energy and the promotion of electrification of automobiles to achieve carbon neutrality. Power devices are key components in power electronics, and their performance has been improving. As their performance improves, the occurrence of unstable behaviors such as oscillation and noise in power device packages and circuits can cause system failures. Hence, a new design technology to ensure the stable operation is required. In this study, a novel design method is proposed and applied to oscillation phenomena of SiC-MOSFETs and Si-IGBTs during short-circuit operation. The effectiveness of the method is demonstrated by comparing the results calculated using the proposed method and the results obtained using conventional methods and experimental results.

In chapter 1, the requirements for power semiconductors in the international effort to achieve zero  $CO_2$  emissions in 2050 are summarized. Then, the trend of research and development on the improvement of power device characteristics for smaller and higher efficiency power conversion systems is discussed, focusing on Si-IGBT and SiC-MOSFET.

In chapter 2, previous studies on oscillation phenomena and its suppression are summarized, which can become issues as the power devices are improved. These previous studies can be classified into two categories: one based on equivalent circuits and the other based on device physics. However, there has not been sufficient discussion on the oscillation phenomenon that strongly couples circuits and devices, which is becoming more important as power devices become more high-performance. Technology computer aided design (TCAD) mixed mode simulation can handle both circuits and device physics, however, it is difficult to use it for realistic device design due to the large amount of calculation.

In Chapter 3, a new method based on the S-parameter and the signal flow graph (SFG) is introduced to analyze the circuit stability. This method allows us to calculate the frequency response of the output current to the external field maintaining the response of the carrier distribution and electric field inside the device. The signal gain for the focused operating mode can be easily calculated by applying Mason's rule to the SFG. Additionally, the stability analysis using the Nyquist plot enables not only the judgment of the system

stability with respect to the design parameters but also the quantitative evaluation of the stable/unstable margin.

In Chapter 4, the usefulness of the proposed method is verified by applying it to the oscillation phenomenon of SiC-MOSFETs during Type II short-circuit operation. The S-parameters are calculated from the TCAD model for a commercial SiC-MOSFET, and stability analysis is carried out using the SFG. The dependence of the gate resistance required for oscillation suppression obtained from the mixed mode simulation of TCAD is compared with the results obtained from the proposed method. The agreement between the proposed method and the results of TCAD mixed mode simulation is confirmed. Stability analysis is conducted for both the mode in which a single switching device oscillates by coupling with parasitic elements of the circuit and the mode in which oscillation occurs through switching devices connected in parallel. The characteristics of each mode during short-circuit operation are clarified, and the stability phase diagram in the design parameter space is calculated for each mode by taking advantage of the computational speed. It is shown that which mode becomes unstable depends on the design parameters.

In Chapter 5, the proposed method is applied to the oscillation phenomenon of Si-IGBTs under Type II short-circuit operation and the oscillation mechanism is investigated. Experimental results revealed that the oscillation occurred during Type II short-circuit operation and it can be suppressed by increasing the gate resistance. The resistance required for oscillation suppression decreases as the collector voltage increases. The stability analysis is conducted using the proposed method. It is confirmed that the calculated critical gate resistance decreases as the collector voltage increases. The results are in good agreement with the experimental results. The internal behavior of the device under the oscillation state is also analyzed. During the short-circuit operation, a high electric field region is formed at the boundary between the base and drift layers, and the carrier distribution at both ends of the plasma region is modulated through the electron-hole plasma. This modulation becomes more responsive when the collector voltage is smaller.

In Chapter 6, the development potential of the proposed method and future challenges are discussed.

This study presents a new method for accelerating the development of power devices and power electronics systems that contribute to  $CO_2$  reduction, which is becoming an international effort. This method provides an integrated approach for managing the multi-level design hierarchy, from devices to power conversion systems. It is expected that this achievement will make it possible to fully use the potential of power devices and contribute to expanding the application field of power electronics.

#### Abstract

再生可能エネルギーの普及,自動車などの電動化を推進するため,パワーエレク トロニクスの技術革新が期待されている.パワーデバイスはそのキーとなる部品 であり高性能化が進んでいる.高性能化に伴いパワーデバイスのパッケージや回 路で生じる発振・ノイズなどの不安定動作が課題となっている.このような不安 定動作はシステムの故障や誤動作の原因となるため,安定動作を担保する新しい 設計技術が求められている.本研究ではパワーデバイスの内部動作から回路やシ ステムまでを統一的に安定化する新たな設計手法を提案する.

第1章では、2050年の CO<sub>2</sub> 排出量実質ゼロに向けた国際的な取り組みの中 でパワーエレクトロニクスの効率改善、適用範囲拡大に向けた取り組みのまとめ を行った.さらに電力変換システムの小型化・高効率化に向けた炭化ケイ素-金属 酸化膜電界効果トランジスタ(SiC-MOSFET)とシリコン-絶縁ゲート型バイポー ラートランジスタ(Si-IGBT)の高性能化の現状をまとめた.

第2章では、パワーデバイスの高性能化に伴い顕在化する発振現象と、その抑制に関する先行研究の到達点を整理した。先行研究は等価回路に基づく研究 と、デバイス物理に基づく研究に分類される。しかし、パワーデバイスの高性能 化に伴い顕在化する回路とデバイスがより強く結合する発振現象について十分な 議論がされていなかった。Technology computer aided design (TCAD)の mixed mode simulation は回路とデバイス物理の双方を取り扱えるが計算量が多く、現実の素子 設計への適用は難しく、課題となっている。

第3章では、パワーデバイスの内部動作から回路やシステムまでを統一的に 設計する手法を提案する.本手法では、デバイスモデルを元に、TCADシミュレ ーションの結果から求めた S-parameter と回路を、signal flow graph (SFG)を用い て統一的に取り扱い安定性を解析する.この手法では、デバイス内部のキャリア 分布や電界の外場応答を維持したモデル化が可能である.SFG に対して Mason's rule を適用することで着目した動作モードに対する信号ゲインを容易に計算する ことができる.安定性解析に Nyquist plot を用いることで、設計パラメータに対す る安定・不安定の判定を行うだけでなく、設計者が定量的にマージンを設定する ことが可能になる. 第4章では,提案手法をSiC-MOSFETのTypeII短絡動作時の発振現象に適用 することで手法の有用性を示した.市販のSiC-MOSFETの動作を模擬したTCAD モデルからS-parameterを計算し,SFGを使って安定性解析を実施した.TCAD mixed mode simulationから求めた発振抑制に必要なゲート抵抗の回路パラメータ依 存性と提案手法から求められた計算結果を比較し,提案手法とTCAD mixed mode simulationの結果が一致する事を確認した.また,単素子が回路の寄生要素と結合 して発振するモードと,並列接続された素子を通じて発振するモードの双方につ いてそれぞれ安定性解析を実施した.短絡動作時の各モードの特徴を明らかにす るとともに,計算速度を生かし,モード毎に設計パラメータ空間内での安定性の 相図を計算し,設計パラメータにより不安定になるモードが異なる事を示した.

第5章では,提案手法を Si-IGBT の Type II 短絡動作時の発振現象に適用した. はじめに, Si-IGBT の Type II 短絡動作時の発振を実験的に調べ,提案手法による計算結果が実験結果と一致することを示した.また,発振状態でのデバイス内部動作の解析により,短絡動作時にベースとドリフト層境界に,キャリア密度が低下した高電界領域が形成され,外場によってこの領域が伸縮する際,電子正孔プラズマを介して,プラズマ領域両端のキャリア分布が変調されることがわかった.この変調はコレクタ電圧が小さく,高電界領域が狭いほど大きいことが分かった.実験結果の対応から,短絡時に生じる高電界領域とプラズマ領域の外場に対する応答が,外部回路との結合により発振を引き起こすと考えられる.以上のように本手法は,簡易な計算で回路安定性評価とデバイス内部状態解析を同時に行うことができる.

第6章では、本研究のまとめを行い、本手法の発展性について述べた.電磁 界解析と本手法を組み合わせたモジュール構造最適化などについて触れた.

本論文は、今後国際的な取り組みが高まる CO<sub>2</sub> 削減に貢献するパワーエレクトロニクスシステムの開発を加速し、デバイスからシステムまでの全体設計を行うための新しい手法を示したものである.本手法は、これまでその特性を十分に生かしきれていなかったパワーデバイスの特性活用を進め、パワーエレクトロニクスの適用範囲拡大に貢献することが期待される.

## **Table of contents**

| Li | st of fi | gures                                                                        | xi |

|----|----------|------------------------------------------------------------------------------|----|

| Li | st of t  | ables                                                                        | XV |

| 1  | Over     | view of power electronics and power semiconductor                            | 1  |

|    | 1.1      | Social demand for power electronics                                          | 1  |

|    | 1.2      | Functions of power semiconductors in power electronics                       | 3  |

|    | 1.3      | Power semiconductor devices and their trends                                 | 4  |

|    |          | 1.3.1 Silicon insulated gate bipolar transistor                              | 4  |

|    |          | 1.3.2 Silicon carbide metal-oxide-semiconductor field-effect transistor      | 7  |

|    | 1.4      | Summary                                                                      | 13 |

| 2  | Osci     | llation phenomena in power semiconductor operation                           | 15 |

|    | 2.1      | Circuit oriented oscillation                                                 | 16 |

|    | 2.2      | Device oriented oscillation                                                  | 17 |

|    |          | 2.2.1 Oscillation phenomena in short-circuit operation                       | 17 |

|    | 2.3      | Conventional approaches to solve the problem and their limit                 | 18 |

|    | 2.4      | Objective of this study                                                      | 19 |

|    | 2.5      | Summary                                                                      | 20 |

| 3  | Theo     | ory of oscillation analysis with a signal flow graph and a scattering param- |    |

|    | eter     |                                                                              | 21 |

|    | 3.1      | General theory of Scattering parameter (S-parameters)                        | 21 |

|    | 3.2      | Signal flow graph                                                            | 28 |

|    | 3.3      | Novel stability analysis criteria for integrated design in power electronics |    |

|    |          | circuits                                                                     | 33 |

|    | 3.4      | Oscillation condition factor for parallel connected power switches           | 39 |

|    | 3.5      | S-parameter calculation for power switches connected with circuit components | 42 |

|    |          | 3.5.1 S-parameter for single power switch                                    | 42 |

|    |        | 3.5.2 S-parameter for power switches connected in parallel                  | 43  |

|----|--------|-----------------------------------------------------------------------------|-----|

|    | 3.6    | Comparison of oscillation conditions determined from S-parameter and trans- |     |

|    |        | fer function                                                                | 47  |

| 4  | Ana    | lysis of Oscillation phenomena of SiC MOSFETs                               | 51  |

|    | 4.1    | Oscillation phenomena of SiC MOSFETs on Type II short-circuit operation     | 51  |

|    | 4.2    | TCAD simulation model for SiC-MOSFET                                        | 54  |

|    |        | 4.2.1 Device structure                                                      | 54  |

|    |        | 4.2.2 S-parameter                                                           | 54  |

|    | 4.3    | Calculation for a single MOSFET                                             | 55  |

|    | 4.4    | Calculation for parallel connected SiC MOSFETs                              | 60  |

|    |        | 4.4.1 Signal flow model for MOSFETs connected in parallel                   | 60  |

|    |        | 4.4.2 Calculation results of oscillation of MOSFETs connected in parallel   | 63  |

|    | 4.5    | Summary                                                                     | 70  |

| 5  | Ana    | lysis of Oscillation phenomena of Si-IGBTs                                  | 71  |

|    | 5.1    | Oscillation phenomena of Si IGBTs on short-circuit Type II operation        | 71  |

|    |        | 5.1.1 Experiment for oscillation on Type II short circuit operation         | 71  |

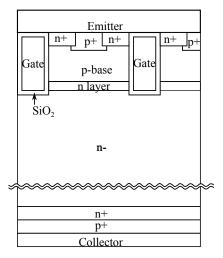

|    | 5.2    | TCAD simulation model for Si-IGBT                                           | 74  |

|    | 5.3    | Analysis of device operation during the oscillation                         | 77  |

|    | 5.4    | Analysis of oscillation mechanism                                           | 80  |

|    | 5.5    | Summary                                                                     | 87  |

| 6  | Con    | clusions                                                                    | 89  |

|    | 6.1    | Summary                                                                     | 89  |

|    | 6.2    | Significance of the proposed method to the power converter design and fu-   |     |

|    |        | ture development                                                            | 90  |

| Re | eferen | nces                                                                        | 93  |

| Aj | opend  | lix A Matrix calculation                                                    | 101 |

## List of figures

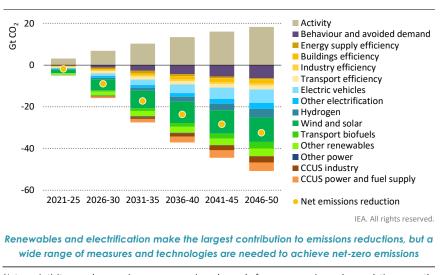

| 1.1  | Average annual $CO_2$ reductions from 2020 in the net zero emission. [1]                | 2  |

|------|-----------------------------------------------------------------------------------------|----|

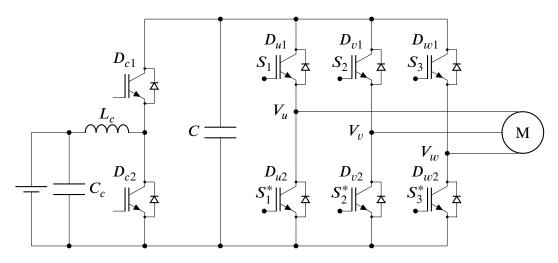

| 1.2  | Circuit diagram of a three phase inverter                                               | 4  |

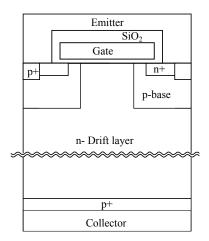

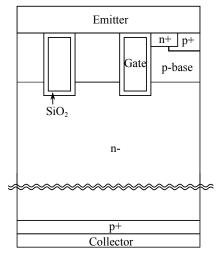

| 1.3  | Schematics of insulated gate bipolar transistors                                        | 5  |

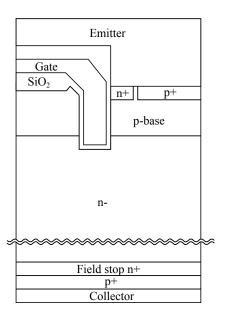

| 1.4  | Cristal structures of silicon carbide poly types [2]                                    | 8  |

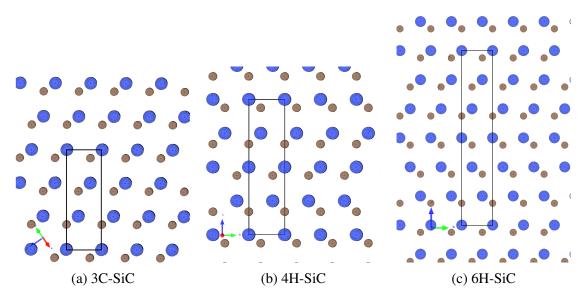

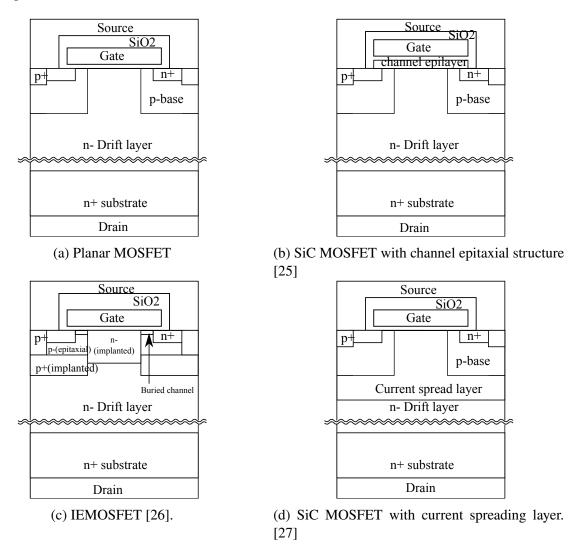

| 1.5  | Schematics of Silicon Carbide MOSFETs                                                   | 10 |

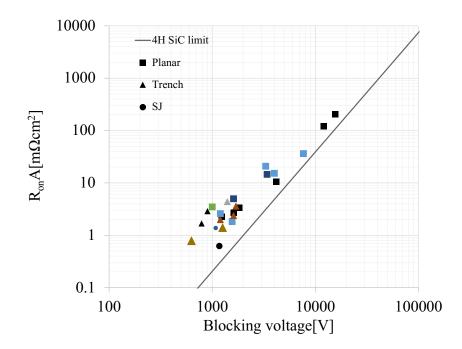

| 1.6  | The trade-off relationship between $R_{on}A$ and $V_{bd}$ of SiC MOSFETs. $\ . \ . \ .$ | 13 |

| 3.1  | N-port network and incident power waves and reflected power waves on the                |    |

|      | ports.                                                                                  | 22 |

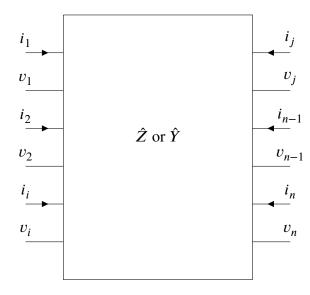

| 3.2  | Voltage and current definitions for a multiport network                                 | 25 |

| 3.3  | ABCD matrix for two port network.                                                       | 25 |

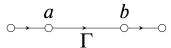

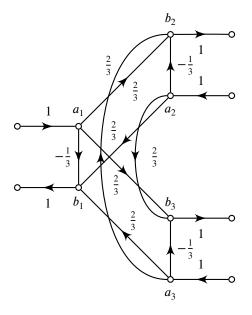

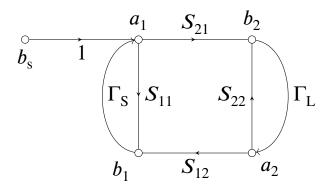

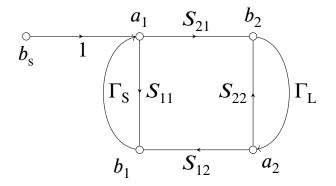

| 3.4  | Description of the signal flow graph.                                                   | 29 |

| 3.5  | Signal flow graph for two port network.                                                 | 30 |

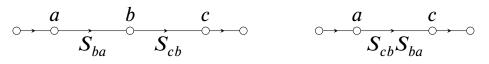

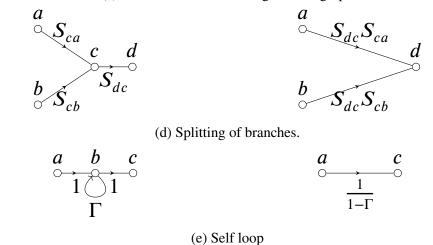

| 3.6  | Transformation of the signal flow graph                                                 | 30 |

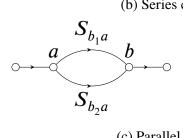

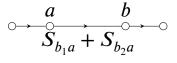

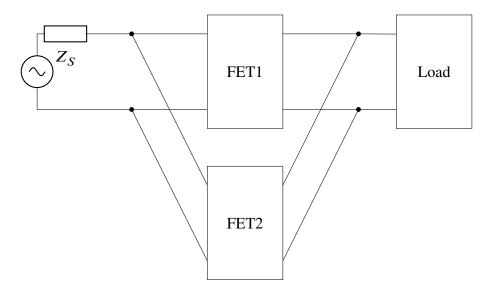

| 3.7  | Sourced and loaded FETs connected in parallel                                           | 31 |

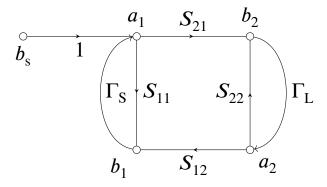

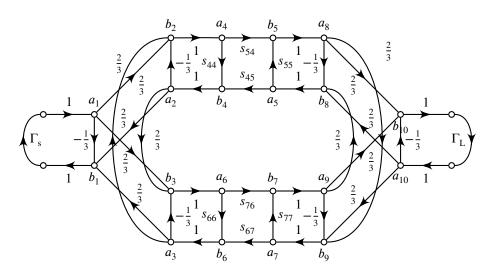

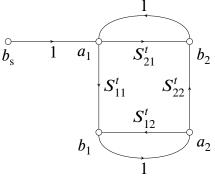

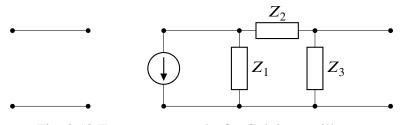

| 3.8  | The signal flow graph on the 3 ports connection.                                        | 32 |

| 3.9  | The signal flow graph of the circuit composed parallel connected devices.               | 33 |

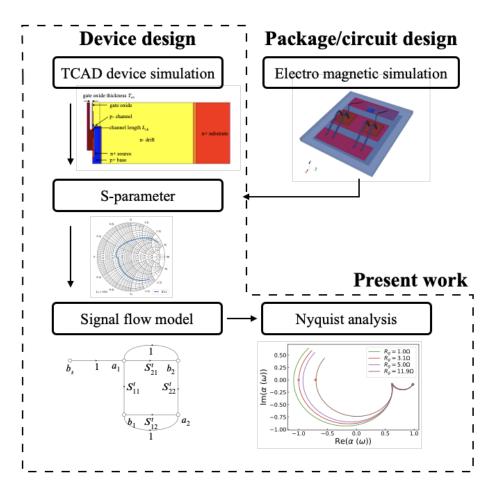

| 3.10 | The proposed concept of design flow integrates device, package and circuit              |    |

|      | design                                                                                  | 34 |

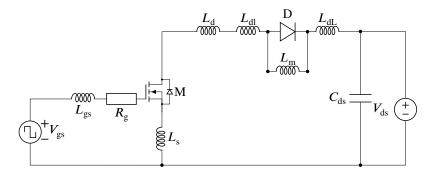

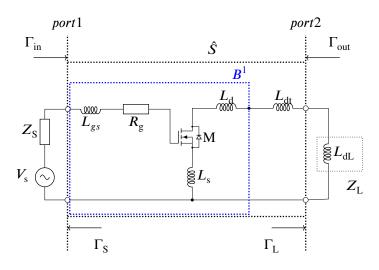

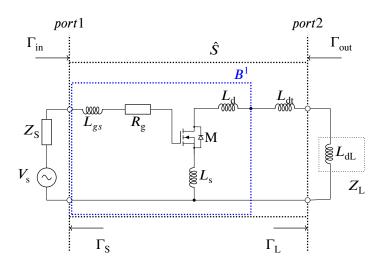

| 3.11 | Chopper circuit investigated in this paper. The circuit consists of a high-side         |    |

|      | diode and a low-side MOSFET                                                             | 35 |

| 3.12 | Simplified equivalent circuit.                                                          | 36 |

| 3.13 | Equivalent Signal flow graph                                                            | 37 |

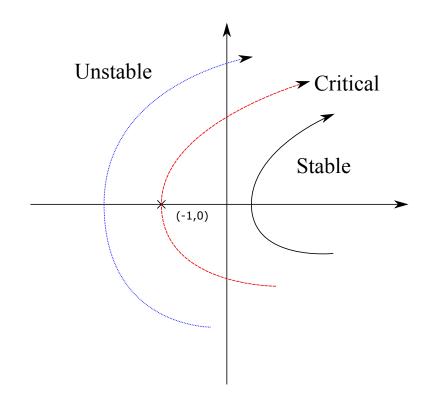

| 3.14 | Nyquist plot of the oscillation condition factor.                                       | 39 |

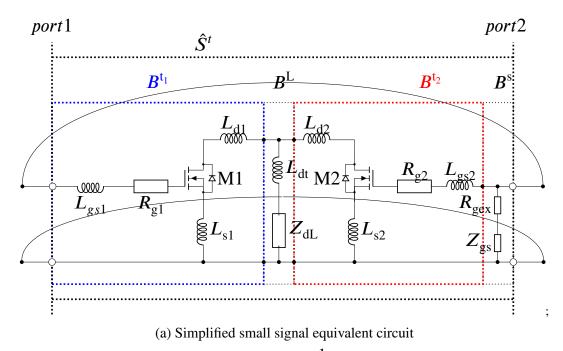

| 3.15 | Simplified small signal equivalent circuit                                              | 40 |

| 3.16 | Simplified equivalent circuit and signal flow graph to evaluate the oscillation         |    |

|      | condition.                                                                              | 41 |

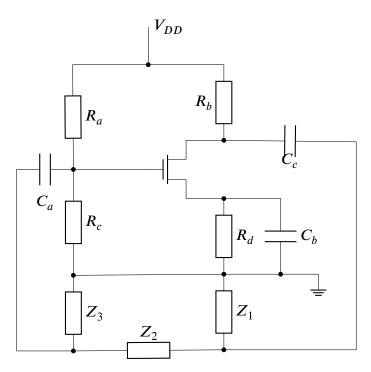

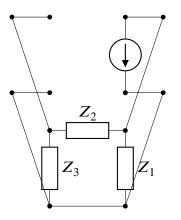

| 3.17 | Circuit of Colpitts oscillator.                                                         | 47 |

| 3.18 | Small signal equivalent circuit for the Colpitts oscillator                                                                                     | 48 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.19 | Two-port networks for Colpitts oscillator.                                                                                                      | 48 |

| 3.20 | Two-port networks for equivalent small signal model                                                                                             | 50 |

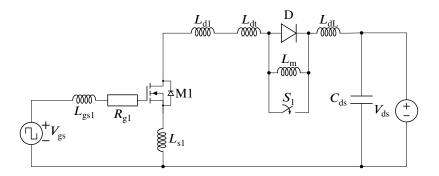

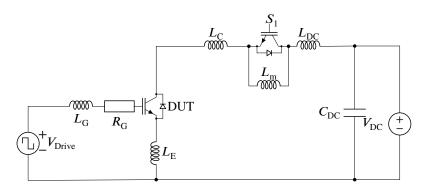

| 4.1  | Evaluation circuit investigated in this chapter. The circuit consists of a high-                                                                |    |

|      | side diode and a low-side MOSFET. The ideal switch is connected in parallel                                                                     |    |

|      | with a high-side diode to reproduce SC type II in transient simulation                                                                          | 52 |

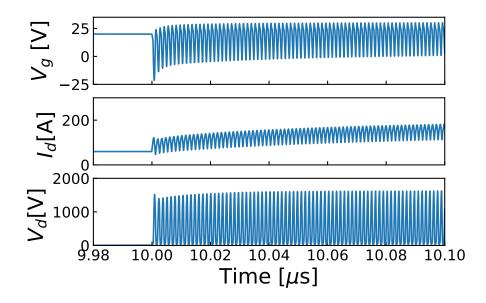

| 4.2  | Experimental waveforms during SC type II. Commercially available SiC                                                                            |    |

|      | MOSFET (C2M0080120) was used                                                                                                                    | 52 |

| 4.3  | Waveform of the gate voltage, the drain voltage and current of M1 at 10 $\mu$ s                                                                 |    |

|      | using TCAD device simulation. Shortage of the high-side load causes an                                                                          |    |

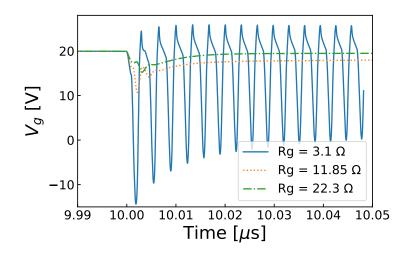

|      | increase in drain voltage and continuous oscillation                                                                                            | 53 |

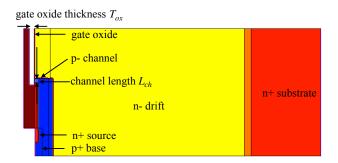

| 4.4  | The two-dimensional half-cell of the TCAD device model of silicon carbide                                                                       |    |

|      | MOSFET                                                                                                                                          | 54 |

| 4.5  | Simplified equivalent circuit.                                                                                                                  | 55 |

| 4.6  | Equivalent Signal flow graph.                                                                                                                   | 56 |

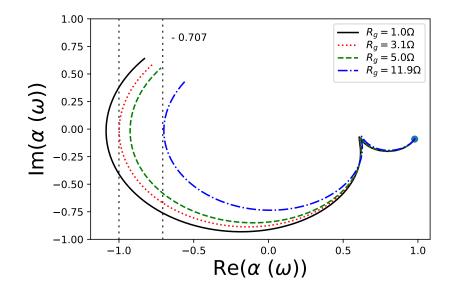

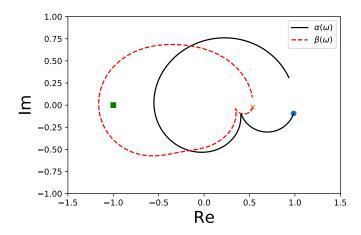

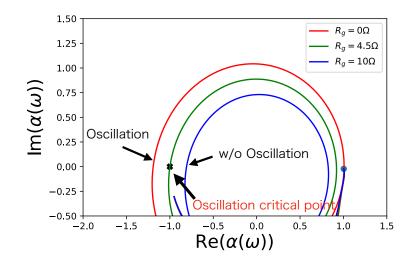

| 4.7  | The Nyquist plot of the oscillation condition factors $\alpha(\omega)$ . The circuit param-                                                     |    |

|      | eters are set as $L_{s1} = 10 \text{ nH}$ , $L_{gs1} = 1 \text{ nH}$ , $L_{dL} = 1 \text{ nH}$ , and $L_{dt} = 1 \text{ nH}$ . These            |    |

|      | plots show the calculated results when $\omega$ changes from 100 kHz to 1 GHz.                                                                  |    |

|      | The circle points indicate the calculation results at 100 kHz                                                                                   | 57 |

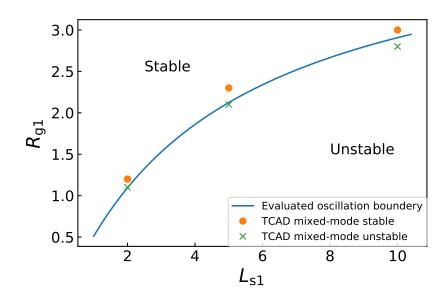

| 4.8  | $L_{s1}$ dependence of the external resistance $(R_{g1})$ to suppress the oscillation.                                                          |    |

|      | The line represents the boundary between the stable and unstable regions.                                                                       |    |

|      | The circles and crosses are the results of the TCAD simulation, which indi-                                                                     |    |

|      | cate where the oscillation was suppressed and occurred, respectively                                                                            | 57 |

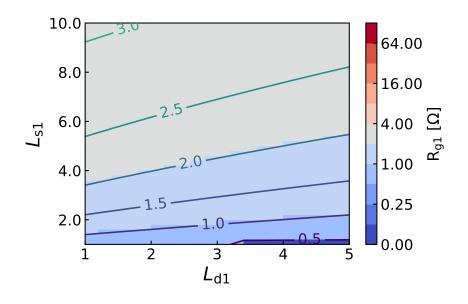

| 4.9  | The critical resistance $(R_{g1})$ to suppress the oscillation evaluated by the os-                                                             |    |

|      | cillation condition factors $\alpha(\omega)$ . The circuit parameters are set as $L_{dL} = 1$                                                   |    |

|      | nH, $L_{gs1} = 2$ nH, and $L_{dt} = 1$ nH.                                                                                                      | 58 |

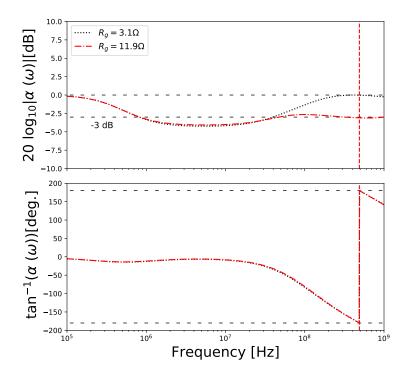

| 4.10 | Bode diagram of the oscillation factor $\alpha(\omega)$ . The phase and gain of the loop                                                        |    |

|      | gain are -180° and 0 db respectively, when $R_{g1} = 3.1 \Omega$ . In contrast, the                                                             |    |

|      | phase and gain of the loop gain are -180° and -3 db respectively when $R_{g1}$                                                                  |    |

|      | $= 11.9 \ \Omega. \qquad \dots \qquad $ | 59 |

| 4.11 | Gate resistance dependence of the gate voltage waveform. When $R_{g1} = 3.1$ ,                                                                  |    |

|      | 11.9, and 22.3 $\Omega$ , the gain corresponds to 0 dB, -3 dB, and -6 dB, respectively.                                                         | 59 |

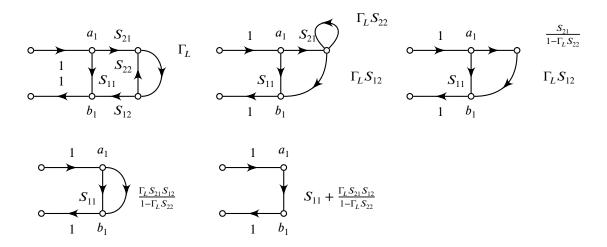

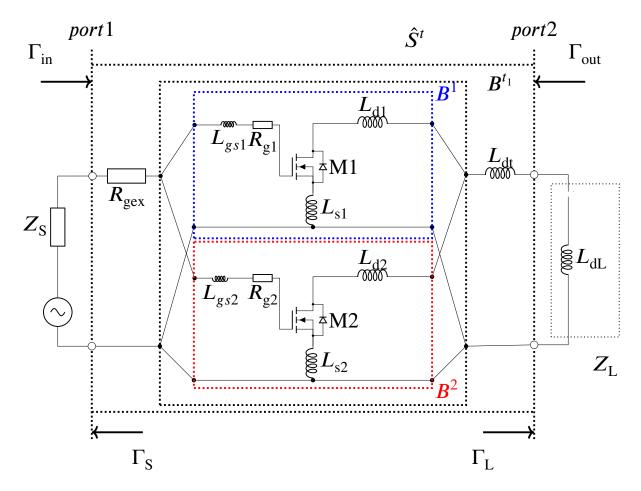

| 4.12 | Evaluation circuit used to calculate oscillation conditions when MOSFETs                                                                        |    |

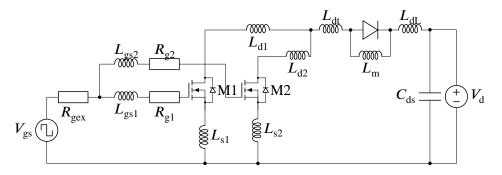

|      | are connected in parallel.                                                                                                                      | 60 |

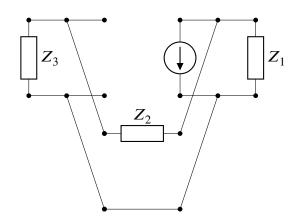

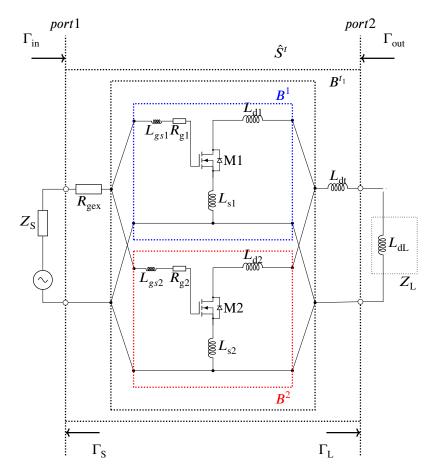

| 4.13 | Simplified small signal equivalent circuit                                                                                                      | 61 |

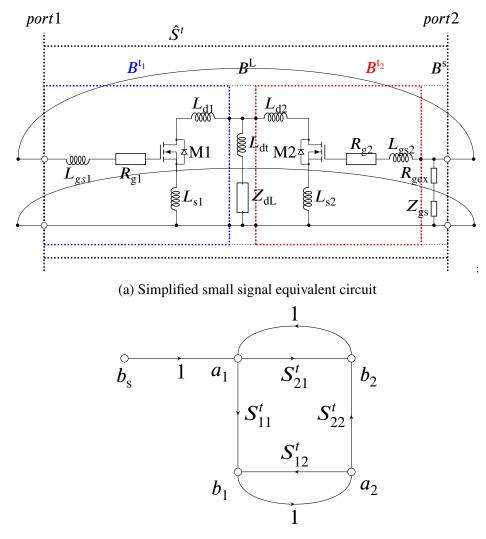

| 4.14 | Simplified equivalent circuit and signal flow graph to evaluate the oscillation condition.                                                                                                                                                                                                                                                                                                                                                                                  | 63       |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

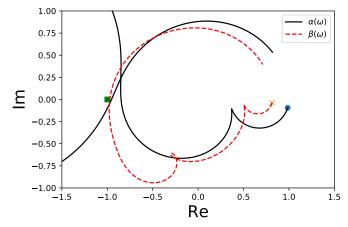

| 4.15 | The Nyquist plot with the oscillation condition factors when the circuit parameters are set as $L_{s1} = L_{s2} = 10$ nH, $L_{dt} = 1$ nH. These plots show the calculated results when $\omega$ changes from 100 kHz to 10 GHz. The circles and cross points indicate the results of the calculation at 100 kHz. The square points indicate the point (-1, 0 <i>j</i> ).                                                                                                   | 64       |

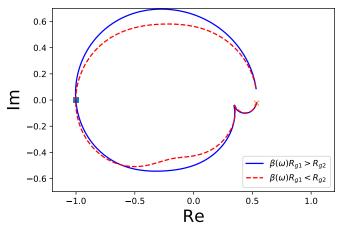

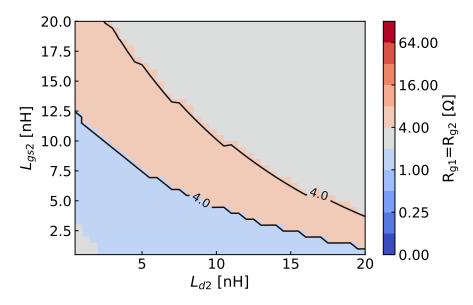

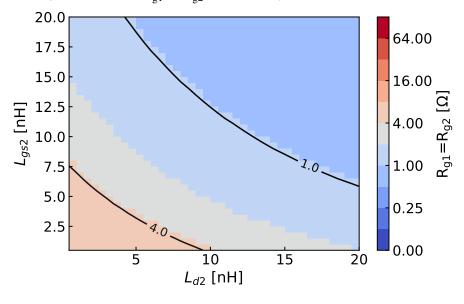

| 4.16 | Critical gate resistance $(R_{g1} = R_{g2})$ evaluated by the oscillation condition<br>factors $\alpha(\omega)$ and $\beta(\omega)$ . The circuit parameters are set as $L_{d1} = L_{d2} = 2$ nH,<br>$L_{s1} = L_{s2} = 10$ nH, $L_{gs1} = 2$ nH, $L_{dL} = 1$ nH, and $R_{gex} = 1.5 \Omega$                                                                                                                                                                               | 66       |

| 4.17 | Critical gate resistance $(R_{g1} = R_{g2})$ evaluated by the oscillation condition<br>factors $\alpha(\omega)$ and $\beta(\omega)$ . The circuit parameters are set as $L_{d1} = 2$ nH, $L_{s1} = L_{s2} = 10$ nH, $L_{gs1} = 2$ nH, $L_{dL} = 1$ , $L_{dt} = 1$ nH, and $R_{gex} = 1.5 \Omega$ .                                                                                                                                                                          | 67       |

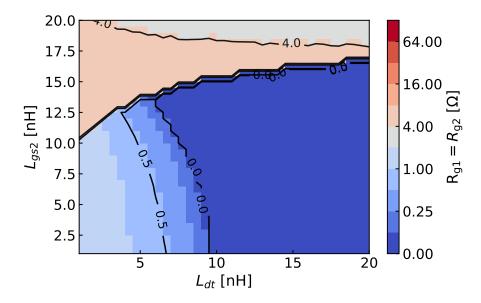

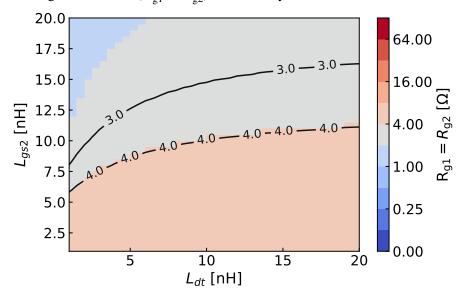

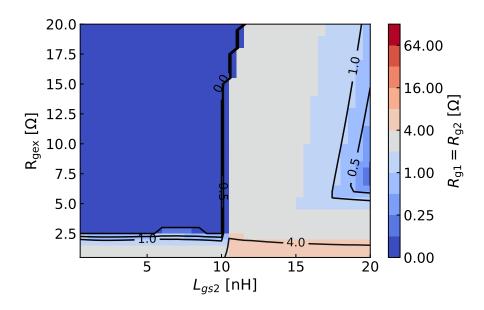

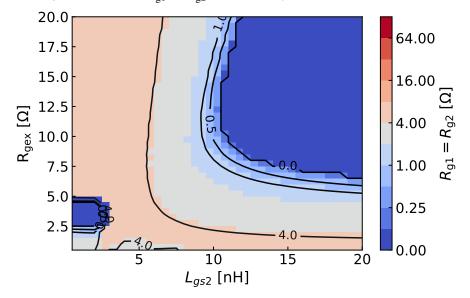

| 4.18 | Critical gate resistance $(R_{g1} = R_{g2})$ evaluated by the oscillation condition factors $\alpha(\omega)$ and $\beta(\omega)$ . The circuit parameters are set as $L_{d1} = L_{d2} = 2$ nH,                                                                                                                                                                                                                                                                              | 68       |

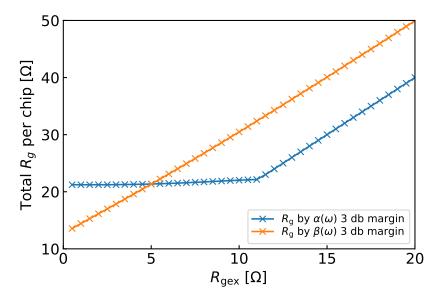

| 4.19 | $L_{s1} = L_{s2} = 10 \text{ nH}, L_{gs1} = 2 \text{ nH}, L_{dL} = 1 \text{ nH}, \text{ and } L_{dt} = 1 \text{ nH}.$<br>Total gate resistance par chip evaluated by oscillation condition factors $\alpha(\omega)$<br>and $\beta(\omega)$ with 3 db gain margin. The circuit parameters are set as $L_{d1} = L_{d2}$<br>$= 2 \text{ nH}, L_{s1} = L_{s2} = 10 \text{ nH}, L_{gs1} = 2 \text{ nH}, L_{gs2} = 5 \text{ nH}, L_{dL} = 1, \text{ and } L_{dt} = 1 \text{ nH}.$ | 69       |

| 5.1  | Evaluation circuit investigated in this study. The circuit consists of a high-<br>side IGBT with a parallel connected fast recovery diode and a low-side<br>IGBT                                                                                                                                                                                                                                                                                                            | 72       |

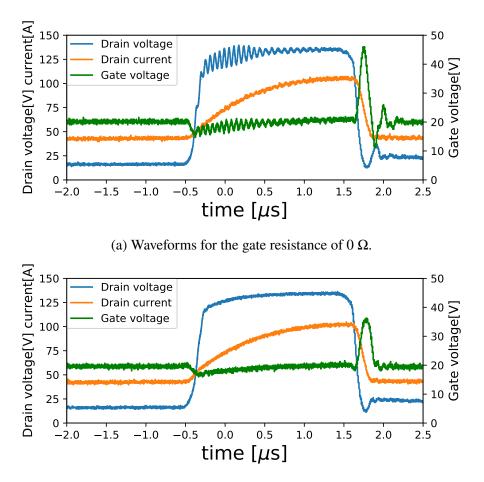

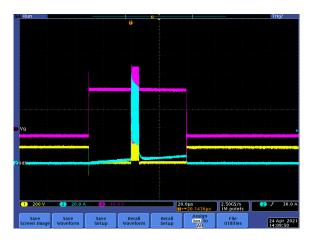

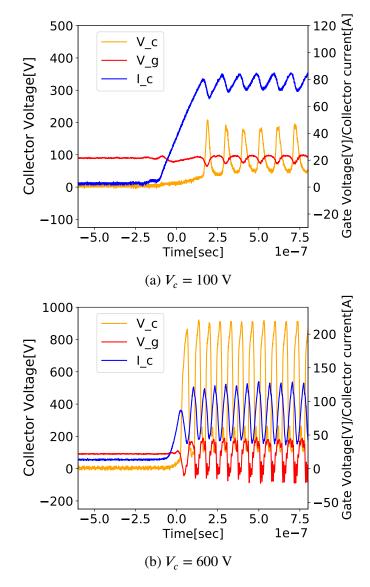

| 5.2  | Switching waveforms of the IGBT in SC type II. The high-side switch was turned on during low-side IGBT.                                                                                                                                                                                                                                                                                                                                                                     | 72       |

| 5.3  | Enlarged switching waveforms of the IGBT in SC type II. The high-side switch was switched on while the low-side IGBT was on. The short-circuit current induced a parasitic oscillation of the IGBT.                                                                                                                                                                                                                                                                         | 73       |

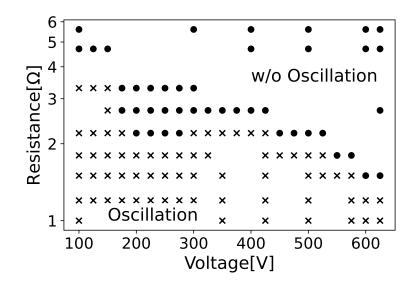

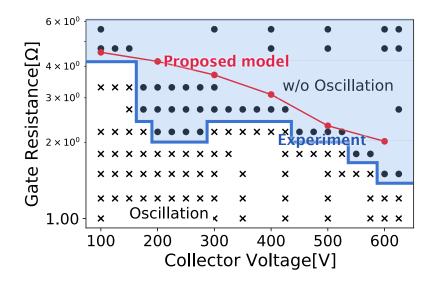

| 5.4  | Dependence of the occurrence of oscillation on gate resistance and collector voltage. The circles indicate the points that oscillation was not observed, and crosses indicate the points that oscillation was observed.                                                                                                                                                                                                                                                     | 74       |

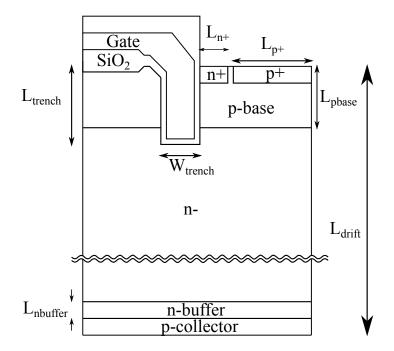

| 5.5  | Schematic of simulation model structure of the trench IGBT                                                                                                                                                                                                                                                                                                                                                                                                                  | 75       |

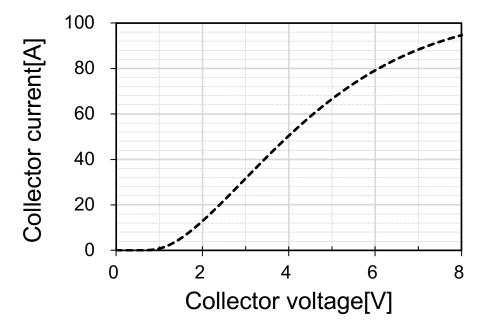

| 5.6  | Collector-Emitter current versus voltage by TCAD simulation.                                                                                                                                                                                                                                                                                                                                                                                                                | 75       |

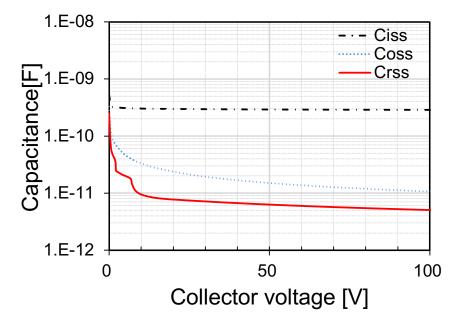

| 5.7  | Collector voltage dependences of the input, output, and feedback capaci-                                                                                                                                                                                                                                                                                                                                                                                                    | 76       |

| 5.8  | tances calculated using TCAD simulation                                                                                                                                                                                                                                                                                                                                                                                                                                     | 70<br>77 |

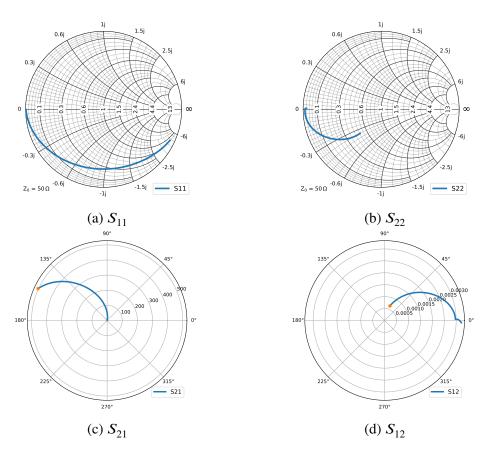

| 5.0  | Smith charts of the calculated S-parameter when $V_d = 100$ V                                                                                                                                                                                                                                                                                                                                                                                                               | 11       |

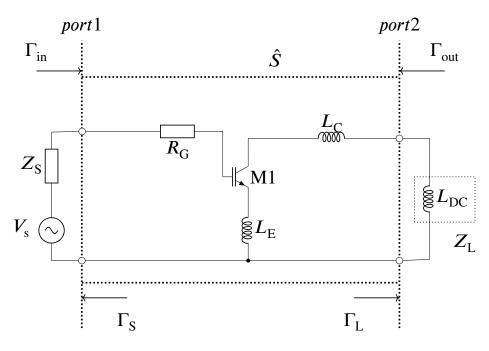

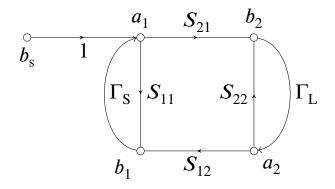

| 5.9  | Simplified equivalent circuit.                                                                    | 78  |

|------|---------------------------------------------------------------------------------------------------|-----|

| 5.10 | Equivalent signal flow graph                                                                      | 79  |

| 5.11 | The Nyquist plot of the oscillation condition factors $\alpha(\omega)$ when $V_c = 100 \text{ V}$ |     |

|      | and $V_g = 20$ V                                                                                  | 80  |

| 5.12 | Calculated drain voltage dependence of the gate resistance to suppress the                        |     |

|      | oscillation.                                                                                      | 80  |

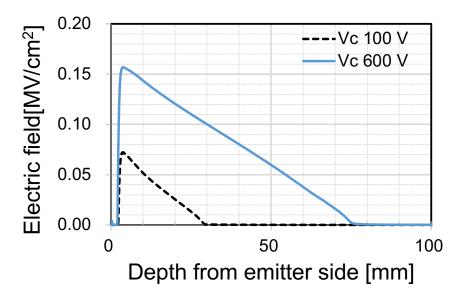

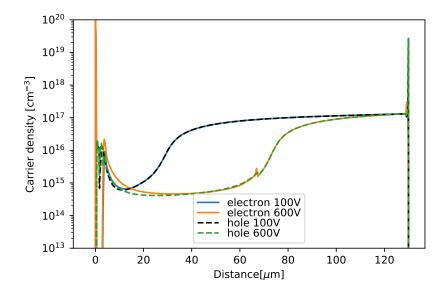

| 5.13 | Electric field distribution during SC type II when $V_c = 100$ V and 600 V.                       | 81  |

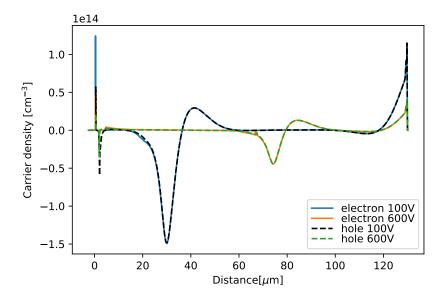

| 5.14 | Carrier density distribution during SC type II when $V_c = 100$ V and 600 V.                      | 81  |

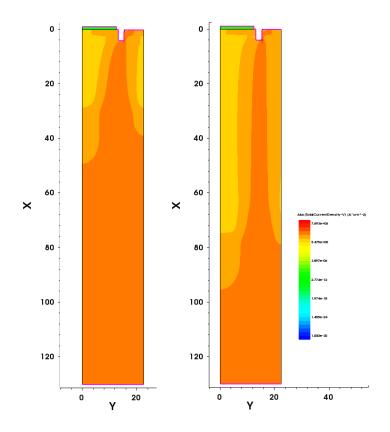

| 5.15 | Current density distribution when $V_c = 100$ V and 600 V                                         | 82  |

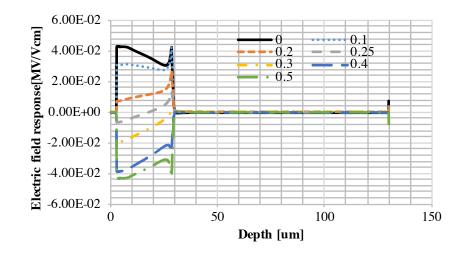

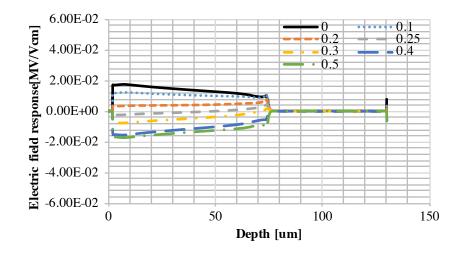

| 5.16 | Response Distribution at 10MHz.                                                                   | 83  |

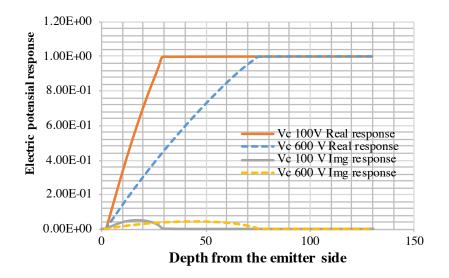

| 5.17 | The distributions of electric potential responses for corrector voltages when                     |     |

|      | $V_c = 100 \text{ V} \text{ and } 600 \text{ V}.$                                                 | 84  |

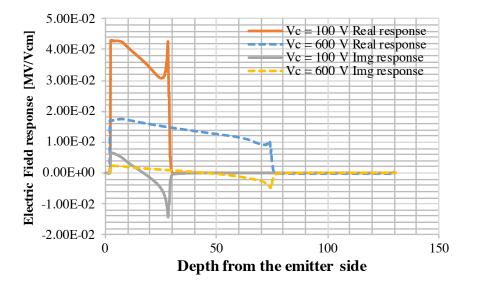

| 5.18 | Electric field responses for corrector voltages calculated by derivation of the                   |     |

|      | potential response when $V_c = 100$ V and 600 V                                                   | 84  |

| 5.19 | The time dependences of electric field distribution when $V_c = 100$ V                            | 85  |

| 5.20 | The time dependences of electric field distribution when $V_c = 600$ V                            | 85  |

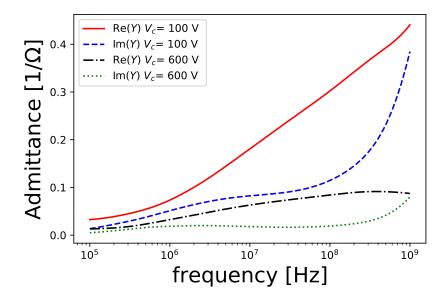

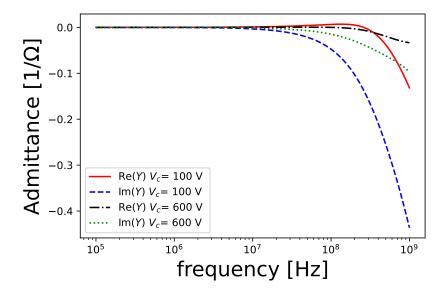

| 5.21 | Frequency dependences for $Y_{cc}$ when $V_c = 100$ V and 600 V                                   | 86  |

| 5.22 | Frequency dependences of $Y_{gc}$ when $V_c = 100$ V and 600 V                                    | 86  |

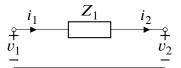

| A.1  | A two-port network consisting of a series impedance $Z_1 \ldots \ldots \ldots$                    | 102 |

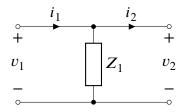

| A.2  | A two-port network consisting of a shunt impedance $Z_1$                                          | 102 |

| A.3  | A small signal model of a FET                                                                     |     |

## List of tables

| 1.1 Comparison of material properties of Silicon Carbide poly types and Silic |                                             |    |  |

|-------------------------------------------------------------------------------|---------------------------------------------|----|--|

|                                                                               | [3, 4]                                      | 7  |  |

| 4.1                                                                           | Device parameters of the TCAD device model. | 54 |  |

| 4.2                                                                           | S-parameter calculated by TCAD simulator.   | 55 |  |

| 5.1                                                                           | TCAD device parameters shown in Fig.5.5.    | 72 |  |

| 5.2                                                                           | Device parameters of the TCAD device model  | 76 |  |

| 5.3                                                                           | S-parameter calculated by TCAD simulator    | 78 |  |

## Chapter 1

## **Overview of power electronics and power semiconductor**

#### **1.1** Social demand for power electronics

Global warming is considered as one of the most important and urgent issues for human society. The Paris agreement was an international agreement to limit the temperature increase to less than 2 degrees Celsius compared to pre-industrial levels. The intergovernmental panel on climate change's (IPCC's) 2018 "Global warming of 1.5°C" report [5] states that the average global temperature in 2017 was about 1 degree Celsius higher than it was before the industrial revolution, and that the average temperature increase will reach 1.5°C between 2030 and 2050 if the current rate of temperature increase is maintained.

This report also states that if global warming is limited to  $1.5^{\circ}$ C, it will be possible to suppress the loss of some ecosystems that would occur with a high degree of certainty if temperatures are allowed to increase to 2°C. This scenario requires a 45% reduction in CO<sub>2</sub> emissions by 2030 and a net-zero level by 2050. International energy agency (IEA) shows a roadmap to reduce CO<sub>2</sub> emissions to NET zero by 2050 [1]. According to the roadmap, 60 percent of global vehicle sales must shift to electric vehicles by 2030, new sales of internal combustion engine vehicles must be ceased by 2035, and renewable energy sources must account for 90 percent of electricity generation by 2050.

This roadmap states that the improvement in power electronics technology will expand its application field and improve the performance of power converters and increase the ratio of renewable energy to total power generation.

Because power electronics handles a wide range of output power, the technology requirements depend on the application field and output power.

Notes: Activity = changes in energy service demand from economic and population growth. Behaviour = change in energy service demand from user decisions, e.g. changing heating temperatures. Avoided demand = change in energy service demand from technology developments, e.g. digitalisation.

Fig. 1.1 Average annual  $CO_2$  reductions from 2020 in the net zero emission. [1]

For example, in the case of a power converter unit used in a vehicle such as an automobile, downsizing the volume of the converter unit may be more important than other applications. It has been reported that the improved aerodynamic performance of the vehicle body due to the downsized converter contributes to the improved cruising range as well as improved efficiency of the converter [6].

It has also been reported that the use of silicon carbide (SiC) power devices in railroad inverters not only improves an inverter efficiency but also enables power regeneration under the high load operating conditions, thereby reducing the need for deceleration using thermal brakes and improving the overall power efficiency by sharing the regenerated power with other trains [7, 8].

In this way, to expand the field of applications of power electronics, it is necessary not only to improve the efficiency of individual systems components, but also to optimize the entire system in terms of required characteristics, operation, and cost. Therefore, the development of design technology to realize these requirements is an important theme.

#### **1.2 Functions of power semiconductors in power electron**ics

To realize the requirements for power electronics described in the previous section, it is necessary to improve the characteristics of the power device and the circuit system. Recently, it has been shown that SiC power devices can significantly improve the performance of power devices by achieving unipolar switching devices in the high breakdown voltage region, which could not be achieved with conventional silicon metal-oxide-semiconductor field-effect transistors (Si-MOSFETs). As can be seen from the examples of automobiles and railroads introduced in the previous section, the improvement of power devices can not only reduce the loss of the power devices themselves but also resolve the issues of the power electronics system.

Figure 1.2 shows a circuit diagram connecting a bidirectional chopper circuit and a motor drive inverter. In this circuit, the voltage of the storage battery is boosted by the chopper circuit and it is used as an input to the motor drive inverter. By increasing the voltage, it becomes possible to reduce the current required to drive the motor, which enables the wiring and motor to be smaller and lighter. The bidirectional chopper can also charge the storage battery during regeneration from the inverter.

Although the output of the chopper circuit is desired to be constant, it has a finite ripple due to the switching of the FETs. The ripple current  $\delta i_L$  is proportional to  $\frac{T}{L}(V_{in} - V_{out})$ , where  $V_{in}$  and  $V_{out}$  are the input and output voltages, T is the switching period, and L is the inductance. Therefore, the switching frequency is inversely proportional to the inductance L when the ripple current is to be suppressed to a particular value.

Generally, the volume and weight of the inductor increase with the inductance. Therefore, by increasing the switching frequency, it becomes possible to reduce the size of the inductor and filter capacitor, which occupy a large proportion of the weight and volume of the power conversion unit. However, an increase in the switching frequency increases the switching loss of the power devices. Therefore, it is important to reduce the switching loss to downsize the power conversion system.

In a three phase inverter circuit, two switching devices like as insulated gate bipolar transistors (IGBTs) or FETs, are connected in series for each phase (U, V, and W), and a diode such as a PiN diode or SBD is connected in parallel with each switching device. In some cases, the parasitic diodes of the MOSFETs are used instead of connecting the diodes in parallel. In the inverter circuit, the motor is rotated by switching the gate signals of the U, V, and W phases. When the gate signal is switched off, the current is diverted from the FET

Fig. 1.2 Circuit diagram of a three phase inverter.

to the reverse side diode. For this reason, the diode is required in parallel with the switching device.

In addition to efficiency during normal operation, power converters must prevent the failure of components triggered by a failure of another component. Normally, if an excessive voltage or current flow is applied, the controller sends an off signal to the power devices to protect them. Therefore, power devices must have tolerant before entering the protective operation. For example, if the load is short-circuited during the switching operation, the device must be able to withstand high voltage and high current for several microseconds to safely cut off the current flowing through the device.

#### **1.3** Power semiconductor devices and their trends

In this section, the trends of technological development in power devices are discussed, focusing on Si-IGBT and SiC-MOSFET.

#### **1.3.1** Silicon insulated gate bipolar transistor

Si-IGBTs have been developed to realize both MOSFET-like usability of voltage driving and the characteristics of bipolar transistors, such as high current capability, wide safety operating area and short-circuit tolerance, in contrast to the gate-turn off thyristors (GTOs), which were the mainstream until IGBTs were developed. The device structure is shown in Figure 1.3(a). The structure consists of a bipolar transistor connected to a MOSFET in series. This structure allows the device to handling higher current than ordinary MOSFETs and simpli-

fies the control circuits compared to ordinary bipolar devices. In this subsection, the trends in the development of IGBTs are discussed [9].

(a) Insulated gate bipolar transistor (IGBT).

(c) Carrier stored trench-gate bipolar transistor (CSTBT).

(b) Injection enhanced gate transistor (IEGT).

(d) Trench field-stop IGBT.

Fig. 1.3 Schematics of insulated gate bipolar transistors.

IGBT structures were proposed in the late 1970s and early 1980s. Baliga et al. proposed an insulated gate rectifier (IGR) with a p+ region on the back side of the MOSFET [10]. This device had the problem of low latch-up tolerance of the parasitic thyristor when a large current was applied. Nakagawa's non latch-up IGBT structure solved this problem [11]. They showed that the latch-up can be suppressed by omitting the source contact area in the horizontal direction. This structure led to the widespread use of IGBTs in power supply circuits with high voltage and high current.

As there is a trade-off between the on-voltage and the switching characteristics, how to improve this trade-off relationship has been the history of IGBT development. To reduce the on-voltage of IGBTs, the cells were miniaturized, and trench-gates were developed. In the process of increasing the breakdown voltage of these trench-gate IGBTs, there was the problem that the on-voltage could not be reduced sufficiently. This problem was solved by the injection enhancement (IE) effect. The IE effect is achieved by reducing the number of emitters in the trench-gate IGBTs, which reduces the extraction of holes from the emitters during conductivity modulation and increases the carrier concentration on the surface side. This structure enables a reduction in on-voltage even in high voltage devices [12].

A carrier stored trench-gate bipolar transistor (CSTBT) has also been reported [13]. The CSTBT has a high concentration n layer on the surface side of the device, as shown in Fig. 1.3(c), based on the same concept as the IE effect. This region reduces the efficiency of hole extraction from the emitter side.

The structure of the drift layer has also been improved. Initially, epitaxial growth was performed on the p-substrate to provide a junction. Additionally, the design was optimized by controlling the lifetime of holes due to the trade-off with switching loss (punch-through: PT-IGBT). Goodman et al. proposed an n+ buffer structure. By adding the n+ buffer region on the back side with a higher concentration than that of the drift layer, the trade-off between on-voltage and switching speed can be improved by controlling the lifetime [14].

Later, using a thin-wafer process, the non punch-through (NPT) structure was proposed to reduce the injection efficiency from the p-collector layer without lifetime control [15]. In contrast to the conventional drift layer formed by epitaxial growth on a Czochralski (CZ) wafer, the NPT-IGBT uses a floating zone (FZ) wafer and forms a backside p-structure using a thin-wafer process. In this process, the injection efficiency from the p-collector is reduced so that the lifetime control is not applied.

This design allows us to reduce the carrier injection concentration on the backside compared to conventional PT-IGBTs and to flatten the carrier concentration in the entire drift layer during conductivity modulation. This makes it possible to increase the contribution of the electron current to the total current, thus lowering the drift layer resistance with a smaller carrier concentration. As a further improved concept to the NPT-IGBT, a field stop (FS) structure IGBT was proposed to reduce the n-drift layer thickness in order to lower on-voltage and to stop the depletion layer reaching the back side [16].

After that, optimization of the surface structure, drift layer, and back surface structure have been carried out, and IGBTs with various breakdown voltage ranges from 1.2 kV to 6.5 kV are used in various application fields, including home appliances, automobiles, trains, and grid power conversion devices.

#### 1.3.2 Silicon carbide metal-oxide-semiconductor field-effect transistor

#### Physical properties of silicon carbide

As described in the previous section, IGBTs have played a major role in the field of power electronics as high-voltage and high-current switching devices. Although many studies have been conducted to improve their performance, there is a limit to the switching speed because they are bipolar devices. In recent year, silicon carbide metal-oxide-semiconductor field-effect transistors (SiC MOSFETs) have attracted attention as devices that overcome the limitation of Si-IGBTs.

SiC is a semiconductor material of which the band gap is three times larger than that of silicon. It has a higher electric field for breakdown than Si. Therefore, it is possible to reduce drift layer resistance by increasing the drift layer doping concentration and thinning the drift layer thickness. It is theoretically possible to reduce the drift layer resistance to about 1/1000 of that of a Si device with the same breakdown voltage [17].

|                                       | Silicon | 3C-SiC | 4H-SiC     | 6H-SiC     |

|---------------------------------------|---------|--------|------------|------------|

| Energy Band Gap                       | 1.12    | 2.23   | 3.26       | 3.02       |

| [eV]                                  |         |        |            |            |

| Critical electric field for breakdown | 0.3     | 1.5    | 2.8        | 3.0        |

| [MV/cm]                               |         |        |            |            |

| Thermal Conductivity                  | 1.5     | 4.9    | 4.9        | 4.9        |

| [W/cm K]                              |         |        |            |            |

| Electron mobility                     | 1350    | 1000   | 1000 (⊥ c) | 450 (⊥ c)  |

| [cm <sup>2</sup> /Vs]                 |         |        | 1200(   c) | 100 (   c) |

Table 1.1 Comparison of material properties of Silicon Carbide poly types and Silicon [3, 4].

Incidentally, SiC has many polytypes. The atomic configurations of 3C, 4H, and 6H-SiC are shown in Figure 1.4. Table 1.1 shows the physical properties of each polytype. The band gaps of 4H-SiC and 6H-SiC are larger than that of 3C-SiC, and they have a higher breakdown electric field. In addition, Baliga's figure of merit of 4H-SiC is better than that of

6H-SiC because the electron mobility of 4H-SiC is higher than that of 6H-SiC. As shown in Fig. 1.4, 3C-SiC, 4H-SiC, and 6H-SiC have a repeating structure of silicon and carbon atom pairs with 3, 4, and 6 cycles in the stacking direction [2]. Stacking faults are easily generated by the fluctuation between other polytypes during the crystal growth process. In particular, 3C-SiC is steady state at epitaxial growth temperature and other polytypes can change into 3C-SiC during epitaxial growth. To solve this problem, step-flow epitaxial growth has been proposed, in which an off-angle is applied to the SiC bulk substrate. This method enable the crystal growth maintaining the repetitive structure of the crystal [18]. Although the advent of this method has enabled high-quality epitaxial growth, the number of epitaxial defects is larger than that in Si, and it is an ongoing challenge to reduce defects during crystal growth and improve its quality.

Fig. 1.4 Cristal structures of silicon carbide poly types [2].

Basal plane dislocations (BPDs) and stacking faults are important factors in the crystal quality of SiC. There are many threading screw dislocations (TSDs), threading edge dislocations (TEDs) and BPDs generated during crystal growth in 4H-SiC available in the commercial market today. During epitaxial growth, most of the BPDs are converted to harmless TEDs in the buffer layer. A few BPDs, however, are inherited in the epitaxial layer. Some of the BPDs change into stacking faults due to the recombination energy of electrons and holes injected into the epitaxial layer when the device operates in a bipolar mode. The expand of the stacking faults causes degradation of the conductivity of the epitaxial layer. Therefore, the operation of body diodes in MOSFETs can induce the degradation as well as bipolar devices such as PiN diodes. To solve this problem, it has been proposed to place another epitaxial buffer layer between the bulk substrate and the drift layer with a higher doping

concentration [19]. This buffer layer can suppress the injection of holes and the expansion of stacking faults.

Since the material properties of SiC can improve the trade-off between breakdown voltage and specific on-resistance  $R_{on}A$ , unipolar devices can be used in the voltage range where bipolar devices have been used. SiC-MOSFETs have been reported in the breakdown voltages range from 650 V to 10,000 V.

One of the features of SiC is that the MOS interface can be formed by thermal oxidation. However, the SiC/SiO<sub>2</sub> MOS interface has more defects than Si, and the effective invertinon channel mobility is lower than the bulk mobility, so improving the interface quality of SiC-MOSFETs has been an important problem since the beginning of SiC device development. The improvement of MOS interface on SiC has been reported in many studies [20, 21]. It has been reported that nitridation of the MOS interface improves the mobility of SiC, which is less than 10 cm<sup>2</sup>/Vs using conventional dry oxidation [22–24]. It has also been reported that MOS channels on the carbon-, a-, and m-faces with respect to the silicon-face can improve the inversion channel mobility to 100 cm<sup>2</sup>/Vs [20, 21].

In particular, since the a- and m-planes correspond to the perpendicular directions of the surface of SiC, these surfaces can be used to form channels for trench MOSFET structures. In addition, it has been reported that the channel mobility is greatly improved by using the (00–38) plane [24].

One of the solutions to the high channel resistance is to increase the channel density in the device structure. In particular, for 650 V and 1.2 kV class devices, the ratio of the channel resistance to total device resistance is high, the reduction of the cell pitch is effective in improving the channel density.

Vertical structures are the main type of SiC power MOSFETs being developed. The two different channel structures, planar and trench gate have been developed. Although the high critical electric field for the breakdown is the one of the advantage of SiC, the high electric field at pn junction increases the electric field on the gate oxide film of the MSOFETs. The high electric field causes breakdown and the decrease in lifetime of the gate oxide. Therefore, reducing the electric field of the gate oxide is an essential design topic for SiC power MOSFETs that require high reliability. Although silicon trench MOSFETs can achieve low ON-resistance due to the absence of JFET resistance, SiC-MOSFETs require a JFET-like structure to reduce the electric field of the oxide film.

#### **Planar MOSFET**

In the planar SiC MOSFET, the channel and source regions are formed under the gate oxide film on the semiconductor surface, similar to the planar structure of Si, as shown in Figure 1.5(a). On the other hand, it is difficult to form channels by impurity diffusion through an activation annealing because of low diffusion coefficient of impurities in SiC. To activate the implanted impurities, an activation annealing of 1500-degree C or higher is needed. Hence, a different process is required such as the formation of a gate oxide film after the activation annealing.

Fig. 1.5 Schematics of Silicon Carbide MOSFETs.

Shortening the channel length and shrinking the cell pitch is effective for reducing the channel resistance because of the low MOS channel mobility of SiC [25]. Palmour et al. have reported on planar MOSFETs in the 900 V to 15 kV range [28]. In this paper, the specific on-resistance of the planar MOSFET for a 1620 V device was reported of 2.7 m $\Omega$ cm<sup>2</sup>.

In comparison in the channel mobility between ion implantated p-base and epitaxial grown p-base, the channel mobility on the latter is higher [29]. Implanted and epitaxial

MOSFET (IEMOSFET) is proposed [30] as shown in Fig. 1.5(c). IEMOSFET is a planar MOSFET that is fabricated by forming an ion implantation region at the bottom of the p-base, followed by p-type epitaxial growth to form the channel region, and N-type implantation to form the JFET region. The low-mobility channel can be improved using a buried channel [31]. DIOMOS with the buried channel not only reduces channel resistance by improving the channel mobility but also suppresses a bipolar operation by optimizing the epitaxial channel structure [32].

The MOS channel on carbon-face can achieve several times higher mobility than that of Si-face. Using this property, DIMOSFET on the carbon-face can improve the trade-off between  $R_{on}A$  and breakdown voltage [26, 33].

The JFET resistance can be reduced by adding a current spreading layer with higher impurity concentration than that in the drift layer (see Fig. 1.5(d)). By applying this structure, the trade-off between on-resistance and breakdown voltage can be improved [27].

#### Trench MOSFET

The SiC trench MOSFET enables the channel length and cell pitch reduction. It can use the channel on a-plane and m-plane, which have higher mobility than that of silicon-face.

To reduce the electric field of the gate oxide of trench MOSFETs, various structures have been proposed. One of these is the double trench structure [34]. In this structure, trenches are formed across the gate trench and p-type regions are formed on the trench side wall using ion implantation. SiC-MOSFETs with the double trench structure show 1260 V breakdown voltage and 1.41 m $\Omega$ cm<sup>2</sup> whereas the planar MOSFETs show 2.3 m $\Omega$ cm<sup>2</sup> [34]. A significant improvement in characteristics have been achieved for 1.2kV class SiC MOSFETs with the double trench structure.

In another structure, a p-type region is formed at the bottom of the gate trench. The trench MOSFET with the bottom p-well structure has achieved 2.15 m $\Omega$ cm<sup>2</sup> with 652 V breakdown voltage [35] and 1.19 m $\Omega$ cm<sup>2</sup> with 1080 V break down voltage (this report excludes the substrate resistance) [36]. In the bottom p-well structure, if the bottom p-well is not connected to the source region, the avalanche tolerance decreases [37]. Therefore, it is necessary to connect the bottom p-well to the source region. However, due to the low activation rate of p-type impurities in SiC, the sheet resistance of the p-region is high, and it is necessary to provide a connection region to the source electrode at certain intervals, and optimization of these region is important in the viewpoint of reducing R<sub>on</sub> [35].

An asymmetric trench structure has been proposed. In this structure, the p-type region protecting the bottom of the gate oxide film is directly connected to the source region. The gate oxide electric field is suppressed by the asymmetric p-type region surrounding the gate trench. Although there is a disadvantage that half of the gate channel is disabled,  $3.5 \text{ m}\Omega \text{cm}^2$  has been achieved in a 1.2 kV class device. It can also operate stably during avalanche breakdown [38].

TEDMOS that reduces channel resistance by increasing channel density and channel mobility through the formation of trenches in the channel region has been reported [39].

A V-groove-type trench MOSFET of which channel is formed on the (03–38) plane has been proposed because the channel mobility on the crystal plane is higher than that on the (0001) plane [40, 41]. In order to mitigate the electric field at the bottom of the V-groove gate structure, a structure with a thicker oxide film and an embedded p-structure to reduce the electric field has also been reported [42].

#### **Super Junction**

In SiC MOSFETs, while the reduction of channel resistance has been the focus of technological development for a long time, the reduction of drift layer resistance has also been studied recently. In particular, the development of the super junction (SJ) structure, which is used in Si power MOSFETs, has progressed rapidly in recent years. Kosugi et al. have been reported that SiC-SJ structure can exceed the SiC limit by experiment [43]. In this study, a 5.5  $\mu$ m SJ structure was fabricated by two repetitions of MeV-accelerated ion implantation and epitaxial growth. The TEG showed a breakdown voltage of 1545 V and a drift layer resistance of 1.06 m $\Omega$ cm<sup>2</sup> was obtained.

By combining the trench structure and SJ structure,  $3.2 \text{ m}\Omega\text{cm}^2$  was achieved at a breakdown voltage of 1500 V [44]. Although the absolute value of  $R_{on}A$  is comparable to that of conventional structures, it has been reported that the temperature dependence of  $R_{on}$  can be reduced by adopting the SJ structure. A combination of SJ and V-groove structures can achieve  $R_{on}A = 0.63 \text{ m}\Omega\text{cm}^2$  and  $V_{bd} = 1170\text{V}$  [45]. Additionally, devices that exceed the SiC limit have been reported, such as a 6kV-class device with multi-epitaxial growth. The SJ structure is expected to be applied to devices up to 10 kV in the future because unipolar devices with high breakdown voltages are effective in taking advantage of the potential of SiC. For practical use, the cost increase due to multiple epitaxial growth is an issue. Epitaxial backfilling technology is also being studied [46], however, breakthroughs related to anisotropic growth conditions and doping concentration control, and improvements in process technology are desired in the future.

#### **Summary**

Figure 1.6 shows the trade-off relationship between  $R_{on}A$  and  $V_{bd}$  for MOSFETs and the theoretical limit for 4H-SiC [47]. The square represents the planar type, the triangle represents the trench type, and the circle represents the trench SJ type. At high voltages, the effect of the channel resistance is small, so the values are close to the SiC performance limit, while the increase due to the channel resistance is not negligible in the 600 V to 1200 V region. The trench structure has a higher potential than planar MOSFETs due to the effect of channel resistance reduction. Additionally, the SJ structure has been reported to exceed the SiC limit in recent years, and is expected to be commercialized in the future.

Fig. 1.6 The trade-off relationship between R<sub>on</sub>A and V<sub>bd</sub> of SiC MOSFETs.

#### 1.4 Summary

In this chapter, the history and the latest topics of the development of power device technologies are summarized, which are increasingly demanded by society to achieve zero  $CO_2$ emissions by 2050. In particular, the trends in the research and development of Si-IGBT and SiC-MOSFET are summarized. The characteristics of Si-IGBTs have been improved by optimizing the carrier distribution in the drift layer to reduce the switching loss, which is a trade-off between the reduction of conduction loss by the bipolar operation. Additionally, SiC-MOSFETs have enabled high breakdown voltage and low on-resistance by taking advantage of their high breakdown electric field, however, the high breakdown electric field in the semiconductor increases in the electric field of the gate oxide on SiC surface. Hence, the structure of the device must be designed to reduced the electric field of the gate oxide. Various structures have been proposed to achieve both reliability and low ON-resistance. This chapter summarizes the research on Planar, Trench type MOSFETs and SJ-MOSFETs.

### Chapter 2

# Oscillation phenomena in power semiconductor operation

As the application field of power electronics expands, it has become important to ensure the stable operation of the power devices under various operating conditions. In this chapter, the oscillation phenomenon, which is one of the most important issues for the stability of the power converter systems, is discussed. The oscillation on the device not only causes the destruction of the power device but also radiation noise. For this reason, the mechanism of the oscillations and how to prevent it have been studied from various aspects. In the conventional approaches, devices, packages, control circuits, and power circuits were designed individually. And focuses were optimization for their connection at the design phase of a power conversion system.

As the performance of power devices improves, however, individual optimization at each design phase does not allow to use the full potential of the device due to the accumulation of margins for characteristic fluctuations among components, response delay and reliability. To utilize the benefits of the performance-improved power devices, device, package, control circuit, and power circuit design parameters must be optimized simultaneously to prevent undesirable oscillation.

The major issues discussed for Si-IGBTs and SiC-MOSFETs are

- Ringing and oscillation during turn-on and turn-off in single device operation of Si-IGBTs,

- Ringing and oscillation phenomena during turn-on and turn-off of Si-IGBTs connected in parallel,

- Ringing and oscillation during turn-on and turn-off in single device operation of SiC-MOSFETs,

- Oscillation and ringing during turn-on and turn-off of SiC-MOSFETs connected in parallel,

- PETT oscillation at turn-off of Si-IGBTs,

- Oscillation during short-circuit operation of Si-IGBTs and Si-MOSFETs.

In this chapter, previous studies that investigated these oscillation phenomena will be reviewed.

#### 2.1 Circuit oriented oscillation

Si-IGBTs and SiC-MOSFETs work as amplifiers in power conversion circuits, and change the collector/drain current and voltage depending on the gate voltage. Additionally, MOS-FETs and IGBTs have feedback paths from the output to the input side because of their own parasitic capacitances (feedback capacitance, input capacitance, output capacitance), parasitic inductances and capacitances of the package. If the transfer functions of these feedback loops become unstable, the devices can cause oscillation.

When several switching devices are connected in parallel, the feedback signal may be returned to the gate via the devices connected in parallel [48, 49]. This feedback causes oscillation and ringing of output voltage and current of switching devices such as IGTBs and MOSFETs [50–52].

These oscillation and ringing sometimes destruct the power devices, and even if they do not, they increase the loss of power converter and cause EMI. Therefore, it is necessary to suppress these oscillation and ringing. Then oscillation phenomena in various operating conditions, such as turn-on, turn-off, and short-circuit operation, have been studied [51–57].

Oscillation phenomenon in the hybrid module in which Si-IGBT and SiC-SBD are connected in parallel, during a turn-on operation has been reported [51]. It has been reported that the presence of the oscillation was determined by the gate resistance and parasitic inductance of the Si-IGBT and capacitance of the SiC-SBD. Then it was necessary to reduce the parasitic inductance of the module in order to suppress the oscillation without increasing the device loss [51].

In SiC-MOSFETs, self-sustained oscillation during switching operation has been reported [53, 56, 58]. It is shown that several feedback paths can cause the self-sustain oscillation [58]. The drain and source inductance, gate resistance, and the ratio of drain capacitance to gate capacitance are an important parameter to understand the self-sustained oscillation [56].

#### 2.2 Device oriented oscillation

In this section, the oscillation phenomena caused by the internal characteristics of the power devices will be discussed.

Si-IGBTs connected in parallel show a current oscillation between the IGBTs at high collector voltage condition [59]. In order to analyze this oscillation phenomenon of IGBTs, negative gate capacitance has been proposed as an oscillation mechanism [59, 60]. The existence of negative gate capacitance is shown by device simulation using TCAD based on the derived equivalent circuit, and then the stability of oscillation is analyzed analytically.

In IGBTs, plasma extraction transit time oscillation (PETT oscillation) is sometimes observed during a turn-off [61–63]. This phenomenon causes the oscillation of tens to hundreds of MHz in the current and voltage during the tail current flow during the turn-off of the IGBT.

This phenomenon is caused by a negative resistance due to the transfer delay of holes injected from the electron-hole plasma edge to the source electrode [61]. A packet of holes injected from the electron-hole plasma boundary at a certain time moves through the depletion layer over a certain amount of time, and the oscillation frequency can be estimated from the migration speed  $v_s$  and the depletion layer width W.

$$f = \frac{3v_s}{4W}.$$

(2.1)

In order to estimate the specific charge transfer, information on the depletion layer, electron and hole plasma states at the external voltage in the oscillating state is required. For this reason, TCAD transient simulation has been used to simulate the internal state of the device when the external voltage is modulated near the oscillation frequency. This method has been used to estimate the chip-to-chip oscillation state [62], and to estimate the oscillation state inside the module [63].

Particularly in bipolar devices such as Si-IGBTs, impact ionization is caused by an increase in the electric field in the drift layer during the turn-off, and this can lead to a continuous oscillation phenomenon. This is known as impact ionization avalanche transit time (IMPATT) oscillation, and its suppression is one of the important themes in IGBT [64–66].

#### 2.2.1 Oscillation phenomena in short-circuit operation

Stable operation of power devices during the short-circuit (SC) protection is an important theme. The stable operation of Si-IGBTs and SiC-MOSFETs under SC type I, II, and III conditions has been studied [67–70].

The di/dt during SC type I is determined by the switching device itself, while that of SC type II is determined by the parasitic inductance of the short-circuit loop and the DC link voltage [69]. Therefore, the peak value of SC type II current becomes larger than that of SC type I due to the increase in the gate voltage caused by the displacement current. The experimental waveform shows that oscillation occurs during SC type II [69].

The oscillation between parallel-connected IGBTs during turn-on has been reported [57].

## 2.3 Conventional approaches to solve the problem and their limit

In order to understand these oscillation phenomena, various studies have been reported on the derivation of equivalent circuits and the analysis of oscillation on the equivalent circuits. There are three major approaches to deriving the equivalent circuit.

The first approach is to determine the circuit parameters of the equivalent circuit by fitting the experimental results. Parameters such as parasitic inductance are determined to reproduce the changes in voltage and current during switching in the experiment.

The second approach is to determine the parameters based on actual measurements. For the measurements, a method using impedance and S-parameter measurements have been proposed [53, 71, 72]. In the method using impedance measurement, the parasitic parameters of each signal terminal are assumed to be the series parasitic parameters of the LCR and calculated from the results of terminal-to-terminal impedance measurements [53]. To improve the precision and accuracy of the measurements of the circuit parameters, a measurement technique using S-parameters has been proposed [71, 72]. This method can avoid the precision degradation caused by the coupling between the floating terminal and the ground when measuring the impedance of power devices. The package impedance can be calculated from the measurement results of each combination of the module terminals, and the S-parameter measurement can be used to model the internal parameters of the package more accurately and easily than the conventional impedance measurement.

The third approach is to calculate the equivalent circuit model based on simulation, which generally uses the finite element method and electromagnetic field analysis [73]. In this method, self and mutual inductance and resistance of copper patterns, terminals, bonding wires and bus-bars are calculated in some current flow conditions.

Once the equivalent circuit is obtained, the operating conditions are analyzed. Several methods are used for this analysis, including the method for determining the time dependence by analytical calculation of small-signal equivalent circuits, the method for perform-

ing stability analysis analytically from the frequency dependence [48, 49], and the method of determining the stable circuit parameters by calculating the time-dependent waveform and frequency dependence using SPICE simulation [49].

In these approaches, MOSFET or IGBT chips are treated as a small-signal model. The small-signal models of the power devices are calculated by parameter fitting to the measured curve forms or simulation calculated curve forms [49].

The other approach is to use technology computer-aided design (TCAD) tools for timedependent simulation. TCAD simulation using mixed-mode techniques can compute timedependent behavior of the devices and circuits simultaneously. This is a useful method to compute oscillation phenomena [67, 74]. However, this method has limited applications because it is difficult to converge to the correct state near the oscillation state and the CPU time tends to be long.

#### 2.4 Objective of this study

Oscillation phenomena can be caused by the switching devices with the connected circuits and the internal behavior of the devices. In the conventional approach, circuits and devices are discussed separately, and the phenomena caused by the combination of the both cannot be fully discussed.

As shown in this chapter, ensuring the stable operation of IGBTs and MOSFETs has been a longstanding issue in power devices, and various studies have been conducted. TCAD simulation is a powerful tool for understanding the oscillation phenomena because it can calculate the internal state of the device and the behavior of the circuit simultaneously. However, it requires a large amount of computational time, and its use is limited for parameter optimization. Generally, the device model is replaced by an approximate small-signal model, and then the parameters are optimized by SPICE simulation or analytical calculation.

Additionally, the coupled analysis with the internal simulation of the device requires a large amount of computation time. Although it is possible to analyze the origin of the oscillation phenomenon, the computation cost is too large to optimize the devices and circuits design parameters.

The purpose of this study is to develop a method for parameter optimization based on the TCAD simulation results. This will provide a unified method for the optimization of devices and circuits, and contribute to the realization of technology that can maximize the characteristics of power devices.

### 2.5 Summary

In this chapter, the oscillation phenomenon and mechanism of Si-IGBTs and SiC-MOSFETs are reviewed. The methods on analyzing these physical phenomena are also summarized. In this study, a novel design method is proposed to discuss the oscillation phenomena by incorporating the internal behavior of the device and circuit parameters.

### Chapter 3

# Theory of oscillation analysis with a signal flow graph and a scattering parameter

In this study, an analysis based on a scattering parameter (S-parameter) is proposed to treat the oscillation phenomena as discussed in the previous chapter. Impedance measurements of devices and circuits are generally difficult at high frequency because open and short calibration measurements are difficult at high frequency. S-parameter solves this difficulty in high-frequency measurements by using a characteristic impedance termination. Additionally, once the frequency dependence of a circuit element is determined, the internal behavior of the circuit element can be treated as a black box. It is possible to handle from the internal operation of the switching devices to the operation of the circuit system. In this chapter, the general treatment of the S-parameter is briefly described, and then the theoretical method for calculating the oscillation condition based on a TCAD device model is discussed.

### **3.1** General theory of Scattering parameter (S-parameters)

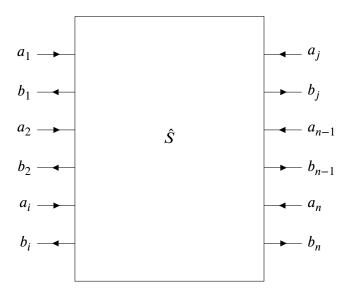

The figure 3.1 illustrates a multiport network with incident power waves and reflected power waves at its ports.

The incident power waves of *i*-th port is defined as

$$a_{i} = \frac{1}{2\sqrt{Z_{0i}}} \left( V_{i} + Z_{0i}I_{i} \right), \qquad (3.1)$$

where  $Z_{0i}$  is the characteristic impedance of *i*-th port and  $V_i$  and  $I_i$  are the voltage and current of *i*-th port. The reflected power waves also defined as

$$b_i = \frac{1}{2\sqrt{Z_{0i}}} \left( V_i - Z_{0i} I_i \right).$$

(3.2)

The input voltage and current are represented using  $a_i$  and  $b_i$  as

$$V_{i} = \sqrt{Z_{0i}} \left( a_{i} + b_{i} \right), I_{i} = \frac{1}{\sqrt{Z_{0i}}} \left( a_{i} - b_{i} \right).$$

(3.3)

Fig. 3.1 N-port network and incident power waves and reflected power waves on the ports.

Matrix elements of the S-parameter are defined in relation to these incident and reflected power waves as

$$\vec{b} = \hat{S}\vec{a},\tag{3.4}$$

where  $\vec{a}$  and  $\vec{b}$  are incident power wave vector and reflected power vector which are expressed as

$$\vec{a} = \begin{pmatrix} a_1 \\ a_2 \\ \vdots \\ a_i \\ \vdots \\ a_{n-1} \\ a_n \end{pmatrix}$$

(3.5)

and

$$\vec{b} = \begin{pmatrix} b_1 \\ b_2 \\ \vdots \\ b_i \\ \vdots \\ b_{n-1} \\ b_n \end{pmatrix},$$

(3.6)

respectively.

The matrix components of the S-parameter connected to N-port network are defined as follows:

$$S_{ii} = \frac{b_i}{a_i} \bigg|_{\substack{a_k = 0 \\ k = 1, 2, \dots, N}},$$

(3.7)

$$S_{ji} = \frac{b_j}{a_i} \Big|_{\substack{a_k = 0 \\ k = 1, 2, \dots, N}}^{a_k = 0}.$$

(3.8)

If an impedance at a port *i* is defined as

$$Z_i = \frac{V_i}{I_i},\tag{3.9}$$

a reflect coefficient  $\Gamma$  of the port *i* is written as