# 2.4 GHz wireless sensor network for smart electronic shirts

J. P. Carmo<sup>\*1</sup>, P. M. Mendes<sup>2</sup>, C. Couto<sup>2</sup>, J. H. Correia<sup>2</sup> <sup>1</sup>Polytechnic Institute of Braganca, Campus Santa Apolonia, 5301-857, Braganca, Portugal <sup>2</sup>University of Minho, Dept. Industrial Electronics

# ABSTRACT

This paper presents a wireless sensor network for smart electronic shirts. This allows the monitoring of individual biomedical data, such the cardio-respiratory function. The solution chosen to transmit the body's measured signals for further processing was the use of a wireless link, working at the 2.4 GHz ISM band. A radio-frequency transceiver chip was designed in a UMC RF 0.18 µm CMOS process. The power supply of the transceiver is 1.8 V. Simulations show a power consumption of 12.9 mW. Innovative topics concerning efficient power management was taken into account during the design of the transceiver.

Keywords: Wireless sensors networks, smart textiles, RF transceivers

# 1. INTRODUCTION

Today, the link between textiles and electronics is more realistic than ever. An emerging new field of research that combines the strengths and capabilities of electronics and textiles into one: electronic textiles, or e-textiles is opening new opportunities. E-textiles, also called smart fabrics, have not only wearable capabilities like any other garment, but also have local monitoring and computation, as well as wireless communication capabilities. Sensors and simple computational elements are embedded in e-textiles, as well as built into yarns, with the goal of gathering sensitive information, monitoring vital statistics, and sending them remotely (possibly over a wireless channel) for further processing [1].

For integration into everyday clothing, electronic components should be designed in a functional, unobtrusive, robust, small, and inexpensive way. Therefore, small single-chip microelectronic systems rather than large-scale computer boxes are a promising approach. The e-shirt's goal is the monitoring of the cardio-respiratory function. This makes it able to recognize qualitatively and quantitatively the presence of respiratory disorders, both during wake and sleep-time in free-living patients with chronic heart failure, providing clinical and prognostic significance data. With the ongoing progress of miniaturization, many complex and large electronics systems will soon be replaced by tiny silicon microchips measuring just a few square millimeters. Your shirt, coat or sweater, is the device. Conductive fibers woven into the fabric using standard textile techniques carry power sensors, actuators, and microcontrollers embedded in the cloth. Software controls the communications inside the on-fabric network and can send radios signals using Bluetooth or any flavour of the IEEE 802.11 wireless standard to PCs and PDAs, and over Internet. Manufacturers can mix and match sensors, processors, and communications devices that plug into knitted or woven garments made from cotton, polyester, or blends. These devices have the look and feel of typical garments and, after the attachments are unplugged, can be tossed into the washing machine. Applications are astoundingly diverse and following examples will demonstrate the implementation of microelectronics components into clothes and textiles structures in a reliable and manufacturing way. Researchers at Tampere University of Technology, Finland, developed a machine-washable jacket, vest, trousers, and two-piece underwear set for snowmobilers. The jacket is embedded with a GSM chip, sensors monitoring position, motion, and temperature. If a crash occurs, the jacket automatically detects it and sends a distress message to emergency medical officials via SMS. Infineon Technologies, Germany, unveiled a carpet that can detect motion – of unwanted intruders, for example – and also light the way to exits in the event of a fire [3].

\*jcarmo@ipb.pt; phone +351-273-303000; fax +351-273-313051;

The carpet is woven with conductive fibers and studded with pressure, temperature, or vibration sensors chips, microcontrollers and light-emitting-diodes (LEDs).

This paper presents a 2.4 GHz wireless sensor network for smart electronic shirts. In order to send the acquired information from sensors in the smart electronic shirt, it was designed in a UMC RF 0.18 µm CMOS process, a RF transceiver operating in the 2.4 GHz ISM band. This process has a poly and six metal layers, allowing the use of integrated spiral inductors (with a reasonable quality factor), high resistor value (a special layer is available) and a low-power supply of 1.8 V. The use of this technology, allows the development of a complete systems-on-a-chip, cutting in the final costs.

# 2. TRANSCEIVER

Typically, a microsensor node in a wireless network performs several functions, including:

- sensing environmental physical parameters,

- processing the raw data locally to extract characteristic features of interest,

- storing this information momentarily, and

- using a wireless link to transmit the information to its neighbours.

Without proper design, communication will increase network power consumption significantly because listening and emitting are power-intensive activities [4]. Thus, in order to optimise power consumption, it was included in the design of the RF transceiver, the use of control signals. With these control signals it is possible to enable and disable all the transceiver subsystems. These signals allows for example to switch off the receiver when a RF signal is being transmitted, to switch off the transceiver in sleeping mode when neither RF signals are being transmitted, nor being received.

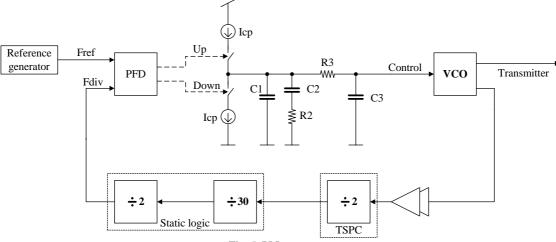

#### 2.1 Transceiver architecture

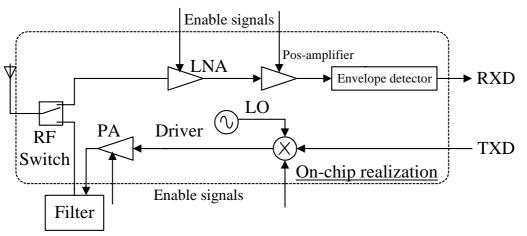

The transceiver has a low-noise amplifier (LNA) that provides a 50  $\Omega$  input impedance, using a tuned load to provide high selectivity. The amplified RF signal is downconverted to the baseband with an envelope detector. Internal oscillator is a phase-locked loop (PLL) working at 2.4 GHz, with a stable crystal oscillator reference of 20 MHz. An internal antenna-switch was included in the design. The whole transceiver structure is illustrated in Fig. 1.

Fig. 1. The block schematic of the transceiver.

#### 2.2 Antenna-switch

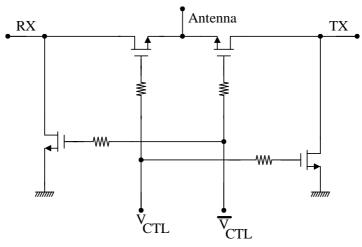

An internal antenna-switch makes this transceiver a true complete system-on-a-chip. The antenna-switch connects the antenna to one of the receiver or transmitter path, that are connected to the RX and TX ports, respectively. The signal  $V_{CTL}$  selects the port to be connected to the antenna. The isolation between non-connected ports must be high. In order to have a

power efficient transceiver without degrading its sensitivity, the losses in the switch must be low. The next table shows the simulation results for the antenna-switch. These results are much better, compared with reference values [6].

Fig. 2. The antenna-switch [6].

| S parameters                                                 | V <sub>CTL</sub> state |

|--------------------------------------------------------------|------------------------|

| $S_{RX,Antenna} = -1.32 \text{ dB}$                          | On                     |

| $S_{RX,Antenna} = -41.51 \text{ dB}$                         | Off                    |

| $S_{Antenna,TX} = -41.50 \text{ dB}$                         | On                     |

| $S_{Antenna,TX} = -1.32 \text{ dB}$                          | Off                    |

| $S_{RX,TX} = -43.44 \text{ dB}$                              | On                     |

| $S_{RX,TX} = -43.54 \text{ dB}$                              | Off                    |

| T-11-1 Circultated Constructions for the entering consistent |                        |

Table 1 - Simulated S parameters for the antenna-switch.

#### 2.3 Receiver

#### 2.3.1 Low-noise amplifier

The low-noise amplifier (LNA) is the first gain stage in the receiver path. The noise figure (NF) of the LNA is a measure of the degradation of the signal-to-noise ratio (SNR) at the output of the LNA, compared to that at the input. Another main performance parameter is its gain. The signal should be amplified as much as possible, with hardly lowering the SNR. This is achieved with the best noise figure.

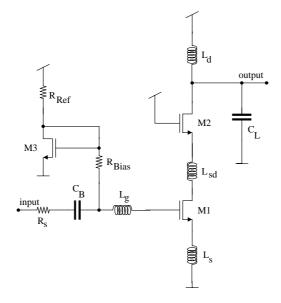

As illustrated in Fig. 3, the LNA is an inductively degenerated common source amplifier [7,8]. This makes the input impedance at 2.4 GHz equal to 50  $\Omega$ , for matching with antenna switch. Cascoding transistor M<sub>2</sub> is used to increase the gain, to better isolate the output from the input and to reduce the effect of M<sub>1</sub>'s C<sub>gs</sub>. Transistor M<sub>3</sub> is used to bias the transistor M<sub>1</sub>, and its width is a small fraction of M<sub>1</sub>'s width, to minimise the power overhead of the bias circuit.

A source inductance  $L_s=1.5$  nH, a gate inductance  $L_g=21.1$  nH and an inductance  $L_{sd}=10$  nH, placed between the source of  $M_2$  source and the drain of  $M_1$  were used in the design. The inductance  $L_{sd}$  helps to overcome the problem that happens due to the bond pad effect. These effect appears due to the addition of the inductance in the wire, used to connect the pads in the die circuit to the PCB, with a RF substrate. Simulations show a gain of 20 dB, a return loss at the input of -23.6 dB and a noise figure NF=0.71 dB (F=1.18). Simulations also show a stability factor K=1.6 (greater than the unity), that makes this amplifier unconditionally stable.

As cited before, the transceiver must have a power efficient management, thus in the idle or transmitting modes, the LNA is disabled by switching off the bias circuitry. The same principle applies to all subsystems of the transceiver, being no more cited on this paper.

Fig. 3. LNA circuit [7,8].

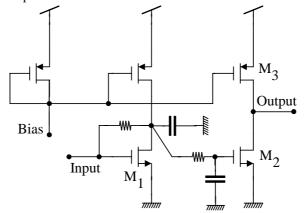

### 2.3.2 Envelope detector

Figure 4 shows the envelope detector schematic. Basically, the idea is that an increasing input amplitude implies a decrease in the transistor  $M_1$  gate voltage (in order to keep branch current constant) what means a decrease in the gate voltage of the transistor  $M_2$  (after filtering), thus decreasing the transistor  $M_2$  current itself. When this current reach a point where cancels with the transistor  $M_3$  mirror current, then the output capacitance starts to discharge and the output voltage goes to high. The minimum voltage amplitude at the input is 70 mV.

Fig. 4. The envelope detector, and voltage  $V_{\text{in}}$  at the input and voltage  $V_{\text{out}}$  at the output.

# 2.4 Transmitter

### 2.4.1 Phase-locked loop

As depicted in Fig. 5, the PLL has a reference generator circuit with a crystal based oscillator at 20 MHz, followed by a Phase-Frequency Difference Circuit (PFD) without dead zone, a current steering charge pump (CP), a third order passive

582 Proc. of SPIE Vol. 5836

filter. The passive section output is connected to the Voltage Controlled Oscillator (VCO), that generates the desired frequency of 2.4 GHz. Finally, in order to get the 2.4 GHz, this frequency must be divided by 120 and connected to the PFD again, closing the loop.

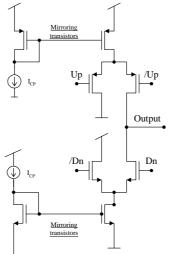

Fig. 5. PLL structure.

The charge pump is a current steering, with Up and Down currents  $I_{Up}=173 \ \mu A$  and  $I_{down}=178 \ \mu A$ , with a detector gain constant  $K_{\phi}=175 \ \mu A/2\pi$  rad. This circuit avoids the conventional problem in charge pumps, that limits the opening and closing of current sources, in fact, in spite of being switched, the current is routing from the load, to a alternative path, and from that path to the load.

Fig. 6. The currents steering charge-pump.

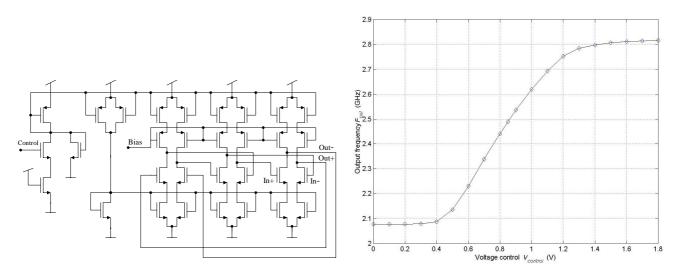

In order to saving on-chip area, it was used a current starved ring oscillator [9] to implement the VCO, rather than a tuned LC oscillator. This VCO has the advantage to control the full range [0, 1.8 V], providing a frequency range of

[2.016, 2.757 GHz], with a tuning constant  $K_{VCO}$ =876.6 MHz/V, calculated in the linear working range. The structure of this VCO is shown in Fig. 7.

Fig. 7. Voltage controlled oscillator [9] and the working characteristic.

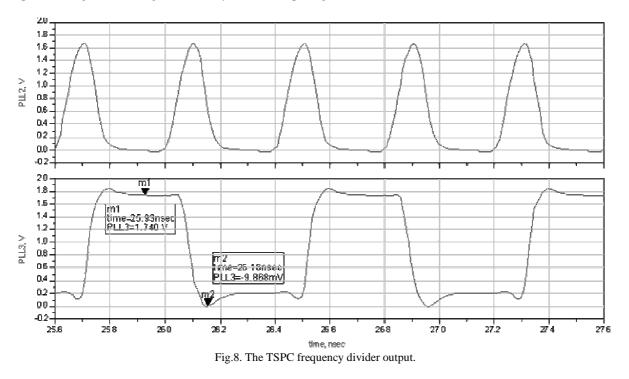

The 2.4 GHz frequency is achieved with a 20 MHz reference, dividing it by 120. This is done with a cascade constituted by one half divider implemented with true single phase clock (TSPC) logic, one divider by 30, followed by a toggle flip-flop. As depicted in Fig. 8, TSPC logic works only when the input signals are rail-to-rail [10].

#### 2.4.2 Power amplifier

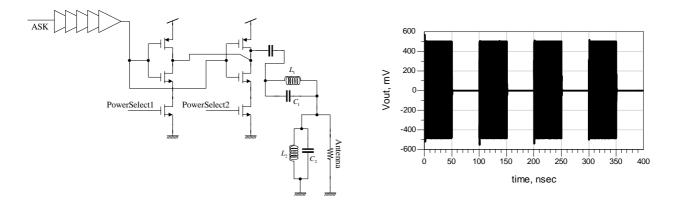

The function of the power amplifier is to provide a transmitted signal with an appropriated output power. The power amplifier has a cascade of five inverters, in order to drive the ASK output signal to the input of power amplifier. The Fig. 9 shows the power amplifier, where it is possible to select between none or three different output powers. In that figure, the network  $L_1$ - $C_1$  eliminates the strong second harmonic of the carrier, while the network  $L_2$ - $C_2$ , is tuned to carrier frequency. The maximum simulated output power is 1.28 mW.

Fig. 9. The power amplifier and simulated output voltage at the antenna, for the maximum power selected.

# 3. CONCLUSIONS

A 2.4 GHz wireless sensor network for smart electronic shirts was presented in this paper. It is intended to use the smart shirt to monitor the cardio-respiratory function. The acquired information is to be transmitted for further processing by a low-power low-voltage RF transceiver working at the 2.4 GHz ISM band. Simulations show a total power consumption of 12.9 mW, for the transceiver. This makes our transceiver suitable for low power applications.

#### REFERENCES

- 1. D. Marculescu et al., Electronic Textiles: A Platform for Pervasive Computing, Proceedings of the IEEE, Vol. 91, Nº 12, pp. 1995-2018, December 2003.

- 2. IEEE Spectrum magazine, Ready to ware, pp.29-32, October 2003.

- B.A. Floyd, Hung Chih-Ming; K.K O, "Intra-chip wireless interconnect for clock distribution implemented with integrated antennas, receivers, and transmitters", IEEE Journal of Solid-State Circuits, Vol. 37, N

<sup>o</sup> 5, pp. 543–552, May 2002.

- 4. C. C. Enz, A. El-Hoiydi, J. Decotignie, V. Peiris, "WiseNET: An ultralow-power wireless sensor network solution", IEEE Computer, Vol. 37, Nr. 8, pp. 62-70, August 2004.

- S. Cho, A. P. Chadrakasan, "A 6.5-GHz energy-efficient BFSK modulator for wireless sensor applications", IEEE Journal of Solid-State Circuits, Vol. 39, N° 5, pp. 731-738, May 2004.

- M. Ugajin, A. Yamagishi, J. Kodate, M. Harada, T. Tsukahara, "A 1-V CMOS SOI Bluetooth RF Transceiver Using LC-Tuned and Transistor-Current-Source Folded Circuits", IEEE Journal of Solid-State Circuits, Vol. 39, N

<sup>o</sup> 4, pp. 569-576, April 2004.

- D. Shaeffer, T. Lee,, "A 1.5-V, 1.5-GHz CMOS low noise amplifier", IEEE Journal of Solid-State Circuits, Vol. 32, N° 5, pp. 745-759, May 1997.

- 8. E. Kunz, S. Parke, "2.4 GHz high gain low power narrowband low-noise amplifier (LNA) in 0.18 um TSMC CMOS", in Workshop on Microelectronics and Electron Devices, 2004, pp. 52-54.

- 9. B. Razavi, K. Lee, R. Yan, "Design of high-speed, low-power frequency dividers and phase-locked loops in deep submicron CMOS", IEEE Journal of Solid-State Circuits, Vol. 30, N° 2, pp. 101-108, February 1995.

- 10. J. Yuan, C Svensson, "High speed CMOS circuit technique", IEEE Journal of Solid-State Circuits, Vol. 24, N° 2, pp. 62-70. February 1989.

- 11. S. Pellerano, S. Levantino, C. Samori, A. Lacaita, "A 13.5 mW 5-GHz frequency synthesizer with dynamic-logic frequency divider", IEEE Journal of Solid-State Circuits, Vol. 39, N° 2, pp. 378-383, February 2004.

- 12. Q. Huang, R. Rogenmoser, "Speed optimization of edge-triggered CMOS circuits for gigahertz single-phase-clock", IEEE Journal of Solid-State Circuits, Vol. 31, N° 3, pp. 456-465, March 1996.

- 13. F. Gardner, "Charge Pump PLL", IEEE Transactions on Communications, Vol. 28, № 11, pp. 1849-1859, November 1980.