# Integrated Chip-Size Antenna for Wireless Microsystems: Fabrication and Design Considerations

P.M. Mendes, A. Polyakov<sup>\*</sup>, M. Bartek<sup>\*</sup>, J.N. Burghartz<sup>\*</sup>, J.H. Correia

Dept. of Industrial Electronics, University of Minho, Portugal \*Lab. of ECTM/DIMES, Delft University of Technology Phone: +351-253510190 Fax: +351-253510189 E-mail: paulo.mendes@dei.uminho.pt

*Summary:* This paper reports on fabrication and design considerations of an integrated folded shortedpatch chip-size antenna for applications in short-range wireless microsystems and operating frequency of 5.7 GHz. Antenna fabrication is based on wafer-level chip-scale packaging (WLCSP) techniques and consists of two adhesively bonded glass wafers with patterned metallization and through-wafer electrical interconnects. Two different fabrication options based on via formation in glass substrates using excimer laser ablation or powder blasting are presented.

*Keywords:* chip-size antenna, WLSCP, wireless microsystem, laser ablation, powder blasting. *Category:* 8, 9, 2.

## **1** Introduction

Monolithic solutions to small-size distributed systems equipped with short-range wireless communication capabilities will highly be facilitated if cheap and easy-to-use 'on-chip' or 'in-package' solutions would be available. A chip-size antenna is the key element in order to obtain a fully integrated wireless microsystem on a single chip. On-chip integration requires the antenna to be small and to be realised on a low-loss substrate compatible with integrated circuits operation and fabrication [1, 2]. A folded shorted-patch antenna (FSPA) can be used as a compact solution for the on-chip antenna integration [3]. Due to its rather complicated structure, its implementation is not trivial. In this paper, design and process considerations for on-chip implementation of an FSPA are presented.

#### 2 Antenna Design

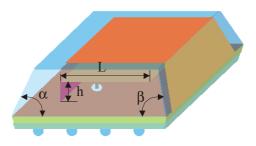

The proposed, on-chip integrated, folded shortpatch antenna is shown in Fig. 1. It consists of three horizontal metal sheets that are electrically connected by two vertical metal walls. All this is embedded in a dielectric substrate having certain electrical permittivity and dielectric losses. These two parameters together with the antenna geometry and its actual dimensions will determine its radiation characteristics and overall performance.

For the best performance, the metal sheets should have minimum resistivity and the dielectric should be a low-loss material with high electrical permittivity. This allows achieving small antenna dimensions and high efficiency.

At frequencies above 1 GHz, glass becomes a very attractive option. Its main advantages are low losses, reasonable  $\varepsilon_r$ , availability in a form of wafers with any required thickness and diameter, and last but not least low cost. There is also sufficient experience in processing of glass wafers from MEMS and WLCSP applications [4].

Fig. 1: Proposed folded shorted-patch antenna.

An FSPA can be realised as a stack of two glass wafers with patterned metal layers and through-wafer interconnects in the form of metallized vias. High antenna efficiency requires thicker substrates (>300  $\mu$ m) and therefore high aspect ratio vias in glass are required.

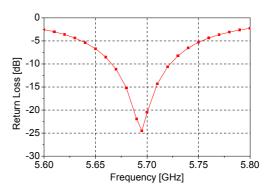

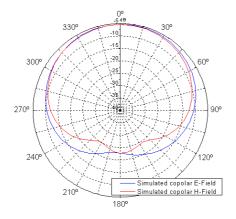

Fig. 2 shows return loss of the proposed FSPA, considering the use of two stacked, 500  $\mu$ m thick Corning Pyrex #7740 glass substrates and dimensions of 4.5x4x1 mm<sup>3</sup>. The simulated radiation efficiency of 60 % and bandwidth of 50 MHz at -10 dB return loss have been achieved. The predicted far-field radiation diagrams (Fig. 3) shows that the power is being mainly radiated upwards and the antenna interference with backside devices is minimized.

Fig. 2: Simulated return loss of the FSPA.

Fig. 3: Simulated co-polar far-field gain patterns for FSPA operating at 5.695 GHz.

## **3** Fabrication

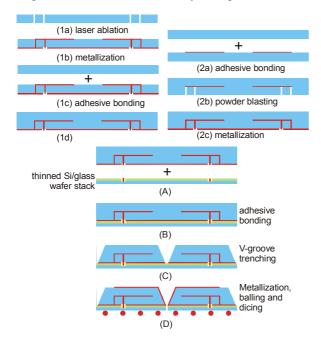

We have proposed and currently investigate two different fabrication options for realization of an onchip integrated FSPA. Both are based on WLCSP techniques and are schematically shown in Fig. 4. The first one is based on laser drilling of high aspect ratio vias in glass with subsequent electroless plating and patterning of the bottom and middle Cu layers, followed by glass-to-glass adhesive bonding. The second fabrication option starts with deposition and patterning of Cu layer on a glass wafer followed by adhesive bonding to the upper glass wafer. The encapsulated middle Cu patch is then reached by powder blasting followed by plating and patterning of the bottom Cu layer. In both cases, the fabrication sequence continues by bonding to a temporary carrier and a V-groove trenching using shaped dicing blade [5]. Finally the upper Cu layer is deposited and patterned. The processing sequence is completed by singulation into individual dies by dicing.

Fig. 4: Schematic fabrication sequence using laser ablated vias (left); using powder blasted vias (right).

### 3.1 Laser ablation

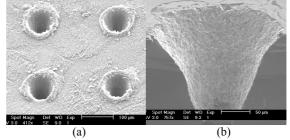

Glass starts to loose its transparency in the UV region and therefore excimer lasers are needed for glass ablation to form through wafer vias. Due to the limitations of the focusing system, direct ablation of the required pattern is not possible and an intermediate hard mask between the laser beam and glass wafer was required. Fig. 5a shows SEM photograph of 80  $\mu$ m diameter vias formed in a 500  $\mu$ m thick glass wafer using a 193 nm excimer laser. Note that no protection layer has been applied and therefore contamination on the wafer surface resulting from the ablation process is clearly visible.

Fig. 5: SEM picture of (a) 80 µm circular vias in a 500 µm glass substrate fabricated using a 193 nm excimer laser; (b) cross-section of a 200 µm diameter powder-blasted via.

#### **3.2 Powder blasting**

Powder blasting is a widely used method in glass processing. Its main disadvantage is that the typical side-wall slope is about 75° which results in rather limited achievable aspect ratio of powder-blasted vias of ~2.5:1. Fig. 5b shows a cross sectional SEM photograph of a powder-blasted, 200  $\mu$ m diameter via in a 240  $\mu$ m thick substrate.

#### 4 Conclusions

This work demonstrates that folded shorted-patch antennas operating at 5-6 GHz are feasible using WLSCP techniques and suitable for microsystems aiming wireless short-range links. A folded shortedpatch antenna was designed and possible fabrication options were analysed.

#### Acknowledgements

The authors would like to thanks the Portuguese Foundation for Science and Technology (POCTI / ESE / 38468 / 2001 and SFRH/BD/4717/2001) and EU (IST-2000-10036) for funding this work.

### References

[1] P.M. Mendes, et al., Integrated 5.7 GHz Chip-Size Antenna for Wireless Sensor Networks, *Transducers'03*, Boston, USA, June 8-12, 2003.

[2] P.M. Mendes, et al., Design and Analysis of a 6 GHz Chip Antenna on Glass Substrates for Integration with RF/Wireless Microsystems, *IEEE APS Int. Symp.*, Columbus, Ohio, USA, June 22-27, 2003.

[3] R.L. Li, et al., Novel Small Folded Shorted-Patch Antennas, *IEEE APS Int. Symp.*, Vol. 4, pp. 26-29, 2002.

[4] A. Polyakov, et al., Processability and Electrical Characteristics of Glass Substrates for RF WLCSP, *ECTC* 2003, New Orleans, USA, May 27-30, 2003.

[5] http://www.shellcase.com/