### UvA-DARE (Digital Academic Repository)

### Improving application timing predictability and caching performance on multicore systems

Xiao, J.

Publication date 2019 Document Version Final published version License Other

Link to publication

### Citation for published version (APA):

Xiao, J. (2019). *Improving application timing predictability and caching performance on multicore systems*. [Thesis, fully internal, Universiteit van Amsterdam].

### General rights

It is not permitted to download or to forward/distribute the text or part of it without the consent of the author(s) and/or copyright holder(s), other than for strictly personal, individual use, unless the work is under an open content license (like Creative Commons).

### **Disclaimer/Complaints regulations**

If you believe that digital publication of certain material infringes any of your rights or (privacy) interests, please let the Library know, stating your reasons. In case of a legitimate complaint, the Library will make the material inaccessible and/or remove it from the website. Please Ask the Library: https://uba.uva.nl/en/contact, or a letter to: Library of the University of Amsterdam, Secretariat, Singel 425, 1012 WP Amsterdam, The Netherlands. You will be contacted as soon as possible.

Improving Application Timing Predictability and Caching Performance on Multi-core Systems

• JUN XIAO •

00

οd

**O**

0

Improving Application Timing Predictability and Caching Performance on Multi-core Systems

JUN XIAO

ò

0

P

مر

60

$\overline{\mathbf{9}}$

# Improving Application Timing Predictability and Caching Performance on Multi-core Systems

Jun Xiao

# Improving Application Timing Predictability and Caching Performance on Multi-core Systems

ACADEMISCH PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Universiteit van Amsterdam op gezag van de Rector Magnificus prof. dr. ir. K.I.J. Maex ten overstaan van een door het College voor Promoties ingestelde commissie, in het openbaar te verdedigen in de Aula op 18 oktober 2019, te 11:00 uur

door

Jun Xiao

geboren te Jiangxi

### Promotiecommissie

| D           |   |

|-------------|---|

| Promotor    | ٠ |

| 1 IOIIIOIOI | ٠ |

|                | Prof. dr. ir. Cees T. A. M. de Laat | Universiteit van Amsterdam            |

|----------------|-------------------------------------|---------------------------------------|

|                | Dr. Andy D. Pimentel                | Universiteit van Amsterdam            |

| Overige leden: |                                     |                                       |

|                | Prof. dr. Sebastian Altmeyer        | University of Augsburg                |

|                | Prof. dr. Giuseppe Lipari           | University of Lille                   |

|                | Dr. John Shalf                      | Lawrence Berkeley National Laboratory |

|                | Prof. dr. Rob van Nieuwpoort        | Universiteit van Amsterdam            |

|                | Prof. dr. Cees G.M. Snoek           | Universiteit van Amsterdam            |

|                | Dr. Clemens Grelck                  | Universiteit van Amsterdam            |

|                | Dr. Ana Lucia Varbanescu            | Universiteit van Amsterdam            |

|                |                                     |                                       |

Faculteit der Natuurwetenschappen, Wiskunde en Informatica

The research was supported by NWO under project number 12696 (CPS-4).

Copyright © 2019 Jun Xiao, Amsterdam, The Netherlands Cover by Shichen Li Printed by Ipskamp Printing, Enschede

ISBN: 978-94-028-1739-3

### Acknowledgements

It is about four and half years since I started working towards my PhD in March, 2015. In those years, there were disappointments, worries, and depression, but there were more joys, cheers and hope. It has been surely a long, hard but enjoyable journey for me. As I finish this journey, my heart are filled with gratitude for a number of extraordinary people who made it possible. This dissertation could never have been completed without the help from them.

First and foremost, I would like to express my sincere gratitude to my daily supervisor Andy Pimentel, for being valuable sources of technical knowledge, tactical advice and scientific support. You have made selfless dedication to me: I can not count how much coffee you consumed before our regular meetings, but I remember that you corrected almost every sentences of the draft I wrote for the first paper of my PhD. Thank Andy for having faith in me and encouraging me when I got stuck with research and fell into darkness. I am especially grateful to you for letting me pursue my own research agenda as you provided the nurturing blend of trust, support, encouragement, patience, and funding. Your contribution to me as a person goes beyond our professional relationship: you showed me the art of communication and you taught me the power of respect. Your teachings and principles will continue to influence me, both as a researcher and as an individual. Thank you very much for all the help, Andy!

I am also greatly indebted to my promoter Prof. Cees de Laat, for always being available for discussions on my research and providing me with constructive comments and suggestions for the improvement of my work.

I was very fortunate to work with, and learn from, a number of (both formal and current) colleagues in and SNE research group: Benjamin Rouxel, Catalin Ciobanu, Dolly Sapra, Hao Zhu, Hongyun Liu, Hugo Meyer, Junchao Wang, Julius Roeder, Lu Zhang, Lukasz Makowski, Ralph Koning, Uraz Odyurt, Wei Quan, Xiaofeng Liao, Zeshun Shi, Zhiming Zhao and so on. Those incredible colleagues helped by brainstorming, exchanging ideas, providing feedback, and being exceptional friends. A warm thanks to Giulio Stramondo for your humor and pleasing words at the moment when we held a cup of wine and "Ganbei". A sincere thanks also goes to Simon Polstra, who provided technical support at the the early stages of my PhD and helped me translate this dissertation summary into Dutch. I also would like to give special thanks to Huan Zhou and Hu Yang for interesting talks and jokes we had during our daily coffee times.

I would like to thank the members of my examination committee: Prof. Sebastian Altmeyer, Prof. Giuseppe Lipari, Dr. John Shalf, Prof. Rob van Nieuwpoort, Prof. Cees G.M. Snoek, Dr. Clemens Grelck and Dr. Ana Lucia Varbanescu for reviewing this dissertation, providing me with invaluable comments and feedback and taking time to come to Amsterdam to discuss the various aspects of this work. Additionally, I wish to thank Giuseppe for your master course on design patterns in object-oriented programming, which have profoundly influenced the way I now develop software and your help in building the SysRT simulator. A Special thanks goes to Sebastian, for attending my practice talks, proof-reading papers, participating in discussions, listened, and argued like good friends. I will also not forget your help in preparing the rebuttal letter for the RTSS paper: we exchanged mails at the very dark night. A sincere thanks

goes to Clemens, for many discussions we had, in which I always benefit from your critical ideas and insights. I also learned a lot from you about the compilers. Thank Ana, for giving me the access to equipment for conducting experiments.

I met exceptional people and made formidable friendships throughout the various stages of my PhD. I would like to thank all my great and cheerful friends during my stay in the Netherlands: Biwen Wang, Hui Xiong, Jian Lin, Jinglan Wang, Linlin Zhang, Renjie Lv, Songyu Yang, Shunan He, Shuangshuang Hu, Shaojie Jiang, Si Wen, Wenyang Wu, Wei Du, Weiyu Li, Xiaolong Liu, Yumei Wang, Yipeng Song, Zijian Zhou, Ziming Li, Zenglin Shi and so on. Without them, I would never have had such a wonderful life in the past years. I also want to thank my friends who are far away from me but have provided support: Binfei Lin, Jiachang Chen, Lianhua Liu, Mao Nie, Michele Linardi, Shichen Li, Youcai Gao and so on.

I am very grateful to meet and talk with many brilliant researchers. I want to thank Prof. Lieven Eeckhout for hosting my short visit to your research group, and discussions we had about simulation and modeling of computer architecture. I desire to thank Prof. Per Stenstorm for interesting discussions we had about cache contention problems. I wish to thank Prof. Xu Liu for your guidance in programming with Intel's PEBS techniques and cache locality theory. I learned a lot from their expertise. I hope the cooperation with them will continue.

特别感谢我的妻子孙祎玮。三年前你放弃在意大利的学习生活,选择来荷兰 陪我。感谢你这些年陪伴、支持与理解。在我工作一筹莫展的时侯,你总会做 一桌好菜,讲述有趣之事来排解我的失落沮丧。在我为第二天的演讲焦虑的时候,你总是不厌其烦地听完我的准备练习。在我企图放弃学术之时,及时提醒 我还有比金钱更重要的东西。感谢你为了实现我的梦想所作出的牺牲!感谢岳 父岳母的信任,把您们心爱的女儿交给我。

感谢我可爱漂亮的女儿,肖千淮,欢迎你在我博士最后阶段的到来。你的 微笑,是我忙时最好的放松。

衷心感谢爸爸妈妈和外婆,对我每一次抉择和人生每一步的无条件的支持 和鼓励!您们的教育和引导是我攻读博士最坚实的基础。感谢您们的理解,我 深知,七年多的欧洲留学生涯,于我是追梦,对于您们而言,更多的是日日夜 夜的思念与牵挂。感谢在我二十多年成长道路中倾注的无私的爱,让我感受这 个世界的美好,给我探索世界的勇气和自由。

最后,感谢生命中遇到的每一个人提供的帮助!在此,谨以此文献给所有 我爱的和爱我的你们,以及为未来不懈奋斗的自己。

> Jun Xiao 肖俊 Almere, 18th September 2019

### Contents

| 1 | Intr | ntroduction 1                                                        |  |  |

|---|------|----------------------------------------------------------------------|--|--|

|   | 1.1  | Research Outline and Questions                                       |  |  |

|   | 1.2  | Main Contributions 6                                                 |  |  |

|   | 1.3  | Thesis Overview                                                      |  |  |

|   | 1.4  | Origins                                                              |  |  |

| 2 | Bac  | kground 11                                                           |  |  |

| - | 2.1  | Computer architecture                                                |  |  |

|   |      | 2.1.1 Multi-core processors                                          |  |  |

|   |      | 2.1.2 Processor caches                                               |  |  |

|   |      | 2.1.3 Shared cache interference                                      |  |  |

|   |      | 2.1.4 Cache Partitioning                                             |  |  |

|   |      | 2.1.5 Cache Allocation technology                                    |  |  |

|   |      | 2.1.6 Hardware prefetching                                           |  |  |

|   |      | 2.1.7 Hardware PMU                                                   |  |  |

|   | 2.2  | Real-time systems                                                    |  |  |

|   |      | 2.2.1 Real-time task models                                          |  |  |

|   |      | 2.2.2 Scheduling algorithms                                          |  |  |

|   |      | 2.2.3 Schedulability analysis                                        |  |  |

|   |      |                                                                      |  |  |

| 3 |      | RT: A Modular Multiprocessor RTOS Simulator for Early Design Space   |  |  |

|   | -    | loration 27                                                          |  |  |

|   | 3.1  | Modeling Framework                                                   |  |  |

|   | 3.2  | Application model                                                    |  |  |

|   |      | 3.2.1 Task Model                                                     |  |  |

|   |      | 3.2.2 Instruction Model                                              |  |  |

|   | 3.3  | RTOS Kernel Model         33                                         |  |  |

|   |      | 3.3.1 UNPKernel Model                                                |  |  |

|   |      | 3.3.2 SMPKernel Model                                                |  |  |

|   |      | 3.3.3 PartiKernel Model                                              |  |  |

|   |      | 3.3.4 Scheduler Model                                                |  |  |

|   | ~ .  | 3.3.5 Resource Management Model                                      |  |  |

|   | 3.4  | Experimental Results                                                 |  |  |

|   |      | 3.4.1 Simulation performance and accuracy                            |  |  |

|   |      | 3.4.2 Flexibility of SysRT                                           |  |  |

|   | 2.5  | 3.4.3 Benefit of SysRT in DSE                                        |  |  |

|   | 3.5  | Conclusion                                                           |  |  |

| 4 | Sche | edulability Analysis of Global Scheduling for Multicore Systems with |  |  |

|   | Sha  | red Caches 43                                                        |  |  |

|   | 4.1  | Related work                                                         |  |  |

|   | 4.2  | System Model                                                         |  |  |

|   |      | 4.2.1 Task Model                                                     |  |  |

|   |      | 4.2.2 Architecture Model                                             |  |  |

|   |      |                                                                      |  |  |

|   |                 | 4.2.3    | Global Schedulers                                                     | 47  |

|---|-----------------|----------|-----------------------------------------------------------------------|-----|

|   | 4.3             | Sched    | ulability Analysis                                                    | 47  |

|   |                 | 4.3.1    | Overview                                                              | 47  |

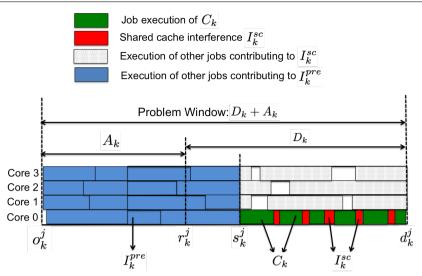

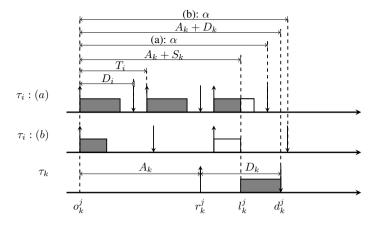

|   |                 | 4.3.2    | Computation of $\bar{I}_k^{pre}$                                      | 49  |

|   |                 | 4.3.3    | Computation of $\bar{I}_k^{sc}$                                       | 56  |

|   | 4.4             | Iterativ | ve Computation                                                        | 61  |

|   | 4.5             | Experi   | ments                                                                 | 65  |

|   | 4.6             | Conclu   | usions                                                                | 68  |

| 5 | Part            | itioned  | Scheduling for Real-time Systems with Shared Caches                   | 71  |

|   | 5.1             | System   | n Model and Prerequisites                                             | 73  |

|   |                 | 5.1.1    | System Model                                                          | 73  |

|   |                 | 5.1.2    | The Demand-Bound Function                                             | 74  |

|   |                 | 5.1.3    | Uniprocessor Schedulability                                           | 74  |

|   |                 | 5.1.4    | Cache Interference                                                    | 75  |

|   | 5.2             | Cache    | interference aware task partitioning : CA-TPAR                        | 75  |

|   |                 | 5.2.1    | The Task Partitioning Algorithm: CA-TPAR                              | 76  |

|   |                 | 5.2.2    | Calculation of The Upper Bound on Cache Interference: $\bar{I}_k^c$ . | 78  |

|   |                 | 5.2.3    | Schedulability Analysis                                               | 81  |

|   | 5.3             | Experi   | ments                                                                 | 85  |

|   |                 | 5.3.1    | Experimental Setup                                                    | 85  |

|   |                 | 5.3.2    | Results                                                               | 85  |

|   |                 | 5.3.3    | Average Execution Time                                                | 87  |

|   | 5.4             | Conclu   | usions                                                                | 87  |

| 6 | $\mathbf{CP}_p$ | f: a pro | efetch aware LLC partitioning approach                                | 91  |

|   | 6.1             | Motiva   | ation                                                                 | 93  |

|   |                 | 6.1.1    | The impact of hardware prefetching on cache performance               | 93  |

|   |                 | 6.1.2    | Inter-core prefetch-related cache pollution                           | 95  |

|   | 6.2             | PS and   | <i>INPS</i> applications                                              | 95  |

|   |                 | 6.2.1    | Definition of <i>PS</i> and <i>NPS</i> applications                   | 95  |

|   |                 | 6.2.2    | Cache sensitivity of <i>PS</i> and <i>NPS</i> applications            | 96  |

|   | 6.3             | Prefeto  | ch aware LLC Partitioning                                             | 97  |

|   |                 | 6.3.1    | Online classification of applications                                 | 97  |

|   |                 | 6.3.2    | LLC partitioning for <i>PS</i> and <i>NPS</i> applications            | 101 |

|   | 6.4             |          | iments                                                                | 102 |

|   | 0               | 6.4.1    | $CP_{pf}$ performance gain                                            | 103 |

|   |                 | 6.4.2    | Cases study of $CP_{pf}$                                              | 103 |

|   |                 | 6.4.3    | $CP_{pf}$ with multithreaded workloads                                | 103 |

|   |                 | 6.4.4    | Sensitivity Analysis                                                  | 104 |

|   |                 | 6.4.5    | Overhead                                                              | 105 |

|   | 6.5             |          | usion                                                                 | 105 |

|   | 0.0             | 2011010  |                                                                       | 100 |

| 7            | 7.1          | clusions<br>Main findings |  |  |  |  |

|--------------|--------------|---------------------------|--|--|--|--|

| Bibliography |              |                           |  |  |  |  |

| Summary      |              |                           |  |  |  |  |

| Sa           | Samenvatting |                           |  |  |  |  |

# Introduction

Both Moore's Law (the number of transistors in a processor will double every two years) and Dennard Scaling (power density remains constant because of transistor scaling) have allowed us to make large improvements over the last decades of microprocessor design. While Dennard Scaling is seen as now coming to an end, the resulting inability to increase clock frequencies significantly has fueled the move to the multi-core processors, which allows to continue to scale the performance of computing platforms through the use of multiple (and many) efficient cores.

The high performance achieved by the modern multi-core processors has been accomplished by using new architectural mechanisms. An important class of those mechanisms aims to overcome the performance gap between the processors and memory, referred to as the *memory wall*. For example, a hierarchy of cache memory levels, which rely on the principle of memory access locality, and hardware prefetching, which predicts future memory accesses and issues requests for the corresponding memory blocks in advance of the explicit accesses, are deployed in nearly every modern multi-core processors to hide memory access latency.

Although there are many benefits to moving from single-core processors to multicore processors, architects must address disadvantages and associated risks such as the contention on the shared hardware resources. Cores on the same processor share both processor-internal resources like L3 cache, system bus, memory controller, I/O controllers and interconnects and processor-external resources like main memory, I/O devices and networks. Multiple applications executing concurrently on a multi-core system can interfere with each other at those shared resources. Such inter-application interference, if uncontrolled, could lead to unpredictable execution delay for individual applications and severe performance degradation for the whole system.

In this dissertation, we investigate two issues raised by the increasing complexity of the underlying hardware and software for multi-core systems: timing predictability for embedded computing and caching performance for high performance computing.

## Challenges to build timing predictable multi-core embedded systems

In many embedded systems, a high performance is useless if we can not provide guarantees on the timing performance of the applications when designing the system. One example of such systems is real-time systems, where the computing system must interact with its environment in a timely manner. Violating timing constraints is fatal to such a system, which may lead to catastrophic consequences such as loss of human life. For example, an air-bag controller, which must inflate the air-bag in time before the driver's head hits the steering wheel. A flight control system must correct turbulence before the airplane becomes unstable.

A significant trend in embedded computing hardware is the paradigm shift from uniprocessor to multi-core processors. This brings great benefits such as higher computation power at lower cost of energy consumption, while at the same time also poses new challenges for the timing analysis of embedded software executing on a multi-core processor.

The scheduling of applications on multi-core processors not only involves the time dimension, i.e., to decide when to execute a certain application, but also involves the spatial dimension as it also needs to decide where (i.e., on which core) to execute the application. Apart from the processing cores, different applications also contend on many shared hardware resources in multi-core processors, such as caches, buses and main memory. Interleaving of concurrent accesses to these shared hardware resources results in execution delays for individual applications and creates a tremendous state space of the system behavior, making its timing analysis extremely difficult.

# Challenges to manage shared resources for high performance computing systems

Different from real-time embedded systems, the primary goal of high performance computing is to achieve the best system performance, i.e., to increase system throughput or to process the computing jobs as fast as possible. Here, the major challenges are to mitigate the inter-application interference and to efficiently manage the shared hardware resources in multi-core processor for high performance computing.

Applications running simultaneously on different cores utilize a plethora of memory components including a hierarchy of caches, prefetchers and memory controllers. Interapplication interference makes it difficult to the predict the performance degradation for individual applications, as some applications may be slowed down significantly, others may not

Furthermore, the interaction between these various components can be fairly complicated and it is challenging to study the impact of the interaction on application performance at run time due to the current limited transparency and monitoring capabilities for hardware behaviors. Since recent commodity CPUs have provided hardware support for control over hardware resources such as caches and memory bandwidth, a large amount of research attention is given to the management of shared hardware resources. However, mitigating the impact of the hardware interaction and resource contention and allocating the shared resources among the co-running applications to maximize system performance, remain challenges in high performance computing systems.

Next, we elaborate more in details on the research questions that we address in the thesis.

### 1.1 Research Outline and Questions

The work in this thesis focuses on developing tools, analyses and algorithmic methods for addressing the challenges raised in the two general research themes described above: time predictability for real time embedded computing and shared resource management for high performance computing. More specifically, in the first research line, we deal with two subtopics related to simulation and analytical approaches for the timing analysis: system-level modeling and simulation of real time systems for design space exploration and schedulability analysis of (global and partitioned) real-time scheduling for multi-core systems with shared caches. In the second research line, we study the interaction between the hardware prefetching and shared cache management and we exploit the opportunity to improve caching performance in the presence of hardware prefetching.

### Modeling and simulation of real time embedded system

In today's embedded systems, together with the increasing multi-core hardware platform complexity, the software complexity has also been growing dramatically. Modern embedded systems increasingly execute several applications of different types concurrently on the underlying computing platform. These applications can have different execution requirements. For example, control applications typically are hard real-time applications and thus have stringent timing constraints, while best-effort applications prefer a short task response time. These systems are usually managed by a Real-Time Operating System (RTOS).

The complexities of the multi-processor system-on-chip (MPSoC) design space have made traditional cycle- or instruction-accurate simulators inefficient. Raising the level of abstraction is generally considered as a solution to address the design complexity, thus reducing time-to-market. To help in the design space exploration (DSE) at the early stages of design [68], various system-level design languages (SLDL) such as SystemC [93] and SpecC [85] have been proposed to provide a simulation environment. Originally, SLDLs primarily focused on hardware modeling and did not properly address the modeling of software aspects.

The modeling and simulation of RTOS with SLDL have received widespread attention from many researchers [40, 50, 116, 117]. Those simulators are built by a quantum-granularity based simulation approach, in which the modeled scheduler is invoked every simulation quantum, similar to the way a real OS scheduler behaves. This therefore introduces large overheads, resulting in low simulation speeds. Later efforts [48, 89] were made to trade-off speed for accuracy. [73] and [78] rely on the prediction of preemption points to speedup simulation while maintaining accuracy. However, predictions of preemption points are difficult if the simulation uses more complex task models like Directed Acyclic Graphs (DAGs) and resource sharing models.

Therefore, our research questions in the first study are the following, which are referred as **RQ1**:

**RQ1** How to provide fast simulation of real-time embedded systems for design space exploration at the early stages of system design? How to accurately capture

the timing behaviour of embedded software? How to efficiently implement the simulator to provide support for easy plug-in of new task models, new schedulers and new resource sharing protocols?

### Schedulability analysis of real-time multi-core systems

In single-core systems, timing behaviour is typically verified via a two-step process [61]. In the first timing analysis step, the Worst-Case Execution Time (WCET) of each task is derived. The WCET is an upper bound on the execution time, assuming the task runs in full isolation on the platform, i.e. without preemption, nor any co-runners. The WCET is then integrated into the second step, schedulability analysis. Schedulability analysis involves considering the worst-case pattern of task execution under a scheduling policy. Schedulability analysis determines the Worst-Case Response Time (WCRT) of each task, by which the timing constraint of each task can be verified.

The clear separation between the two steps can not applied to the timing verification of multi-core systems where the interference on shared hardware resources can depend heavily on the behaviour of co-runners executing concurrently on other cores. When a task executes alone on a multi-core processor platform, the timing behaviour of the system is defined by that task alone, the same as executing the task on a uniprocessor platform. However, when multiple tasks run simultaneously on different cores, the interplay between the tasks on shared hardware resources may results in unpredictable execution delays. Therefore, using the WCET of tasks executing in isolation on a multi-core platform without considering the co-runner interference can potentially lead to incorrect WCRT values.

With a multi-core system, the WCRTs are strongly dependent on the amount of inter-core interference on shared hardware resources such as main memory, shared caches and interconnects. In this dissertation, we shall only focus on the shared cache interference.

The schedulability analysis of global multiprocessor scheduling has been intensively studied [8, 14, 22, 51, 57, 118], of which comprehensive surveys can be found in [26, 82]. Most multi-core scheduling approaches assume that the WCETs are estimated in an offline and isolated manner and that WCET values are fixed. A few works address schedulability analysis for multi-core systems with shared caches [35, 113], but these works assume that so-called cache space isolation is deployed, which requires explicit hardware support.

In this thesis, we consider multi-core systems in which cache isolation techniques are not deployed, i.e. the last level cache is shared by cores. We study the schedulability analysis of global scheduling (Earliest Deadline First and Fixed Priority) for hard real-time tasks that exhibit shared cache interferences. Thus, we ask the following research questions, which are referred as **RQ2**:

**RQ2** Is it possible to derive an upper bound on shared cache interference between two tasks running simultaneously on a multi-core system? Given a real-time taskset globally scheduled by EDF or FP, how to obtain an upper bound on the shared cache interference exhibited by each task in the taskset? How to derive a schedulable condition for the globally scheduled taskset, accounting for the shared cache interference?

Besides the global scheduling, the partitioned (semi-partitioned) scheduling is another paradigm that are widely used for scheduling real-time tasks. In partitioned scheduling, tasks are statically allocated to processor cores, i.e., each task is assigned to a core and is always executed on that particular core. Although the partitioned approaches cannot exploit all unused processing capacity since a bin-packing-like problem needs to be solved to assign tasks to cores, it offers lower runtime overheads and provides consistently good empirical performance at high utilizations [11].

Furthermore, taking the shared cache interference into account, partitioned scheduling may achieve better schedulability than global scheduling, which will be shown in Chapter 5.

Therefore, it is interesting to extend the answer to the previous question, which is developed for real-time global scheduling, to the partitioned scheduling. We then ask the following questions, referred as **RQ3**:

**RQ3** How to develop a cache interference aware partitioned scheduling for real-time multi-core systems? Is the partitioned scheduling better than global scheduling in terms of schedulability performance?

### Prefetch-aware cache partitioning for high performance caching

Hardware cache prefetching is a popular technique that is deployed in modern multicore processors to reduce memory latencies, addressing the memory wall problem [105]. However, it tends to increase the Last Level Cache (LLC) contention among applications executing on multi-core system, leading to a performance degradation for the overall system.

Shared cache management has attracted a lot of research attention in the past decades. Heracles [59] and Dirigent [120] control the amount of shared hardware resources, including the LLC, used by latency sensitive applications to improve Quality of Service and utilization. Selfa et. al. [79] cluster applications using the k-means algorithm and distributes cache ways between the groups to improve system fairness. Pons et. al. [69] assigns more cache space to critical applications to improve system turnaround time. [106] proposes a framework that dynamically monitors and predicts a workload's cache demand and reallocates the LLC given a performance target. KPart [30] leverages online profiling to obtain miss ratio curves for clustering applications and assigns each cluster of applications to a cache partition to improve system throughput.Park et. al. [66] proposed a coordinated partitioning of the LLC and memory bandwidth to improve the fairness of workloads on commodity servers. All these works have been implemented on existing processors, however, those works do not study the impact of hardware prefetching on cache performance and do not explicitly reveal the interaction between the hardware prefetching and LLC management.

In a real system, cache references by hardware prefetching also contributes to last level shared cache (LLC) interference [103]. However, there is little understanding about the interaction between the hardware prefetching and the shared caches. In this research line, we focus on the *LLC* management to improve system performance in the presence of hardware prefetching.

Our questions in this study, then, are the following , refered as RQ4:

**RQ4** How does hardware prefetching affect the caching performance? How to manage shared caches to improve system performance in the presence of hardware prefetching?

### 1.2 Main Contributions

In this section, we summarize the main contributions presented in this thesis.

**Modeling and simulation of RTOS.** We developed SysRT, a simulator of RTOS in SystemC that allows developers and researchers to easily explore and validate embedded RTOS design alternatives. Compared with quantum-granularity based simulators and prediction-based simulators, SysRT has two main advantages: (i) it has been developed to be generic and modular to support for easy plug-in of new schedulers as well as new resource sharing protocols. Thus, it is more flexible to simulate various real-time scheduling algorithms; (ii) it typically achieves higher simulation speeds via an event-driven simulation approach while obtaining identical accuracy results.

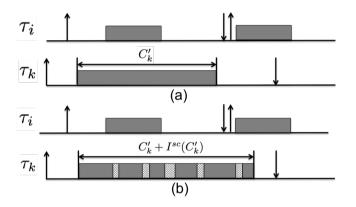

A Method to derive the upper bound on shared cache interference. We construct an integer programming formulation to calculate the upper bound on the cache interference exhibited by a task within a given execution window. We then present an iterative algorithm to obtain the upper bound on inter-core cache interference a task may exhibit during its job executions.

The above approach is extended to compute the upper bound on the cache interference for tasks under partitioned scheduling.

Schedulability analysis for real-time multi-core systems with shared caches. A schedulability condition is derived by integrating the calculated upper bound on intercore cache interference into the schedulability analysis for global scheduling algorithms (EDF and FP).

We also propose a novel cache interference aware task partition algorithm: CA-TPAR. We conduct schedulability analysis of CA-TPAR and formally prove the correctness of CA-TPAR.

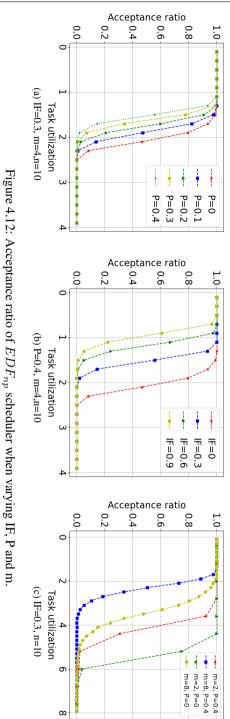

**Evaluation of schedulability performance for global and partitioned scheduling.** We perform a range of experiments to investigate how the schedulability of global (EDF and FP) and partitioned (CA-TPAR) scheduling are degraded by shared cache interference. We also compare the schedulability performance of EDF, FP scheduling and CA-TPAR over randomly generated tasksets.

Study of the interaction between hardware prefetching and cache management. We study the interaction between hardware prefetching and LLC management in a real system instead of in a simulator. We evaluate the variation of application performance when varying the effective LLC space in the presence and absence of hardware prefetching. We observed that hardware prefetching can compensate the application performance loss due to the reduced effective cache space. Based on this observation, we classify applications into two categories, prefetching sensitive (*PS*) and non prefetching sensitive (*NPS*) applications, by the performance benefit they experience from hardware prefetchers.

A prefetch-aware cache partitioning approach. We propose  $CP_{pf}$ , a prefetchaware LLC partitioning approach for improving LLC management.  $CP_{pf}$  consists of a method using Precise Event-Based Sampling (PEBS) techniques for online classification of PS and NPS applications and a LLC partitioning scheme using Cache Allocation technology (CAT) for PS and NPS applications. We have implemented the prototype of  $CP_{pf}$  as a user-level runtime system on Linux.

### 1.3 Thesis Overview

This thesis is organized in 7 chapters. After a background chapter, we present four research chapters containing our core contributions plus a concluding chapter:

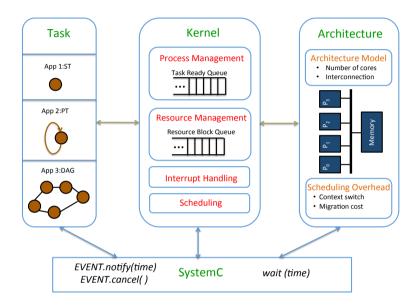

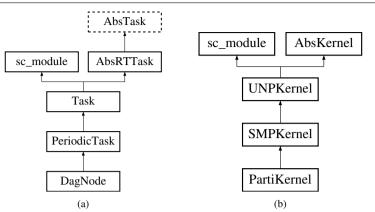

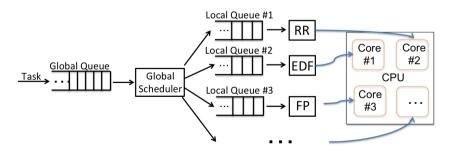

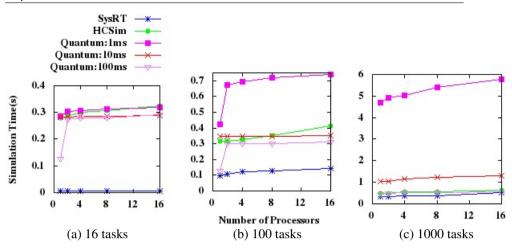

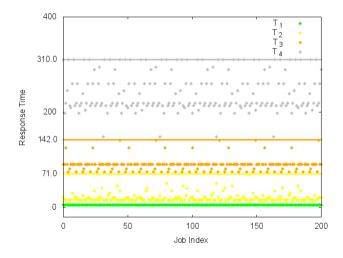

**Chapter 3** answers the research question RQ1. We present SysRT, a generic, modular and high-level RTOS simulator that is highly suited for early design space exploration. The simulator contains different types of application models and a modular RTOS kernel model, all developed in SystemC. Efficient and precise modeling of preemptive scheduling is achieved via an event-driven simulation approach, allowing simulations to be performed much faster than cycle-accurate simulations. We compare SysRT with state-of-art simulators to show the advantage of SysRT in both simulation speeds and accuracy. We also demonstrate the flexibility of SysRT and its benefits for early DSE using experiments with a mixed workload executing on multiprocessor platforms with different numbers of cores.

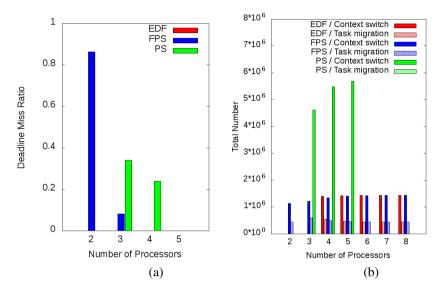

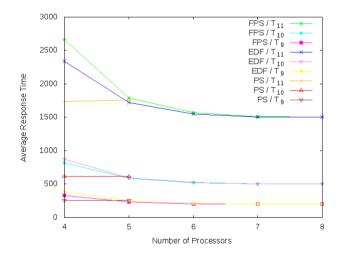

**Chapter 4** addresses the research question RQ2. We develop a new schedulability analysis for real-time multicore systems with shared caches, globally scheduled by EDF and FP algorithms. We construct an integer programming formulation, which can be transformed to an integer linear programming formulation, to calculate an upper bound on cache interference exhibited by a task within a given execution window. Using the integer programming formulation, an iterative algorithm is then presented to obtain the upper bound on cache interference a task may exhibit during one job execution. The upper bound on cache interference is subsequently integrated into the schedulability analysis to derive a new schedulability condition. A range of experiments is performed to investigate how the schedulability is degraded by shared cache interference. We also evaluate the schedulability performance of EDF against FP scheduling over randomly generated tasksets.

**Chapter 5** answers the research question RQ3. We propose a novel cache interference aware task partitioning algorithm, called CA-TPAR. We extended the approach to calculating the upper bound on cache interference for tasks that are globally scheduled, presented in the previous chapter, to bound the shared cache interference for tasks under partitioned scheduling. We conduct schedulability analysis of CA-TPAR and formally prove its correctness. A set of experiments is performed to show CA-TPAR outperforms global EDF scheduling in terms of schedulability performance over the randomly generated tasksets.

**Chapter 6** answers the research question RQ4. We propose  $CP_{pf}$ , a prefetch aware LLC partitioning approach for high performance caching. We first study the interaction between hardware prefetching and LLC cache management by analyzing the variation of application performance when varying the effective LLC space in the presence and absence of hardware prefetching. We observe that hardware prefetching can compensate the application performance loss due to the reduced effective cache space. Motivated by this observation, we then classify applications into two categories, prefetching sensitive (*PS*) and non prefetching sensitive (*NPS*) applications, by the performance benefit they experience from hardware prefetchers. After that, we propose  $CP_{pf}$ .  $CP_{pf}$  first classifies *PS* and *NPS* applications at run time and then partitions the *LLC* among *PS* and *NPS* applications. Finally, we show the system performance improvement achieved by  $CP_{pf}$ , compared with the baseline configuration, in which the LLC is unpartitioned and is fully shared among all applications.

**Chapter 7** draws the Conclusions. We summarize our main findings and discuss directions for future research.

### 1.4 Origins

For each research chapter, we list on which publication(s) it is based, and we briefly discuss the role of the co-authors.

**Chapter 3** is based on J. Xiao, A. D. Pimentel and G. Lipari [109], SysRT: A modular multiprocessor RTOS simulator for early design space exploration, proceedings of the 17th International Conference on Embedded Computer Systems: Architectures, Modeling, and Simulation (SAMOS), 2017. I am the principal author of this paper. I proposed the ideas, built the simulator, and was the lead writer of the paper. All the co-authors contributed to the discussions and paper writing.

Chapter 4 is based on J. Xiao, S. Altmeyer and A. D. Pimentel [108], Schedulability analysis of non-preemptive real-time scheduling for multicore processors with shared caches, *proceedings of IEEE Real-Time Systems Symposium (RTSS)*, 2017, and its extension as a journal version: J. Xiao, S. Altmeyer and A. D. Pimentel [110], Schedulability analysis of global scheduling for multicore systems with shared caches, *submited to IEEE Transactions on Computers*. I am the principal author of the two papers. I proposed the ideas, proved the results, conducted the experiments, and was the lead writer of the two papers. All the co-authors contributed to the discussions and paper writing.

**Chapter 5** is based on **J. Xiao and A. D. Pimentel [46], Partitioned non-preemptive scheduling for real-time multi-core systems with shared caches,** *submitted to De-sign, Automation and Test in Europe Conference 2020 (DATE2020).* I am the principal author of this paper. I proposed the ideas, proved the results, conducted the experiments, and was the lead writer of the paper. All the co-authors contributed to the discussions and paper writing.

Chapter 6 is based on J. Xiao, A. D. Pimentel and X. Liu [111], CP<sub>pf</sub>: a prefetch

**aware LLC partitioning approach**, *proceedings of the International Conference on Parallel Processing*, 2019 (*ICPP'19*). I am the principal author of this paper. I proposed the ideas, conducted the experiments and analyses, and was the lead writer of the paper. All the co-authors contributed to the discussions and paper writing.

Work on other publications also contributed to the thesis, albeit indirectly. We mention the following paper:

J. Xiao and G. Buttazzo [107], Adaptive embedded control for a ball and plate system, proceedings of the 8th International Conference on Adaptive and Self-Adaptive Systems and Applications, 2016. Buttazzo proposed the project, I did the implementation, conducted the experiments and analyses, and was the lead writer of the paper. All the co-authors contributed to the discussions and paper writing.

Paper not related to the thesis but published during the PhD:

- J. Xiao, S. Chiaradonna, F. Di Giandomenico, and A. Pimentel [47], Improving voltage control in mv smart grids, 2016 IEEE International Conference on Smart Grid Communications (SmartGridComm).

- S. Chiaradonna, F. Di Giandomenico, and J. Xiao [20], Quantification of the effectiveness of medium voltage control policies in smart grids, proceedings of the 17th International Symposium on High Assurance Systems Engineering (HASE), 2016.

# **2** Background

In this chapter, we provide the concepts and background needed in later chapters in this thesis. We start with a brief introduction to computer architecture in Section 2.1, then we briefly describe the real-time scheduling theory in Section 2.2.

### 2.1 Computer architecture

We begin with a discussion of relevant computer architecture fundamentals. Given the breadth of the topic, a comprehensive review of computer architecture is beyond the scope of this dissertation. Instead, we focus on the parts of a computing platform: multi-core processors, caches, hardware prefetching and hardware performance monitoring unit.

### 2.1.1 Multi-core processors

During the last decades, the performance of uniprocessor systems has been increasing by several magnitudes. The high performance has been achieved by using a high processor clock frequency. While Dennard Scaling is seen as now coming to an end, the resulting inability to increase clock frequencies has fueled the move from uniprocessor systems to the multi-core processors, which allows to continue to boost the performance of processors through scaling up the number of cores in a processor. By doing so, the software architect is able to process in parallel, thereby significantly improving performance.

In this dissertation, a multi-core processor is considered to be a computer system with multiple (two or more) central processing units (CPUs) that share full access to a main memory and peripherals. We do not distinguish between multi-core processors and multiprocessors, thus multi-core processor is used as a synonym for multiprocessor.

Depending on the memory organization and interconnect, multiprocessors can be divided into two shared-memory model categories: *symmetric shared-memory multiprocessors* (SMPs) and *distributed shared memory multiprocessors* (DSMs) [41]. In SMPs, the processors share a single centralized memory and a bus is typically used to interconnect the processors and memory. As all processors have a uniform access latency to the memory, this type of architectures are also called *uniform memory access* (UMA) multiprocessors. By contrast, in DSMs, memory is distributed among the processors but forms a single shared address space. A processor can access its local memory faster than accessing remote memories. Therefore, a DSM multiprocessor is also referred to as a *nonuniform memory access* (NUMA) multiprocessor. In this dissertation, we restrict our focus to SMP architectures.

### 2.1.2 Processor caches

To hide high off-chip memory latencies, a hierarchy of fast cache memories that contain recently accessed instructions and data is employed, taking the benefits of the principal of locality and cost-performance of memory technologies.

The *principal of locality* is the tendency of programs to access the same set of instructions or data repetitively over a short period of time. There are two types of locality: temporal and spatial locality [41].

**Temporal locality:** if an item is referenced, it tends to be referenced again in the near future.

**Spatial locality:** if an item is referenced, items whose addresses are close by tend to be referenced in the near future.

Temporal and spatial locality in programs arise from natural program structures. For example, most programs contain loops, instructions and data tend to be accessed repeatedly, experiencing high degrees of temporal locality. It is also common that instructions and elements of an array or a record are accessed sequentially, showing a high amounts of spatial locality.

**Cache access.** Each access to the cache results in either a *cache hit* or a *cache miss*. Cache hits occur when an application accesses data (or instructions) and finds that data (or instructions) in the cache. A cache miss happens when accessed data is not present in the cache.

**Cache organization.** Data is transferred between memory and cache in blocks of fixed size, referred to as *cache lines*. A cache line usually contains multiple data elements. An access to one data element causes the whole cache line to be loaded into the cache. As a result, a following access to another element in the same cache line also results in a cache hit.

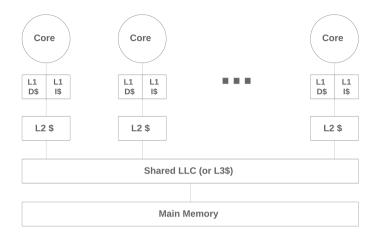

Caches are typically organized as a hierarchy of several cache levels. The fastest and smallest caches are denoted level-1 (L1) caches, with deeper caches (L2, L3, etc.) being successively larger but slower. A cache contains either instructions or data, and can also contain both if it is unified. In multiprocessors, caches can be either private or shared. Private caches serve only one core. By contrast, shared caches can be accessed by multiple cores. Usually lower level caches are private while the last level caches are shared. A typical design of cache hierarchy is shown in Figure 2.1, where each core has a private L1 and L2 cache and four cores share an L3 cache.

The size of an L1 cache is about several tens of KB and has an access latency of less than 5 cycles. If a memory access misses in the L1 cache, the L2 cache is queried. The capacity of L2 caches may range from hundreds of KB to several MB, with an access latency of around 10 cycles. In some high performance multi-core processors, an L3 cache with the size of several tens of MB is deployed to further expand cache capacity. The access latency of an L3 cache ranges from 40 to 80 cycles. Misses in

Figure 2.1: A typical design of cache hierarchy in a multi-core processor.

the last level cache trigger accesses to the main memory via the off-chip memory bus, causing a delay in the order of hundreds of cycles.

**Cache mapping.** Another issue in cache design is to decide where lines should be stored, i.e. if a cache line is fetched from main memory, where should it be placed? The answer depends on the cache mapping. At one extreme is a *fully associative cache*, in which a newly fetched memory block can be placed at any location in the cache. At the other extreme is a *direct mapped cache*, in which each memory block is mapped directly to exactly one location in the cache. Intermediate schemes are *n*-way set associative caches. In these schemes, every cache set has a fixed number of ways, each of which is a single cache line. The total number of ways within a cache set is called associativity. To load a memory block, the processor first determines which cache set the block maps to and then selects one of the n different ways in the cache set for the data placement.

**Cache replacement.** When a cache miss occurs in a direct-mapped cache, as the requested memory block can only be loaded to exactly one position, and the block occupying that position must be replaced. When a memory block can be mapped to several different locations in a cache like in a fully associative and n-way set associative cache, it is necessary to decide which cache line should be replaced. In a fully associative cache, all cache lines are candidates for replacement. In an n-way set associative cache, a way within the selected cache set has to be chosen for placing the requested block. A *cache replacement policy* is responsible for deciding which cache line is replaced when a cache miss occurs. The most commonly used scheme is *least recently used* (LRU). In an LRU scheme, the cache line that has been unused for the longest time will be chosen for the replacement. First In First Out (FIFO), and Pseudo-LRU (PLRU) are alternative cache replacement algorithms currently used by multi-core processors.

**Three C's model.** Cache misses are classified into one of three categories in the **three C's** model, by the source of misses in a cache [43]:

· Compulsory misses: these are cache misses caused by the first access to a memory

block that has never been brought into the cache.

- *Capacity misses:* these are cache misses caused when the cache cannot contain all the memory blocks accessed by a program. Capacity misses occur because of blocks being replaced in the cache and later on requested again by the CPU.

- *Conflict misses:* these are cache misses that occur when multiple memory blocks map to and compete for the same cache set. These cache misses are also called *collision misses*.

A special Cache: TLB. Processors with virtual memory using *memory management units* (MMU) usually have a *translation look-aside buffer* (TLB) [64]. A MMU translates virtual memory addresses into physical memory addresses. Since performing such a translation is relatively slow, the TLB, a special address translation cache, is deployed to store previously resolved virtual-to-physical address mappings. Thanks to the principle of locality (if the accesses have locality, the address translations for the accesses will also have locality), the TLB ensures that the MMU does not have to perform a translation on every memory reference.

### 2.1.3 Shared cache interference

When multiple applications run concurrently on a multi-core processor, they compete among each other for cache space. The execution time of a task in a multi-core processor can be affected by two types of cache interference: intra-core cache interference and inter-core cache interference.

**Intra-core cache interference** intra-core interference occurs within a core, specifically, when a task is preempted and its data is evicted from the cache by the preempting tasks. As a result, the preempted task may experience an extra execution delay due to the increased data access time as soon as it is rescheduled. The severity of the experienced delay depends on the particular cache replacement policy, the length of the preemption and the data access pattern of the preempting task [49, 74].

**Inter-core cache interference** inter-core interference may happen when tasks executing on different cores access the shared cache simultaneously [49]. If data in the different addressing spaces of the running tasks are loaded to the same cache line, memory (i.e. cache) accesses from different tasks can evict each other in cache, leading to complex timing interactions. Since this type of interference is suffered from tasks that run in parallel, an exact analysis requires analyzing all the possible interleavings of task executions, which is intractable. Therefore, it is extremely difficult to integrate the inter-core interference into a static timing analysis framework.

### 2.1.4 Cache Partitioning

Cache partitioning, i.e., dividing cache space between applications (or cores), is a promising approach to mitigate the negative impact of cache sharing. Cache partitioning has been widely used to improve system performance, fairness and QoS (quality-of-service) guarantees. We now present three common techniques (hardware, software and hybrid techniques) for partitioning shared caches in multi-core processors.

**Hardware Techniques.** Hardware techniques modify the cache to support partitioning. Way-partitioning [3, 21, 76], the most common technique, restricts insertions from each partition to its assigned subset of ways. However, simple, way-partitioning has significant limitations: it supports only coarsely-sized partitions, which is multiples of the way size, and the number of partitions is proportional to the number of ways. Prior work has proposed alternative hardware cache partition techniques. For example, in [12, 72, 96], the cache is partitioned by sets instead of ways by configuring the indexing function. [63, 77, 97, 102, 112] modify the cache insertion and replacement policies.

**Software Techniques.** The most common software-based cache partitioning technique is page coloring[94]. Page coloring exploits the virtual to physical page address translations present in virtual memory systems at OS-level. Each partition is allowed to use its own assigned physical pages that are mapped to specific cache sets. By restricting the physical pages used by each partition, the overlap of cache spaces can be avoided. Page coloring has the advantage of no need for hardware support and does not sacrifice associativity. However, it has several drawbacks. First, page coloring requires heavy modifications to the OS's virtual memory subsystem and precludes the use of other beneficial features, such as superpages. Second, partitions are coarsely sized, which is in multiples of page size  $\times$  cache ways, resulting in a limited number of partitions. Third, repartitioning incurs large overheads due to the costly process of recoloring memory pages.

**Hybrid Techniques.** As a hybrid cache partition technique, SWAP [98] combines both set- and way-partitioning to achieve finer-granularity partitions. By cooperatively managing cache ways and sets, SWAP can successfully provide hundreds of fine-grained cache partitions for the manycore era. SWAP requires no additional hardware beyond way partitioning. In fact, SWAP is readily implemented in existing commercial servers whose processors provide support for hardware way-partitioning. However, SWAP leverages page coloring, thus inherits the limitations of page coloring.

### 2.1.5 Cache Allocation technology

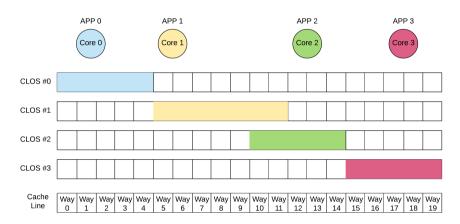

Recent Intel processors have proposed the so-called *cache allocation technology* (CAT), as hardware support for Way-partitioning [42]. CAT provides software-programmable control over the amount of cache space that can be used by a given application.

Processors that support CAT have a predefined number of classes of service (CLOS), for example, 11 in the Intel Xeon Gold 6148 processor and 20 in the Intel Xeon E5 2658 processor. Each CLOS is associated with a capacity bit mask (CBM) that controls the accessibility of cache lines at cache-way granularity. Each bit CBM grants write access to the corresponding way in the cache set. Cores (or threads) can be configured to belong to a CLOS. CBMs can overlap at some cache ways, which means that parts of cache ways can be shared by different CLOSs. One requirement of configuring a CBM is that all the bits set in a CBM must be consecutive, i.e. a CLOS uses consecutive cache ways in the cache. Each application is assigned a CLOS and an application can only access the cache ways defined by the CBM for that CLOS.

One can use Intel-cat-cmt, which is a library [24] developed by Intel, to configure CAT. By default, all cores (and applications) are grouped into to CLOS #0.

Figure 2.2 shows an example of a possible cache partitioning scheme. Each of the four possible classes of service (CLOS #0 to CLOS #3) has assigned a subset of the 20 ways of the LLC, and each core is mapped to a CLOS. Each CLOS is identified by a color which marks both the applications that belong to the CLOS and the cache ways they can access. For instance, core 0 is assigned to CLOS #0 and core 1 to CLOS #1. Note that all the CBMs are contiguous and core 1 and core 2 share cache ways 10 and 11.

Figure 2.2: An cache partitioning scheme using cache allocation technology.

### 2.1.6 Hardware prefetching

Hardware prefetching is another optimization technique that is commonly employed to reduce the observed memory access time and the performance gap between processors and memory. Prefetching predicts the memory addresses a program will access in the near future and issues memory requests to those addresses in advance of explicit accesses. By doing so, prefetching can hide the latency of a memory access since the processor either does not experience a cache miss for that data access or incurs a cache miss that is satisfied before the processor needs that data. There have been a myriad of proposed prefetching techniques, and nearly every modern processor includes some hardware prefetching mechanisms targeting simple and regular memory access patterns.

For example, there are five distinct hardware prefetchers on Intel Xeon platforms. Two prefetchers are associated with the L1-data caches: a Data Cache Unit (DCU) IP prefetcher and a DCU streamer prefetcher per core. The DCU IP prefetcher keeps track of individual load instructions. It uses sequential load history to determine whether to prefetch additional lines. The DCU streamer prefetcher is triggered accesses to very recently loaded data. It fetches the next cache line into L1-D cache.

Two prefetchers are associated with the L2 caches: a Mid-Level Cache (MLC) spatial prefetcher and a MLC streaming prefetcher. The spatial prefetcher strives to complete every cache line fetched to the L2 cache with the pair line that comprises a 128-byte aligned chunk. The streamer prefetcher monitors read requests from the L1

cache for ascending (and descending) sequences of addresses. Monitored read requests include L1 data cache requests initiated by load and store operations, and L1 instruction cache requests for fetching code. When a forward or backward stream of requests is detected, the anticipated cache lines are prefetched into the L2 cache. Prefetched cache lines must be in the same 4K virtual memory page.

Xeon processors support a special L2 streaming prefetcher, which prefetches data only into the L3. It is also known as LLC prefetch (or L3 prefetch) though it is still initiated by L2.

We can activate or deactivate these hardware prefetchers by setting the corresponding machine state register (MSR) bits [25].

### 2.1.7 Hardware PMU

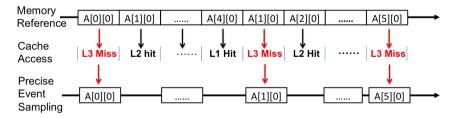

To provide realtime micro-architectural information about the processes currently executing on the chip, a rich set of *Hardware Performance Monitoring Units* (PMUs) is implemented in today's processor micro-architectures. PMUs are a set of specialpurpose registers to store the counts of hardware-related activities within computer systems such as cpu cycles, instructions executed, cache statistics, etc. PMUs also support advanced event sampling, a mechanism that collects event samples at a predefined sampling period. The event based sampling is realized by Intel's Precise Event-Based Sampling (PEBS) [36] and AMD's Instruction Based Sampling (IBS) [28].

To use the PEBS mechanism, a counter is configured to overflow after it has counted a preset number of events. After the counter overflows, the processor copies the current state of the general-purpose registers and instruction pointer in the records buffer. The processor then resets the performance counters and restarts the event counter.

As illustrated in Figure 2.3, the event MEM\_LOAD\_UOPS\_RETIRED: L3\_MISS is configured to drive PMU sampling. It precisely monitors cache misses at the LLC. If the sampling period is set to n, the PMU samples one data address that causes an LLC miss every n LLC misses.

Figure 2.3: PMU data address sampling.

Linux' perf\_event is a standard programming interface to set up performance monitoring through PMUs. More specifically, perf\_event\_open [27] can set the PMUs in sampling mode, and the overflow event can be enabled via ioctl() calls. The Linux kernel can deliver a signal to the threads whose PMU event counter overflows. The user code can mmap a circular buffer into which the kernel keeps appending the PMU data on each sample. The user can also read those circular buffers.

### 2.2 Real-time systems

Some embedded systems, which are referred to as real time systems, must react to events in the environment with precise time constraints. A real-time system is a computer system whose behavior depends not only on the functional correctness of the computation, but also on the time at which results are produced [18]. Violating timing constraints of a real time system such as chemical and nuclear plant control, railway switching systems, flight control systems, may lead to catastrophic consequences.

Rather than being computationally fast, a real-time computing system must be predictable. To achieve predictability, it is necessary to apply methodologies at every stage of the development of the system, from design to testing. Over the last decades, a number of methodologies and analysis techniques have been proposed in the literature to improve the predictability of real-time systems. In the following, we briefly review the real-time task models, real-time scheduling algorithms and schedulability analysis.

### 2.2.1 Real-time task models

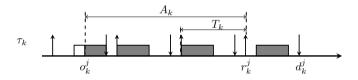

A *task* is a computational activity that is executed by the processor in a sequential fashion. Particularly well-studied real-time task models are the *periodic task model* and the *sporadic task model*. In both models, a task is a infinite sequence of jobs. In the periodic task model, the jobs of a task are released periodically, separated by a fixed time interval. In the sporadic task model, two consecutive jobs are separated by a minimum inter-arrival time. Each task  $\tau_k = (C_k, D_k, T_k)$  is characterized by a worst-case computation time  $C_k$ , a period or minimum inter-arrival time  $T_k$ , and a relative deadline  $D_k$ .

Three levels of constraint on task deadlines are studied in the literature: (1) Implicit deadlines, in which task deadlines are equal to their periods ( $D_k = T_k$ ), (2) Constrained deadlines, in which task deadlines are less than or equal to their periods ( $D_k \le T_k$ ), (3) Arbitrary deadlines, in which task deadlines can be less than, equal to, or greater than their periods. In this dissertation, we restrict our focus to constrained deadlines.

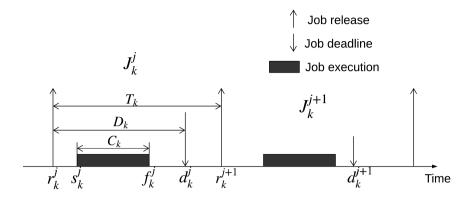

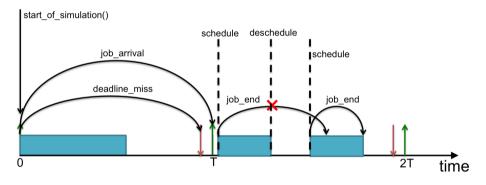

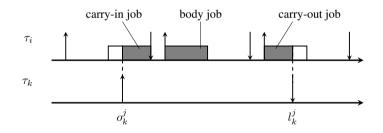

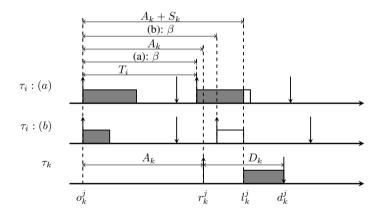

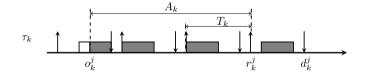

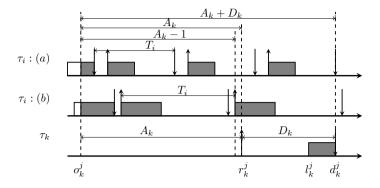

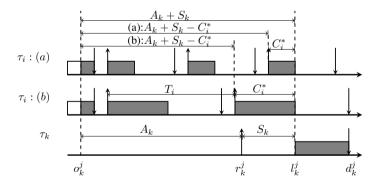

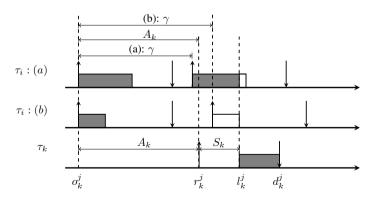

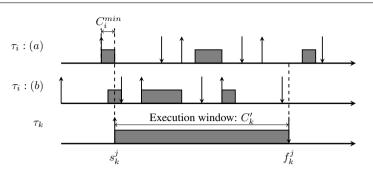

As illustrated in Figure 2.4, a task  $\tau_k$  is a sequence of jobs. Let  $J_k^j$  denote the *j*th instance of task  $\tau_k$ . The arrival time of  $J_k^j$ , i.e. the time instant when a job becomes available for execution, is denoted by  $r_k^j$ . Once a task is ready for execution, it may not get executed immediately. The time instant at which  $J_k^j$  starts to execute is denoted by  $s_k^j$  and  $J_k^j$  completes its execution at  $f_k^j$ . The absolute deadline of  $J_k^j$  is  $d_k^j = r_k^j + D_k$ .

$J_k^j$ 's response time, denoted by  $R_k^j$ , is the time interval from the arrival time to the time when the job is terminated, i.e.  $R_k^j = f_k^j - r_k^j$ . The goal of a real-time scheduling algorithm is to guarantee that each job will complete before its absolute deadline:  $f_k^j \leq d_k^j$ .

### 2.2.2 Scheduling algorithms

From the perspective of real-time scheduling, shared-memory multiprocessors can be further classified into three categories based on the capabilities of their constituent processors: *identical multiprocessors, uniform multiprocessors* and *heterogeneous*

Figure 2.4: Periodic (sporadic) task model and task parameters.

*multiprocessors*. In *identical multiprocessors*, each processor has the same computation power, hence the amount of work completed by executing a task for a fixed duration of time on a processor is the same, regardless of which task is being executed, and on which processor. In *uniform multiprocessors*, each processor is characterized by its own computing capacity hence the execution rate of a task depends on which processor it executes on. Finally, in *heterogeneous multiprocessors*, each processor may have special capabilities such as application-specific co-processors hence the amount of work completed by executing a job for a fixed duration of time upon a processor depends on the identities of both the job and the processor. We restrict our focus to identical multiprocessors in this dissertation.

In multitasking systems, the processor(s) are assigned to the various tasks according to a predefined criterion, referred as a *scheduling policy*. The set of rules that determines the order in which tasks are executed is called a *scheduling algorithm*. Real-time scheduling problems can be divided into two categories by the number of processors in the computation platform: uniprocessor real-time scheduling and multiprocessor real-time scheduling.

### Uniprocessor real-time scheduling

Research on uniprocessor real-time scheduling started in the late 1960s and significant research efforts were made in the 1980s and 1990s. [5] and [82] provide historical accounts of the most important achievements in the field of uniprocessor scheduling during those decades. The uniprocessor real-time scheduling theory is reasonably mature, as a large amount of research results are documented in the textbooks such as [17, 18], and some of those results are successfully applied to industrial practice. The two well-known uniprocessor scheduling policies are *fixed-priority* (FP) and *earliest-deadline first* (EDF) scheduling.

Under FP scheduling, each task is statically assigned a unique priority prior to execution. At runtime, competing jobs are then scheduled in order of decreasing task priority. One example of FP scheduling is *rate monotonic* (RM) scheduling. RM

scheduling assigns priorities to tasks according to their request rates. Specifically, tasks with higher request rates, i.e. shorter periods, get higher priorities. Since task periods are constant, the priority assigned to the task does not change over time.

EDF is a dynamic priority scheduling algorithm that selects tasks according to their absolute deadlines. Specifically, tasks with earlier deadlines are assigned with higher priorities. Since each job's absolute deadline changes over time, the priority of a task changes dynamically. In a classic result, EDF is optimal for uniprocessor real-time scheduling with HRT constraints [56].

### Multiprocessor real-time scheduling

Multiprocessor real-time scheduling theory also traces its origins back to the late 1960s. As noted in [55], multiprocessor real-time scheduling is intrinsically a much more difficult problem than uniprocessor scheduling. Few of the results obtained for a uniprocessor generalize directly to the multiprocessor case. Unlike uniprocessor scheduling, in which the scheduling of tasks only involves the dimension of time, i.e., to decide when to execute a certain task, multiprocessor scheduling also involves the dimension of space as it also needs to decide where (i.e., on which core) to execute a task.

There are two fundamental classes of multiprocessor schedulers: global and partitioned. Under global scheduling, all processors serve a single queue of tasks ready to execute and jobs may migrate among processors. In contrast, under partitioned scheduling, tasks are statically assigned to processors during an offline phase and no task migration is permitted. Each processor then is scheduled individually using a uniprocessor policy such as EDF or FP.

In some systems, the running task can be interrupted at any time. If a task with higher priority becomes ready to execute and all processors are occupied by some other tasks, the running task with lowest priority is suspended, leaving the processor for the execution of the ready task with higher priority. The operation of suspending a running task is called *preemption*.

Scheduling algorithms can be further classified into three categories with respect to whether preemption is allowed or not. (1) Preemptive scheduling. The running task can be preempted at any time, giving the core to another ready task. (2) Non-preemptive scheduling. Once a task starts executing, it will not be preempted and will therefore occupy the core until the completion of its execution. (3) Cooperative. Tasks can only be preempted at defined scheduling points within their execution. We restrict our focus to preemptive and non-preemptive scheduling in this dissertation.

We now show some examples of preemptive and non-preemptive real-time scheduling by considering a taskset  $\tau$  consisting of 4 real-time tasks:  $T_1 = (2, 4, 4), T_2 = (2, 5, 5), T_3 = (4, 9, 10), T_4 = (5, 20, 20)$  to be scheduled on a processor with 2 cores. Note that the 3-tuple task model is explained in Section 2.2.1.

### Preemptive scheduling

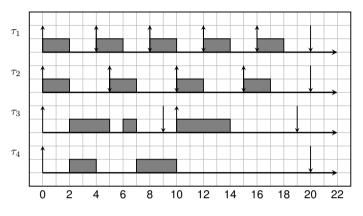

The scheduling of  $\tau$  under preemptive RM scheduling is depicted in Figure 2.5. RM scheduling assigns a fixed priority  $P_i$  to each task  $\tau_i$  (i = 1, 2, 3, 4), such that  $P_1 >$

$P_2 > P_3 > P_4.$

At t = 0, although all tasks are ready to execute, only  $\tau_1$  and  $\tau_2$  execute as only two core are available. At t = 2, both  $\tau_1$  and  $\tau_2$  finish execution, so  $\tau_3$  and  $\tau_4$  start their execution. At t = 4,  $\tau_1$  becomes ready again. Since  $\tau_1$  has the highest priority, the executing task with the lowest priority, which is  $\tau_4$ , is preempted, leaving one core for the execution of  $\tau_1$ . Similarly, at t = 5,  $\tau_3$  is preempted for the execution of  $\tau_2$ .

Figure 2.5: The scheduling of taskset  $\tau$  under preemptive RM.

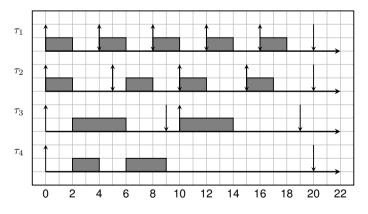

Figure 2.6 shows the scheduling of the same taskset  $\tau$  under preemptive EDF. Different from preemptive RM scheduling, at t = 5,  $\tau_2$  can not preempt  $\tau_3$  since the absolute deadline of the job from  $\tau_3$  (i.e. t = 9) is earlier than the absolute deadline of  $\tau_2$ 's ready job (i.e. t = 10). Thus,  $\tau_2$  starts its execution when  $\tau_3$  finishes.

Figure 2.6: The scheduling of taskset  $\tau$  under preemptive EDF.

### Non-preemptive scheduling

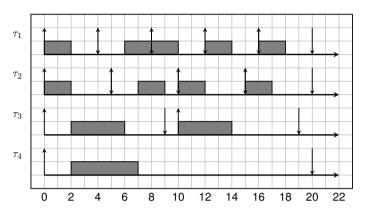

The scheduling of  $\tau$  under non-preemptive RM is illustrated in Figure 2.7. At  $t = 2, \tau_3$  and  $\tau_4$  start their job execution. Once a job gets executed, it is assigned with the highest

priority. Even though  $\tau_1$  and  $\tau_2$  have a higher task priority than  $\tau_3$  and  $\tau_4$ , they can not preempt  $\tau_3$ 's and  $\tau_4$ 's executing jobs.  $\tau_1$ 's job starts its execution when the job of  $\tau_3$  finishes. Similarly, the processing of  $\tau_2$ 's job begins when the job of  $\tau_4$  completes.

The scheduling of taskset  $\tau$  under non-preemptive EDF is same as shown in Figure 2.7.

Figure 2.7: The scheduling of taskset  $\tau$  under non-preemptive RM.

Preemptive scheduling typically allows higher efficiency, in the sense that it allows to schedule a real-time task set with higher processor utilization. However, preemption destroys program locality and consequently may introduce cache preemption related delay that inflates the execution time of tasks.

### 2.2.3 Schedulability analysis

A task is *schedulable* according to a given scheduling algorithm if all of its released jobs can be guaranteed to complete their executions before their deadlines. A taskset is schedulable according to a given scheduling algorithm if all of its tasks are schedulable.

The fundamental problem in embedded real-time system design is to analyze and verify the schedulability of the taskset under the scheduling algorithm, which is referred to as *schedulability analysis*.

The schedulability analysis of global multiprocessor scheduling has been intensively studied, of which comprehensive surveys can be found in [26, 82]. Details on the analytical schedulability analysis can be found in textbooks like [58] and [18]. As one of the fundamental methodologies for schedulability analysis, the Response Time Analysis (RTA) [18], which employs an iterative procedure to compute a task's worst-case response time, has been wildly applied to the timing verification of real-time systems.

Most multi-core scheduling approaches assume that the WCETs are estimated in an offline and isolated manner and that WCET values are fixed. when two or more tasks are executed in parallel on different cores. However, the interplay between the tasks on shared caches may lead to unpredictable delays [95].For example, useful cache blocks that were loaded by one task can be evicted by another task executing simultaneously

on a different core. Therefore, using the WCET of tasks executing in isolation on a multi-core platform without considering co-runner interference can potentially lead to incorrect WCRT values in the context of the complete multi-core system, which invalidates the traditional analysis framework with independent program-level and system-level timing analysis. This problem is a major obstacle to use multi-core processors for real-time systems [61].

Now we have provided the necessary background for the reminder of this dissertation, we move to the first research chapter: SysRT: A Modular Multiprocessor RTOS Simulator for Early Design Space Exploration.

## Timing predictability for embedded multi-core computing

## 3 SysRT: A Modular Multiprocessor RTOS Simulator for Early Design Space Exploration

In the previous chapter we have described the background knowledge for this thesis. Starting from this chapter, we begin to present our research and answer the research questions we listed in Chapter 1. This chapter addresses RQ1, which is concerned with modeling and simulation of real time embedded systems.

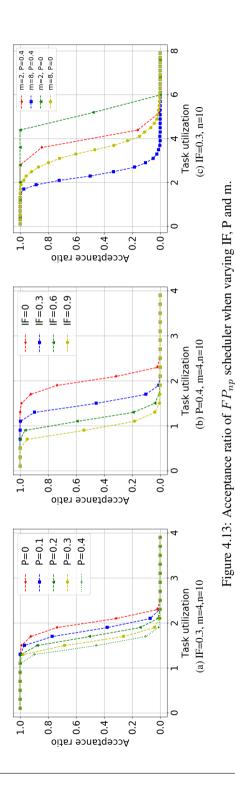

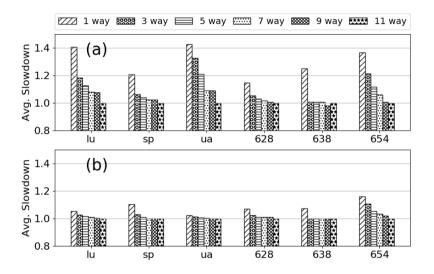

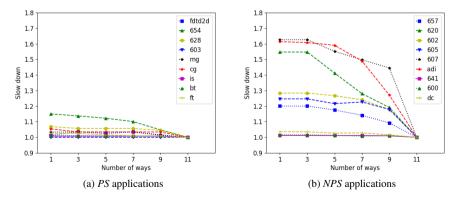

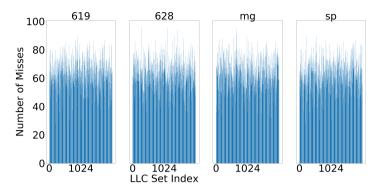

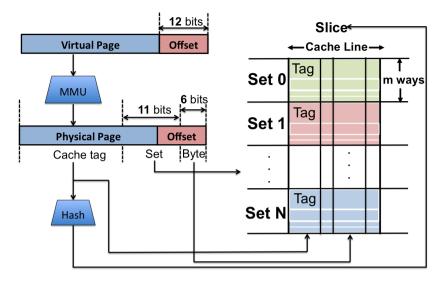

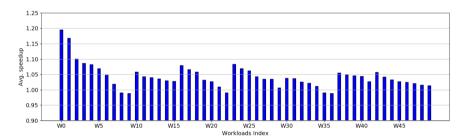

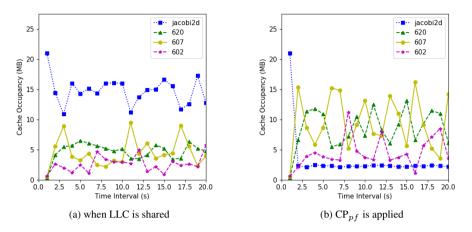

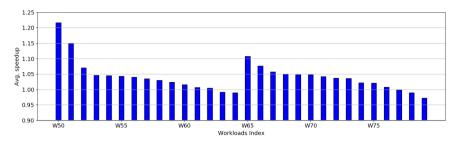

In the past years, the design of systems-on-chip (SoCs) has become increasingly complex. Hardware architectures are migrating from simple single-core based systems to more complex multi-core architectures. In the embedded systems domain, together with the increasing hardware complexity, the software complexity has also been growing dramatically. Modern embedded systems increasingly execute several applications of different types concurrently on the underlying computing platform. These applications can have different execution requirements. For example, control applications typically are hard real-time applications and thus have stringent timing constraints, while best-effort applications prefer a short task response time. These systems are usually managed by a Real-Time Operating System (RTOS).