Norwegian University of Life Sciences

## Master's Thesis 2018 30 ECTS

Faculty of Science and Technology Main supervisor Tor Anders Nygård Secondary supervisor Jonas Nøland (HSN)

## Feasability Demonstration of The Vienna type Excitation System for Synchronous Generators

Martin M. S. Giset Environmental Physics and Renewable Energy Faculty of Science and Technology

## Contents

| Ι   | Abbre  | eviations a | and acronyms                  | 2  |

|-----|--------|-------------|-------------------------------|----|

| п   | Intro  | luction     |                               | 3  |

|     | II-A   | Problem     |                               | 3  |

|     |        |             |                               |    |

| III | Theor  | у           |                               | 4  |

|     | III-A  | Fundame     |                               | 4  |

|     |        | III-A1      | The three-phase system        | 4  |

|     |        | III-A2      | IGBT                          | 4  |

|     |        | III-A3      | Drivers                       | 4  |

|     |        | III-A4      | Capacitors and inductors .    | 4  |

|     |        | III-A5      | Harmonies and THD             | 5  |

|     | III-B  | The roto    | r-field in a synchronous gen- |    |

|     |        | erator .    |                               | 5  |

|     |        | III-B1      | Static versus brushless ex-   |    |

|     |        |             | citation                      | 5  |

|     |        | III-B2      | Open-circuit field winding    |    |

|     |        |             | as a RL-load                  | 6  |

|     |        | III-B3      | Pole configuration            | 6  |

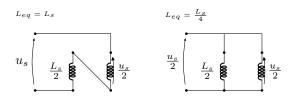

|     | TTT O  | III-B4      | Main windings inductance .    | 6  |

|     | III-C  | -           | ation and demagnetization .   | 7  |

|     |        | III-C1      | Magnetization                 | 7  |

|     |        | III-C2      | Demagnetization               | 8  |

|     | III-D  |             | etization with RPE            | 9  |

|     | III-E  |             | cal challenges with RPE       | 10 |

|     |        | III-E1      | IGBTs                         | 10 |

|     | III E  | III-E2      | Capacitors                    | 11 |

|     | III-F  |             | ctification                   | 11 |

|     | III-G  | The vier    | nna rectifer                  | 11 |

| IV  | Imple  | mentation   | 1                             | 14 |

|     | IV-A   | Control     |                               | 14 |

|     |        | IV-A1       | Hysteresis-control            | 14 |

|     | IV-B   | Control o   | criteria                      | 15 |

|     |        | IV-B1       | Rough estimation of input-    |    |

|     |        |             | currents                      | 15 |

|     |        | IV-B2       | Conflict between              |    |

|     |        |             | capacitor-voltage-            |    |

|     |        |             | difference and current-signal | 16 |

|     |        | IV-B3       | Modulation factor and         |    |

|     |        |             | maximum supply voltage .      | 16 |

|     |        | IV-B4       | Minimum field-current         | 16 |

|     |        | IV-B5       | Winding inductance            | 16 |

|     |        | IV-B6       | Additional chopper            | 17 |

|     |        | IV-B7       | Communication                 | 17 |

|     | IV-C   | Capacito    |                               | 18 |

|     |        | IV-C1       | Voltage rating and voltage    |    |

|     |        |             | ripple                        | 18 |

|     |        | IV-C2       | Ripple current                | 18 |

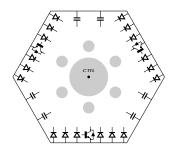

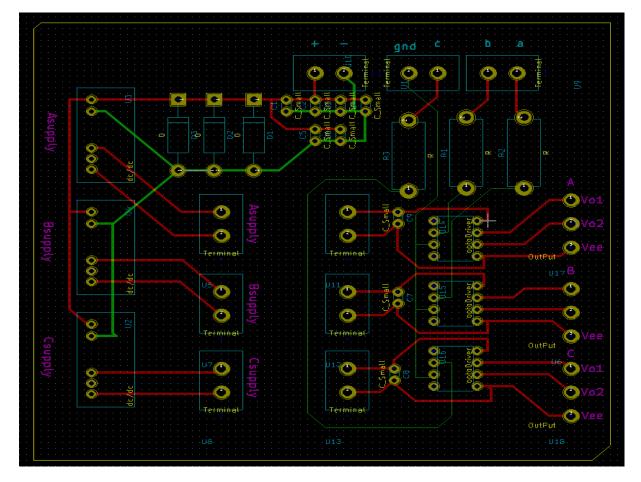

|     | IV-D   |             | considerations                | 18 |

|     |        | IV-D1       | Trace-width and thickness .   | 18 |

|     | IV-E   |             | strig Svante                  | 19 |

|     |        | IV-E1       | Electrical parameters         | 19 |

|     |        | IV-E2       | Possibility for re-           |    |

|     |        |             | connecting main windings .    | 19 |

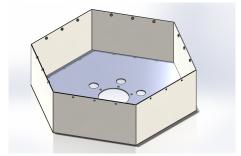

|     | 11 / T | IV-E3       | Enclosure for RPE             | 19 |

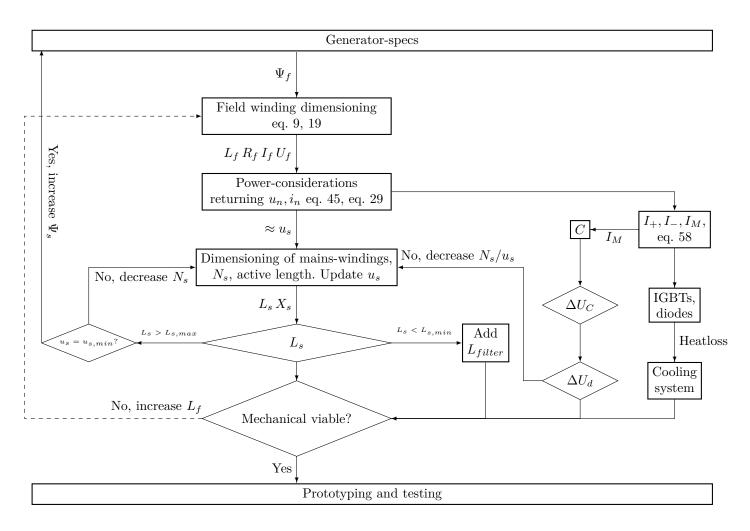

|     | IV-F   | Overview    | 7                             | 19 |

| $\mathbf{V}$  | Simula     | tion resu   | lts                                                       | 21 |

|---------------|------------|-------------|-----------------------------------------------------------|----|

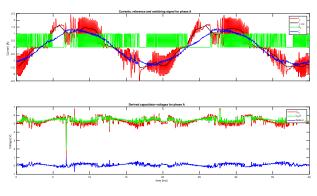

|               | V-A        | Steady sta  |                                                           | 21 |

|               |            | V-A1        | Initial calculations                                      | 21 |

|               | V-B        | Changing    | main windings connection .                                | 22 |

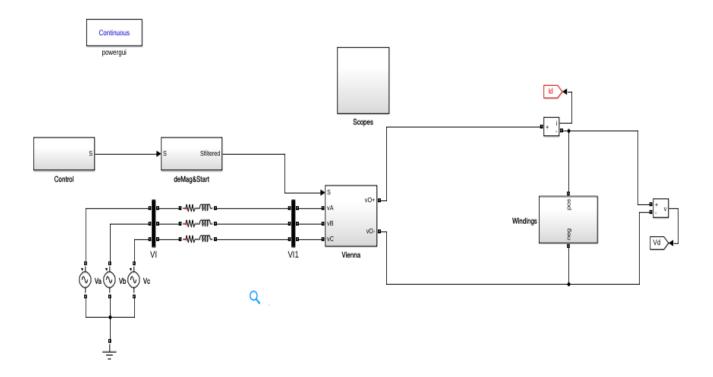

|               |            | V-B1        | Machine-model                                             | 23 |

|               |            | V-B2        | Simplified model consider-                                |    |

|               |            |             | ing only X"                                               | 24 |

|               |            | V-B3        | Adding chopper                                            | 25 |

|               |            |             |                                                           |    |

| $\mathbf{VI}$ | Demor      | stration    |                                                           | 26 |

|               | VI-A       | Introduct   | ion $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 26 |

|               | VI-B       | Compone     |                                                           | 26 |

|               |            | VI-B1       | Mains-supply                                              | 26 |

|               |            | VI-B2       | The control-board $\ldots$ .                              | 27 |

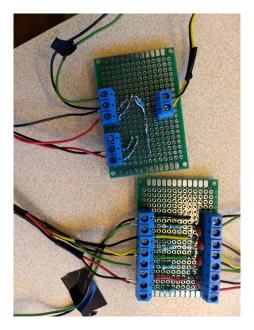

|               |            | VI-B3       | Current- and voltage-                                     |    |

|               |            |             | measurements                                              | 28 |

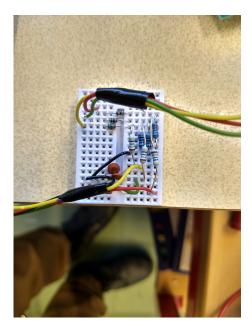

|               |            | VI-B4       | Gate driver $\ldots$ $\ldots$ $\ldots$                    | 29 |

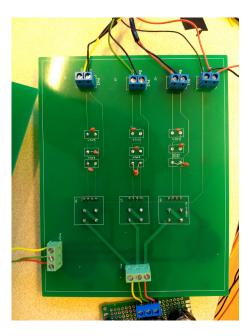

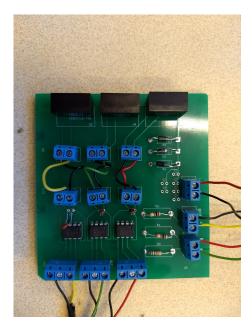

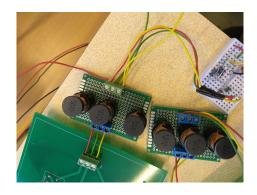

|               |            | VI-B5       | PCB-boards                                                | 31 |

|               |            | VI-B6       | Load                                                      | 31 |

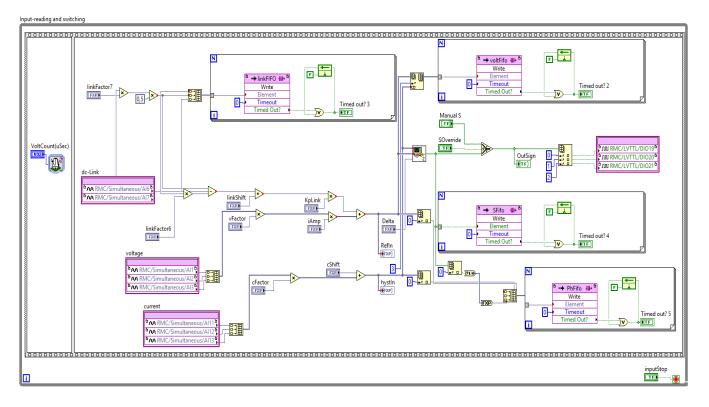

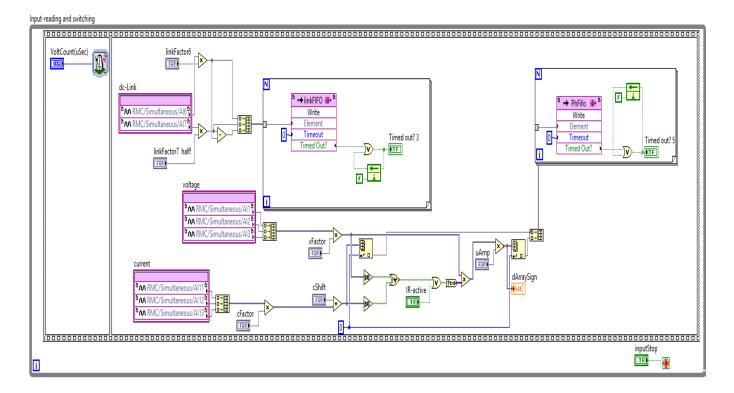

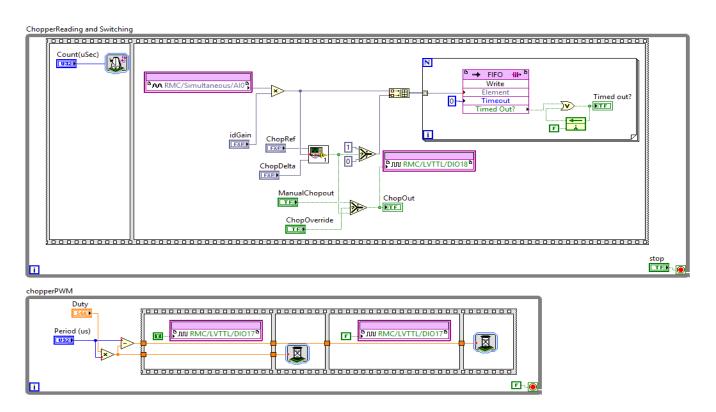

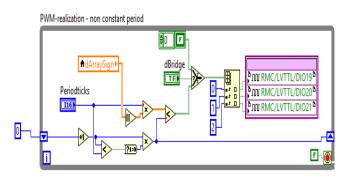

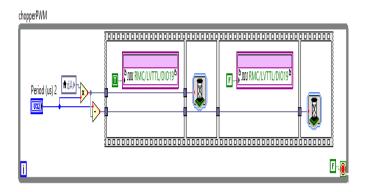

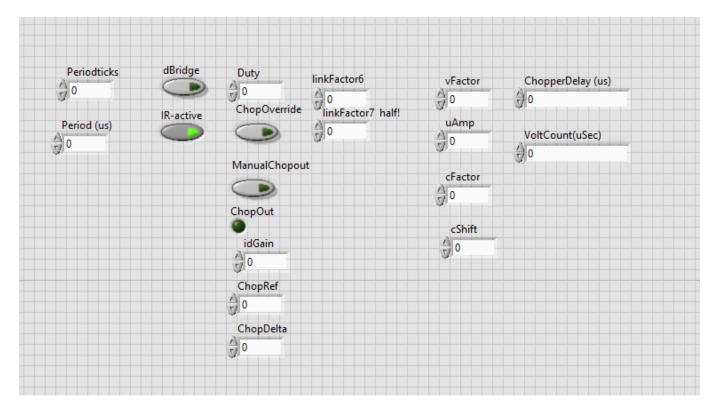

|               | VI-C       | Labview i   | mplementation                                             | 32 |

|               |            | VI-C1       | Override and safety measures                              | 32 |

|               |            | VI-C2       | Reading and displaying data                               | 33 |

|               |            | VI-C3       | Control-loops                                             | 33 |

|               |            | VI-C4       | Elements missing for a                                    |    |

|               |            |             | fully working VR                                          | 33 |

|               |            | VI-C5       | Easy to implement im-                                     |    |

|               |            |             | provements                                                | 33 |

|               | VI-D       | -           | ntal setup $\ldots$ $\ldots$ $\ldots$ $\ldots$            | 34 |

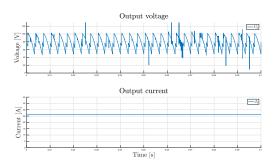

|               |            | VI-D1       | Event                                                     | 34 |

|               |            | VI-D2       | Results                                                   | 34 |

|               |            | VI-D3       | Suggestions for improved                                  |    |

|               |            |             | prototype                                                 | 35 |

| VII           | Discus     | sion        |                                                           | 36 |

|               | VII-A      | Suitability | y                                                         | 36 |

|               |            |             | trol-systems                                              | 37 |

|               | VII-C      |             | considerations                                            | 37 |

|               | VII-D      |             | ves to the VR                                             | 37 |

|               | VII-E      |             | s thyristor bridge                                        | 38 |

|               | VII-F      |             | l circuitry                                               | 38 |

|               |            |             |                                                           |    |

| VIII          | Conclu     | ision and   | final recommendations                                     | 39 |

|               | VIII-A     | Additiona   | l circuitry                                               | 39 |

|               | VIII-B     | Implemen    | tation in Svante testrig                                  | 39 |

|               | VIII-C     | Further re  | $esearch \ldots \ldots \ldots \ldots \ldots$              | 39 |

|               |            |             |                                                           |    |

| Refe          | rences     |             |                                                           | 40 |

| Biog          | raphies    |             |                                                           | 41 |

| Diog          |            | Giset       |                                                           | 41 |

|               | 19101 0111 | GIBCU       |                                                           | 71 |

| IX            | Appen      | dix         |                                                           | 42 |

|               | IX-A       |             |                                                           | 42 |

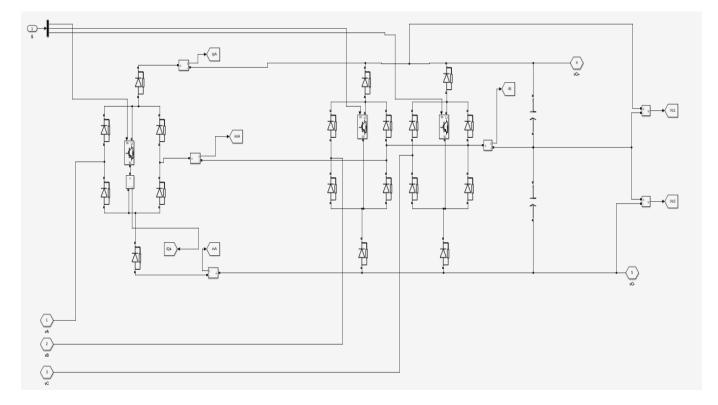

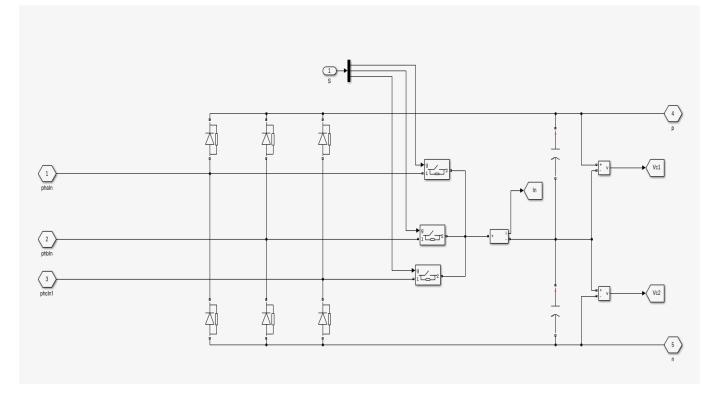

|               | IX-B       |             | - models                                                  | 43 |

|               |            | IX-B1       | Vienna-rectifiers                                         | 43 |

|               | IX-C       | LabView     | implementation                                            | 51 |

## I. Abbreviations and acronyms

| $\alpha$             | Firing angle for a thyristorbridge                          |

|----------------------|-------------------------------------------------------------|

| B                    | Magnetic field strength                                     |

| $\rm CCM/\rm DCM$    | Continuously/Discontinuously conduction mode                |

| d, D                 | duty cycle, average duty cycle                              |

| $\Delta u_c$         | Voltage difference of the output capacitors                 |

| IGBT                 | Insulated-gate bipolar transistor                           |

| $f_s$                | Frequency of supply                                         |

| $f_{\Delta}$         | Switching-frequency                                         |

| FPGA                 | Field Programmable Gate Array                               |

| HDBS                 | High-speed De-excitation for Brushless Synchronous machines |

| $i_s$                | Mains phase currents                                        |

| $i_{N,M}$            | Neutral point current                                       |

| $\mu$                | Switching angle in thyristorbridge                          |

| $L_f$                | Inductance of field-windings                                |

| $\frac{-J}{\psi_f}$  | Rotorside magnetic flux                                     |

| $l^{+J}$             | Active length of solonid                                    |

| $\mu_{0/r}$          | Magnetic permability of air/relative                        |

| $L_s$                | Total input-inductance                                      |

| M                    | Modulation index                                            |

| MPC                  | Model-predictive control                                    |

| $N_r/N_s$            | Winding on the rotor/stator of the feeder                   |

| $N_{r,SG}/N_{s,SG}$  | Winding on the rotor/stator of the SG                       |

| $Q_x$                | Ideal switch x, e.g. two IGBT's in antiparalell.            |

| pf                   | Power factor                                                |

| PFC                  | Power Factor Corrected                                      |

| PM                   | Permanent Magnet                                            |

| PWM                  | Pulse width modulation                                      |

| $R_s$                | Total input-resistance                                      |

| RPE                  | Rotating Power Electronics                                  |

| $S_x$                | State of switch x. '1' indicates a closed switch.           |

| $\mathbf{S}^x$       | Switching vector, e.g. $\mathbf{S} = [110]$ in sector 2     |

| $\mathbf{S}_x$       | Sector invariant switching vector , e.g. $\mathbf{S}_7$     |

| $S_x$ SVM            | Space vector modulation                                     |

| THD                  | Total Harmonic Distortion                                   |

|                      | Mains phase voltages                                        |

| $u_s$                | Threshold voltage for a diode                               |

| $u_{th}$             | Output voltage from the VR                                  |

| $u_d$                | Applied demagnetization voltage                             |

| $U_{dm}$<br>$U_{BE}$ | Base-emitter voltage of an IGBT                             |

|                      | Variable v in $\alpha\beta$ -coordinates                    |

| $v_{lphaeta}$        | Variable v for phase x where $x \in a, b, c$                |

| $v_x  V$             | Time invariant variabel v, rms or DC                        |

|                      | Phasor v                                                    |

| $\frac{v}{\not v}$   | Not variable v. If $v = 1, \rightarrow \not v = 0$          |

| $\vec{v}$            | Vector v                                                    |

| $v^*$                | The reference value of the variable v                       |

| $v^1$                | Fundamental of the variable v                               |

| vVR                  | Vienna rectifier                                            |

| vn<br>v              | Maximum value of the variable v                             |

| $v \over v$          | Average value of the variable v                             |

| v<br>VI              | Virtual Instrument, LabView filetype.                       |

| V I                  | virtuar montumente, nauview metype.                         |

|                      |                                                             |

# Feasibility Demonstration of the Vienna type Excitation Systems for Synchronous Generators

## Martin Giset

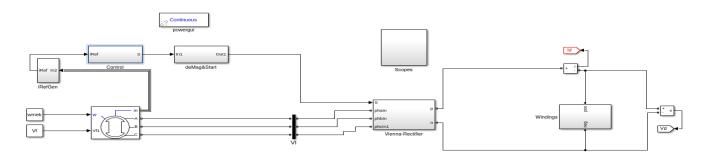

Abstract—The operation of the Vienna rectifier has been analyzed and relevant literature on the rectifier has been reviewed. Furthermore, the Vienna rectifier in scope of rotating power electronics in brushless excitation has been discussed and found to be an viable option. The Vienna Rectifier have been simulated with the parameters from the Svante testrig in Matlab Simulink with satisfactorily results. A re-connection of the main windings is necessary. Also demagnetizationstrategies and necessary modification to the Vienna Rectifier has been discussed and simulated. A demonstration of the Vienna Rectifier were build, but experimental results are remain qualitative due to practical issues with the demonstration rig. The control were designed in LabView Instruments and the workings of the control-scripts were confirmed.

The main challenge is comes from dealing with the large inductance from the mains winding on the rotating exciter, but this challenge may be overcome. Additional circuitry consisting of a chopper on the output and demagnetization resistor and switch should be added to ensure better controllability and demagnetization-capability.

## II. INTRODUCTION

**I** n his PhD thesis A New Paradigm for Large Brushless Hydrogenerators Advantages Beyond the Static System [29], Jonas Nøland among other things scrutinized several different configurations of rotating power-electronics (RPE) in a prototype test rig situated at Uppsala University. Previous demonstrations clearly overlooked the Vienna Rectifier (VR) as a potential topology for excitation systems. This thesis will address this question with this test-rig specially in mind.

The excitation system of synchronous machines have recently experienced a new era of developments. Rotating power electronics as a means to excite the field windings of synchronous machines is a promising development in the mature field of electrical power-generation. Considering the improvements in the semiconductor technology and new possibilities for fast and flexible control, more complex topologies than the thyristor-bridge may be considered a realistic possibility. The issues related to rotating power electronics are not strictly electrical - also mechanical and thermal challenges as well as communication with the circuit must be met. Some of these issues will be addressed in this thesis; However, the main subject will be the electrical performance. The VR is a power factor correcting boost-type rectifier that has been thoroughly analyzed and tested since it's emergence in the early 90's. Its high power density and proven reliability makes it a probable candidate for the brushless excitation scheme, in addition to possibly also the static excitation system. The workings of the Vienna is however not straight forward and will be described in depth in section III.

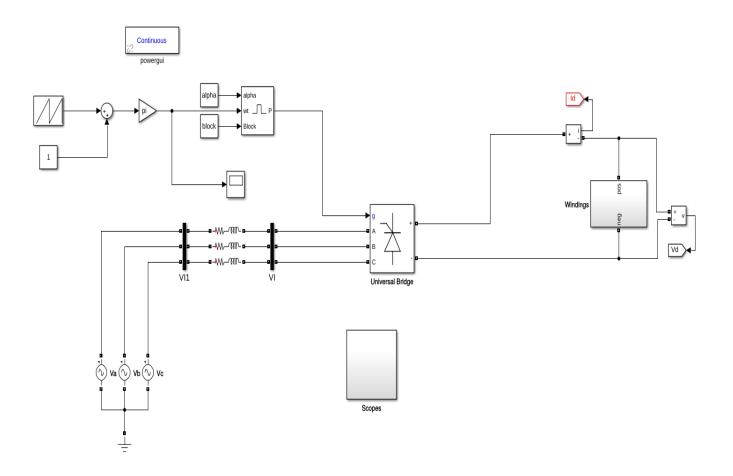

The VR will be simulated using Matlab Simulink/Simscape Power systems both in steady state and in transients. Rapid demagnetization and magnetization (field forcing) is one of the key qualities of the excitation topologies, and different suggestions will be scrutinized.

The VR is a commercially available product[20]. However, hands on experience is needed to be able to advice an optimal design for new applications, i.e., excitation systems. In this thesis, a downscaled demonstration-rig of the VR were built as to gather experience regarding building such prototype VR to pass on to design engineers or possibly later master-students finishing the project. This will also enable measurements over e.g. individual components and a flexibility that may not included in a commercial product. The demonstration rig will be described in section VI. The control will be written in LabView and implemented in a National Instruments (NI) control-board. To the authors best knowledge, there is not public available examples in either LabView or Simulink Powersystems of a working VR, and hopefully this thesis may be used as inspiration for engineers wanting to implement such a prototype for excitation purposes.

In the autumn of 2017 the author took a special course under the supervision of Jonas Nøland were the VR was initially considered. Partly to avoid overlap, PWM and other control-strategies that were considered in the special course, will not be discussed in this thesis. The report from the course is available for download [17]. Another reason why hysteresis-control were chosen is its simplicity.

## A. Problem

One of the inspirations for considering the VR as topology is it's good track record in literature as well as the possibility to utilize the winding-inductance as filterinductances. In traditional applications these are added and are a central design-aspect for the VR. In this application the input-inductances are a constraint rather than a design-question in and of itself. The main issues that are attempted answered in this thesis are:

- May the VR be used as excitation topology in the scope of RPE, especially with Svante testrig in mind?

- Which, and in what manner, should necessary modifications to ensure demagnetization-strategies be applied?

Secondary tasks are:

- Estimate whether the necessary components (capacitors, IGBTs, diodes) are able to withstand the rotary forces that RPE demands or not.

- Build Matlab Simulink models modeling the VR in this application

- Build and control a small VR prototype to get insight in the construction of such a prototype.

## III. THEORY

#### A. Fundamentals

1) The three-phase system: The power-system, and as a consequence also the VR, utilizes a three phase system. A three phase system can be written as:

$$u_{a} = \hat{u}_{a} \sin(\omega t)$$

$$u_{b} = \hat{u}_{b} \sin(\omega t - \frac{2\pi}{3})$$

$$u_{c} = \hat{u}_{c} \sin(\omega t + \frac{2\pi}{3})$$

$$\omega = 2\pi f$$

(1)

In a *balanced* three-phase system  $\hat{u}_a = \hat{u}_b = \hat{u}_c$ . In many applications, the VR being one of them, it is instructive to describe the three phase-system in the complex plane and describe them by a single phasor. This is done by a Clark/Park transform

$$\underline{u_{\alpha\beta0}} = \begin{bmatrix} u_{\alpha} \\ u_{\beta} \\ u_{0} \end{bmatrix} = K\vec{C}u_{\vec{x}N} = K\begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \\ \frac{1}{2} & \frac{1}{2} & \frac{1}{2} \end{bmatrix} \begin{bmatrix} u_{a} \\ u_{b} \\ u_{c} \end{bmatrix}$$

(2)

In 2 the scaling-factor is mostly chosen as  $K = \frac{2}{3}$ , resulting in a *amplitude-invariant* transformation. That is,  $|u_{u_{\alpha\beta0}}| = u_{abc}$ . As a consequence the power in the system is not equal. To get the *power-invariant* transformation  $K = \sqrt{\frac{2}{3}}$ . In this thesis the amplitude-invariant transform will be used.

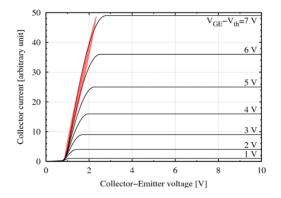

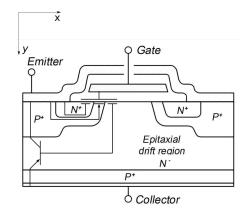

2) IGBT: A simplified schematic of an IGBT is illustrated in Fig. 1. The physical structure of the IGBT is shown in 15, where the rotary centrifugal forces are adressed For a schematic view of the doping-layer is shown in the discussion regarding the rotary forces on an IGBT.

The red slope marked in 2 is to indicates what kind of area one operates the devices in power electronics. The goal is to supply an gate-emitter voltage that ensures that the device never goes into saturation. In other words, that it operates in the ohmic area. Ideally, it should conduct

Fig. 1. The illustration is taken from [33] where also much of the inspiration for this section were found.

Fig. 2. The characteristic of an IGBT [7]. The red area is added by the author.

current with a low forward voltage drop, i.e., the lowohmic region. The values in the chart is not representative for the switches used in this thesis.

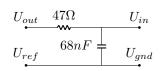

3) Drivers: Important for the discussion in this thesis is the gate-emitter capacitance,  $C_{GE}$ . To turn the IGBT fully on this need to be charged up to  $U_{GE,th}$ . Micro controllers and similar devices seldom have the current-capability (if they can supply  $U_{GE,th}$  at all) to charge and thus turn on the IGBT on satisfactory speeds. Therefore external drive circuity is employed to ensure satisfactory operation of the IGBT. In every case a gate resistor should be employed to limit the turn-on current. The peak-current can be estimated as [33]:

$$I_p = \frac{V_{on} - V_{off}}{R_g + R_{internal}} \tag{3}$$

There are several online tools and guidelines[45], [47], [40] regarding the selection of parameters and drivertypes. There are several techniques to design the drive circuitry [41] depending on the needs for isolation, whether the emitter is tied to ground or not and many other considerations.

4) Capacitors and inductors: Despite fundamental differs in construction, these two components may be described together as twins. The defining equations describing the components are shown below on integral and derivative forms:

$$\frac{u_c}{dt} = \frac{1}{C}i_C$$

$$\int_{t_0}^t i_C = Cu_C + U_{C,0}$$

(4)

The physical explanation of of eq. 4 is easies described thought the integral-form: As charge (the time-derivative of current) accumulates/is being removed from the sides of the capacitors, they will produce an electrostatic-field across the capacitor, causing a charging up to a voltage. Capacitance, as well as inductance, is component-specific property.

$$\frac{i_L}{dt} = \frac{1}{L}U_L$$

$$\int_{t_0}^t u_L = i_L L$$

(5)

A current through a conductor produces a magnetic field. If the conductor is correctly wound into a coil around a material with large magnetic permeability, an substantial magnetic field may be produced (and upheld) by the current. If the current sinks, the magnetic field will experience weakening. According to Faraday's law this will induce a voltage over the coil, containing the current. The current will be reduced slower, lagging the applied voltage. The same mechanism applies for increasing of the current in the coil, according to Lenz' law.

5) Harmonies and THD: In the field of powerelectronics, the currents and voltages aren't necessarily smooth sine-forms. To describe these, they are described as the sum of several sine- and cosine waves with different amplitude and frequency. This is formulated in complex form for a periodical function f(t)

$$f(t) = \sum_{-\infty}^{\infty} c_n e^{\frac{i2\pi nt}{T}}$$

$$c_n = \frac{1}{T} \int_{-T/2}^{T/2} f(t) e^{\frac{i2\pi nt}{T}} dt$$

$$n = 0, \pm 1, \pm 2, \dots$$

(6)

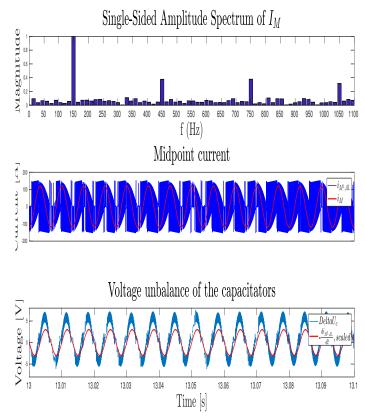

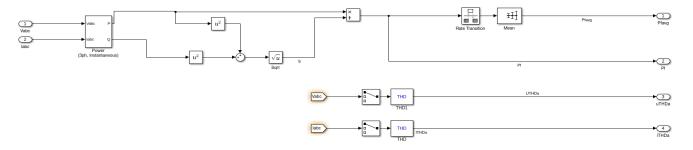

where T is the period of the signal. An illustration using Matlabs FFT (fast fourier transform) function illustrating how such a signal can be described is shown in Fig. 3

The signal with n = 1 is <u>the fundamental</u>. Total Harmonic Distortion (THD) is a measure of how distorted (non-sinusoidal) the signal is:

$$THD = \frac{\sqrt{U_2^2 + U_3^2 + U_4^2 \dots}}{U_1} \tag{7}$$

where  $U_n$  describes the rms-value of the n-th harmony of the signal U. In this thesis the power factor of nonsinusoidal currents are central. This is related to THD through the power factor of the the fundamental,  $pf^1$ .

$$pf = \frac{1}{\sqrt{1 + THD^2}} pf^1 \tag{8}$$

The calculation of THD and pf in these simulations will be done through Matlab functions.

Single-Sided Amplitude Spectrum of U(t)

Fig. 3. The first harmonies and the sums thereof taken from a square signal. The summation shows that for such a signal, the lower harmonies alone can describe it quite good. The upper plot shows the frequency-spectrum. Note that the signal only contains harmonies of the order 1, 3, 5... This is due to the odd nature (u(-t) = -u(t)) of the signal.

#### B. The rotor-field in a synchronous generator

1) Static versus brushless excitation: The earlier methods for excitation of synchronous machines has been;

- Permanent magnets (PMs) with no field regulation on the rotating frame

- Non-salient rotor and salient stator

- Fed from the grid

- Excited from auxiliary source

The latter options offers many advantages over the former and is also the typical choice for direct on line (DOL) connected synchronous machines. The ability to control the rotor magnetic field makes the machine viable to regulate the flow of reactive power to the grid as well as reacting dynamically to faults in the grid. In the case of fault such as disconnection of other generators and subsequence voltage drop in the grid, the machine may increase  $i_f$  and thus  $\Psi_f$  to a) avoid falling out of synchronizity b) Keeping the power-balance and maintain frequency in the grid. c) Ability to demagnetize itself to avoid the dangerous effects of internal faults in the machine. A thorough explenation of the workings of the synchronous machine can be found in classic texbooks such as [23]. The main drawback in this scheme is the need to transfer current to the field winding through (usually) carbon brushes. Due to wear and tear from the mechanical stresses these are subjected to, they contribute a large deal to the maintenance of the machine. Further drawbacks using brushes are dust from the brushes which can interfere with the rest of the machine and a slight voltage drop over the brushes.

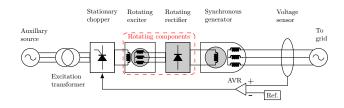

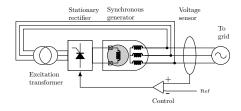

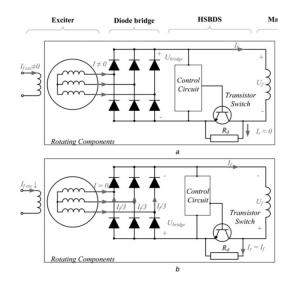

The modern, more robust excitation system transfers energy to the field winding through induction as seen in Fig. 4. The conventional static system is shown in Fig. 5

Instead of the chopper one may use, e.g. a thyristorbridge - the main concept is that through controlling the voltage over the field winding, one controls the current and thus also the magnetic field.

Fig. 4. Conventional, brushless excitation

Fig. 5. Conventional, static excitation

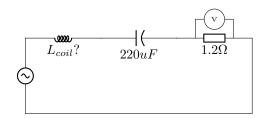

2) Open-circuit field winding as a RL-load: The field winding can be analyzed as shown in Fig. 6.

Fig. 6. The field winding ignoring the effect of mutual inductance in the open-circuit conditions of the stator

$$U_f = i_f R_f + \frac{di_f}{dt} L_f$$

$$I_f = \frac{U_f}{R_f}$$

(9)

The magnetic field produced by  $i_f$  is given by eq. (10)

$$\Psi_f = i_f L_f \tag{10}$$

The magnetic field produced by the rotor is magnetically linked with the one from the stator windings.

The solution to the first order differential eq. (9) is

$$i_f = I_f + Ce^{\frac{-t}{\tau}}$$

$$T'_{do} = \frac{L_f}{R_f}$$

(11)

$I_f$  is in other words the DC-component of the steady state field current, assuming constant  $U_f$ . If one were to consider the mutual inductance the time-constant for the RL-load would become[37];

$$L_{f}^{*} = \frac{L_{f} - (M_{f}^{2}/L_{d})}{R_{f}}$$

(12)

where  $M_f$  is the mutual inductance between stator and rotor and  $L_d$  is the stator-winding direct-axis inductance. For the sake of simplicity the simplification  $L_{f^*} \approx L_f$ for the rest of the analysis, but must of course taken into consideration when dimensioning the actual rectification system.

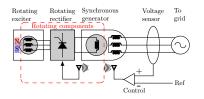

Rather than using a passive diode bridge as shown in Fig.

4, an active circuit like the VR or a thyristor bridge on the rotor may be used. The stator winding of the excitation system may be fed from a stationary diode bridge feeding an armature-winding or PMs as shown in Fig. 7.

Fig. 7. Excitation using an activ rectifier and PM exitation on the stator of the exciter.

3) Pole configuration: It may be fortunate to increase the frequency on the exciter-mains. This has to advantages:

- 1) Slightly faster demagnetization using a thyristorbridge

- 2) Smaller current-ripple on the output

- 3) Smaller filter-inductance is needed  $\rightarrow$  Smaller volume used by power-electronics on rotor.

In advantage (1) an ideal thyristor bridge can go from maximum to the minimum voltage in:

$$T_{thy,max \to min} = \frac{1}{6f_s} \tag{13}$$

which shows how the increasing the supply frequency may improve the transient capacity of the thyristorbridge.

For a typical electrical machine, is the frequency on the mains is [52];

$$f_s = \frac{\omega_{mec}}{8\pi} P_s P_r \tag{14}$$

where P is the number of poles on the stator and rotor respectively.

4) Main windings inductance: Due to the crucial effect  $L_s$  may have on the operation of the VRs operation some basic considerations of the mains-windings inductans is necessary. For an ideal solonoid, the inductance can be formulated as

$$L = \frac{\mu_0 \mu_r N^2 A}{l} \tag{15}$$

Considering the field winding as such, A can be considered almost given from the mechanical constraints on the rotor. N may however be varied more easily by sectioning the available space designated for the windings into several windings. As a consequence the cross-section for <u>each conductor</u> has to be reduced proportional to N. Keeping series connections for all the conductors making up the field windings the length of conductor that the field current passes through also increases proportional to N. Since the resistance of a conductor is given by:

$$R = \frac{\rho l}{A_c} \tag{16}$$

where  $\rho$  is a material constant, l is the length of the conductor and  $A_c$  is the cross-section.

$$R_f \propto N^2 \rightarrow$$

$$R_f \propto L_f^4 \rightarrow$$

$$U_f \propto L_f^4 \qquad (17)$$

Here it is assumed that the "new section" of windings is connected in series with the first one, in effect increasing the total length l as well as reducing the cross-section  $A_c$ . The last step in eq. (17) is assuming steady field current and drawing on eq. (9).

The induced voltage in the mains-winding is given by

$$\varepsilon = -N \frac{d\Psi}{dt} = -N \frac{d(BA)}{dt} \approx -NB \frac{dA}{dt}$$

(18)

The last approximation in eq. (18) can be made since we're in this application is considering a stationary magnetic field on the stator supplying a constant field. The perpendicular cross-section between the coil and the magnetic field A is changing with the rotation of the rotor and coil. In the case of electric magnetization on the stator Amperes law governs approximation for a long solonoid is proportional with the current-magnitude:

$$B \propto N l \mu_r I$$

(19)

In the case of PMs, the magnetic field is given by the PMs properties. In addition comes considerations regarding air-gap, angle of windings, winding-configurations and so forth, but will be left out of this discussion.

Ideally,  $\hat{B} \approx 1T$  due to saturation effect usually comes into play for materials used in stator-teeth around 1.5-2T

If one were to reduce the inductance of the stator coil the most straight forward measure is to reduce the number of coils. But one would in turn get an reduction in the induced voltage according to:

$$\frac{\Delta_N \varepsilon}{\Delta_N \mathcal{L}_s} = \frac{1}{2} \tag{20}$$

In other words, a 25% reduction in inductance due to fewer windings would result in a 50% reduction of induced voltage.

The losses in the windings determining are mainly[41]:

- Copper losses from ohmic losses in the winding.  $P_c \propto i^2 R$

- Iron losses

- Hysteresis-losses from hysteresis-loop in magnetization-demagnetization,  $P_h \propto u^a f^b$

- Core losses from induced eddy-currents, also  $P_{eddy} \propto u^2 f^2$

where i is the current in the winding, u is the induced voltage in the winding, a and b are material-specific constants.

From the above list it clear that the windings are determined by the current and voltage independently. Therefore such a rating is dimensioned after apparent power S. Achieving  $P = S \rightarrow pf = 1$  entails in other words the full utilization of the windings rating.

#### C. Magnetization and demagnetization

In this thesis, magnetization and demagnetization will refer to the transient response of the excitation system. Magnetization refers to a step in reference  $I_f^*$  from a running, synchronous state, not at startup of the generator. In this case a different approach must be taken to ensure correct grid synchronization and so forth.

1) Magnetization: In the case of e.g. a line to ground fault, the grid voltage in nearby area will be greatly reduced. The magnitude will warv with distance to the fault. type of fault (single pole or not, resistance to ground etc.), but will in many cases be of such an magnitude that it may cause a problem for the generator with synchronization with the grid. A review of the effects of generator and grid parameters on these kind of faults can be found in [42]. During a low-voltage ride-through (LVRT) fault there are mainly two issues; a) Faulty tripping of protectionsystems causing the generator to be disconnected possibly contributing to an increase of the fault and b) Weakened magnetic link between stator and rotor due to fall in stator-voltage leads to runaway speed and loss of synchronization of the synchronous generator. Only b) and measures taken on the generator-side is in scope of this thesis. There are many possible measures that can be made [43]. The valve action is typical too slow to react in time, but the excitation system can react in the matter of tens of milliseconds. An increase in  $I_f$  leads to a stronger magnetic coupling.

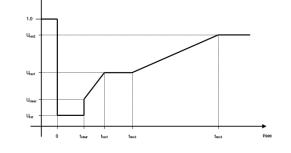

The transient behavior of synchronous generators under FRT is regulated in mostly national grid codes. In Norway, Statnett is responsible for these and are currently working on implementing EU-regulations on this field that harmonises the grid codes somewhat[1]. In fig. 8, the fault are cleared at  $t_{clear}$  and the curve shows the rising terminalvoltage after clearance.

U/p.u

Fig. 8. A typical curve for required terminal-voltages after a fault. [1]

What for the excitation system goes, it is the ceiling voltage, that is how much and how fast  $U_f$  may be increased  $U_f[pu]$  that is regulated in the grid codes rather than  $i_f$ . The Norwegian TSO Statnett is demanding voltage of  $2U_{f,n}$  over ten seconds, [32] and also dimensioning of the

Fig. 9. The classical way of demagnetization using DC-breakers [46]

system to bare  $2I_{f,n}$  over ten seconds. For the application of the Vienna this implies that a comparing quality is how fast and how much the topology is capable of increasing  $U_f$ .

In the conventional topology shown in fig. 4 this is achieved by controlling the stationary chopper or the firing angle of a thyristor bridge in its place. In most cases [29], the "auxillary source" in the fig. really is the grid. In this case the excitation-system would be rather exposed to a low voltage fault since it also would limit the available voltage at the stationary excitation-topology's terminals and thus  $U_f$ . Several other topologies [11][39] have been suggested with fast magnetization in mind. Using permanent magnets instead of an electromagnet controlled by stationary power electronics on the stator would mitigate this problem, but again demand RPE to regulate  $U_f$ .

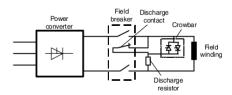

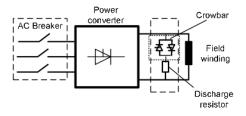

2) Demagnetization: The need for good transient qualities of the excitation system is motivated by the same aspects as magnetization. From at regulatory view the rotor-field must be able to vary in response to varying mechanical power, and to change the reactive power delivered from the machine. As a safety mechanism the field must be possible to shut down very rapidly in case of faults that warrants a rapid seizure of the power delivered to the stator-windings. Such faults can be earths on stator side, flash over in the field winding or other electrical errors on the rotor side. An excellent review of demagnetization systems is found in [46].

As seen in fig. 9, the demagnetization system consists of three (four) parts;

- (a) Power converter that may supply negative field voltage (e.g. thyristorbridge)

- (b) Field breakers to disconnect the field winding from field voltage

- (c) Discharge resistor in which the energy stored in the field windings magnetic field is dissepated.

- (d) A crowbar circuit protecting the field winding from over-voltages.

Discussing the VR, especially the necessary modifications necessary to achive a) is of interest since the VR doesn't originally allow reverse power-flow. Breaking the DCcurrent will necessarily lead to the formation of an arc, which is the reason for the extra discharge breaker that ensures commutation of the current to the *RL*-circuit consisting of  $R_{dm}$  and  $L_f$ . In many cases a voltage-dependent

Fig. 10. Using AC-side breakers [46]

non-linear resistor is used for  $R_{dm}$ . This is made out of semi conducting material and increase the resistance with increased voltage. In this way the voltage over the field winding is kept low (high voltage reduces the resistance and thus lowers the voltage thorough current surge).

Breaker on the AC-side of the converter has also been used as shown in fig. 10. Altought this leads to a much simpler breaking of the current due to the utilization of the zero-crossings, special considerations have to be taken regarding longer arcing times and three phase faults at the stator. The more mechanical compact realization of the AC-breaker is a strong argument for the utilization of these in RPE since space is a constraint.

The effects of a) and c can be described mathematical straight forward. Observering fig. 6 again, a) can be described as supplying a negative  $u_f = -|U_{dm}$ . Setting  $i_f(0) = I_f$ , the solution of the eq. (11) will be;

$$i_f = (I_f + \frac{|U_{dm}|}{R_f})e^{-\frac{t}{\tau}} - \frac{|U_dm|}{R_f}$$

(21)

d) is equivalent to setting  $U_f = 0$  and introducing the demagnetization resistance  $R_{dm}$  into the circuit. The solution then becomes;

$$i_f = I_f e^{-\frac{t}{\tau_{dm}}}$$

$$\tau_{dm} = \frac{L_f}{R_f + R_{dm}}$$

(22)

Writing the expressions with base quantities,

$$I_{f,b} = I_f$$

$$R_b = R_f$$

$$L_b = L_f$$

$$t_b = \frac{L_{f,b}}{R_{f,b}}$$

(23)

gives relative eq. from (21) and (22),

$$\begin{aligned} \ddot{c}_{f,r} &= e^{-t_r(1+R_r)} \\ R_r &= \frac{R_{dm}}{R_r} \end{aligned}$$

(24)

$$U_{r} = \frac{|U_{dm}|}{U_{f}}$$

$$i_{f,r} = (1+U_{r})e^{-t_{r}} - U_{r}$$

(25)

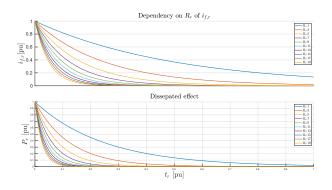

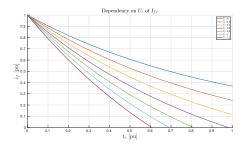

Figure 11 illustrates eq. (24), also with the relative power dissipated in the demagnetization resistance.

$$P_{dm,r} = i_{f,r}^2 R_r \tag{26}$$

The field winding is dimensioned for full-load current, but this must be heeded when choosing demagnetization resistor. Equation (25) is illustrated in fig. 12 where only  $U_r$  is varied.

Fig. 11. The dissipated amount of power falls exponentiatial relative to  $i_{f,r}$ . The effect of increasing  $R_r: 1 \rightarrow 3$  is more expressed than e.g. $R_r: 17 \rightarrow 19$ .

Fig. 12. Note that using  $U_r = \frac{|U_{dm}|}{U_f} = 0 \rightarrow U_{dm} = 0$  results in simple demagnetization through field resistor with time constant  $\tau$  and  $i_{f,r}(1) = 37\% I_f$

#### D. Demagnetization with RPE

Common practice for conventional brushless excitation fail to include a discharge resistance and so forth since a commutation link to the rotor that can fire a demagnetize signal and switch over to the demagnetize-circuit isn't in place. In the conventional brushless excitation scheme shown in fig. 4 there is no breakers, AC or DC on the rotor at all. During demagnetization the statorside excitation is turned of. In addition to the large time constant given in eq.s (11), the effect of the stator main windings will also come into play. Due to the winding-inductance the rotormains current cannot collapse immediately and contribute to the slow reduction of  $i_f$ . Notable this contribution is small since  $\frac{L_s}{L_f} << 1$  and has a much smaller time constant than the field-winding. A solution to this obvious drawback of brushless magnetization is presented in the series of papers [34], [37] and [38]. This configuration will be referred to as High-speed De-excitation for Brushless Synchronous machines (HDBS)

In fig. 13, the control circuit senses  $U_f$ . The rapid reduction of  $I_f$  and as a consequence the current into the

Fig. 13. A self-triggering demagnetization mechanism. [34]

diode bridge is not explicitly described in the research, but may e.g. be achived through a DC-breaker on the stator side. In an event where demagnetization is needed, the breakers on the stator feeding the rotor-mains will be triggered. With no voltage provided from the diode-bridge, the current in the field winding will fall and the polarity across the field winding will switch. This is the triggering signal for the control-circuitry that subsequently switches of  $Q_1$  in fig. 13. This forces the current through the demagnetization-resistance instead, leading to a demagnetization with the qualities described in eq. (22).

PM stator magnetization of the exciter requires that breakers necessarily needs to be placed on the rotor, either on the DC or AC side. If the nature of the system (e.g. very safe operations, protection of the stator side) warrants it, one could go without breakers altogether as in conventional brushless system. But as the previous discussion has highlighted, this at least demands an power-converter that is able to supply negative field voltage so that the constant rotor mains-voltage can be used to reduce the time-constant of the demagnetization.

| Excitation $\rightarrow$ | PMs      | EMs           |

|--------------------------|----------|---------------|

| Affected of              | No       | Yes, but not  |

| stator voltage dip       | NO       | instantly     |

| Breakers                 | Rotor    | Stator        |

| Alt. to reverse          | Breakers | Extra         |

| powerflow                | Dieakeis | demag circuit |

TABLE I: Consequences for stator magnetization. In the EMs case it is given that the excitations takes power from the grid.

#### E. Mechanical challenges with RPE

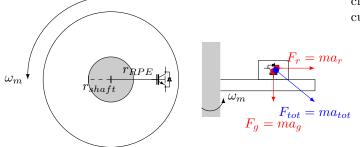

Rotating power electronics (RPE) needs to achive a high level of reliability and be relatively maintenance free to be a worth competitor to the static system using brushes. RPE is using other components than a diode bridge is not yet common in the industry and the experience regarding the mechanical effects on the power electronics are limited. In such a critical application as excitation, it is key that the components can stand the rotary forces over time. An illustration of the forces affecting a single device placed on the rotor (which is considered lying parallel with the ground) can be seen in fig. 14

Fig. 14. The placement of the device is critical for the forces affecting it.

In fig. 14  $F_g$  designates the gravitational forces ( $F_g = G$ ) and  $F_r$  the apparent rotary forces.  $\omega_m$  is the mechanical, angular velocity and the grey area designates the shaft of the generator. For most applications,  $a_g \ll a_r$ .

$$a_r = \omega^2 r \tag{27}$$

This can be seen from eq. (27) and the fact that even for relatively small rotational speed (400 rpm) and RPE very close (10cm) to the axis, the gravitational forces will be an order of magnitude lower than the once from the rotating movement.

The forces acting on the RPE will be both shear and normal forces if the PCB is placed perpendicular to the shaft and only secured thought soldering, either punchthrough or surface mounted.

1) IGBTs: Modeling of the expected overall lifetime of a semiconductor power-module is a science in itself and is usually conducted by accelerated cycling test where both turn on/off and temperature cycling is used. The most common failures are bond wire fatigue/lift off, issues such as cracking at the solder-points and cracking of substrate. A cause for these failures may often be different Coefficient of thermal expansion which leads to internal stress as the transistor expands as a consequence from heating[22]. With RPE the additional stress that must be considered are not internal, but from the large rotary forces.

Rotating diodes for excitation purposes have been applied with great results [54]. The question remains regarding the considerations that must be taken when choosing capacitors and IGBTs. Barring the life-time issues, pressure applied to an IGBT may affect the characteristics of the semiconductor. It were shown in [8] and [26] that pressure on a IGBT or MOSFET would affect parameters as transconductance, saturation current and  $v_{th}$ . The direction of the pressure relative to the current-flow is key. For illustration a cross-section of an IGBT is shown in fig. 15. In [8], it was shown that compressive stresses in the Y-direction reduced the saturation current and in [6] that compressive stress in the X-direction didn't effect the saturation current notably. As both papers states, the crystalline structure of the IGBT will determine the mechanical structures of the semiconductor. In addition, [6] shows that by knowing the crystalline orientation aligning the semiconductor correctly relative to the radi of the circular motion one may reduce the effect of saturationcurrents.

Fig. 15. A schematic view of an IGBT[51].

It should be noted that the size of the IGBTs and crystaline structure are different across the studies and from the components used in an RPE-application. The pressure that were applied were several MPAs However, comparing the results may give an indication on where the issues may arise. A simpler and probably safer solution is dimension the gate driver such that the IGBT will turn safely on and of also with modified saturation currents. At Sintef there have been conducted considerable research regarding press-packed IGBTs and film capacitors subjected to high pressure under water. Summary of the early results can be found in [18] and more detailed modeling and test-results for press-packed IGBTs in [35]. Press packed IGBTs were subjected to pressures up to clamping pressure up to 4000N and it was found that "low influence on the electrical behavior of the system in the range of rated current". Both a special-designed drivers and presspacked IGBT-modules were subjected to 100 and 300 bar liquid pressure. Also an off the shelf driver were testet on also lower pressures. Even thought the non-modified components suffered somewhat already in the 100 bar-test, they still performed.

Taking e.g. MII 200-12 A4 IGBT array from IXYS with  $m = 250g, A = 6, 8e - 3m^3$  at n1500 rpm and mounting 30cm from the center of the shaft the maximum pressure experienced of the array at the mounting (perpendicular to  $a_r$ ) is  $\approx 270kPa = 2,7bar$  using eq. (27). This indicates

that the rotary forces will not effect the electrical characteristics of the IGBTs, but as mentioned this should be tested with industry application in mind.

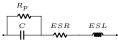

2) Capacitors: Sintef has also tested power capacitors in the same manner as press packed IGBTs with in general the same results. Electrolytic capacitors in the driver were the component which failed during high-pressure tests. The master thesis [48] is treating this research and results closer. Although having a large capacitance, this is one indication why wet-electrolyte capacitors should not be used in RPE. Another aspect is that the viscous gel in these components may be drained from one side to the other of the capacitor to the other during prolonged rotation. Using solid polymer would mitigate this danger, but limit the application regarding some demagnetization-strategies since it cannot be reversed polarized. Film- or ceramic capacitors seems to be the ideal choice on this background.

As goes for both the case of capacitors and IGBTs it must be noted that the mechanical stress these components have been subjugated to in the above mentioned research differs not only in magnitude, but also in what manner it is applied, from what would be the case with RPE. Since no research were found directly testing such components on a generator shaft, these results may indicate the expected behavior. Further research is needed, but from these results it seems that using press-packed IGBTs and film capacitors there should be no issues with the components in the RPE application.

Solder-points can also be a weak-spot for e.g. surface mounted ceramic capacitors[36].

#### F. Active rectification

In most applications of brushless excitation, thyristorbridge is used to deliver the regulated voltage to the field winding of the machine as seen in Fig. 4. Even though considered a robust solution, one of the issues is that of regulated powerfactor (pf). In an ideal thyristorbridge, the output voltage is given by;

$$\bar{u_d} = \frac{3}{\pi} \hat{u_s} (\cos \alpha - \frac{\omega L_s i_d}{\hat{u_s}}) \tag{28}$$

As shown in textbooks such as [41], the firing angle reduces the pf at the input of the rectifier. In addition, the current form is distorted to an non-sinusoidal form and in the process increasing THD thus high-frequency EMI. Since excitation demands variable output voltage, this means possibly over-dimensioning both of the rotorside mains-windings to deal with the maximum apparent power delivered for probable levels of  $u_d^*$ . If  $S \approx P$  the whole rating of the rotorside mains-winding would be utilized. Using a conventional diode-bridge with a chopper the power factor will typically lay around pf = 0.85[41], due to commutation inductances. Utilizing power electronics the armature windings can reduce it's ratings with up to 15%. For a thyristor bridge the

pf-considerations are worse since the pf is correlated with the firing-angle. To be able to provide ceiling voltage of factor 2, the output voltage in steady state has to be kept half the maximum voltage, that is, what voltage that is achievable on the output at  $\alpha = 0$ . This corresponds to a steady-state firing angle of at least  $\alpha = 60^{\circ}$  and a pf = 0.5. In addition comes considerations from the voltage loss due to commutation, increasing the firing angle. The result of this is the mains windings has to be rated twice the size of what was necessary if  $pf \approx 1$ . In other words, even though the thyristor bridge has a good controllability of  $u_d$ , the cost on main windings ratings is quite high compared to the diode bridge.

An alternative to active rectification through a thyristor bridge are Power Factor Correcting (PFC) rectifiers. These can be active or passive and allow for either uni- or bidirectional power flow depending on which topology is chosen. Both buck (M < 1)- and boost (M > 1)alternatives are available, where the modulation index Mis given for boost and buck respectively by;

$$M = \frac{2u_n^1}{U_o}$$

$$M = \frac{I_n^1}{I_o}$$

(29)

The modulation describes the relationship between the AC input and DC-output defining characteristics. A PFC-rectifier has (usually) the following qualities:

- Sinusoidal input currents

- Controlled (to a limit) pf

- Controlled output voltage

- High power density

- Small losses

- Relatively simple topologies and control of these

Sinusoidal input currents are described as THD < 5% in IEEE-standards[2].

#### G. The Vienna rectifer

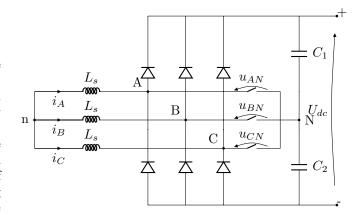

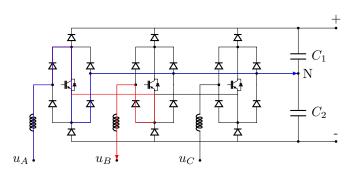

Fig. 16. EC with ideal switches for the Vienna Rectifier

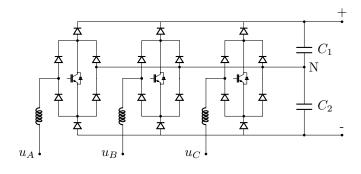

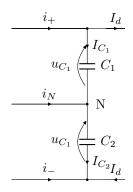

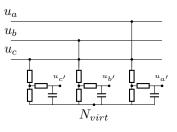

The VR is a boost-type PFC-rectifier which utilizes the capacitators  $C_1, C_2$  to achive sufficient switching-states

Fig. 17. The Vienna-rectifier realized with many diodes but only three switches.

to regulate the output-characteristics and ensure sinusoidal input-currents. The two most common topologies are shown in Fig. 16 where the switches is realized by a pair of antiparallell mosfets or IGBT, and in Fig. 17 the VR is realized with fewer switches but more diodes. For analytical purposes they are the same and Fig. 16 will be used. Defining the voltage-unbalance as;

$$\Delta u_C = U_{C1} - U_{C_2} \tag{30}$$

the voltages  $u_{Nx}$  can be written as

$$u_{xN} = \frac{U_d}{2} \left[ sgn(i_x) + \frac{\Delta u_C}{U_d} \right] (1 - S_x) \approx u_{xN} \approx \frac{U_d}{2} \left[ sgn(i_x) \right] (1 - S_x)$$

(31)

The simplification is done considering that  $\Delta u_C$  is keps small to ensure operation of the VR. There is an important requirement (IR) that arises from the topology and eq. (31):

$$sign(u_{xN}) \in (0, sign(i_x))$$

(32)

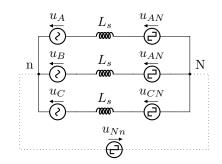

Considering the system in  $\alpha\beta$ -coordinates the system can be formulated as:

$$\vec{i_x} = \frac{\vec{u_x} - (\vec{u_x}N + \vec{u_N}n)}{\vec{Z}}$$

(33)

where  $\vec{Z} \approx j\omega L_s$ .  $u_N \vec{n}$  is the common mode voltage and can be derived assuming an virtual connection n-N. This is shown in Fig. 18

$$u_N n = \frac{1}{3} \Sigma u_{xN} \tag{34}$$

From eq. (34) and eq. (33) it is apparent that each phase-switch also affects the current in the other phases and thus are not decoupled.

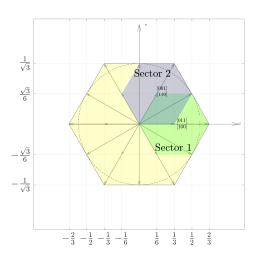

It is instructive to view the system in  $\alpha\beta$ -coordinates using the Clarc transform. From (31) it is apparent that

$$u_{xN} \in \{\frac{U_d}{2}, -\frac{U_d}{2}, 0\}$$

(35)

Fig. 18. The virtual connection illustrates the coupling of phases.

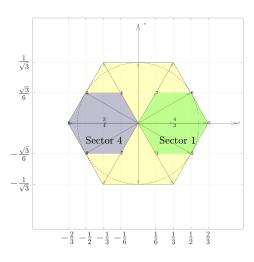

Eq. (35) generates  $3^3 = 27$  possible vectors of  $u_{xN}$ . Subtracting the illegal vectors  $u_{xN} = \left[\frac{U_d}{2}, \frac{U_d}{2}, \frac{U_d}{2}\right]$  and  $u_{xN} = \left[-\frac{U_d}{2}, -\frac{U_d}{2}, -\frac{U_d}{2}\right]$  corresponding to impossible combinations of current-signs, leaves 25 possible vectors. Applying the transformation in eq. (2) on these 25 vectors, it results in 19 unique vectors in the  $\alpha\beta$ -plane. These can be seen as grey vectors in Fig. 19. Theoretically, only four available vectors in the  $\alpha\beta$ -plane is needed to control the phasor  $\underline{u}_N$ . In other words, the Vienna rectifier offers a redundancy in switching vectors regarding space vector modulation.

However, due to the IR of the phase-currents there is only  $3^2 - 2 = 7$  available vectors at any given time, of which one is the zero-vector  $\mathbf{S}_0 = [111]$ . The available vectors are dependent on the current-polarities. The different combinations are called sectors, and can be seen fully listed in Tab. II.

| Sector | $sign(i_a)$ | $sign(i_b)$ | $sign(i_c)$ |

|--------|-------------|-------------|-------------|

| 1      | +           | -           | -           |

| 2      | +           | +           | -           |

| 3      | -           | +           | -           |

| 4      | -           | +           | +           |

| 5      | -           | -           | +           |

| 6      | +           | -           | +           |

TABLE II: Sector-numbering in the Vienna-rectifier

The numbering of the sectors is apparent observing Fig. 19, as they are counted going counter-clockwise. Each sector covers  $\frac{\pi}{3}$  electrical degrees. However, the possible voltage vectors in each sector spans  $\frac{2\pi}{3}$ . Being 6 sectors, they overlap  $\frac{\pi}{3}$  degrees. In Fig. 19, the area available to the each sector is shown colored. An important observation is that the different sectors are not sharing all vectors in the shared interval. Sector 1 and 2 is in this example, only share the switching-vector [110] and not [001], which would results in a vector in sector 2 that is a different from the one in sector 1. The IR expressed with sectors can be formulated that  $u_n$  must be in the same sector as  $\underline{i}$ .

Fig. 19. The possible switching states seen in  $\alpha\beta$ -coordinates. The numbering og the axis gives the fraction of  $u_d$ . That is, the maximum magnitude is  $\frac{2u_d}{3}$ .

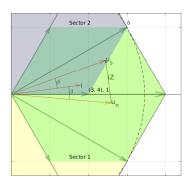

Fig. 20. Due too symmetry the switching vectors can be represented by numbers for better readability.

It is apparent from Fig. 19 that the relative angle and magnitude of the vectors are symmetric across all sectors. In some of the further discussion, the numbering in Fig. 20 will be used. Another key observation which can be drawn from this illustration is the limitation on the modulation index. In connotation with eq. (29) the following should be remembered:

- To prevent collaps of functionality due to unattainable  $u_n^*$ :  $M < \frac{2}{3}$

- To prevent over-modulation: M < <sup>2</sup>/<sub>√3</sub>

To utilize all the neighboring switching vectors: M >

These constraints in part governs the design of the inverter and supplying mains. Closer scrutiny of these will be found in the seperate control-chapters.

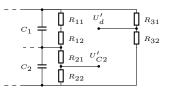

The charging of the output capacitors by the inputcurrents is key to the VRs operation. Considering only the DC-link of the rectifier:

Fig. 21. DC-link only as a basis for the discussion regarding the charging of the dc-link. Even though  $I_d$  follows the shown currentdirection, the other will fluctuate and are chosen arbitrarily in this representation.

In connotation with Fig. 21 the following expressions for the current can be found;

$$i_{\pm} = \Sigma(1 - S_x) \left(\frac{sgn(i_x) \pm 1}{2}\right) i_x$$

$$i_N = \Sigma(S_x i_x)$$

$$x \in \{a, b, c\}$$

(36)

Considering the current in the N-node; the following expression can be derived

$$\frac{du_{C1}}{dt} = \frac{i_{C_1} - \frac{i_N}{2}}{C}

\frac{du_{C2}}{dt} = \frac{i_{C_1} + \frac{i_N}{2}}{C}

\frac{\Delta U_c}{dt} = \frac{d(u_{C1} - u_{C2})}{dt} = -\frac{i_N}{C}$$

(37)

From (37) it is clear that  $i_N$  on average must equal to zero to ensure proper operation of the VR. As a consequence, we can on an average level state that;

$$\frac{di_x}{dt} \approx \frac{u_{sx} - u_{nx}}{L_s} \tag{38}$$

Observing fig.s 20 and 16 it is clear that vector 3 and 4 will have the same qualities regarding producing an voltage  $u_n$ . Using eq. (36) and taking the inverse transformation in 2 regarding these vectors (3 and 4) one sees that these have the opposite effect, switching every second sector. This is summarized in Tab. III. The result is that  $\Delta u_c$  may be controlled independently of  $u_n$ .

$|i_N|$  for the other switching-vectors are summarized in Tab. IV, the sign is sector-dependent. Another results regarding  $i_N$  is that it shares the qualities of a zerosequence current. The reason is as follows: Since  $u_{Nn}$ is controlled to be sinusoidal to achive sinusoidal inputcurrents, one has on average a natural point in N that no current should flow into. But this is ofcourse not the case due to switching. A neutral point current in a three-phase

| Sector | $\Delta U_C > 0$        | $\Delta U_C < 0$        |

|--------|-------------------------|-------------------------|

| 1      | $100 \ (S_3)$           | $011 \; (\mathbf{S_4})$ |

| 2      | $110 \ (S_4)$           | $001 \ (S_3)$           |

| 3      | $010 \ (S_3)$           | $101 \; (\mathbf{S_4})$ |

| 4      | $011 (S_4)$             | $100 \ (S_3)$           |

| 5      | $001 \ (S_3)$           | $110 \ (S_4)$           |

| 6      | $101 \; (\mathbf{S_4})$ | 010 $(S_3)$             |

TABLE III: S-vectors which can be utilized for  $\Delta U_C$ control

system can be described as a zero-sequence current [42] having harmonics of  $f_0 = 3f_s, 9f_s, 15f_s, 23f_s$ . This also goes for  $i_N$ .

| Vector | $ I_N $ |

|--------|---------|

| 1      | Medium  |

| 2      | Small   |

| 3      | Large   |

| 4      | Large   |

| 5      | 0       |

| 6      | Small   |

| 7      | Medium  |

#### TABLE IV: $|I_N|$ for different vectors

Fig. 22 shows a snapshot of the Vienna in  $\alpha\beta$ coordinates where there is a lagging pf at the mains and leading on the input of the VR. Due to the IR (expressed through sectors) there is a limitation on how much  $\underline{u}_n$  can lag or lead  $\underline{i}$ ;

$$|\beta| < \frac{\pi}{6} \tag{39}$$

Fig. 22. Current sector is still sector 1. The vector-number in sector 2 is shown in parenthesis, the ones of sector 1 not.

Expressing the relationship in Fig. 22 with phasors;

$$u_{s}|e^{j\phi} = |i||Z|e^{j\theta_{Z}} + |u_{N}|e^{j\beta}$$

$$\theta_{Z} = atan(\frac{\omega L_{s}}{R_{s}})$$

(40)

It is naturally  $\phi$  that is of greatest interest to us since it is affecting the construction of the mains-windings. The rectifiers input inductance  $(L_s)$  draws reactive power. If static power correction is not utilized, this must come from the rectifier itself. According to this observation it can be seen that the capacitive capacity on the input is larger than the inductive one.

$$\begin{aligned} |\phi| &< \beta & if \quad \beta < 0\\ |\phi| &< \beta + \zeta & if \quad \beta > 0 \end{aligned}$$

(41)

The constraint of eq. (41) corresponds to leading and lagging current on the input of the rectifier.  $\zeta$  corresponds to the angle shift due to Z and is dependent both on |i|and Z.  $\beta$  refers to the angle that corresponds to the pfwanted on the terminal of the Vienna. The limitation on power factor in the Vienna is in other words rather strict. A thorough analysis of the role of the input filter and derivation of (41) is found in [24]. The modulation index also effects the flexibility regarding pf at the input of the Vienna-rectifier [16].

#### IV. IMPLEMENTATION

#### A. Control

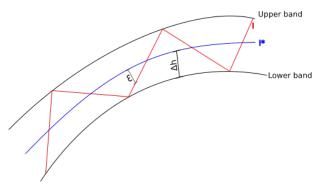

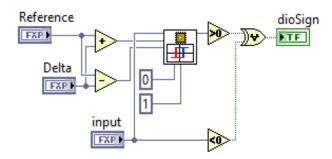

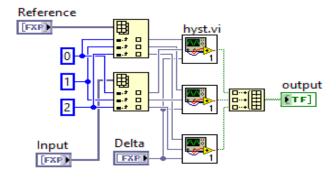

1) Hysteresis-control: In contrast to most of the literature, it is  $I_f^*$  which is the governing characteristic in this application, rather than  $u_d$ . The concept is as follows: The difference between the reference value  $i^*$  and the measured value *i* result in an error  $\epsilon = i^* - i$ . It is given that the polarity of  $\frac{di}{dt}$  is controllable. To prevent constant switching, there is a tolerance-band,  $\Delta h$  which determines how much from the reference value of the measured value is allowed to fall/rise. If  $|\epsilon| > \Delta h$  the polarity of  $\frac{di}{dt}$ , is reversed so that  $|\epsilon|$  is reduced. A general description can be seen in Fig. 23. Note that the upper and lower band can have different distances from  $i^*$  in systems where this is needed.

Fig. 23. Controlling i with hysteresis-controll

One of the most mentioned drawbacks of hysteresiscontrol is the non-constant switching frequency.

Observing Fig. 16, it is apparent that the change in phase currents,  $\frac{di_x}{dt}$  is determined both by current polarity and  $S_x$ . The magnitude increases if  $Q_x$  is closed. This can be formulated as:

$$sgn\left(\frac{di_x}{dt}\right) = \left[1 + 2(S_x - 1)\right]sgn(i_x) \tag{42}$$

Note that the currents in each phase isn't decoupled in this control-strategy. The magnitude of  $\frac{di_x}{dt}$  will be dependent

on the other switching vectors,  $S_{\not{a}}$ . Another consequence of eq. (42) is that the polarity of the phase currents has to be gauged to determine the right switching-vector. Equation (42) summarizes to the following switching logic:

$$s'_{x} = \begin{cases} 0 & ifi_{x} > i^{*} + \Delta h \\ 1 & ifi_{x} < i^{*} - \Delta h \end{cases}$$

$$s_{x} = \begin{cases} s'_{x} & ifi_{x}^{*} > 0 \\ \beta'_{x} & ifi_{x}^{*} < 0 \end{cases}$$

(43)

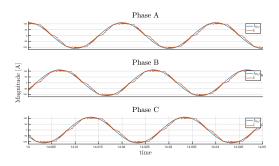

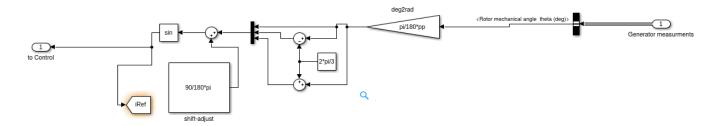

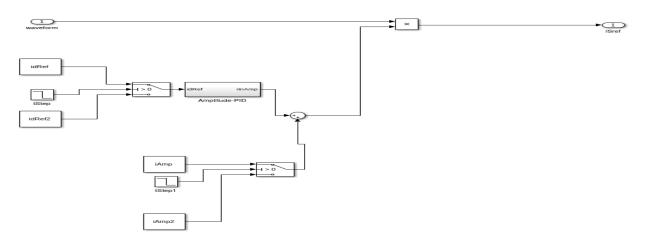

The methods used to determine  $i^*$  will vary between applications and methods. The following approaches have been used in the simulation part of the thesis:

- 1) Sinusoidal form is a requirement

- 2) Phase is determined either by PLL or directly from the supply-voltages - if a shift is needed this is calculated relative to it.

- 3) Amplitude is determined by  $I_{d*}$  or  $U_{d*}$  through a feedback loop, e.g. PID-regulator. This has proven considerable tuning if an offset isn't used.

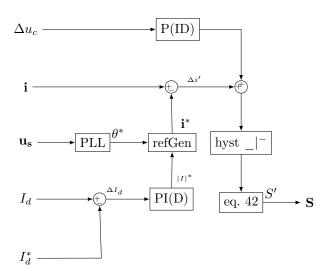

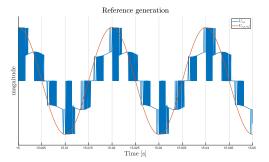

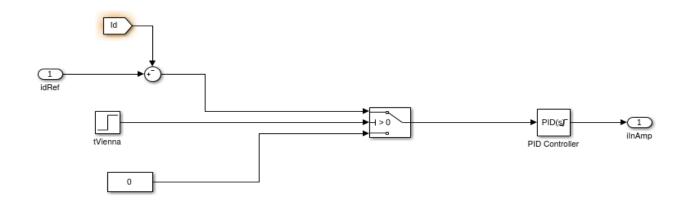

$\Delta u_C$  must be actively controlled to ensure correct operation of the rectifier. This can be done by a second controlloop, adjusting the reference signal depending on  $\Delta u_C$ . The reason for that this very simple control works can be seen from Tab. IV. A larger  $\Delta U_c$  will cause a higher  $|i_s^*|$  and thus less utilization of switching vectors 3, 4, 1, 2 ( $|I_N| = large, medium$ ) relative to 6, 2 ( $|I_N| = small$ ). Seen together with eq. (37) this leads regulation of  $\Delta U_c$ . The input to this control-loop, easiest implemented as a Pcontroller, can be  $\Delta u_C$  or the direct cause of  $\Delta u_C$ , which noting eq. (37), is  $i_N$ . A conventional hysteresis control which uses a P-controller and  $\Delta u_C$  is shown in Fig. 24.

Fig. 24. A very basic hysteresis-control

A more advanced hysteresis control utilizing  $u_{Nn}$ and the filter-inductances to decouple the three phases is suggested in [10]. Here, a virtual Nn connection is established like shown in Fig. 18 to calculate the correcting signal to the reference. Yet another controlmethod that is used is the injection of a third-harmonic component from  $i_s$  into the reference, noting that  $f_N = 3f_s[20]$ . In addition to a simple and independent control of each phase, this strategy ensures an inherent stability of the center point balance. Moreover, it has also been shown in [25] that it is possible to realize satisfactory current control without use of a controller multipliers. In the scope of Fig. 24, this method is equivalent to greatly simplify the workings of the refGen-box which calculates the actual waveform of the reference current.

## B. Control criteria

1) Rough estimation of input-currents: The tuning of the control-loop supplying the amplitude of the inputcurrent is made considerably easier having a set-point which the PID-controller adjust to. In other words, combining a feed-forward model with a feedback loop. Considering a few assumptions one can get satisfactorily results:

- pf = 1 at the terminals of the VR

- Lossless operation

- Sinusoidal input-currents and voltages

- A guess estimation  $i_{s,guess}$  of the input-current is supplied.

Using the active power on the input and output, as well as the considerations from (40) one can set up the following relations:

$$P_{out} = I_f u_f = \frac{I_f^2}{R_f}$$

$$P_{in} = \frac{3}{2} \hat{U}_n \hat{I}_n$$

(44)

Equating  $P_{out} = P_{in}$ , this results in the following estimate

$$\hat{i_s} \approx \frac{2}{3} \frac{I_f u_f}{\hat{u_n}} \tag{45}$$

To determine what magnitude  $\hat{U_{nx}}$ , one can observe (29) which gives:

$$\hat{u_n} \in [\frac{1}{3}U_d, \frac{2}{3}U_d]$$

(46)

keeping the limitation on modulation factor in mind. An mathematical aspect here is that  $U_{Nn}$  has been ignored since it on average is zero, but in power-considerations over time this still gives satisfactorily results.

In addition to thermal and saturation issues, the VRlends itself to further constrains on  $\hat{i}_s^*$ . These are invoked in conjecture with the constrains described below (50) regarding maximum filter inductance. An additional factor limiting  $\hat{i}_s^*$  is the zero vector. When the zero-vector is active, no current flows into the dc-link. In other words,  $\mathbf{S}_0$ serves to maintain the current form, but in no form uphold the output current. In normal operation this should pose no problems, but this can at higher magnitudes of current limit the operation through the upper limit for  $\hat{i}_s^*$ .

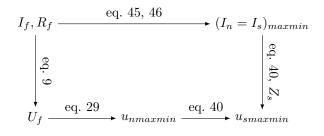

Fig. 25. Flowchart for determining the mains-voltages from  $I_f$  and M-limitations.

2) Conflict between capacitor-voltage-difference and *current-signal:* As  $i_s$  rises, also  $I_N$  must rise due to the operation of the VR. As explained in the theory,  $\Delta U_c$ also rises and contributes in a to larger degree to the hysteresis-reference. If the current is large enough, this signal will dominate and the current cannot anymore follow it's reference since the capacitor-part is dominating. There exists two solutions to address this issue:

- 1) Increase capacitance

- 2) Dynamic PID-controller of the  $\Delta U_c$

Item (1) is problematic due to realization and size in RPE. Item (2) will only work on very short time scales, e.g. if the reference is set high for a brief moment. If  $\Delta U_c$  becomes too large the whole operation of the VR is jeopardized.

3) Modulation factor and maximum supply voltage: Designing the Vienna with the hysteresis-control in mind one has to heed the limitation on modulation-factor. Given an mains-impedance  $Z_s$ , a field current  $I_f$  and the limitation given regarding the modulation factor M. The derivation in the previous subsection is used to determine  $I_s$ , but this will not have a large impact as a limiting factor, relatively seen. For typical applications the magnitude of the input-current doesn't need to be found since this will have a small effect on the overall limitation. It is important to emphasize that, given  $\hat{u}_s$  from the flowchart 25,  $I_f$  may still be increased. The challenges arises if  $I_f^*$ falls to minimal values and should be accounted for in the control-strategy. Not doing this would result in the control-strategy trying to achieve an  $u_n^*$  that lies outside the hextagon of possible switching states shown partly in Fig. 22. This can also be interpret as a an upper limitation on  $u_s$ . Observing the illustration in Fig. 26 it is apparent that a too large  $u_s$  results in over-modulation since for the given  $I_s$  and  $Z_s$  it is not possible to have a  $u_n$ inside the hexagon. The size of the hexagon is determined by  $U_d$  which again is found from the output current using eq. (11).

4) Minimum field-current: If  $\mathbf{S} = [000]$  the VR operates as a diode-bridge and the dc-component of the output voltage is given by:

$$U_{f,000} = \frac{3\sqrt{3}}{\pi}\hat{u_s}$$

(47)

The associated  $I_f$  can be found through (9). In hysteresiscontrol the use of individual S-vectors aren't controlled,

Fig. 26. A too large input-voltage may result in over-modulation.

also not the zero-vector  $S_0 = [111]$ . This entails that if a  $\hat{i}_{s}^{*}$  signal is given that is *below* that associated with  $i_{f,000}$  there is no way of controlling that the switching-logic produces more instances of  $\mathbf{S}_{\mathbf{0}}$  and thus ensuring reduction of  $i_f$  relative to  $i_{f,111}$ . Using the zero-vector and effectively shorting the three phases is the only way of not dumping any current into the dc-link. Baring saturation effects this would also charge the magnetic field in  $L_s$  which would result in voltage spikes when the switches changes sign. Therefore,

$$I_{f,min} = I_{f,111} = \frac{3\sqrt{3}}{\pi} \hat{u_s} \frac{1}{R_f}$$

(48)

Note that this limitation is only relevant for steady state during demagnetization a different control strategy is used altogether.

5) Winding inductance: Another, crucial limitation of this control-strategy is linked to how fast the input currents may change. Observing eq. (38), this is dependent on three parameters; the supply voltage, the input-inductance and  $u_{nx}$ . For the hysteresis-control to work, the  $\frac{di_x}{dt}$  must at all times be larger than the rate of change of the reference value  $i_{sx}^*$ . This can be put as;

$$\frac{di_x}{dt} = \frac{1}{L_s} |(u_{sx} - u_{nx})| \rangle \frac{di_x^*}{dt}$$

$$\frac{di_a}{dt} = \frac{1}{L_s} |(U_{sa}\sin((\omega_s t) - u_{na})| \rangle \hat{I_a}^* \omega \cos(\omega_s t)$$

(49)

Here phase A is used to and defined with no shift from a sine wave for illustration purposes. In the hysteresisscheme the different switching strategies are determined independently and thus the "worst case" should be considered. These can be summarized as:

- $\sin(\omega_s t) \approx 0$

- $i_s = \hat{I}_s$ , may be found from eq. (45)  $u_{nx} = \frac{U_d}{3}$ , observing eq. (46)

Rearranging eq. (49) for  $L_s$  and considering the worst case situation, the expression becomes:

$$L_s << \frac{I_f R_f/2}{\omega_s \hat{I}_s} \tag{50}$$

As the simulations will suggest,  $L_s$  should be as small as 20% of the maximum inductance found in (50). This is due to the fact that also the other phases will be affected by faulty switching.

Traditionally, the input impedances is calculated from a minimum value since common applications haven't been to connect the VR to windings with such stator inductances as in the case with RPE. To smooth the current than a minimum inductance need to be calculated. This minimum inductances can be found from:

$$L_s > \frac{u_s - u_n}{\Delta I_s f_\Delta}.$$

(51)

Equation (51) can't give an unambiguous result alone since  $u_s$  varies through the period while  $u_n$  according to (35) is semi-constant. Using PWM-control  $f_{\Delta}$  is constant, but in the case of hysteresis-control this will wary. The average switching frequency is not easily determined since it is also determined of the system and thus also  $L_s$  and  $\Delta I_s$ . A upper limitation on  $f_{\Delta}$  may be set to minimize switching losses and ensure correct operations of the drivers.

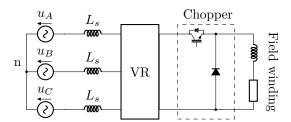

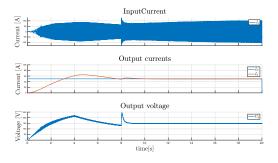

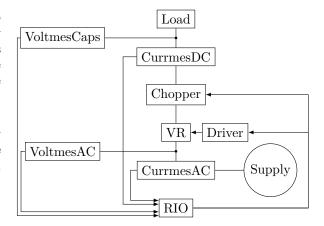

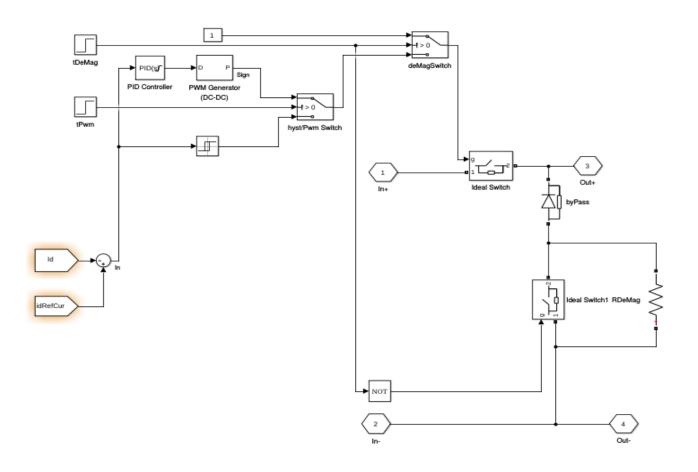

6) Additional chopper: Due to the large time constant of the field-winding, there should be implemented some kind of additional circuitry to possibly hurry the demagnetization. A simple and effective topology is to use a singlequadrant chopper. This will be connected on the output of the VR. Utilizing this chopper one may also greatly simplify the control of the VR. In this control-scheme the VR only controls the total voltage of the DC-link and ensures sinusoidal input-currents. The chopper ,using pwm or hysteresis-control, controls the output current. The addition is shown in Fig. 27.

Fig. 27. The addition of a chopper makes faster demagnetization possible.

The chopper decouples the amplitude of the input and output currents. This makes an important controlconstraints of the hysteresis-control void, namely eq. 48 setting a minimal  $I_f$ . What  $\hat{i}_s^*$  goes, this could now be derived from the desired  $U_d$ .  $U_d^*$  should be set at least to:

$$U_{d,absmin}^* >> 2U_f^* \tag{52}$$

This is motivated that in the case of a need to go to ceilingvoltages (2 p.u.) this could be achieved by changing the on-times (possible turning completely on). 7) Communication: In the case of brushless excitation with an active rectifier an communication link needs to be used. There is a wide variety of RF-transmitters in the marked several protocols (Wi-Fi, Bluetooth, Ziigbee etc.) that has been applied in wireless control of power electronics. Nonetheless, one has to make the consideration regarding switching-frequency and baudrate of the communication link. For switching of e.g. IGBTs in the circuit the necessary transfer-frequency is:

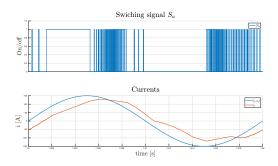

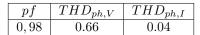

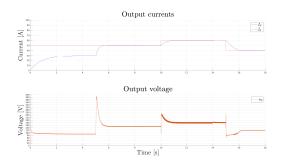

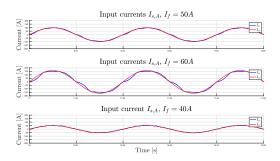

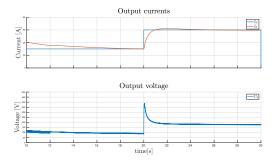

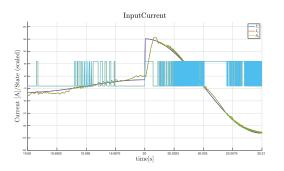

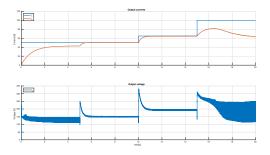

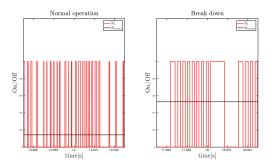

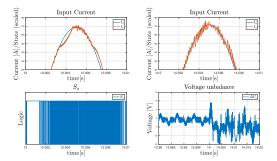

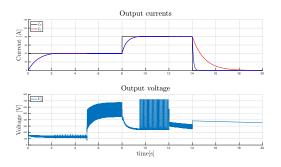

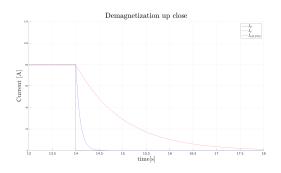

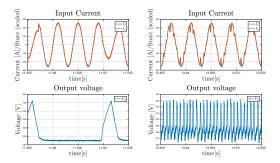

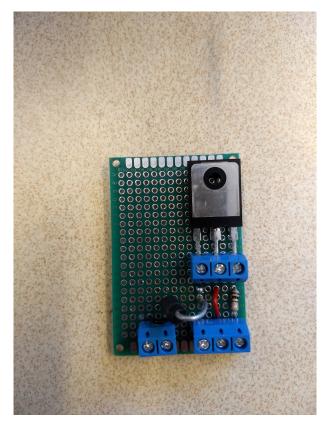

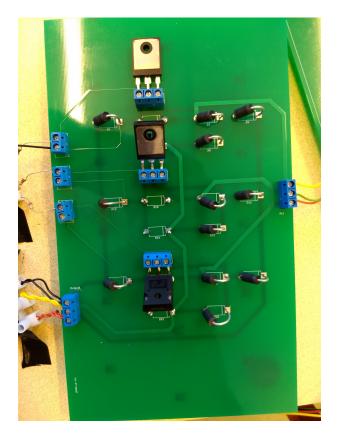

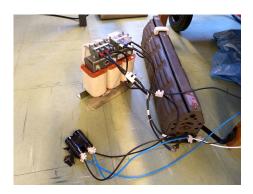

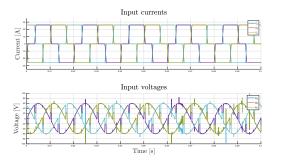

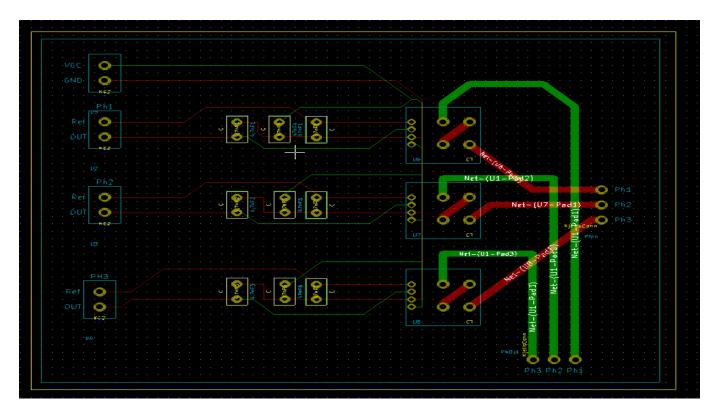

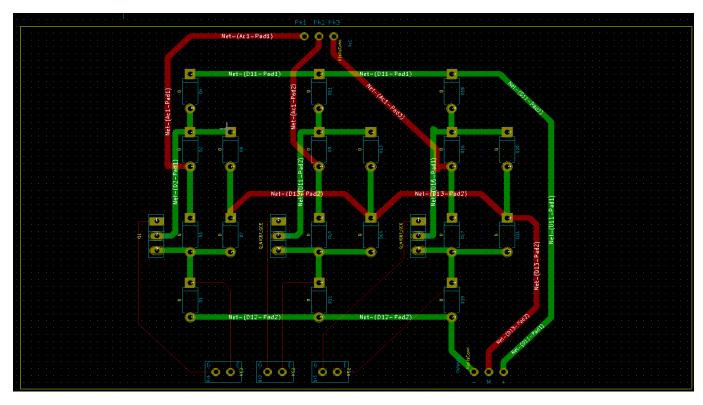

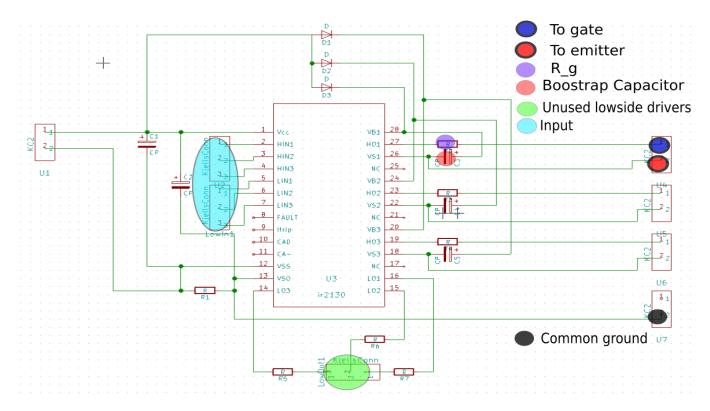

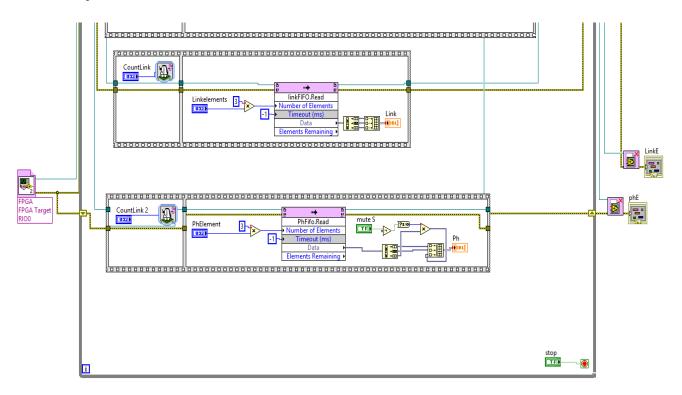

$$f_t \approx f_p(RN_Q + K) \tag{53}$$