#### ABSTRACT

| Title of Dissertation:    | ULTRA-THIN ON-CHIP ALD LIPON AS<br>SOLID-STATE ELECTROLYTE FOR HIGH<br>ENERGY AND HIGH FREQUENCY<br>CAPACITOR APPLICATIONS |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------|

|                           | KUNAL AHUJA<br>Doctor of Philosophy, 2022                                                                                  |

| Dissertation directed by: | Professor F. Patrick McCluskey<br>Department of Mechanical Engineering                                                     |

|                           | Professor Gary Rubloff<br>Department of Material Science and Engineering                                                   |

Liquid electrolytes dominate the supercapacitor market due to their high ionic conductivity leading to high energy and power density metrics. However, with the increase in demand for portable and implantable consumer electronics, all solid-state supercapacitor systems with high safety are an attractive option from both application perspectives and their similar charge storage mechanism. For solid state ionic capacitors, there remains significant room for innovation to increase the ionic conductivity and capacitor architecture to enhance the performance of these devices. Nano-structuring along with advanced manufacturing techniques such as atomic layer deposition (ALD) are powerful tools to augment the performance metrics of these all-solid-state capacitors that can compete with state-of-the-art liquid electrolyte-based supercapacitors. This dissertation has two primary objectives; 1) Study the behavior of polymorphs of ALD LiPON as

a capacitor material and 2) Enhance the performance metrics using advanced materials and 3D nanostructuring for improved energy storage and high-frequency applications.

In this work, ALD LiPON-based solid state capacitors are fabricated with a gold current collector to study the behavior of the solid electrolyte. LiPON shows a dual energy storage behavior, in low frequency (<10 kHz), LiPON shows an ionic behavior with electric double layer type energy storage, beyond this frequency, LiPON shows an electrostatic behavior with a dielectric constant of 14. The capacitor stack's thin film structure and dual frequency behavior allow for extended frequency operation of these capacitors (100 Hz to 2000 MHz). Next, LiPON's energy storage metrics are enhanced by pseudocapacitive energy storage behavior and increased surface area using ALD oxy-TiN. Finally, new fabrication techniques and ALD recipes are developed and optimized for integration into 3D templates. For fabrication of these capacitors, the material's chemistry is analyzed, and ALD techniques are developed for deposition of electrode/electrolyte materials and current collectors into the 3D nanostructures. The intermixing during the ALD processes is studied to understand the behavior and reliability of these thin films. This work highlights LiPON characteristics as a capacitor material for high-energy and highfrequency applications. Though incomplete, we discuss progress towards the development of all ALD solid-state 3D supercapacitors that can compete against state-of-the-art capacitors available in the market.

#### ULTRA-THIN ON-CHIP ALD LIPON CAPACITORS FOR HIGH ENERGY AND HIGH FREQUENCY APPLICATIONS

by

Kunal Ahuja

#### Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park, in partial fulfillment of the requirements for the degree of Doctor of Philosophy 2022

Advisory Committee:

Professor, F. Patrick McCluskey, Chair

Professor, Gary W. Rubloff, Co-Chair

Professor, Sang Bok Lee (Dean's Representative)

Professor, Peter Sandborn

Professor, Aris Christou

Professor, Hugh Bruck

Associate Research Scientist, Keith Gregorczyk

© Copyright by Kunal Ahuja 2022

# Dedication

To my parents, sister, and grandmom.

## Acknowledgements

First and foremost, I want to express my sincere gratitude to my advisors, Prof. Patrick McCluskey and Prof. Gary Rubloff, for giving me the opportunity to work with them at CALCE and ANSLab, respectively. Their thorough guidance, deep understanding and invaluable advice helped steer my research positively. I am also grateful to Dr. Keith Gregorczyk for introducing me to the nano-materials world with his never-ending motivation and technical expertise. I would also like to extend my gratitude to Dr. Alex and Dr. David, for further technical guidance in molding my research profile. Altogether, I have been fortunate enough to work at the CALCE and ANSLab for providing me the best technical and social exposure along with longlasting memories with all the people with whom I have worked. I also sincerely acknowledge the technical inputs and advice from my committee members towards my research.

I am also thankful to my colleagues –Blake, Nam, Victoria, Daniela for creating an every-day healthy environment in the lab, instilled with sense of humor and technical learnings. Besides this, I am also indebted to my best friend of more than ten years, Gargi Kailkhura and Veeresh Ayyagari, for having my back in all my endeavors, starting from our undergrad days to the present. From sharing same undergrad classes to graduating together with Ph.Ds at the same university, all three of us have shared a common research and personal journey. To add to my family of friends, I am thankful to my cat, Stella, whom I found in Dr. McCluskey's lab, for her indispensable love and support.

And not to forget, I am here because of my parents, who ensured the best things for me at every step in my life. Their undying love has given me the strength to face all the challenges. I also appreciate the love and care of my sister, who has been instrumental in my shaping my life since our childhood. Lastly, I thank my grandma for always showering her love towards me.

In the end, I want to thank Murata for the needed financial and technical support which was critical and inevitable during my time at UMD.

# Table of Contents

| Preface                                          | .Error! Bookmark not defined. |

|--------------------------------------------------|-------------------------------|

| Foreword                                         | .Error! Bookmark not defined. |

| Dedication                                       | ii                            |

| Acknowledgements                                 |                               |

| Table of Contents                                | v                             |

| List of Tables                                   | vii                           |

| List of Figures                                  |                               |

| List of Illustrations                            |                               |

| List of Abbreviations                            |                               |

| Chapter 1: Introduction                          |                               |

| 1.1 Motivation                                   |                               |

| 1.2 What are Capacitors?                         |                               |

| 1.2.1 Thin Film Solid State Ionic Capacitors     |                               |

| 1.3 Literature Survey: Solid State Electrolyte   |                               |

| 1.3.1 Polymer Electrolyte                        |                               |

| 1.3.2 Inorganic Solid State Electrolyte          |                               |

| 1.4 Atomic Layer Deposition of LiPON             |                               |

| 1.5 Dissertation Overview                        |                               |

| Chapter 2: Experimental Techniques               |                               |

| 2.1 Advanced Nanostructures Laboratory (ANSLa    | b) 15                         |

| 2.2 Atomic Layer Deposition                      |                               |

| 2.3 X-ray Photoelectron Spectroscopy (XPS)       |                               |

| 2.4 Spectroscopic Ellipsometry                   |                               |

| 2.5 Dry Reactive Ion Etch (DRIE)                 |                               |

| 2.6 Electrochemical Analysis                     |                               |

| Chapter 3: On-Chip ALD LiPON Solid State Ca      |                               |

| Application                                      |                               |

| 3.1 Overview                                     |                               |

| 3.2 Introduction                                 |                               |

| 3.3 Experimental Procedure                       |                               |

| 3.3.1 Device fabrication                         |                               |

| 3.3.2 Device Characterization                    |                               |

| 3.4 Results                                      |                               |

| 3.4.1 Characterization and Metrology of ALD L    |                               |

| 3.4.2 Electrochemical Impedance Spectroscopy     |                               |

| 3.2.3 Cyclic Voltammetry Comparison              |                               |

| 3.4.3 Chronoamperometry                          |                               |

| 3.2.5 Stability                                  |                               |

| 3.5 Application                                  |                               |

| 3.6 Conclusion                                   |                               |

| Chapter 4: All Solid state ALD LiPON capacitor v |                               |

| Materials                                        |                               |

| 4.1 Introduction                                             | 49    |

|--------------------------------------------------------------|-------|

| 4.2 ALD TiO <sub>2</sub> and TiN Asymmetric Capacitors       | 50    |

| 4.2.1 ALD TiO <sub>2</sub> Recipe                            | 50    |

| 4.2.2 ALD TiN Recipe                                         | 52    |

| 4.2.3 Device fabrication                                     | 53    |

| 4.3 Results: ALD TiO <sub>2</sub> Asymmetric Capacitors      | 53    |

| 4.3.1 Characterization and Metrology of ALD TiO <sub>2</sub> | 54    |

| 4.3.2 Electrochemical Characterization                       | 55    |

| 4.3.3 Dunn's Analysis                                        | 61    |

| 4.3.4 Performance of TiO <sub>2</sub> Capacitors             | 62    |

| 4.4 Results: ALD TiN Asymmetric Capacitors                   | 64    |

| 4.4.1 Characterization and Metrology of ALD TiO <sub>2</sub> |       |

| 4.4.2 Electrochemical Characterization                       | 67    |

| 4.4.3 Stability of TiN capacitors                            | 69    |

| 4.4.4 Performance of TiN Capacitors                          | 70    |

| 4.5 Conclusion                                               | 71    |

| Chapter 5: Towards Integration with On-wafer 3D Substrates   | 73    |

| 5.1 Why 3D?                                                  |       |

| 5.2 Anodic Aluminum Oxide UMD                                | 75    |

| 5.2.3 AAO Manufacturing UMD                                  | 75    |

| 5.2.3 AAO Architecture                                       | 76    |

| 5.3 Process Modification for Full ALD stack development      | 77    |

| 5.4 Etching: ToF-SIMS                                        | 80    |

| 5.5 XPS Depth profile                                        | 82    |

| 5.6 Etch at FABLAB UMD                                       | 85    |

| 5.7 Integration into 3D AAO pores for High Energy Density    | 90    |

| 5.8 Conclusion                                               | 96    |

| Chapter 6: Conclusion and Future work                        | 98    |

| 6.1 Conclusion                                               | 98    |

| 6.2 Future Work                                              |       |

| AppendicesError! Bookmark not defi                           |       |

| GlossaryError! Bookmark not defi                             |       |

| Bibliography                                                 | . 103 |

|                                                              |       |

This Table of Contents is automatically generated by MS Word, linked to the Heading formats used within the Chapter text.

# List of Tables

| Table 1: Gel polymer electrolyte used in supercapacitors                  | 6  |

|---------------------------------------------------------------------------|----|

| Table 2: Inorganic SSE and their ionic conductivity                       | 7  |

| Table 3: Inorganic SSE for supercapacitors                                | 8  |

| Table 4: ALD parameters for different polymorphs of LiPON                 | 13 |

| Table 5: ALD TiO2 recipes                                                 | 51 |

| Table 6: Ion milling etch at FABLAB UMD, process parameters and etch rate | 86 |

# List of Figures

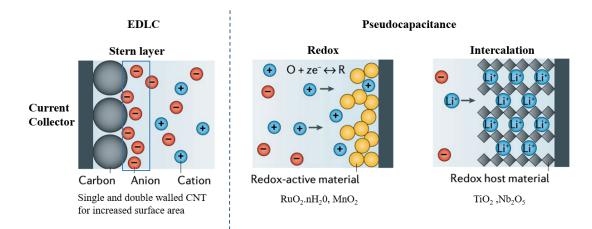

| Figure 1: Supercapacitors based on charge storage, EDLC and Pseudocapacitance 2         |

|-----------------------------------------------------------------------------------------|

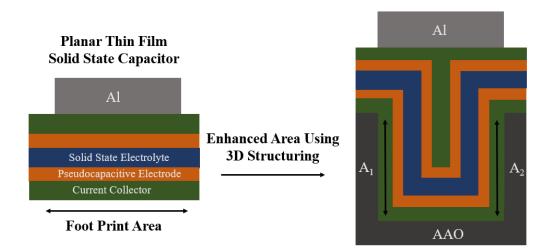

| Figure 2: 3D structuring to enhance energy and power density metrics                    |

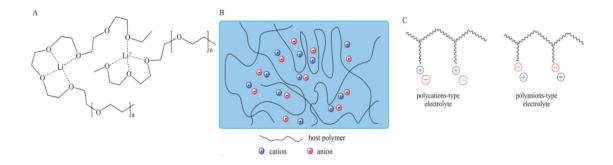

| Figure 3:P Schematic diagrams of (a) a dry solid polymer electrolyte (b) gel polymer    |

| electrolyte, and (c) a polyelectrolyte                                                  |

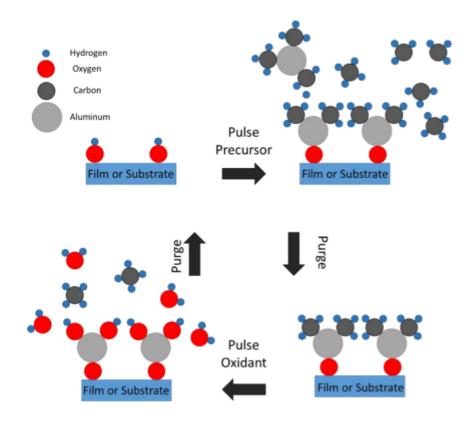

| Figure 4: Reaction Scheme of ALD Aluminum Oxide process                                 |

| Figure 5: (a) Phase diagram showing LiPON compositions in the LixPOyNz space.           |

| (b) Possible N binding environments in LiPON structures. Na is apical N, Nd is          |

| doubly coordinated N, Nt is triply coordinated N. Color code: N (blue), O (red), P      |

| (gray). From Lacivita                                                                   |

| Figure 6: Schematic of ANSLab equipment used to fabricate, characterize, and            |

| evaluate materials in this dissertation                                                 |

| Figure 7: Fiji-F200 ALD Reactor (Mario) in ANSLab. Mario is equipped with in-line       |

| mass spectrometry sampling and in-operando spectroscopic ellipsometry. ALD films        |

| can be transferred directly to a surface analysis system for XPS through the RTTA       |

| UHV transfer cham                                                                       |

| Figure 8: Kratos Ultra DLD surface analysis system in ANSLab used for XPS               |

| measurements                                                                            |

| Figure 9: (a) Biologic VSP potentiostat (b) LiPON SSE undergoing electrochemical        |

| testing                                                                                 |

| Figure 10: (a) Sample holder (b) Shadow mask for ALD (c) Shadow mask for top            |

| contacts                                                                                |

| Figure 11: Thermal LiPON XPS spectra high resolution scan (a) Li 1s (b) P 2p (c) O      |

| 1s (d) N 1s                                                                             |

| Figure 12: Plasma LiPON XPS spectra high resolution scan (a) Li 1s (b) P 2p (c) O 1s    |

| (d) N 1s                                                                                |

| Figure 13: FIB-SEM cross-section of (a) Thermal LiPON (b) Plasma LiPON                  |

| Figure 14: (a) Nyquist plot comparison between tLiPON and pLiPON (b)                    |

| Capacitance and Phase Angle as a function of frequency (tLiPON) (e) Capacitance         |

| and Phase Angle as a function of frequency (pLiPON) (d) Imaginary Capacitance as        |

| a function of frequency (thermal)                                                       |

| Figure 15: CVs (a) tLiPON at low scan rate (b) tLiPON at high scan rate (c) pLiPON      |

| at low scan rate (b) pLiPON at high scan rate                                           |

| Figure 16: Leakage Current under 2V DC bias (a) Thermal LiPON (b) Plasma LiPON          |

|                                                                                         |

| Figure 17: (a) GCD for 10000 cycles (b) Nyquist plot at different applied potential (c) |

| Phase angle as a function of frequency at different applied potential                   |

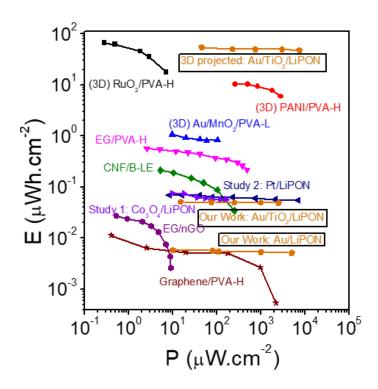

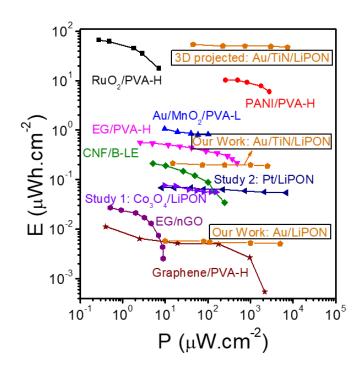

| Figure 18: Ragone Plot                                                                  |

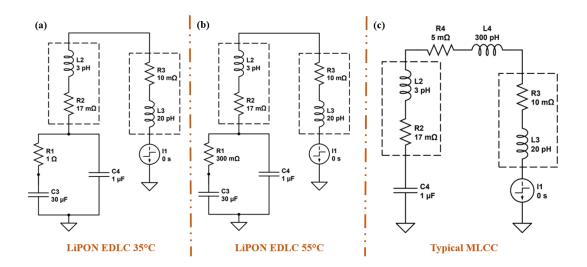

| Figure 19: Capacitor impedance circuit with wired connection (a) LiPON EDLC at          |

| 35°C (b) LiPON EDLC at 55°C (d) Typical MLCC                                            |

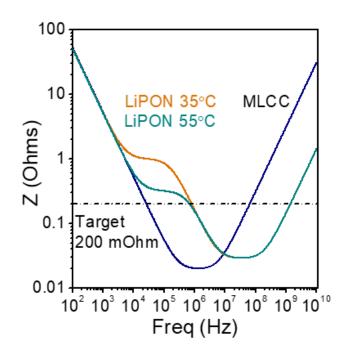

| Figure 20: Comparison of impedance spectra of LiPON capacitors with state of the        |

| art MLCCs                                                                               |

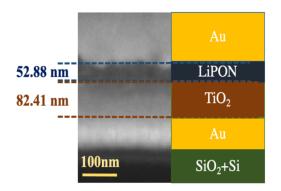

| Figure 21: Asymmetric Capacitor Stack (a) FIB-SEM image with cartoon (b) picture        |

| of fabricated asymmetric capacitor                                                      |

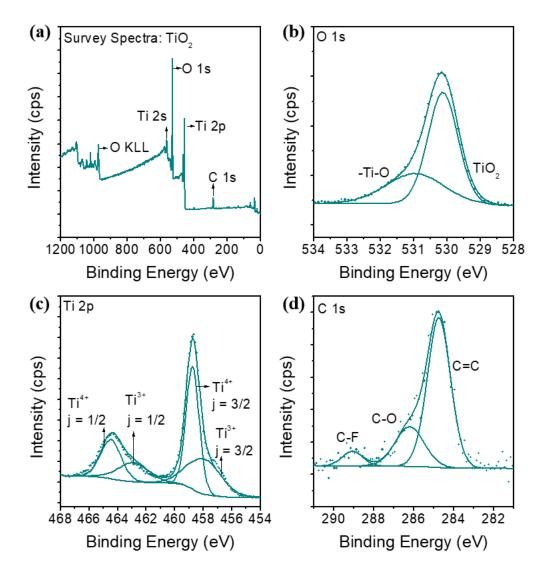

| Figure 22: XPS of TiO2 (a) Survey Spectra (b) high resolution O 1s (c) high             |

| resolution Ti 2p (d) high resolution C 1s                                               |

| viii                                                                                    |

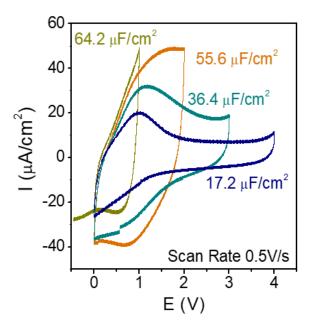

| Figure 23: Characterization of asymmetric capacitor (a) CVs 0-1V to 0-4V at           |

|---------------------------------------------------------------------------------------|

| 500mV/s                                                                               |

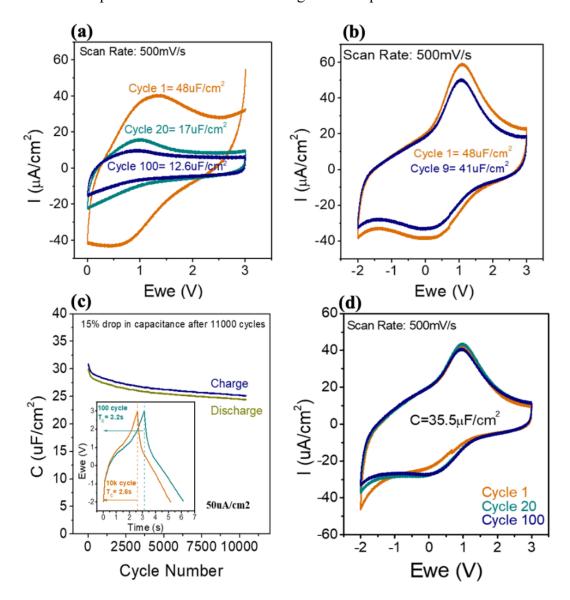

| Figure 24: Characterization of asymmetric capacitor (a) CVs 0-3V at 500mV/s (b)       |

| CV between -2V to 3V at 500mV/s (c) 10000 charge discharge cycles (d)100 CV           |

| cycles post 10k charge discharge cycles                                               |

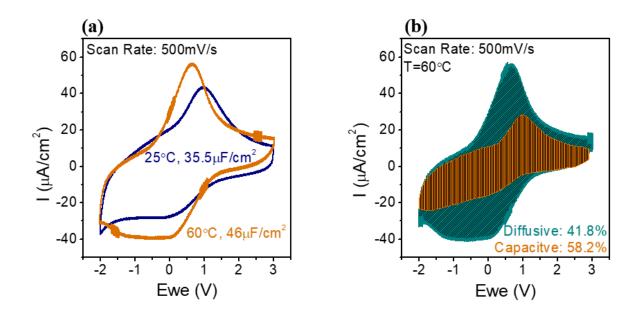

| Figure 25: Asymmetric Capacitor (a) CV comparison at 25C and 60C (b) Dunn's           |

| analysis at 60C, 500mV/s                                                              |

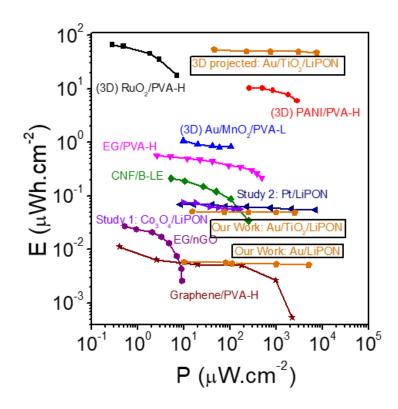

| Figure 26: Ragone plot showing a comparison to current state of the art 2D and 3D     |

|                                                                                       |

| capacitors                                                                            |

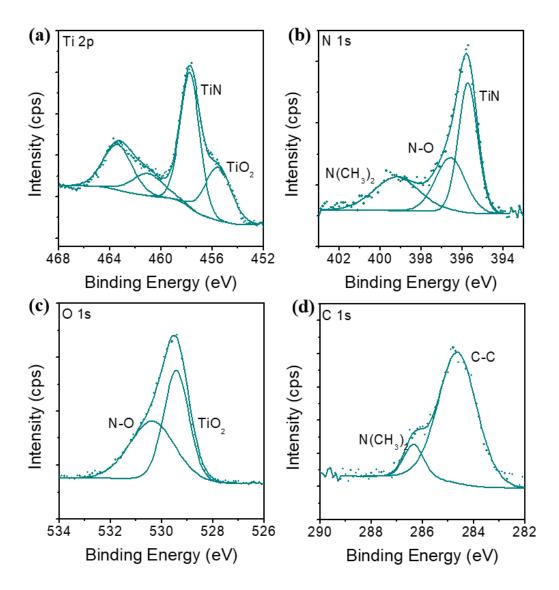

| 1s                                                                                    |

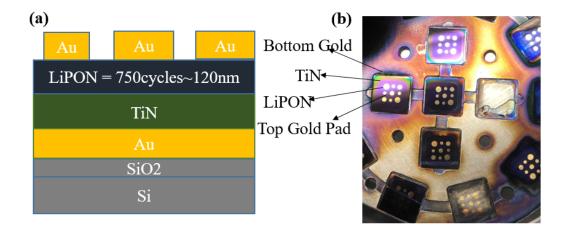

| Figure 28: (a) Sketch of the asymmetric stack (b) Picture of the capacitor            |

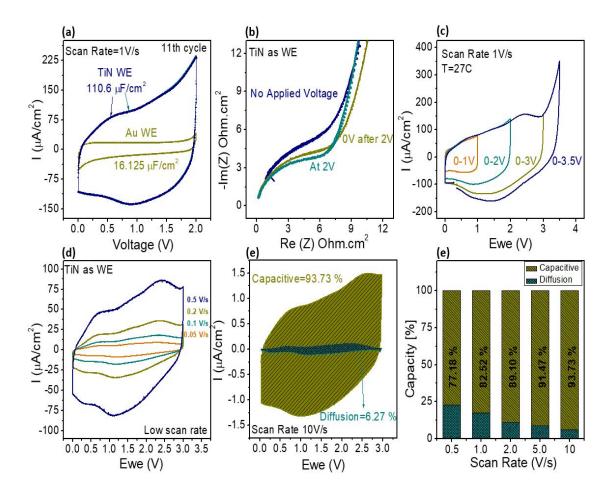

| Figure 29: (a) CVs with TiN and Au as WE (b)Nyquist plot before and after applying    |

| 2V (c) CVs done at different voltage window (d) CVs at low scan rate with TiN as      |

| WE (e) Dunn's analysis at 10V/s (f) Comparison between capacitive and diffusion       |

| current at different                                                                  |

| Figure 30: (a) GCD at 200uA/cm2 between (0-3)V (b) 500 CV cycles before GCD (c)       |

| 1000 CV cycles after GCD                                                              |

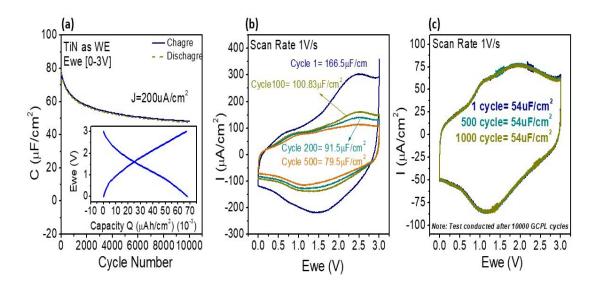

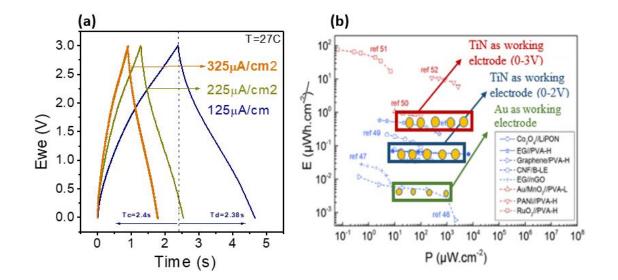

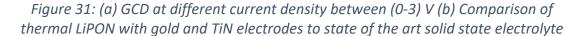

| Figure 31: (a) GCD at different current density between (0-3)V (b) Comparison of      |

| thermal LiPON with gold and TiN electrodes to state of the art solid state            |

| electrolyte65                                                                         |

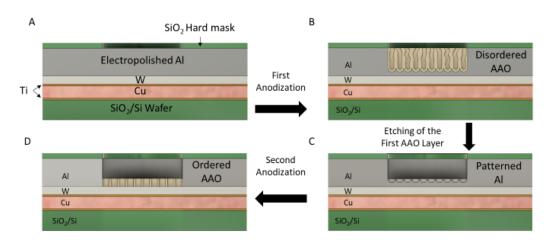

| Figure 32: A schematic of the UMD developed 200V Thompson's method process. A         |

| stack of materials is deposited by PVD as shown in (A). After which standard          |

| 1 1                                                                                   |

| photolithography is used to define regions for anodization with a SiO2 hard mask. A   |

| first anodization is conducted, as shown in (B), where the initial pore formation is  |

| random, but aligns at the bottom of the pores. The disordered AAO is then removed,    |

| leaving an ordered pattern of divest in the Al layer, as shown in (C). Finally (D), a |

| second anodization is conducted producing well-ordered pores. Post processing is      |

| done to widen the pores and remove the WO3 plug at the bottom                         |

| Figure 33: Anodized Aluminum Oxide Schematic                                          |

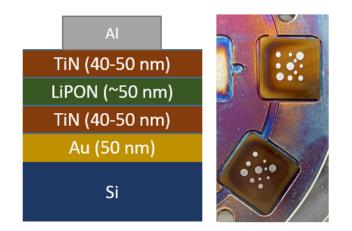

| Figure 34: As deposited planar TiN-LiPON-TiN stack cartoon along with original        |

| sample                                                                                |

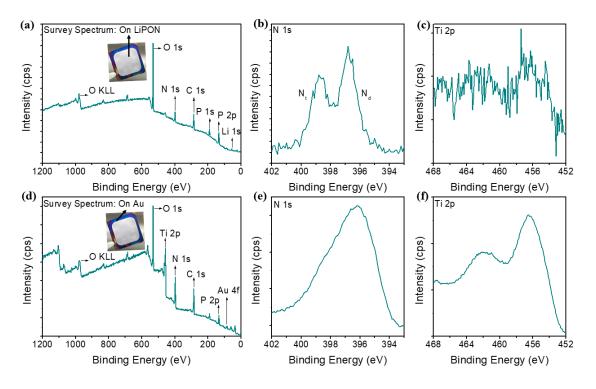

| Figure 35: XPS Survey and high resolution scan, "On LiPON": (a) Survey Scan (b)       |

| N 1s (c) Ti 2p, "On Au": (d) Survey Scan (e) N 1s (f) Ti 2p                           |

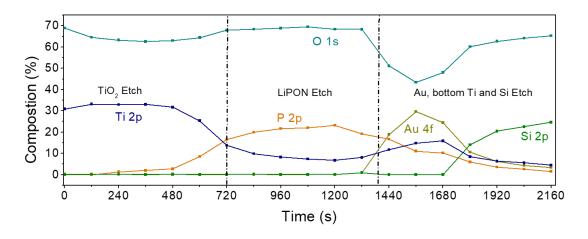

| Figure 36: TOF-SIMS etching of top TiO2 layer                                         |

| Figure 37: Depth profile to calculate etch rates for TiO2 and LiPON                   |

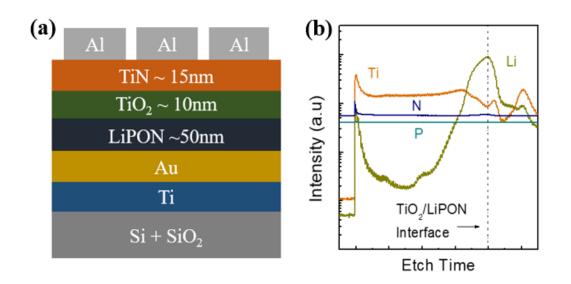

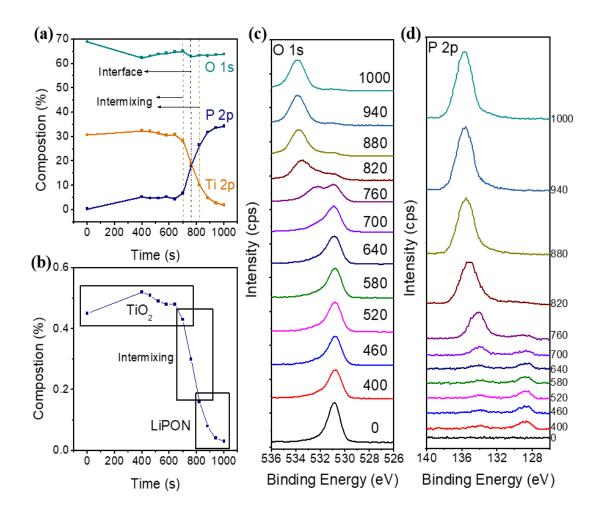

| Figure 38: XPS depth profile (a) Composition percentage of Ti, O and P (b)            |

| Compoition percentage of TiO2 (c) O 1s high resolution scan (d) P 2p high             |

| resolution scan                                                                       |

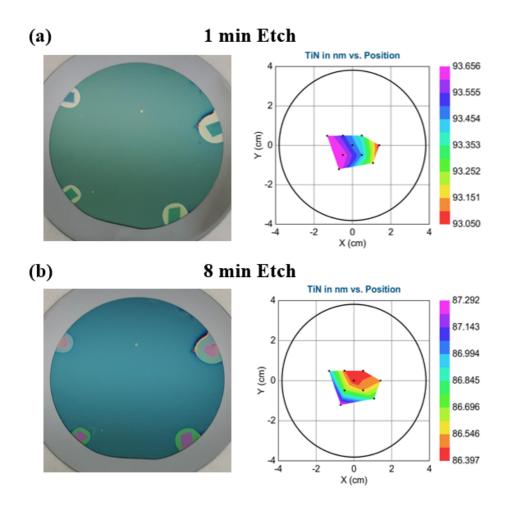

| Figure 39: Etch at FABLAB of TiN sample with a picture of original wafer along        |

| with wafer mapping (a) 1 minute etch (b) 8 minutes etch                               |

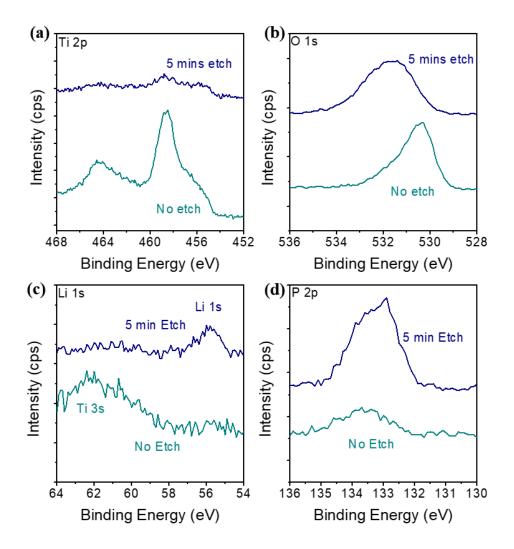

| Figure 40: High resolution XPS characterization before etch and after 5 minutes of    |

| etch (a) Ti 2p (b) O 1s (c) Li 1s (d) P 2p                                            |

| Figure 41: CVs at scan rates form 1 V/s to 10V/s (a) Al as WE (b) Au as WE 90 $$      |

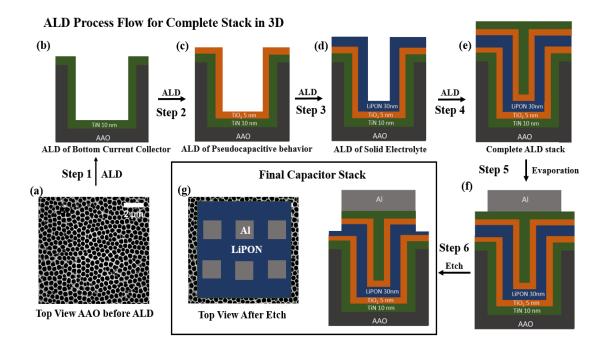

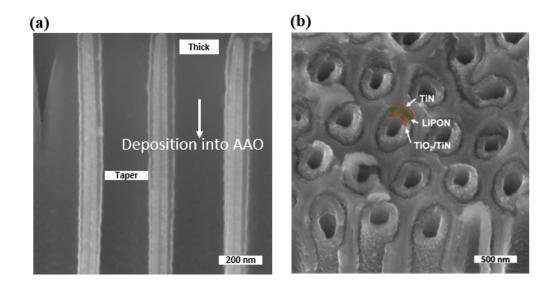

| Figure 42: ALD process flow of complete capacitor stack in 3D (a) SEM image of        |

| AAO before deposition (b) Schematic after bottom TiN electrode deposition (c)         |

| Schematic after bottom TiO2 pseudocapacitive electrode deposition (d) Schematic       |

|---------------------------------------------------------------------------------------|

| after solid state electrod                                                            |

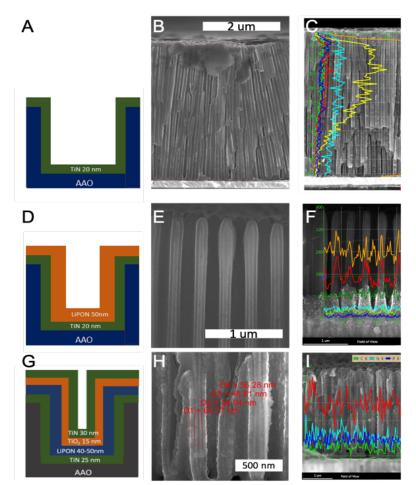

| Figure 43: A schematic of the fabrication process along with associated SEM cross-    |

| sections and EDS. Conformality of the TiN later is shown in (A-C). LiPON              |

| conformality is shown and confirmed in (D-E). Finally, the final two layers, TiO2 and |

| TiN are deposited and t                                                               |

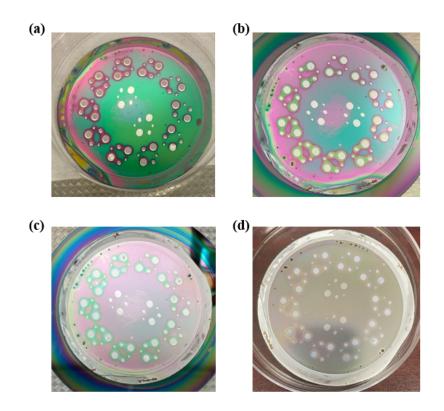

| Figure 44: Full stack images after etching (a) 0 minutes (b) 8 minutes (c) 16 minutes |

| (d) 24 minutes                                                                        |

| Figure 45: : 3D depositions in AAO pores (a) SEM images showing incomplete            |

| deposition inside the pores (b) SEM images showing need for optimized recipes 96      |

| Figure 46: Ragone plot showing a comparison of 2D vs 3D LiPON capacitors 98           |

|                                                                                       |

## **Chapter 1: Introduction**

#### **1.1 Motivation**

The move towards miniaturization of electronics and efficient storage of energy is one of the major target for the academic as well as the industrial community of the 21<sup>st</sup> century. With an increase in usage for emerging technologies such as electric vehicles, biomedical devices, autonomous sensors, and portable electronic devices, the need for efficient electronic circuit have also increased.<sup>1,2</sup> This growing demand for miniaturization of electronic circuit not only apply to integrated chips but also needs passive technologies which can cater the needs of the superfast transient current response and high energy storage with minimum losses.<sup>3,4</sup> Capacitors are once such passives which are used in every electronic circuit and has a variety of applications such as power conditioning, noise filtering, signal coupling and decoupling, and energy storage.<sup>5,6</sup> Supercapacitors in particular are a class of capacitors which have high energy density and are used for energy storage and power condition application. However, a major concern with supercapacitor technology is safety due to the flammability and reactivity of their organic solvents.<sup>7,8</sup> Also, most of these capacitors with liquid electrolyte either work on DC or limited to low frequency response (<1000 Hz). This limits their application into the wearable and implantable electronics where safety and fast response is of prime concern. All solid state ionic capacitors are viable solution for energy storage based on their safety advantage over liquid electrolytes. Another advantage of solid state ionic capacitor is their high temperature and voltage stability along with high power density.<sup>9,10</sup> Beyond their physical and chemical properties, the easy of manufacturing and packaging with growing demand of miniaturization makes them a perfect candidate for next generation supercapacitor devices.

## 1.2 What are Capacitors?

Figure 1: Supercapacitors based on charge storage, EDLC and Pseudocapacitance11

Capacitors are devices that consist of two or more parallel plates separated by an electronically insulating material called the dielectric/electrolyte. Generally, they store energy through in two ways. First, and most common, is through charge separation between two metal plates in an electric field. Second is through electrochemical surface reactions or intercalaction.<sup>11–13</sup> Supercapacitors are devices that have a higher capacitance than the conventional capacitors and are used for applications that require higher energy. Supercapacitors can be divided into two categories based on charge storage mechanisms; electric double-layer capacitors (EDLC) and pseudocapcitors (Figure 1). The EDLC stores charge at an electrodeelectrolyte interface through the adsorption of ions. An electrical double layer is formed at the interface when a voltage bias is applied across an EDLC. The double-layer consists of a stern and diffuse layer. The thickness of these layers depends on the ionic concentration and is on the order of 5-10Å. Charge separation in the stern and diffuse layer leads to a high electric field due to its low thickness and thus energy stored in an EDLC is higher than conventional capacitors. Pseudocapacitors involve fast faradaic reactions and intercalation of ions into an electrode material. This faradaic reaction stores charge in the form of chemical energy, and hence they have a higher capacitance and higher energy densities.

#### **1.2.1 Thin Film Solid State Ionic Capacitors**

One of the major advantages of solid state electrolyte is their inherent safety and stability and thus allowing their use in applications such as implantable and wearable electronics. However, a huge challenge preventing their application for next generation energy storage devices is due to their low ionic conductivity and high interfacial impedance. Thin-film processing presents one method to alleviate this concern, where thin layers (<100 nm) do not require high ionic conductivity comparable to the liquid electrolyte (1 mS/cm) and reduce interfacial impedance.<sup>14–17</sup> Another advantage associated with thin film capacitors is their low parasitic inductance and resistance thus allowing for enhanced frequency operation of these capacitors.<sup>18</sup> In spite of thin film configuration, the energy density of the planar solid state ionic capacitor configuration remains a huge challenge and limits its use to applications with limited energy metrics.

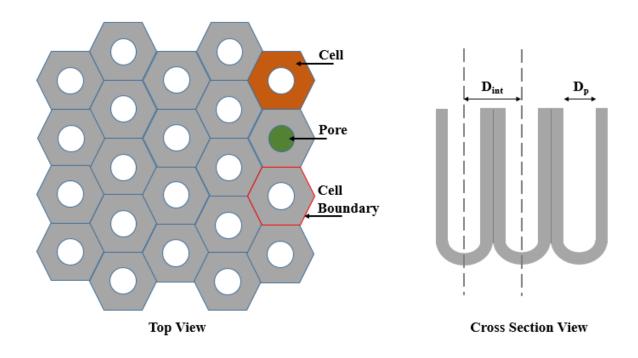

#### Figure 2: 3D structuring to enhance energy and power density metrics

To enhance the energy and power density of these thin film capacitors, one way is to the change the architecture as shown in Figure 2. The 3D structuring enhances the effective area although the footprint area remains constant. The areal enhancement can be quantitatively defined by the area enhancement factor (AEF =  $A/A_f$ ), which represents the ratio of the internal surface area, A, to the footprint area,  $A_f$ , of the substrate. However, the standard manufacturing techniques such as sputtering might face conformality problems in 3D architecture.<sup>19</sup> Thus, to enhance the performance of these capacitors it not only requires thin films but advanced manufacturing techniques to enable deposition of these thin films.

#### **1.3 Literature Survey: Solid State Electrolyte**

#### **1.3.1 Polymer Electrolyte**

Solid-state electrolytes can mainly be classified into polymer electrolytes and inorganic electrolytes. Polymer-based electrolytes are further classified into three basic types, (1) gel-based, (2) solid-state, and (3) polyelectrolyte. A diagram of each can be found in Figure 3 (a-c). Solid-state polymer electrolytes, Figure 3 (a), consist of a polymer and salt mixture, with their ionic conductivity based on the transport of ions inside the polymer matrices while the polyelectrolytes (Figure 3 (c)) have charged polymer chains which are responsible for their ionic conductivity. In contrast, gel polymer electrolytes (Figure 3 (b)) contains a solvent with conducting salt inside the polymer host. Ion transport takes place inside the solvent and hence they have higher ionic conductivity than solid polymer electrolytes. Since gel electrolytes have superior ionic conductivity and high flexibility, they are the most common supercapacitor electrolytes.<sup>20-24</sup>

Figure 3:P Schematic diagrams of (a) a dry solid polymer electrolyte (b) gel polymer electrolyte, and (c) a polyelectrolyte<sup>22</sup>

Table 1 shows gel electrolyte supercapacitors with high energy and power density, but a significant drawback of these electrolytes is poor mechanical strength, leading to short circuits and safety issues. Gel polymer electrolytes cannot be operated in a wide temperature range as solvents dry up at extreme temperatures. Also, miniaturization remains a major issue in gel polymer electrolytes as it is hard to make devices down to nanoscale thickness with high conformality and rigidity. Thus, with safety being a primary concern, polymer gel electrolytes are not suitable for supercapacitor applications which demand high-temperature stability (>70°C) along with high mechanical strength at low thicknesses (<100nm). <sup>25,26</sup>

| Electrolyte                                                        | Capacitance            | Energy Density            | Power Density           |

|--------------------------------------------------------------------|------------------------|---------------------------|-------------------------|

| PVA/KOH/K <sub>3</sub> [Fe(CN)                                     | 430.95 F/g             | 57.84 Wh/kg               | 59.84 kW/kg             |

| 6]27                                                               |                        |                           |                         |

| PVA/H <sub>2</sub> SO <sub>4</sub> /P-                             | 474.29 F/g             | 10 Wh/kg                  | 1000 W/kg               |

| benzenedio] <sup>28</sup>                                          |                        |                           |                         |

| PVA/H <sub>3</sub> PO <sub>4</sub> /H <sub>2</sub> O <sup>29</sup> | 108 F/cm <sup>3</sup>  | 7.5 Wh/cm <sup>3</sup>    | 2.9 W/cm <sup>3</sup>   |

| CMC/Na <sub>2</sub> SO <sub>4</sub> <sup>30</sup>                  | 92 F/g                 | 41 Wh/kg                  | 1276 W/kg               |

| PVA/ LiClO <sub>4</sub> <sup>31</sup>                              | 145 F/g                | 41 Wh/kg                  | 2.1 kW/kg               |

| PVA/LiCl <sup>32</sup>                                             | 0.52 F/cm <sup>3</sup> | 0.234 mWh/cm <sup>3</sup> | 0.133 W/cm <sup>3</sup> |

| PVA/KOH <sup>33</sup>                                              | 4.28 F/cm <sup>3</sup> | 1.21 mWh/cm <sup>3</sup>  | 13.29 W/cm <sup>3</sup> |

| PMMA/LiClO <sub>4</sub> <sup>34</sup>                              | 270 F/g                | 9.8 Wh/kg                 | 0.85 kW/kg              |

| PVP/ Na <sub>2</sub> SO <sub>4</sub> <sup>35</sup>                 | N/A                    | 24.8 Wh/kg                | 120 W/kg                |

| PAAK/KCl <sup>36</sup>                                             | 72.6 F/g               | 32.7 Wh/kg                | N/A                     |

Table 1: Gel polymer electrolyte used in supercapacitors

## **1.3.2 Inorganic Solid State Electrolyte**

Inorganic electrolytes consist of ceramic and oxide materials. A significant advantage of inorganic electrolytes is their high thermal stability, high mechanical strength, and a higher electrochemical stability window. Their ionic conductivities very widely but are generally considered to be lower than liquid and polymer counterparts. Their high rigidity compared to solid state polymer electrolytes, makes them an excellent material for thin film supercapacitor applications. Unlike polymer gel electrolytes, they don't suffer from problems related to solvent drying and hence reduce packaging cost.<sup>21,25</sup> Table 2 shows some state-of-the-art inorganic electrolytes with their respective ionic conductivities. These inorganic electrolytes have shown excellent characteristics in battery performance, but their application in capacitors has yet to be studied intensively.

| Solid Electrolyte                                                          | Ionic Conductivity (S/cm) |

|----------------------------------------------------------------------------|---------------------------|

| Perovskite <sup>37–39</sup>                                                | 10-4-10-3                 |

| NASICON <sup>40–42</sup>                                                   | 10-4-10-3                 |

| Garnet <sup>43_46</sup>                                                    | 10-6-10-3                 |

| Amorphous Li <sub>2</sub> S-P <sub>2</sub> S <sub>5</sub> <sup>47,48</sup> | 10-4-10-2                 |

| Thio-LiSiCON <sup>49–51</sup>                                              | 10-2                      |

| LiPON <sup>52–56</sup>                                                     | 10-8-10-5                 |

| Hydride <sup>57,58</sup>                                                   | 10-7-10-2                 |

Table 2: Inorganic SSE and their ionic conductivity

| Halide <sup>59</sup> | 10-8-10-3 |

|----------------------|-----------|

|                      |           |

Table 3 shows a brief survey of inorganic SSE for capacitor applications. NASICON-type SE ( $Li_{1.4}Al_{0.4}Ti_{1.6}(PO_4)_3$ )) (LATP), which have a high ionic conductivity (10<sup>-4</sup> S/cm) was sandwiched between two nanostructured electrodes which incorporate single-wall carbon nanotubes mixed with LATP.<sup>60</sup> LATP shows EDLC behavior, and the highest capacitance measured was 11 mF/cm<sup>3</sup> at 0.01Hz. However, a major drawback is that the capacitance reduces drastically with an increase in frequency. At less than 100Hz, the material loses its electric double layer behavior and acts as an electrostatic capacitor with high impedance.

| Electrolyte         | Electrode         | Capacitan              | Voltag | Comments            |

|---------------------|-------------------|------------------------|--------|---------------------|

|                     |                   | ce                     | е      |                     |

| NASICON:LAT         | Au with Carbon    | 0.13 F/cm <sup>2</sup> | 0.8 V  | Porous/dense/por    |

| $P^{61}$            | coating           |                        |        | ous using carbon    |

|                     |                   |                        |        | to enhance          |

|                     |                   |                        |        | capacitance         |

| NASICON:LAT         | LATP with CNTs    | $11 \text{ mF/cm}^3$   | 0.5 V  | Porous dense        |

| P <sup>60</sup>     |                   |                        |        | porous to enhance   |

|                     |                   |                        |        | surface area at the |

|                     |                   |                        |        | interface           |

| $Li_2S-P_2S_5^{62}$ | Carbon paper with | 8.7 mF/cm <sup>2</sup> | 0.5 V  | Electrolyte         |

|                     | MWCNTs            |                        |        | formed using heat   |

|                     |                   |                        |        | treatment           |

| 0.4LiClO <sub>4</sub> -                         | LiMn <sub>1.5</sub> Ni <sub>0.45</sub> Mg <sub>0.05</sub> | 29 F/g                | 2 V | High temperature |

|-------------------------------------------------|-----------------------------------------------------------|-----------------------|-----|------------------|

| 0.6Al <sub>2</sub> O <sub>3</sub> <sup>25</sup> | $O_4$ ,                                                   |                       |     | stability :150 C |

|                                                 | Mn <sub>2</sub> O <sub>3</sub> ,MnO                       |                       |     |                  |

| Graphene                                        | Reduced graphene                                          | 3 mF/cm <sup>2</sup>  | 1 V | Water trapped    |

| Oxide <sup>63</sup>                             | oxide                                                     |                       |     | inside the       |

|                                                 |                                                           |                       |     | graphene oxide   |

|                                                 |                                                           |                       |     | serves as ion    |

|                                                 |                                                           |                       |     | conductor        |

| LiPON <sup>64</sup>                             | Platinum                                                  | 50 uF/cm <sup>2</sup> | 3 V | High cycling     |

|                                                 |                                                           |                       |     | stability, high  |

|                                                 |                                                           |                       |     | voltage window   |

| LiPON <sup>65</sup>                             | Cobalt/Cobalt oxide                                       | 15 F/cm <sup>3</sup>  | 2 V | High temperature |

|                                                 |                                                           |                       |     | stability 90C    |

In another work, LATP shows a capacitance of 50 uF/cm<sup>2</sup> with gold as the current collector, but the capacitance shows a limited voltage stability window of 0.8V, limiting the capacity and hence energy density.<sup>61</sup> Li<sub>2</sub>S-P<sub>2</sub>S<sub>5</sub>, a ceramic, has been investigated as an electrolyte.<sup>62</sup> The electrolyte is prepared by heat treatment of Li<sub>2</sub>S and P<sub>2</sub>S<sub>5</sub>, and the resulting mixture has an ionic conductivity of 1 mS/cm. The electrolyte shows an EDLC behavior with a high capacitance of 8.7 mF/cm<sup>2</sup>. Also, the capacitor showed a small electrochemical voltage stability window of 0.5V.

Finally, initial studies have investigated lithium phosphorous oxynitride (LiPON) as SSE for supercapacitors. In one study, 140 nm of LiPON was sputtered using Li<sub>3</sub>PO<sub>4</sub>-Li<sub>2</sub>O as the target on platinum electrodes. A high capacitance of 50 uF/cm<sup>2</sup> was achieved and showed an excellent voltage stability window of up to 3V

between platinum electrodes.<sup>64</sup> In another study, 20 nm of LiPON was sputtered using a Li<sub>3</sub>PO<sub>4</sub> target in a nitrogen atmosphere. The resulting LiPON was sandwiched between Cobalt/Cobalt oxide electrodes and showed a high capacitance and high energy density. The paper also reports the flexibility of LiPON and exhibits stability at high temperature (90°C).<sup>65</sup> Though sputtered LiPON shows high voltage stability, hightemperature stability, and mechanical stability, a major problem is low energy and power density compared to liquid electrolytes. Also, sputtering possesses conformality problems limiting the growth of SSE into 3D architectures.

Figure 4: Reaction Scheme of ALD Aluminum Oxide process

In contrast, atomic layer deposition (ALD) is a technique that allows deposition of thin film materials from vapor phase. It consists of sequential alternating pulses of gaseous chemical precursors that reacts with the substrate. Each individual gas-surface reactions make up only part of the materials synthesis. During each reaction, the precursor is allowed to fully react with the substrate surface through a self-limiting process that leaves no more than one monolayer at the surface. Thus, ALD offers precise control of thickness and composition of the material. Along with confirmability and uniformity on 3D surfaces, the remarkable selectivity and superior scalability make it an excellent choice for synthesizing SSE for supercapacitor applications.<sup>66</sup> One of the most common ALD process is the thermal growth of aluminum oxide using trimethyl aluminum (TMA) and water and the process is shown in Figure 4. The reaction on a substrate with OH termination is described below.<sup>67</sup>

$-OH^* + Al(CH_3)_{3(g)} - O-Al(CH_3)_2^* + CH_{4(g)}$  $-O-Al(CH_3)_3^* + H_2O_{(g)} - O-Al-OH^* + CH_{4(g)}$

## **1.4 Atomic Layer Deposition of LiPON**

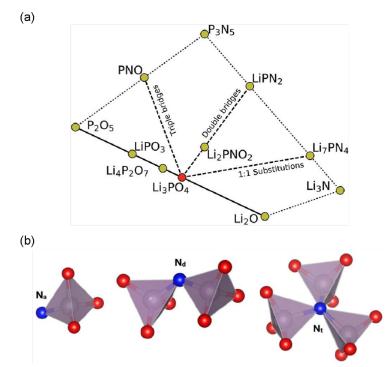

Figure 5: (a) Phase diagram showing LiPON compositions in the LixPOyNz space. (b) Possible N binding environments in LiPON structures. Na is apical N, Nd is doubly coordinated N, Nt is triply coordinated N. Color code: N (blue), O (red), P (gray). From Lacivita68

LiPON is an inorganic glassy material commonly used as a thin film solid electrolyte in solid-state batteries (SSBs) with a general formula of  $Li_xPO_yN_x$ . It was first developed at Oak Ridge National Laboratory via sputtering.<sup>52</sup> The LiPON structure is based on  $Li_3PO_4$  metaphosphate chain with nitrogen doping which is either doubly (N<sub>d</sub>, P-N=P) or triply (N<sub>t</sub>, P-N<P) coordinated. Recent molecular dynamic simulation study from Lacivita et al.<sup>68</sup> suggests nitrogen as singly coordinated or apical nitrogen (N<sub>a</sub>, P-N) in the LiPON structure. Due to different nitrogen bridging, many polymorphs of Nitrogen exists as shown in Figure 5 (a). The different nitrogen configurations with phosphate units are shown in Figure 5 (b). The high incorporation of nitrogen into the LiPON film is associated with high ionic conductivity due to decreased electrostatic interactions of the P-O bond and replacement with a covalent P-N bonds.<sup>69,70</sup> ALD LiPON was first developed at UMD by the Rubloff group. Since, three ALD LiPON recipes have been developed with different precursors combinations and different growth windows.<sup>53–55</sup> Table 4 shows the deposition of ALD LiPON with different precursors and their respective growth per cycle along with the reported ionic conductivity. In this work, we have studied plasma ALD LiPON and thermal ALD LiPON previously developed by our group.

| Chemical                                                | ALD             | Precursor                 | Growth per     | Ionic                                              |

|---------------------------------------------------------|-----------------|---------------------------|----------------|----------------------------------------------------|

| Formula                                                 | temperature     |                           | cycle (GPC)    | Conductivit                                        |

|                                                         | $(0\mathbf{C})$ |                           | $(\mathbf{A})$ | $\mathbf{v}_{\mathbf{r}}(\mathbf{S}_{\mathbf{r}})$ |

|                                                         | (°C)            |                           | (A)            | y (S/cm)                                           |

|                                                         |                 |                           |                |                                                    |

| Li <sub>0.99</sub> PO <sub>2.55</sub> N <sub>0.30</sub> | 250             | LiO <sup>t</sup> Bu, H2O, | 0.7-1.05       | 3×10-7                                             |

| 0000 2020 0020                                          |                 | , , ,                     |                |                                                    |

| 53                                                      |                 | TMP                       |                |                                                    |

| 55                                                      |                 |                           |                |                                                    |

|                                                         |                 |                           |                |                                                    |

| $Li_2PO_2N^{54}$                                        | 300             | LiO <sup>t</sup> Bu, DEPA | 0.6-0.9        | 6.51×10-7                                          |

|                                                         |                 | ,                         |                |                                                    |

| LiPON <sup>55</sup>                                     | 300             | LiHMD,                    | 0.7            | ND                                                 |

|                                                         | 500             |                           | 0.7            | ND                                                 |

|                                                         |                 |                           |                |                                                    |

|                                                         |                 | DEPA                      |                |                                                    |

|                                                         |                 |                           |                |                                                    |

|                                                         |                 |                           |                |                                                    |

Table 4: ALD parameters for different polymorphs of LiPON

#### **1.5 Dissertation Overview**

In this dissertation, we explore ALD LiPON based solid-state capacitors that can provide high energy density and power density for next-generation applications. Different ALD LiPON polymorphs are investigated with reasonable high ionic conductivity and high-temperature stability for better-performing supercapacitors. Further, the solid electrolyte capacitors are characterized based on their electrochemical working potential, frequency, and leakage currents to define their application range. Also, the electrochemical stability of solid electrolytes is tested with different electrode materials to expand the energy density of the capacitors using pseudocapacitive behavior. Finally, we investigate and develop ALD recipes, fine tune process parameters and develop etching techniques to fabricate all solid state 3D capacitor.

## **Chapter 2: Experimental Techniques**

#### 2.1 Advanced Nanostructures Laboratory (ANSLab)

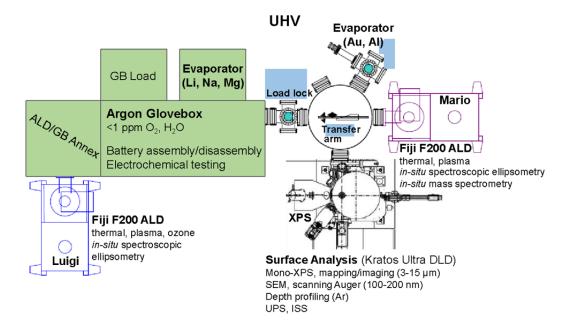

ANSLab is one of a kind highly equipped laboratory with state of the art tools for manufacturing, characterizing and testing materials and devices which are air sensitive with a focus of applications related to solid state batteries/supercapacitor and other microelectronic devices. It consists of advanced thin film deposition tools, surface analysis instruments which are coupled using Ar-filled glove box and ultrahigh vacuum chamber. A schematic describing the state of the art tools with their respective position and integration with other equipment is shown in Figure 6. It consists of two ALD reactors, Veeco Fiji F200 which are named as Luigi and Mario respectively. All the thin film depositions done in this thesis mainly for solid electrolyte and capacitor fabrication is done using Luigi. An ultra-high vacuum chamber connects Luigi to the glove box. The glove box is also coupled to the RTTA chamber on the other side which has 8-inch pneumatic gate valves that connects to the evaporation chamber, the Krataos Ultra DLD surface analysis system and the other ALD reactor "Mario". An advantage of this coupled system is that it allows for testing, fabrication along with surface analysis without air exposure. The RTTA system consist of a robotic arm which can transfer 3-inch wafers for fabrication and testing into different tools attached to it. The glove box is mainly used for transferring samples and precursors from atmosphere into the inert atmosphere and storing them. Another key advantage of glove box is that it has the biologic potentiostat for testing and characterizing materials and microelectronics. Along with this, the glove box has a custom-built evaporator attached for Li, Na and Mg metal evaporation. These coupled systems along with all the fabrication and characterization tool makes ANSLab a highly advanced research facility at UMD.

Figure 6: Schematic of ANSLab equipment used to fabricate, characterize, and evaluate materials in this dissertation

## **2.2 Atomic Layer Deposition**

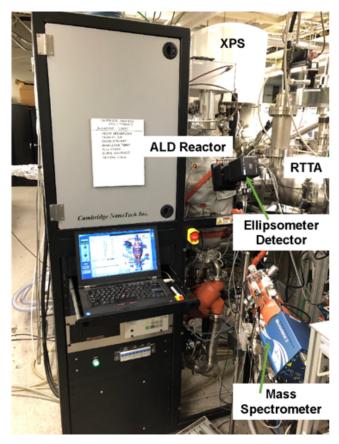

In this dissertation, the primary deposition technique used is ALD which allows for growing thin film coatings with high conformality and ultra-high purity. The ALD process parameters varies with different materials and substrates and is defined in each chapter where the reactor is used for depositions. In this research ALD is used to deposit different polymorphs of LiPON, TiN and TiO<sub>2</sub>. The Luigi ALD reactor is used for all the depositions and is shown in Figure 7. An advantage of Luigi is that it has an inoperando spectroscopic ellipsometry that allows for thickness control at angstrom scale. This along with coupled glove box and RTTA tool allows for complete analysis of thin film devices.

Figure 7: Fiji-F200 ALD Reactor (Mario) in ANSLab. Mario is equipped with in-line mass spectrometry sampling and in-operando spectroscopic ellipsometry. ALD films can be transferred directly to a surface analysis system for XPS through the RTTA UHV transfer chamber

## 2.3 X-ray Photoelectron Spectroscopy (XPS)

XPS is one of the most used characterization technique used in this thesis to understand and confirm the chemical structure of the solid state electrolyte and electrodes. One of the key elements of XPS is surface sensitivity which makes it the perfect choice for analyzing the chemical composition of thin films deposited using ALD. Another advantage of our XPS tool is its construction into the ANSLab which allows for characterizing pure ALD films without air exposure. The XPS works on the photoelectric principal which was first proposed by Einstein in 1922.<sup>71</sup> In this technique, X-rays are irradiated on the sample and the analyzed detects the kineteic energy of electrons which are emitted from the top surface. The binding energy of the emitted electron is calculated using conservation of energy equation as shown in equation below.

$$E_{binding} = h\nu - E_{kinetic} + \phi$$

where,  $E_{tonding}$  is the binding energy of the excited electron, hv is the photon energy,  $E_{tonding}$  is the kinetic energy of the excited electron, and  $\varphi$  is the work function of the material. The work function term defines the instrument correction factor and that is different for different working conditions and instruments. The calculated binding energy is then used to analyze the material and their respective oxidation state. This allows for calculating the overall stoichiometry of the thin films along with their bonding structure.

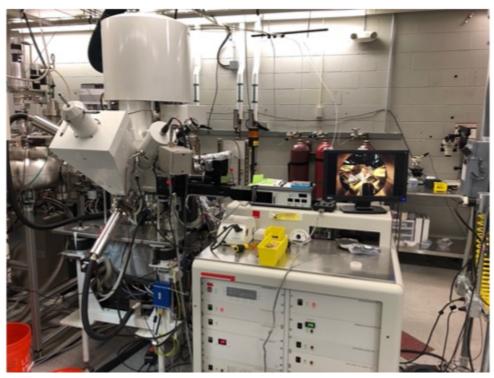

Figure 8 shows the Kratos surface analysis tool that is installed in our lab. Every film was characterized using XPS to analyze their chemical structure to conclude deposition on different substrate material and analyze results. For characterization of ALD films, the films were transferred into the Kratos tool without air exposure. Preventing air exposure is a critical parameter to understand thin films and their interfaces as it allows for accurate material characterization which are air sensitive.

Figure 8: Kratos Ultra DLD surface analysis system in ANSLab used for XPS measurements

## 2.4 Spectroscopic Ellipsometry

The capacitor fabrication along with process development of each thin film relies on in-operando ellipsometry which is attached to the Luigi tool in ANSlab. Ellipsometry not only allows for thickness measurements but also quantifies process development. The precursor doses and purge time is determined using ellipsometry. It also allows for angstrom level thickness control and thus allows us to deposit thin films with high accuracy and conformality to our specifications.

The ellipsometry analyzed measures the change in polarization of light as it interacts with the surface of the sample. This is correlated to the film thickness using various optical models.<sup>72</sup> The polarization of light is described by the equation below.

$$\overset{\sim}{p} = \frac{\overset{\sim}{r_p}}{\overset{\sim}{r_s}} = \frac{\begin{vmatrix} \overset{\sim}{r_p} \end{vmatrix}}{\begin{vmatrix} \overset{\circ}{r_s} \end{vmatrix}} e^{i(\delta_p - \delta_s)} = \tan \tan \Psi e^{i\Delta}$$

where  $r_p$  and  $r_s$  are the Frensel reflection coefficients for the p- and s- polarized light, respectively. The amplitude ratio ( $\Psi$ ) and phase difference ( $\Delta$ ) are measured dynamically across the spectral range (200-2000 nm) throughout the deposition process and are correlated to film thickness through optical models. A J.A. Woollam M-2000D spectroscopic ellipsometer was used for *in-operando* and *ex-situ* measurements of samples in this work.

#### **2.5 Dry Reactive Ion Etch (DRIE)**

DRIE technique is used to fabricate planar 2D capacitors or 3D capacitors by etching the top current collector. We used an Oxford Plasmalab System 100 too; which is an inductively Coupled plasma (ICP) reactive ion etcher. Though this tool uses a variety of gas for selective etching. In this work we used Ar ion milling and developed our own recipe. We used the plasma along with various flow of Ar ions at different ICP power. The recipe was developed using spectroscopic and XPS analysis. Timed etches were performed to further quantify the etch rates. Chapter 5 discusses the recipe development process in detail.

#### **2.6 Electrochemical Analysis**

This research work is highly dependent on electrochemical analysis for evaluating the performance of materials and solid-state capacitors. A biologic VSP was used in this work to test the capacitors in 2D and 2D configuration. A picture of the biologic VSP along used for electrochemical analysis is shown in figure 2.4(a). Electrochemical tests include electrochemical impedance spectroscopy (EIS), cyclic voltammetry (CV), and galvanostatic capacitor cycling measurements. Figure 9 (b) shows an image of a LiPON capacitor undergoing electrochemical testing on a custom probe station inside the Ar glovebox. It is critical to evaluate such SSEs in the glovebox to avoid air-exposure for precise determination of electrochemical properties.

(b)

(a)

Figure 9: (a) Biologic VSP potentiostat (b) LiPON SSE undergoing electrochemical testing<sup>72</sup>

The first characterization and one of the most important to evaluate thin films is electrochemical impedance spectroscopy (EIS). This technique measures current repose to a sinusoidal low potential AC voltage and calculates the impedance characteristics of the film. The impedance equation is shown below.

$$Z(\omega) = \frac{E}{I} = Z_o \exp \exp (i\varphi) = Z_o (\cos\varphi + i\sin\varphi)$$

where Z is the impedance,  $\omega$  is the frequency, E is the voltage, I is the current, Z<sub>o</sub> is the magnitude, and  $\varphi$  is the phase shift.<sup>73</sup> This data is represented in a Nyquist diagram,

which plots the imaginary part of the impedance vs. the real part of the impedance. An equivalent circuit model is used to fit the Nyquist plot to determine the total resistance, from which ionic conductivity and resistance are determined.

Another important technique to understand capacitors electrochemical behavior is cyclic voltammetry (CV). In this technique, the potential between the electrode systems is changed and the current response is measured. The potential vs current response gives a detailed analysis of oxidation and reduction peaks. This helps in defining the capacitor characteristics along with their respective oxidation and reduction state in a particular capacitor setup. The results are used in this work to report the behavior of our on chip characterization and calculating the capacity of these electrochemical capacitors.

## **Chapter 3: On-Chip ALD LiPON Solid State Capacitors for High Frequency Application**

#### **3.1 Overview**

Multi-layer ceramic capacitors have been used for high frequency decoupling application due to a lower overall impedance leading to fast current response. However, high parasitic inductance limits the application of these capacitors in ultra-high frequency domain. Thus, MLCCs are placed close to the IC to improve circuit efficiency and reduce inductance. With next generation applications, the demand for frequency range has further increased which not only requires enhanced capacitor material but improved manufacturing techniques to limit the inductive path. Here, we demonstrate ALD of two different polymorphs of ultra-thin film lithium phosphorus oxynitride (LiPON) as an inorganic solid-state electrolyte (SSE) for on chip capacitors for decoupling application. Both the LiPON capacitors shows an electric double layer behavior with a capacitance of 15 uF/cm<sup>2</sup> and a low leakage current (<20 nA/cm<sup>2</sup>) at 2V. The LiPON shows EDLC behavior up to 10 kHz and beyond this frequency, both the polymorphs show an electrostatic behavior with a high dielectric constant (14). This dual frequency behavior along with low parasitic inductance and on chip integration allows for extended frequency range. Further, integration of these capacitor into 3D nanostructures would enhance the energy density and frequency range beyond state-ofthe-art MLCCs.

#### **3.2 Introduction**

Capacitors are an indispensable part of electronic circuits, where they are used for a variety of applications, such as, power conditioning, memory, sensors, energy storage, and, more particularly, power spike management.<sup>74–77</sup> The increase in demand for portable and wearable electronics has led to an increased use for capacitor devices for power conditioning applications. In order to improve their power-efficiency, ICs embedded into wearable and portable electronics integrate advanced power management (i.e. voltage to frequency scaling) features requiring very stable (few mV of voltage swing) and fast settling of the DC voltage supply. Ensuring this voltage stability, implies smart design of the power distribution network (PDN). A very common approach is to place a decoupling capacitor at no electrical length from the load, shorting the inductive path that limits the current flowing from the slow and distant battery.<sup>78,79</sup> During fast current transient on the PDN, resulting from load activity (ex. a wakeup event) the capacitor would be acting as the temporary current supply for few ps~ns, preventing the PDN voltage from swinging. In the AC domain, this would imply a capacitor capable of maintaining a very low PDN impedance (10's of mOhm) over a wide frequency range (DC – 100's of MHz).

The traditional aluminum electrolytic and multi-layer ceramic capacitors (MLCC) have been used for these applications, but a significant problem is their high intrinsic parasitic inductance (i.e. in-operative at fast current transients), bulky volume, rigid shapes, and low energy density.<sup>80–82</sup> Thus, they are incompatible with higher frequency application demands that require miniaturization. In contrast, electric double layer capacitors (EDLCs) match the criterion for both compact size and high energy density. EDLCs consist of two electrodes separated by an electrolyte containing mobile ions and stores energy by adsorption of ions on the surface of electrodes.<sup>12,83</sup> However, due to high impedance and low ionic mobility, EDLCs are limited to low frequency or DC operation.<sup>84</sup> Hence, there is a significant push towards high performing EDLCs which can compete or surpass the current capacitors available in the market for high frequency applications.

A considerable effort has been made to enhance the performance of these EDLCs for high-frequency applications by changing the electrode/electrolyte materials and structures. Most of these studies have report liquid or polymer electrolytes to enhance the frequency operation of these capacitors.<sup>84–89</sup> However, liquid and polymer

electrolytes have low voltage and temperature stability, significantly limiting their application space. Furthermore, liquid electrolytes have leakage issues leading to safety concerns for their application in wearable and implantable electronics. Recent studies have reported the use of all solid state electrolytes for SCs and batteries to reduce the safety issues and increase the application domain.<sup>65,90–92</sup> Solid-state SCs eliminate hazardous electrolyte leakage problems, expand temperature range, voltage windows, and provide structural stability.<sup>55,66,93–95</sup> However, the current solid state solid state EDLCs have a large electrolyte thickness along with moderate ionic conductivity, also limiting their use in high frequency applications.

Lithium phosphorus oxynitride (LiPON) has been extensively studied as a solid-state battery electrolyte. It has a high voltage stability up to 5V vs Li/Li<sup>+</sup> and a high temperature stability up to 300°C.<sup>96-98</sup> These same properties have recently garnered interest from the SC community. Sputtered LiPON has been characterized as a EDLC electrolyte by Sallez *et al.* They reported 140 nm of sputtered LiPON between platinum electrodes and showed a high energy density of 0.04 uWh/cm<sup>2</sup> and a limited cutoff frequency of 1000 Hz.<sup>99</sup> However, to meet the current state of the art application demands the capacitors require an increase in the cutoff frequency. This can be achieved by (1) increasing the ionic conductivity of the SSE, (2) decreasing the thickness of the electrolyte, and/or (3) integration into ultra-high-aspect ratio structures.<sup>85,100</sup> Our group showed this previously integrating ultra-thin Al<sub>2</sub>O<sub>3</sub> into porous anodic aluminum templates to drastically expand the areal storage capacity of electrostatic capacitors.<sup>101</sup> More recently, this same structure-based approach was used to report the first 3D solid-state battery.<sup>102</sup>

ALD allows deposition of thin-film materials into high-aspect ratio nano/microstructures with high conformality. It consists of cyclic and sequential alternating pulses of gaseous precursors. Ideally, during each half-reaction, the precursor reacts in a self-limiting process that leaves no more than one monolayer. Typically, however, reactions are less than ideal and have growth rates below a monolayer. Despite this, ALD offers precise control of the thickness and composition of the material through choice of number of deposition cycles and precursors. The first ALD LiPON was a plasma enhanced process (PEALD) involving sequential pulsing of lithium tert-butoxide (LiOtBu), deionized water, trimethyl phosphate (TMP), and N<sub>2</sub> plasma.<sup>53</sup> Since two additional thermal ALD processes have been developed producing different polymorphs of LiPON.<sup>54</sup>

Herein, we report the fabrication and characterization of thin-film ALD LiPON supercapacitors. First, we compare PEALD and thermal ALD LiPON based on their electrochemical stability using cyclic voltammetry and electrochemical impedance spectroscopy. Here, the thermal LiPON shows extended ionic operation up to 10k Hz and cycling stability to 10k cycles. Plasma LiPON shows two states, one in the low-frequency region due to ionic transport, and a high-frequency region above 80k Hz from electrostatic polarization with a high dielectric constant of 13. Finally, we perform impedance simulations of a LiPON capacitor and compare it with MLCCs available in the market. The results demonstrate the suitability of ALD LiPON solid-state electrolytes for wider frequency applications compared to traditional MLCCs.

# **3.3 Experimental Procedure**

# **3.3.1 Device fabrication**

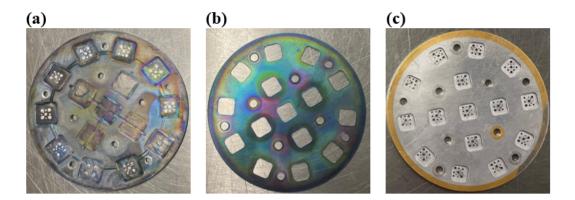

76 mm silicon wafers were oxidized by chemical vapor deposition (Tystar CVD) to create a 500 nm insulating layer of SiO<sub>2</sub>. A thin titanium layer (~5 nm) was then deposited on top of the SiO<sub>2</sub> layer by electron beam evaporation (Angstrom NexDep Ebeam evaporator) to act as an adhesion layer for the bottom gold electrode (100 nm), which was also prepared by e-beam evaporation. The wafer was then diced into 1cm ×1cm chips using a dicing saw (Make, model) and cleaned by sonication in baths of acetone, isopropyl alcohol, and H<sub>2</sub>O. The chips were then blown dry and heated at 70°C for 12 hours in a convection oven to remove excess water. The diced chips were loaded into a custom-built sample holder (Figure 10 (a)) with shadow mask on top (Figure 10 (b)) and transferred into the ALD reactor for LiPON deposition.

Figure 10: (a) Sample holder (b) Shadow mask for ALD (c) Shadow mask for top contacts

Two ALD (Veeco, Fiji) processes were used to deposit LiPON. First, a thermal process at 350°C (<sup>t</sup>LiPON) was used. Here, lithium tert-butoxide (LiO<sup>t</sup>Bu) (Sigma,

97%) and diethyl phosphoramidate (DEPA) (Sigma, 98%), were reacted sequentially. The LiO'Bu was loaded into a stainless-steel bubbler which was heated to 150°C. The DEPA was loaded in a stainless-steel cylinder and maintained at 115°C. The base pressure of the ALD reactor was  $1 \times 10^{-6}$  Torr, and the process pressure was maintained at ~200 mTorr by flow of UHP Argon (Airgas, 99.999%). The reaction was carried out with saturated doses of 20s for LiO'Bu and 2s for DEPA followed by 20s and 10s purges after each dose respectively. Details of this process were published previously.<sup>54</sup>

For a second set, a PEALD LiPON (<sup>P</sup>LiPON) process was used at 250°C with the same reactor pressure conditions listed above. LiO'Bu (Sigma, 99.7%), deionized H<sub>2</sub>O, trimethyl phosphate (TMP) (Sigma, 99.9%), and nitrogen plasma (<sup>P</sup>N<sub>2</sub>) were used as precursors. The LiO'Bu was loaded into a stainless-steel bubbler which was preheated to 150°C. The H<sub>2</sub>O and TMP were loaded into stainless-steel vapor-draw cylinders and were used at room temperature and 70°C respectively. Films were deposited using saturated doses of 20 s for the LiO<sup>t</sup> Bu, 0.06 s for the H<sub>2</sub>O, and 0.4 s for the TMP with 30 s purges after each dose. The <sup>P</sup>N<sub>2</sub> pulse was carried out for 10s at 40 sccm with a plasma power of 300 W, and a 5s purge step. Details of this process were published previously.<sup>53</sup>

After deposition, the samples were transferred under vacuum to a glove box and a custom-built shadow mask (Figure 10 (c)) was used to limit and vary the size of the top contact. The samples were then transferred in-vacuum to an evaporation chamber. Finally, a thermal evaporation process was done using a custom effusion cell to deposit the top gold electrode (200 nm).

# **3.3.2 Device Characterization**

Surface characterization was conducted using a vacuum coupled Kratos Ultra DLD X-ray photoelectron spectrometer (XPS). The spectra were collected using monochromatic Al K $\alpha$  radiation at 12kV. Survey spectra were collected using a pass energy of 160 eV in hybrid lens mode with a step size of 1 eV. High-resolution scans were collected at 20 eV using 0.1 eV as the step size. The charge neutralizer was turned on during the data collection using a flood gun with 1A filament current, 1.15 V charge balance, and 1 V filament bias. CasaXPS was used to analyze the data collected from the XPS spectra with a Shirley background. All the spectra were calibrated to C 1s at 284.8 eV.

Scanning electron microscopy (SEM) and focused ion beam (FIB) cross sections were performed using a Tescan GAIA dual SEM/FIB system. FIB cross sections required a two-step cutting and polishing process, using a 30 kV Ga ion beam energy at 500 pA and 50 pA currents for each step, respectively. No protective coating was used on the top surface; the Au top contact provided enough protection for the underlying interfaces.

Electrochemical characterization was performed using a Biologic potentiostat (model) attached to a glove box. Samples were mounted on a custom-made mica glass-ceramic stage with an attached temperature controller for testing.

# **3.4 Results**

# **3.4.1 Characterization and Metrology of ALD LiPON Processes**

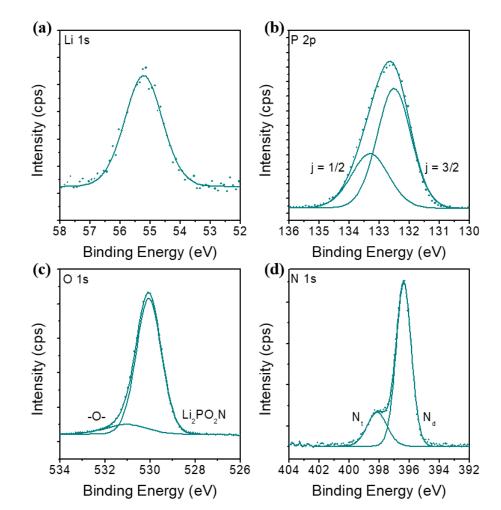

Figure 11: Thermal LiPON XPS spectra high resolution scan (a) Li 1s (b) P 2p (c) O 1s (d) N 1s

To quantify the composition of the different ALD LiPON processes, 50 nm of each was deposited on to Au coated Si chips and were characterized by XPS. The highresolution spectra's of Li 1s, P 2p, O 1s and N 1s are found in Figure 11 (a-d.). The results show a consistent stoichiometry of Li<sub>2</sub>PO<sub>2</sub>N as seen in our previously published results. In the high-resolution Li 1s spectra, only one state is identified (Figure 11 (a)) which is also observed in a polyphosphazene chain structure. The P 2p high resolution scan also shows a single phase of phosphorus as seen in Figure 11 (b). In contrast, the O 1s and N 1s high resolution spectra has 2 components. In the O 1s spectra (Figure 11 (c)), the low binding energy peak is associated with the polyphosphazene chain whereas the small peak at high binding energy is associated with surface contamination. The N 1s spectra also contains 2 peaks that are associated with double coordinated and triply coordinated N as shown in Figure 11 (d). However, the ratio of triply coordinated to doubly coordinated is too small. Also the ratio of P:N is one, indicating fully nitrogenated polyphosphazene phase, as published previously.<sup>54,103</sup>

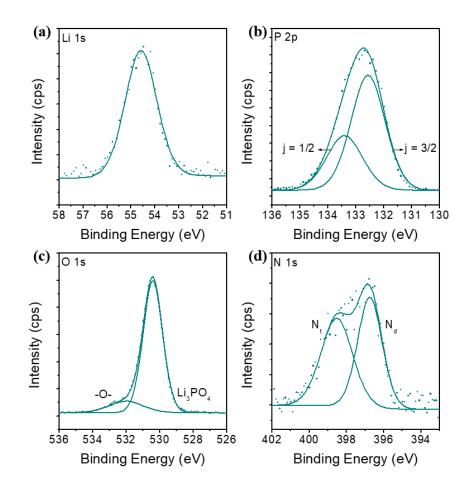

Figure 12: Plasma LiPON XPS spectra high resolution scan (a) Li 1s (b) P 2p (c) O 1s (d) N 1s

The <sup>p</sup>LiPON was characterized identically with the high-resolution spectra and is presented in Figure 12 (a-d). The result shows a stoichiometry of Li<sub>3.47</sub>PO<sub>3.43</sub>N<sub>0.24</sub>, with a P:N ratio of 0.24. The high-resolution peaks show a similar component as in thermal LiPON structure. However, the film has lower nitrogen content in the plasma LiPON film. This is due to the difference in nitrogen incorporation process. In thermal LiPON DEPA has a preformed P-N bond whereas in plasma LiPON process nitrogen dosing is done using a plasma step as discussed in the experimental section.

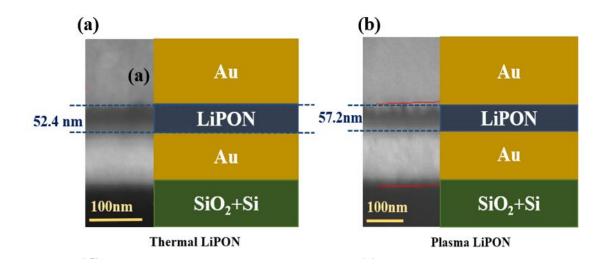

Cross-sections were made by FIB to confirm the thickness of the electrolyte. The results are shown in Figure 13Figure 12 (a) and 13(b). Here, ~50 nm <sup>t</sup>LiPON and <sup>p</sup>LiPON, are respectively witnessed and confirm the electrolyte thickness.

Figure 13: FIB-SEM cross-section of (a) Thermal LiPON (b) Plasma LiPON

# **3.4.2 Electrochemical Impedance Spectroscopy**

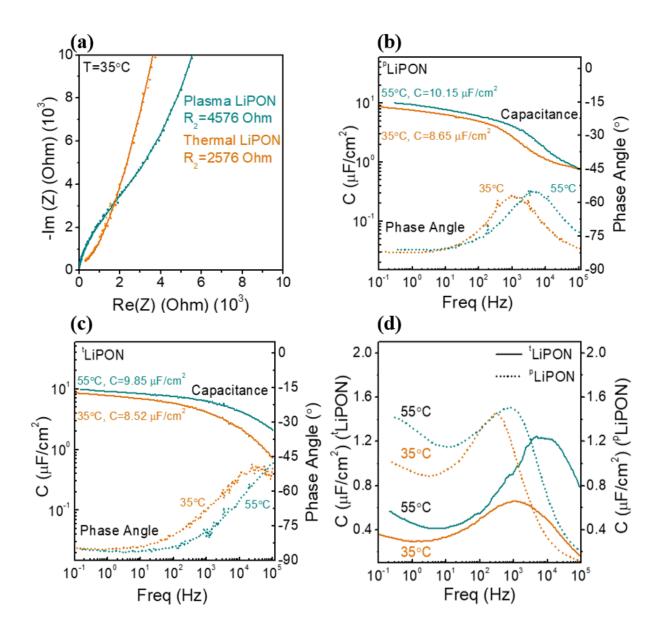

The ionic conductivity of the <sup>t</sup>LiPON and <sup>p</sup>LiPON was quantified using electrochemical impedance spectroscopy (EIS), Figure 14 (a-d). The EIS was

conducted from 0.01 Hz to 100k Hz with a sine amplitude of 10mV. Nyquist plots at room temperature are compared and shown in Figure 14 (a). These data were modeled using two constant phase elements one for the high-mid frequency region (CPE1) and the other for the low-frequency region (CPE2). The resistance and diffusion in the high and mid frequency is modelled using a resistor (Ra) and Warburg diffusion (W), respectively. A diagram of the model is shown in the inset of Figure 14 (a). Here, a semicircular arc in the high-frequency region (>10 kHz) is witnessed followed by a non-vertical line in the intermediate frequency region (10 kHz), and a straight line in the low-frequency region (<10k Hz). The semicircular arc is lithium-ion transport in the solid-state electrolyte. The nonvertical line in the mid frequency range is the impedance caused by non-uniform ion transport from the bulk of the solid-state electrolyte (LiPON) to the Au electrode.<sup>104</sup> Finally, the straight line in the low frequency corresponds to the double-layer capacitance formed at the LiPON/Au interface. The ionic conductivity of the film calculated from the model was  $5.42 \times 10^{-7}$ S/cm for <sup>t</sup>LiPON and  $6.82 \times 10^{-8}$  S/cm for <sup>p</sup>LiPON film at room temperature and agrees with previous reported results.

Figure 14: (a) Nyquist plot comparison between tLiPON and pLiPON (b) Capacitance and Phase Angle as a function of frequency (<sup>t</sup>LiPON) (c) Capacitance and Phase Angle as a function of frequency (<sup>p</sup>LiPON) (d) Imaginary Capacitance as a function of frequency (thermal)

Frequency dependence of both <sup>t</sup>LiPON and <sup>p</sup>LiPON was analyzed to quantify the capacitive characteristics of the electrolytes. The impedance data from the EIS spectra is used to calculate the real capacitance (C') and imaginary capacitance (C'') as a function of frequency using eq1, eq2 respectively, with the results shown at 35°C and 55°C in Figure 14 (b) and Figure 14 (c).

$$C' = \frac{-Z''(w)}{2\pi f S |Z(w)|^2} \quad eq1$$

$$C'' = \frac{-Z'(w)}{2\pi f S |Z(w)|^2} eq 2$$

where Z'(w) and Z''(w) is the real and imaginary part of the impedance Z(w)whereas, *f* denotes the frequency and *S* the active area.

For the <sup>p</sup>LiPON, the capacitance vs. frequency curve shows two plateaus, the first at low frequency region (<1k Hz) and the second at high frequency region (>10k Hz) as seen in Figure 14 (b) (left axis). In the low-frequency region, a capacitance of  $8.65 \text{uF/cm}^2$  at  $35^{\circ}$ C is measured, decreasing to ~1 uF/cm<sup>2</sup> at high-frequency. At  $55^{\circ}$ C, the capacitance value increases to  $10.15 \text{ uF/cm}^2$  at low frequency, but again decreases to ~1 uF/cm<sup>2</sup> at high frequency. The increase in double layer capacitance in the low frequency region is directly related to the increased ionic conductivity with elevated temperature. The phase angle as a function of frequency is plotted in the same Figure on the right axis. Here, a bell-shaped curve is witnessed. At both, high and low frequency, a phase angle of -82 is seen indicating capacitive behavior. Thus, the low frequency capacitive behavior is attributed to the ionic transport in the solid electrolyte, whereas the high frequency behavior is correlated with electrostatic polarization. Using

equation S2, the dielectric constant calculated from the high-frequency region capacitance is 14.

Figure 14 (c) shows the properties of 'LiPON as a function of frequency and temperature. The capacitance was measured to be 8.95 uF/cm<sup>2</sup> at 35°C, which increases to 15.7 uF/cm<sup>2</sup> at 55°C. The phase angle as function of frequency is plotted on the right axis in Figure 14 (c). The phase does not show a complete bell shape curve as observed in <sup>p</sup>LiPON. Similarly, the phase angle at low frequency region is close to -85, implying a double layer behavior of 'LiPON. Since the 'LiPON has an order-of-magnitude higher ionic conductivity, Figure 14 (c) shows all the same characteristics seen for the <sup>p</sup>LiPON shifted towards higher frequency, however, the electrostatic behavior of 'LiPON at high frequency is beyond the range of our potentiostat.

The relaxation time constant is a critical factor to determine performance in AC applications and defines the minimum time required to discharge the capacitor and maintain more than 50 percent efficiency. The lower value of  $\tau_0$  corresponds to the supercapacitor's better rate capability, which helps to eliminate the high order harmonics and thus protect the electronic circuits. To evaluate the relaxation time, the imaginary capacitance was plotted as a function of frequency at two different temperatures, using equation 2, and is shown in Figure 14 (d). The curve shows a typical bell shape, and the cutoff frequency (f<sub>0</sub>) corresponds to the peak of the curve. From Figure 14 (d) (right axis), the cutoff frequency for <sup>p</sup>LiPON at 35°C is 200 Hz and increases to 850 Hz at 55°C. Thus, implying a relaxation time constant ( $\tau_0$ =1/f<sub>0</sub>) of 5 ms at 35°C, which decreases to 1.1 ms at 55°C. The cutoff frequency for 'LiPON at

35°C is 1 kHz, increasing to 10 kHz at 55°C (figure 3.5(d) (left axis)). This corresponds to a relaxation time of 1 ms at 35°C and decreases to 0.1 ms at 55°C.

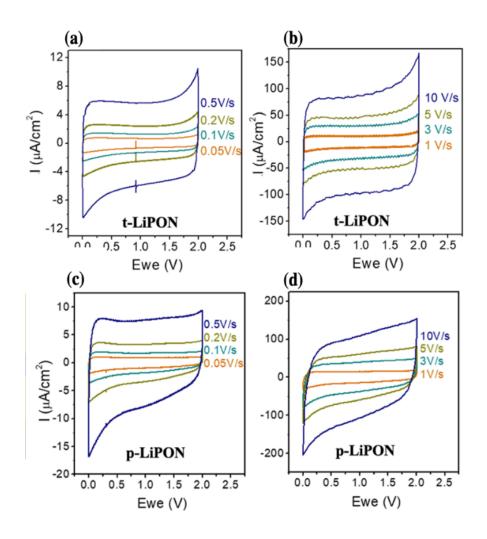

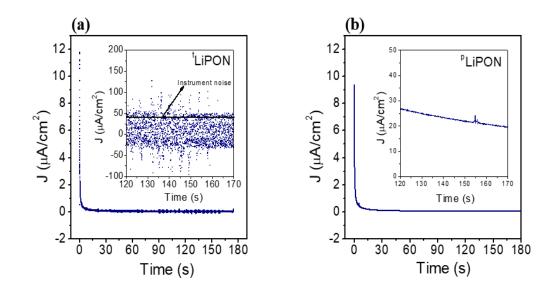

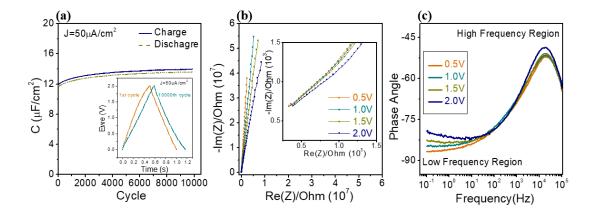

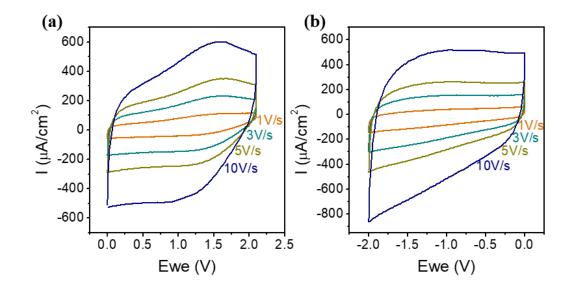

# **3.2.3** Cyclic Voltammetry Comparison