# Design of low power fast full adder using Domino Logic based on magnetic tunnel junction (MTJ) and memristor

Pooria Parvizi<sup>a</sup> (iD), Reza Sabbaghi-Nadooshan<sup>\*,b</sup> (iD), Mohammad Bagher Tavakoli<sup>a</sup> (iD)

<sup>a</sup>Electrical Engineering Department, Islamic Azad University of Arak, Arak, Iran. <sup>b</sup>Electrical Engineering Department, Islamic Azad University Central Tehran Branch, Tehran, Iran.

#### https://doi.org/10.54139/revinguc.v27i3.148

Abstract.- Domino CMOS circuits are widely used in high-performance very large scale integrated (VLSI) systems. The topology of domino circuits for high-speed operation, lower power consumption and robustness is of great importance in designing digital systems. The present paper proposes a low-power high-speed full adder circuit, which uses a new CMOS domino logic family based on magnetic tunnel junction (MTJ) elements and memristor in gate diffusion input (GDI) technique. In comparison with a static CMOS logic circuit, a dynamic logic circuit is of importance since it provides higher speed and requires fewer transistors. In comparison with the recently proposed circuit for dynamic logic styles, very low dynamic power consumption and less delay are the features of the proposed circuit. The problem with dynamic circuits is the lack of a stable output at different times, while the proposed circuit preserves the output value using memory elements such as MTJ and memristor-based full adders. Moreover, the proposed technique shows a maximum power consumption of 0,317  $\mu$ W in MTJ/memristor-based full adders. Moreover, the proposed technique shows a maximum delay of 0,35 ns. The proposed full adder is simulated, and its power dissipation and performance are analyzed using HSPICE in standard 7 nm CMOS technology.

Keywords: MTJ; Memristor; Domino Logic; Full Adder.

# Diseño de sumador completo rápido de baja potencia utilizando Domino Logic basado en Unión de Túnel Magnético (UTM) y Memristor

**Resumen.-** Los circuitos CMOS de Domino se utilizan ampliamente en sistemas integrados de gran escala (VLSI) de alto rendimiento. La topología de los circuitos dominó para operación de alta velocidad, menor consumo de energía y robustez es de gran importancia en el diseño de sistemas digitales. El presente artículo propone un circuito sumador completo de baja potencia y alta velocidad, que utiliza una nueva familia lógica de dominó CMOS basada en elementos de unión de túnel magnético (UTM) y memristor en la técnica de entrada de difusión de puerta (GDI). En comparación con un circuito lógico dinámico es importante ya que proporciona una mayor velocidad y requiere menos transistores. En comparación con los circuitos propuestos recientemente para estilos lógicos dinámicos, las características del circuito propuesto son un consumo de energía dinámica muy bajo y menos retardo. El problema con los circuitos dinámicos es la falta de una salida estable en diferentes momentos, mientras que el circuito propuesto conserva el valor de salida utilizando elementos de memoria como UTM y memristor durante el ciclo de reloj. La técnica propuesta muestra un consumo máximo de energía de 0,317  $\mu$ W en sumadores completos basados en MTJ/Memristor. Además, la técnica propuesta muestra un retraso máximo de 0,35 ns. Se simula el sumador completo propuesto, y su disipación de potencia y rendimiento se analizan utilizando HSPICE en tecnología CMOS estándar de 7 nm.

Palabras clave: MTJ; Memristor; Domino Logic; Sumador completo.

Received: August 25, 2020. Accepted: September 21, 2020.

### 1. Introduction

In last few years, the use of internet of things (IoT) devices, cell phones, tablets and

sensors has been dramatically increased. Most of these devices are battery-powered, so power consumption (battery life) can be considered as a design challenge. Consequently, researchers have attempted to present new techniques to design lowpower electronics [1]. Non-conventional CMOS and nano-technology pave the way for designing low-power electronics, which reduce the leakage

<sup>\*</sup> Correspondence author:

e-mail:r\_sabbaghi@iauctb.ac.i (R. Sabbaghi-Nadooshan)

power consumption, so low-power applications can rely on emerging technologies in this area [2]. For reducing dynamic power consumption, the energy stored in load capacitors can be recovered instead of being dissipated as heat. This technique is referred to as adiabatic (reversible) circuit design [3].

Magnetic tunnel junction (MTJ) is a nonvolatile memory with short access time and small dimensions as well as compatibility with CMOS technology [4]. Thus, it is well suited for using in logic-in-memory (LiM) architectures. LiM structures use MTJs and are very suitable for low-power designs because of almost zero static power dissipation. A memristor is also used as a memory element in this paper to design 1-bit full adder based on domino logic, and the results are eventually compared with MTJ family. In the following of this section, we will introduce the works that have been done in these fields.

Low-power designs are of great importance as the demand for battery-operated portable devices is ever-increasing. In a large number of this type of devices, the battery life is more important than the operating speed. Nano-devices and adiabatic designs are used in LiM structures to reduce, respectively, the static and dynamic power consumption. As an emerging technology, MTJ has many advantages when used in LiM structures along with CMOS technology. Sharifi [5] introduces a new adiabatic hybrid MTJ/CMOS structure for designing AND/NAND, exclusive-OR (XOR)//XNOR and 1-bit full adder circuits. The power consumption of the proposed adiabatic MTJ/CMOS full adder is more than 7 times less than those of the previous MTJ/CMOS full adders. In [6], the presented domino logic is based on MTJ elements in gate diffusion input (GDI) technique. A dynamic logic circuit is more interesting than a static CMOS logic circuit since it has higher speed and requires fewer transistors. In comparison with the recently proposed circuits for dynamic logic styles, very low dynamic power consumption and less delay are the features of the proposed circuit. Additionally, the proposed circuit shows extreme fault tolerance. A Monte Carlo simulation proves the fault tolerance of the full adder proposed in this reference. Standard 0,18 µm CMOS technology is used to simulate the proposed full adder. Both memory cell and sensing amplifier in this type of circuit, however, are less reliable, and this greatly limits the practical application of this type of circuit in logic computation. To resolve this issue, a new magnetic full adder (MFA) is presented in [7] based on pre-charge sensing amplifier (PCSA) and thermally assisted switching (TAS)-MTJ cell. Using the 65 nm CMOS technology and a precise TAS-MTJ model, mixed simulations are performed to show the high reliability while keeping low power consumption and small die area.

A few years ago, practical memristors were introduced and very soon attracted the interest of researchers and scientists. A memristor is the fourth basic two-terminal passive circuit element apart from well-known resistor, capacitor and inductor. Recently, memristor-based architectures have gained much attention from many researchers.

In this paper, we design memristor-based AND, OR and XOR gates. Using these gates, a memristor-based full adder circuit is proposed. The simulation results of the proposed circuit with these gates are reported. The remarkable improvements in the proposed circuit, compared to the conventional circuits, are lower power consumption by 54,74 %, less delay by 14,84 and using fewer transistors [8].

## 2. Background

The noise margin in domino logic is lower than that of static CMOS logic, so a relatively higher sensitivity towards noise source can be expected in domino logic circuits. Downscaling of the technology enhances noise immunity of domino logic circuits, while the power consumption of the circuit also increases. For reducing the consumed power, the supply voltage is scaled down, so the circuit delay increases. To compensate this delay, both the supply and threshold voltage scaling are performed. Reduction in the threshold voltage leads to a higher speed domino logic, while the noise immunity of the circuit decreases due to an increase in subthreshold leakage current [9, 10]. The thickness of the gate oxide is reduced as a result of downscaled technology, and this leads

to an exponential increase in gate leakage and subthreshold currents. These leakage currents may discharge the precharge node of domino circuits. Therefore, at high frequencies, leakage currents, low threshold voltage and noise sources degrade the performance of domino logic circuits [11].

Power consumption of CMOS full adders can be reduced by some techniques:

- Output and input capacitances can be minimized to reduce the dynamic power.

- Simultaneous use of both Vdd and GND in circuit components should be avoided to reduce the short and static power.

- For fewer transistors, we can use a pass transistor in a circuit; this reduces power consumption, while sometimes causes threshold losses.

- By varying the W/L ratio to minimize transistor conduction.

Various components of power consumption can be reduced by scaling down the device dimensions and supply voltage. The scaling down increases the leakage current due to the unfavorable short channel effects (SCEs) [12, 13, 14]. These effects decrease the effective channel length, which in turn, decreases the threshold voltage. Many research works have been conducted for reducing the power consumption in domino logic circuits [15, 16, 17].

### 2.1. Domino logic styles

To implement high-speed high-performance microprocessors, domino logic is more suitable than other dynamic logic styles since it requires less area and lower power [18]. Domino logic uses only one PMOS transistor in pull-up network (PUN) [13], so the area and the power consumption in domino logic is reduced compared to dynamic CMOS logic that uses n (number of inputs) PMOS transistors in the PUN.

The effects of leakage current and charge sharing on the dynamic node are prevented by the keeper transistor MK. The keeper ratio K is given by equation (1)

$$K = \frac{W_{Keeper}}{W_{PDN}},\tag{1}$$

where  $W_{Keeper}$  is the keeper transistor width and  $W_{PDN}$  is the evaluation transistor width in the *PDN*. The upsizing of keeper transistor MK enhances the robustness of the circuit by trading off the speed performance [15].

The control of the keeper circuit uses the following items:

- 1. delayed enabling of the keeper circuit,

- 2. abrupt keeper control mechanism,

- 3. keeper control signal with voltage swing variation,

- 4. keeper mechanisms with process variation tolerance and

- 5. bias voltage variation of the keeper device.

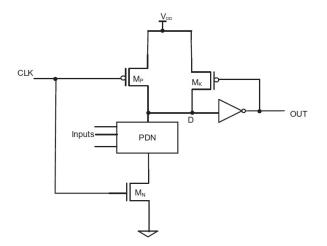

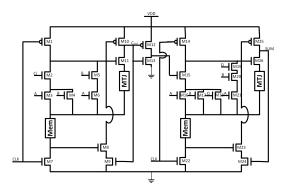

Other topologies based on PDNs with an additional discharge path have also been proposed in the literature. This modification results in increased operating speed and reduction in leakage current [15, 19]. Figure 1 shows a conventional domino logic circuit.

Figure 1: Conventional domino logic circuit

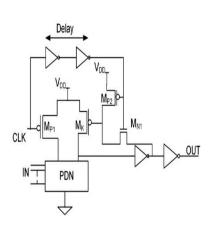

Figure 2a depicts a high-speed domino (HSD) logic [20]. In the leakage current replica (LCR) keeper technique shown in Figure 2b, an analog current mirror circuit controls the strength of the keeper device, which depends on the leakage current of PDN [21].

An additional keeper transistor and the existing conventional keeper transistor decrease the loop

(a) High-speed Domino Logic

(b) Leakage current replica keeper domino logic

(c) Grounded PMOS keeper

(d) Foot-driven stacked transistor domino logic

Figure 2: Existing domino logic circuit

gain and the delay variability in the grounded PMOS keeper structure depicted in Figure 2c [22]. The additional discharge path is controlled by the output and foot node voltages in foot-driven stacked transistor domino logic (FDSTDL) as shown in Figure 2d.

A CDDK circuit uses the principle of delayed enabling of keeper circuit, which consists of two PMOS keeper transistors in series. The delayed enabling of keeper circuit decreases the contention current between the keeper transistor and PDN. Therefore, if the PDN evaluates a TRUE condition, it facilitates faster discharge of the dynamic nodal charge through PDN, and this increases the operating speed of the circuit. In domino logic circuits, variations in the process parameters and feedback loop gain contribute considerably to the delay variability [23, 24]. These issues emphasize the need for identifying appropriate improvement techniques.

## 2.2. Magnetic Tunnel Junction (MTJ) Review

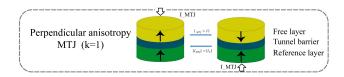

Magnetic tunnel junction comprises two ferromagnetic (FM) layers and an oxide barrier layer sandwiched between these two layers (Figure 3). Parallel and antiparallel configurations can be

realized according to the FM layers alignment. These two configurations are behind the low resistance (RP) or high resistance (RAP) behaviors of MTJ [25]. Therefore, these behaviors can be used in LiM designs.

Figure 3: Vertical MTJ nanopillar structure. MTJ states change from P to AP and vice versa by applying a current (IMTJ) higher than the critical current (IC)

The techniques proposed for switching MTJ configurations are as follows: field induced magnetization switching (FIMS), thermally assisted switching (TAS) and spin torque transfer (STT). Spin torque transfer is the most promising technique, which is considered as a replacement for the other two techniques. This technique needs only a bi-directional low switching current. The states of the MTJ are switched when the current of MTJ (IMTJ) becomes higher than a critical current [26]. FIMS is the conventional approach for switching MTJ states, RAP and RP, which depend on the applied magnetic field. The disadvantages of this method are high power consumption, poor selectivity and poor scalability, which result from high switching currents.

#### 2.3. Memristor

Custom neuromorphic hardware platforms are of great interest for accelerating neural network algorithms since they can perform complex tasks that are analogous to the physical processes in biological nervous systems [27]. A fundamental feature of these systems is their capability to overcome the restrictions [28]. The modern CMOS technology is employed to mimic the behavior of neurons; however, the lack of a device for effectively performing synaptic operations has hindered the advancement in this area for several years. We propose a domino logic architecture for memristor-based neuromorphic computing. The architecture uses a simple binary neuron activation function and the delay of memristor RC circuits to perform synaptic computations. Synchronization schemes are presented to communicate information between the layers of neural network, and a simple linear power model is developed to estimate the energy efficiency of the architecture for a particular network size.

### 2.3.1. Memristor Modeling

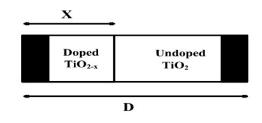

Chua and Kang introduced physical memristive devices; however, the area of memristors and memristive devices has not drawn any interest for more than 35 years. In 2008, the theory of memristive devices was developed by Hewlett Packard researchers, and this theory was implemented in  $TiO_2$  resistive switches. Hewlett Packard researchers proposed a device, which was claimed to be similar to an ideal memristor when it came to the structure and behavior of the device.

Figure 4: Hewlett Packward original device model

Figure 5: Equivalent circuit of memristor

The proposed structure is shown in Figure 4, and the equivalent electrical circuit of the memristor is shown in Figure 5. Time-dependent voltage and current can be expressed with equations (2), (3) and, (4) [29]:

$$v(t) = R(t) \cdot i(t) \tag{2}$$

$$R(t) = \frac{R_{on}w(t)}{D} + \frac{R_{off}(1 - w(t))}{D}$$

(3)

$$\frac{dw(t)}{dt} = \frac{\mu v R_{on}}{D} \cdot i(t) \tag{4}$$

where  $R_{on}$  is the resistance for x(t) = D, and  $R_{off}$  is the resistance for x(t) = 0; x(t) is the state variable over [0, D].

Memristors are characterized by relatively short switching time, high endurance and low switching energy (typically 0,1–1 PJ), so memristive technologies are basically studied for memory applications [30, 31, 32, 33].

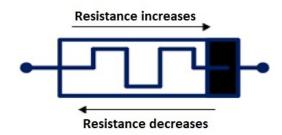

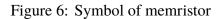

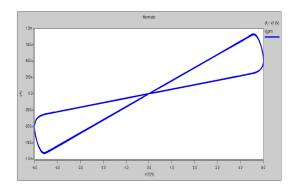

The symbol of memristor is shown in Figure 6. When current flows into (out of) the black strip, memristance decreases (increases) [34]. However, plotting the current flowing in the memristor versus the voltage across it results in a hysteresis loop (Figure 7), which is always pinched at the origin.

## 2.3.2. Physics Of Hysteresis Loop

Sinusoidal current i(t) can lead to hysteresis. In this case, maxima and minima are shifted with respect to the corresponding memristor voltage v(t). When both i(t) and v(t) become simultaneously zero, pinching occurs. The memristor can reach a maximum value of Roff and a minimum value of  $R_{on}$ . The maximum resistance can be expressed by the amplitude of input parameters. Many research works [35, 36, 37, 38, 39] have used mathematical models of memristor but a nonlinear dopant drift memristor model has been used for simulation of the proposed circuits [29].

282 - 293

Figure 7: Hysteresis curve of memristor model (current–voltage pinched hysteresis loop)

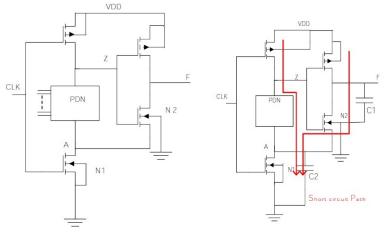

### 2.4. Pseudo Domino Circuit

The pseudo domino logic outperforms domino logic because of precharge pulse propagation. A pseudo domino circuit [40] connects source node of the nMOS of the inverter to the drain terminal of the evaluation MOS at node A, instead of ground (Figure 8a). Thus, the value at node Z cannot propagate to the output node F in precharge phase, when the evaluation transistor N1 is off. This connection saves up to 32 % more power than conventional domino logic designs. This topology essentially improves the performance during the precharge phase. The pseudo domino logic circuit experience charge sharing and leakage issues because of short circuit paths. These issues can be resolved by using a keeper circuit.

The voltage drop at output node occurs because of charge sharing issue. In Figure 8b, when all inputs of pull-down network are equal to 1 in precharge phase, the threshold voltage drops at the output node Z. This voltage drop can be propagated to node F. The output voltage is redistributed on capacitances C1 and C2 as transistor N2 is ON. Therefore, the speed and power dissipation of the circuit are deteriorated, so a voltage drop occurs at output node F. If the value of output load capacitance C1 is equal to the node capacitance C2, then the voltage at output node reaches VDD/2.

Two methods can be used as solutions: 1) using a load capacitor with a capacitance much greater than any other charge sharing capacitance [40] and 2) using a keeper circuit [41]. Different keeper techniques are used in pseudo domino logic for power dissipation in this reference.

(a) Pseudo domino circuit

(b) Charge sharing problem in pseudo domino circuit

Figure 8: Pseudo domino

## 3. Proposed preamplifier topology

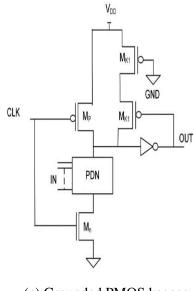

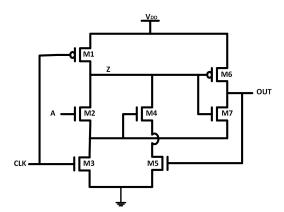

A new method is proposed in this section to design a domino logic. The proposed domino logic circuit shown in Figure 9, has a higher speed than conventional domino logic circuits.

Figure 9: The proposed domino logic circuit

The circuit consists of two clock transistor elements. In this circuit, when the clock and A both are low, Z will be high and the output node will not change. The same is true when the clock is grounded and input A is high. When the clock and A both are high, both Z and the output will be high. When the clock is high and input A is low, Z will not change. In this condition, if Z is high (grounded), the output will be low (high).

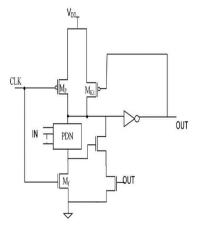

Now, a full adder based on the novel domino logic circuit as well as MTJ and memristor

components as shown in Figure 10. In the proposed circuit, MTJ components are used in the output inverter to improve the circuit performance to stay at stable values. Additionally, to reduce the delay due to the use of memory elements in these circuits, we use discharge transistors to remove the electric charge from the z-storage node. This reduces the power consumption and delays the main nodes.

Figure 10: Schematic of the proposed final full adder based on MTJ and memristo

## 4. Simulation results

The simulation results of the proposed domino logic and full adder are presented in this section.

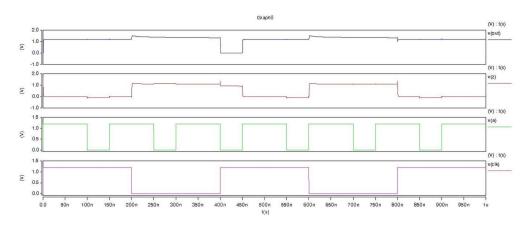

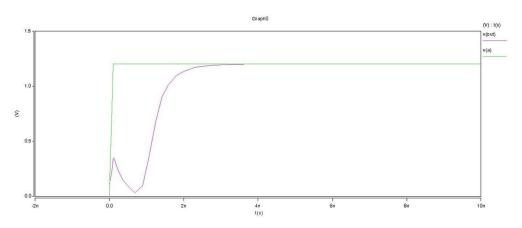

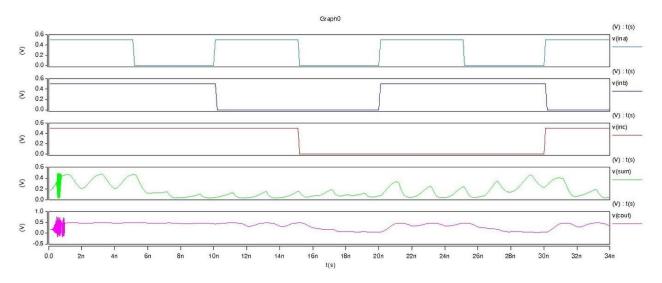

Figure 11 shows the simulation results of the proposed domino logic. The delay of this domino is plotted in Figure 12. As can be seen, the delay of this circuit is about 2 ns.

288

Universidad

de Carabobo

Figure 11: Simulation results of the proposed domino logic

Figure 12: Delay of the proposed domino

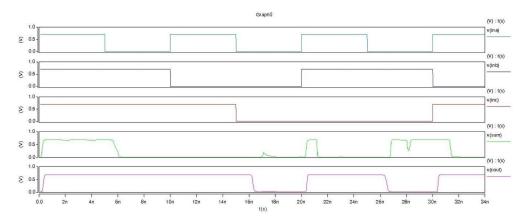

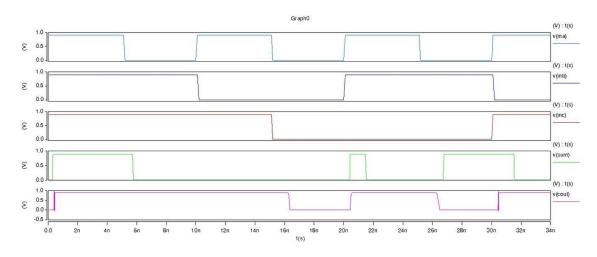

Figure 13: Simulation result of the proposed full adder based on memristor and MTJ

Figure 13 shows the simulation results of the proposed full adder based on memristor and MTJ. As can be seen, when all inputs are high, the sum of both outputs and *Cout* are high. When two inputs are high and the other input is low, one output is low and the other is high.

In Table 1, a comparison is made between the proposed full adder and those in other works.

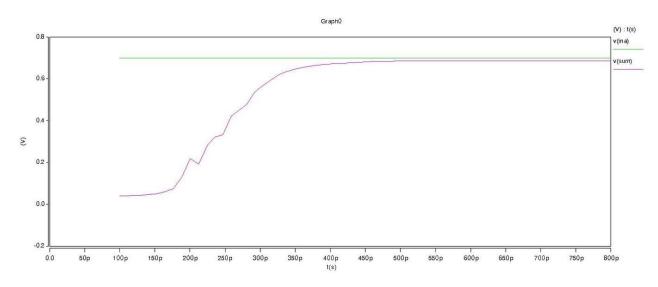

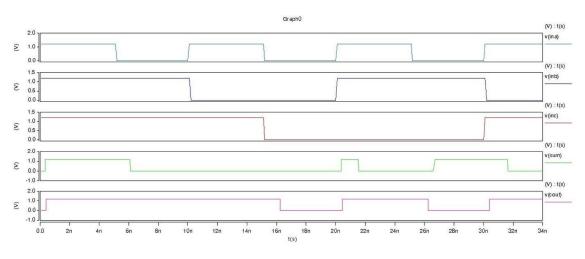

To show the stability of the circuit against voltage fluctuations, the circuit output for different values of voltage is investigated. Figures 15, 16 and 17 show the circuit output for 0,5; 0,9 and 1,2V

Figure 14: Delay of the proposed full adder

Table 1: Comparison of the proposed full adder and those in other references

| Paper                  | Voltage supply | Power                  | Delay | Technology |

|------------------------|----------------|------------------------|-------|------------|

|                        | (v)            | consumption ( $\mu$ w) | (ns)  |            |

| 5                      | 0,9            | 0,12                   | 1     | 32nm CMOS  |

| 6                      | 2,5            | 0,447                  | 0,35  | 180nm CMOS |

| 43                     |                | 1730                   | 1,009 |            |

| 44                     |                | 5,736                  | 0,179 |            |

| 45                     |                | 127                    | 1,117 |            |

| This work<br>(MTJ&MEM) | 0,7            | 0,317                  | 0,35  | 7nm CMOS   |

Figure 15: Simulation result of the proposed full adder for 0.5v

respectively.

Figure 16: Simulation result of the proposed full adder for 0.9v

Figure 17: . Simulation result of the proposed full adder for 1.2v

## 5. Conclusion

A new low-power high-speed full adder circuit, which uses a new CMOS domino logic family, was presented in this paper. A new structure for adiabatic hybrid MTJ and MEM-CMOS circuits was also presented in this work. Moreover. the proposed full adder was compared with other previously presented basic logic gates and full adders. The advantages of the proposed circuits were their simpler architecture, lower power consumption, higher speed and using fewer The designs were simulated and transistors. compared with several state-of-the-art designs. We used Synopsys HSPICE simulator with 7 nm technology files to test the presented designs. The results showed the lower power consumption of the proposed adiabatic MTJ-CMOS designs compared to state-of-the-art designs. In the final full adder circuit, sustainable outputs with optimal power consumption were achieved for hybrid structure of memristor and MTJ. Accordingly, the results of outputs indicated the feasibility of an optimal full adder design.

## 6. References

- M. Pedram and J. M. Rabaey, *Power aware design methodologies*. Boston, MA, USA: Springer Science & Business Media, 2002.

- [2] Y. Zhang, W. Zhao, J. O. Klein, W. Kang, D. Querlioz, Y. Zhang, D. Ravelosona, and C. Chappert, "Spintronics for low-power computing," in *DATE '14: Proceedings of the conference on Design, Automation* & *Test in Europe*, Leuven, BEL, 2014.

- [3] W. C. Athas, L. J. Svensson, J. G. Koller, N. Tzartzanis, and E. Y. C. Chou, "Low-power digital systems based on adiabatic-switching principles," *IEEE Transactions* on Very Large Scale Integration (VLSI) Systems, vol. 2, no. 4, pp. 398–407, 1994.

- [4] E. Deng, Y. Zhang, J. O. Klein, D. Ravelsona, C. Chappert, and W. Zhao, "Low power magnetic fulladder based on spin transfer torque MRAM," *IEEE transactions on magnetics*, vol. 49, pp. 4982–4987, 2013.

- [5] F. Sharifi, Z. Saifullah, and A. H. Badawy, "Design of adiabatic MTJ-CMOS hybrid circuits," in 2017 IEEE 60th International Midwest Symposium on Circuits and Systems (MWSCAS). IEEE, 2017, pp. 715–718.

- [6] S. j. Jassbi and m. mousavi, "A Novel Low Power Full Adder Using a Modified Domino Logic," *International Journal of Computer Sciences and Engineering*, vol. 4, no. 6, pp. 8–11, 2016.

- [7] Y. Gang, W. Zhao, J. Klein, C. Chappert, and P. Mazoyer, "A High-Reliability, Low-Power Magnetic Full Adder," *IEEE Transactions on Magnetics*, vol. 47, no. 11, pp. 4611–4616, 2011.

- [8] M. Anis, S. Areibi, and M. Elmasry, "Design and optimization of multithreshold CMOS (MTCMOS) circuits," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 22, no. 10, pp. 1324–1342, 2003.

- [9] M. J. Gitanjali, "Efficient adders for assistive devices," *Engineering Science and Technology, an International Journal*, vol. 20, no. 1, pp. 95–104, 2017.

- [10] K. Roy, S. Mukhopadhyay, and H. Mahmoodi-Meimand, "Leakage current mechanisms and leakage reduction techniques in deep-submicrometer CMOS circuits," *Proceedings of the IEEE*, vol. 91, no. 2, pp. 305–327, 2003.

- [11] S. H. Choi, B. C. Paul, and K. Roy, "Dynamic noise analysis with capacitive and inductive coupling [high-speed circuits]," in *Proceedings of ASP-DAC/VLSI Design 2002. 7th Asia and South Pacific Design Automation Conference and 15h International Conference on VLSI Design*, 2002, pp. 65–70.

- [12] S. M. Sharroush, Y. S. Abdalla, A. A. Dessouki, and E. A. El-Badawy, "Impact of technology scaling on the performance of domino CMOS logic," in 2008 *International Conference on Electronic Design*, 2008, pp. 1–7.

- [13] M. J. Garima and H. Lohani, "Design, implementation and performance comparison of multiplier topologies in power-delay space," *Engineering Science and Technology, an International Journal*, vol. 19, no. 1, pp. 271–278, 2016.

- [14] M. H. Moaiyeri, M. Nasiri, and N. Khastoo, "An Efficient ternary serial adder based on carbon nanotube FETs," *Engineering Science and Technology, an International Journal*, vol. 19, no. 1, pp. 355–363, 2016.

- [15] F. Moradi, T. V. Cao, E. I. Vatajelu, A. Peiravi, H. Mahmoodi, and D. T. Wisland, "Domino logic design for high performance and leakage-tolerant applications," *Integration*, vol. 46, no. 3, pp. 247–254, 2013.

- [16] F. Moradi, H. Mahmoodi, and A. Peiravi, "A High Speed and Leakage-Tolerant Domino Logic for High Fan-in Gates," in *Proceedings of the 15th ACM Great Lakes Symposium on VLSI*, ser. GLSVLSI '05. New York, NY, USA: Association for Computing Machinery, 2005, pp. 478–481.

- [17] A. Dadoria, K. Khare, T. Gupta, and R. Singh, "A Novel High-Performance Lekage-Tolerant, Wide Fan-In Domino Logic Circuit in Deep-Submicron Technology," *Circuits and Systems*, vol. 6, no. 4, pp. 103–111, 2015.

- P. Gronowski, *Design of High-Performance Microprocessor Circuits*. Piscataway, NJ: IEEE Press, 2001, ch. Issues in dynamic logic design, Design of High-Performance Microprocessor Circuits, pp. 140–157.

- [19] S. Garg and T. K. Gupta, "Low power domino logic circuits in deep-submicron technology using CMOS," *Engineering Science and Technology, an International Journal*, vol. 21, no. 4, pp. 625–638, 2018.

- [20] M. H. Anis, M. W. Allam, and M. I. Elmasry, "Energyefficient noise-tolerant dynamic styles for scaleddown CMOS and MTCMOS technologies," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 10, no. 2, pp. 71–78, 2002.

- [21] Y. Lih, N. Tzartzanis, and W. W. Walker, "A Leakage Current Replica Keeper for Dynamic Circuits," *IEEE Journal of Solid-State Circuits*, vol. 42, no. 1, pp. 48– 55, 2007.

- [22] G. Palumbo, M. Pennisi, and M. Alioto, "A Simple Circuit Approach to Reduce Delay Variations in Domino Logic Gates," *IEEE Transactions on Circuits* and Systems I: Regular Papers, vol. 59, no. 10, pp. 2292–2300, 2012.

- [23] M. Alioto, G. Palumbo, and M. Pennisi, "Understanding the Effect of Process Variations on the Delay of Static and Domino Logic," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 18, no. 5, pp. 697–710, 2010.

- [24] H. F. Dadgour and K. Banerjee, "A Novel Variation-Tolerant Keeper Architecture for High-Performance Low-Power Wide Fan-In Dynamic or Gates," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 18, no. 11, pp. 1567–1577, 2010.

- [25] B. Behin-Aein, J.-P. Wang, and R. Wiesendanger, "Computing with spins and magnets," *MRS Bulletin*, vol. 39, no. 8, pp. 696–702, 2014.

- [26] W. Zhao, E. Belhaire, C. Chappert, and P. Mazoyer, "Spin Transfer Torque (STT)-MRAM–Based Runtime Reconfiguration FPGA Circuit," ACM Trans. Embed. Comput. Syst., vol. 9, no. 2, Oct. 2009.

- [27] R. Douglas, M. Mahowald, and C. Mead, "Neuromor-

phic Analogue VLSI," *Annual Review of Neuroscience*, vol. 18, no. 1, pp. 255–281, 1995, pMID: 7605063.

- [28] S. R. Nandakumar, S. R. Kulkarni, A. V. Babu, and B. Rajendran, "Building Brain-Inspired Computing Systems: Examining the Role of Nanoscale Devices," *IEEE Nanotechnology Magazine*, vol. 12, no. 3, pp. 19–35, 2018.

- [29] Z. Biolek, D. Biolek, and V. Biolkov, "SPICE Model of Memristor with Nonlinear Dopant Drift," *Radioengineering*, vol. 18, no. 2, pp. 210–214, 2009.

- [30] F. Argall, "Switching phenomena in titanium oxide thin films," *Solid-State Electronics*, vol. 11, no. 5, pp. 535–541, 1968.

- [31] J. J. Yang, M. D. Pickett, X. Li, D. A. A. Ohlberg, D. R. Stewart, and R. S. Williams, "Memristive switching mechanism for metal/oxide/metal nanodevices," *Nature Nanotechnology*, vol. 3, no. 7, pp. 429–433, 2008.

- [32] M. D. Pickett, D. B. Strukov, J. L. Borghetti, J. J. Yang, G. S. Snider, D. R. Stewart, and R. S. Williams, "Switching dynamics in titanium dioxide memristivev devices," *Journal of Applied Physics*, vol. 106, no. 7, pp. 074 508–074 514, 2009.

- [33] R. S. Williams, G. Medeiros Ribeiro, D. Borisovich Strukov, and J. Yang, "Controlled switching memristor," U.S. patentus US20 120 313 070A1, 2012.

- [34] M. Mahvash and A. C. Parker, "A memristor SPICE model for designing memristor circuits," in 2010 53rd IEEE International Midwest Symposium on Circuits and Systems, 2010, pp. 989–992.

- [35] J. G. Simmons, "Generalized Formula for the Electric Tunnel Effect between Similar Electrodes Separated by a Thin Insulating Film," *Journal of Applied Physics*, vol. 34, no. 6, pp. 1793–1803, 1963.

- [36] D. B. Strukov, G. S. Snider, D. R. Stewart, and R. S. Williams, "The missing memristor found," *Nature*, vol. 453, pp. 80–83, 2008.

- [37] T. A. Wey and S. Benderli, "Amplitude modulator circuit featuring TiO<sub>2</sub> memristor with linear dopant drift," *Electronics Letters*, vol. 45, no. 22, pp. 1103–1104, 2009.

- [38] Y. N. Joglekar and S. J. Wolf, "The elusive memristor: properties of basic electrical circuits," *European Journal of Physics*, vol. 30, no. 4, pp. 661–683, 2009.

- [39] S. Shin, K. Kim, and S.-M. Kang, "Compact Models for Memristors Based on Charge-Flux Constitutive Relationships," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 29, no. 4, pp. 590–598, 05 2010.

- [40] T. Fang, B. Amine, and G. Zhouye, "Low power dynamic logic circuit design using a pseudo dynamic buffer," *Integration*, vol. 45, no. 4, pp. 395–404, 2012.

- [41] V. Kursun and E. G. Friedman, "Domino logic with variable threshold voltage keeper," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 11, no. 6, pp. 1080–1093, 2003.