# Time Dynamics of the Down-Coupling Phenomenon in 3-D NAND Strings

Mattia Giulianini, Gerardo Malavena<sup>®</sup>, *Member, IEEE*, Christian Monzio Compagnoni<sup>®</sup>, *Senior Member, IEEE*, and Alessandro S. Spinelli<sup>®</sup>, *Senior Member, IEEE*

are listed in Table I.

Abstract— We present a detailed analysis of the time dynamics of the down-coupling phenomenon (DCP) in 3-D NAND Flash memory strings. The transient time dynamics of the channel potential following the wordline (WL) bias transition from the pass voltage to zero is studied via numerical simulation, highlighting the existence of three temporal regimes controlled by different physical processes: electron emission from traps, hole injection from the string edges followed by capture, and propagation along the string. The impact of these processes is separately studied, followed by an analysis of the dependence of the DCP recovery time on architectural parameters. Results highlight the relevant physics and can be used as a design guideline for NAND strings with reduced sensitivity to the DCP.

Index Terms—3-D NAND Flash memories, down-coupling phenomenon (DCP), gate-induced drain leakage (GIDL) current, macaroni MOSFET, self-boosting effect.

#### I. INTRODUCTION

THE transition from planar to 3-D NAND Flash memories has allowed the pursuit of astonishing results in terms of density and cost [1], stacking more than 170 memory layers and overcoming the 10-Gb/mm<sup>2</sup> density figure [2], [3]. To continue along this path, however, an ever-increasing number of challenges from the process, design, and system viewpoints must be overcome [4], on top of which we must also account for reliability. From this standpoint, the peculiar architecture of 3-D NAND has brought to the forefront new concerns that add to the well-known problems inherited from planar arrays [5]. Examples of such new issues include phenomena related to the polycrystalline nature of the conduction channel [6], [7], [8], [9], [10], [11] and issues connected to floating-body effects in the vertical string channels.

The down-coupling phenomenon (DCP) is one of the latter. Reported for the first time in 2016 [12], it describes the sudden drop in the channel potential  $V_{ch}$  of the string that

Manuscript received 5 October 2022; revised 21 October 2022; accepted 21 October 2022. Date of publication 4 November 2022; date of current version 30 November 2022. The review of this article was arranged by Editor P.-Y. Du. (*Corresponding author: Alessandro S. Spinelli.*)

The authors are with the Dipartimento di Elettronica, Informazione e Bioingegneria, Politecnico di Milano, 20133 Milan, Italy (e-mail: mattia.giulianini@polimi.it; gerardo.malavena@polimi.it; christian.monzio@polimi.it; alessandro.spinelli@polimi.it).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TED.2022.3217718.

Digital Object Identifier 10.1109/TED.2022.3217718

SL oxide polySi ONO h<sub>WL</sub> h<sub>IC</sub> h<sub>SG</sub> BL filler channel layer

dotted line. Blue regions = oxide. Yellow/orange regions = polysilicon.

Green region = nitride. Red lines = metal contacts. Parameter values

can result following a wordline (WL) step from the pass voltage to zero. Depending on the programed pattern of the string, the capacitive coupling between gates and channel can bring  $V_{ch}$  to negative values, which can be detrimental to memory operation: under program verify, for example, the negative potential can reduce the boosted potential, affecting the program disturb [13], [14]. Such phenomena depend on both the amplitude and duration of the DCP, but the latter has not been the focus of previous studies.

This article aims to provide a comprehensive analysis of the transient behavior of the DCP using numerical simulations. We discuss the different physical processes involved in the string transient, highlighting the role of electrons and holes, of trapping and propagation. Then, we investigate the dependence of the return-to-equilibrium time on the architectural parameters of the string. Results are useful as a design guide-line for minimizing the DCP effects in future NAND strings.

## **II. STRING DYNAMICS**

### A. Device Structure and Parameters

We consider one of the most common architectures for 3-D NAND arrays, i.e., the one employing cylindrical vertical strings running from a sourceline (SL) to a bitline (BL), in which individual transistors are defined by the intersection with planar WLs [15]. A radial cross section of a string including two select elements (SGs) is reported in Fig. 1: note that the silicon channel region is a hollow cylinder internally filled with oxide, according to [16]. A continuous ONO (SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub>) layer is used as gate-stack element. Parameters of the structure are similar to the one used in [17] and [18] and are reported in Table I (all dopings are *n*-type).

This work is licensed under a Creative Commons Attribution 4.0 License. For more information, see https://creativecommons.org/licenses/by/4.0/

TABLE I STRUCTURE PARAMETERS

| $\overline{n}$ | 64       | $h_{WL} = h_{SG}$          | 40 nm                         |

|----------------|----------|----------------------------|-------------------------------|

| $r_{f}$        | 30 nm    | $h_{IC}$                   | 40 nm                         |

| $z_{ch}$       | 10 nm    | $h_{IC}$<br>Channel doping | $10^{15}~{ m cm}^{-3}$        |

| $z_{ONO}$      | 4/8/8 nm | BL/SL contact doping       | $5	imes 10^{19}~{ m cm}^{-3}$ |

|                | , ,      | 1 10                       |                               |

In our analysis, we exploit the cylindrical symmetry of the string, conducting 2.5-D simulations [19]. For simplicity, moreover, the polycrystalline nature of the silicon channel that results from the manufacturing process with the current technology [20], [21] was represented following [22], where the nonuniform polysilicon with a granular structure is treated as a uniform material with spatially uniform bulk traps. A large number of papers confirmed the validity of such an approach, reporting trap energy distributions with a double-exponential shape in the energy gap [23], [24], [25], [26], [27], [28], [29], [30], [31], i.e.,

$$N_A(E) = N_{A,t} e^{\Delta E_C/k_B T} + N_{A,d} e^{\Delta E_C/k_B T}$$

$$N_D(E) = N_{D,t} e^{\Delta E_V/k_B T} + N_{D,d} e^{\Delta E_V/k_B T}$$

(1)

where  $N_A$  and  $N_D$  are acceptor-like and donor-like states, respectively, suffixes t and d stand for tail and deep states,  $\Delta E_C = E - E_C$  and  $\Delta E_V = E_V - E$  ( $E_C$  and  $E_V$  being the conduction and valence band edges), and  $k_B T$  is the thermal energy. As for the parameter values, we selected the ones from [26], adding a polysilicon/oxide interface state density. Following [32], we assumed a constant density  $N_{\rm it}$  of acceptor-like and donor-like states in the upper and lower halves of the gap, respectively, with density picked in agreement with the range reported in [33] and equal to  $3 \times 10^{12}$  cm<sup>-2</sup> eV<sup>-1</sup>. Capture cross sections for polysilicon states were taken from [34]  $(4 \times 10^{-14} \text{ and } 4 \times 10^{-16} \text{ cm}^2 \text{ for}$ charged and neutral states), while a value of  $10^{-15}$  cm<sup>2</sup> was retained for interface states. Finally, a constant mobility of 100 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> was assumed for both electrons and holes (this parameter has little effect on results), and a tungsten metal gate considered [14], with a work function of 4.5 eV. With such parameters, the neutral threshold voltage  $(V_T)$  of the cells (defined at a constant current of 10 nA, with 1 V applied to the BL) is around 0.5 V.

As for the physical models accounted for, we followed previous works on polysilicon conduction [26], [27] and included Poole–Frenkel (PF) emission and trap-assisted tunneling (TAT) for polysilicon traps, using default parameters [19]. Direct band-to-band tunneling (BBT) was also included, with a simple model [35] and using the standard parameters for silicon. It is important to point out that the quantitative value of our results is obviously dependent on such choices and can vary even strongly if the parameters are modified. In fact, the purpose of the work is not to present results calibrated against experimental data, difficult if not impossible to obtain, but to clarify the different processes involved and their roles, which remains correct, irrespective of the exact numerical values.

## B. DCP Transient Results

We simulated the behavior of an inhibited string at the end of a program-verify phase, during which BL and SL are left

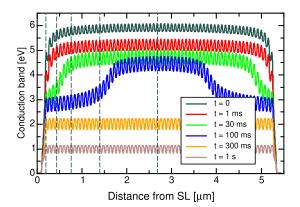

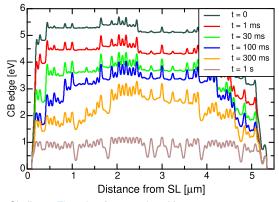

Fig. 2. CB edge along the string for different times after the trailing edge of the WL pulse. Dashed lines show the positions at which the time dynamics is investigated.

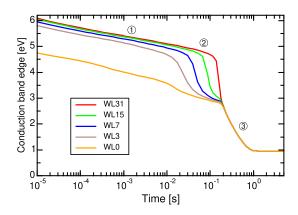

Fig. 3. CB edge at selected points in Fig. 2 as a function of time.

to ground, while the WLs and the SGs are lowered from a positive voltage  $V_{\text{pass}} = 8$  V to zero [12] (we neglect for simplicity that one WL should be at read voltage, as this has no impact on the results). Moreover, as the purpose of this article is to investigate the physical processes involved in the transient, we considered the simplest case, where all cells (except the SGs) are programed to a threshold  $V_T = 5.5$  V (by placing a suitable amount of charge in their nitride layers). As pointed out in [12], when the WL voltage falls below  $V_T$ , the cells are cut off, and the string enters a floating condition, its potential being determined by capacitive coupling with the adjacent nodes. The negative WL step from  $V_T$  to zero is then mirrored in the string potential, that falls to around  $-V_T$  at the end of the pulse, recovering then the equilibrium value. This behavior clearly appears from Fig. 2, where the polysilicon conduction band (CB) profile along the string is plotted for different times (t = 0 being the time at which the WL voltage reaches zero). Results show an initial phase, with less than 1-eV decrease in 1 ms, followed by a sudden drop that propagates from the contacts to the middle of the string, and a final phase with uniform lowering of the CB edge.

To investigate the dynamics, it is better to look at the CB edge as a function of time for different positions along the string, as reported in Fig. 3. Positions are marked as dashed lines in Fig. 2 and correspond to the centers of WL31, WL15, WL7, WL3, and WL0. The transients can be broken down into three parts: a logarithmic transient (1), a sequential drop

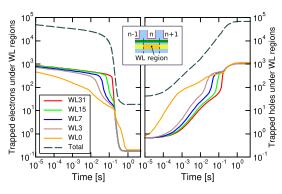

Fig. 4. Trapped carriers in the polysilicon under the selected WL regions as a function of time. The inset shows the considered region for each WL, including the area below the gate and half the intercell region per side.

Fig. 5. Pictorial view of conduction and valence bands along the string, with filled acceptor-like (red band) and donor-like (green band) trap states. Carrier capture/emission and flow are marked by arrows, assuming that the closest electrode lies on the left-hand side. A diminishing hole flow toward the center is suggested by decreasing line thickness in the valence band.

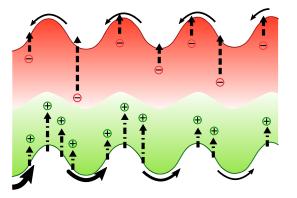

of the WL CB edges (2), and a final stage with uniform string evolution ③. To understand these behaviors, we can look at the charges: Fig. 4 shows the total number of trapped carriers in the polysilicon under each selected WL region (a region including the WL itself plus half the intercell distance per side, as schematically depicted in the inset) as a function of time, plus the total trapped charge under the 64 cells (free carriers are not shown as their number is always much smaller than the trapped ones). Let us first recall the initial condition: at the beginning of the  $V_{\text{pass}}$  transient, the string is biased above threshold, and the total charge is dominated by electrons. When  $V_{\text{pass}}$  has reached zero, we enter region ①: bulk and interface traps emit electrons in the CB, that move toward the electrodes (overcoming the energy barrier setup by the programming charge), as schematically depicted in Fig. 5. It is important to point out that the logarithmic dependence of this part of the transient suggests that the limiting factor is electron emission from traps rather than the electron transit time: as time elapses, deeper and deeper traps are involved, with longer and longer emission times. Such a logarithmic trend is similar to what is observed in-say-detrapping phenomena from oxide traps in Flash memories [36], [37].

We now turn our attention to holes: initially, almost no holes are present, neither free nor trapped. As the string potential is negatively boosted, holes are generated at the string edges via BBT and TAT and are trapped under the first WLs [see the

Fig. 6. Similar to Fig. 3 but under different conditions: red = full simulation, blue = no BBT nor TAT, and green = no BBT nor TAT nor PF. Solid lines = WL31. Dashed lines = WL0.

early increase under WL0 in Fig. 4 (right)]. The majority of the injected holes are trapped and recombine with electrons, while a minor fraction is emitted over the barrier and diffuse toward the center of the string, being trapped under some downstream WL. This process is schematically depicted in Fig. 5, showing that hole trapping is higher in edge WLs and resulting in a decreasing flow of holes toward the center of the string. Note that hole generation is related to the electric field at the string edges, which does not change appreciably during phase (D). Hence, a linear increase in the total hole concentration results, as reported in Fig. 4 (the dashed line in the log–log scale has unity slope).

The local increase in trapped holes has two consequences: first, it slows down further trapping as less free traps are available, increasing the hole flux toward inner WLs and resulting in a sequential filling of the WL regions, as can be seen in Fig. 4 (right). Second, it begins to affect the electrostatics: when the number of holes trapped under a WL becomes large enough, the local WL CB edge is lowered, and we enter phase Q). This process takes place sequentially starting from the edge WLs and goes on until a uniform hole concentration and CB profile are established. Note also that the holes can recombine with electrons in acceptor-like states, resulting in the sudden drop of trapped electron concentration at the onset of phase Q [Fig. 4 (left)].

The lower potential and field determined by the hole concentration mean that the BBT and TAT generation rates must now decrease. This determines a slower transient characterized by a uniform evolution of the string, labeled as phase ③, that eventually brings the string to the equilibrium.

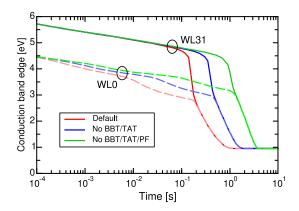

# C. Physical Processes and Parameters

Once the main picture is made clear, we have investigated, the role played by the different physical processes during the string transient. Fig. 6 shows the same curves as in Fig. 3 (for WL0 and WL31 only) when different mechanisms are turned off (red is the default case). In particular, the blue curves show the transient when tunneling-related phenomena (i.e., BBT and TAT) are turned off. This lowers the hole injection at the string edges, slowing the transient. Note, however, that part ① of the transient, governed by electrons, is not affected by this choice. Even further delay in the CB drop is achieved when

Fig. 7. Similar to Fig. 6 but for different values of bulk trap density: red = nominal case, blue = acceptor-like state density =  $5\times$ , and green = donor-like state density =  $5\times$ . Solid lines = WL31. Dashed lines = WL0.

PF emission, also dependent on the electric field, is removed (green curves). This limiting case is particularly interesting as the only remaining process that can give rise to phase  $\bigcirc$  is Shockley–Read–Hall generation. However, as the initial  $V_{\text{pass}}$  is higher than  $V_T$ , donor-like states are filled with electrons, and no holes exist in the valence band at the beginning of the transient. The only hole generation process left is then electron emission from very deep donor-like states, resulting in trapped holes, which is the ultimate mechanism that can bring the string to equilibrium.

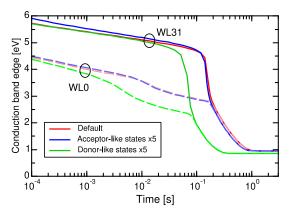

We have then investigated the role played by the trap density, by separately changing the density of donor- and acceptor-like states in the poly-Si, adjusting the nitride charge in order to retain  $V_T = 5.5$  V. Results (with all generation mechanisms being active) are shown in Fig. 7: if the density of acceptor-like states only is increased (by a factor of 5), the blue transients result, that are very close to the reference case (red). On the other hand, a much faster transient ensues if we increase the donor-like state density by the same factor (green curves). This result hints that TAT is the dominant hole generation mechanism rather than BBT, as the latter is not affected by the trap density. This is also confirmed by the results (not shown) obtained from a lower donor-like state density: in this case, hole generation by TAT is reduced, and phase ① persists up to longer times.

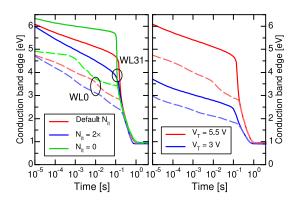

The impact of the interface trap density is instead investigated in Fig. 8 (left), where the nominal case (red curves,  $N_{\rm it} = 3 \times 12 \ {\rm cm}^{-2} \ {\rm eV}^{-1}$  for both acceptor-like and donorlike states) is compared against a double-density (blue curves) and a zero-density case (green curves), always retaining  $V_T =$ 5.5 V. Results show that interface traps play a major role in phase ①, changing the slope of the CB energy loss: higher trap density means more emitted electrons and faster CB drop. When the interface trap density is zero, the limiting case in which only emission from bulk polysilicon matters is reached (green curves). Note that hole generation is not affected by changes in the interface state density: donor-like states are only defined in the lower half of the energy gap and only come into play at long times, when holes generation by tunneling is already very strong. This is why parts (2) and (3) are barely affected by changes in  $N_{\rm it}$ . It should also be noted that all

Fig. 8. Similar to Fig. 6, but showing (left) the dependence on oxide trap density: red = nominal case, blue = trap density =  $2 \times$ , and green = trap density = 0. Right: dependence on cell  $V_T$ . Red = nominal case ( $V_T = 5.5$  V). Blue =  $V_T = 3$  V.

Fig. 9. Similar to Fig. 2 but for a random  $V_T$  pattern.

capture/emission processes (including TAT) are proportional to the trap cross sections. Therefore, such values play an important role in the transient, slowing the dynamics when they are reduced.

The right-hand side of Fig. 8 shows instead the dependence on the stored charge in the nitride, i.e., the programed  $V_T$ . When  $V_T = 3$  V is considered (blue curves), a level lower than the reference  $V_T = 5.5$  V (red curves), the CB receives less boosting, but the slope of phase ① is the same, as this phase is controlled by electron emission. Moreover, the programming charge in the nitride affects the modulation of the energy bands, i.e., the energy barriers in Fig. 5, that are now lowered from about 180 to 130 meV at the beginning of the transient. However, the effect on the transient duration is not strong, for two reasons: first, the final phase ③ is not affected by the barriers; second, barrier lowering, speeding up the hole transient, is balanced by a smaller injection due to the lower field.

Finally, Fig. 9 shows the same results as Fig. 2, but for a random  $V_T$  pattern. Note that the string behavior is similar, with the same processes involved, and the previous explanation still holds.

#### **III. ARCHITECTURE DEPENDENCE**

The previous section has shown that the different parameters can affect the quantitative duration of the transient, but do not change the general behavior of the string. It is, therefore, of interest to investigate the architectural dependence. In fact, the NAND technology evolution has long led to strings made

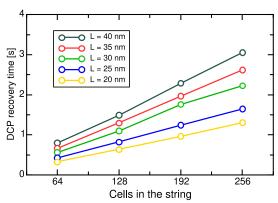

Fig. 10. DCP recovery time as a function of the number of cells in the string and for different values of the cell length.

up by much more than 64 cells. Moreover, scaling in the cell length and silicon thickness has been pursued in order to increase performance. Fig. 10 shows the DCP recovery time  $t_r$  (defined as the time needed for the CB of the center cell to reach the final value within 10%) as a function of the number *n* of cells in the string and cell length  $h_{WL}$  (equal to the selector gate length and intercell distance). Results show a linear dependence on n:  $t_r$  doubles as n doubles. However, this does not mean that  $t_r$  is controlled by charge propagation through the string: in fact, propagation phenomena are important up to phase (2), but not in the final stage ③, where a uniform evolution of the string takes place. The proposed interpretation is the following: as holes are mainly generated at the cell edges, the same generation rate exists for different n values: however, the total amount of charge that is needed to bring the string capacitor to zero increases linearly with the string length, hence n, resulting in a linear dependence. The dependence on  $h_{\rm WL}$  goes by the same explanation, with the addition of a higher initial generation rate in shorter strings, due to the different electric field profiles. Such higher rate determines a much shorter phase (1), but not necessarily a much shorter  $t_r$ : as the CB drops, the electric field is lowered, and the generation rate also decreases, leading to a converging behavior: as a reference,  $t_r$  is reduced by a factor of about 2.3 when going from 40 to 20 nm.

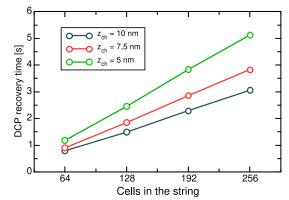

The abovementioned interpretation is supported by results on NAND strings with different poly-Si channel thicknesses  $z_{ch}$ , reported in Fig. 11. Note that the propagation time is not affected by  $z_{ch}$ , but the DCP recovery time increases for thinner channels. The reason for this is that the hole current is (roughly) proportional to the channel thickness, while the total string capacitance is only slightly affected by this parameter, resulting in an increase by a factor of about 1.67 when  $z_{ch}$  is reduced from 10 to 5 nm.

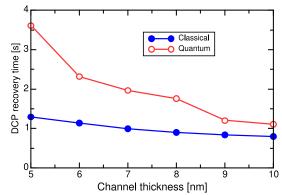

Finally, we have investigated the effects of charge quantization, in view of the values adopted for  $z_{ch}$  in the last analysis. Fig. 12 shows the recovery time as a function of the silicon channel thickness, for the case of classical and quantum solution, the latter obtained via the density gradient approach [38]. Note that quantization pushes charge away from the interfaces, resulting in an equivalent "thinning" of the channel and a smaller current. Note also that no modification to the capture/emission rate formulas has been considered

Fig. 11. DCP recovery time as a function of the number of cells in the string and for different values of the channel thickness.

Fig. 12. DCP recovery time as a function of the channel thickness according to classical and quantum models.

here as a result of quantization. This looks reasonable in the investigated range, where the lowest occupied energy level is about 15 meV above the CB for  $z_{ch} = 5$  nm, but deserves further investigation.

## IV. CONCLUSION

We have investigated the time dynamics of the DCP in 3-D NAND strings. Our analysis shows that the string transient is controlled by different physical processes, namely, BBT and TAT, electron and hole capture/emission from traps, and propagation along the string. The dependence of the transient on the physical parameters is analyzed, highlighting the role played over different timescales. The recovery time dependence on architectural parameters is then studied, showing a linear dependence on the string length and an increase for ultrathin silicon channels, enhanced by the inclusion of quantum effects. The results provide useful indications to support the design of future 3-D NAND arrays with improved immunity to the DCP.

## REFERENCES

- A. L. Lacaita, A. S. Spinelli, and C. M. Compagnoni, "High-density solid-state storage: A long path to success," in *Proc. IEEE Latin Amer. Electron Devices Conf. (LAEDC)*, Apr. 2021, pp. 1–4, doi: 10.1109/LAEDC51812.2021.9437865.

- [2] J.-W. Park et al., "A 176-stacked 512 Gb 3b/cell 3D-NAND flash with 10.8 Gb/mm<sup>2</sup> density with a peripheral circuit under cell array architecture," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2021, pp. 422–423, doi: 10.1109/ISSCC42613.2021.9365809.

- [3] A. Khakifirooz et al., "A 1Tb 4b/cell 144-tier floating-gate 3D-NAND flash memory with 40 MB/s program throughput and 13.8Gb/mm<sup>2</sup> bit density," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2021, pp. 424–425, doi: 10.1109/ISSCC42613.2021.9365777.

- [4] T. Ghilardi, "3D-NAND cell challenges to enable high density and high-performance devices," in *Proc. 5th IEEE Electron Devices Technol. Manuf. Conf. (EDTM)*, Apr. 2021, pp. 1–3, doi: 10.1109/EDTM50988.2021.9420872.

- [5] A. S. Spinelli, C. M. Compagnoni, and A. L. Lacaita, "Reliability of NAND flash memories: Planar cells and emerging issues in 3D devices," *Computers*, vol. 6, no. 2, p. 16, 2017, doi: 10.3390/computers 6020016.

- [6] W.-J. Tsai et al., "Polycrystalline-silicon channel trap induced transient read instability in a 3D NAND flash cell string," in *IEDM Tech. Dig.*, 2016, pp. 11.3.1–11.3.4, doi: 10.1109/IEDM.2016.7838395.

- [7] H. Oh, J. Kim, R.-H. Baek, and J.-S. Lee, "Threshold voltage variation depending on single grain boundary and stored charges in an adjacent cell for vertical silicon-oxide-nitride-oxide-silicon NAND flash memory," *Jap. J. Appl. Phys.*, vol. 57, no. 4, 2018, Art. no. 04FE17, doi: 10.7567/JJAP.57.04FE17.

- [8] S.-H. Lee et al., "Investigation of transient current characteristics with scaling-down poly-Si body thickness and grain size of 3D NAND flash memory," *Solid-State Electron.*, vol. 152, pp. 41–45, Feb. 2019, doi: 10.1016/j.sse.2018.11.009.

- [9] A. S. Spinelli, G. Malavena, A. L. Lacaita, and C. M. Compagnoni, "Random telegraph noise in 3D NAND flash memories," *Micromachines*, vol. 12, no. 6, p. 703, Jun. 2021, doi: 10.3390/mi12060703.

- [10] Y.-L. Chou et al., "Investigation of Vth distribution tails of groundselect-line cells and edge dummy cells in a 3-D NAND flash memory," *IEEE Trans. Electron Devices*, vol. 68, no. 5, pp. 2260–2262, May 2021, doi: 10.1109/TED.2021.3063215.

- [11] H. Jo, S. Ahn, and H. Shin, "Investigation and modeling of Zinterference in poly-Si channel-based 3-D NAND flash memories," *IEEE Trans. Electron Devices*, vol. 69, no. 2, pp. 543–548, Feb. 2022, doi: 10.1109/TED.2021.3137094.

- [12] Y. Kim and M. Kang, "Down-coupling phenomenon of floating channel in 3D NAND flash memory," *IEEE Electron Device Lett.*, vol. 37, no. 12, pp. 1566–1569, Dec. 2016, doi: 10.1109/LED.2016.2619903.

- [13] Y. S. Jeong et al., "Analysis of natural local self-boosting effect due to down-coupling phenomenon in 3D NAND flash memory," in *Proc. Extended Abstr. Int. Conf. Solid State Devices Mater.*, Sep. 2018, pp. 291–292.

- [14] A. Goda, "3D NAND technology achievements and future scaling perspectives," *IEEE Trans. Electron Devices*, vol. 67, no. 4, pp. 1373–1381, Apr. 2020, doi: 10.1109/TED.2020.2968079.

- [15] K. Parat and A. Goda, "Scaling trends in NAND flash," in *IEDM Tech. Dig.*, Dec. 2018, pp. 27–30, doi: 10.1109/IEDM.2018.8614694.

- [16] Y. Fukuzumi et al., "Optimal integration and characteristics of vertical array devices for ultra-high density, bit-cost scalable flash memory," in *IEDM Tech. Dig.*, 2007, pp. 449–452, doi: 10.1109/IEDM.2007.4418970.

- [17] G. Malavena, A. L. Lacaita, A. S. Spinelli, and C. M. Compagnoni, "Investigation and compact modeling of the time dynamics of the GIDLassisted increase of the string potential in 3-D NAND flash arrays," *IEEE Trans. Electron Devices*, vol. 65, no. 7, pp. 2804–2811, Jul. 2018, doi: 10.1109/TED.2018.2831902.

- [18] G. Malavena, A. Mannara, A. L. Lacaita, A. S. Spinelli, and C. M. Compagnoni, "Compact modeling of GIDL-assisted erase in 3-D NAND flash strings," *J. Comput. Electron.*, vol. 18, no. 2, pp. 561–568, Jun. 2019, doi: 10.1007/s10825-019-01328-0.

- [19] TCAD Sentaurus Device V. T-2022.03, Synopsys, Mountain View, CA, USA, 2022.

- [20] C. M. Compagnoni, A. Goda, A. S. Spinelli, P. Feeley, A. L. Lacaita, and A. Visconti, "Reviewing the evolution of the NAND flash technology," *Proc. IEEE*, vol. 105, no. 9, pp. 1609–1633, Sep. 2017, doi: 10.1109/JPROC.2017.2665781.

- [21] C. M. Compagnoni and A. S. Spinelli, "Reliability of NAND flash arrays: A review of what the 2-D-to-3-D transition meant," *IEEE Trans. Electron Devices*, vol. 66, no. 11, pp. 4504–4516, Nov. 2019, doi: 10.1109/TED.2019.2917785.

- [22] G. Fortunato and P. Migliorato, "Model for the above-threshold characteristics and threshold voltage in polycrystalline silicon transistors," *J. Appl. Phys.*, vol. 68, no. 5, pp. 2463–2467, Sep. 1990, doi: 10.1063/1.346507.

- [23] G. Fortunato and P. Migliorato, "Determination of gap state density in polycrystalline silicon by field-effect conductance," *Appl. Phys. Lett.*, vol. 49, no. 16, pp. 1025–1027, Oct. 1986, doi: 10.1063/ 1.97460.

- [24] M. Hack, J. G. Shaw, P. G. LeComber, and M. Willums, "Numerical simulations of amorphous and polycrystalline silicon thin-film transistors," *Jpn. J. Appl. Phys.*, vol. 29, pp. 2360–2362, Dec. 1990, doi: 10.1143/JJAP.29.L2360.

- [25] M. D. Jacunski, M. S. Shur, and M. Hack, "Threshold voltage, field effect mobility, and gate-to-channel capacitance in polysilicon TFTs," *IEEE Trans. Electron Devices*, vol. 43, no. 9, pp. 1433–1440, Sep. 1996, doi: 10.1109/16.535329.

- [26] L. Colalongo, M. Valdinoci, G. Baccarani, P. Migliorato, G. Tallarida, and C. Reita, "Numerical analysis of poly-TFTs under off conditions," *Solid. State Electron.*, vol. 41, no. 4, pp. 627–633, Apr. 1997, doi: 10.1016/S0038-1101(96)00201-8.

- [27] M. Valdinoci et al., "Analysis of electrical characteristics of polycrystalline silicon thin-film transistors under static and dynamic conditions," *Solid-State Electron.*, vol. 41, no. 9, pp. 1363–1369, 1997, doi: 10.1016/S0038-1101(97)00130-5.

- [28] C. T. Angelis, C. A. Dimitriadis, J. Brini, G. Kamarinos, V. K. Gueorguiev, and T. E. Ivanov, "Low-frequency noise spectroscopy of polycrystalline silicon thin-film transistors," *IEEE Trans. Electron Devices*, vol. 46, no. 5, pp. 968–974, May 1999, doi: 10.1109/16.760405.

- [29] T.-K.-A. Chou and J. Kanicki, "Two-dimensional numerical simulation of solid-phase-crystallized polysilicon thin-film transistor characteristics," *Jpn. J. Appl. Phys.*, vol. 38, pp. 2251–2255, Apr. 1999, doi: 10.1143/jjap.38.2251.

- [30] T. Chow and M. Wong, "An analytical model for the transfer characteristics of a polycrystalline silicon thin-film transistor with a double exponential grain-boundary trap-state energy dispersion," *IEEE Electron Device Lett.*, vol. 30, no. 10, pp. 1072–1074, Oct. 2009, doi: 10.1109/LED.2009.2029352.

- [31] T. Gao, M. Wang, H. Wang, and D. Zhang, "TCAD analysis of the four-terminal poly-Si TFTs on suppression mechanisms of the DC and AC hot-carrier degradation," *IEEE J. Electron Devices Soc.*, vol. 7, pp. 606–612, 2019, doi: 10.1109/JEDS.2019.2916619.

- [32] D. Resnati et al., "Characterization and modeling of temperature effects in 3-D NAND flash arrays—Part I: Polysilicon-induced variability," *IEEE Trans. Electron Devices*, vol. 65, no. 8, pp. 3199–3206, Aug. 2018, doi: 10.1109/TED.2018.2838524.

- [33] N. A. Hastas, D. H. Tassis, C. A. Dimitriadis, and G. Kamarinos, "Determination of interface and bulk traps in the subthreshold region of polycrystalline silicon thin-film transistors," *IEEE Trans. Electron Devices*, vol. 50, no. 9, pp. 1991–1994, Sep. 2003, doi: 10.1109/TED.2003.815372.

- [34] P. Gaucci et al., "Role of field enhanced mechanisms and impact ionization on the threshold voltage of short channel polycrystalline silicon thin film transistors," *J. Appl. Phys.*, vol. 93, Oct. 2008, Art. no. 193512, doi: 10.1063/1.3027478.

- [35] N. Righetti and G. Puzzilli, "2D vs 3D NAND technology: Reliability benchmark," in *Proc. IEEE Int. Integr. Rel. Workshop (IIRW)*, Oct. 2017, pp. 51–56, doi: 10.1109/IIRW.2017.8361235.

- [36] G. M. Paolucci, C. M. Compagnoni, C. Miccoli, A. S. Spinelli, A. L. Lacaita, and A. Visconti, "Revisiting charge trapping/detrapping in flash memories from a discrete and statistical standpoint— Part I: V<sub>T</sub> instabilities," *IEEE Trans. Electron Devices*, vol. 61, no. 8, pp. 2802–2810, Aug. 2014, doi: 10.1109/TED.2014. 2327661.

- [37] G. M. Paolucci, C. M. Compagnoni, C. Miccoli, A. S. Spinelli, A. L. Lacaita, and A. Visconti, "Revisiting charge trapping/detrapping in flash memories from a discrete and statistical standpoint—Part II: On-field operation and distributed-cycling effects," *IEEE Trans. Electron Devices*, vol. 61, no. 8, pp. 2811–2819, Aug. 2014, doi: 10.1109/TED.2014.2327149.

- [38] M. G. Ancona and G. J. Iafrate, "Quantum correction to the equation of state of an electron gas in a semiconductor," *Phys. Rev. B*, *Condens. Matter*, vol. 39, no. 13, pp. 9536–9540, 1989, doi: 10.1103/ PhysRevB.39.9536.

Open Access funding provided by 'Politecnico di Milano' within the CRUI CARE Agreement