Received 7 December 2022, accepted 25 December 2022, date of publication 3 January 2023, date of current version 6 January 2023. Digital Object Identifier 10.1109/ACCESS.2022.3233812

# **RESEARCH ARTICLE**

# Rule-Based Design for Low-Cost Double-Node Upset Tolerant Self-Recoverable D-Latch

# SEYEDEHSOMAYEH HATEFINASAB<sup>®1</sup>, ALFREDO MEDINA-GARCIA<sup>®2</sup>, DIEGO P. MORALES<sup>®1</sup>, ENCARNACION CASTILLO<sup>®1</sup>, AND NOEL RODRIGUEZ<sup>®1</sup>

**ENCARNACION CASTILLO<sup>D</sup>**<sup>1</sup>, **AND NOEL RODRIGUEZ**<sup>D</sup><sup>1</sup> <sup>1</sup>Department of Electronics and Computer Technology, University of Granada, 18071 Granada, Spain <sup>2</sup>Infineon Technologies AG, 85579 Neubiberg, Germany

Corresponding author: Seyedehsomayeh Hatefinasab (hatefi@correo.ugr.es)

This work was supported in part by the Spanish Department of Science and Innovation financial item MCIN/AEI/10.13039/ 501100011033/FEDER under Grant PID2020-117344RB-I00; and in part by the Regional Government under Grant P20\_00265, Grant P20\_00633, and Grant B-RNM-680-UGR20.

**ABSTRACT** This paper presents a low-cost, self-recoverable, double-node upset tolerant latch aiming at nourishing the lack of these devices in the state of the art, especially featuring self-recoverability while maintaining a low-cost profile. Thus, this D-latch may be useful for high reliability and high-performance safety-critical applications as it can detect and recover faults happening during holding time in harsh radiation environments. The proposed D-latch design is based on a low-cost single event double-node upset tolerant latch and a rule-based double-node upset (DNU) tolerant latch which provides it with the self-recoverability against DNU, but paired with a low transistor count and high performance. Simulation waveforms support the achievements and demonstrate that this new D-latch is fully self-recoverable against double-node upset. In addition, the minimum improvement of the delay-power-area product of the proposed rule-based design for the low-cost DNU tolerant self-recoverable latch (RB-LDNUR) is 59%, compared with the latest DNU self-recoverable latch on the literature.

**INDEX TERMS** Delay-power-area product (DPAP), double node upsets (DNU), high impedance state (HIS), low cost single event double node upset tolerant (LSEDUT), power-delay product (PDP), single node upset (SNU), soft error (SE).

#### I. INTRODUCTION

As CMOS technology is scaled down, the amount of charge needed to disturb the logic state of nodes of electronic circuits is dramatically reduced, primarily due to the low supply voltage and smaller capacitance of transistors. This fact is translated into an increasing vulnerability of the state of digital circuits to glitches formed by particle striking [1]. Therefore, increasing the reliability of integrated circuits for soft error (SE) tolerance or even SE self-recoverability has become a challenge of paramount importance [2].

The particle striking can affect the node state of memory cells, flip flops, and D-latches, which causes SEs. A SE occurring at one specific node is called single node upset (SNU). This phenomenon is responsible for the increasing investment in hardening D-latches against SNU [3], [4], [5].

The associate editor coordinating the review of this manuscript and approving it for publication was Nagarajan Raghavan<sup>(D)</sup>.

Furthermore, the consequence of the nano scaling race, the probability of occurrence of a double node upset (DNU) increases. For example, it is more than twenty-five percent for technologies below the 45nm node [6], which redoubles the need to design D-latches that can handle DNU [7], [8], [9], [10].

One of the approaches to increase the tolerance of D-latches against DNU is to use larger transistors for sensitive nodes, but even under this solution, some nodes can be upset by large charge injection [11]. Other approaches resort to layout technology making use of well isolation or extending the node space and guard ring to help tolerate DNU [7]. Thereby, the design of circuits becomes very complex. Many researchers are motivated to apply radiation hardening by design techniques (RHBD), in which C-elements, inverters, and Dual Interlocked storage Cell (DICE) [1], [12], [13], [14], [15] are used. However, these D-latches cannot recover by themselves and present, at least,

one pair of nodes unable to tolerate DNU [12], [13], [15], [16] or they are not optimized for power consumption or delay [10], [14].

This paper presents a novel and improved low-cost DNU-self-recoverable D-latch to meet the demand for reliable and low-cost circuits for harsh environments. This proposed D-latch is an improvement of the low-cost singleevent double-node upset tolerant (LSEDUT) latch [12] based on the rule design for multiple nodes upset tolerant latch architecture [17], to confer it with self-recoverability. By using a different design approach, such as a clock-gating (CG) technique, this proposed D-latch has a lower transistor count, which results in lower power and area consumption. As there are separate paths for transparent mode and hold-ing time, the delay also is minimum. SEU and DNU fault simulation results will show that this D-latch is not only immune against SEU and DNU, but the whole D-latch is self-recoverable against them.

The paper is structured as follows: section II focuses on reviewing previous self-recoverable DNU and DNU tolerant D-latches. In section III, the characteristics of the proposed D-latch are presented and the immunity against SNU and DNU is tested. In section IV, simulation methodology and comparative studies of robustness, power consumption, delay, area, and delay-power-area-product with previous hardened D-latches are discussed. Finally, the main conclusions derived from this work are summarized in Section V.

# II. STATE OF THE ART: PREVIOUS HARDENED LATCH DESIGNS

In this section, a review of self-recoverable DNU and DNU tolerant D-latches is presented. Previous hardened latch designs such as double-node charge sharing (DNCS) SEU tolerant latch [7], non-temporally hardened latch (NTHLTCH) [10], triple path dual-interlocked storage cell (TPDICE)-based latch [18], LSEDUT latch [12], DNU self-recoverable latch design for high performance and low power application (DNURHL) latch [19], and rule-based DNU tolerant latch (RDTL) [17] are analyzed.

# A. DNCS-SEU TOLERANT LATCH

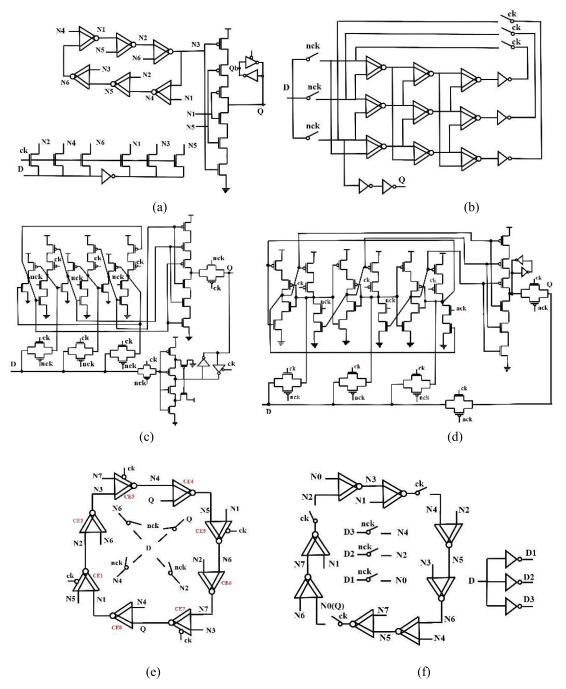

Figure 1(a) shows the structure of the DNCS SEU tolerant D-latch. This D-latch has some immunity constraints originating from the interlock between different nodes, such as N1 and N4. To illustrate this issue, as can be seen in figure 1(a), N1 is the input of one C-element and N4 is the output of this C-element. Also, in the other C-element, N4 node becomes input and N1 is output, which stablishes one feedback path for these two nodes N1 and N4. Therefore, if the pair of nodes <N1, N4> has an upset, it will result in a high impedance in N5 and N2 nodes, and as the 3-input C-element has N1 upset, the output and inverter of output (Qb) will present high impedance. If at the output of the D-latch, a high impedance state (HIS) occurs, it yields that the D-latch does not have the ability to self-recover, and the upset at the latch can stay for the long term. This D-latch can experience upset by DNU

in pairs such as <N2, N5>, <N3, N6>. Furthermore, this circuit is a pseudo-static D-latch and new data are written based on an overcoming process, which makes temporary competition between the driving output and the feedback inside, causing high leakage power consumption. Also, this D-latch presents a high delay from the input to the output node.

# B. NTHLTCH

The structure of NTHLTCH D-latch is displayed in figure 1(b). This D-latch is self-recoverable, but it is not cost effective in terms of silicon area and power consumption due to the use of nine C-elements and five inverters to ensure that it is immune against DNU and able to recover itself against DNU [19].

# C. TPDICE-BASED D-LATCH

TPDICE-based D-latch is a hardened D-latch with immunity against single event transient (SET), SNU, DNU, and HIS insensitivity [18]. As figure 1(c) shows, this structure includes a TPDICE used for keeping the data in holding time, a three input C-element for filtering DNU, an embedded Schmitt trigger inverter for filtering the SET in the transparent path, and a keeper for avoiding HIS in the output node.

#### D. LSEDUT D-LATCH

Figure 1(d) shows the structure of the LSEDUT latch. This DNU tolerant D-latch is based on a TPDICE with full use of its interlocked node character to make it reliable for storing data. It has a keeper to avoid high impedance at the output node and two separate paths for holding time and transparent mode.

#### E. DNURHL LATCH

The DNURHL latch is DNU tolerant, however, due to the feedback architecture used, it is not fully recoverable. As figure 1(e) shows, it has pairs of input of C-elements, which makes improper feedback to the output of these C-elements: if there is any DNU at the input of these C-elements, their outputs will lose their data and it will result in an upset of the D-latch. These pair of input nodes of C-elements are, <N1, N5>, <N2, N6>, <N3, N7>, and <N4, Q>. This originated since node pair <N2, N6> is the input of two C-elements and if it is affected by charge injections, its upset can perturb the rest of the C-elements. A careful analysis shows that if N2 and N6 lose their value, N3 and N7 which are the output of C-elements (CE2) and CE6 will be affected, and their outputs lose their data. Therefore, two C-elements, CE3 and CE7, are affected and they lose their data. The <N1, N5>, <N3, N7>, and <N4, Q> pairs of nodes can experience the same upsets when a particle strikes two nodes of each of these pairs. The feedback of C-elements cannot recover their valid data because of the improper feedback mechanism. Consequently, the D-latch will be upset.

FIGURE 1. Previous hardened latch designs (a) DNCS-SEU tolerant latch, (b) NTHLTCH, (c) TPDICE-based latch, (d) LSEDUT latch, (e) DNURHL latch, (f) RDTL.

# F. RDTL LATCH

The DNURHL D-latch is not self-recoverable since the node pairs of C-element inputs are repeated, and these input pairs suffer from improper feedback to the output nodes of these C-elements. This problem is solved in RDTL (figure 1(f)), which is designed based on rule design so that the pairs of nodes of input C-elements are not repeated, presenting appropriate feedback in loops to become fully self-recoverable against DNU [17]. However, the RDTL, in comparison with the DNURHL latch, has more transmission gates and inverters, which introduces more area and power consumption penalty.

# **III. PROPOSED D-LATCH**

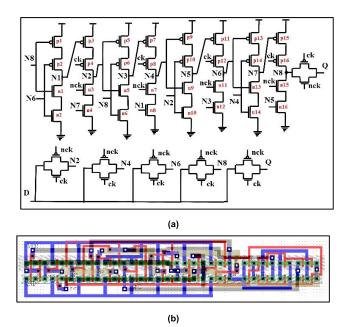

The proposed D-latch is based on the LSEDUT and the RDTL latches, in which the number of transistors, power consumption, and area consumption are reduced. The structure of this latch consists of four 2-input C-elements, four

FIGURE 2. Proposed RB-LDNUR D-latch (a) schematic, (b) layout.

input-split inverters, and six transmission gates. Also, each input of the proposed D-latch is connected to the four transistors, storing the input in more nodes to tolerate DNU and making this proposed D-latch self-recoverable against DNU. D, Q, ck, and nck are the input, output, clock, and inverted clock, respectively. Figure 2(a) shows the schematic of the proposed rule-based design for a low-cost DNU tolerant selfrecoverable latch (referred to as RB-LDNUR) and figure 2(b) shows the layout of the proposed D-latch. When ck = 1, the latch is in transparent mode and the input is connected to N2, N4, N6, N8, and Q. After the propagation of D input from 2-input C-elements, N1, N3, N5, and N7 are defined. The output is driven by D, and N8 is not connected to the output directly targeting the reduction of the (D-Q) delay since N8 introduces more delay in the latch because it is connected to four gates of transistors (which introduces large capacitance in this node).

When ck = 0, the latch is in hold mode, N2, N4, N6, N8, and Q are disconnected from D, and Q is driven by N8. The interlocked feedback of the RB-LDNUR is active to retain robustly the data. These feedbacks are activated just during holding mode to save power.

The proposed D-latch structure is optimized in comparison with the DNURHL latch. Since the DNURHL latch consists of clock-gating 3-input C-elements, which are not applied in the proposed D-latch (the proposed design features 2-input C-elements), which optimizes area, power consumption, and transistor count. On the other hand, the RDTL latch has extra transmission gates and inverters in the feedback loop in comparison with the proposed D-latch, which reduces the transistor count of the new solution. In consequence, the power consumption and silicon area are also reduced. By applying the structure of the LSEDUT with the rule design of the RDTL, the proposed latch has larger interlocked

VOLUME 11, 2023

feedback in holding time. By combining these two structures, the proposed D-latch is self-recoverable against DNU with fewer transistors. Also, in this structure, one transmission gate between Q and N8 is used for reducing the delay.

Following the rule design in [17], the proposed D-latch is immune against DNU, therefore, n = 2, and d = 2(n-1), where n is the number of nodes upset simultaneously in the D-latch, and d is the number of elements between Ni and Nj. To configure the proposed D-latch, assuming the Ni is the first node to one element, Nj is the second node, and  $i = (j-d-1) \mod (4d)$ . Therefore the pair of nodes entering different elements are as follows: <N1, N7>, <N2, N8>, <N3, N1>, <N4, N2>, <N5, N3>, <N6, N4>, <N7, N5>, <N8, N6>.

For evaluating the immunity against SNU, there are nine nodes and each of them can be affected by SNU. If N1 is affected by an SNU, a glitch will occur; in the case of D =0, N2 = 0, and N1 = N7 = 1 (p3 off and n8 ON), if the SNU occurs in N1, the value of N1 = 0 (p3 ON and n8 off), which makes N2 and N4 becomes unstable, but as N8 and N6 are not affected by SNU, N1 can be recovered by N8 and N6, then consequently, N2 and N4 can be stabilized by N1, which means N1 is self-recovered against SNU. This analysis can be applied to the whole of other nodes, which proves this latch is immune and self-recoverable against SNU.

For immunity against DNU, there are nine nodes in holding time making  $C_2^9 = 36$  cases of node pairs. In the following, the different cases of DNU are evaluated based on the design of the hardened D-latch, but this DNU is independent of where the charge is injected into the D-latch. As the structure is symmetric, there are five cases to study: (1) <N1, N2>, <N2, N3>, <N3, N4>, <N4, N5>, <N5, N6>, <N6, N7>, <N7, N8>, <N8, N1>; (2) <N1, N3>, <N2, N4>, <N4, N5>, <N5, N6>, <N6, N7>, <N7, N8>, <N8, N1>; (2) <N1, N3>, <N2, N4>, <N3, N5>, <N4, N6>, <N5, N7>, <N6, N8>, <N7, N1>, <N8, N2>; (3) <N1, N4>, <N2, N5>, <N3, N6>, <N4, N7>, <N5, N8>, <N6, N1>, <N7, N2>, <N8, N3>; (4) <N1, N5>, <N2, N6>, <N3, N7>, <N4, N8>; (5) <N1, Q>, <N2, Q>, <N3, Q>, <N4, Q>, <N5, Q>, <N6, Q>, <N7, Q>, <N8, Q>.

Case 1:  $\langle N1, N2 \rangle$  is affected by a DNU and perturbed by charge injection. As example D = N2 = 0 and N1 = 1; p3, n5, and n10 are off and n8, p5, and p10 are ON. If upset happens, N1 = 0 and N2 = 1, n8, p5, and p10 are off and p3, n5, and n10 are ON. But, N3 does not lose its value because N8 has valid data. As N8 and N6 have valid data, they can recover N1. Then, by recovering N1, p3 becomes off and N7 has valid data and can recover N2, which means  $\langle N1, N2 \rangle$  is immune and self-recoverable against DNU. Other pairs of this case can be analyzed similarly. As the result, the proposed RB-LDNUR D-latch is DNU-immune and self-recoverable in case 1.

Case 2: in this case, <N1, N3> is evaluated. Since N1 and N3 lose their value, there are weak instabilities in N2 and N4. But, as N6 and N8 have valid data, N1 can be recovered, and then N2 will be stable. The stability of N2 can help N3 to be recovered and N4 becomes stable. This explanation shows <N1, N3> is self-recoverable and immune against DNU.

For other pair groups, the analysis against DNU is similar, thus they can be self-recover against DNU and this proposed D-latch is self-recoverable against DNU in case 2.

Case 3: in this case where  $\langle N1, N4 \rangle$  is affected by DNU, an upset happens. For example, D = N2 = 0, and N1 = 1; p3, n14, and n9 are off and n8, p9, and p14 are ON. If there are charges injected to N1 and N4, then N1 = 0 and N4 = 1, therefore, n8, p9, and p14 are off and p3, n14, and n9 are ON. N2 becomes weakly unstable. But, N5 does not lose its value. As N8 and N6 have a valid value, N1 can be recovered by N6, and N8 and N2 can be stable. Also, N4 can be recovered by N3 and N1. This explanation demonstrates  $\langle N1,$ N4 $\rangle$  is immune and self-recoverable against DNU. Other pairs of nodes can be analyzed similarly, thus they are also self-recoverable and DNU-immune. Therefore, this proposed RB-LDNUR D-latch can be self-recover from DNU in case 3.

Case 4: in this situation,  $\langle N1, N5 \rangle$  is affected by DNU. For this case, D = N2 = 0, and N1 = N5 = 1, p11, and p3 are off; n8 and n16 are ON. If N1 and N5 are affected by DNU, N1 = N5 = 0, p11 and p3 are ON; n8 and n16 are off. Then, N2 and N6 can be weakly unstable. But, N1 and N5 can be recovered by N8 and N4, respectively. Therefore, N2 and N6 become stable and the D-latch can become selfrecoverable against DNU. Other pair groups recover themselves in the same way as  $\langle N1, N5 \rangle$ . Consequently, the proposed RB-LDNUR D-latch is self-recoverable in case 4.

Case 5: in this situation  $\langle N1, Q \rangle$  is affected by DNU. As among nodes N1 to N8, just N1 is affected by DNU, this case is similar to SNU in nodes N1 to N8 because Q is not feedback to any other part of the RB-LDNUR latch. When N1 is affected by DNU, N2 and N4 become unstable, but N6 and N8 have valid data and N1 can be recovered by them. Then, N2 and N4 become stable. Also, Q can be recovered by N8. This analysis is valid for other pairs of nodes in this group. As the result, the proposed RB-LDNUR D-latch is immune and self-recoverable against DNU in case 5.

When D = 1, the performance of the proposed RB-LDNUR D-latch is similar to the case when the input data is D = 0. This structure is immune and self-recoverable against DNU. Therefore, the proposed RB-LDNUR D-latch is DNU-self-recoverable for all these key node pairs.

# **IV. SIMULATION RESULTS**

The proposed RB-LDNUR D-latch, DICE [20], DNCS SEU tolerant latch [7], DNUCT [21], NTHLTCH [10], TPDICE-based latch [17], LSEDUT latch [12], DNURHL [19], RDTL [17], RH-latch [22], FPADRL [23], LOCDNU-TRL [24], HTNURE [25], LOCTNUTRL [24] are simulated at 0.8 V at room temperature using Synopsys<sup>®</sup> HSPICE in 22nm CMOS technology from PTM library [26]. For a fair comparison, PMOS transistors have an aspect ratio of W/L = 35 nm/22 nm, and NMOS transistors have an aspect ratio of W/L = 24 nm/22 nm.

In the error injection test, the proposed RB-LDNUR D-latch is evaluated against SNU and DNU by a current transient (current source) simulating the charge injection given

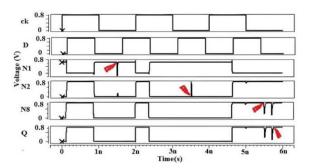

FIGURE 3. Simulation results of SNU injections to key single nodes of the proposed RB-LDNUR D-latch.

by the following mathematical expression [27]:

$$I = \frac{Q_{total}}{T\sqrt{\pi}} \sqrt{\frac{t}{T}} e^{-t} T$$

(1)

where, T is the value of the time constant of the injected current charge, which is 0.1 ps and  $Q_{total}$  is the total charge injected being 20 fC in this test, which is large enough to prove immunity of the proposed RB-LDNUR D-latch against SNU/DNU [4].

The simulation results show that the operation of the proposed D-latch is similar to that of the traditional D-latch. Thus, in the transparent mode, the input is equal to the output, and in the holding mode, the output is equal to the input at the moment the clock becomes low level, as can be seen in figure 3.

For SNU simulation, to prove the self-recoverability of the proposed RB-LDNUR D-latch, one charge is injected into different nodes, such as internal nodes or Q. When the output and internal nodes do not lose their logical value after injections, which means they are self-recoverable against SNU.

As can be seen in figure 3, the key single nodes N1, N2, N8, and Q are injected by SNU, respectively. These key nodes are based on the different situations of SNU at the proposed RB-LDNUR latch, which analysis is mentioned above. The simulation results show that the output and other internal nodes do not lose their values after SNUs, which proves that the proposed RB-LDNUR D-latch is self-recoverable against SNU.

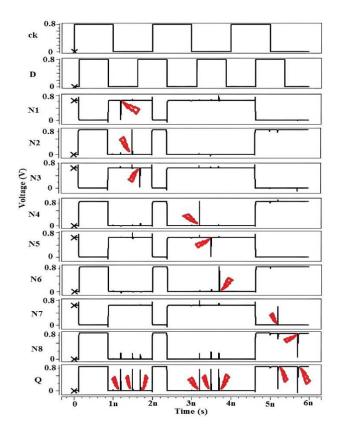

Based on different pairs of nodes in the DNU immunity of the proposed RB-LDNUR D-latch, the following tests are considered. Table 1 shows the key patterns of DNUs used for the charge injections in figure 4. As can be seen in this figure, different key pattern injections of DNU do not change the logical value of the internal nodes and output node, which means that the proposed RB-LDNUR D-latch is immune and self-recoverable against DNU. This table shows the precise time at which two charge injections are introduced at two different nodes. If after these injections the values of the nodes do not change, it means that they are self-recoverable against these DNUs. Moreover, the output node has to maintain its value during these injections and as can be seen in figure 4, the Q value is stable during the whole of these DNUs.

TABLE 1. Key pattern of DNU injections of the proposed RB-LDNUR latch in figure 4.

| Time<br>(ns)             | SNUs/DNUs                            | State                                 |  |

|--------------------------|--------------------------------------|---------------------------------------|--|

| 1.2<br>1.8<br>3.2<br>3.8 | N1, N2<br>N1, N3<br>N1, N4<br>N1, N5 | Q = 0 $Q = 0$ $Q = 0$ $Q = 0$ $Q = 0$ |  |

| 5.8                      | N1, Q                                | Q =1                                  |  |

FIGURE 4. Simulation results of key patterns of DNU injections for the proposed RB-LDNUR latch.

Figure 5 shows the simulation waveforms for the proposed RB-LDNUR latch based on the pairs of nodes in table 2. These pairs of nodes are different internal nodes and the output node, Q. The results show that in all of the pairs of nodes, the proposed RB-LDNUR latch and all internal nodes can be self-recoverable from the DNU. Therefore, the output node is self-recoverable from every DNU at the proposed RB-LDNUR latch. For example at 1.2 ns in figure 5, the DNU injection occurs at N1 and Q nodes, when Q = 0, as can be seen for this DNU test, the values of Q and N1 nodes are the same as before the injections.

In summary, the above explanation and simulation results demonstrate the reliability of the proposed RB-LDNUR latch against SNU/DNU injections and its self-recoverability.

In table 3, there is a comparative summary of SNU, DNU immunity, HIS insensitivity, self-recoverability of the proposed RB-LDNUR latch and state-of-the-art SNU, DNU, and triple node upset (TNU) hardened D-latches, such as DICE, DNCS-SEU tolerant, DNUCT, NTHLTCH, TPDICE- based latch, LSEDUT, DNURHL, RDTL, RH-latch, FPADRL, LOCDNUTRL, HTNURE, LOCTNUTRL latches. DICE and DNCS-SEU tolerant latches are not fully immune against

# **TABLE 2.** Pattern of DNU injections to pairs with output node (Q) and other nodes of the proposed RB-LDNUR latch.

| Time<br>(ns) | SNUs/DNUs | State |  |

|--------------|-----------|-------|--|

| 1.2          | N1, Q     | Q =0  |  |

| 1.5          | N2, Q     | Q = 0 |  |

| 1.7          | N3, Q     | Q =0  |  |

| 3.2          | N4, Q     | Q =0  |  |

| 3.5          | N5, Q     | Q =0  |  |

| 3.7          | N6, Q     | Q =0  |  |

| 5.2          | N7, Q     | Q =1  |  |

| 5.7          | N8, Q     | Q =1  |  |

FIGURE 5. Simulation results of DNU injections to pairs related to the output node (Q) and other internal nodes of the proposed RB-LDNUR latch.

DNU. For self-recoverability, DICE can recover itself against SNU, but DNCS-SEU cannot recover itself against SNU. NTHLTCH is self-recoverable against DNU and it is fully immune against SNU and DNU, but it is not efficient in terms of cost. DNUCT, LSEDUT, and TPDICE-based latches and RH-latch are fully immune against SNU and DNU, but none of them are self-recoverable against DNU. The DNURHL latch is not fully immune against DNU because of improper feedback between pair nodes of 2-input C-elements and outputs of 2-input C-elements, causing the D-latch cannot recover its valid data when a pair nodes of 2-input C-elements are affected by DNU. The RDTL, FPADRL, and LOCDNUTRL latches are fully immune against SNU and

| D-latch                 | FULL IMMUNE SNU | Full Immune DNU | SELF-<br>RECOVERABILITY | HIS<br>INSENSITIVE |

|-------------------------|-----------------|-----------------|-------------------------|--------------------|

| DICE [20]               | $\checkmark$    | x               | $\checkmark$            | ×                  |

| DNCS-SEU tolerant [7]   | $\checkmark$    | ×               | ×                       | $\checkmark$       |

| DNUCT [21]              | $\checkmark$    | $\checkmark$    | x                       | $\checkmark$       |

| NTHLTCH D-latch [10]    | $\checkmark$    | $\checkmark$    | $\checkmark$            | $\checkmark$       |

| TPDICE-based latch [18] | $\checkmark$    | $\checkmark$    | ×                       | $\checkmark$       |

| LSEDUT latch [12]       | $\checkmark$    | $\checkmark$    | ×                       | $\checkmark$       |

| DNURHL latch [19]       | $\checkmark$    | ×               | ×                       | ×                  |

| RDTL latch [17]         | $\checkmark$    | $\checkmark$    | $\checkmark$            | $\checkmark$       |

| RH-latch [22]           | $\checkmark$    | $\checkmark$    | ×                       | $\checkmark$       |

| FPADRL [23]             | $\checkmark$    | $\checkmark$    | $\checkmark$            | $\checkmark$       |

| LOCDNUTRL [24]          | $\checkmark$    | $\checkmark$    | $\checkmark$            | $\checkmark$       |

| HTNURE[25]              | $\checkmark$    | $\checkmark$    | $\checkmark$            | $\checkmark$       |

| LOCTNUTRL [24]          | $\checkmark$    | $\checkmark$    | $\checkmark$            | $\checkmark$       |

| Proposed RB-LDNUR latch | $\checkmark$    | $\checkmark$    | $\checkmark$            | $\checkmark$       |

DNU and can be self-recoverable, but it is not optimized for low-cost effectiveness. Also, HTNURE and LOCTNUTRL are TNU tolerant latches and self-recoverable against DNU, but still, they are not cost-efficient. Considering the proposed RB-LDNUR latch and applying the rule design of the RDTL latch and the structure of the LSEDUT latch, this new design is fully immune against SNU/DNU, can be self-recoverable, while maintaining a low-cost architecture. Moreover, as the proposed RB-LDNUR latch is HIS insensitive, it does not feature any driving ability during holding time.

Aiming at a quantitative comparison, the proposed RB-LDNUR latch and the mentioned hardened D-latches are simulated using the same PMOS and NMOS aspect ratios (transistors size), room temperature with 250 MHz input frequency at 0.8 V power supply in the 22nm CMOS technology. In the following simulation, a comparison of D-latch features related to area consumption, (D-Q) delay, average power consumption, PDP (power-delay product), transistors count, and DPAP (delay-power-area product) is presented. DPAP can be calculated by multiplying delay, power consumption, and area. Area consumption can be calculated by silicon footprint extracted from the layout of the proposed RB-LDNUR latch and the mentioned hardened D-latches using L-EDIT Tanner software.

Table 4 presents the improvement percentage of proposed D-latch DPAP in comparison with all other mentioned D-latch alternatives, which is increased dramatically. The minimum percentage of improvement of DPAP of the proposed D-latch is 59% in comparison with DPAP of the best alternative (FPADRL D-latch) and the average improvement is 86.1%.

As shown in table 5, the lowest power consumption, area, delay, PDP, and DPAP are featured by the proposed RB-LDNUR D-latch in comparison with previous mentioned DNU/TNU tolerant D-latches. DICE and DNCS-SEU tolerant D-latches have the least number of transistors followed

TABLE 4.

Percentage improvement of DPAP proposed D-latch in comparison with other D-latches.

| nprovement |

|------------|

| 98.3%      |

| 98.3%      |

| 76%        |

| 96%        |

| 99.1%      |

| 94%        |

| 62%        |

| 93%        |

| 64%        |

| 59%        |

| 97%        |

| 88%        |

| 95%        |

|            |

by the proposed D-latch, however, they are not fully immune against DNU and the DNCS-SEU latch is not self-recoverable against SNU. Also, the area consumption in table 5, besides depending on the number of transistors, depends on the complexity of the layout of the D-latches. Because of that, even FPADRL has two transistors less than the proposed RB-LDNUR D-latch, but it does not feature lower area consumption in comparison to the proposed RB-LDNUR D-latch. Moreover, FPADRL in comparison with the proposed RB-LDNUR D-latch presents a higher power consumption because of its structure.

In the design of the proposed RB-LDNUR D-latch, the minimum (D-Q) delay is achieved by using a transmission gate between N8 and Q. Since the capacitor of N8 is large due to the four gates of transistors connected to this node. By separating the output node (Q) and N8, the delay is reduced considerably. By applying the LSEDUT latch structure, the

#### TABLE 5. Properties comparative features of D-latches.

| Features                   | Power<br>(µW) | DELAY<br>(ps) | AREA $(\mu m^2)$ | $\begin{array}{c} \text{PDP} \\ (10^{-18} \times W) \end{array}$ | TRANSISTOR<br>COUNT | DPAP  | $Q_{crit}(fc)$ |

|----------------------------|---------------|---------------|------------------|------------------------------------------------------------------|---------------------|-------|----------------|

| DICE [20]*                 | 0.74          | 18.20         | 0.90             | 13.40                                                            | 18                  | 12.10 | 1              |

| DNCS-SEU tolerant [7]*     | 0.37          | 19.70         | 1.66             | 7.28                                                             | 32                  | 12.10 | 10             |

| DNUCT [21]                 | 0.53          | 0.56          | 3.10             | 0.28                                                             | 70                  | 0.87  | 5              |

| NTHLTCH D-latch [10]       | 0.42          | 4.88          | 2.53             | 2.04                                                             | 58                  | 5.18  | 8              |

| TPDICE-based latch [18]    | 1.01          | 11.80         | 2.12             | 11.97                                                            | 46                  | 25.20 | 10             |

| LSEDUT latch [12]          | 3.00          | 0.56          | 2.09             | 1.70                                                             | 44                  | 3.51  | 6              |

| DNURHL latch [19]          | 0.26          | 1.14          | 1.85             | 0.30                                                             | 48                  | 0.55  | 8              |

| RDTL latch [17]            | 0.35          | 4.28          | 1.99             | 1.48                                                             | 50                  | 2.98  | 8              |

| RH-latch [22]              | 0.53          | 0.56          | 1.99             | 0.29                                                             | 36                  | 0.58  | 5              |

| FPADRL [23]                | 0.62          | 0.56          | 2.64             | 0.32                                                             | 42                  | 0.84  | 3              |

| LOCDNUTRL [24]             | 3.16          | 0.95          | 2.24             | 3.01                                                             | 44                  | 6.74  | 2              |

| HTNURE [25]                | 0.39          | 1.15          | 3.82             | 0.45                                                             | 72                  | 1.72  | 8              |

| LOCTNUTRL [24]             | 3.75          | 0.56          | 2.48             | 1.96                                                             | 50                  | 4.86  | 2              |

| Proposed RB-LDNUR<br>latch | 0.24          | 0.56          | 1.57             | 0.14                                                             | 44                  | 0.21  | 8              |

\*Not DNU tolerant

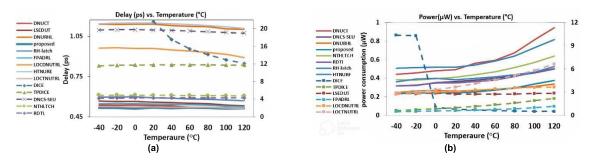

FIGURE 6. Impacts of temperature variation on: (a) Delay (b) Power consumption.

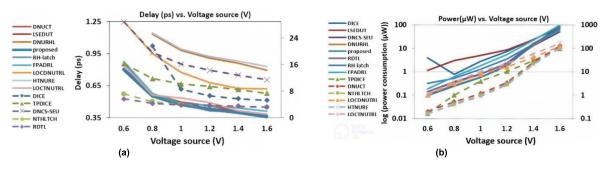

FIGURE 7. Impacts of supply voltage variation on: (a) Delay (b) Power consumption.

number of transistors, power consumption, and area are reduced in comparison with DNURHL and RDTL structures containing 2-input C-elements and the clock gating 3-input C-elements. The minimum improvement of power consumption of the proposed latch is 7.7% in comparison with the best alternative (DNURHL latch); the minimum improvement of silicon area is 5.4% as compared with the best alternative (DNCS-SEU tolerant latch), except for DICE, and the minimum improvement of PDP is 50% in comparison with the best alternative (DNUCT latch). Based on the reliability of the hardened D-latch against charge injections, the minimum charge injections that can produce SNU in different nodes of latches are calculated [28]. Since the purpose of hardening the D-latch is increasing the value of  $Q_{crit}$  to tolerate SE, the

minimum charge injections should be considered. This  $Q_{crit}$  is the minimum charge injection that can flip the value of the most sensitive D-latch nodes. As can be seen in table 5, the minimum charge injection that can change the value of proposed D-latch nodes is infinite, which means the proposed D-latch is full immune.

Process, voltage, and temperature (PVT) variation is considered for latches and flip-flops in nanotechnology [29], [30], [31], [32], [33]. Figure 6 and figure 7 show the temperature and voltage supply variation impact on the delay and power consumption of previous D-latches and the proposed D-latch. For a better comparison, both figure 6 and figure 7 include two different axes. The dashed lines with markers are adjusted by the secondary axes on the right side of the charts whereas the solid lines are adjusted by the axes on the left side of the charts.

In figure 6, for temperatures ranging between  $-40^{\circ}$ C to  $120^{\circ}$ C, the power consumption and D-Q delay are monitored. In figure 6 (a), the delay is not affected by the temperature except for the case of DICE, since most of the mentioned D-latches have one transmission gate from input to output in transparent mode. The proposed D-latch features the minimum delay being its delay-temperature below the ones by its competitors. In figure 6 (b), by increasing the temperature, the carriers' mobility of the transistors decreases [15], which results in increased power consumption of D-latches, except for the DICE case. As can be seen in figure 6, the proposed D-latch is highly immune against the variation of temperature, approximately during the range of  $-40^{\circ}$ C to  $120^{\circ}$ C, it maintains its minimum delay and power consumption.

Figure 7 shows the impact of the variation of supply voltages (0.6 V-1.6 V) on power consumption and delay (D-Q). In figure 7 (a), the delay of D-latches reduces due to the large current driven by the transistors, however, during the range of supply voltages (0.6 V-1.6 V), the proposed D-latch maintains its minimum value delay. Additionally, power consumption rises by increasing the supply voltage. The reason behind this must be sought in the fact that by increasing the supply voltage, dynamic and static power increase (capacitors accumulate more charge and transistors drive more current [15]), as shown in figure 7 (b) in logarithmic scale. This figure shows that by increasing power consumption in the range of the supply voltages (0.6 V-1.6 V), the proposed D-latch maintains its minimum value of power consumption, which is translated into better performance in this range of supply voltage in comparison to its alternatives.

#### **V. CONCLUSION**

Scaling CMOS technology boosts the demand for D-latch reliability. This paper proposes a low-cost, self-recoverable D-latch featuring immunity against SNUs and DNUs. Since most hardened DNU D-latches are not self-recoverable and low-cost, the proposed RB-LDNUR latch is conceived based on different rule designs and structures to achieve these purposes. Simulation results show that the proposed RB-LDNUR latch design is DNU self-recoverable and cost effective in comparison with other recently proposed DNU/TNU self-recoverable latch structures. The minimum improvement of power consumption is 7.7%, in comparison with the best alternative (DNURHL latch); the minimum improvement of silicon area is 5.4% when compared with the best alternative (DNCS-SEU tolerant latch, except for DICE which is not DNU tolerant), the minimum improvement of PDP is 50% in comparison with the DNUCT latch. Finally, the minimum improvement of DPAP of the proposed D-latch in comparison with the FPADRL D-latch is 59% and compared with other mentioned D-latches, the average improvement is approximately 86.1%. Also, the temperature has little effect on the performance of the proposed D-latch and by changing the value of supply voltage, the proposed D-latch keeps its high performance compared with other mentioned previous D-latches.

# **DECLARATION OF COMPETING INTEREST**

The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

#### REFERENCES

- A. Watkins and S. Tragoudas, "Radiation hardened latch designs for double and triple node upsets," *IEEE Trans. Emerg. Topics Comput.*, vol. 8, no. 3, pp. 616–626, Jul. 2020, doi: 10.1109/TETC.2017.2776285.

- [2] S. N. P. K. Anjan and M. S. Baghini, "Robust soft error tolerant CMOS latch configurations," *IEEE Trans. Comput.*, vol. 65, no. 9, pp. 2820–2834, Sep. 2016, doi: 10.1109/TC.2015.2509983.

- [3] S. Hatefinasab, N. Rodriguez, A. Garcia, and E. Castillo, "Low-cost soft error robust hardened D-latch for CMOS technology circuit," *Electron.*, vol. 10, no. 11, pp. 1256–1275, May 2021, doi: 10.3390/electronics10111256.

- [4] R. Rajaei, M. Tabandeh, and M. Fazeli, "Single event multiple upset (SEMU) tolerant latch designs in presence of process and temperature variations," *J. Circuits, Syst., Comput.*, vol. 24, no. 1, Jan. 2015, Art. no. 1550007, doi: 10.1142/S0218126615500073.

- [5] H. Wang, X. Dai, Y. Wang, I. Nofal, L. Cai, Z. Shen, W. Sun, J. Bi, B. Li, G. Guo, L. Chen, and S. Baeg, "A single event upset tolerant latch design," *Microelectron. Rel.*, vols. 88–90, pp. 909–913, Sep. 2018.

- [6] A. Dixit and A. Wood, "The impact of new technology on soft error rates," in *Proc. Int. Rel. Phys. Symp.*, 2011, pp. 5B.4.1–5B.4.7, doi: 10.1109/IRPS.2011.5784522.

- [7] K. Katsarou and Y. Tsiatouhas, "Soft error interception latch: Double node charge sharing SEU tolerant design," *Electron. Lett.*, vol. 51, no. 4, pp. 330–332, 2015, doi: 10.1049/el.2014.4374.

- [8] Y. Yamamoto and K. Namba, "Complete double node upset tolerant latch using C-element," *IEICE Trans. Inf. Syst.*, vol. 103, no. 10, pp. 2125–2132, Oct. 2020, doi: 10.1587/transinf.2020EDP7103.

- [9] N. Eftaxiopoulos, N. Axelos, G. Zervakis, K. Tsoumanis, and K. Pekmestzi, "Delta DICE: A double node upset resilient latch," in *Proc. IEEE 58th Int. Midwest Symp. Circuits Syst. (MWSCAS)*, Aug. 2015, pp. 1–4, doi: 10.1109/MWSCAS.2015.7282145.

- [10] Y. Li, H. Wang, S. Yao, X. Yan, Z. Gao, and J. Xu, "Double node upsets hardened latch circuits," *J. Electron. Test.*, vol. 31, nos. 5–6, pp. 537–548, Dec. 2015, doi: 10.1007/s10836-015-5551-3.

- [11] J. Jiang, W. Zhu, J. Xiao, and S. Zou, "A novel high-performance low-cost double-upset tolerant latch design," *Electron.*, vol. 7, no. 10, pp. 247–255, 2018, doi: 10.3390/electronics7100247.

- [12] J. Jiang, Y. Xu, J. Ren, W. Zhu, D. Lin, J. Xiao, W. Kong, and S. Zou, "Low-cost single event double-upset tolerant latch design," *Electron. Lett.*, vol. 54, no. 9, pp. 554–556, May 2018, doi: 10.1049/el.2018.0558.

- [13] N. Eftaxiopoulos, N. Axelos, and K. Pekmestzi, "DIRT latch: A novel low cost double node upset tolerant latch," *Microelectron. Rel.*, vol. 68, pp. 57–68, Jan. 2017, doi: 10.1016/j.microrel.2016.11.006.

- [14] K. Katsarou and Y. Tsiatouhas, "Double node charge sharing SEU tolerant latch design," in *Proc. IEEE 20th Int. Line Test. Symp. (IOLTS)*, Jul. 2014, pp. 122–127, doi: 10.1109/IOLTS.2014.6873683.

- [15] H. Li, L. Xiao, J. Li, and C. Qi, "High robust and cost effective double node upset tolerant latch design for nanoscale CMOS technology," *Microelectron. Rel.*, vol. 93, pp. 89–97, Feb. 2019, doi: 10.1016/j.microrel.2019.01.005.

- [16] Y. Li, X. Cheng, C. Tan, J. Han, Y. Zhao, L. Wang, T. Li, M. B. Tahoori, and X. Zeng, "A robust hardened latch featuring tolerance to doublenode-upset in 28 nm CMOS for spaceborne application," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 67, no. 9, pp. 1619–1623, Sep. 2020, doi: 10.1109/TCSII.2020.3013338.

- [17] F. M. Sajjade, N. K. Goyal, and B. K. S. V. Varaprasad, "Rulebased design for multiple nodes upset tolerant latch architecture," *IEEE Trans. Device Mater. Rel.*, vol. 19, no. 4, pp. 680–687, Dec. 2019, doi: 10.1109/TDMR.2019.2945917.

- [18] A. Yan, Z. Huang, X. Fang, Y. Ouyang, and H. Deng, "Single event double-upset fully immune and transient pulse filterable latch design for nanoscale CMOS," *Microelectron. J.*, vol. 61, pp. 43–50, Mar. 2017, doi: 10.1016/j.mejo.2017.01.001.

- [19] A. Yan, K. Yang, Z. Huang, J. Zhang, J. Cui, X. Fang, M. Yi, and X. Wen, "A double-node-upset self-recoverable latch design for high performance and low power application," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 66, no. 2, pp. 287-291, Feb. 2019, doi: 10.1109/TCSII.2018.2849028.

- [20] T. Calin, M. Nicolaidis, and R. Velazco, "Upset hardened memory design for submicron CMOS technology," IEEE Trans. Nucl. Sci., vol. 43, no. 6, pp. 2874-2878, Dec. 1996.

- [21] A. Yan, Y. Ling, J. Cui, Z. Chen, Z. Huang, J. Song, P. Girard, and X. Wen, "Quadruple cross-coupled dual-interlocked-storage-cells-based multiple-node-upset-tolerant latch designs," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 67, no. 3, pp. 879-890, Mar. 2020.

- [22] J. Guo, S. Liu, L. Zhu, and F. Lombardi, "Design and evaluation of low-complexity radiation hardened CMOS latch for double-node upset tolerance," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 67, no. 6, pp. 1925-1936, Jun. 2020.

- [23] J.-J. Park, Y.-M. Kang, G.-H. Kim, I. Chang, and J. Kim, "A fully polarityaware double-node-upset-resilient latch design," Electronics, vol. 11, no. 15, pp. 2465-2477, 2022, doi: 10.3390/electronics11152465.

- [24] H. Xu, L. Zhou, H. Liang, Z. Huang, C. Sun, and Y. Ning, "Highperformance double-node-upset-tolerant and triple-node-upset-tolerant latch designs," Electronics, vol. 10, no. 20, pp. 2515-2529, 2021.

- [25] H. Xu, C. Sun, L. Zhou, H. Liang, and Z. Huang, "Design of a highly robust triple-node-upset self-recoverable latch," IEEE Access, vol. 9, pp. 113622-113630, 2021.

- [26] Arizona State University. (Jun. 1, 2012). Latest Models. [Online]. Available: http://ptm.asu.edu/

- [27] M. Fazeli, S. G. Miremadi, A. Ejlali, and A. Patooghy, "Low energy single event upset/single event transient-tolerant latch for deep sub Micron technologies," IET Comput. Digit. Techn., vol. 3, no. 3, p. 289, 2009, doi: 10.1049/iet-cdt.2008.0099.

- [28] P. Liu, T. Zhao, F. Liang, J. Zhao, and P. Jiang, "A power-delay-product efficient and SEU-tolerant latch design," IEICE Electron. Exp., vol. 14, no. 23, 2017, Art. no. 20170972.

- [29] Z. Huang, X. Li, Z. Gong, H. Liang, Y. Lu, Y. Ouyang, and T. Ni, "Design of MNU-resilient latches based on input-split C-elements," Microelectron. J., vol. 116, Oct. 2021, Art. no. 105243.

- [30] M. Alioto, E. Consoli, and G. Palumbo, "Variations in nanometer CMOS flip-flops: Part I-Impact of process variations on timing," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 62, no. 8, pp. 2035-2043, Aug. 2015.

- [31] M. Alioto, E. Consoli, and G. Palumbo, "Variations in nanometer CMOS flip-flops: Part II-Energy variability and impact of other sources of variations," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 62, no. 3, pp. 835–843, Mar. 2015.

- [32] A. Yan, H. Liang, Z. Huang, C. Jiang, Y. Ouyang, and X. Li, "An SEU resilient, SET filterable and cost effective latch in presence of PVT variations," Microelectron. Rel., vol. 63, pp. 239-250, Aug. 2016.

- [33] H. Nan and K. Choi, "Novel radiation hardened latch design considering process, voltage and temperature variations for nanoscale CMOS technology," Microelectron. Rel., vol. 51, no. 12, pp. 2086-2092, Dec. 2011.

ALFREDO MEDINA-GARCIA was born in Cordoba, Spain, in 1979. He received the B.Sc. degree in industrial engineering from the University of Cordoba, in 1999, the M.Sc. degree in electronics engineering from the University of Granada, in 2002, and the M.Sc. degree in telecommunication engineering from the University of Seville, in 2008. He is currently pursuing the Ph.D. degree.

In 2004, he joined Infineon Technologies AG, Munich, Germany, where he is currently working as the Lead Principal Engineer with the Innovation Department for Power Conversion. He has contributed with several patents and scientific publications.

DIEGO P. MORALES received the M.Sc., and Ph.D. degrees in electronics engineering from the University of Granada, in 2001 and 2011, respectively. Since 2001, he has been an Associate Professor with the Department of Computer Architecture and Electronics, University of Almeria. Before joining the Department of Electronics and Computer Technology, University of Granada, in 2006, where he is currently working as a Professor (tenured). He is also the Co-Founder of the

Biochemistry and Electronics as a Sensing Technologies (BEST) Research Group, University of Granada. He has coauthored more than 80 scientific contributions. His current research interests include low-power energy conversion, energy harvesting for wearable sensing systems, and new materials for electronics and sensors.

ENCARNACION CASTILLO received the M.A.Sc. and Ph.D. degrees in electronic engineering from the University of Granada, in 2002 and 2008, respectively. From 2003 to 2005, she was a Research Fellow at the Department of Electronics and Computer Technology, University of Granada, where she is currently a Tenured Professor. All this work has led to the publication of 50 articles in indexed journals and more than 60 contributions to international conferences. She has coauthored two

patents in Spain and contributed to 13 projects in the several national and regional programs, as well as 11 technology-transfer contracts. Her current research interests include cryptoprocessors on FPGA, memory devices, smart instrumentation, and acquisition and processing of biosignals. She serves as a reviewer and a guest editor for several journals.

the bachelor's and master's degrees in electrical and electronic engineering. She is currently pursuing the Ph.D. degree with the University of Granada, Spain. Previously, she worked in analog and digital circuits in several research institutions and companies. Her research interests include VLSI, microelectronics reliability, and fault tolerance. She has published several manuscripts on these topics.

SEYEDEHSOMAYEH HATEFINASAB received

NOEL RODRIGUEZ received the B.Sc. and M.Eng. degrees in electronics engineering from the University of Granada, in 2004, and the dual Ph.D. degree from the University of Granada and the National Polytechnic Institute of Grenoble, France, in 2008. From 2017 to 2020, he was the Head of the Pervasive Electronics Advanced Research Laboratory (PEARL), University of Granada. He is currently a Full Professor of electronics with the Department of Electronics and

Computer Technology, University of Granada. He has coauthored 15 international patents, several book chapters, and more than 150 peer-reviewed scientific contributions. His current research interests include low-power energy conversion, memory devices, and new materials and devices for electronic applications. He received the First National Award of University Education for his B.Sc. and M.Sc. degrees and the Extraordinary Award for his Ph.D. degree.