#### University of Wisconsin Milwaukee

### **UWM Digital Commons**

Theses and Dissertations

December 2022

# High Power, Medium Frequency, and Medium Voltage **Transformer Design and Implementation**

Ahmad El Shafei University of Wisconsin-Milwaukee

Follow this and additional works at: https://dc.uwm.edu/etd

Part of the Electrical and Electronics Commons

#### **Recommended Citation**

El Shafei, Ahmad, "High Power, Medium Frequency, and Medium Voltage Transformer Design and Implementation" (2022). Theses and Dissertations. 3105. https://dc.uwm.edu/etd/3105

This Dissertation is brought to you for free and open access by UWM Digital Commons. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of UWM Digital Commons. For more information, please contact scholarlycommunicationteam-group@uwm.edu.

# HIGH POWER, MEDIUM FREQUENCY, AND MEDIUM VOLTAGE TRANSFORMER DESIGN AND IMPLEMENTATION

by

Ahmad El Shafei

A Dissertation Submitted in

Partial Fulfillment of the

Requirements for the Degree of

Doctor of Philosophy

in Electrical Engineering

at

The University of Wisconsin-Milwaukee

December 2022

#### **ABSTRACT**

# HIGH POWER, MEDIUM FREQUENCY, AND MEDIUM VOLTAGE TRANSFORMER DESIGN AND IMPLEMENTATION

by

#### Ahmad El Shafei

The University of Wisconsin-Milwaukee, 2022 Under the Supervision of Professor Adel Nasiri

Many industrial applications that require high-power and high-voltage DC-DC conversion are emerging. Space-borne and off-shore wind farms, fleet fast electric vehicle charging stations, large data centers, and smart distribution systems are among the applications. Solid State Transformer (SST) is a promising concept for addressing these emerging applications. It replaces the traditional Low Frequency Transformer (LFT) while offering many advanced features such as VAR compensation, voltage regulation, fault isolation, and DC connectivity.

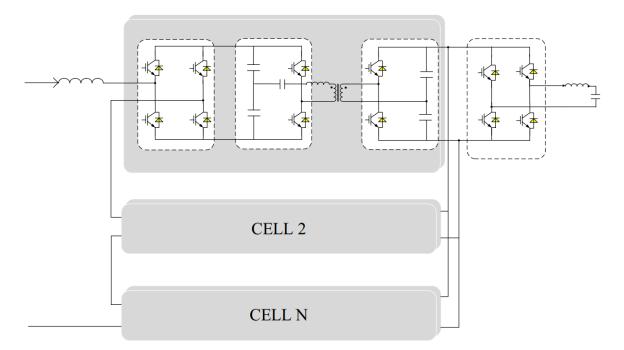

Many technical challenges related to high voltage stress, efficiency, reliability, protection, and insulation must be addressed before the technology is ready for commercial deployment. Among the major challenges in the construction of SSTs are the strategies for connecting to Medium Voltage (MV) level. This issue has primarily been addressed by synthesizing multicellular SST concepts based on modules rated for a fraction of the total MV side voltage and connecting these modules in series at the input side. Silicon Carbide (SiC) semiconductor development enables the fabrication of power semiconductor devices with high blocking voltage capabilities while achieving superior switching and conduction performances. When compared to modular lower voltage converters, these higher voltage semiconductors enable the construction of single-cell SSTs by avoiding the series connection of several modules, resulting in simple, reliable, lighter mass, more power dense, higher efficiency, and cost effective converter

#### structures.

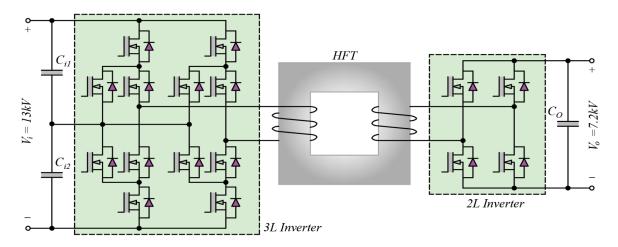

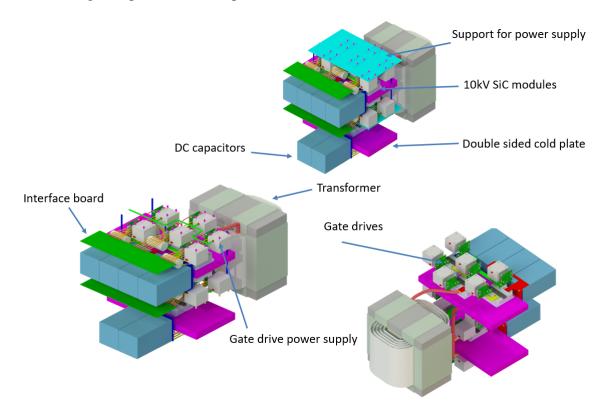

This dissertation proposes a solution to this major issue. The proposed work focuses on the development of a dual active bridge with high power, medium voltage, and medium frequency control. This architecture addresses the shortcomings of existing modular systems by providing a more power dense, cost-effective, and efficient solution. For the first time, this topology is investigated on a 700kW system connected to a 13kVdc input to generate 7.2kVdc at the output. The use of 10kV SiC modules and gate drivers in an active neutral point clamped to two level dual active bridge converter is investigated. A special emphasis will be placed on a comprehensive transformer design that employs a multi-physics approach that addresses all magnetic, electrical, insulation, and thermal aspects. The transformer is designed and tested to ensure the system's viability.

# TABLE OF CONTENTS

| LIST<br>LIST<br>LIST | RACT OF FIGURES OF TABLES OF TERMS AND ABBREVIATIONS OWLEDGEMENTS | vi<br>xii<br>xiii |

|----------------------|-------------------------------------------------------------------|-------------------|

| 1                    | Introduction                                                      | 1                 |

| 1.1                  | Trends and Motivations                                            | 1                 |

| 1.2                  | Research Objectives and Contributions                             | 7                 |

| 1.3                  | Dissertation Organization                                         | 9                 |

| 2                    | DC-DC Converters                                                  | 10                |

| 2.1                  | Overview                                                          | 10                |

|                      | 2.1.1 Hard switching/Soft switching                               | 12                |

|                      | 2.1.2 Unidirectional/Bidirectional                                | 13                |

| 2.2                  | Dual Active Bridge                                                | 14                |

|                      | 2.2.1 Applications                                                | 15                |

|                      | 2.2.2 Principle of Operation                                      | 16                |

|                      | 2.2.3 Modeling of DAB                                             | 18                |

|                      | 2.2.4 Switching and Modulation Techniques                         | 20                |

|                      | 2.2.5 Soft-Switching Operation                                    | 27                |

|                      | 2.2.6 DAB Controller                                              | 32                |

| 2.3                  | DAB - High Frequency Transformer                                  | 36                |

|                      | 2.3.1 Overview                                                    | 37                |

|                      | 2.3.2 Applications                                                | 40                |

|                      | 2.3.3 Challenges                                                  | 46                |

|                      | 2.3.4 State-of-the-art Power and Voltage Levels                   | 49                |

| 3                    | Power Converter Topology                                          | 55                |

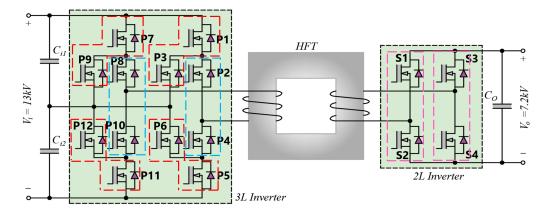

| 3.1                  | Three-Level to Two-Level Topology                                 | 55                |

|                      | 3.1.1 Symmetric Phase-Shift Modulation                            |                   |

|                      | 3.1.2 Neutral Point Diode Clamped Configuration                   | 57                |

|                      | 3.1.3 Switching States of the 3L-NPC Bridge                       | 58                |

|                      | 3.1.4 Symmetric Modulation                                        | 61                |

|                      | 3.1.5 Power Flow Equations and Soft Switching                     | 62                |

| 3.2                  | Thermal Analysis                                                  | 74                |

|                      | 3.2.1 Overview                                                    | 74                |

|                      | 3.2.2 Loss Estimation of HV-side Devices                          | 75                |

|                      | 3.2.3 Loss Estimation of LV-side Devices                          | 80                |

|                      | 3.2.4 Converter Cooling System Design                             | 80                |

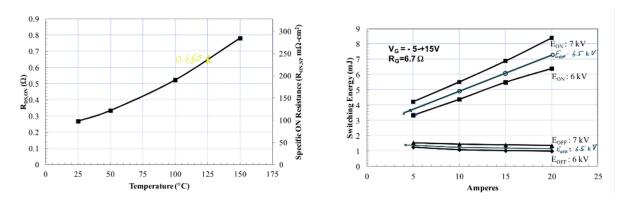

| 3.3                  | HV SiC Power Module                                               | 89                |

|                      | 3.3.1 Semiconductor Switches                                      | 89                |

|                      | 3.3.2 Module Parasitics                                           | 92                |

|                      | 3.3.3 Layout and System Interface                                 | 94                |

|                      | 3.3.4 Terminal Arrangement                                        | 96                |

| 3.4 | Insulation Coordination                        | 99  |

|-----|------------------------------------------------|-----|

| 4   | High Power, MV, and MF Transformer             | 107 |

| 4.1 | Electromagnetic Analysis                       | 110 |

|     | 4.1.1 Overview                                 | 110 |

|     | 4.1.2 Magnetic Material Selection              | 112 |

|     | 4.1.3 Core Loss Calculation Methods            | 117 |

|     | 4.1.4 Modified Empirical Expressions           | 126 |

|     | 4.1.5 Windings and Transformer Geometry        | 129 |

|     | 4.1.6 Winding Loss                             | 131 |

|     | 4.1.7 Leakage Inductance                       | 137 |

|     | 4.1.8 Area Product                             | 141 |

| 4.2 | Insulation Analysis                            | 142 |

| 4.3 | Thermal Analysis                               | 148 |

|     | 4.3.1 Overview                                 |     |

|     | 4.3.2 Thermal Resistance                       |     |

|     | 4.3.3 Heat Capacity                            |     |

|     | 4.3.4 Equivalent Thermal Network               |     |

|     | 4.3.5 Governing Equations                      |     |

|     | 4.3.6 Numerical Solution                       |     |

|     | 4.3.7 Transient Behavior                       |     |

| 4.4 | Transformer Six-capacitor Model                |     |

|     | 4.4.1 Overview                                 |     |

|     | 4.4.2 Common-mode Derivation                   |     |

| 4.5 | Transformer Parameters Compilation             |     |

| 5   | FEA Simulations and Experimental Results       | 171 |

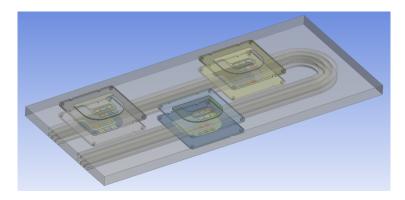

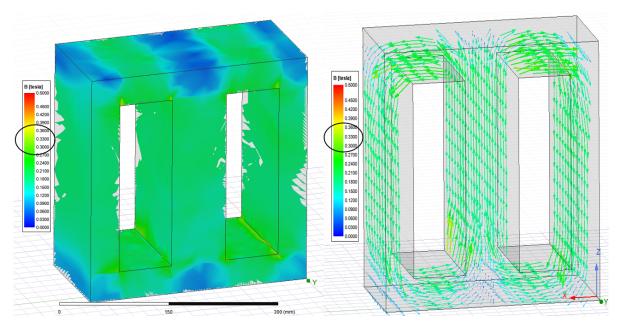

| 5.1 | Electromagnetic Ansys Simulation               | 171 |

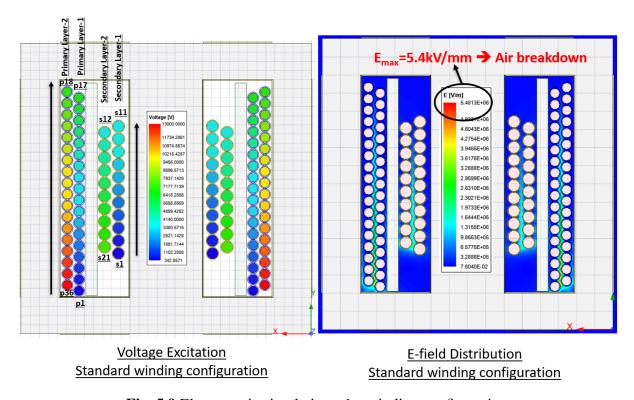

| 5.2 | Electrostatic Ansys Simulation                 |     |

| 5.3 | Thermal Ansys Simulation                       |     |

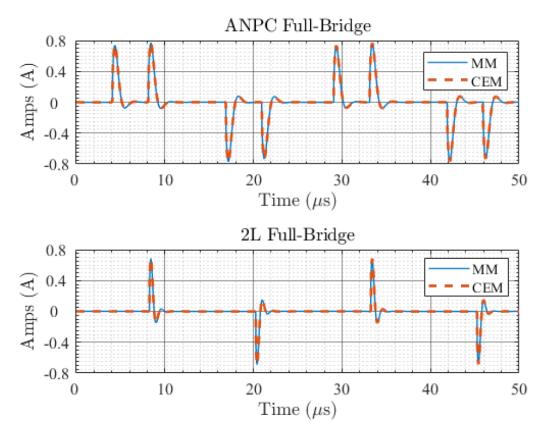

| 5.4 | EMI PLECS/Simulink Simulation                  |     |

|     | 5.4.1 Simulation Validation                    |     |

|     | 5.4.2 Hardware Validation/EMI Characterization |     |

| 5.5 | Prototype Build and Testing                    |     |

| 6   | Conclusion and Future Work                     | 195 |

| -   | LIST OF PUBLICATIONS                           |     |

|     | REFERENCES                                     |     |

|     | CURRICULUM VITAE                               |     |

## LIST OF FIGURES

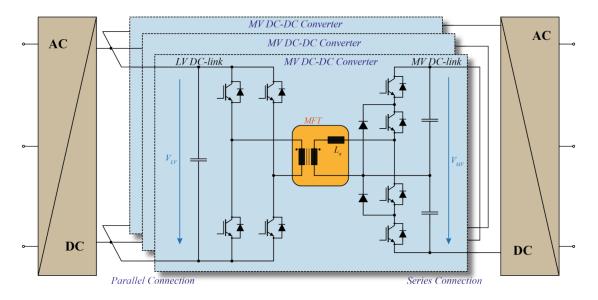

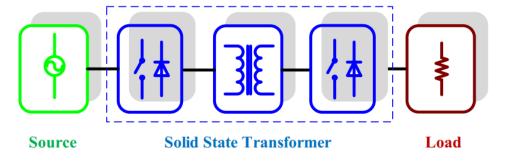

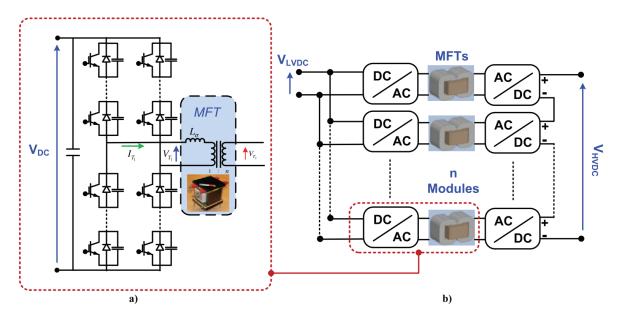

| 1.1  | Medium frequency power conversion system                                      | 3  |

|------|-------------------------------------------------------------------------------|----|

| 2.1  | DC-DC converter interfacing two DC grids with different voltage levels        | 11 |

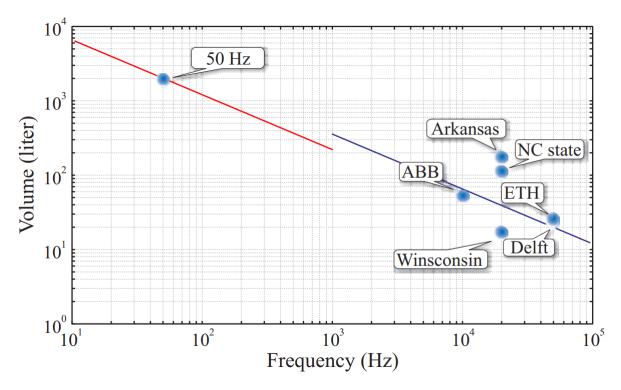

| 2.2  | Volume reached by different transformer designs with different operating fre- |    |

|      | quencies (all scaled to 1 MW power rating)                                    | 12 |

| 2.3  | Bidirectional DC-DC converter                                                 | 13 |

| 2.4  | Electrical systems in a series Hybrid Electrical Vehicle (HEV)                | 14 |

| 2.5  | Conventional full bridge based isolated bidirectional DC-DC converters        | 16 |

| 2.6  | Key waveforms of conventional FB BOC: (a) A-to-B mode, (b) B-to-A mode .      | 17 |

| 2.7  | SPS control                                                                   | 22 |

| 2.8  | Topology of DAB-IBDC                                                          | 22 |

| 2.9  | EPS control                                                                   | 23 |

| 2.10 | DPS control                                                                   | 25 |

| 2.11 | TPS control                                                                   | 27 |

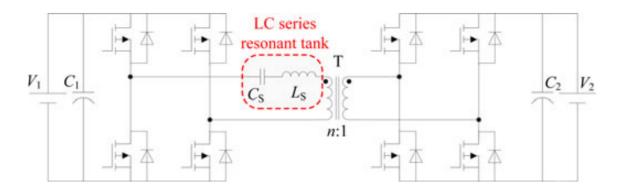

| 2.12 | LC-type resonant DAB-IBDC                                                     | 28 |

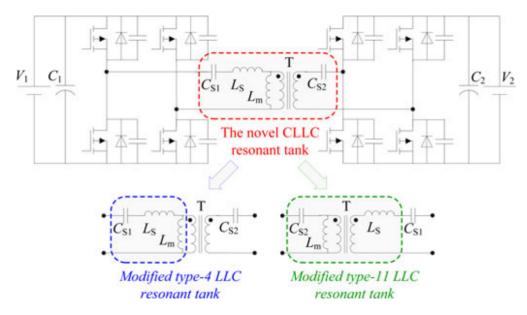

| 2.13 | CLLC-type asymmetric resonant DAB-IBDC                                        | 29 |

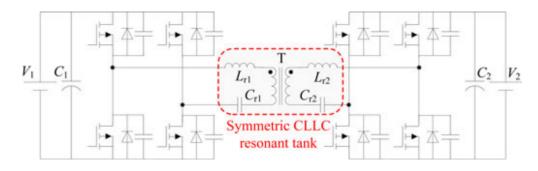

| 2.14 | CLLC-type symmetric resonant DAB-IBDC                                         | 30 |

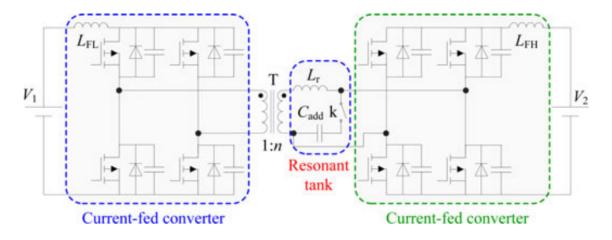

| 2.15 | Current-current-fed resonant DAB-IBDC                                         | 31 |

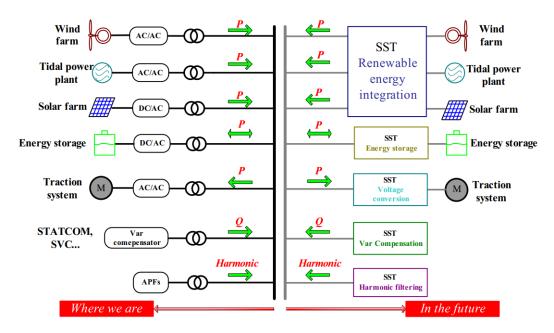

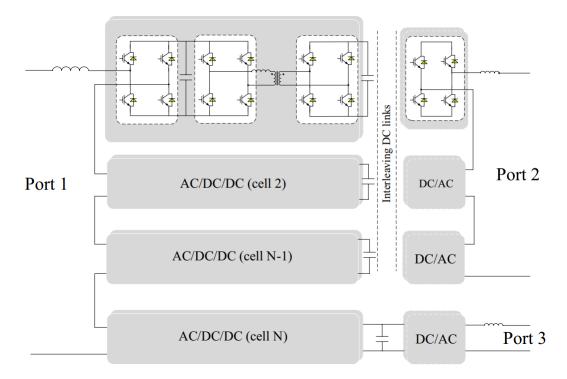

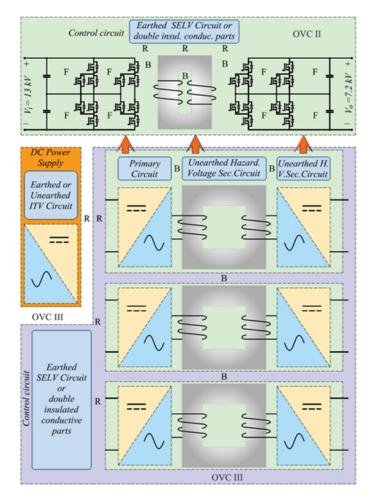

| 2.16 | SST configuration                                                             | 40 |

| 2.17 | Potential application of SST in the future distribution system                | 41 |

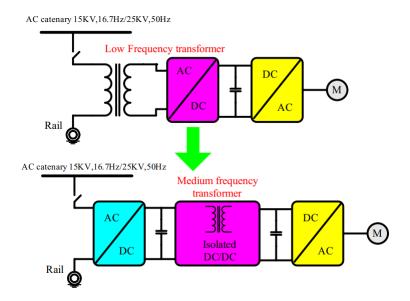

| 2.18 | SST-based tractions system                                                    | 42 |

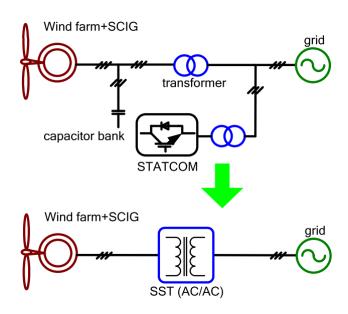

| 2.19 | Wind energy system interfaced by SST                                          | 43 |

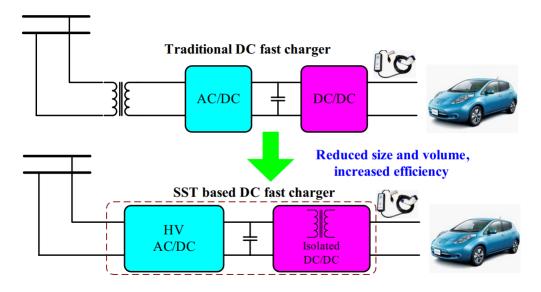

| 2.20 | SST-based DC fast charger                                                     | 44 |

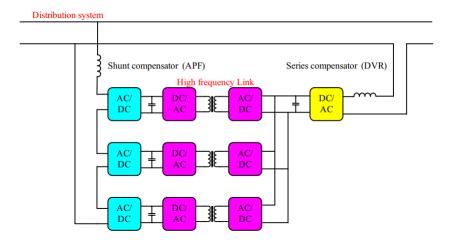

| 2.21 | High-frequency link UPQC structure                                            | 45 |

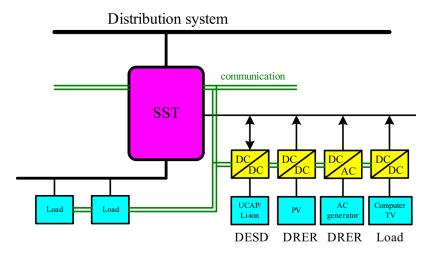

| 2.22 | SST for smart grid integration                                                | 46 |

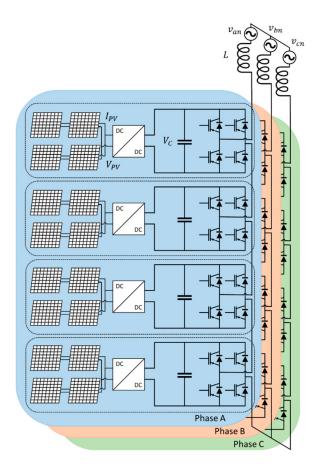

| 2.23 | MV grid-connection using SST based power electronics building block           | 47 |

| 2.24 | UNIFLEX SST topology for smart grid application                               | 52 |

| 2.25 | EPRI SST topology (with inverter stage) for DC fast charger application       | 53 |

| 2.26 | Basic unit of GE SST topology for substation application                      | 53 |

| 2.27 | ABB SST topology for traction application                                     | 54 |

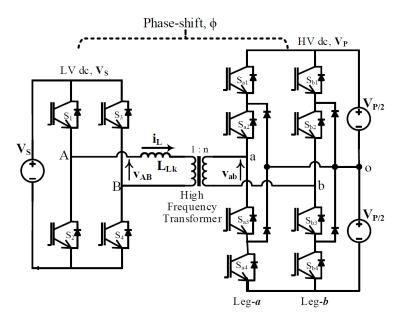

| 3.1  | Boost configuration ( $V_P > V_S$ ) a multilevel dual active bridge (ML-DAB), where                                                       |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | the transformer primary voltage $(v_{AB})$ two-level (2L) and the secondary $(v_{ab})$                                                    |    |

|      | of 5L                                                                                                                                     | 57 |

| 3.2  | Buck configuration ( $V_S < V_P$ ) of the ML-DAB where the transformer primary                                                            |    |

|      | voltage $(v_{ab})$ is of 5L and the secondary $(v_{AB})$ is of 2L                                                                         | 57 |

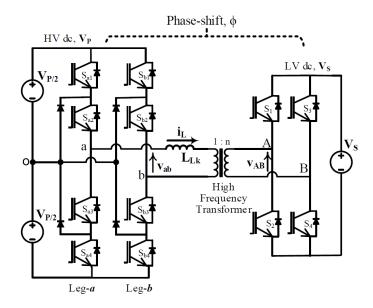

| 3.3  | Switching states and corresponding 3L voltage $v_{ao}$ synthesized from leg-a of a                                                        |    |

|      | 3L-NPC bridge                                                                                                                             | 60 |

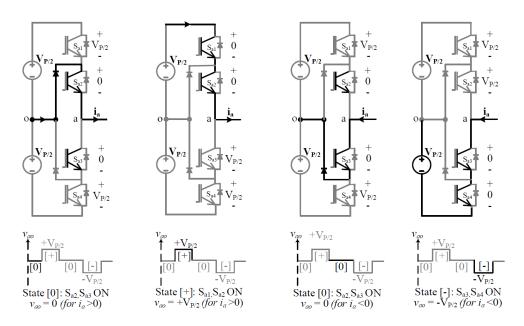

| 3.4  | Switch pulses and corresponding voltage waveforms and primary current in a                                                                |    |

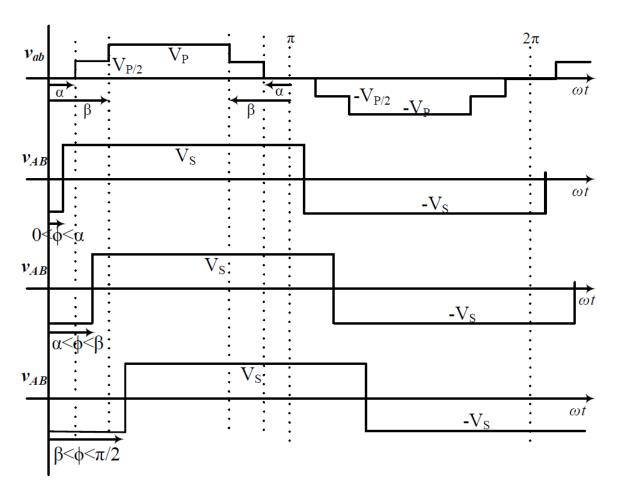

|      | 2L-5L DAB boost topology                                                                                                                  | 60 |

| 3.5  | Voltage waveforms in a 5L-2L DAB for three different cases of buck topology                                                               |    |

|      | when formed using D = $0.5$                                                                                                               | 61 |

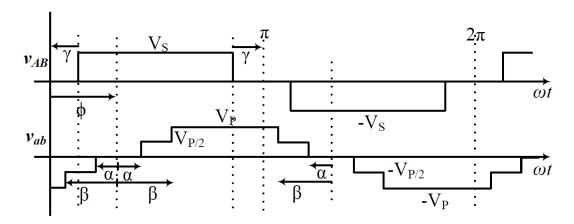

| 3.6  | Voltage waveforms in a 3L-5L DAB boost topology when $v_{AB}$ formed using                                                                |    |

|      | D<0.5                                                                                                                                     | 62 |

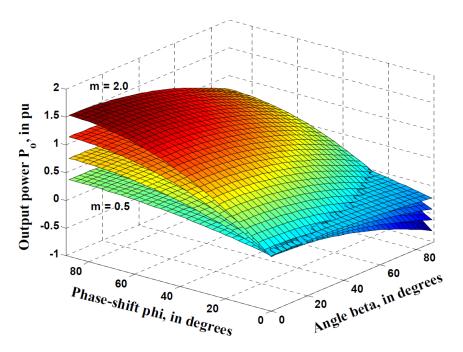

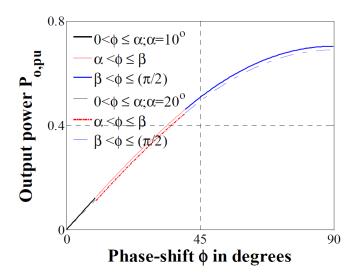

| 3.7  | ML-DAB output power $P_{Op.u}$ vs. $\phi$ and $\beta$ with $\alpha$ = 10° for m = 0.5, 1, 1.5 and 2                                       | 65 |

| 3.8  | Power flow through DAB for all three cases (3.12) to (3.14), concerning phase-                                                            |    |

|      | shift $\phi$ ; here, $\alpha$ =10° and 20°, $\beta$ =40° are assumed for calculation                                                      | 67 |

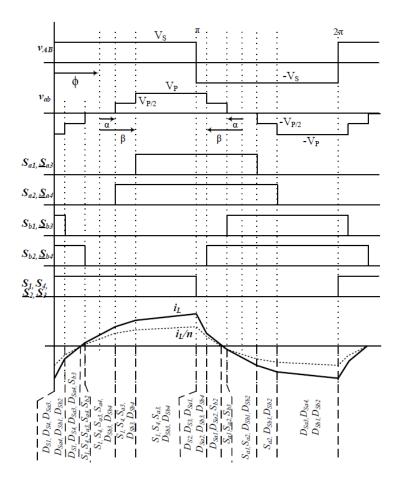

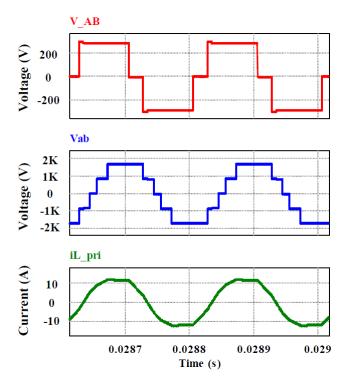

| 3.9  | Primary 3L voltage $v_{AB}$ , secondary 5L voltage $v_{ab}$ and current through the pri-                                                  |    |

|      | mary referred leakage inductance $i_L$ ; where test case was done for $V_S$ = 290V,                                                       |    |

|      | $V_P = 1868 \text{V}, \ \alpha = 10^o, \ \beta = 40^o, \ \gamma = 20^o \ \text{and} \ \phi = 60^o. \ \dots \dots \dots \dots \dots \dots$ | 68 |

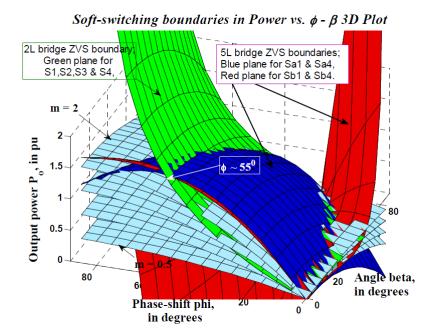

| 3.10 | Soft switching boundaries shown in three-dimensional power vs. $\phi$ - $\beta$ planes                                                    |    |

|      | (where $\alpha$ = $15^o$ , $0 < \beta < 90^o$ and $0 < \phi < 90$ ); the grey planes (3.15) show                                          |    |

|      | the power vs. phi-beta relations for $m = 0.5, 1, 1.5, 2$ ; the green plane (3.17) is                                                     |    |

|      | for two-level bridge, and the ZVS is possible while operating under this plane;                                                           |    |

|      | the blue (3.18) and red (3.19) planes are for five-level bridge leg-a and leg-b,                                                          |    |

|      | respectively                                                                                                                              | 69 |

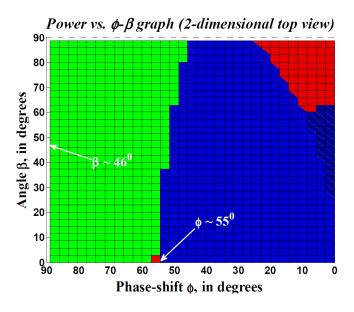

| 3.11 | Two-dimensional view of Fig. 3.10 showing the ZVS boundaries of $\phi$ and $\beta \;$ .                                                   | 69 |

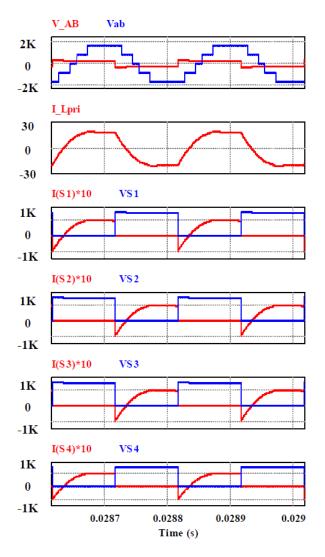

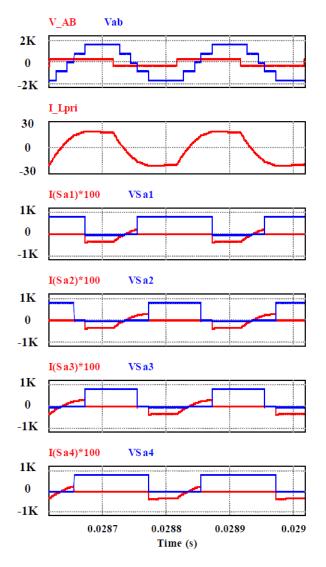

| 3.12 | Voltage across the transformer $v_{AB}$ and $v_{ab}$ , inductor current $i_L$ and switch cur-                                             |    |

|      | rents and voltages for $S_1$ to $S_4$                                                                                                     | 70 |

| 3.13 | Voltage across the transformer $v_{AB}$ and $v_{ab}$ , inductor current $i_L$ and switch cur-                                             |    |

|      | rents and voltages for $S_{a1}$ to $S_{a4}$                                                                                               | 72 |

| 3.14 | Voltage across the transformer $v_{AB}$ and $v_{ab}$ , inductor current $i_L$ and switch cur-                                             |    |

|      | rents and voltages for $S_{k1}$ to $S_{k4}$                                                                                               | 73 |

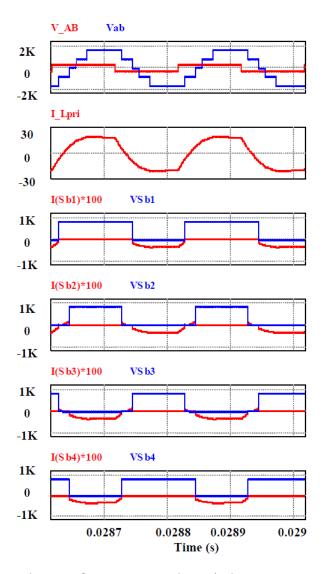

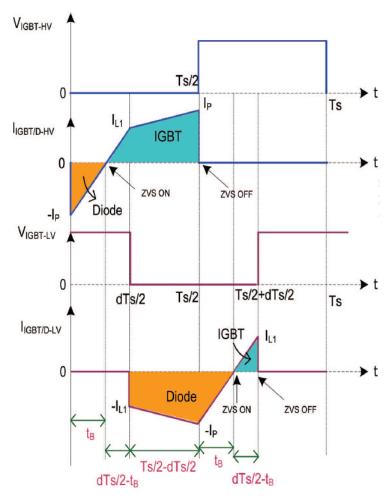

| 3.13 | Theoretical waveforms of devices on the HV side and LV side of the DAB         |     |

|------|--------------------------------------------------------------------------------|-----|

|      | DC-DC converter (Device conduction intervals are marked in pink)               | 76  |

| 3.16 | HV-side switch and anti-parallel diode power loss comparison for various man-  |     |

|      | ufacturers                                                                     | 79  |

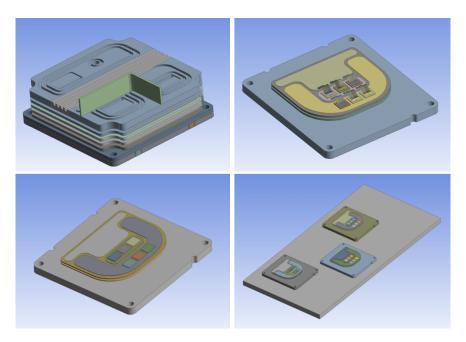

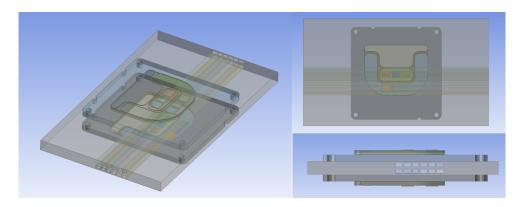

| 3.17 | SiC power modules and designed cold-plate                                      | 81  |

| 3.18 | SiC MOSFET half-bridges configuration to create ANPC-2L converter              | 81  |

| 3.19 | Module $R_{DS,ON}=0.65\Omega$ and switching energy plots                       | 82  |

| 3.20 | Primary double sided cold plate                                                | 83  |

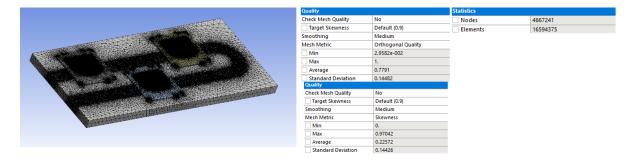

| 3.21 | FEA meshing texture                                                            | 83  |

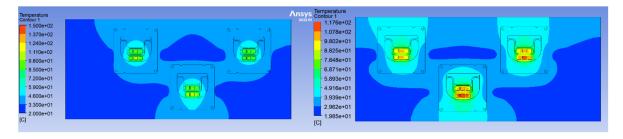

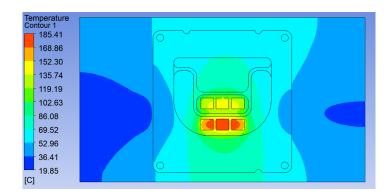

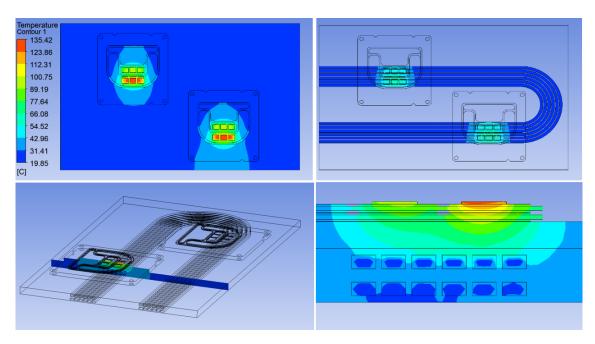

| 3.22 | First iteration temperature distribution                                       | 84  |

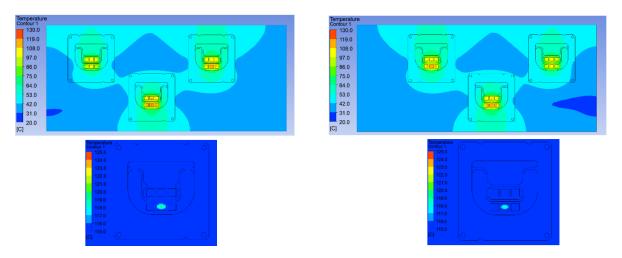

| 3.23 | Copper vs. Aluminum cold material material temperature comparison              | 84  |

| 3.24 | Reduced copper cold plate thickness temperature distribution                   | 85  |

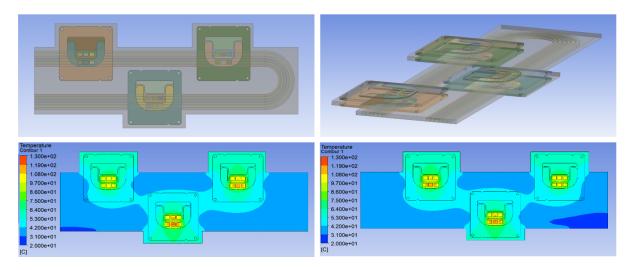

| 3.25 | Primary double-sided cold plate                                                | 86  |

| 3.26 | 1st iteration: secondary double-sided cold plate                               | 86  |

| 3.27 | 1st iteration: secondary double-sided cold plate temperature distribution      | 87  |

| 3.28 | Secondary side single-sided cold plate                                         | 87  |

| 3.29 | Secondary side single-sided cold plate                                         | 88  |

| 3.30 | (a) Modularity from device-level (b) modularity from converter level as se-    |     |

|      | ries/parallel connections of building blocks                                   | 90  |

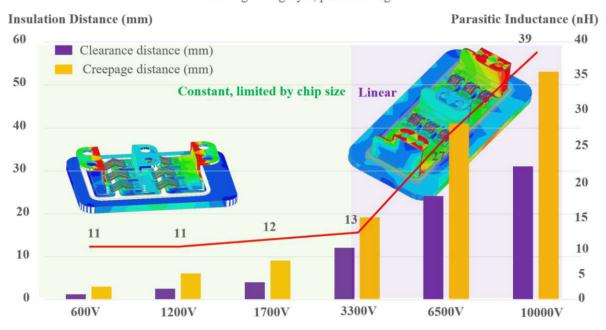

| 3.31 | Insulation distance and parasitic inductance at typical voltage levels         | 93  |

| 3.32 | Parasitic inductance and parasitic capacitance at typical insulation distance  | 93  |

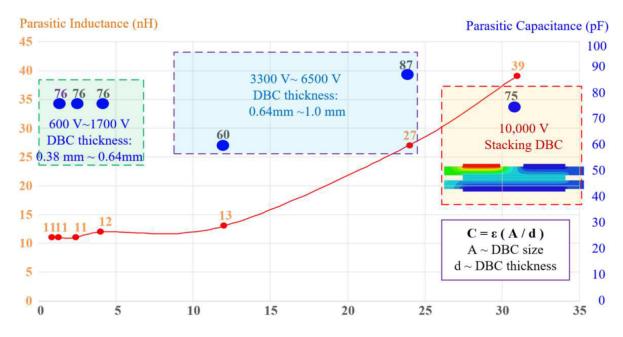

| 3.33 | Typical layouts and the busbar arrangements                                    | 95  |

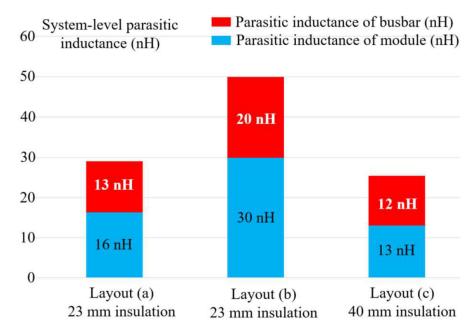

| 3.34 | Parasitic inductance of typical layouts with 50mm laminated busbar             | 96  |

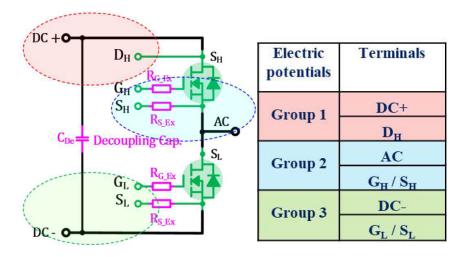

| 3.35 | Electric potentials groups in a half-bridge topology                           | 97  |

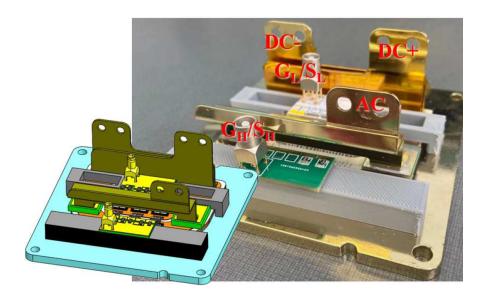

| 3.36 | Module inner layout for layout (c)                                             | 98  |

| 3.37 | Converter Structure                                                            | 99  |

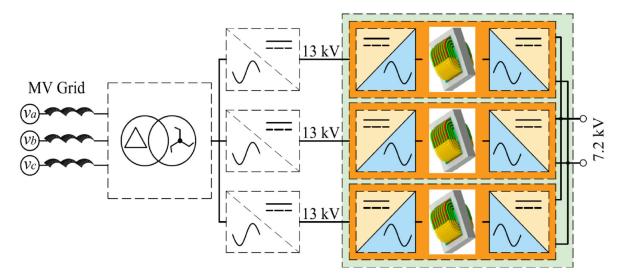

| 3.38 | Required insulation and OVC levels                                             | 102 |

| 3.39 | A single stage of the 3L-2L converter                                          | 103 |

| 3.40 | Power Converter Design Assembly                                                | 106 |

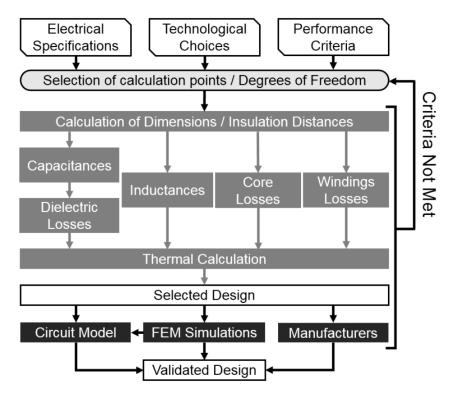

| 4.1  | Design flow chart showing pre-design steps (top-white), analytical design cal- |     |

|      | culation (middle-light grey) and validation steps (bottom-black)               | 109 |

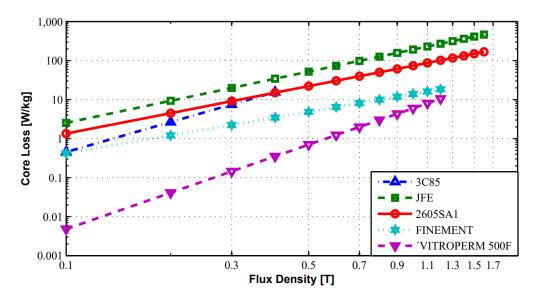

| 4.2  | Specific core loss comparison of different soft magnetic material versus mag-                     |

|------|---------------------------------------------------------------------------------------------------|

|      | netic flux density at 5kHz                                                                        |

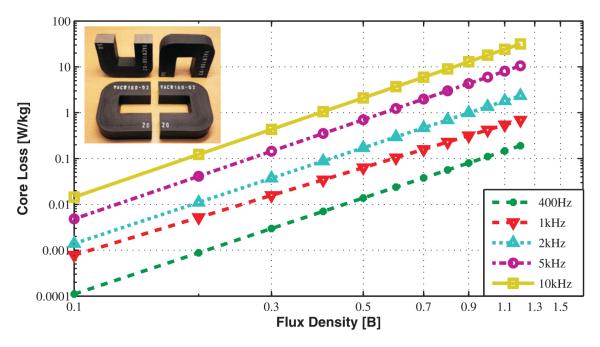

| 4.3  | Specific core loss of Vitroperm500F at different frequencies                                      |

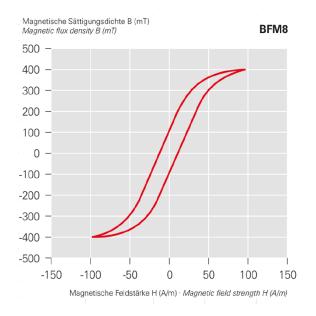

| 4.4  | Ferrite BFM8 B-H curve at 100C                                                                    |

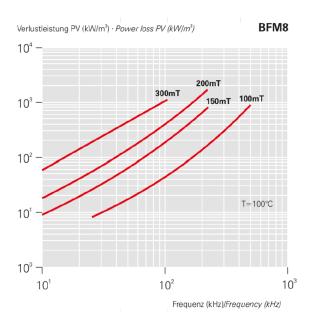

| 4.5  | Ferrite BFM8 power loss vs. frequency at 100C                                                     |

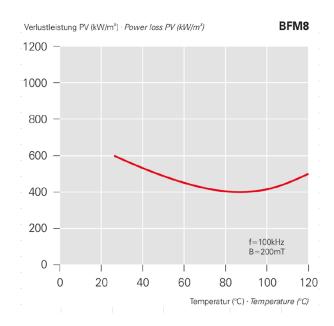

| 4.6  | Ferrite BFM8 power loss vs. temperature                                                           |

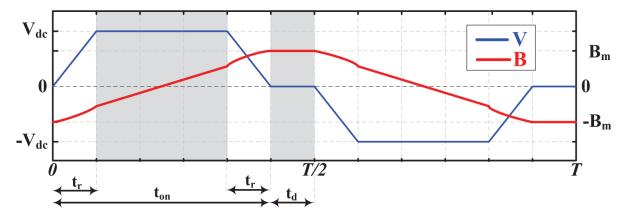

| 4.7  | Example of the excitation voltage and the corresponding instantaneous value of                    |

|      | magnetic flux density                                                                             |

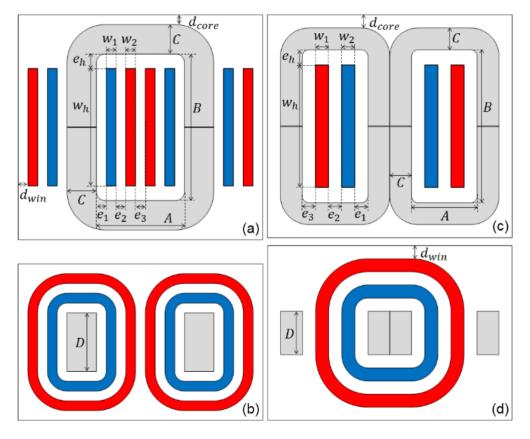

| 4.8  | Geometry schematics for (a) Core-Type front view, (b) Core-Type top view, (c)                     |

|      | Shell-Type front view, and (d) Shell-Type top view in case of air insulation 129                  |

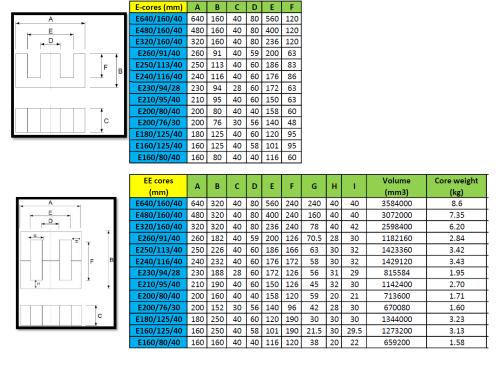

| 4.9  | Largest available ferrite E-cores used in design stage                                            |

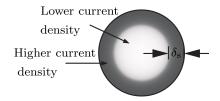

| 4.10 | Illustration of skin effect in a single current-carrying conductor                                |

| 4.11 | Illustration of proximity effect between two neighboring current carrying con-                    |

|      | ductors                                                                                           |

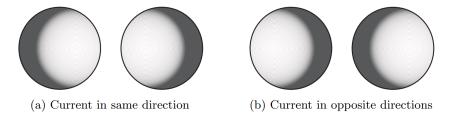

| 4.12 | Litz wire                                                                                         |

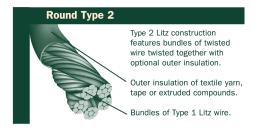

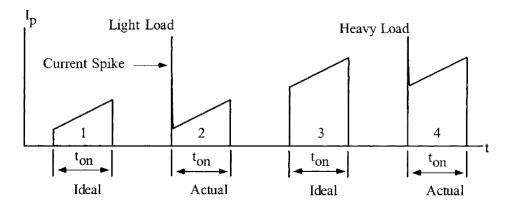

| 4.13 | Switching Voltage and Current Waveforms                                                           |

| 4.14 | Switching Voltage and Current Waveforms                                                           |

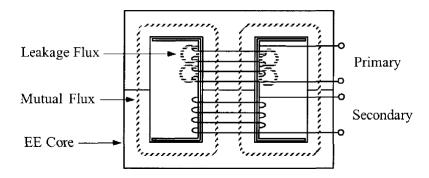

| 4.15 | Leakage Flux                                                                                      |

| 4.16 | Leakage Flux                                                                                      |

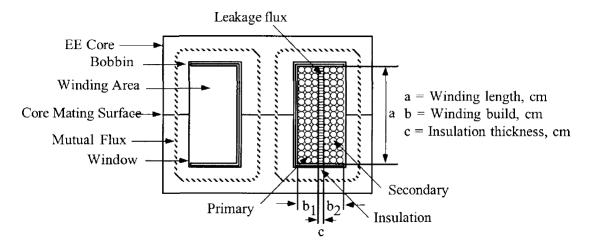

| 4.17 | Conventional Transformer Configuration                                                            |

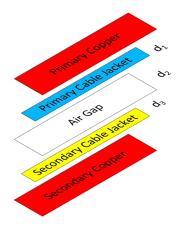

| 4.18 | Zoomed-in insulation structure between primary winding and secondary winding 142                  |

| 4.19 | 3M <sup>TM</sup> CeQUINBORD CGA Inorganic Insulating Board                                        |

| 4.20 | Step-wise consolidation into an equivalent lumped model (a) Distributed turns                     |

|      | and layers (b) Consolidation of turns into a lumped layer (c) Consolidation of                    |

|      | layers into a lumped-winding                                                                      |

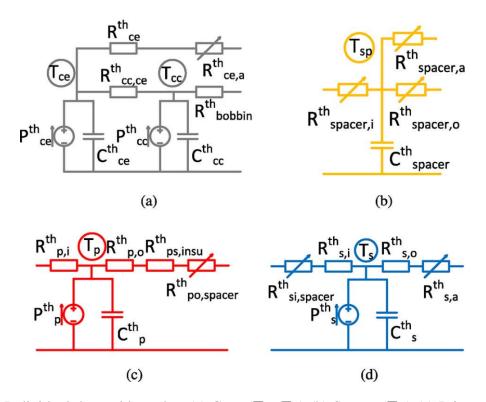

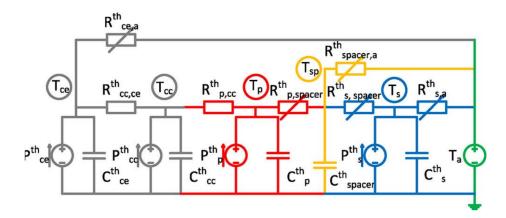

| 4.21 | Individual thermal branches (a) Core $(T_{cc}, T_{ce})$ (b) Spacer $(T_{sp})$ (c) Primary $(T_p)$ |

|      | (d) Secondary $(T_s)$                                                                             |

| 4.22 | Equivalent thermal network of transformer                                                         |

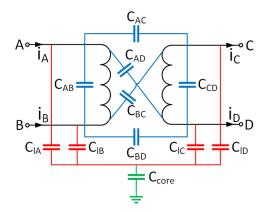

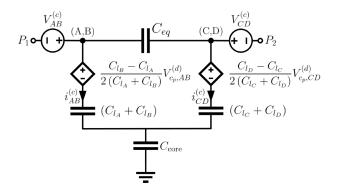

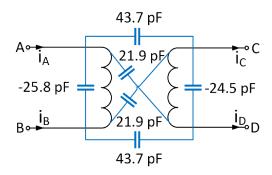

| 4.23 | EMI Characterization Platform, Dual Active Bridge MM Circuit with LISNs 159                       |

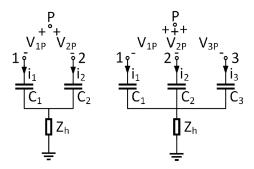

| 4.24 | Two-line (left) and three-line (right) capacitor models                                           |

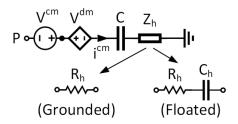

| 4.25 | CEM section example                                                                               |

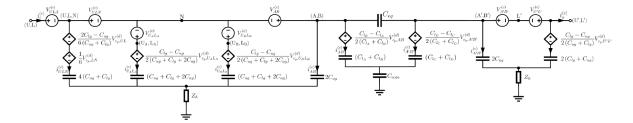

| 4.26 | Dual Active Bridge CEM                                                                            |

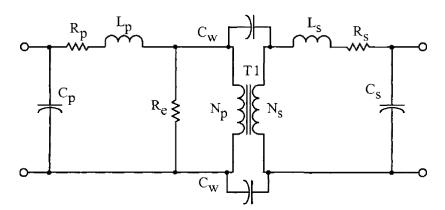

| 4.27 | Simplified transformer model                                                    |

|------|---------------------------------------------------------------------------------|

| 4.28 | Transformer CEM                                                                 |

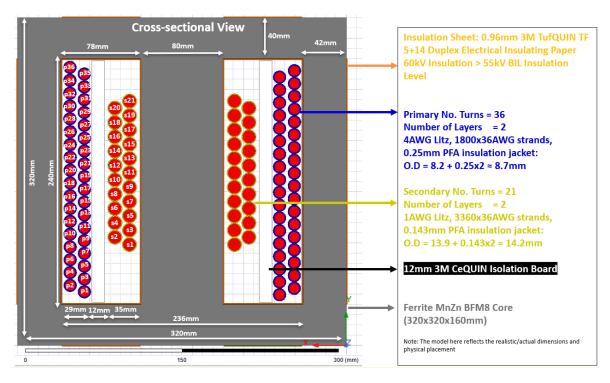

| 4.29 | Transformer cross-sectional view                                                |

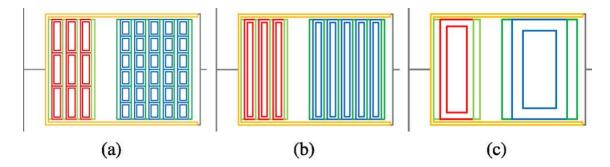

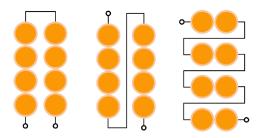

| 4.30 | (a) Standard winding; (b),(c) flyback winding                                   |

| 4.31 | Calculated Winding Parasitics                                                   |

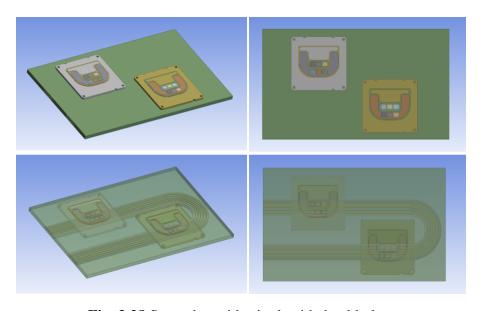

| 5.1  | Ansys Maxwell-3D Transformer Model                                              |

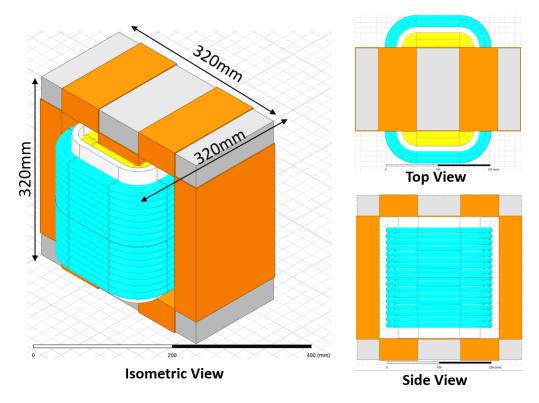

| 5.2  | Transformer cross-sectional view                                                |

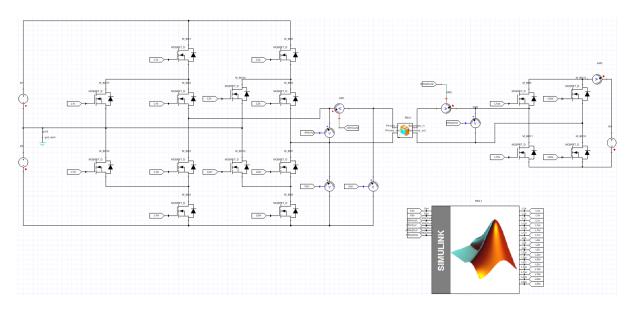

| 5.3  | Ansys Simplorer ANPC -2L circuit implementation                                 |

| 5.4  | Simulink PWM generation                                                         |

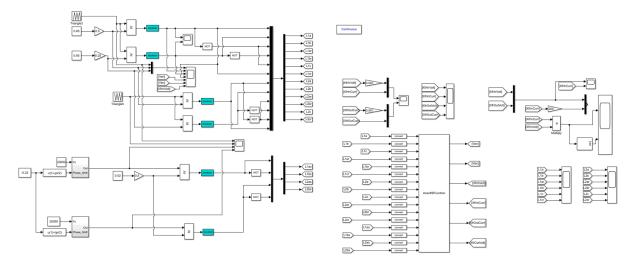

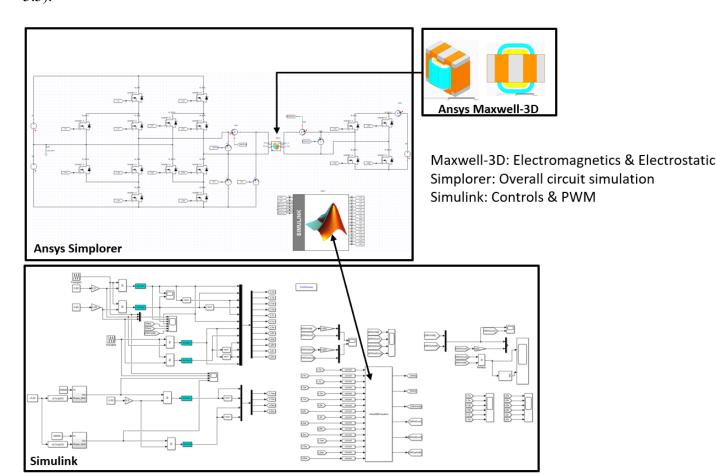

| 5.5  | System level transient co-simulation                                            |

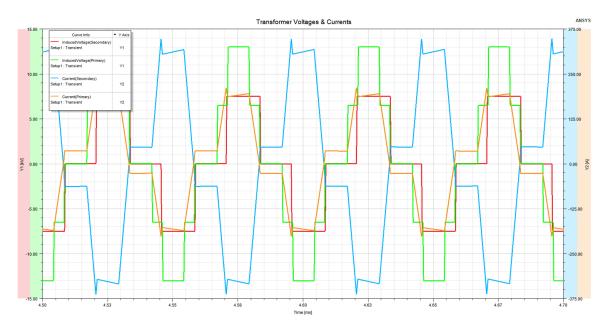

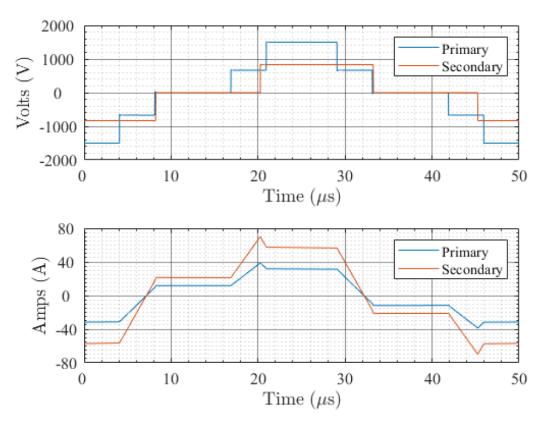

| 5.6  | Voltages and currents waveforms                                                 |

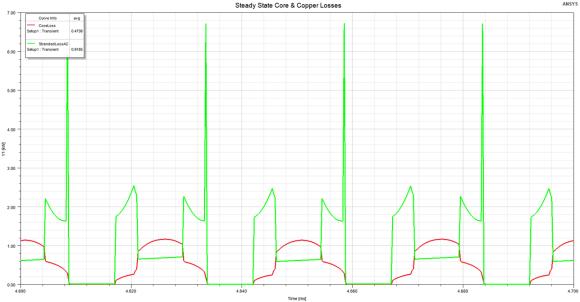

| 5.7  | Core and copper losses                                                          |

| 5.8  | Peak flux density                                                               |

| 5.9  | Electrostatic simulation - 1st winding configuration                            |

| 5.10 | Electrostatic simulation - 2nd winding configuration                            |

| 5.11 | Steady-state voltages (top), currents (bottom)                                  |

| 5.12 | CM validation, grounded heatsink                                                |

| 5.13 | CM validation, floated heatsink                                                 |

| 5.14 | ANPC CM current, neutral clamped heatsink                                       |

| 5.15 | Two-level full-bridge converter on EMI characterization platform 185            |

| 5.16 | Two-level full-bridge converter EMI characterization in time-domain. (a) mixed- |

|      | mode (DC+ and DC-), (b) common-mode, (c) differential-mode                      |

| 5.17 | Two-level full-bridge converter EMI characterization in frequency domain. (a)   |

|      | mixed-mode, (b) common-mode, (c) differential-mode                              |

| 5.18 | Transformer Prototype                                                           |

| 5.19 | Transformer connected to 80kV HiPot tester                                      |

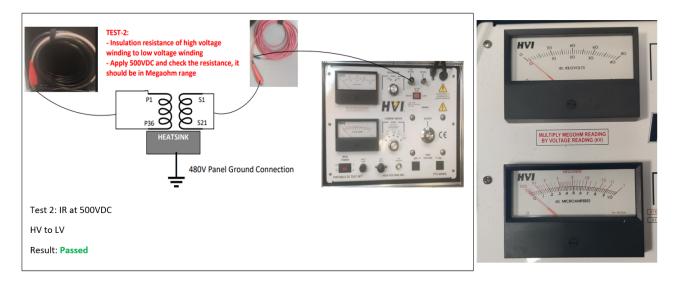

| 5.20 | IR: primary to secondary and ground                                             |

| 5.21 | IR: primary to secondary                                                        |

| 5.22 | IR: primary to ground                                                           |

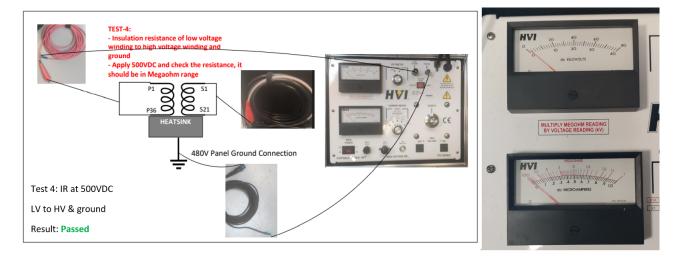

| 5.23 | IR: secondary to primary and ground                                             |

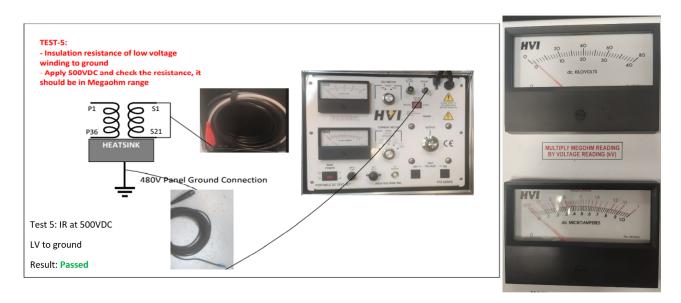

| 5.24 | IR: secondary to ground                                                         |

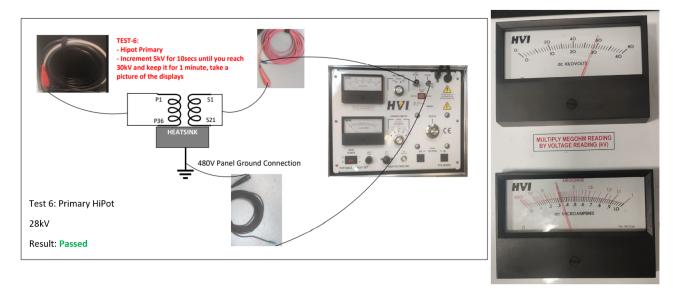

| 5.25 | Primary HiPot test                                                              |

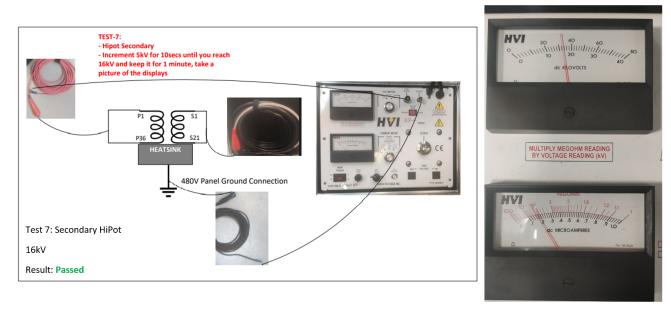

| 5.26 | Secondary HiPot test |   |   |   |   |   |   |   |   |  |   |   |   |   |   |   |  |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 19 | )4 |

|------|----------------------|---|---|---|---|---|---|---|---|--|---|---|---|---|---|---|--|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----|----|

| — -  |                      | - | - | - | - | - | - | - | - |  | - | - | - | - | - | - |  | - | - | - | - | - | - | - | - | - | - | - | - | - | - |    |    |

## LIST OF TABLES

| 2.1 | Comparison of Different Soft-Switching Solutions                                |

|-----|---------------------------------------------------------------------------------|

| 2.2 | Performance Comparison of Four SST Topologies                                   |

| 3.1 | Switching states in a 3L-NPC leg                                                |

| 3.2 | Calculated conduction and switching losses                                      |

| 3.3 | Insulation Distance and Parasitic Distance at Typical Voltage Level 94          |

| 3.4 | Working Voltage, Clearance, and Creepage Distances                              |

| 4.1 | Magnetic Material Characteristics                                               |

| 4.2 | Magnetic Material Characteristics                                               |

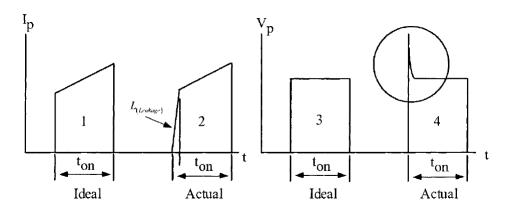

| 4.3 | Litz cables characteristics                                                     |

| 4.4 | Primary and Secondary Cables Parameters Summary                                 |

| 4.5 | Dielectric insulation levels for dry-type transformers used on systems with BIL |

|     | ratings 350kV BIL and below                                                     |

| 4.6 | 3M TufQUIN TF 5+14 Duplex Electrical Insulating Paper                           |

| 4.7 | Heat Transfer Coefficients (h)                                                  |

| 4.8 | Coolant Properties of Oil (T = Temperature [C])                                 |

# LIST OF TERMS AND ABBREVIATIONS

| <b>AFE</b> Active Front End                                     |

|-----------------------------------------------------------------|

| BIL Basic Impulse Lightning                                     |

| CHB Cascaded H-Bridge                                           |

| <b>CM</b> Common Mode                                           |

| CTI Comparative Tracking Index                                  |

| <b>DAB</b> Dual Active Bridge                                   |

| <b>DBC</b> Direct Bonded Copper                                 |

| <b>DESD</b> Distributed Energy Storage Devices                  |

| <b>DM</b> Differential-Mode                                     |

| <b>DPS</b> Dual Phase Shift                                     |

| <b>DPT</b> Double Pulse Test                                    |

| <b>DRER</b> Distributed Renewable Energy Resources              |

| <b>DVC</b> Decisive Voltage Classification                      |

| <b>DVR</b> Dynamic Voltage Restorer                             |

| <b>EEL</b> Equivalent Elliptical Loop                           |

| <b>EMC</b> Electromagnetic Compatibility                        |

| <b>EPRI</b> Electric Power Research Institute                   |

| <b>EPS</b> Extended Phase Shift                                 |

| <b>FACTS</b> Flexible AC Transmission System                    |

| FB Full Bridge                                                  |

| FC Flying Capacitor                                             |

| <b>FEM</b> Finite Element Method                                |

| FREEDM Future Renewable Electric Energy Delivery and Management |

| FWC Flux Waveform Coefficient                                   |

| <b>GSE</b> Generalized Steinmetz Equation                       |

| GTO Gate Turn-off Thyristor                  |

|----------------------------------------------|

| <b>HEV</b> Hybrid Electrical Vehicle         |

| <b>HFL</b> High Frequency Link               |

| <b>HV</b> High Voltage                       |

| <b>HVDC</b> High Voltage Direct Current      |

| IBDC Isolated Bi-directional DC-DC Converter |

| IGCT Integrated Gate-Commutated Thyristors   |

| iGSE improved Generalized Steinmetz Equation |

| <b>KBM</b> Krylov Bogoliubov Mitropolsky     |

| LFT Low Frequency Transformer                |

| LISN Line Impedance Stabilization Network    |

| <b>LV</b> Low Voltage                        |

| MF Medium Frequency                          |

| MFT Medium Frequency Transformer             |

| <b>MM</b> Mixed-Mode                         |

| MSE Modified Steinmetz Equation              |

| MV Medium Voltage                            |

| NPC Neutral Point Clamped                    |

| <b>OSE</b> Original Steinmetz Equation       |

| <b>OVC</b> Over Voltage Category             |

| PD Partial Discharge                         |

| PE Power Electronic                          |

| PI Proportional-Integral                     |

| PLD Pollution Degree                         |

| PR Proportional-Resonant                     |

| <b>PWM</b> Pulse Width Modulation            |

| RMS Root Mean Square                         |

| S-DAB Semi-Dual Active Bridge                                         |

|-----------------------------------------------------------------------|

| SiC Silicon Carbide                                                   |

| <b>SiC-JFET</b> Silicon Carbide Junction Gate Field-Effect Transistor |

| SMC Sliding Mode Control                                              |

| SMPS Switch Mode Power Supply                                         |

| SOA Safe Operating Area                                               |

| SPS Single Phase Shift                                                |

| SRC Series Resonant Converter                                         |

| SST Solid State Transformer                                           |

| STATCOM Static Synchronous Compensator                                |

| SVC Static Var Compensator                                            |

| <b>THD</b> Total Harmonic Distortion                                  |

| <b>TPS</b> Triple Phase Shift                                         |

| UNIFLEX Universal and Flexible                                        |

| UPQC Unified Power Quality Conditioner                                |

| <b>UPS</b> Uninterruptible Power Supply                               |

| WBG Wide Band-gap                                                     |

| WCSE Waveform Coefficient Steinmetz Equation                          |

| <b>ZCS</b> Zero Current Switching                                     |

| <b>ZVS</b> Zero Voltage Switching                                     |

#### **ACKNOWLEDGEMENTS**

I would like to thank God first and foremost for being able to conduct this research and writing this dissertation. A special thanks go to my family and friends who encouraged and supported me for the past six years of my graduate studies. I would like to convey my appreciation and gratefulness to my advisor Professor Adel Nasiri and my co-advisor Professor Robert Cuzner for their support and the knowledge they passed down throughout this journey. This work is funded by GRAPES NSF I/UCRC, I would like to thank the academic and corporate members of GRAPES for their support. I would like to pass my sincere gratitude to all of my Professors and colleagues at the University of Wisconsin Milwaukee CSEES center, University of South Carolina, Gazi University, Imagen Energy LLC, Eaton Corporation, and Leonardo DRS teams.

#### **CHAPTER 1**

#### Introduction

#### 1.1 Trends and Motivations

Some define a smart grid as an "electric grid using digital technologies". "Smart grids" are a relatively broad concept with several definitions. A smart meter allows two-way communication between a utility and its customers (bi-directional smart metering), and a variable electricity rate based on demand during the day. In addition to the self-healing capabilities of power grids, another definition of a smart grid is the ability of power grids to recover from faults in transmission lines and substations by utilizing distributed sensors and automatic controllers. As a result of incorporating Future Renewable Electric Energy Delivery and Management (FREEDM) into the smart grid, the concept has broadened and includes the deeper penetration of distributed renewable electric power generation, as well as greater interaction between utility services and consumers [1] - [2].

Energy routers provide direct control of power flows, facilitating bi-directional power flow and the sale of electric energy back to the utility. Additionally, the energy router provides additional features to the distribution power system, including power factor correction, fault current limits, and ride-through capability for sags and swells. A distributed communication and control protocol enables utilities and consumers to communicate more effectively beyond two-way communication through smart meters. All of these characteristics will contribute to improved

power quality at the distribution level. It is the supervisor and controller of the distribution system, enabling management and ensuring optimal power generation and distribution. In the current state of technology, it is not possible to create a device that performs all the functions discussed above in an energy router. In addition, conventional passive transformers are unable to control power flow; switched capacitor banks and Static Var Compensator (SVC) are merely reactive power compensators. The concept of SST was introduced to fill the void that was left by the Unified Power Quality Conditioner (UPQC) of offering power factor correction and harmonic compensation. However, none of these devices have the functionality of a router. This is where the concept of SST is introduced. An SST is a high-speed switching frequency power electronic converter that has the following functionalities: provides galvanic isolation between the input and output, and provides active power control in both directions. It also provides ports or interfaces for connecting distributed power generators or energy storage devices and compensates for power grid disturbances, including variations in input voltage, and short-term sags or swells.

An SST serves as a buffer between the power grid, loads, distributed energy sources, and energy storage devices in the FREEDM system as a whole. As a result of decoupling the load from the source, consumers would not be affected by grid disturbances since the SSTs compensate for the disturbance. Moreover, since the SSTs compensate for reactive power generated by loads, the power grid would not observe it. This is one of the advantages of SSTs. One of the benefits of SSTs for the power grid is their ability to enhance the efficiency and stability of the distribution system. Besides serving as buffers for renewable energy sources, SSTs minimize the impact of unpredictable and unschedulable fluctuations on power grids and loads that result from renewable energy sources. SSTs offer this advantage for the generation of renewable energy [3].

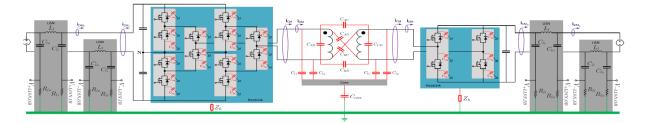

As an interface between the inherently fluctuating power sources and the grid, power conversion systems based on Medium Frequency (MF) DC-DC converter isolated with Medium Frequency Transformer (MFT) shown in Fig.1.1 are becoming more and more significant. Compared with conventional LFTs, MF power conversion systems operating at the kilo-hertz range feature significant reduction of weight and size, dynamic control of power flow, and enhanced power quality. Such a compact system is also attractive for railway applications where space is limited [4].

Fig. 1.1 Medium frequency power conversion system

With the proliferation of power electronic semiconductor switches for high-power SST applications, the notion of substituting the traditional LFT in MV distribution grids (e.g all-DC offshore wind farms) and onboard traction applications with the system consisting of much smaller and lighter MFTs driven by power electronic converters, namely the SST, has been gaining popularity [5]. One major application that is seeking MV SST deployment is data centers. Due to the increasing use of cloud computing and big data, the power consumption of data centers alone reached 10% of the total electrical power consumption in the world by the year 2020. Considering the booming data center industry, the high copper cost and conduction

loss associated with low voltage (480Vac) power distribution outside the server hall need to be addressed. Despite increased global research effort [6], SST is still at a level of advanced academic and industry prototypes.

The LFT has been one of the most widely used technologies in electrical engineering for many years, however high-power, high-voltage MFT has not yet reached a mature and standardized state. In terms of electromagnetic modeling, insulation coordination, electrical parameter control, thermal coordination, and overall design optimization, numerous areas need to be investigated. In the documented research on modeling and design optimization of the MFT [6] - [8], the design considerations tied to the proper insulation coordination are usually neglected and there is no information about any insulation testing (e.g. Partial Discharge (PD) and Basic Impulse Lightning (BIL)). Furthermore, besides the discussion, selection and application of the available analytical sub-system models (e.g. leakage inductance [9], core [10] - [12], and winding losses [13] - [22]), from the often quite old literature, there has not been many efforts directed into improving the accuracy and precision of these estimations [23].

Over the past decade, there has been a great deal of attention given to moving towards higher power densities in power conversion units, especially in applications that are highly restricted, such as remote offshore wind farms and traction systems [24] - [25]. Increasing the operational frequency is the most common solution to achieve higher power densities, since the weight and volume of the magnetic part, perhaps the bulkiest element in power electronic converters, are then decreased [8]. In low-power and high-frequency applications, this solution is well established, but in recent years, there has been considerable interest in utilizing high-frequency at higher power and voltage levels. In addition, power electronic interfaces are used in smart grids as well as traction converter systems, which require full control of the power flow and high power density [26] - [27]. Due to the increased isolation requirements and

thermal stress that result from reduced size, MFTs become more challenging to design [4]. As a result of electrical, magnetic, dielectric, and thermal performance limits encountered in the system, a high-power, high-voltage MFT presents multiple technical challenges. Moreover, the outcome of a generic multi-objective optimization depends on how well the models used are selected. Furthermore, various technological choices need to be carefully selected before being incorporated. Therefore, all relevant phenomena within the physical subsystems of this complex multi-physical system must be modeled as accurately as possible to understand their impact on the given application. For resonant converters, electric parameters must be controlled precisely since the transformer is part of a resonant circuit. In addition, there is still much discussion and citation about the issue of correct insulation and thermal coordination, as well as choosing the technologies involved in transformer design [23].

For high-power applications, the DC-DC converters are usually cascaded and connected to the MV grid. The design challenges are mainly high efficiency, thermal management, and high voltage insulation due to the reduced size and higher frequency. Previous research focusing on MFT design has been reported in [28] - [29] for traction applications and in [30] - [31] for renewable energy and smart grid applications. Although transformer design and optimization are widely discussed in numerous publications, the detailed design and optimization procedure for MFT can be found only in a few recent publications. In [32], a design methodology for MFT based on amorphous alloy is proposed, a simplified thermal model is used and the heat dissipation capability is considered for optimization. In [33], different core materials are considered and temperature calculation is included in the optimization process. However, as simplified thermal models for windings are employed in these studies, the heat transfer between different layers of windings is not included and the electric field distribution which is essential for insulation design is also not included in the optimization procedure [4].

Operating higher up in frequency is the most common solution to achieve higher power density. This is because the weight and volume of the magnetic part, the bulkiest element in power electronics converters, is decreased. However, on the other hand, it will lead to increased loss density due to enhanced core loss and more importantly enhanced winding loss [34] - [35]. One of the potential applications of the high-power MFT is high-power isolated DC-DC converters for wind energy DC collection and transmission grids. This could lead to a significant weight and size reduction, which is of a particular value for offshore wind installations as stated in [30], in which a 3MW, 500Hz transformer is shown to be more than three times lighter than the equivalent 50Hz one. Most of the classical attempts for high-power MFT designs were focused on a parameter called area product whereby the power handling capability of the core is determined [36]. Petkov in [37] presented a more detailed design and optimization procedure of high power high frequency transformers. Some years later, another work reported a similar approach accounting for non-sinusoidal excitations. However, parasitics are essentially ignored in both approaches [38].

It is important to consider the effects of high power, high voltage, and high frequency. This is because the technology in this area has not yet advanced to a mature level. These challenges essentially originate from the basic requirements of SSTs, i.e., simultaneous fulfillment of high power, high voltage, and high-frequency requirements [8].

#### 1.2 Research Objectives and Contributions

Typical LFTs are used for electrical isolation between systems as well as to fulfill the voltage-matching requirement. However, the 50/60Hz transformers are bulky and large in size and weight [39]. Through the use of power electronic converters, the gap between the old power system and the proposed microgrid concept will be minimized. The SST idea was born for this application. It is defined as a high/medium frequency transformer implemented with a power converter. In contrast to traditional LFTs, this will have a direct impact on the size, compactness, and power density. Recent developments in advanced magnetic materials with low power loss and high saturation flux density as well as high power-high frequency switching devices have made it possible to design high-efficiency high power density SSTs [40] - [43].

SSTs represent a suitable candidate for DC-DC converters in DC grid applications, such as future offshore wind farms collection networks [39] - [44]. SSTs also allow better efficiency and a lower weight, which can be very useful for offshore applications. The gain in performance obtained by the use of SSTs is mainly due to the possibility of increasing semiconductor density, which allows using MFTs which are more compact and more efficient than the traditional 50-60Hz transformers [45]. However, high power high voltage applications combine electromagnetic, insulation, electrical, and cooling constraints on the MFT. Therefore, the MFT design must take into account all of these specifications, which represent a multi-objective optimization process [41], [46].

As a novelty, this work presents an integrated multi-physics design that covers all aspects of a medium voltage medium frequency high power SST, including power converter and transformer electromagnetics, insulation, EMI, and thermal analyses. The research will include numerical Finite Element Method (FEM) validation of the selected design utilizing novel hands-

on experience in terms of electromagnetic/power-electronic transient co-simulation, electrostatic, EMI, and thermal simulations. A special focus is also placed on the development of a 700kW, 13/7.2kV, 20kHz transformer. To the author's knowledge, this transformer is the highest-designed, prototyped, and tested transformer out there. Experimental validation of the transformer was performed after a prototype transformer was built.

#### 1.3 Dissertation Organization

This dissertation will be presented in the following format:

The first chapter discusses the trends that led to this work and the motivation for it, as well as the challenges and opportunities involved in fully implementing a medium voltage medium frequency high power solid state transformer.

The second chapter provides an overview of DC-DC converters, with a focus on dual active bridge topology, as well as the difficulties and current state of the art in terms of power and voltage levels for its transformer design.

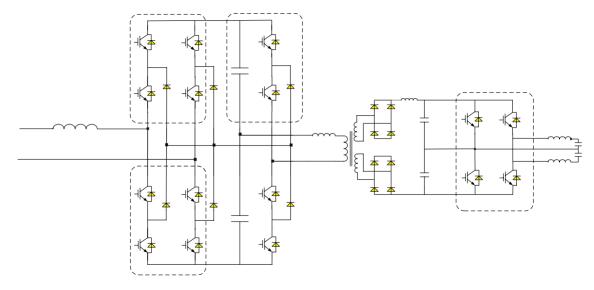

The third chapter delves deeper into the ANPC-2L topology chosen for this study, from which the voltages and currents are calculated. A thermal analysis is also presented, as well as the use of HV SiC power modules and the coordination of insulation between the various DAB power converter components.

The fourth chapter of this thesis discusses the electromagnetic, thermal, electromagnetic interference (EMI), and overall parameter optimization and compilation aspects of the transformer's multi-physics design.

The fifth chapter presents Ansys FEA electromagnetic, electrostatic, and thermal simulations, as well as PLECS/Simulink for EMI results. The transformer prototype's construction is discussed, and the experimental findings obtained thus far on the transformer are broken down and clarified.

Finally, the sixth chapter is where the conclusions drawn from the research work developed in this dissertation are gathered, as well as areas for further research are proposed.

#### **CHAPTER 2**

#### **DC-DC Converters**

#### 2.1 Overview

The dependence and use of electronic devices in our daily lives has grown exponentially over the past few years. Since the majority of these devices are battery-operated, different levels of DC voltages are required to meet their unique requirements. The use of DC-DC converters allows for these different voltage levels [47] - [48]. DC-DC converters take DC voltage at the input and step it up or down at the output according to the given requirement. Small electronic devices requiring few volts to very high voltage levels (i.e., transmission lines) can all be powered by DC-DC converters. Regulated Switch Mode Power Supply (SMPS) and DC motor drive applications both widely use DC-DC converters. It uses very high-frequency switches, such as MOSFET, that is controlled by a microprocessor to regulate the duty cycle of the switches. In essence, the duty cycle determines the feature of stepping up or down the output DC voltage. It can control whether the converter steps up or down as well as how much the output of the converter steps up or down [49] - [51].

Distribution using DC level is becoming more and more enticing as renewable energy generation is integrated into power grids on a larger scale. For instance, because no reactive power is generated or consumed by the transmission cable, DC transmission is more efficient than AC transmission. This is similar to installing wind farms offshore. Additionally, a significant

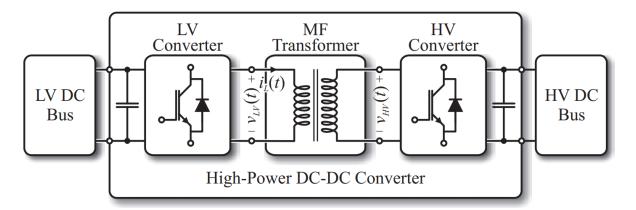

reduction in weight/volume and consequently installation costs could be achieved by substituting the massive 50/60Hz transformers with higher-frequency transformers. This new concept has been evaluated in [52], where high power DC-DC converters in the MW range are required to interface different voltage levels within the wind farm. This novel idea has been evaluated in [52], where different voltage levels within the wind farm are interfaced with high power DC-DC converters in the MW range. On the other hand, the generation of energy using renewable resources is extremely susceptible to changes in the natural conditions [53]. For instance, photovoltaic panels can only produce energy during the day, so they must be combined with sizable storage systems to produce the necessary energy when there is insufficient sunlight. Here, a high-power bidirectional DC-DC converter that can dynamically control the power within the system and to the power grid is required to connect the photovoltaic generators with their respective storage systems. High-power DC-DC converters are, as can be seen, key technologies for this upcoming power generation scene [24]. A schematic representation of a high-power DC-DC converter interfacing two voltage levels, i.e. Low Voltage (LV) and High Voltage (HV), is shown in Fig. 2.1.

Fig. 2.1 DC-DC converter interfacing two DC grids with different voltage levels

Providing step-up/down in voltage levels and ensuring electrical isolation between LV and HV sides, which must adhere to international standards [54], are the main duties of the MFT,

which are essentially the same as with 50/60Hz transformers. In this MFT, the excitation frequency offered by the power electronic components is several times higher than in conventional 50/60Hz systems, resulting in a significant reduction in the transformer's overall size and weight. In Fig.2.2, a map of transformer designs from various research groups, along with their operating frequencies and achieved volumes is shown. Here, with higher operating frequencies, a significant volume reduction is noticeable where the break in the fitted line is given by a change in the utilized core material [33].

**Fig. 2.2** Volume reached by different transformer designs with different operating frequencies (all scaled to 1 MW power rating)

The below subsections briefly discuss two properties of DC-DC converters namely: hard/soft switching and unidirectional/bidirectional power flow.

#### 2.1.1 Hard switching/Soft switching

Switching based on the relationship between current and voltage is referred to as hard switching and soft switching. Hard switching is a simple method to accomplish this. It is the method

where the transistor is turned on or off by increasing the current or voltage to enable the state change. Switching loss, which is caused by the non-instantaneous transition time in transistors, is a major drawback of this method. It occurs when the voltage and current intersect. As a result, as switching frequency increases, switching loss also increases. However, high switching frequency is required to reduce the circuit size. In contrast, soft switching converters significantly reduces switching loss [55] - [57]. This is achieved due to the LC resonant circuit, which allows the device to turn on or off at zero current (Zero Current Switching (ZCS)) or voltage (Zero Voltage Switching (ZVS)). As a result, DC-DC converters can be operated at high switching frequency without experiencing significant switching loss [58] - [60].

#### 2.1.2 Unidirectional/Bidirectional

The main purpose of fundamental DC-DC converters is to provide a unidirectional power supply to the load [47] - [61]. Due to the use of unidirectional components like a diode, the power flow is unidirectional. However, by implementing current bidirectional switches, such converters can be converted into bidirectional converters [62]. A schematic of a bidirectional DC-DC converter is shown in Fig. 2.3 [49].

Fig. 2.3 Bidirectional DC-DC converter

#### 2.2 Dual Active Bridge

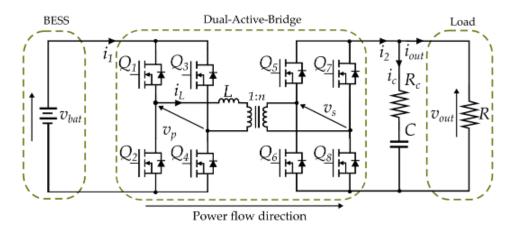

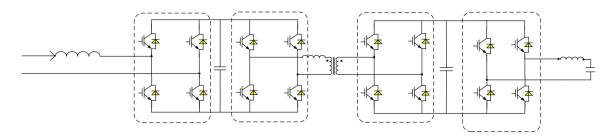

One enticing type of DC-DC converters is Dual Active Bridge (DAB). The isolated bidirectional DAB DC-DC converters illustrated in Fig. 2.4 have many benefits over conventional DC-DC converter circuits, such as electrical isolation, high reliability, easiness in realizing soft-switching control, and bidirectional energy flow [63].

Fig. 2.4 Electrical systems in a series Hybrid Electrical Vehicle (HEV)

A DAB converter is a high-power, high-power-density, and high-efficiency power converter with galvanic isolation. One high-frequency transformer and two active power switching H-bridges make up the converter. The high-frequency transformer provides both galvanic isolation and energy storage in its winding leakage inductance. The phase shift between the two H-bridges regulates the amount and direction of power flow and the two H-bridges typically operate at a fixed 50% duty ratio. There are DC-DC DAB converters and AC-AC DAB converters based on the configuration of switching devices.

Bidirectional isolated DC-DC DAB converters were initially proposed as candidates for high power density and high-power DC-DC converters. ZVS, bi-directional power flow, and lower component stresses contribute to making the DAB topology desirable. Two H-bridges and one high frequency transformer constitute a DAB converter. The input voltage is converted

by one of the H-bridges into an intermediate high-frequency AC voltage, while the other Hbridge converts the high-frequency square wave AC voltage back to the output voltage. A high frequency transformer is used in conjunction with high-frequency switching devices because they reduce the weight and volume of passive magnetic devices. The primary and secondary windings of the high-frequency transformer have some leakage inductance in addition to galvanic isolation, which together function as an energy storage component. Additionally, the leakage inductance enables achieving soft switching. During switching transients, transformer current resonates with the capacitors in parallel with switching devices, limiting the dv/dt and di/dt across the switches. Soft switching contributes to higher power efficiency and the reduction of switching loss. DAB converters, in contrast to other isolated DC-DC converters using asymmetrical topologies, have symmetrical circuit configuration that enables the bi-directional power flow required for SSTs. Varying the phase shift between those two bridges, the power flow of a DAB converter can be controlled. The voltage across the transformer leakage inductance is altered by such phase shift. In this manner, both the amount of power transferred and direction of power flow are controlled. Power is transferred from the leading bridge to the lagging bridge [3].

#### 2.2.1 Applications

The DAB DC-DC converter has been utilized in battery application systems, such as Uninterruptible Power Supply (UPS), auxiliary power supplies for electric or hybrid vehicles, battery management systems, microgrids, and energy storage systems. Research literature for instance examines multiple DAB applications such as offline UPS design based on the DAB topology, control of the bidirectional energy transfer between an energy storage system and a DC power system, and being a crucial element for automotive applications. DAB converters are also recognized as the central component of the power electronic converter system that links a renewable energy source and an AC power system. Multiple input/output ports are now enabled by the expanded topology of DAB converters [3]. The application of DAB converters in high power renewable power generation is detailed in [64].

#### 2.2.2 Principle of Operation

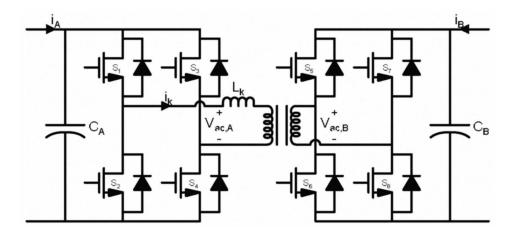

A high-frequency transformer is included in the conventional Full Bridge (FB) based Isolated Bi-directional DC-DC Converter (IBDC) (Fig. 2.5) and is primarily used to maintain galvanic isolation between the input and output terminals. For this converter, the input and output voltages are  $V_A$  and  $V_B$ , respectively. In addition, n is the transformer turns ratio, the phase shift between the two AC voltages ( $V_{ac,A}$  and  $V_{ac,B}$ ) is  $\phi$ , and the sum of the primary-referred leakage inductance and an optional external inductor is represented by  $L_k$ .

Fig. 2.5 Conventional full bridge based isolated bidirectional DC-DC converters

In Fig. 2.6, the main waveforms of this converter are displayed. Each bridge in this converter produces a square-wave voltage. To regulate the amount of power flowing through the inductor  $L_k$ , the two voltages  $(V_{ac,A})$  and  $(V_{ac,B})$  are phase-shifted with respect to one another

at an angle of  $\phi$ . The average of transferred power can be expressed as:

$$P = \frac{V_A V_B}{nww_k} \phi (1 - \frac{\phi}{\pi}) \tag{2.1}$$

Proper timing control of the converter switches enables leading or lagging phase shift (to transfer power from A to B or B to A, respectively). The DC voltage conversion ratio, defined as  $d=\frac{V_B}{nV_A}$ , determines the soft-switching range. The soft-switching may be lost if the input voltage varies widely. When d>1, side-A can experience hard switching.

Fig. 2.6 Key waveforms of conventional FB BOC: (a) A-to-B mode, (b) B-to-A mode

Under idealized conditions, the soft-switching operation range is as:

$$|\phi| > \frac{\pi}{2} (1 - \frac{1}{d}) \tag{2.2}$$

For side-B, hard-switching can be occurred when d < 1 and the soft-switching operation range

is as:

$$|\phi| > \frac{\pi}{2}(1 - d) \tag{2.3}$$

Full control range under soft-switching is achievable for d = 1 [65].

#### 2.2.3 Modeling of DAB

Good plant models are necessary for a good DAB controller design. Due to its switching nature, a high switching frequency power converter is essentially a nonlinear and time-varying system. However, a linear and time-invariant plant is more desired by the majority of control methodologies. In order to provide a linear and time-invariant approximation of the relevant power converter, various modeling techniques have been proposed to approximate the non-linearity and time-varying behaviors of a power converter. State-space averaging is one modeling method that is commonly applied. This traditional method makes the assumptions that the switching frequency is significantly higher than the frequencies of interest and that the state variables' ripples (such as inductor current and capacitor voltage) are sufficiently small. It eliminates all quadratic terms, produces a time-invariant model, and approximates the matrix exponentials in the solution of the power converter state equations using only linear and bilinear terms. A linear, time-invariant small-signal model is produced by further linearizing this model around a steady-state operating point. The DC terms in the Fourier series of state variables are essentially accounted for in state-space averaging. Generalized state space averaging is another averaging method that preserves more terms in the Fourier series of state variables (normally the switching frequency terms). The fact that generalized averaging does not assume that state variable ripples are small is one of its advantages. This method could produce more accurate models while discarding less data. The Krylov Bogoliubov Mitropolsky (KBM) averaging method is another averaging method along with generalized averaging. The KBM

method approximates converter state variables using piecewise-polynomial equations rather than applying Fourier series of state variables. This will include the effect of ripples brought on by switching. The KBM method is simpler than generalized averaging and does not require small ripples either. When modeling pure AC state variables, KBM method might not be as helpful as generalized averaging. All three of the aforementioned modeling methods operate in the continuous-time domain. On the other hand, sampled-data models are in the discrete-time domain. A sampled-data model makes use of the fact that power converter state variables have cycle-by-cycle repeatable trajectories in steady state. It is frequently derived by integrating the switched piecewise linear differential equations of the state variables over a single control cycle. Given a set of initial conditions, the integration entails multiplying and integrating exponentials in order to solve the state equations. The Taylor series expansion is a common method for simulating this process. Like other power converter controller designs, the DAB converter controller design also needs an average model of DAB converters.

There are two different ways to model a DAB converter: (1) a simplified reduced-order model that ignores the dynamic of the transformer current, and (2) a full-order discrete time model that maintains the dynamic of the transformer current. One method to model those converters with high variation and resonant operations is discrete-time modeling. However, because it offers more physical insight and makes control design easier, a continuous-time model is typically preferred. Negligible current ripple is required by the standard state-space averaging method for DC-DC converters. The transformer current of a DAB converter is entirely AC, so this condition is not met by DAB converters. Instead, the effect of pure AC current on converter dynamics can be captured using the generalized averaging method, which employs more terms in the Fourier series of state variables. By choosing the appropriate converter parameters, it is generally recommended to separate the dynamics of current and voltage in a

DC-DC converter design. The previously mentioned simplified reduced order model assumes that the output capacitor voltage dynamics are significantly slower than those of the transformer current. This presumption hasn't been analytically verified, though. The conditions for the separation of the dynamics are provided by singular perturbation theory, along with an analytical method for doing so. In the literature, [3] reports the time-scale separation criteria for state variables in DC-DC boost converters.

### 2.2.4 Switching and Modulation Techniques

Researchers work to advance DAB modulation techniques. For DAB converters, dual phase-shift modulation has been suggested to reduce reactive power and loss. Hybrid modulation methods have been developed to increase soft-switching range. To increase the degree of control freedom, phase shift modulation and duty-ratio control have been applied to DAB converters. In the literature, various modulation techniques are analyzed and compared. To decrease switching loss and boost DAB converter efficiency, new switching strategies are presented. In order to address some of the parasitic and nonlinear effects of DAB converters, more detailed circuit models are created and analyzed. Several circuit design optimizations are published, and some published works concentrate on efficiency evaluation of DAB converters [3] in which one of the key areas of research for DAB-IBDC is control strategy.

In the following section, control methods which are the most widely researched methods for DAB-IBDC will be introduced and analyzed. To achieve improved topologies and variant, the control techniques may differ; however, all of these methods can be derived from the following ones [66]:

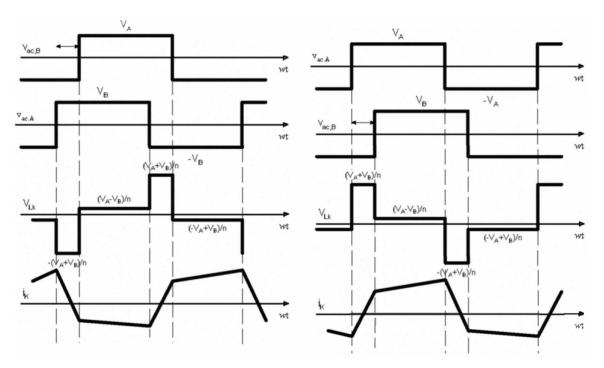

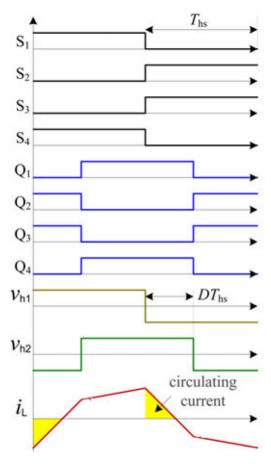

## 2.2.4.1 Single Phase Shift Control

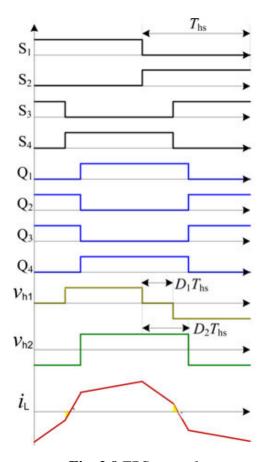

The most widely used control method for DAB-IBDC is Single Phase Shift (SPS) control which is shown in Fig. 2.7.  $S_1$  –  $S_4$  and  $Q_1$  –  $Q_4$  are square-wave gate signals with 50% duty ratio for the corresponding switches in Fig. 2.8.  $v_{h1}$  and  $v_{h2}$  are the equivalent AC output voltages of full-bridges  $H_1$  and  $H_2$ , respectively, and  $i_L$  is the current of inductor L. Crossconnected switch pairs in both full bridges are switched in-turn during SPS control to produce phase-shifted square waves with a 50% duty ratio for the primary and secondary sides of the transformer. It is only possible to control the phase-shift ratio (or angle) D. The voltage across the leakage inductor of the transformer can be altered by adjusting the phase-shift ratio between  $v_{h1}$  and  $v_{h2}$ . Thus, the power flow's magnitude and direction can then be easily controlled. SPS control is becoming more popular as a result of its benefits, including its low inertia, high dynamic, and ease of realizing soft-switching control. However, in this method, the control of the power flow is dependent on the transformer's leakage inductor, which causes significant circulating power when the voltage amplitude of the transformer's two sides is not matched. As a result, both the peak current and Root Mean Square (RMS) increase. Additionally, in this scenario, the converter is unable to operate under ZVS in the whole power range. As a result, the efficiency is considerably reduced, and the power loss increased [66].

Fig. 2.7 SPS control

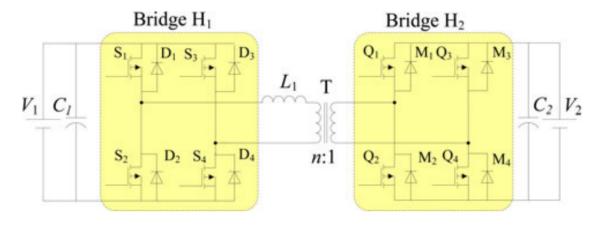

Fig. 2.8 Topology of DAB-IBDC

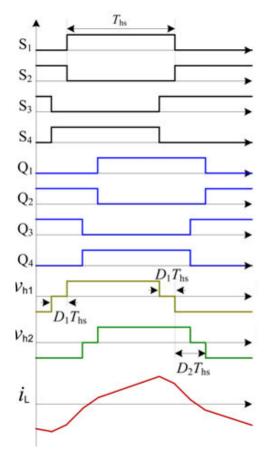

## 2.2.4.2 Extended Phase Shift Control

An improved method of SPS control is Extended Phase Shift (EPS) control, as shown in Fig. 2.9. Switch pairs in one bridge that are cross-connected are switched in-turn during EPS con-

trol, whereas switch pairs in the other bridge are switched with an inner phase-shift ratio. After that, one bridge's output AC voltage changes to a three-level wave, while the other produces a two-level 50% square wave. Since the backflow power is zero when the three-level wave's zero voltage occurs, the circulating power drops for a given transmission power. In the literature, it is discussed how the EPS control works and how well transmission power, current stress, power loss, and soft switching perform. In comparison to SPS control, EPS control increases regulating flexibility and efficiency while also reducing current stress and expanding the ZVS operation range. In contrast to the single phase shift ratio D in the SPS control, the EPS control has two phase shift ratios: an inner phase shift ratio  $D_2$  and an outer phase shift ratio  $D_1$ . The inner phase-shift ratio is used to reduce circulating power and increase ZVS range, whereas the outer phase-shift ratio is used to control the power flow direction and magnitude.

Fig. 2.9 EPS control

However, in order to achieve the decreased circulating power for the EPS control [66], the operating states of the two bridges must be switched. The switching occurs when the voltage conversion states are switched between the boost and buck states and the power flow directions are switched between the forward and reverse power flow.

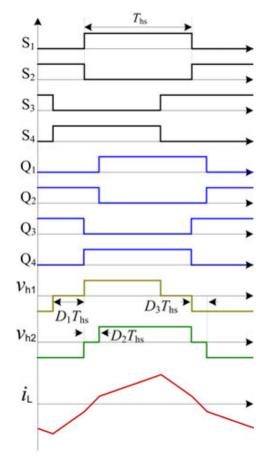

#### 2.2.4.3 Dual Phase Shift Control

Similar to the EPS control, the Dual Phase Shift (DPS) control was proposed as shown in Fig. 2.10. In contrast to EPS control, the cross-connected switch pairs in both full bridges in DPS control are switched using an inner phase-shift ratio, and the inner phase-shift ratios are identical. After that, both bridges' output AC voltages are three-level waves. Other research works included extensive information about the operation principle, transmission power, current stress, power loss, soft switching, and optimization design methods for the DPS control. When compared to SPS control, DPS control can reduce output capacitance and steady-state current, increase efficiency, and extend the ZVS operation range. Dead-band compensation can be easily implemented in the DPS control even if there is no current sensor, depending on the operating circumstances. When the states of voltage conversion or the direction of power flow are altered, the operating states of the two bridges will remain the same in comparison to the EPS control. Hence, DPS control is simpler to implement and may have better dynamic performance [66].

Fig. 2.10 DPS control

## 2.2.4.4 Triple Phase Shift Control

Researchers proposed the Triple Phase Shift (TPS) control, as shown in Fig. 2.11. Similar to the DPS control, The cross-connected switch pairs in both full bridges are switched with an inner phase-shift ratio. The inner phase-shift ratios, however, might not be equal. TPS control can also control three degrees of freedom. As a result, research on TPS control mainly focuses on the optimization operation field. Small signal model for digital control of DAB-IBDC with TPS control was studied in research literature. For DAB-IBDC with TPS control, an optimal modulation scheme that enables minimum copper losses and conduction was presented. Based on this, a design method and efficiency-optimized modulation scheme were created for an existing DAB-IBDC prototype. To increase the power range for ultra-capacitor application,

a hybrid modulation scheme and a feedback-linearized control were developed. In another research, an ideal modulation strategy for TPS control's reverse-mode operation was analyzed. Additionally, a stability analysis technique to improve the systematic and accuracy of DAB-IBDC with TPS control stability determination was discussed. Additionally, a composite TPS control scheme that extends the soft-switching range down to zero-load conditions, lowers RMS and peak currents, and significantly reduces transformer size was explored. This control method used an extensive analysis and experimental verification with Pulse Width Modulation (PWM) control.

In fact, the TPS control—a unified type of phase-shift control—was proposed after SPS, EPS, and DPS controls. SPS, EPS, and DPS control can also be regarded as special cases of TPS control. SPS control only requires one control degree to be implemented, EPS and DPS controls require two control degrees, and TPS control needs three control degrees. TPS control is therefore the most challenging to implement, and there is currently no common implementation standard. When the voltage conversion states or power flow directions change, the operating states of the two bridges for EPS control should also be altered. Additionally, there are problems with the SPS control's effectiveness, ZVS range, etc. Thus, considering both performance and implementation difficulty, DPS control may be a relatively optimal method for the large-scale practical application [66].

Fig. 2.11 TPS control

## 2.2.5 Soft-Switching Operation

DAB-IBDCs transcend other topologies through the easiness of realizing soft switching, their ability to transfer power in both directions, and their modular and symmetric structure. However, when the voltage amplitude of the transformer's two sides doesn't match, the circulating current increases significantly and the efficiency decreases rapidly. Additionally, the soft-switching range decreases under light load. To solve these problems, soft-switching technology is researched to improve the performance, as of now, the main research ideas center on the expansion of the DAB-soft IBDC's switching range through the improvement of the High Frequency Link (HFL) resonant tank. This section gives three typical solutions to discuss the soft-switching solution of DAB IBDC.

LC-type resonant topology based on DAB IBDC is shown in Fig. 2.12. Due to its operational advantages over conventional DAB IBDC, the converter can be operated at higher frequency and with greater efficiency; however, the addition of resonant components increases the converter's size and cost. Phase-shift control with fixed frequency (all switches in both full bridges are driven with 50% duty cycle) serves as the converter's control method, and two AC equivalent (with fundamental component) circuit analysis approaches are used for design purposes. The LC-type resonant DAB IBDC has common features with the conventional series resonant unidirectional full-bridge DC-DC converter and still has some unique features due to the secondary-side bridge, such as the capability of bidirectional power flow. ZVS for primary-side switches and ZCS for secondary-side switches could be accomplished from soft-switching performance.

Fig. 2.12 LC-type resonant DAB-IBDC

Fig. 2.13 shows a CLLC-type asymmetric resonant topology based on DAB IBDC. Both the power flow directions are modulated under variable frequency modulation above resonance. The inverter switches are driven with a 50% duty cycle, and the rectifier switches are driven by the additional resonant signals. Similar to the LC-type converter mentioned above, ZVS for inverter switches and ZCS for rectifier switches could be achieved for a wide variation of voltage gain [66].

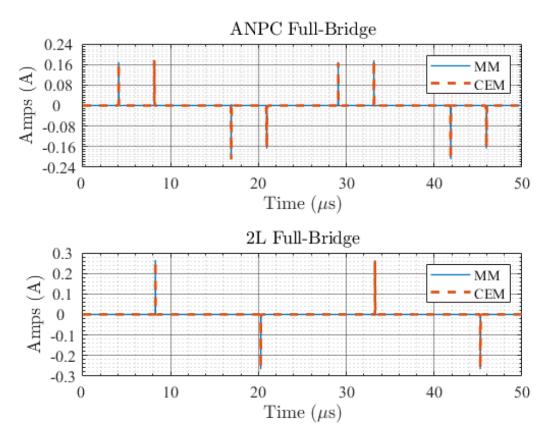

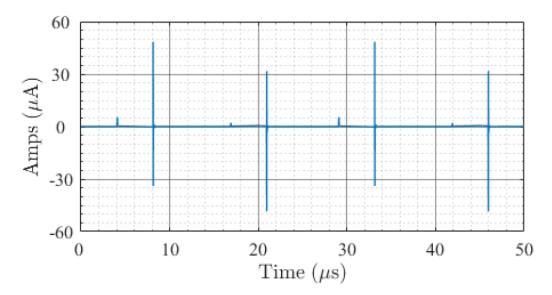

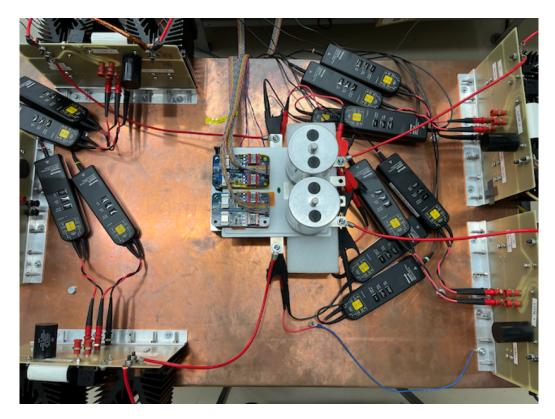

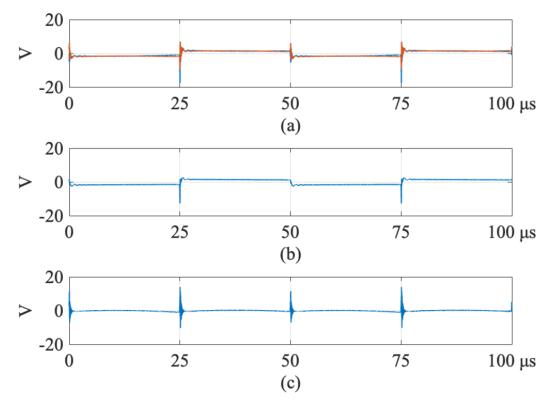

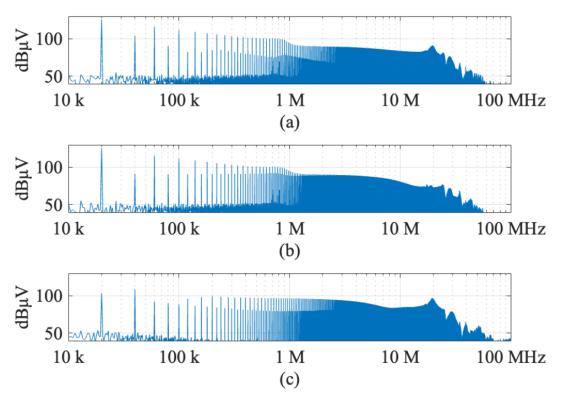

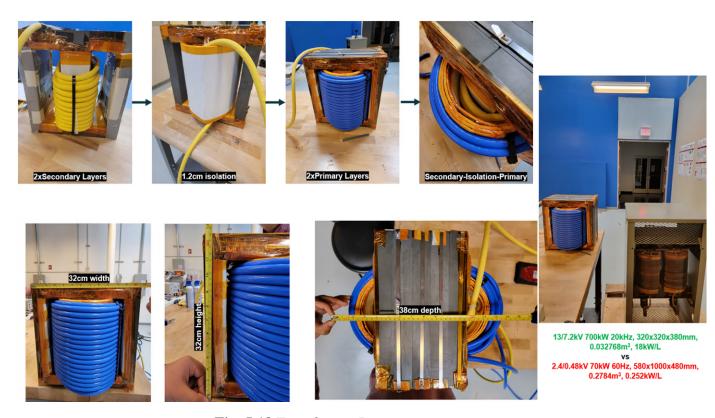

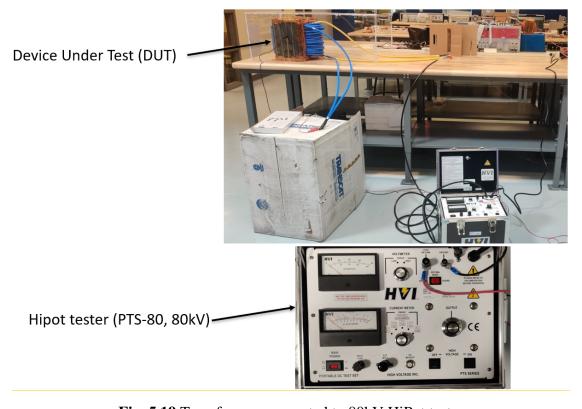

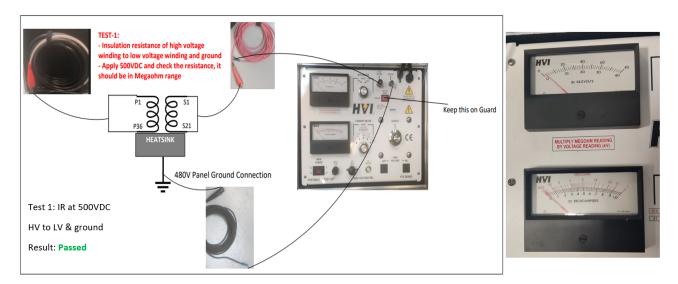

Fig. 2.13 CLLC-type asymmetric resonant DAB-IBDC