# Forensic applications of analog memory: the digital evidence bag

A review of information security and its applications in digital forensics, including the creation of a digital evidence bag by exploiting the properties of analog memory

# Benjamin James Agnew

Bachelor of Engineering (Honours) (Electrical and Electronic) University of Adelaide, 2015

> A thesis presented for the degree of Master of Philosophy in

Electrical and Electronic Engineering University of Adelaide

January 2022

# Contents

| A  | bstra                 | $\mathbf{ct}$ | · · · · · · · · · · · · · · · · · · ·                | v |  |  |

|----|-----------------------|---------------|------------------------------------------------------|---|--|--|

| D  | Declaration           |               |                                                      |   |  |  |

| A  | Acknowledgements viii |               |                                                      |   |  |  |

| Li | ist of                | Figur         | es iz                                                | ĸ |  |  |

| Li | ist of                | Table         | 5 x                                                  | i |  |  |

| 1  | Intr                  | oducti        | on                                                   | 1 |  |  |

|    | 1.1                   | Conte         | xt                                                   | 1 |  |  |

|    | 1.2                   | Aim           |                                                      | 2 |  |  |

|    | 1.3                   | Scope         |                                                      | 2 |  |  |

|    | 1.4                   | Overv         | iew                                                  | 3 |  |  |

| 2  | Dig                   | ital Ev       | idence, Forensics and Investigation                  | 4 |  |  |

|    | 2.1                   | Introd        | uction to Forensics                                  | 4 |  |  |

|    |                       | 2.1.1         | Relevance of the storage medium                      | 5 |  |  |

|    |                       | 2.1.2         | Evidence integrity and chain of custody              | 5 |  |  |

|    | 2.2                   | The fo        | rensic process                                       | 5 |  |  |

|    |                       | 2.2.1         | Identification                                       | 6 |  |  |

|    |                       | 2.2.2         | Collection                                           | 6 |  |  |

|    |                       | 2.2.3         | Examination                                          | 7 |  |  |

|    |                       | 2.2.4         | Analysis                                             | 8 |  |  |

|    |                       | 2.2.5         | Presentation                                         | 8 |  |  |

|    | 2.3                   | Existi        | ng standards                                         | 9 |  |  |

|    |                       | 2.3.1         | SWGDE                                                | 9 |  |  |

|    |                       | 2.3.2         | Global Guidelines for Digital Forensics Laboratories | 9 |  |  |

|    |                       | 2.3.3         | ETSI TS 103 643                                      | 0 |  |  |

|   |      | 2.3.4  | ISO/IEC 17025                                                                                                                     |

|---|------|--------|-----------------------------------------------------------------------------------------------------------------------------------|

|   |      | 2.3.5  | Forensic Photography (ANZPAA) 12                                                                                                  |

|   | 2.4  | Other  | research                                                                                                                          |

|   |      | 2.4.1  | Custom SD card with log file 13                                                                                                   |

|   |      | 2.4.2  | Watermarking                                                                                                                      |

|   | 2.5  | Evider | nce Bags                                                                                                                          |

|   |      | 2.5.1  | Digital Evidence Bags                                                                                                             |

|   |      | 2.5.2  | Requirements for a digital evidence bag 14                                                                                        |

|   | 2.6  | Digita | l Evidence in Court $\ldots \ldots 16$ |

|   | 2.7  | Conclu | usion                                                                                                                             |

| 3 | Info | matio  | n Security 18                                                                                                                     |

| - | 3.1  |        | uction                                                                                                                            |

|   | -    | 3.1.1  | Aims of Information Security                                                                                                      |

|   | 3.2  | Avenu  | es of approach                                                                                                                    |

|   | 3.3  |        | ography                                                                                                                           |

|   |      | 3.3.1  | Cryptographic hashes                                                                                                              |

|   |      | 3.3.2  | Symmetric key cryptography 22                                                                                                     |

|   |      | 3.3.3  | Public key cryptography                                                                                                           |

|   |      | 3.3.4  | Digital signatures                                                                                                                |

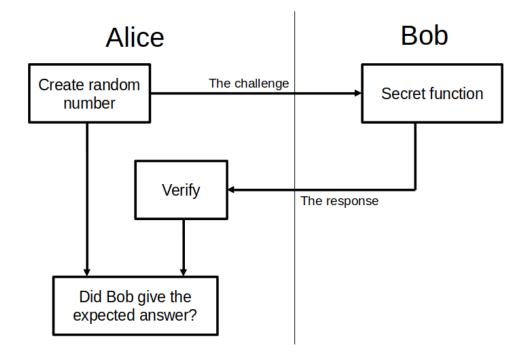

|   |      | 3.3.5  | Authentication                                                                                                                    |

|   | 3.4  | Widel  | y witnessed                                                                                                                       |

|   |      | 3.4.1  | Merkle trees         28                                                                                                           |

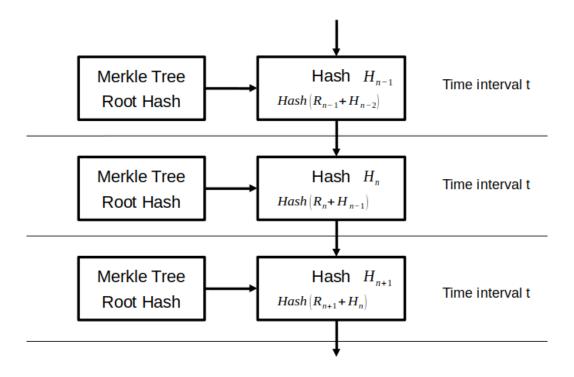

|   |      | 3.4.2  | Hashchains                                                                                                                        |

|   |      | 3.4.3  | Blockchains                                                                                                                       |

|   | 3.5  |        | vare/Physical security                                                                                                            |

|   |      | 3.5.1  | Write-once memory                                                                                                                 |

|   |      | 3.5.2  | Securing microcontroller code                                                                                                     |

|   |      | 3.5.3  | Smart cards                                                                                                                       |

|   |      | 3.5.4  | Hardware Security Modules                                                                                                         |

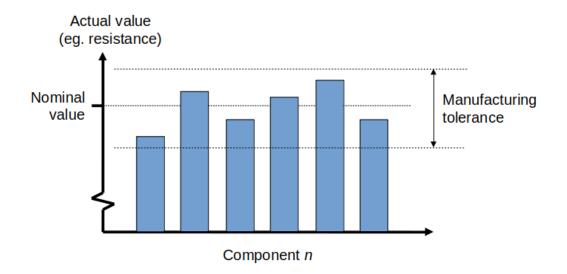

|   | 3.6  | Manuf  | facturing variances/defects                                                                                                       |

|   |      | 3.6.1  | Mathematics of Correlation                                                                                                        |

|   |      | 3.6.2  | Digital Fingerprint                                                                                                               |

|   |      | 3.6.3  | Photography as an example of digital fingerprinting                                                                               |

|   |      | 3.6.4  | Digital memory                                                                                                                    |

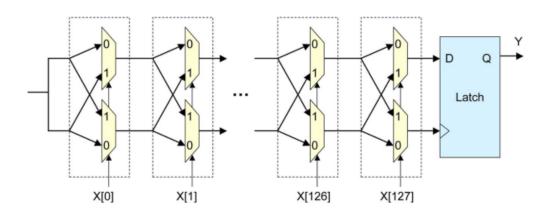

|   |      | 3.6.5  | Physically unclonable functions                                                                                                   |

|   |      | 3.6.6  | Static RAM power on state                                                                                                         |

|   | 3.7  | Conclu |                                                                                                                                   |

|   |      | 3.7.1  | Relevance to the Digital Evidence Bag                                                                                             |

|   |      |        |                                                                                                                                   |

| 4                      | Dig | ital Mem                                                                                              | ory Fingerprinting                   | 41                               |

|------------------------|-----|-------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------|

|                        | 4.1 | Introduct                                                                                             | tion                                 | 41                               |

|                        |     | 4.1.1 B                                                                                               | ackground                            | 42                               |

|                        | 4.2 | Experime                                                                                              | ent overview                         | 43                               |

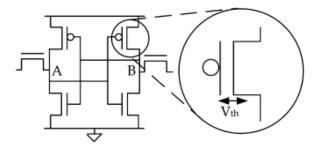

|                        |     | 4.2.1 M                                                                                               | Iemory Architecture                  | 43                               |

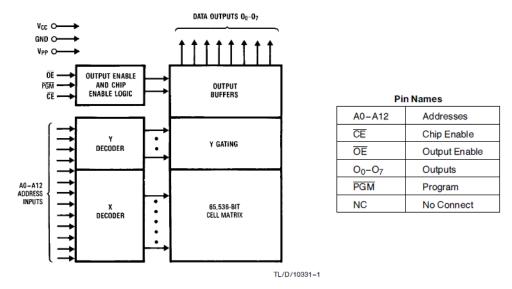

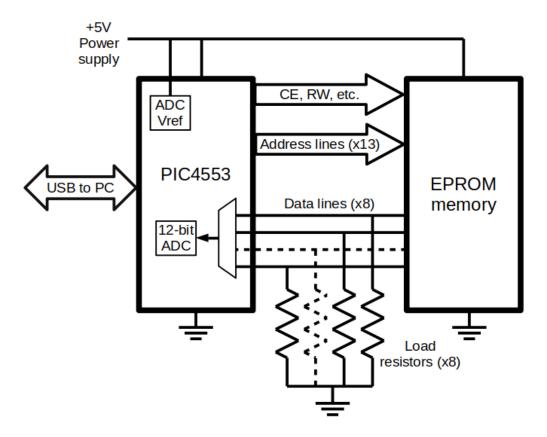

|                        |     | 4.2.2 N                                                                                               | MOS vs CMOS                          | 44                               |

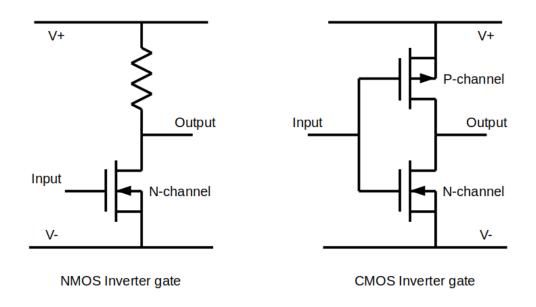

|                        | 4.3 | Experime                                                                                              | ental setup                          | 46                               |

|                        |     | 4.3.1 In                                                                                              | npact of the test circuit            | 46                               |

|                        |     | 4.3.2 M                                                                                               | Iemory read method                   | 46                               |

|                        |     | 4.3.3 Pe                                                                                              | ower supply                          | 48                               |

|                        |     | 4.3.4 Te                                                                                              | emperature Effects                   | 49                               |

|                        | 4.4 | Results .                                                                                             |                                      | 50                               |

|                        |     | 4.4.1 N                                                                                               | MOS (TMS2764)                        | 50                               |

|                        |     | 4.4.2 C                                                                                               | MOS (27C64)                          | 54                               |

|                        | 4.5 | Conclusio                                                                                             | on and future work                   | 56                               |

|                        |     | 4.5.1 O                                                                                               | utput buffer fingerprinting          | 56                               |

|                        |     | 4.5.2 B                                                                                               | uffer Problem                        | 56                               |

|                        |     | 4.5.3 F                                                                                               | lash Memory                          | 57                               |

|                        |     | 4.5.4 R                                                                                               | elevance to the digital evidence bag | 57                               |

| -                      | •   |                                                                                                       |                                      | 50                               |

| 5 An Analog Memory DEB |     |                                                                                                       | -                                    | <b>59</b>                        |

|                        | 5.1 |                                                                                                       | tion                                 |                                  |

|                        |     |                                                                                                       |                                      |                                  |

|                        | 5.0 |                                                                                                       | haracteristics                       |                                  |

|                        | 5.2 |                                                                                                       | examples                             |                                  |

|                        |     |                                                                                                       | apacitors                            |                                  |

|                        |     |                                                                                                       | loating gate FETs                    |                                  |

|                        |     |                                                                                                       | hotodiodes/Image sensors             |                                  |

|                        |     |                                                                                                       | lemristors                           |                                  |

|                        |     |                                                                                                       | Iagnetic tape and disks              |                                  |

|                        | 5.3 | Tamper-e                                                                                              | avident Memory                       | 66                               |

|                        |     | <b>H A I</b>                                                                                          |                                      |                                  |

|                        |     |                                                                                                       | dditive writes                       | 66                               |

|                        |     | 5.3.2 C                                                                                               | dditive writes                       | 66<br>67                         |

|                        |     | 5.3.2 C<br>5.3.3 R                                                                                    | dditive writes                       | 66<br>67<br>71                   |

|                        |     | 5.3.2 C<br>5.3.3 R<br>5.3.4 R                                                                         | dditive writes                       | 66<br>67<br>71<br>73             |

|                        |     | 5.3.2 C<br>5.3.3 R<br>5.3.4 R<br>5.3.5 R                                                              | dditive writes                       | 66<br>67<br>71<br>73<br>73       |

|                        |     | 5.3.2 C<br>5.3.3 R<br>5.3.4 R<br>5.3.5 R                                                              | dditive writes                       | 66<br>67<br>71<br>73<br>73       |

|                        | 5.4 | 5.3.2       C         5.3.3       R         5.3.4       R         5.3.5       R         5.3.6       O | dditive writes                       | 66<br>67<br>71<br>73<br>73<br>76 |

|    |      | 5.4.2   | Results                                                    | . 81  |

|----|------|---------|------------------------------------------------------------|-------|

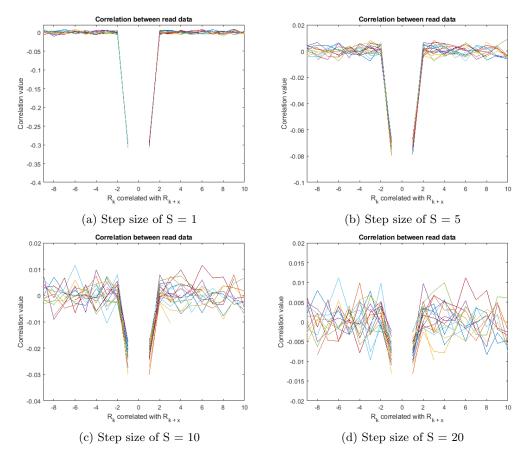

|    |      | 5.4.3   | Step size                                                  | . 82  |

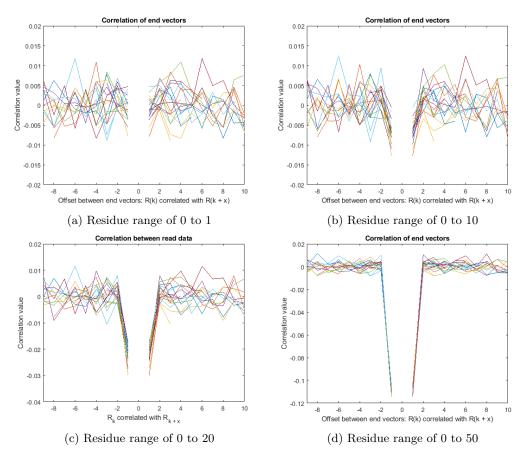

|    |      | 5.4.4   | Residue range                                              | . 83  |

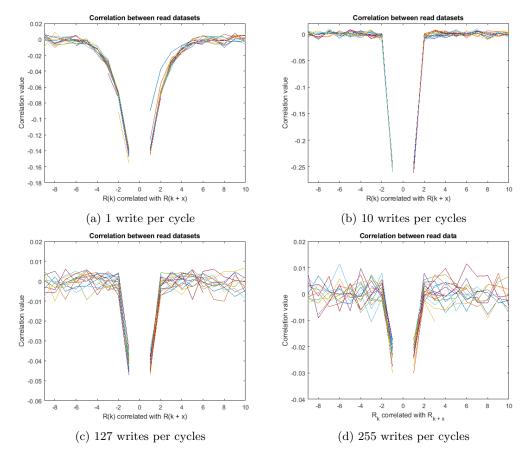

|    |      | 5.4.5   | Writes per cycle                                           | . 84  |

|    |      | 5.4.6   | Limitations                                                | . 86  |

|    | 5.5  | Conclu  | usion                                                      | . 87  |

|    |      | 5.5.1   | Future Work                                                | . 88  |

| 6  | Mer  | nristo  | cs                                                         | 90    |

|    | 6.1  | Introd  | uction                                                     | . 90  |

|    | 6.2  | Ideal I | Memristors                                                 | . 90  |

|    |      | 6.2.1   | I-V curves                                                 | . 92  |

|    |      | 6.2.2   | Memristor applications                                     | . 93  |

|    | 6.3  | Practi  | cal Memristors                                             | . 94  |

|    |      | 6.3.1   | Metastable Switch Model                                    | . 94  |

|    |      | 6.3.2   | Simulations                                                | . 96  |

|    | 6.4  | Experi  | imental Measurements                                       | . 99  |

|    |      | 6.4.1   | Sine Wave Response                                         | . 100 |

|    |      | 6.4.2   | Step Response                                              | . 100 |

|    |      | 6.4.3   | Analog Memory                                              | . 101 |

|    | 6.5  | Conclu  | ısion                                                      | . 102 |

|    |      | 6.5.1   | Future Work                                                | . 103 |

| 7  | Con  | clusio  | a                                                          | 105   |

|    | 7.1  | Digita  | l forensics and the Digital Evidence Bag                   | . 105 |

|    | 7.2  | Inform  | nation security technologies                               | . 106 |

|    | 7.3  | Finger  | printing digital memory                                    | . 106 |

|    | 7.4  | Creati  | ng an analog memory based DEB                              | . 107 |

|    | 7.5  | Using   | memristors as analog memory cells                          | . 107 |

|    | 7.6  | Future  | e Work                                                     | . 108 |

| Aj | open | dices   |                                                            | 109   |

| A  | Full | correl  | ation data for individual bit lines from NMOS memory chips | 109   |

|    |      |         |                                                            |       |

| DI | nnog | graphy  |                                                            | 113   |

# Abstract

Digital evidence is electronic data that "has the potential to make the factual account of either party more probable or less probable than it would be without the evidence" [1]. We consider digital evidence stored on a physical memory device, collected in the field and transported to a lab where the digital content is stored and analyzed. Digital Forensics is the area of study that deals with the science behind this process, as well as establishing best practices and legal requirements. The core aspects of digital forensics are preserving evidence integrity and the chain of custody during the handling and storage of the evidence [2].

In this thesis, we look specifically at digital evidence where only digital data is collected (such as forensic photography), as opposed to digital evidence that also includes the storage medium (such as seized mobile phones). We review the existing procedures used for collecting and transporting evidence and explore how these processes could be improved to better suit this kind of digital evidence.

The field of Information Security deals with providing confidentiality and integrity of data, along with authentication and non-repudiation of both data and entities [3]. This is a widely researched and well developed area with many commercial applications, the most well known being internet security. We review and categorize the existing technologies used in information security into four avenues of approach based upon the fundamental security concepts of each: cryptography, widely witnessed, hardware security and exploitation of manufacturing defects. Many information security systems incorporate several of these approaches which leads to the overall security of the system being improved.

The aims of Digital Forensics and Information Security are similar, however the processes and systems used are very different. This partly reflects that digital forensics is usually subject to a greater level of legal scrutiny, but it also highlights that there are potentially opportunities to improve the processes and systems used.

Hence we develop the concept of a "digital evidence bag" (DEB), a device for the secure transport of digital evidence that has the same requirements as physical evidence bags: tamper-evident, unforgeable and clean. To achieve these requirements through technological solutions, we look at technology used in Information Security along with traditional forensic processes and explore how they can be adapted to create a DEB.

Given the nature of digital data, it is easy to produce exact copies and edit the data without loss of quality. From a forensics point of view, this strips out a lot of the imperfections that are usually exploited in the traditional forensic processes. However the technology used to build digital memory is still inherently analog and has non-ideal characteristics, which are usually obfuscated in the digital application space. We show how these characteristics can be exploited to achieve the DEB requirements.

We explore how a digital fingerprint for conventional digital memory could be used to meet the requirements of the DEB. We also propose a DEB based on analog memory cells which offers a novel method to meet the requirements.

# Declaration

I certify that this work contains no material which has been accepted for the award of any other degree or diploma in my name in any university or other tertiary institution and, to the best of my knowledge and belief, contains no material previously published or written by another person, except where due reference has been made in the text. In addition, I certify that no part of this work will, in the future, be used in a submission in my name for any other degree or diploma in any university or other tertiary institution without the prior approval of the University of Adelaide and where applicable, any partner institution responsible for the joint award of this degree.

I give permission for the digital version of my thesis to be made available on the web, via the University's digital research repository, the Library Search and also through web search engines, unless permission has been granted by the University to restrict access for a period of time.

I acknowledge the support I have received for my research through the provision of an Australian Government Research Training Program Scholarship.

Signed: \_\_\_\_\_.

Benjamin James Agnew

Date: 25-01-2022

# Acknowledgements

To my supervisors, Dr Matthew Sorell and Professor Michael Liebelt, thank you for the many hours of discussions and advice, without which this thesis would not have been written. I will always be grateful for the teaching, friendships and experiences you provided.

# List of Figures

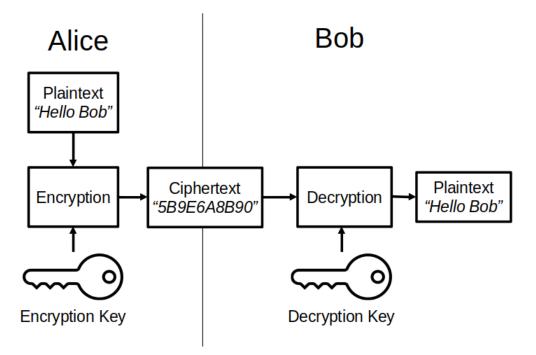

| 3.1  | Block diagram of basic cryptography process                                     | 21 |

|------|---------------------------------------------------------------------------------|----|

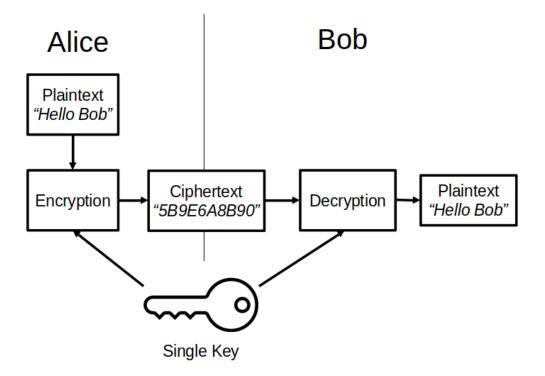

| 3.2  | Block diagram of symmetric cryptography process                                 | 23 |

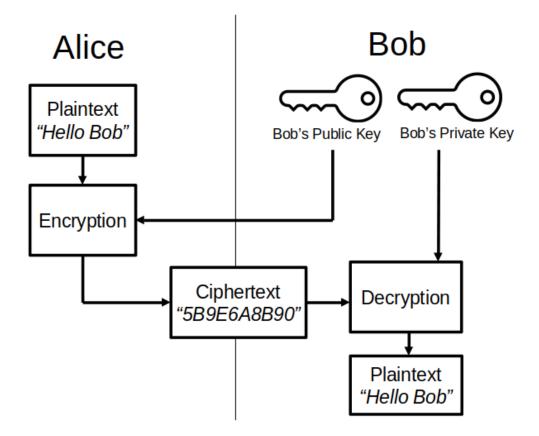

| 3.3  | Block diagram of public key cryptography process                                | 24 |

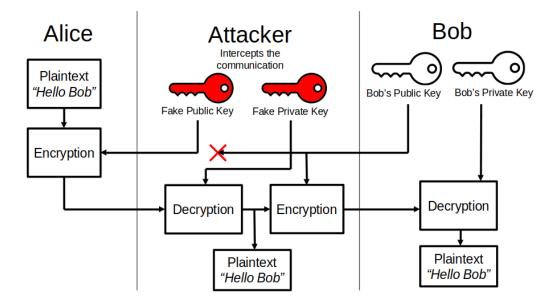

| 3.4  | Block diagram of a man-in-the-middle attack on a message secured with pub-      |    |

|      | lic key cryptography                                                            | 25 |

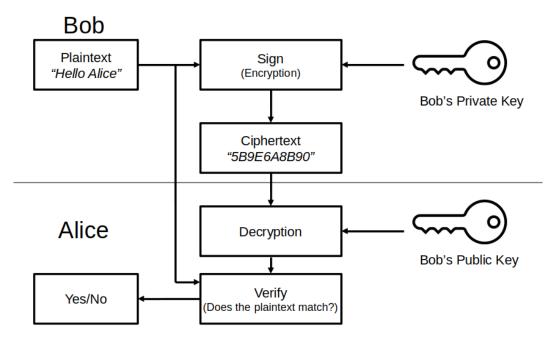

| 3.5  | Block diagram of digital signature algorithm                                    | 26 |

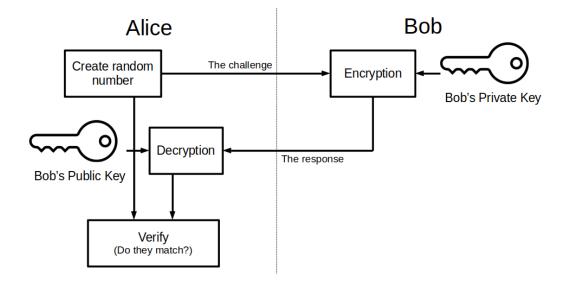

| 3.6  | Block diagram of challenge-response algorithm                                   | 27 |

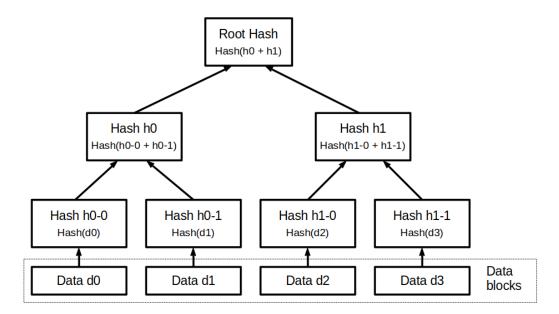

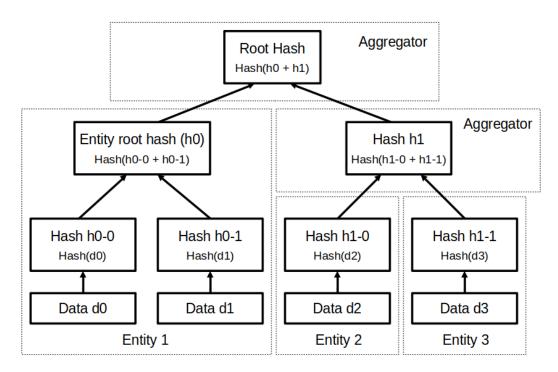

| 3.7  | Block diagram of merkle tree structure                                          | 28 |

| 3.8  | Merkle tree with with data from multiple entities                               | 29 |

| 3.9  | Block diagram of a hashchain                                                    | 30 |

| 3.10 | The small variations between components is used to create a unique digital      |    |

|      | fingerprint of the device                                                       | 35 |

| 3.11 | Block diagram of simple challenge-response algorithm                            | 36 |

| 3.12 | Arbiter PUF circuit [4] ( $\bigcirc$ 2014, IEEE - reproduced with permission)   | 37 |

| 3.13 | SRAM Circuit [4] (© 2014, IEEE - reproduced with permission)                    | 38 |

| 4 1  | Internal black dia many of EDDOM many shine [7] ( Counterna of Tana a           |    |

| 4.1  | Internal block diagram of EPROM memory chips [5] ( <i>Courtesy of Texas In-</i> |    |

|      | struments Inc.)                                                                 | 44 |

| 4.2  | Circuit diagrams of NMOS and CMOS inverters                                     | 45 |

| 4.3  | Circuit used to measure the analog output voltages                              | 47 |

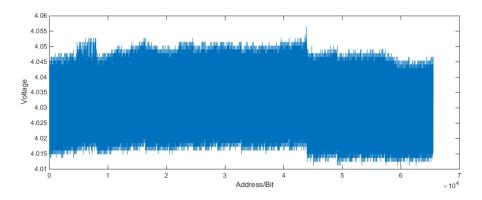

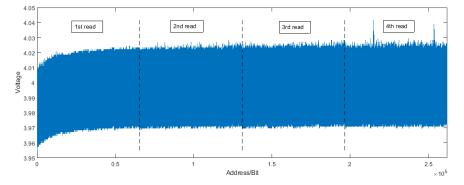

| 4.4  | Memory cell output voltage when the memory chip is powered by the USB bus       | 48 |

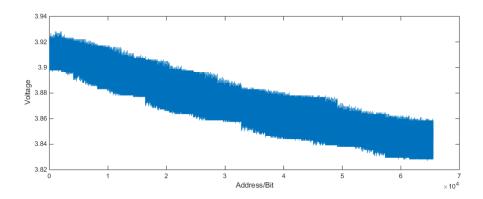

| 4.5  | Memory cell output voltage when the memory chip is powered by alkaline          |    |

|      | batteries                                                                       | 49 |

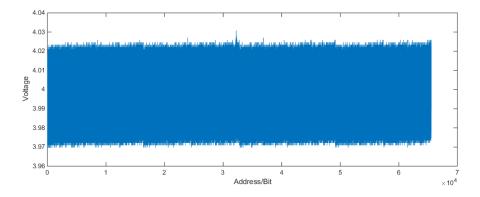

| 4.6  | Memory cell output voltage when the memory chip is powered by the switch-       |    |

|      | mode power supply                                                               | 49 |

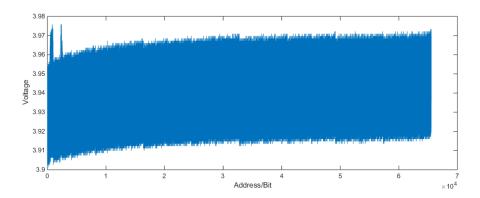

| 4.7  | Memory cell output voltage when the memory chip is cold when the read           |    |

|      | process starts                                                                  | 50 |

| 4.8  | Four consecutive reads from one memory chip, showing the later reads are        |    |

|      | not affected by the cold start                                                  | 50 |

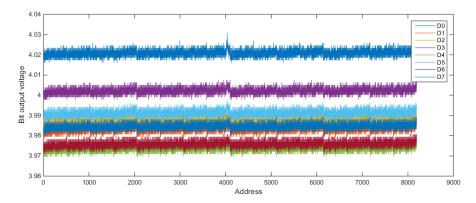

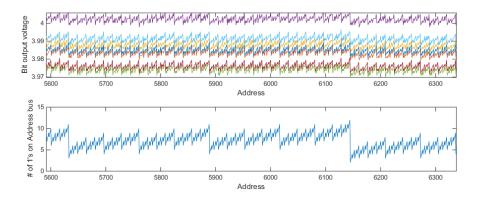

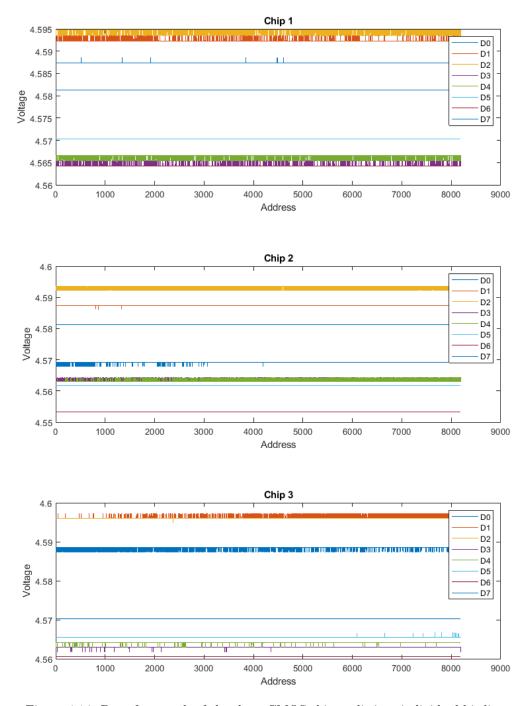

| 4.9         | Data from chip 1, read 1 separated by each bit line in the data bus (NMOS)           | 52       |

|-------------|--------------------------------------------------------------------------------------|----------|

| 4.10        | Data from chip 2, read 1 separated by each bit line in the data bus (NMOS)           | 52       |

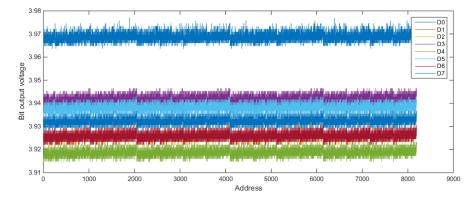

| 4.11        | Data from chip 3, read 1 separated by each bit line in the data bus (NMOS)           | 53       |

| 4.12        | A close up of the data from NMOS chip 1, read 1 showing the effect of the            |          |

|             | address bus state                                                                    | 53       |

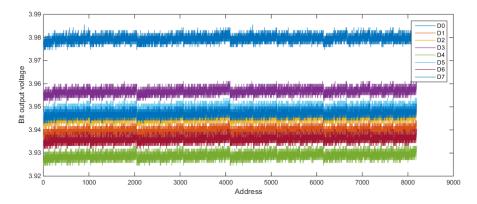

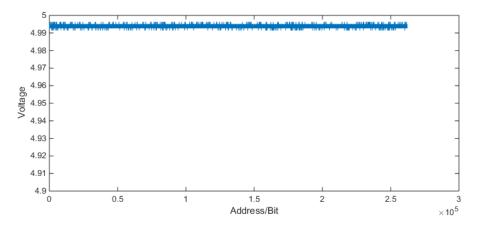

| 4.13        | Data from CMOS memory chip with no load on the output                                | 54       |

| 4.14        | Data from each of the three CMOS chips split into individual bit lines $\ . \ . \ .$ | 58       |

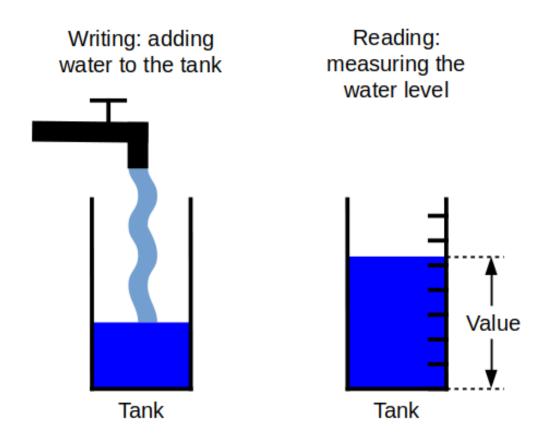

| 5.1         | Water analogy for a analog memory cell                                               | 60       |

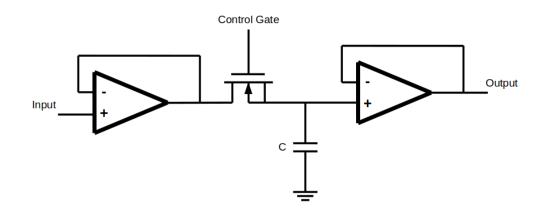

| 5.2         | Sample and Hold circuit                                                              | 63       |

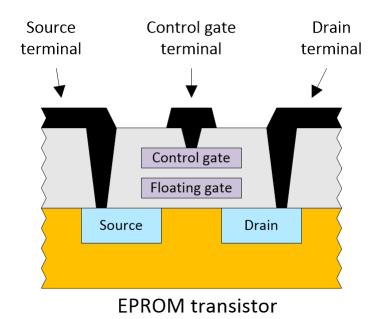

| 5.2<br>5.3  | Internal structure of a Floating Gate FET [6] (reproduced with permission)           | 64       |

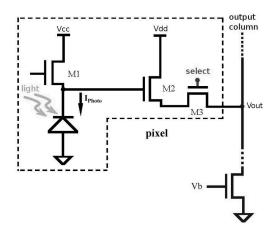

| 5.3         | Circuit diagram of pixel from a CMOS Image Sensor [7] (reproduced with               | 04       |

| 0.4         | permission)                                                                          | 65       |

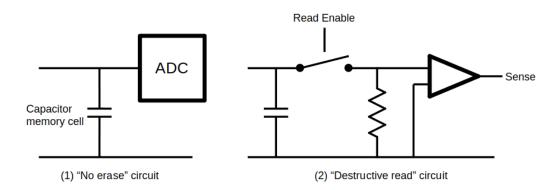

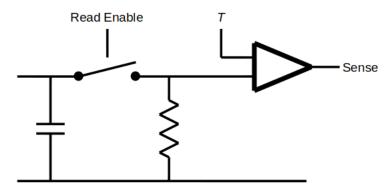

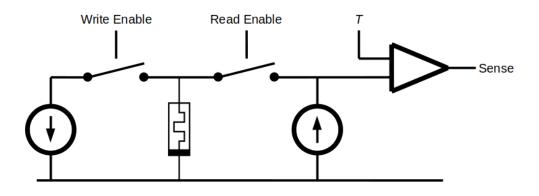

| 5.5         | Example circuit for a memory cell with destructive read                              | 03<br>72 |

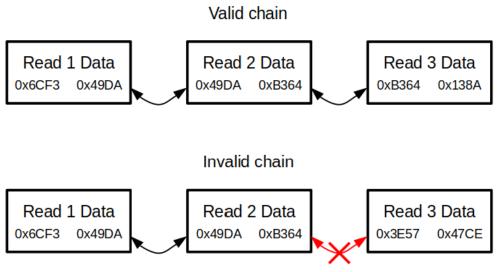

| 5.6         | By chaining read operations together we can detect missing read operations .         | 74       |

| 5.7         | Example circuit for a memory cell with destructive read and residue                  | 74<br>76 |

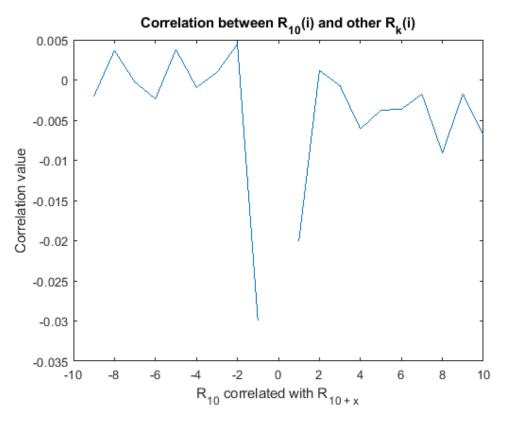

| 5.7<br>5.8  | Correlation results for $R_{10}(i)$                                                  | 70<br>81 |

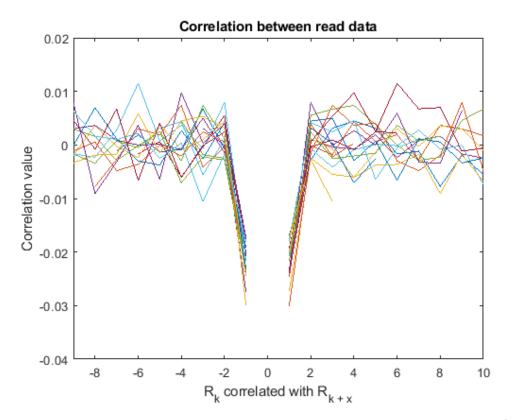

| 5.9         | Correlation results after writing 255 hashes per cycle to the memory array .         | 82       |

| 5.9<br>5.10 | Effect of changing the step size                                                     | 84       |

|             | Effect of changing the residue range                                                 | 85       |

|             |                                                                                      | 86       |

| 0.12        | Effect of changing the number of writes per cycles                                   | 00       |

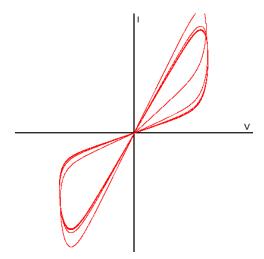

| 6.1         | I-V curve of an ideal memristor                                                      | 92       |

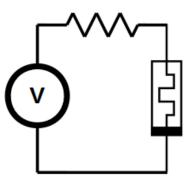

| 6.2         | Memristor memory cell circuit with partially destructive read                        | 94       |

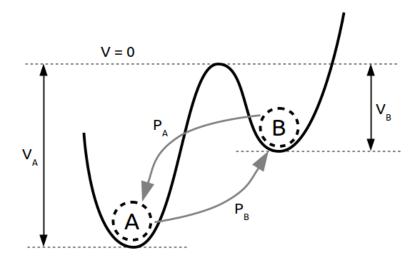

| 6.3         | Potential energy barrier between the two states of the MSS model [8]                 | 96       |

| 6.4         | Memristor test circuit with a current limiting resistor                              | 97       |

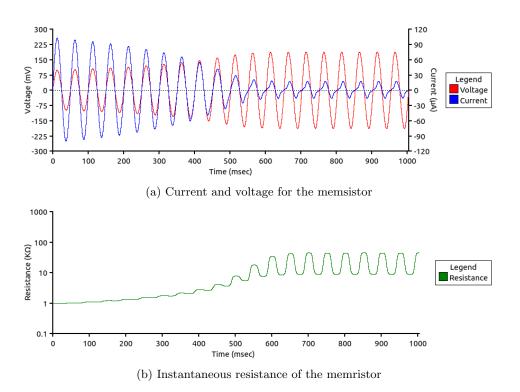

| 6.6         | Simulated time-domain response of a memristor with 20Hz sine wave                    | 99       |

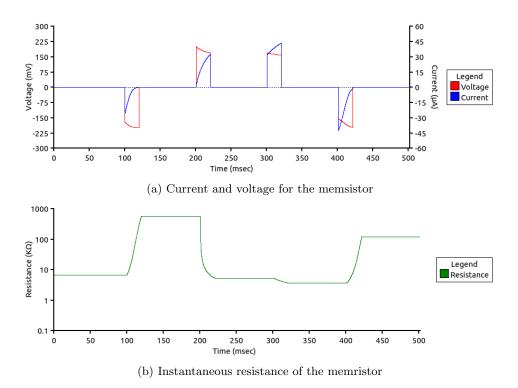

| 6.7         | Simulated time-domain response of a memristor to 20ms pulses                         | 100      |

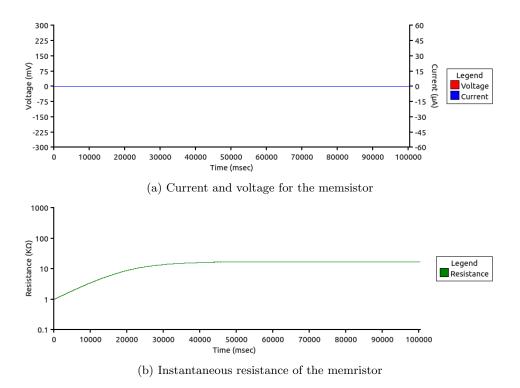

| 6.8         | Simulated time-domain response of a memristor with zero voltage applied $\ .$ . If   | 101      |

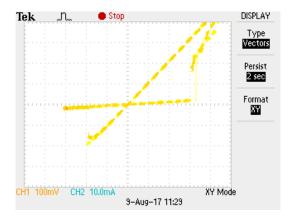

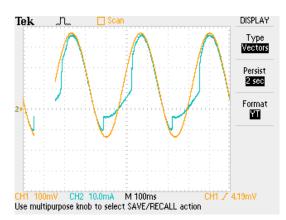

| 6.9         | Measured memristor I-V curve with a 3Hz sine wave                                    | 102      |

| 6.10        | Measured memristor voltage and current with a 3Hz sine wave $\ldots$                 | 102      |

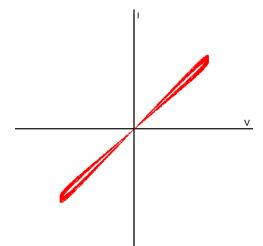

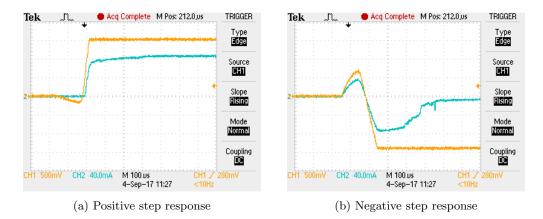

| 6.11        | Measured step responses of the memristor                                             | 103      |

|             |                                                                                      |          |

# List of Tables

| 4.1 | Correlating each result set from the NMOS memory chips (shaded cells rep-               |     |

|-----|-----------------------------------------------------------------------------------------|-----|

|     | resent correlation between data from the same memory chip) $\ldots \ldots \ldots$       | 51  |

| 4.2 | Correlating the NMOS data from each bit line separately (shaded cells rep-              |     |

|     | resent correlation between data from the same memory chip). Each value                  |     |

|     | shown is the average of the 8 correlation results for each bit line. The full           |     |

|     | results are shown in Appendix A                                                         | 54  |

| 4.3 | Correlating each result set from the CMOS memory chips (shaded cells rep-               |     |

|     | resent correlation between data from the same memory chip) $\ \ldots \ \ldots \ \ldots$ | 55  |

| E 1 | Bit Foren Data and May call value for different stop sizes                              | 09  |

| 5.1 | Bit Error Rate and Max cell value for different step sizes                              | 83  |

| 5.2 | Bit Error Rate and Max cell value for different residue ranges                          | 83  |

| 5.3 | Bit Error Rate and Max cell value for different values of N                             | 87  |

| 6.1 | Fundamental circuit elements and their defining equations                               | 91  |

| A.1 | Correlating the NMOS data from each bit line separately (shaded cells rep-              |     |

|     | resent correlation between data from the same memory chip) (part 1) $\ldots$            | 110 |

| A.2 | Correlating the NMOS data from each bit line separately (shaded cells rep-              |     |

|     | resent correlation between data from the same memory chip) (part 2) $\ldots$            | 111 |

| A.3 | Correlating the NMOS data from each bit line separately (shaded cells rep-              |     |

|     | resent correlation between data from the same memory chip) (part 3) $\ldots$            | 112 |

# Chapter 1

# Introduction

# 1.1 Context

Forensic science has been defined as "the application of scientific methods to establish factual answers to legal problems" [2]. Digital forensics is a sub area of this looking at how computers, computer systems and digital data can be used to help establish factual answers to legal problems. Digital forensic evidence is digital data that "has the potential to make the factual account of either party more probable or less probable than it would be without the evidence" [1]. This term often includes the devices that contain the digital data as well, for example hard drives and mobile phones.

During an investigation involving digital forensic evidence, this digital evidence needs to be collected, transported, stored, analyzed and then potentially presented in court. Throughout this process, evidence integrity must be maintained which means protecting the digital evidence against tampering or deletion. Chain of custody is also an important concept in forensic investigations, which refers to keeping thorough records of all actions involving the evidence along with who was responsible for them [2].

In this thesis we are looking at the transport and handling of digital evidence and how this is done securely: that is ensuring that evidence integrity and chain of custody is maintained throughout the investigation. We observe that the requirements of this process are similar to the requirements in the field of information security.

Information security is an area of study that looks at protecting the confidentiality, integrity and availability of data [9]. With the advent of the internet, this field has become more important than ever. Internet security (or cyber-security) is one of the most active and well researched applications of information security. The four core objectives in information security are confidentiality, data integrity, authentication, and non-repudiation [3].

# 1.2 Aim

We note that the aims and requirements in digital forensics are similar to those in the information security field. However after reviewing existing standards and procedures, we find that the processes used to achieve these aims are very different between the two fields. Digital forensics currently uses procedures, paper audit logs, physical security and other non-technical solutions to achieve these aims, whereas information security uses cryptography, widely witnessed data (blockchain), secure hardware and the exploiting of manufacturing defects to achieve the aims.

After reviewing the literature, we observed that the field of information security appears to be further progressed and more thoroughly researched than digital forensics, which leads to the following questions:

- Can we apply similar solutions from information security to the digital forensics field in order to better achieve the aims?

- And if so, what might these look like?

In investigating these questions, the concept of a Digital Evidence Bag (DEB) is introduced, a memory device for the secure transport of digital evidence. The background and requirements of a DEB are fully explained in chapter 2. Once the DEB has been defined, the questions were refined to be: Can we meet the requirements of the DEB by exploiting:

- the analog properties of digital memory, or

- the properties of analog memory cells?

# 1.3 Scope

In some cases, digital data is stored on a device where the device is also evidence itself. An example of this is computers and other electronic equipment seized from the crime scene. These devices contain digital evidence as well as other non-electronic evidence (fingerprints, DNA, etc.). In this thesis, we are not looking at these cases since the procedures used for the transport of physical evidence are well established.

We are looking at the cases where the storage device is not otherwise physically relevant to the investigation, only the digital data within it is relevant. Some examples of this include crime scene photography, CCTV footage and dashcam video. In these cases, the digital evidence can be copied, transferred, sent over the internet, etc., without any loss of evidence.

The DEB is aimed at the collection (and transport) phases of the forensic cycle. Processes for ensuring evidence integrity and chain of custody during the later phases are not in the scope of this thesis. We found that there are four distinct avenues of approach used in information security technology: cryptography, widely witnessed (blockchain), secure hardware and the exploiting of manufacturing defects. Any one of these could potentially be used to address the requirements of the DEB, and a combination of them is likely to give a more secure solution. However in this thesis we have chosen to focus on the exploiting of manufacturing defects since it is a relativity new area of active research. It also potentially offers some innovative solutions to the unforgability requirement of the DEB, one of the four requirements of the DEB (fully explained in section 2.5.2) that deals with preventing fake copies of the DEB being created. This is also the requirement that existing digital evidence handling procedures have struggled with to some extent.

# 1.4 Overview

A background of digital forensics along with a review of existing procedures is given in Chapter 2. The concept and requirements of a DEB are also introduced and explained. Chapter 3 explains and reviews the existing technology used in information security. We then categorized the existing technology into four avenues of approach based on how they provide security: cryptography, widely witnessed data (blockchain), secure hardware and the exploiting of manufacturing defects. Manufacturing defects form the basis of digital fingerprinting.

Chapter 4 then explores how a digital fingerprint could be applied to conventional digital memory in order to help create a DEB. This includes experimentation to create a method for digital fingerprinting older generation EPROM digital memory chips. Then in Chapter 5 we explore a design of a DEB using analog memory cells. This outlines a novel method for the storage of digital data in analog cells that helps meet the requirements of the DEB. Following on from this, Chapter 6 looks at using memristors as analog memory cells. Simulations and experiments are carried out to ascertain if memristors could be used to build the DEB described in Chapter 5.

Finally Chapter 7 provides a conclusion of the work done and highlights the contributions that have been made by this thesis.

# Chapter 2

# Digital Evidence, Forensics and Investigation

# 2.1 Introduction to Forensics

Forensics is the process of answering legal problems using scientific methods across all areas of science from biology to physics and engineering. Digital forensics refers to the application of computer science and electronic engineering in assisting to solve legal problems.

Digital evidence is electronic data that "has the potential to make the factual account of either party more probable or less probable than it would be without the evidence" [1]. This data can be stored and/or manipulated on a computer system or electronic device or transmitted by a communications system. It comes in a number of different forms such as CCTV video, crime scene photography, phone call records, server logs and seized equipment such as computers, phones and hard drives [2].

Forensics is usually considered in the context of criminal law where law enforcement agencies conduct the forensic investigation and then use the evidence collected to prove or disprove the guilt of someone suspected to have committed a crime. However, organizations, both public and private, can also carry out forensic investigations. Often these investigations are looking at an incident that has occurred at the organization where management would like to know more about why and how the incident occurred.

As an example in the digital forensics field, if the security of an organization's servers is breached and data is stolen, a forensic investigation would then be carried out to determine how the breach occurred and what was stolen. The outcome of the investigation is usually to make changes to prevent such an incident from occurring again but a forensic investigation can also improve public relations after an incident and identify who was responsible.

#### 2.1.1 Relevance of the storage medium

Digital evidence can be found and collected from a number of locations including crime scenes, data centres, archives and network traffic. In most cases it is then transported to a digital forensic lab for examination and analysis.

Here we consider two categories of digital evidence, cases where the physical storage medium is also evidence and cases where the digital data is evidence alone. The first case is one often associated with digital forensics, where electronic devices are collected as evidence. For example, computers and phones found at a crime scene are also physical evidence since they are objects that may have fingerprints, DNA and other non-digital evidence on them. In addition, they also contain digital data within the memory of the device which may also be used as evidence.

The second case is less common and often overlooked by standards. In this case the device the data is stored on (or transmitted on) is not relevant to the investigation. For example, crime scene photography, where the data is first stored on a SD card and then transferred to a database. CCTV footage is also in this category as the data is first stored on a digital video recorder before the relevant files are extracted and transferred to the forensic investigator.

## 2.1.2 Evidence integrity and chain of custody

There are two fundamental principles when dealing with evidence, the first, evidence integrity, refers to preserving both the original evidence and any copies of it in their original form. It is vital that evidence integrity is maintained throughout the investigation. In the case of digital forensics, this means ensuring the data hasn't been changed or deleted, either accidentally or intentionally (maliciously) [2].

The second fundamental principle, chain of custody, refers to the documentation that needs to be maintained throughout the forensic process. This documentation includes records of all actions preformed during the collection, handling, analysis and disposal of the evidence, along with who was responsible for each action. This documentation is used to prove the integrity and authenticity of the evidence.

In some cases, the confidentially of evidence is also required, which we will discuss further in section 2.5.2.

# 2.2 The forensic process

The digital forensic process is a five step process that provides some structure to how digital forensic investigations are carried out. The five steps are: [2]

1. Identification

- 2. Collection

- 3. Examination

- 4. Analysis

- 5. Presentation

Throughout the forensic process, evidence integrity and chain of custody must be maintained. The systems used for this are discussed further in section 2.3. The forensic process is also an iterative process in addition to the five linear steps. The collection/examination/analysis process is repeated as the results found in analysis can change the hypothesis or suggest other evidence that could be relevant to the investigation. Hence this process is then repeated with the collection, examination and analysis of the new evidence.

### 2.2.1 Identification

Upon arriving at the scene of an incident, an investigator needs to first identify any evidence (or potential evidence) that may be relevant to the investigation. This includes making an initial hypothesis to help guide in identifying what evidence to focus on. In criminal cases, this will often occur at a crime scene where the digital evidence is identified alongside traditional physical evidence. In other cases, the digital evidence may be identified in a number of locations including live data centres and archives.

Digital evidence may also be found in places other than the scene of an incident. For example, data stored with a cloud service provider can be evidence.

Before an incident even occurs, investigators need to be well trained and prepared so they can work quickly and methodically once at the scene of an incident. Some digital evidence may be in short-term, or volatile memory (eg. RAM) and needs to be dealt with quickly before it is lost. Investigators also need to be careful not to accidentally damage or erase any potentially useful data.

# 2.2.2 Collection

In the context of digital evidence, collection refers to the process of creating a digital copy of the data using forensically sounds techniques. All examination and analysis work should always be carried out using a copy and not the original data. This is done to minimize any chance of accidental changes to the original data.

The difficulty of collection depends largely on the device the data is copied from, along with the format the data is in. Devices such as hard drives, CDs, and USB memory sticks are usually relatively simple to copy. A write-blocker is commonly used when copying from these devices in order to prevent any accidentally changes to the data on the device. Write-blockers are a hardware device that are placed between the computer and the storage medium and which are designed to only allow read operations to pass through from the computer to storage medium. Data contained within a mobile phone can be more difficult to copy and usually involves interaction with the Operating System (OS) on the phone in order to get access to the stored data.

Embedded devices often contain data traces which can potentially become digital evidence. The ease of copying this data can vary greatly depending on the device. In the more difficult cases, it many be necessary to physically remove the memory IC chip from the embedded device (a process know as "chip-off") before placing it in a purpose built circuit for reading and copying.

Digital evidence can also be found in volatile memory such as RAM and CPU caches. Copying data from these locations needs to be done with care since the data in memory can change rapidly and can be completely erased by a loss of power. Encryption can also cause difficulties in collecting digital evidence. While encrypted data can still be copied, it is useless for further analysis unless the decryption key is known or can be found.

### 2.2.3 Examination

The examination phase involves looking through all the data collected and identifying any potential digital evidence. This involves restructuring, phrasing and preprocessing raw data in order to make it easier to analyze later.

In many cases, the raw data takes the form of a file structure and the examiner is looking to find files within it that may be relevant to the investigation. This may involve recovering deleted and partially damaged files as well as searching for hidden files. There are also often many files that are known to be irrelevant to the investigation and can be excluded, for example OS files.

The quantity of data collected in modern investigations is large and getting larger, driven by the ever increasing size of hard drives and other memory devices. As a result, forensic examiners need to be able to quickly identify where the most relevant data will be found. This process is known as "triage" where data is prioritized such that the most relevant data is examined first.

Since examination is a relatively repetitive task, there are a number of software tools designed to assist the examiner in quickly finding the relevant data. These software packages can search vast quantities of data, included compressed data, for strings, image matches, timestamps and cryptographic hashes of files. They include databases of known files to search for, such as OS files and other common software files that can be discounted from the investigation and known malware and contraband images that are likely useful to the investigation.

### 2.2.4 Analysis

In the analysis phase the data identified in examination is processed to establish facts relevant to the investigation. This includes evaluating the significance of the digital evidence and the person(s) responsible for it. This phase often involves visualization, timelining and linking pieces of evidence together in order to fully understand where each piece of evidence fits in the investigation.

The digital data can represent a diverse range of records including text, images, audio, databases and metadata. Each layer of the computer system, along with different software packages, will interpret these data objects differently. Analysis at the file system level will reveal timestamps and file metadata but will often miss metadata that is part of the file itself, for example EXIF data within an image file. EXIF (Exchangeable image file format) is a standard for encoded metadata such as camera settings and the time/location the photo was taken, all within the image file [10]. Hence it is useful to visualize each data object in a way that all aspects of it can be easily interpreted and analyzed.

Timelining involves sorting forensic data, based on timestamps, into chronological order. This allows the investigator to understand the order in which events occurred and may help form hypotheses on why and how they occurred. Timelines constructed from traditional forensic evidence can also be merged with digital forensic timelines to help understand the chain of events. This can then be used to explain how the digital forensic evidence applies to real-world events.

Link analysis is used in all forensic investigations, however it is particularly useful in digital forensic investigations. It involves linking similar or related pieces of evidence together and then visualizing all the links to help identify the relevance of evidence along with any missing links or missing evidence.

#### 2.2.5 Presentation

The final phase involves documenting the findings and results of the investigation for presentation to a court of law or other audience. Whilst this report needs to thoroughly cover all aspects of the investigation, it also needs to be written for a non-specialist audience such as judges, jury members or company executives.

The report needs to cover all aspects of the investigation including, but not limited to, details of all evidence collected, examined and analyzed, roles and tasks of investigators and any information needed to reproduce the results of the analysis. In order to make reports easier to understand, diagrams, images and screenshots are often included to help explain processes used in the investigation. The report also needs to address evidence integrity and chain of custody requirements and outline how these have been maintained during the investigation.

# 2.3 Existing standards

There are a number of standards applicable to digital forensics produced by forensic science and policing organizations around the world. This section explores each of these in detail.

# 2.3.1 SWGDE

The Scientific Working Group on Digital Evidence Framework (SWGDE) has created a framework for a Quality Management System (QMS) for forensic science service providers [11]. It outlines a number of polices and procedures that should be in place for digital evidence handling and investigation. This covers a number of areas including staff qualifications and training, laboratory tools and equipment and periodic reviews of work done.

However there are few details about what these policies and procedures should actually contain. In the area of evidence handling, it simply states that there should be procedures for "properly identifying derivative evidence, securing evidence and logging evidence interaction/transfer". It also states that there should be procedures to enable access control for evidence storage. While there are no details on how these procedures should work, it seems to suggest that audit logs and access control (physical or software) are sufficient for ensuring evidence integrity.

### 2.3.2 Global Guidelines for Digital Forensics Laboratories

The International Criminal Police Organization (Interpol) has published the *Global Guidelines for Digital Forensics Laboratories* [12] which provides guidance on how to build and operate a digital forensics laboratory. This builds upon, and provides more detail around the framework set out by SWGDE.

After receiving the digital evidence, the examiner(s) at the digital forensics laboratory will analyse the evidence. The examiner(s) will then prepare a report before returning the evidence to law enforcement. While the evidence is in the hands of the digital forensics laboratory, it needs to be stored securely whilst it is not being worked on by the examiner(s). To achieve this, Interpol recommends that the digital forensics laboratory be built with surveillance systems and physical access control over rooms and/or cabinets designated for evidence storage. Off-site backups and archive systems are recommended to safe guard against equipment failure.

Guidelines are also provided for staff recruitment and training within a digital forensics laboratory. A security clearance should be required for all staff, along with a background check before they are hired. Due to the complexity and fast-changing nature of digital evidence, ongoing training for staff is recommended. Staff should be well trained in bestpractices for digital evidence handling so as to minimize the chance of accidental damage to the evidence. During investigations, staff will require access to numerous tools, software and hardware, for which suitable training should be provided.

The Interpol guidelines also cover the basics of how forensic analysis is undertaken for both computer equipment and mobile phone devices. This covers a number of common procedures including data extraction and hard drive imaging, data analysis and file reconstruction through to data acquisition on both live and powered-off systems. Data extraction involving interaction with low-level hardware such as JTAG and chip-off are also discussed.

Guidelines around the reporting and presentation of evidence are also given, with a focus on ensuring the admissibility of the electronic evidence. While the specifics vary by jurisdiction, five general requirements for admissibility are given: "Authenticity, Completeness, Reliability, Convincing and Proportionality". However no detail is given as to how these should be achieved and proven to a court. A quality assurance system is recommend though along with accreditation which does assist in fulfilling the requirements for admissibility of evidence.

It is important to note that these guidelines only addresses digital evidence where the physical device holding the digital data is also evidence itself (eg. cases where physical devices with memory are the 'evidence'). It does not address the case where the evidence is purely digital data.

## 2.3.3 ETSI TS 103 643

The European Telecommunications Standards Institute (ETSI) have published a standard titled "*Techniques for assurance of digital material used in legal proceedings*" [13] which introduces the concept of a digital evidence bag (DEB). It outlines a system that can be used to store and transform digital evidence in a way that meets the requirements for admissibility for evidence in court. In this document, "transform" refers to any function or algorithm that is used to process and analyze the data (for example, image enhancement and color correction). ETSI defines a Purely Digital Transformation (PDT) to be a digital function that is repeatable, deterministic, pre-specified, fail-safe and well-defined.

#### **Basic DEB**

Three different levels of DEB are described, with the user to choose the most suitable one depending on the security requirements of the case. The "Basic DEB" simply consists of system to record the time, location, organization, data type and other information about the evidence collected. A Globally Unique Identifier (GUID) is also assigned to each piece of digital evidence to prevent any miss-identification of similar pieces of evidence. If a PDT is applied to the digital evidence, the time, name/version of PDT software and any other information needed to recreate the PDT, along with a new GUID for the transformed data is all recorded in the system.

In effect, the Basic DEB is the electronic equivalent of the paper-based audit log process. It is designed to detect and prevent accidental errors, not malicious attacks. No details are given on how to protect the records from tampering by a malicious attacker.

#### DEB with hashing

This option builds upon the Basic DEB in that the records along with the digital evidence data itself is all used as the input to create a cryptographic hash (effectively an integrity check). This hash is then to be "stored in a manner which provides assurance that it cannot be changed over time" and two methods are provided to achieve this.

The simplest method to store the hash such that it can not be changed is to store the hash in a database/data centre with physical access control and other conventional data security procedures (see chapter 3). The other method is to submit it to a system where it is published to a wide audience who can witness the hash and verify that it has not been changed. This is the concept behind blockchains and is discussed further in section 3.4.

Both of these methods allow the DEB with hashing to offer some protection against malicious attackers. Once the hash has been created and securely stored, any attempt to tamper with the data will be detectable by simply recalculating the hash and checking that it matches the one in storage.

#### DEB with input assurance

The DEB with input assurance also builds upon the Basic DEB in that along with all the basic records, it also records the delivery protocol or technique used to input data into the DEB system. This is usually in the form of credentials of the person who inputted the data, along with how and when they inputted the data, which assigns responsibility for the data's authenticity to a given person.

DEB with input assurance ties the integrity of the data to the person responsible for it. This is useful for cases where the responsible person can testify (in court or elsewhere) that the data is true and correct. This is similar to, and fits in with, traditional evidence procedures in court, which is discussed further in section 2.6.

### 2.3.4 ISO/IEC 17025

ISO/IEC 17025, titled "General requirements for the competence of testing and calibration laboratories" [14] is a widely accepted standard for scientific laboratories around the world. It sets out the requirements for a scientific laboratory and the organization that operates it. This includes requirements in areas such as impartiality and confidentiality of results, laboratory management, technical staff training, equipment maintenance and calibration and ensuring the laboratory is adequately resourced. Many countries have national accreditation bodies that provide laboratory accreditation to the ISO/IEC 17025 standard. In Australia, this is the National Association of Testing Authorities [15].

ISO/IEC 17025 focuses on two main aspects of laboratory work: testing and calibration. Testing refers the process where a sample is provided to the laboratory for testing. Technical staff will then use the laboratory's resources to preform tests on the sample and then report the results (and potentially analysis) back to the customer. Calibration is the process where a measurement instrument of unknown accuracy is compared to a reference with a known accuracy. From this process, the accuracy of the measurement instrument can be calculated and known for future use of the measurement instrument.

#### **Relevance to Digital Forensics**

ISO/IEC 17025 accreditation is a mandatory requirement for digital forensic labs in the UK. However there is some doubt over how well this standard applies to digital forensic procedures with many experts in the field suggesting that it is not relevant [16]. Along with the high cost of accreditation, many experts suggest that the requirements of ISO/IEC 17025 simply does not fit the work that is carried out by digital forensic practitioners.

One of the requirements of ISO/IEC 17025 is that laboratory equipment be tested, calibrated and verified. However, the equipment used in digital forensics is usually software packages designed to search, analyze and visualize data. Requiring that every copy of the software (in the hands of many digital forensic labs) each be individually tested, calibrated and verified is large waste of resources since copies of software all behave in the same way. Potential tampering with the software is an issue that has already been dealt with by using digital signatures to sign the software [17] (discussed further in section 3.3.4).

# 2.3.5 Forensic Photography (ANZPAA)

One of the most common forms of digital evidence, forensic photography is the process in which a law enforcement officer creates a visual record of a crime scene, in the form of video or still photographs, with the aim to present them in court as evidence. In order to maintain evidence integrity and chain of custody, the Australia New Zealand Policing Advisory Agency (ANZPAA) have published guidelines for law enforcement agencies to use when collecting forensic photography [18].

In addition to explaining file formats, image processing and analysis techniques, and best practices for transportation and storage of digital memory devices, it also outlines procedures to help ensure evidence integrity and chain of custody. The core part of this is the audit trail which is a log, recorded manually by the investigators, of all actions taken in relation to the photographs.

The storage of forensic photographs is covered in detail. Transferring images to a secure database is recommended to be done as quickly as possible. This can be a data server with appropriate access control or a number of other data storage technologies. Consideration must be given to how long the data will be stored for and if the storage media will last in archival storage situations. Write-once memory, in particular write-once CDs, are recommended to protect evidence integrity. However, write-once CDs are now largely obsolete.

While reducing the time between the photograph being taken and its transfer to secure storage can reduce the chances of both accidental and malicious tampering, it doesn't eliminate it completely. The photo is still stored on a reusable memory card after it is taken, and until it makes it to the secure storage, it can easily be tampered with by whoever is in possession of the memory card. Photos can also be deleted (even accidentally) and there may be no proof they ever existed.

# 2.4 Other research

There has been some published research into the area of digital evidence integrity and chain of custody. Whilst these have been focused on very specific problems, they are discussed below and may be applicable to other problems.

## 2.4.1 Custom SD card with log file

One possible improvement to the forensic photography process is a modified memory card that contains a log file stored in write-once memory [19]. In this system the memory card logs all read, write and erase operations to the log file along with a cryptographic hash of the written data. Any attempt to maliciously alter or delete the photo data would be detectable by comparing the hashes in the write-once memory to the data stored in the main memory of the card.

However this does not protect against intercept during the legitimate read and write operations. The other security weakness is that the log file from the memory card is required during verification. This requires that the log file be transferred to the secure storage (which is another opportunity for malicious tampering) or the memory card used needs to be physically present during verification which is difficult given that memory cards are reused, can fail and can be accidentally destroyed or lost.

### 2.4.2 Watermarking

The use of a watermark has been considered in [20] along with a biometric photograph of the photographer's eyeball. This allows strong proof of who took the photo and what camera it was taken with to be embedded in the image file as a watermark and cryptographic hash. However there is little protection from manipulation during the process of transferring the

image to secure storage. Manipulating an image, recalculating the hash and then altering the watermark to match is relatively easy to do for someone with the right tools.

# 2.5 Evidence Bags

Physical evidence refers to physical objects that can assist in establishing facts in legal enquiries. This can be due to the object itself, for example, where it came from, who owns it, how did it get there, can all prove useful clues to the investigation. In addition to this, residues on the item, such as fingerprints and DNA, can also assist the investigation. Physical evidence is collected (often from a crime scene) and then presented directly in court, or tested and analyzed to revel further information.

To secure the physical evidence, the objects are placed in purpose designed evidence bags for transport and storage. To prevent contamination, these evidence bags are designed to be single use only. They are designed to be tamper evident and are stamped with serial numbers to prevent swapping out tampered bags with new ones [21].

In order to securely transport digital evidence to the lab, we require the digital equivalent of an evidence bag. In an effort to utilize physical evidence bags for digital evidence, police officers have simply placed the memory device in a evidence bag for transport and storage. This makes sense in the case where the memory device itself is also physical evidence. However when the digital evidence is independent from the memory device, this process may not offer any security benefits.

# 2.5.1 Digital Evidence Bags

The idea of a "Digital Evidence Bag" (DEB) is a relatively novel concept to create the digital equivalent of a physical evidence bag. This device would be used for the secure transport and storage of digital evidence. While mentioned in *ETSI TS 103 643* [13], the term DEB is only used to roughly outline the process of transporting, storing and analyzing digital evidence, as oppose to a physical device used for carrying out this process.

## 2.5.2 Requirements for a digital evidence bag

There is a need for a secure digital evidence bag which can be used to collect and transport digital evidence from the crime scene. After investigating existing procedures for physical evidence and the requirements for physical evidence bags, we formed these requirements for a digital evidence bag:

• Tamper evident. Any attempt to alter or erase the data on the device would be detectable.

- Un-forgeable. Any attempt to swap out the device for a fake one should be detectable.

- Clean. Before digital evidence is loaded onto the device, it needs to be clean and not contaminated with any data from a previous use.

- Offline. During evidence collection and transport, there may not be any network connection available.

The requirement of confidentially can also be included sometimes depending on the case. As with physical evidence, this is usually achieved with physical access control, although cryptography can also be used to this achieve confidentially with digital evidence. Since both of these solutions are well researched and are straight-forward to apply to digital evidence, we have not looked into the confidentially requirement any further in this work.

#### **Tamper Evident**

This is the requirement most often associated with physical evidence bags. If anyone attempts to alter or destroy the evidence, the evidence container needs to clearly show that it has been tampered with. Any attempt to alter the evidence without being detected needs to be prevented. Physical evidence bags achieve this with a one-time seal. After the evidence has been collected and sealed in the bag, it can only be accessed by tearing or cutting the bag open which is a destructive and detectable act.

#### Unforgeable

A malicious attacker can get around the tamper evident properties of a physical evidence bag by removing the evidence from the original bag, tampering with it and then resealing it inside a new bag that looks identical to the original. To prevent this, we need to ensure that each bag is unique and that a forged copy of it cannot be feasibly created. Physical evidence bags achieve this by stamping each bag with a unique serial number that is also recorded in a database.

#### Clean

Before use, we need to ensure each evidence bag is clean and free from any contaminants. This is usually achieved be using only new bags that have been shipped and sorted in protective packaging. After a bag has been used, it is disposed of.

In the case of digital evidence container we need to ensure the memory components are completely erased and contain no trace of data from previous uses. Or, if the devices are low-cost, it may be desirable to dispose of them after a single use.

### Offline

Evidence may be collected in places without network connections. Devices may also be powered off during transport. As such, a digital evidence container must still operate correctly and provide security whilst operating offline or without power.

# 2.6 Digital Evidence in Court

As with all evidence presented in court, digital evidence must comply with the *Evidence Act* 1995 [22] to be admissible in court. For the digital evidence to be admissible, the witness who collected the evidence (often a police officer) must testify to the court that the evidence is authentic and has not been tampered with. The court can then question this witness to establish the witness' credibility and hence the credibility of their evidence. Audit logs created during the processing and storage of the digital evidence are also presented to the court to assist in establishing credibility.

This process is very time consuming for police officers, lawyers and judges since judges rely on these testimonies to determine the authenticity of the digital evidence. There are also cases where the digital evidence has been collected by someone other than a police officer, for example, CCTV footage from a camera operated by a property owner or company employee. In this case the property owner or employee must testify to the court which can be intimidating for these people who usually have no involvement or knowledge of the court processes [23].

There is also a motivation to improve the process to reduce the time courts spend authenticating evidence. Having a witness testify, reading their submissions and making a judgment on their evidence is a time consuming process. The widespread popularity of fake videos (so called "deep-fakes") has only made this issue worse. Every piece of digital evidence is now scrutinized heavily since creating fake digital evidence is now viewed as a easy thing to do. While experts can easily distinguish most fake digital evidence, doing so takes time and experts then need to explain to the court how they reached their conclusion which uses up more court time. Hence a quicker, more automated system for authenticating digital evidence in court would be beneficial.

# 2.7 Conclusion

The digital forensics field deals with the collection of digital evidence in a way that evidence integrity and chain of custody is maintained. This ensures the evidence is admissible in court and trustworthy when it is used to establish facts in legal problems. The forensic process of identification, collection, examination, analysis and presentation outlines how a digital forensic evidence is handled. Evidence integrity and chain of custody must be maintained throughout this process.

There are a number of standards providing procedures and technology to assist in maintaining evidence integrity and chain of custody. This largely relies on the investigators keeping good audit records of all actions done with the evidence. Secure physical storage is also recommended where ever possible. These are mostly the same procedures used for handling physical evidence which have been adapted for digital evidence. In the case where the device containing the digital evidence is also physical evidence, using physical evidence handling procedures seems to be the right solution.

However in cases where the digital evidence exists independently from the storage medium, the procedures have some inherent downsides and security flaws. There is also a lot of dependence on good record keeping by investigators which is both time consuming and prone to mistakes. Some technical measures are used such as write-once memory and storing cryptographic hashes of the data. These do improve security and reliability to some extent however there is still room for further improvement.

Hence we seek to refine the concept of a Digital Evidence Bag, a device for the secure transport and storage of digital evidence. The focus for this device is on use cases where the digital data exists independently from the storage medium, for example, forensic photography, CCTV video and dashcam footage. The four main requirements of the DEB are that it be tamper evident, unforgeable, clean and operational offline. Throughout the rest of this work we will explore how such a DEB might be designed.

# Chapter 3

# **Infomation Security**

# 3.1 Introduction

Information security is an industry and research field focused on protecting the confidentiality, integrity and availability of data (often called the "CIA Triad") [9]. While the use of information security dates back thousands of years, the development, and extensive use of the internet has caused it to become much more common and widespread. Internet security (or cyber-security) has become one of the main applications of information security and as a result, a lot of research has been focused on improving and evolving information security.

There are a number of commonalities between information security and digital forensics. While the procedures used can be quite different, many of the science issues underlying each of these disciplines have common origins and concepts. Throughout this chapter we explore the aims and technology used in information security and how these could be applied to the digital forensics field, in particular to the creation of a Digital Evidence Bag (DEB).

# 3.1.1 Aims of Information Security

The Handbook of applied cryptography [3] defines four core objectives of information security: confidentiality, data integrity, authentication, and non-repudiation. We will briefly define and describe each of these, then discern how each is (or is not) related to forensics.

#### Confidentiality

Confidentially, also known as secrecy, is one of the aims most commonly associated with information security. It involves making sure information is only available to those that are authorized to access it. There are a number of ways to achieve confidentially such as encryption, access control systems and physical protection.