Syracuse University

# SURFACE at Syracuse University

Theses - ALL

12-12-2022

# DESIGN OF TWO STAGE BULK-DRIVEN OPERATIONAL TRANSCONDUCTANCE AMPLIFIER (OTA) WITH A HIGH GAIN FOR LOW VOLTAGE APPLICATION

Pushkar N. Mishra Syracuse University

Follow this and additional works at: https://surface.syr.edu/thesis

Part of the Electrical and Computer Engineering Commons

#### **Recommended Citation**

Mishra, Pushkar N., "DESIGN OF TWO STAGE BULK-DRIVEN OPERATIONAL TRANSCONDUCTANCE AMPLIFIER (OTA) WITH A HIGH GAIN FOR LOW VOLTAGE APPLICATION" (2022). *Theses - ALL*. 648. https://surface.syr.edu/thesis/648

This Thesis is brought to you for free and open access by SURFACE at Syracuse University. It has been accepted for inclusion in Theses - ALL by an authorized administrator of SURFACE at Syracuse University. For more information, please contact surface@syr.edu.

## Abstract

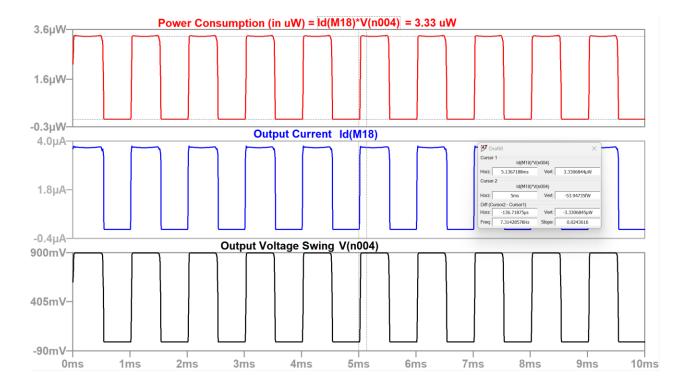

An Operational Transconductance Amplifier (further abbreviated as OTA) is a voltage controlled current source used to produce an output current proportional to the input voltage. A schematic architecture for a 180nm OTA is presented in this thesis with the goal of improving the open-loop gain for a 0.9V supply voltage with a rail-to-rail bulk-driven input stage. Results show an open loop gain 97.14 dB with a power consumption of 3.33uW. An OTA with over 90 dB open loop gain and lower power consumption is highly suitable for low-voltage applications. The slew rate of the OTA is 0.05V/uS with a unity-gain bandwidth of 8.4MHz. A 10uA ideal bias current reference is utilized for the design. The phase margin is around 49.2 degrees.

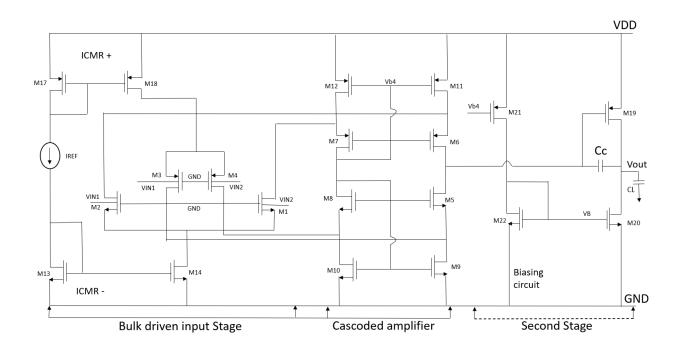

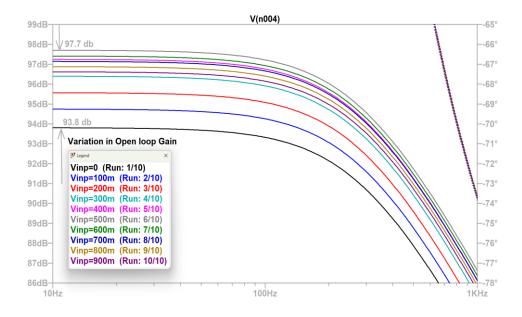

The threshold voltage for a 180nm N-channel Metal Oxide Semiconductor (also known as NMOS) device is around 400mV which restricts the low voltage applications in most amplifier circuits. The fourth terminal (bulk) of the MOS device is utilized to optimize the voltage headroom ( $V_{ds}$ ). The bulk terminal uses a much lesser source to drain voltage than the gate-driven transistors, and the transistors remain ON with an input voltage as low as 0.1V. A bulk-driven input stage ensures the amplification in the subthreshold region (input signal less than the threshold voltage of the MOS device). However, even with the bulk input MOS device, a rail-to-rail input stage is employed to improve the dynamic range for the input signal from 0V to 0.9V with a supply voltage of 0.9V. The fluctuation in open loop gain concerning the change in input signal in the published research is because of the constant instability in the intrinsic transconductance of the input devices. A possible solution is presented in this thesis by adding a second dominant pole to the circuit (i.e., second stage for the OTA), which reduces the dependency of intrinsic transconductance (bulk-

driven device) on the total open loop gain of the amplifier. Thus, a significant gain of 97.14 dB with minimal fluctuations is achieved. Furthermore, adding a second stage improves the gain by distributing the dependency of the gain due to the first stage to both poles in the circuit. Hence, the problem of fluctuating transconductance of the input stage is resolved by the constant intrinsic transconductance of the MOS near the second pole (M19).

To improve the gain, a folded cascoded amplifier connected with the input stage results in a better impedance (in the first stage) known as the gain stage. In the second stage, a large PMOS common source amplifier gives a good output current compared to the input stage to enhance the output swing and drive a purely capacitive load of 0.5pF. Furthermore, a miller capacitance is used to compensate for the frequency between the first and the second stage and improving the unity-gain bandwidth. An additional biasing circuit in the second stage amplifies the current output of the first stage and thus improving the slew rate of the entire device. In addition, the biasing circuit resolves the biasing issues for the second-stage common-source amplifier. It improves the output swing of the device to obtain a clean/undistorted output waveform.

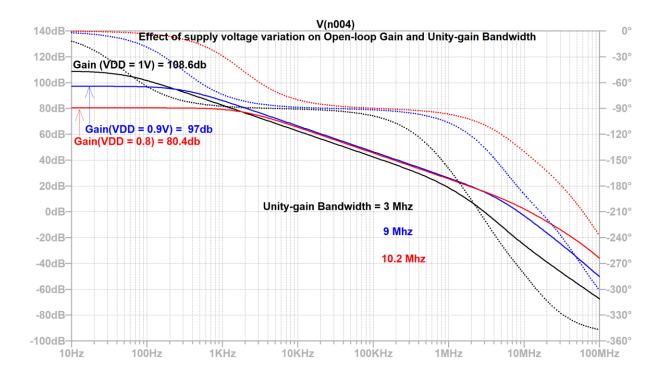

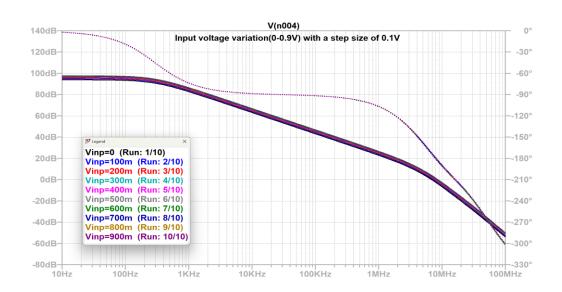

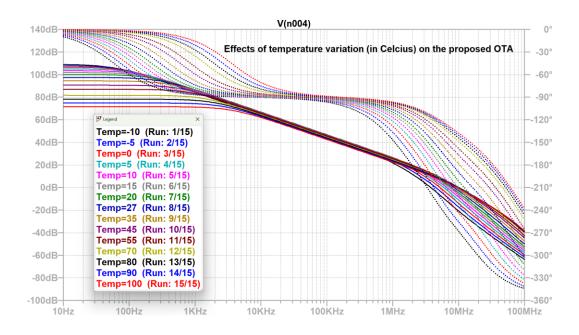

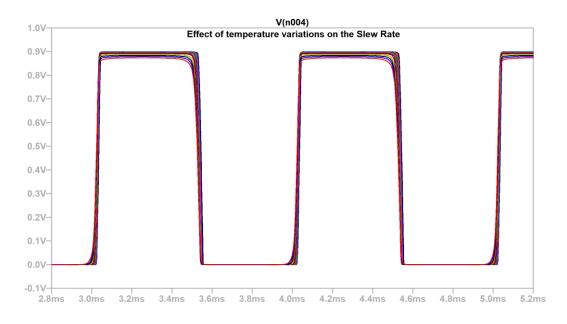

All the simulations are carried out in the LTSpice simulation tool to test the waveforms and bode plot for open loop gain and phase margin (49.2 degrees) at different processes (slow, typical, and fast), input voltages (0-0.9V), supply voltage (0.8V, 0.9V, 1.0V) and temperatures (-10 to 100 degree C).

## DESIGN OF TWO STAGE BULK-DRIVEN OPERATIONAL TRANSCONDUCTANCE AMPLIFIER (OTA) WITH A HIGH GAIN FOR LOW VOLTAGE APPLICATION

by

Pushkar Nath Mishra

## B.E., BMS College Of Engineering, 2019

Thesis Submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering.

> Syracuse University December 2022

Copyright © Pushkar Nath Mishra 2022

All Rights Reserved

# Acknowledgements

It gives me immense pleasure to convey my heartfelt gratitude to my thesis supervisor Prof. PK Ghosh, for allowing me to pursue my thesis on a topic of my choosing and interest. His suggestions, constant guidance, motivation, and patience helped me get through my thesis successfully. Besides my advisor, I would like to express sincere thanks to the rest of my thesis committee, Professor Pankaj Jha, Professor Younes Radi and Professor Sara Eftekharnejed for taking out time from their busy schedule to review my thesis. I thank my fellow friends for their great input, persistent encouragement, and unwavering support during my journey.

I would like to express deep appreciation towards my parents for their unending and unconditional support, love and for encouraging me throughout my graduate program at Syracuse University.

# Table of contents

| Abstract                                      | i        |

|-----------------------------------------------|----------|

| Acknowledgement                               | <b>v</b> |

| Table of contents                             | vi       |

| List of figures                               | viii     |

| List of tables                                | xi       |

| Chapter 1: Introduction                       | 1        |

| 1.1: Literature survey                        | 3        |

| 1.2: Thesis outline                           | 11       |

| Chapter 2: Background knowledge               |          |

| 2.1: IV characteristics                       |          |

| 2.2: Single stage amplifiers                  |          |

| Chapter 3: Method and approach                |          |

| 3.1: Understanding the working of generic OTA | 25       |

| 3.2: Bulk driven input stage                  |          |

| 3.3: Folded cascoded gain stage               |          |

| 3.4: Second stage for OTA                     |          |

| Chapter 4: Analysis                           |          |

| 4.1: Introduction                             |          |

| 4.2: Small-signal analysis and transfer function      |    |

|-------------------------------------------------------|----|

| 4.3: Gain of the OTA                                  | 46 |

| 4.4: Gain-bandwidth product and phase margin          |    |

| 4.5: Slew rate                                        | 51 |

| 4.6: Aspect ratio (W/L) of the transistors            | 52 |

| Chapter 5: LTSpice simulations                        | 58 |

| 5.1: DC characteristics of 180nm technology           |    |

| 5.2: Variation of transconductance with input voltage | 61 |

| 5.3: Operating points from LTSpice                    | 63 |

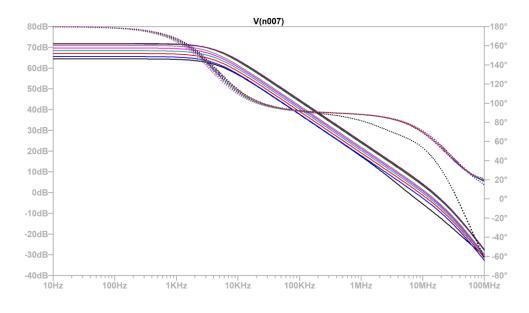

| 5.4: Bode plot (first stage)                          |    |

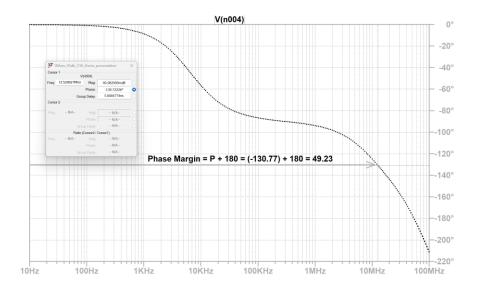

| 5.5: Phase margin                                     | 67 |

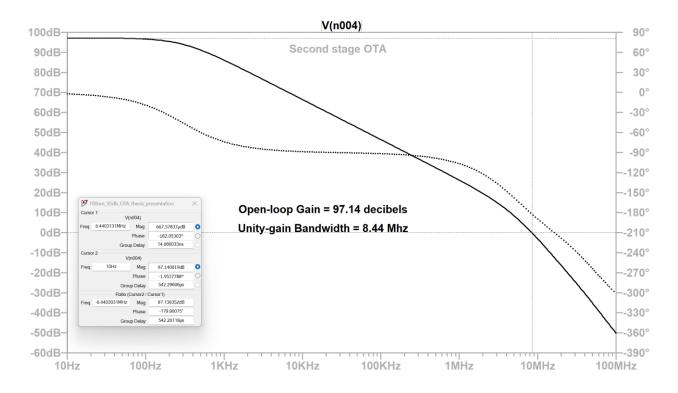

| 5.6: Bode plot (second stage)                         |    |

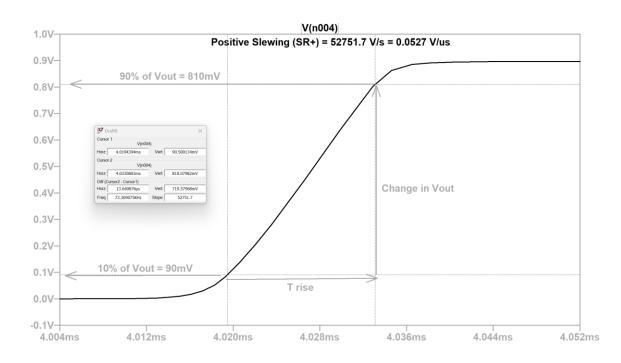

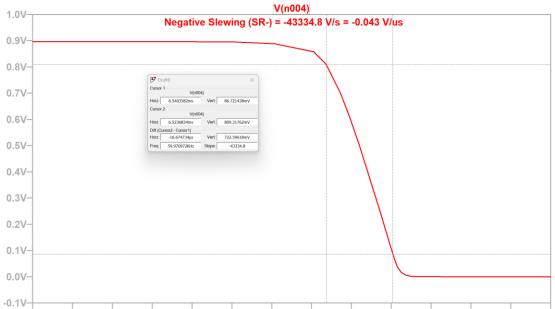

| 5.7: Slew rate                                        | 69 |

| 5.8: Variation in supply voltage                      | 71 |

| 5.9: Variation in input voltage                       | 72 |

| 5.10: Effect of different temperatures on OTA         |    |

| 5.11: Power consumption                               | 74 |

| Chapter 6: Conclusion and future works                |    |

| 6.1: Conclusion                                       |    |

| 6.2: Contribution                                     | 77 |

| 6.3: Future work         | 80 |

|--------------------------|----|

| Bibliography/References  | 82 |

| Vita (biographical data) |    |

# List of figures

| Figure 1.1: Gain boosting amplifier                                                         | 3 |

|---------------------------------------------------------------------------------------------|---|

| Figure 2.1: Cross-section of a) NMOS b) PMOS12                                              | 2 |

| Figure 2.2 a) Circuit diagram of 180nm NMOS b) Simulation for DC characteristics in LTSpice |   |

| 1                                                                                           | 2 |

| Figure 2.3: a) Common-source (CS) amplifier with resistive load b) AC analysis14            | 1 |

| Figure 2.4: Diode connected a) NMOS b) PMOS1                                                | 5 |

| Figure 2.5: a) CS stage with diode connected load circuit b) AC circuit10                   | 5 |

| Figure 2.6: a) Circuit for CS stage with current source load b) AC analysis1                | 7 |

| Figure 2.7: Complementary CS stage1                                                         | 3 |

| Figure 2.8: a) Small-signal analysis for complementary CS stage b) Equivalent circuit19     | ) |

| Figure 2.9: CS stage with triode load20                                                     | ) |

| Figure 2.10: a) CS stage with source degeneration b) AC analysis2                           | 1 |

| Figure 2.11: a) Source follower configuration b) AC analysis                                | 3 |

| Figure 2.12: Source follower with constant current source                                   | 3 |

| Figure 2.13: a) Common-gate circuit b) AC analysis                                       | 24      |

|------------------------------------------------------------------------------------------|---------|

| Figure 3.1 I/O characteristics of generic OTA                                            | 26      |

| Figure 3.2 a) NMOS input OTA b) PMOS input OTA                                           | 26      |

| Figure 3.3 a) Bulk-driven NMOS b) Gate-driven NMOS c) I/V characteristics of bulk-driven | iven    |

| NMOS d) I/V characteristics of gate-driven NMOS e) Operating point of m1 and m2 in I     | TSpice  |

|                                                                                          | 29      |

| Figure 3.4 Input common mode range for PMOS and NMOS bulk-driven input stage             | 30      |

| Figure 3.5 Folded cascoded OTA with a) NMOS input b) PMOS input                          | 32      |

| Figure 3.6 Folded cascoded OTA with bulk-driven rail-to-rail input                       | 33      |

| Figure 3.7 Common-source amplifier using a) PMOS b) NMOS                                 | 34      |

| Figure 3.8 Second stage for the OTA using a PMOS common source configuration with a      | current |

| source load                                                                              | 35      |

| Figure 3.9 Biasing circuit for the second stage OTA                                      | 37      |

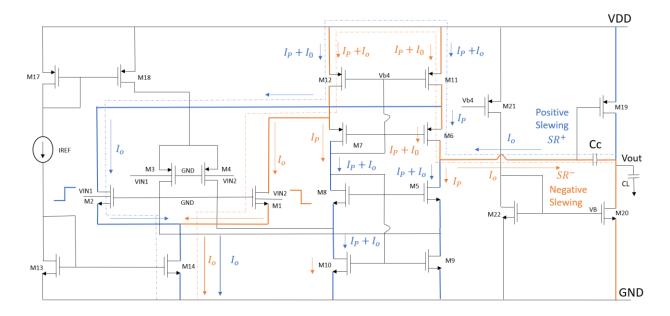

| Figure 3.10 2-stage bulk-driven OTA                                                      | 37      |

| Figure 4.1: Block diagram of the 2-stage OTA                                             |         |

| Figure 4.2: Circuit diagram of the first stage of OTA                                    |         |

| Figure 4.3: Small-signal analysis of the first stage                                     | 40      |

| Figure 4.4: Small-signal analysis of the 2-stage OTA without the miller capacitance      | 40      |

| Figure 4.5: Problem for gain and phase without compensation capacitor                    | 41      |

| Figure 4.6: Miller-effect in the two stage OTA                                           | 42      |

| Figure 4.7: Small-signal analysis of the 2-stage OTA with the miller capacitance                                      | 43 |

|-----------------------------------------------------------------------------------------------------------------------|----|

| Figure 4.8 a) Half equivalent circuit for gain stage b) G <sub>m</sub> calculation c) R <sub>out</sub> calculation d) |    |

| Equivalent circuit for calculation for gain in second stage                                                           | 47 |

| Figure 4.9: Simplified circuit during the positive and negative slewing                                               | 51 |

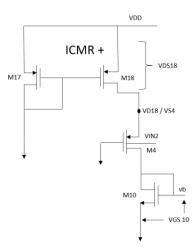

| Figure 4.10: Equivalent circuit for <i>ICMR</i> <sup>+</sup> calculation                                              | 54 |

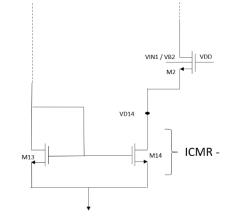

| Figure 4.11: Equivalent circuit for <i>ICMR<sup>-</sup></i> calculation                                               | 55 |

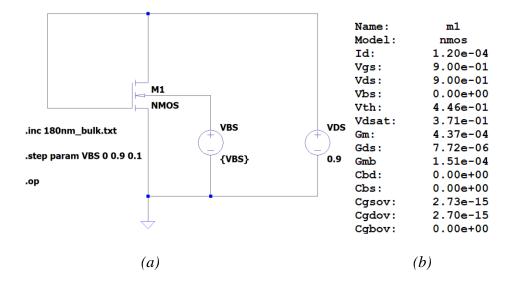

| Figure 5.1: a) Circuit for DC analysis of a single NMOS b) Operating points                                           | 58 |

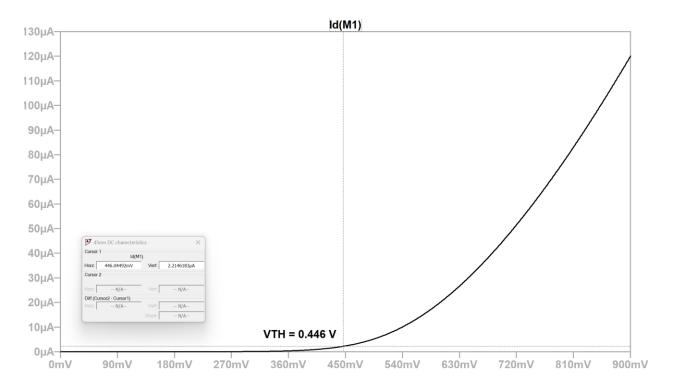

| Figure 5.2: DC sweep for threshold voltage in gate driven NMOS                                                        | 59 |

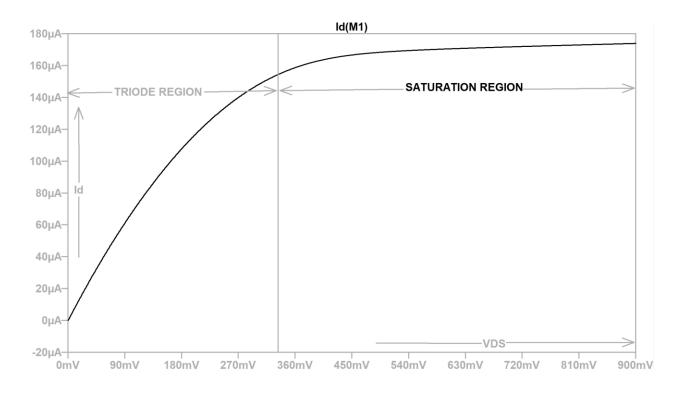

| Figure 5.3: IV characteristics of the NMOS                                                                            | 60 |

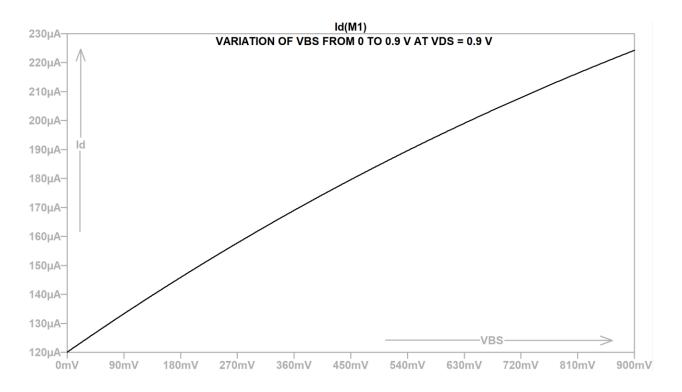

| Figure 5.4: DC sweep for bulk driven NMOS                                                                             | 61 |

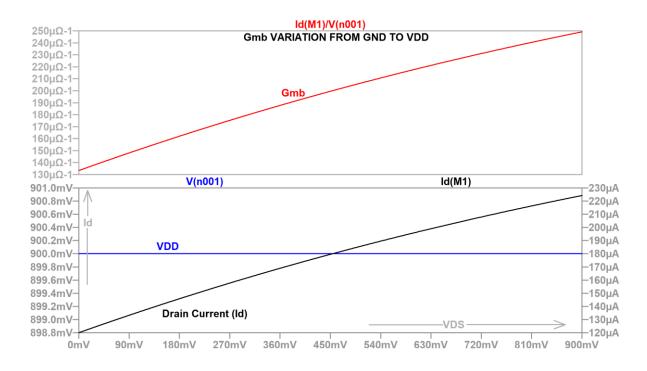

| Figure 5.5: Variation of transconductance over the input common mode range                                            | 62 |

| Figure 5.6: Operating points for variation in the values of $g_m$ and $g_{mb}$ over different input                   |    |

| voltages a) at 0V b) at 0.2V c) at 0.4V                                                                               | 62 |

| Figure 5.7: Bode plot for gain and phase of first stage                                                               | 66 |

| Figure 5.8: Phase margin for the proposed OTA                                                                         | 67 |

| Figure 5.9: Bode plot for gain and phase of second stage                                                              | 68 |

| Figure 5.10: Positive slewing                                                                                         | 69 |

| Figure 5.11: Negative slewing                                                                                         | 70 |

| Figure 5.12: Effect of variation in supply voltage on gain and phase                                                  | 71 |

| Figure 5.13a: Effect of variation in input voltage on gain and phase                                                  | 72 |

| Figure 5.13b: Magnified version for 5.13a                         | 73 |

|-------------------------------------------------------------------|----|

| Figure 5.14: Effect of variation in temperature on gain and phase | 73 |

| Figure 5.15: Effect of variation in temperature on slew rate      | 74 |

| Figure 5.16: Power consumption                                    | 75 |

# List of tables

| Table 4.1: Aspect ratios of MOS devices for the proposed OTA   | .57 |

|----------------------------------------------------------------|-----|

| Table 5.1: DC Operating points for the NMOS devices in the OTA | .63 |

| Table 5.2: DC Operating points for the PMOS devices in the OTA | .64 |

| Table 5.3: Expected and simulated phase margin for the OTA     | .68 |

| Table 6.1: Expected and simulated results for the OTA          | .76 |

| Table 6.2: Comparison for results in similar research          | .79 |

## **Chapter 1: Introduction**

Portable electronics are becoming increasingly popular amongst many users in different application areas. Wearable intelligent devices make life hassle-free in terms of domestic applications (such as smart-ring, smart glasses, and smart earplugs) as well as biomedical applications like pacemakers, hearing aid for hearing-impaired individuals, blood pressure monitoring systems and other biosensors (Electrocardiography or ECG monitoring systems). In wireless body sensors, ECG amplifiers occupy a large proportion of chips in ECG monitoring systems [1]. For example, every small rhythm in your heart has hidden information regarding the health of a person. Sometimes these electrical activities can be significantly smaller, beyond imagination (as low as 0.001V), this calls for employing an addition amplifier circuit for observing every minute details of those electrical activities for understanding the depth of a person's health. An Operational Transconductance Amplifier (OTA) plays a significant role in amplifying the signals from the sensors (body sensors and intelligent sensors for low voltage applications) and further processing [2] the amplified signal to transmit the desired result through the communication channel.

The constant need for advancement in solid-state electronics forces researchers to optimize the device performance, reduce the cost, boost device speed, reduce area, lower power consumption and, most importantly, increase the battery life. The device's size is a significant factor when designing any analog circuitry. In such applications, reducing the device size optimizes most aspects, such as speed of operation, portability, economic feasibility, and user accessibility. Reducing the size of the battery (supply voltage) is the most common way to reduce the overall

footprint and weight of the device. Reduction in supply voltage reduces the power consumed by the amplifier and improves the device's battery life. However, with a reduction in supply voltage, comes the biasing issue because the threshold voltage of a 180nm MOS device used in this design is around 400 mV. This is where we utilize the bulk-driven functionality of our MOS device, hence bypassing the threshold voltage requirement of a transistor to turn ON. Several designing techniques [3], around low voltage analog design can be found in the literature, such as using the MOS in the sub-threshold region (poor gain-bandwidth product), floating gate MOS (increased cost and lower gain), and self-cascaded MOS devices (does not provide many advantages for low voltages). Hence, bulk-driven MOS device is beneficial for low-voltage applications. The main disadvantage of a bulk-driven device is that the intrinsic transconductance of the bulk-driven device is much lower than the gate-driven device, which lowers the total DC gain of the amplifier. To improve the overall gain of the OTA, a gain stage is added to the input stage bulk-driven transistor. This two-stage process improves the gain at the lower voltages.

In addition to reduced size, there is a need to maintain a balance between the stability and the dynamic range of the device to obtain uniformity in the device's operation. Improved dynamic range allows the use of maximum voltage headroom available in the supply using a rail-to-rail input stage described in detail, in Section 1.1 and Section 3.2. Moreover, adding a second stage to the device can improvise the frequency response, bandwidth, and common-mode gain. Higher gain reduces the dependency of the total open loop gain on the bulk-driven input. However, with an improved gain, the power consumption should also be balanced for the device allowing it to work in low power consumption levels. The uniformity in the device operation makes the device more reliable for adverse conditions such as under different Process, Voltages and Temperatures (also

known as PVT corners). To ensure the conformity with the expected results, the schematic design of the circuit is simulated in LTSpice tool using 180nm product design kit [4] (abbreviated as PDK), to avoid the leakage current as we reduce the chip size further. This improves the device performance by reducing the power consumption, leakage current, and hence improving the device speed.

### **1.1 Literature survey**

The ever-rising popularity of OTA, in the field of low voltage application ushers the way for more research and development in the basic structure of amplifiers which desires an improved optimization in gain. A TSMC 0.35  $\mu$ m MOS technology [5] was designed with a dual bulk-driven input at 0.9V supply voltage and reduced power consumption. The amplifier's open loop gain is 62 dB, where the input stage is rail-to-rail. The paper also includes a shut-down circuit which avoids the leakage current, and the risk of latch-up, making it highly suitable for the portable biomedical monitoring system and battery power devices. The input common mode range is not rail to rail, restricting the usage of the amplifier from many applications such as a rail to rail I/O swing described in [6]. A topology that combines the bulk-driven differential pair with dc level shifters with the transistors working in the weak inversion region. The circuit works on a 600-mV supply voltage which is even below the threshold voltage and provides a rail-to-rail input voltage swing, opening a completely new horizon in the field of Medical Electronics. Furthermore, it uses a set of passive elements designed to work in low-power, low-voltage applications with a gain of 69 dB [6].

To understand the application of an Operational Transconductance Amplifier (further abbreviated as OTA) in biomedical application [7] [8] [9], a PMOS input stage transistor operating in the subthreshold region [7] has proven to be more suitable than gate-driven or bulk-driven input stages. Nevertheless, biasing the input transistor in the subthreshold region can be problematic when implementing the circuit for adverse conditions where the supply voltage varies frequently. It can move the input MOS in the saturation/strong inversion region, which defeats the purpose of obtaining high transconductance necessary to obtain the required gain. The proposed circuit in [7], contains a pre-amplifier and low pass filter for attenuating higher frequency components which helps flatten the gain in the passband and attenuate the high-frequency signal with a cut-off of 100 Hz suitable for the ECG signals [7]. However, the unity gain bandwidth [7][8] is low for such a high gain application and makes the gain unstable at different process and temperatures. With an improved unity-gain bandwidth [9], the gain can be stabilized at higher temperatures. In addition, the frequency response is unsuitable for high-frequency operations such as the constant transconductance input stage [10] which affects the irregularity in total open loop gain of the amplifier. The transconductance depends upon the effective  $V_{gs}$  of the device as described in the equation below:

$$g_m = \mu_n C_{ox} \frac{W}{L} V_{gs-effective}$$

Hence  $V_{gs-effective}$  is kept constant for the NMOS and the PMOS input stage to achieve a balanced rail to rail input stage. To satisfy this criterion, [10] compares different type of devices that can keep the effective gate-source voltage constant using an ideal diode pair, and an Electronic Zener. An ideal diode conducts only in forward biased condition while an electronic Zener conducts in both forward and reverse biased conditions. An ideal Zener diode has a constant voltage V<sub>c</sub> and it is placed between the NMOS input pair and the PMOS input pair because it satisfies the given criterion [10] to keep the  $V_{gs-effective}$  constant and hence a constant  $g_m$ . Instead of an ideal Zener diode (not used in practical applications), a diode pair can also be used to control the  $g_m$  using two diodes connected between the input pair. The aspect ratios are maintained significantly large (around 6 times the input stage transistors for the device) [10] to give voltage equal to that of the Zener voltage. The current in the diode reaches an estimated value of three-times the reference current while the input devices have a current of  $I_{ref}$ . This ensures the constant overall transconductance with approximate 23% variations [10] with the variation of the common mode input voltage. It is observed that the variation in transconductance of the input stages in the twodiode architecture is because of the transconductance ( $g_m$ ) dependence on the current ( $I_{ref}$ ) between them. This issue is resolved by increasing the gain of the input Zener using MOSFETs, mitigating the dependance of current variation on the  $g_m$ . This yields a better result and a more stable transconductance with a lesser deviation of 8% [10].

A similar architecture using a cost-effective 0.6um CMOS process with a gain of around 65.8 dB [11] and a rail-to-rail gate-driven input stage with lower power consumption can also be used for higher input common mode range. The proposed architecture provides constant transconductance over the common-mode range with a 6.5% variation like reference [10]. Two MOS devices connected in series in which one acts as a current source and another as a current sink [11]. The device that carries a higher current enters the triode region, and the lower current device remains in saturation. The device with lower current conducts, and the other one remains off or has the nominal value. The constant fluctuation in the total transconductance of the MOSFET is often observed because of the dependence of  $g_m$  on the difference in mobility of electrons ( $\mu_n$ ) and mobility of the holes ( $\mu_p$ ), which can be further improved by selecting W/L ratios of the n-channel

and p-channel MOS such that the beta values become equal ( $\beta_n = \beta_p = \beta$ ) [11]. Width of the MOS devices can be modified in such a way that the ratios of  $W_n$  to  $W_p$  should be equal to  $\frac{\mu_n}{\mu_p}$ , if the lengths are matched. The circuit works with the least variation in the total transconductance. As depicted in [11], when current entering through any device goes to its nominal value, the transconductance shoots above the average value affecting the overall gain to a negligible value. This mostly happens due to the low input impedance (increased demand for bias current at the input) and one of the devices entering the triode region. The amplifier's input impedance is low, which limits the gain-bandwidth product and the overall gain. Therefore, an additional gain stage can further bolster the gain and the output voltage swing.

According to the rail-to-rail OTA described in [12], there can be three possible rail-to-rail OTA designs. We can either process the input stage close to the ground or positive supply voltage or both. To implement an input stage to reach the positive rail or the supply voltage, an N-channel MOSFET must be used, followed by fixing the drain voltage close to the given supply voltage. The input common mode voltage ranges from the VBS and VDSAT above the ground to the supply voltage  $V_{DD}$ . A negative/ground rail input stage for an OTA using a P-channel MOSFET should be implemented while fixing the device drain close to the ground or VSS. The input common-mode voltage ranges from ground to a voltage level which is VBS and VDSAT below the positive supply voltage  $V_{DD}$ . The above two topologies of input stages can be combined to form a complete rail-to-rail input stage which will work simultaneously even if one of the stages do not get enough input common-mode range. The only drawback in implementing a proper rail-to-rail input stage over the entire range of operation from ground/VSS to supply voltage/ $V_{DD}$  is the fluctuating

intrinsic transconductance of the transistors. The input transistors' transconductance varies in most cases, giving different gains at different input voltages which can be fixed by the topologies described [10][11]. Also, the gain of the amplifier can be divided into two stages to split the dependence of gain on the intrinsic transconductance of the input pair.

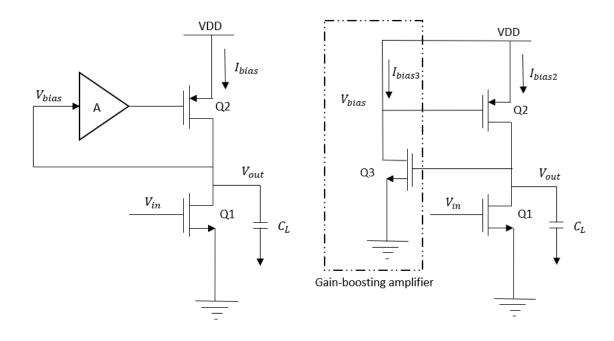

A 3-stage OTA operating on a supply voltage lower than the threshold voltage (around 0.25V railto-rail) [13] is designed for smartphones and wearable electronics with improved gain and the least power consumption using asymmetric self cascoded transistors which increases the output impedance with the help of source degeneration using the lower MOS device in each pair. The improved gain on a subthreshold supply voltage is a proficient way to design the circuit for low voltage applications but the number of transistors and their sizes shown in the paper [13]  $(W/L_{M13} = \frac{320}{0.12} = 2,666)$  are massively larger than usual transistors, which consequently makes the chip area larger and not suitable for applications where size is the main factor. gain can also be increased with a technique called gain-boosting [14][15], which is responsible for increasing the output impedance by adding a feedback loop, followed by the gain. The feedback amplifier is used to increase the gain by 1 and the drain-source voltage is kept as stable as possible. The amplifier increases the output impedance to a significant value using a feeder of one plus the loop gain as shown in fig. 1.1.

Figure 1.1: Gain boosting amplifier [14]

$$R_{out}(s) = g_{m1} \cdot r_{ds1} \cdot r_{ds2} (1 + A(s))$$

Gain of this stage is given by  $A_{\nu}(s) = \frac{V_0(s)}{V_{in}(s)} = -g_{m1} \cdot (R_o(s))||\frac{1}{sC_L})$ . Since the output impedance is increased by a factor of (1+A(s)), therefore the gain of conventional cascoded amplifier will also increase significantly. To further enhance the gain, a parallel combination of several gain-boosting amplifiers can be cascaded, called Repetitive gain-boosting amplifiers [16]. Nevertheless, while designing an amplifier for low voltage applications one needs to consider reduction of the number of transistors between the two rails. To design a buffer amplifier for the NMOS and PMOS the number of transistors increase almost to the double of a conventional cascoded amplifier which gives rise to the depletion of voltage headroom required for biasing of each transistor at a low supply voltage thus causing the transistors to go in triode region. Hence, this type of design is good for 3V [15] and 5V applications [16] but not suitable for, which is the aim of this work,  $V_{DD} = 0.9$ V.

A Gm-C filter is designed using 180 nm CMOS bulk-driven OTA with a THD (total harmonic distortion) of 0.057% [17]. The input common mode range is better than conventional amplifiers because of the bulk-driven input stage but the  $g_m$  variation with varied peak to peak input voltages and frequency variation is more than desired. The output frequency can still be improved by using a folded cascoded structure or a gain boosting technique [14]. A 14 dB OTA described in [18] is designed for medical applications on a 1V rail to rail supply. All the transistors used are bulkdriven and bulk to channel junctions are reverse biased so that the voltage between them control the current flow from source to drain hence it works on a very low voltage and low power consumption. The input common mode range achieved is the maximum but the effective intrinsic gain  $(g_{mb})$  of a MOSFET is much lower than the intrinsic gain  $(g_m)$  of the gate driven MOS giving a lesser gain compared to the conventional amplifier. The paper [18] was reviewed to understand the working of a bulk driven MOSFET in an amplifier. Bulk-driven input stage is also used in Analog-to-Digital converters [19] where power consumption and low supply voltage is the main requirement. The input stage also provides a wide range of common mode input voltage using a supply voltage of around 0.8 V peak-to-peak. The gain stage uses a coupled differential pair to improve the gain 26.53 dB and reduce the power consumption to 0.44 mW [19].

Since the papers discussed earlier show that a bulk driven MOSFET provides a better common mode input range but has a lower intrinsic transconductance, therefore it is important to implement an additional gain stage differential pair for getting a better gain and output impedance. This stage can be included using a folded cascoded OTA with an additional gain of 42.78 dB [20] and a power consumption of around 13.64 uW. The amplifier can be designed based on any technology with

supply voltage of 1.8V or lower. It is observed that the folded cascoded amplifier can further give a higher gain by increasing the channel length and width proportionately taking into consideration the Channel Length Modulation effect. The increase in length of the channel will decrease the drain current and further increase the output resistance of the MOS to improve the overall gain of the circuit. This brings to the fact that one can does not achieve all the parameters simultaneously, there will always be a trade-off between gain, bandwidth, and supply voltage of the circuit. If we increase the gain, bandwidth will deteriorate. On the other hand, if we reduce the supply voltage for low voltage applications, it will be hard to achieve higher transconductance values from smaller transistors with a perfect biasing.

In contrast to the work [10][11], in this research, an attempt has been made to achieve a rail-to-rail OTA with the supply voltage as low as 0.9V and a gain as high as 97dB while maintaining an output gain which varies only 4.1% as a function of input voltage. This stable operation is achieved without the need of stabilizing the bulk transconductance of the input MOS pair. Moreover, a moderately good gain-bandwidth product of 8Mhz is achieved. With low voltage, the power consumption is also optimized for the OTA to work on lower power consumption levels. However, when scaling down the technology, the subthreshold leakage, and the gate leakage current increases [26] which further increases the power consumed by the device. To elaborate, static and dynamic are the two types of power consumptions in a MOS circuit. Static power consumption is the power consumption keeps changing with the device parameters and this is the power consumption which should be more than the static power consumption [27] to minimalize the leakage current

and redundant power consumed by the circuit due to leakage. Therefore, 180nm technology is used rather than other available technologies (45nm, 65nm).

### **1.2 Thesis outline**

A brief explanation of the principle of operation of MOS transistors is described in Chapter 2, which includes a variety of configuration techniques for single-stage amplifiers using NMOS and PMOS transistors. Chapter 3 states the method and approach of this thesis to overcome the issues of gain in bulk-driven OTA for low-voltage applications. Moreover, an explanation to understand the basics of generic OTA is provided with an approach to produce high open loop gain with the lower supply voltage and a better dynamic range. Finally, an additional circuit architecture is proposed for biasing of the second-stage OTA to improve the output swing.

The calculations for designing a 2-stage OTA to produce a gain-bandwidth product of 8 MHz and a slew rate of 0.05 V/uS are shown in Chapter 4. In addition, the calculation includes the derivation of the formulae for the transfer function, open-loop gain, phase margin, slew rate and aspect ratios of each MOS transistor. The dynamic range is further calculated using the results from calculations and LTSpice simulation. Chapter 5 shows all the simulations and compares the results from the calculations (in Chapter 4). Moreover, operating points are presented to confirm the expected results with the obtained simulations. Finally, Chapter 6 summarizes work done and its potential contribution towards the practical applications of OTA with low voltage low power applications compared to the earlier research in similar designs, including the future scope and advancements of this research.

# **Chapter 2 Background knowledge**

### 2.1 IV characteristics of the NMOS

We start with a brief description of the DC characteristics of the NMOS to elaborate the impact of the change in drain to source voltage  $V_{DS}$  on drain current  $I_D$  with different values of  $V_{GS}$ .

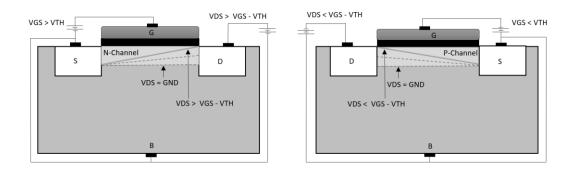

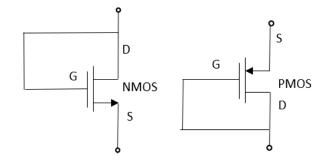

Figure 2.1: Cross-section of a) NMOS b) PMOS [36]

Figure 2.1 shows the cross-sectional view of (a) NMOS structure with the inverted layer (n-channel) and (b) PMOS structure with the inverted layer (p-channel).

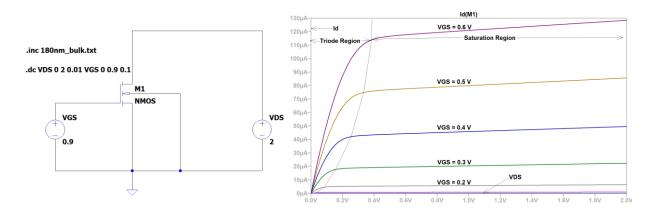

Figure 2.2: a) Biasing of 180nm NMOS b) Simulation for DC characteristics in LTSpice

The NMOS is operating in the saturation region when the drain current becomes almost independent of the drain-to-source voltage and starts acting like a constant current source, whereas

in PMOS, the voltage relation  $V_{DS} \leq V_{gs} - V_{th}$  needs to be satisfied for it to operate in saturation region. In the proposed circuit, all the MOS devices are operating in the saturation region for amplifier application with a certain intrinsic gain and output resistance. The triode and saturation regions are shown in Figure 2.2, for the 180nm technology used in this work. We have analyzed the output current magnitude with different input voltages ( $V_{gs} = 0.2$ -0.6 V) and a fixed drain to source voltage ( $V_{ds}$ ). In the next section, different existing configurations are shown for a MOS to work as a single stage amplifier.

### 2.2 Single stage amplifier

A single MOS transistor can be used either as a voltage controlled current amplifier (in Saturation region) or a resistor (in triode region). There are three basic types of configurations for a MOS device to amplify an input voltage signal: Common-source (CS) amplifiers, Common-drain amplifier, and a Common-gate amplifier. A CS amplifier can be designed with a resistive load, or a diode-connected load, or a current-source load, or an active load, or a triode load or a source-degeneration resistor.

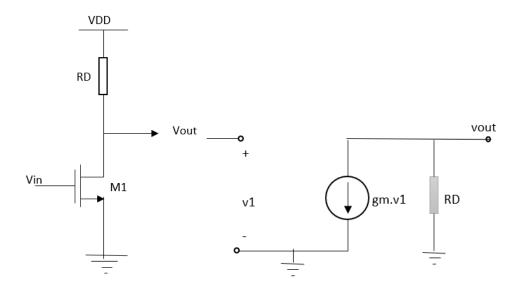

#### 2.2.1 CS stage with resistive load

As illustrated in Figure 2.3a, M1 is Off initially. As  $V_{in}$  increases from 0 ( $V_{out} = V_{DD}$ ) till the input voltage reaches a threshold at this point  $V_{out}$  is maximum. When  $V_{in}$  approaches  $V_{th}$ ,  $V_{out}$  starts drawing the current from the resistor ( $R_D$ ), and the transistor is said to reach the saturation region

where drain current becomes independent of the input voltage  $V_{in}$  (=  $V_{gs}$ ). The output voltage is formulated by applying KVL to the circuit shown in equation 2.1.

$$V_{out} = V_{DD} - I_D R_D = V_{DD} - R_D \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{in} - V_{th})^2$$

(2.1)

If we keep increasing  $V_{in}$  further, the  $V_{out}$  draws more current from  $R_D$ , and the  $V_{out}$  keeps lowering (i.e.,  $V_{in1} = V_{out} + V_{th}$ ).

$$V_{in1} - V_{th} = V_{DD} - R_D \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{in1} - V_{th})^2$$

Further increasing  $V_{in} > V_{in1}$ , M1 goes to the triode region where  $V_{out}$  is represented by:

$$V_{out} = V_{DD} - R_D \frac{1}{2} \mu_n C_{ox} \frac{W}{L} [2(V_{in} - V_{th})^2 \cdot V_{out} - V_{out}^2]$$

(2.2)

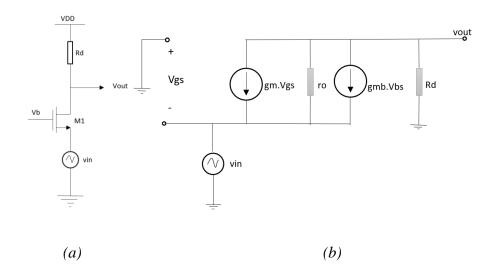

Figure 2.3: a) Common-source (CS) amplifier with resistive load b) AC analysis [36]

Small signal gain of the CS amplifier (fig.2.3b) with a resistive load amplifier is shown below:

$$A_{v} = \frac{\partial V_{out}}{\partial V_{in}} = -R_{D}\mu_{n}C_{ox}\frac{W}{L}(V_{in} - V_{th}) = -g_{m}R_{D}$$

$$\tag{2.3}$$

Therefore,

$$V_{out} = -g_m V_1 R_D$$

(2.4)

The transistor has an intrinsic output impedance  $(r_o)$  that impacts the intrinsic gain of the device,  $A_v = -g_m(R_d||r_o)$ (2.5)

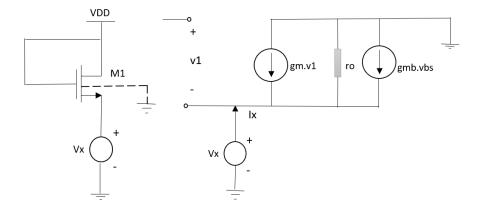

Instead of gate terminal, if the bulk is controlling the channel, i.e., if the input is applied on the bulk rather than the gate, then gain of the device,  $A_v = -g_{mb}R_D$  (2.6)

$$I_d = g_{mb} V_{in} \tag{2.7}$$

It can be observed that as input voltage increases, drain current also increases and the output voltage  $V_{out}$  keeps decreasing. Hence, for the MOSFET to operate in saturation region for amplification, the input voltage should be in the range of  $V_{th}$  to  $V_{out} + V_{th}$ .

### 2.2.2 CS stage with diode connected load

Figure 2.4: Diode connected a) NMOS b) PMOS

In a diode-connected stage, the gate and drain of the transistors are shorted together to operate as a small signal resistor. This forces the transistors to be in the saturation region as the gate and drain terminals are at the same potential. We already know that  $V_{ds}$  should be greater than or equal to

$V_{gs} - V_{th}$  for the device to be in saturation region. If  $V_{ds} = V_{gs}$ ,  $V_{ds}$  will always be greater than  $V_{gs} - V_{th}$ . According to the AC circuit of diode-connected load in fig. 2.5,

$$V_1 = V_x$$

$$I_x = \frac{V_x}{r_o} + g_m V_x$$

Impedance =  $\frac{v_x}{I_x} = \frac{1}{g_m} || r_o \approx \frac{1}{g_m}$

Figure 2.5: a) CS stage with diode connected load circuit b) AC circuit [36]

With the body effect:

$$V_1 = -V_x = V_{bs}$$

Impedance

$$= \frac{v_x}{l_x} = \frac{1}{g_m} + \frac{g_{mb}}{g_m} || r_o \approx \frac{1}{g_m} + \frac{g_{mb}}{g_m} || c_o \approx \frac{1}{g_m} + \frac{g_m}{g_m} || c_o \approx \frac{1}{$$

### 2.2.3 CS stage with current source load

To obtain a large voltage in a single step, we need to increase the load impedance of the common source stage. In the previous two configurations, increasing the load resistor translates to a drop of

dc voltage across the load, which limits the output voltage swing. This phenomenon occurs due to ohms law. Hence, a CS stage with the current source load is suggested because both devices do not follow ohms law. According to Figure 2.6,

Total impedance =

$$r_{o1} || r_{o2}$$

Gain,

$$A_v = -g_{m1}(r_{o1}||r_{o2})$$

(2.9)

$|V_{DSmin}| = |V_{dS2} - V_{th2}| \tag{2.10}$

Lambda,

$$\lambda \propto 1/L$$

(2.11)

$$r_o \propto \frac{L}{I_d} \tag{2.12}$$

Figure 2.6: a) Circuit for CS stage with current source load b) AC analysis [36]

For low voltage applications,  $V_{DSmin}$  can further be minimized by simply increasing the width of M2. If  $r_{o2}$  is not high enough, then the length and width of the transistor M2 should be increased to achieve smaller lambda (maintaining the same overdrive voltage). If L1 is scaled up, the W1 should be scaled up proportionately because  $V_{gs1} - V_{th1} \propto \frac{1}{\sqrt{W1/L1}}$ . Hence, if the L and W are

not scaled up together, the overdrive voltage can increase, limiting the output voltage swing. Compared to a resistive load, a current source load provides a minor voltage swing, but one can achieve a higher gain by increasing the L1 and L2. This configuration is suitable for designing the second stage of an OTA which is discussed in section 3.4.

#### 2.2.4 CS stage with active load (complementary CS)

Instead of using PMOS as the current source load in the previous configuration, we can apply the input voltage to the PMOS and convert it to an Active load (shown in Figure 2.7). Suppose both transistors are in saturation,  $V_{in}$  increases by a change in the output voltage. As  $I_{d1}$  increases,  $V_{out}$  drops because M2 injects lesser current in the output.

Figure 2.7: Complementary CS stage [36]

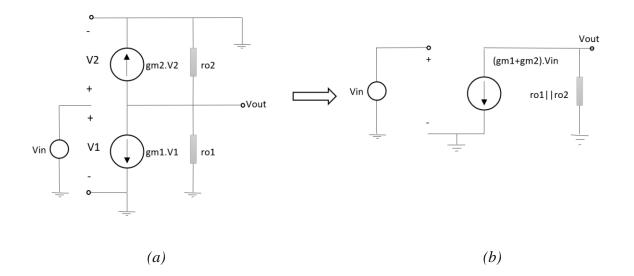

*Figure 2.8: a) Small-signal analysis for complementary CS stage b) Equivalent circuit [36]*

Applying KVL to fig. 2.8:

$$V_{out} = -(g_{m1} + g_{m2}) V_{in} (r_{o1} || r_{o2})$$

(2.13)

Therefore,

Gain,

$$A_v = \frac{V_{out}}{V_{in}} = -(g_{m1} + g_{m2}).(r_{o1}||r_{o2})$$

(2.14)

Compared to the previous configuration, this has the same output impedance but a higher transconductance. This is a good configuration when size of the chip can be large because the number of transistors can be sufficiently large in design of a second stage OTA. Moreover, bias current is a vital function of the PVT variations. According to the figure 2.7,  $V_{gs1} + |V_{gs2}| = V_{DD}$ . Therefore,  $V_{gs}$  will vary if the  $V_{DD}$  fluctuates which leads to a change in the drain current. This makes the circuit unstable for any change in the supply voltage due to any fluctuation in process or voltage.

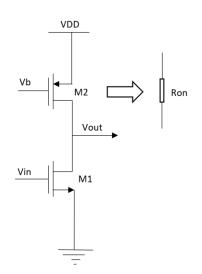

#### 2.2.5 CS stage with triode load

Figure 2.9: CS stage with triode load

In this configuration, the PMOS is kept in the triode region to act as a resistive load. The gate of M2 is biased to a sufficiently lower level to ensure that the load is in the triode region for the entire output voltage swing. The channel resistance of a MOS in triode region is represented as:

$$R_{on} = \frac{1}{\mu_p c_{ox} \cdot \frac{W^2}{L^2} (V_{DD} - V_b - |V_{THP}|)}$$

(2.15)

Ron depends on the  $\mu_p C_{ox}$ ,  $V_b$ , and  $V_{thp}$  that varies with the process and temperature. Moreover, for keeping M2 in triode region one needs to generate precise value for  $V_b$ , which needs an additional complexity in the circuit. This is challenging to design in the practical application for smaller number of transistors, making the circuit less popular in the field of OTA design.

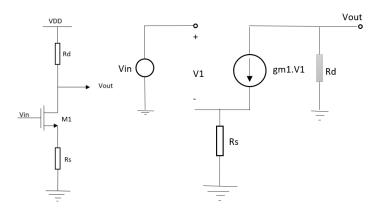

### 2.2.6 CS stage with source degeneration

The non-linear dependence of drain current  $(I_D)$  on the overdrive voltage  $(V_{gs} - V_{th})$  introduces a nonlinearity, making it desirable to soften the device characteristics. CS stage with diode connected load allows post-correction of this nonlinearity. A "degeneration" resistor in series with the source terminal of the MOS is another way to make the input device more linear.

Figure 2.10: a) CS stage with source degeneration b) AC analysis [36]

As  $V_{in}$  increases, the drain current  $I_d$  and voltage across  $R_s$  increases simultaneously. Therefore, a fraction of change in the input voltage appears across the resistor rather than the gate-source overdrive. This softens the device characteristics by adding negative feedback to the circuit making a smoother variation of  $I_d$ .

According to KVL in Figure 2.10a,

Output voltage,

$$V_{out} = V_{DD} - I_D R_D$$

(2.16)

Non-linearity dependence of  $I_d$  on  $V_{in}$ :  $\frac{dV_{out}}{dV_{in}} = -\frac{dI_d}{dV_{in}} R_D$  (2.17)

Equivalent Transconductance,  $G_m = \frac{dI_d}{dV_{in}} = \frac{g_m}{1+g_m R_s}$  (2.18)

If  $R_s$  increase,  $G_m$  becomes a weaker function of  $g_m$  and  $I_D$ .

Gain,

$$A_v = \frac{-g_m R_D}{1 + g_m R_s}$$

(2.19)

Applying KVL to the small signal circuit in fig. 2.10b,  $V_{in} = V_1 + I_d R_s$  (where,  $I_d = g_m V_1$ ) Hence, most of the change in  $V_{in}$  appears across the  $R_s$ , and the drain current is linearized at the cost of lower gain and higher noise.

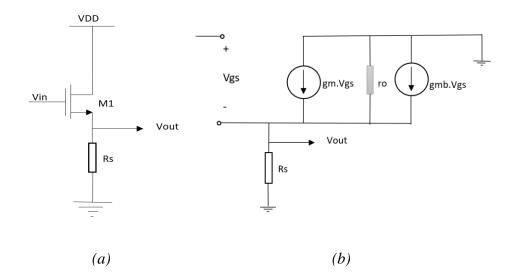

### 2.2.7 Source follower (Common-drain stage)

The common-source stage is suitable for achieving a high voltage gain with a limited supply voltage and an enormous output impedance. But a common-drain stage is used to drive a low impedance load with negligible reduction in gain. It is often used as a buffer placed after the amplifier to drive a low impedance.

Applying KVL to fig. 2.11:

$V_{in} - V_1 = V_{out}$

$$V_{bs} = -V_{out}$$

$$g_m V_1 - g_{mb} V_{out} = \frac{V_{out}}{R_s}$$

Gain,  $A_v = \frac{Vout}{Vin} = \frac{gm.Rs}{1+(gm+gmb)Rs}$  (2.20)

Figure 2.11: a) Source follower configuration b) AC analysis [36]

According to the gain equation, even if Rs = infinity, the voltage gain of the source amplifier is not equal to 1. The resistor is replaced with a constant current source shown below to overcome this problem.

Figure 2.12: Source follower with constant current source

Hence, a source follower exhibits a high input impedance and a moderate output impedance at the cost of nonlinearity and voltage headroom limitation.

### 2.2.8 Common gate stage

Figure 2.13: a) Common-gate circuit b) AC analysis [36]

A common-gate stage senses the input at the source and produces the output at the drain. Gate is connected to a DC voltage to ensure proper biasing such as a current mirror, voltage level shifter or any external DC biasing circuit. Gain of the device is positive, and the input impedance is comparatively lower than the CS stage and source follower stage. Although the input impedance of the CG stage can be increased by applying a bigger load resistor.

## **Chapter 3: Method and approach**

#### 3.1 Understanding the working of a generic OTA

An Operational Transconductance Amplifier (OTA) is the building block for many Analog and mixed-signal systems. The main feature of a transconductance amplifier is to convert the input voltage into a current output. The different levels of complexity in the design of an OTA are used to realize functions ranging from high amplification to a significant slew rate and smaller chip area [22]. The juxtaposition of different features of an OTA (like high gain, high slew rate, lesser chip area, higher input common-mode range) leads to a constant room for research and development in this specific area of Analog circuit design.

A traditional OTA design comprises two input voltages, an amplifier responsible for the transconductance (Gm) and an amplified output current. Output current is directly proportional to the difference in the two input voltages.

$$I_{OUT} = G_m (V_{in}^+ - V_{in}^-)$$

(3.1)

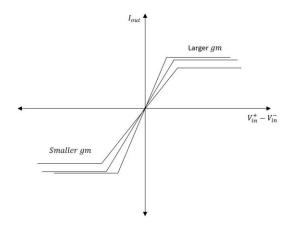

General input-output characteristics of an OTA are shown below. In a generic OTA, the width of the linear region is inversely proportional to the amplifier's transconductance. Thus, higher the transconductance, the lower the width of the Linear/Ohmic Region (Fig. 3.1). Ideally, an OTA should have infinite input impedance for maximum utilization of input voltage by the OTA, and infinite output impedance allows an efficient transfer of output current to the load.

Figure 3.1 I/O characteristics of generic OTA [22]

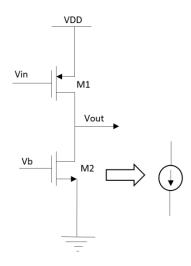

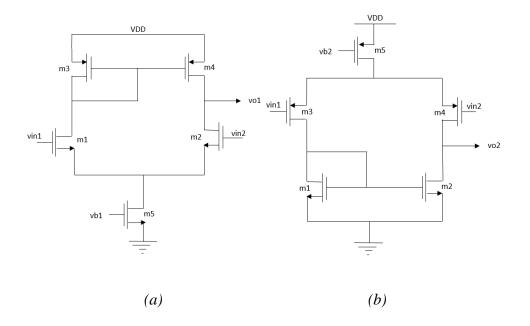

Figure 3.2 a) NMOS input OTA b) PMOS input OTA

Figure 3.2 illustrates the two standard topologies of OTA. First one is the NMOS input and the second one is the PMOS input. The common mode range in an NMOS input can go as high as  $V_{DD}$  but it has problem in going low towards  $V_{SS}$ . While in an PMOS input OTA the input common mode range can go even below low as  $V_{SS}$  but have problem to go higher voltage level towards

$V_{DD}$ . At the same circuit configurations, the first one has the advantage over the PMOS input OTA in terms of high gain.

$$A_{vn} = g_{mn}(r_{o2}||r_{o4}) \tag{3.2a}$$

$$A_{vp} = g_{mp}(r_{o2}||r_{o4}) \tag{3.2b}$$

As we know that intrinsic gain  $(g_m)$  of NMOS is larger than the PMOS because of higher electron mobility, thus  $A_{vn} > A_{vp}$ . Hence, we choose the NMOS input transistor for better gain with a lower input common mode range while we use PMOS input pair for the device to operate on a low input voltage and a much better input common mode range. To run the device on low supply voltages we often use bulk-driven MOS transistors [1] which gives a comparatively lower gain but can operate on the input voltage as low as 0V. A bulk-driven transistor operation is discussed next in the section 3.2.

#### **3.2 Bulk-driven input stage**

In a conventional OTA, we mainly use a gate-driven input stage to achieve better performance with the least complexity in the circuit. In medical applications, OTA is designed to operate under low bias and with lower supply voltage. The bulk terminal is often ignored in circuit design because it is tied to the source terminal to avoid the Body Effect; it is because of the change in threshold voltage when there is a potential difference between the source and body terminal. This phenomenon has been exploited in many gives' applications utilizing the bulk terminal as another gate terminal with the intention of changing effective device threshold voltage ( $V_T$ ). The equation [18] represents this effect:

$$V_T = V_{T0} + \gamma \left[ \sqrt{2.\,\emptyset_F + V_{BS}} - \sqrt{2.\,\emptyset_F} \,\right] \tag{3.3}$$

Where  $\gamma$  is the body bias factor,  $V_{BS}$  is bulk to source voltage and  $\phi_F$  is the surface potential of the device. According to the above equation, one can easily control the device using the change of body to source voltage.  $V_{BS}$  is directly proportional to the device's  $V_T$ , i.e., the MOSFET's threshold voltage will change according to the applied input voltage at the bulk of the device. This topology allows the input voltage to be as minimal as possible to work in the strong-inversion region (saturation). In bulk driven MOSFET, the gate of PMOS is connected to the ground, and the gate of NMOS is connected to the positive supply voltage.

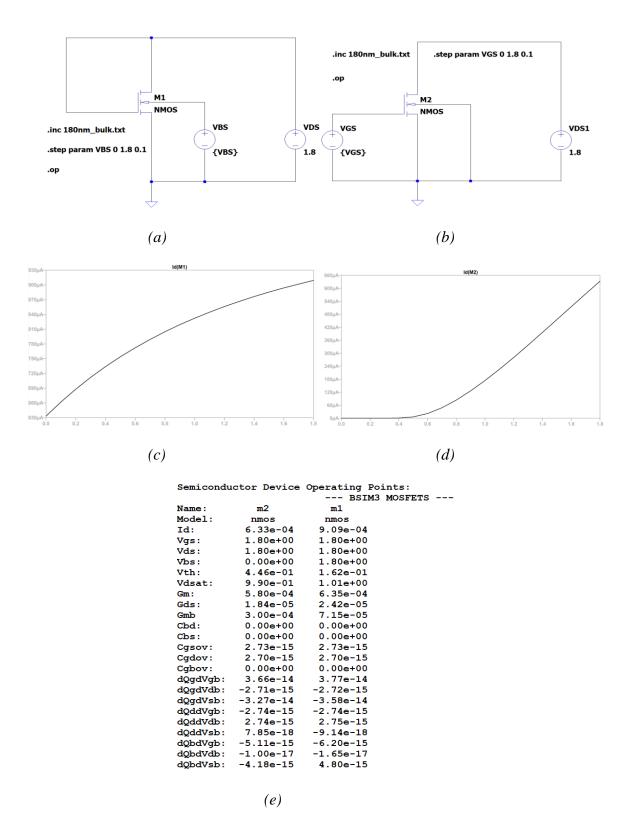

The simulation in figure 3.3 shows the DC characteristics of both the gate-driven and the bulkdriven input stages. According to the observation, the gate-driven NMOS enters the saturation region after a threshold of around 0.5V on a given power supply of 1.8V, which causes a limitation in the application of a low input voltage circuit application. For this purpose, we use a bulk-driven input stage which enters the strong inversion region on input as low as 0V producing a massive output drain current (around 9.09e-04 A) as compared to the former (around 6.33e-04 A). Bulkdriven MOS ( $g_{mb} = 7.15e-05$ ) is much less than the gate-driven MOS's transconductance ( $g_m =$ 5.80e-04) shown in Figure 3.3e. The difference in the  $g_m$  of M2 and  $g_{mb}$  of M1 proves that bulkdriven devices are not the best suited [25] for acquiring a high gain with a least leakage current [27]. Hence, for obtaining higher gain a gate driven gain stage [25] is designed to further optimize the gain [28][29][30][31].

Figure 3.3 a) Bulk-driven NMOS b) Gate-driven NMOS c) I/V characteristics of bulk-driven NMOS d) I/V characteristics of gate-driven NMOS e) Operating point of m1 and m2 in LTSpice

A bulk-driven input stage can have either PMOS as the input or NMOS. Both has their advantage when one wants to increase the input voltage range as shown in the Fig. 3.4. A PMOS input stage gives a voltage headroom from ground to  $V_{DSAT} + V_{BS}$  below the supply voltage while the NMOS input stage acts in a reverse manner and only allows  $V_{DSAT} + V_{BS}$  above the ground to the supply voltage. To design a rail-to-rail circuit, both the above-mentioned input stages are clustered together to achieve the best possible input range and voltage headroom from ground to  $V_{DD}$ . The combination of NMOS and PMOS input stage improves the input dynamic range [25] and the intrinsic bulk-transconductance of the devices. In the mid-input range (between  $V_{DSAT} + V_{BS}$  above the ground and  $V_{DSAT} + V_{BS}$  below the supply voltage) both the devices are in active which ensures a better  $g_{mb}$  for the input transistor and further increases the gain of the first stage.

Figure 3.4 Input common mode range for PMOS and NMOS bulk-driven input stage

Hence, in this thesis bulk-driven device is used only as an input stage [32][33], making the circuit work on a very low input voltage, ideal for low voltage applications. In addition, there can be several types of gate-driven differential pair amplifiers which can be connected to the bulk-driven input pair to get a folded cascoded amplifier with a minimal input voltage to gain a much higher output impedance and in turn increase the total gain of the first stage.

#### **3.3 Folded cascoded gain stage**

The generic OTA discussed in section 3.1 is good for gate driven input stage but gives a poor gain when the device is bulk driven because of the low output impedance. Folded cascoded amplifier [8] is a very good approach in designing an amplifier to achieve a massive gain even if the input stage is not efficient to give a high intrinsic transconductance. In a folded cascoded amplifier, the gain depends on the intrinsic gain of the input stage and the output impedance of the gate-driven transistors of the OTA. Output impedance of an NMOS is calculated by the following equation:

$$r_{o} = \frac{I_{D}}{V_{DS}} = I_{D} = \frac{\frac{\mu_{n}.C_{ox}}{2} \frac{W}{L} (V_{GS} - V_{TH})^{2}}{V_{DS}}$$

(3.4)

Since the  $g_{mb}$  for input stage is comparatively lower than the  $g_m$ , we increase the output impedance of the transistors by increasing the W/L ratio of the transistors. Using the equation of ro, we can easily tweak (increase) the width of the transistor to increase the ro and hence the gain of the first stage. Figure 3.5 shows the cascoded differential pair with a NMOS input and a PMOS input for application in different input common mode range. Improved gain also improves the operating frequency and unity gain bandwidth of the amplifier. A proper calculation of gain and output impedance is shown in section 4.1.

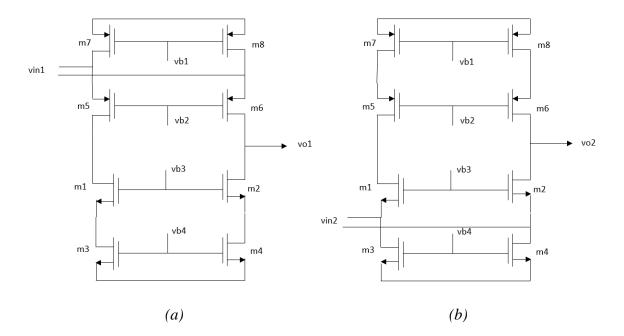

Figure 3.5 Folded cascoded OTA with a) NMOS input b) PMOS input

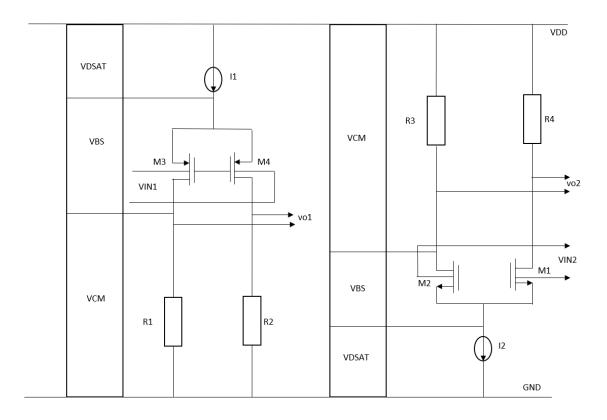

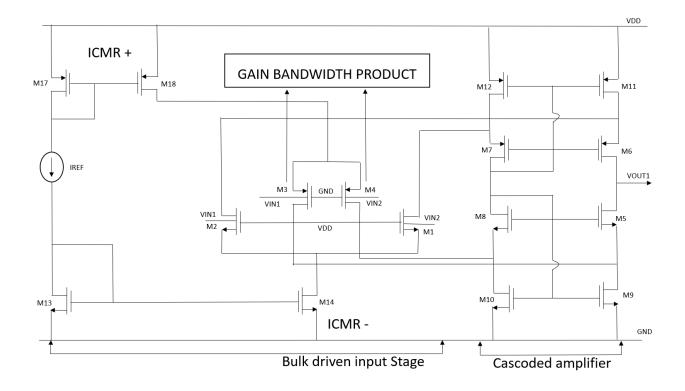

Fig 3.6 shows the bulk-driven rail-to-rail input stage with a folded cascoded gain stage amplifier which ensures low voltage operation of the OTA with a larger gain as desired. R1, R2, R3, R4 can further be replaced by MOS devices acting in saturation region and the current sources can be replaced by constructing current mirror using NMOS and PMOS. M1, M2 are responsible for the upper half of the input range amplification while M3, M4 are used for amplification in the lower half of the input voltage. Since M1, M2, M3, M4 play a crucial role in gain, the W/L ratio of the MOS is kept massively large to get an intrinsic transconductance like that of a gate-driven MOS. As a result, the input devices conduct from ground to  $V_{DD}$  achieving a high gain with the least variation in the transconductance.

Figure 3.6 Folded cascoded OTA with bulk-driven rail-to-rail input

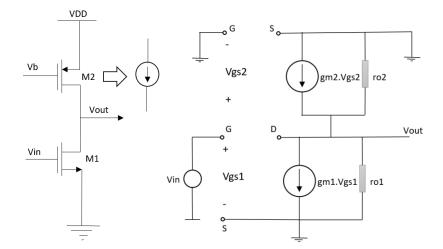

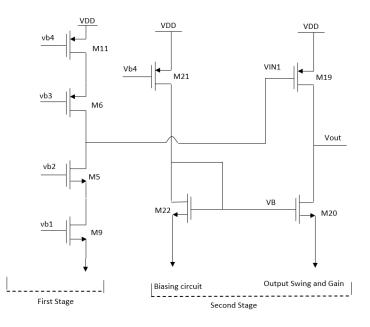

## 3.4 Second stage for OTA

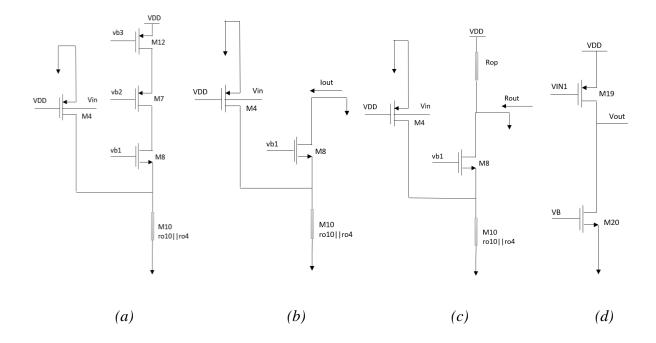

As discussed earlier, gain of the single stage op-amp is solely dependent on the intrinsic transconductance of the input pair and the output impedance of the folded-cascoded amplifier limiting the gain and the output swing which is not adequate for high gain applications of the op-amp. The second stage of the amplifier is implemented to further increase the gain and give a better output voltage headroom. As discussed earlier in chapter 2, common source amplifier is more suitable for designing the second stage of the OTA to improve the output voltage swing. Fig 3.7 shows a generic common source amplifier using a PMOS and an NMOS.

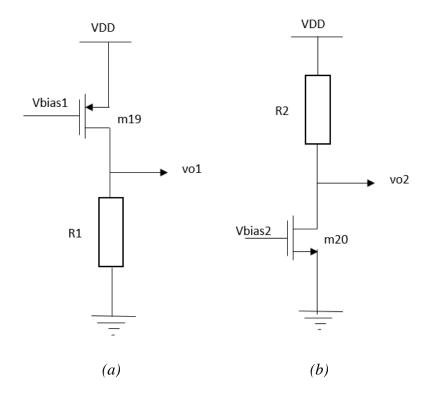

Figure 3.7 Common-source amplifier using a) PMOS b) NMOS

The output swing of the second stage is totally dependent on the overdrive voltages of the transistors in the cascoded differential pair from the first stage.

### $V_{DD}$ – Overdrive voltage of the transistor

To elaborate, let's compare the overdrive voltages of CS amplifier using NMOS vs PMOS,

$$I_D = \frac{1}{2} \mu_{n,p} C_{ox} \frac{W}{L} (V_{GS} - V_{th})^2$$

(3.5)

$$V_{OD} = V_{GS} - V_{th} = \sqrt{\frac{2I_D}{\mu_{n,p} c_{ox} \frac{W}{L}}}$$

(3.6)

According to the equation above, overdrive voltage is dependent on the W/L ratio of the device which is more in case of PMOS device. Hence, PMOS common source amplifier gives the least overdrive voltage giving a higher voltage swing. Therefore, using an NMOS CS amplifier is not

suitable for this type of cascoded circuit as it gives lower output swing as compared to PMOS CS amplifier. As illustrated in Fig. 3.8, the PMOS M19 can be used with an NMOS as a current source load M20. If the output resistance ( $r_{020}$ ) is not high enough, then the length and width of the transistor M20 should be increased to achieve smaller lambda, maintaining a good overdrive voltage. L20 and W20 be scaled up proportionately as  $V_{gs} - V_{th} h \propto \frac{1}{\sqrt{W/L}}$ . Hence, if the L and W are not scaled up together, the overdrive voltage can increase, limiting the output voltage swing. Hence the W/L ratio of M20 is designed to scale up the current in the branch and produce a good overdrive voltage for an optimum voltage swing. Gain of the second stage is dependent on transconductance of M19 in figure 3.8 which requires the transistor to be larger than the transistor used as a current source load.

Figure 3.8 Second stage for the OTA using a PMOS common source configuration with current

source load

It can be seen in the equation below that high current  $(I_{D20} = I_{D19})$  in the branch and larger size of the transistor (M19) will increase the intrinsic transconductance  $g_{m19}$  to a sufficiently larger value which will further increase the gain and output swing of the 2-stage OTA.

$$I_D = \frac{\mu_n c_{ox}}{2} \cdot \frac{W}{L} \cdot (V_{gs} - V_{th})^2$$

(3.7)

$$g_m = \frac{\partial I_D}{\partial V_{gs}} = \mu_n \cdot C_{ox} \cdot \frac{W}{L} \cdot (V_{GS} - V_{TH})$$

(3.8)

$$g_m = \sqrt{2I_D \cdot \mu_n C_{ox} \cdot \frac{W}{L}} \tag{3.9}$$

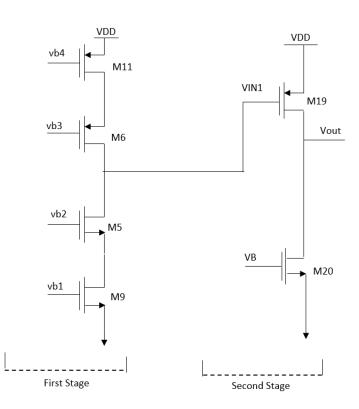

Since M20 is used for current scaling to maintain high current in the branch, therefore it is very important to find the suitable node from which M20 can get the required biasing gate voltage (VB). There are several ways of biasing a transistor [29][32][33] but in case of low voltage application, it is important to consider the fact that gate voltage should not be greater than  $V_{DS20}$  which will force the transistor to operate in triode region. This can be done by adding a biasing circuit in the second stage that includes a series connected NMOS and a PMOS as shown in the figure 3.9. Biasing circuit consists of a PMOS M21 which is biased according to M11 and an NMOS provides a good biasing condition for M20 to be in saturation region using a current mirror. Current scaling is a very common technique to regulate the current flow in the branch using the concept of current mirrored into the CS amplifier circuit to increase the flow of charge in the output branch. As illustrated in Fig. 3.9, the current in the output branch can be scaled "m" times the current in the current in the first stage.

$$\frac{I_{D21}}{I_{D11}} = \frac{W/_{L_{21}}}{W/_{L_{11}}} = m:1$$

(3.10)

Figure 3.9 Biasing circuit for the second stage OTA

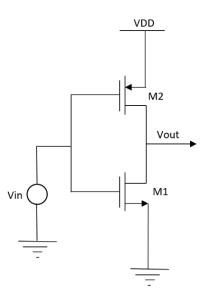

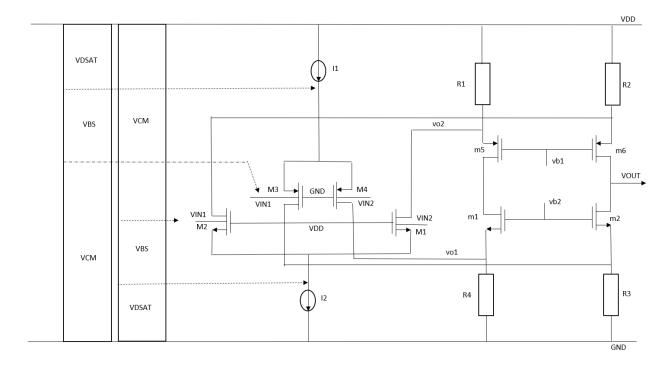

Equivalent circuit of proposed 2-stage OTA can be designed by combining the topologies described in sections 2-4, shown in fig.3.10.

Figure 3.10 2-stage bulk driven OTA

## **Chapter 4: Analysis**

#### **4.1 Introduction**

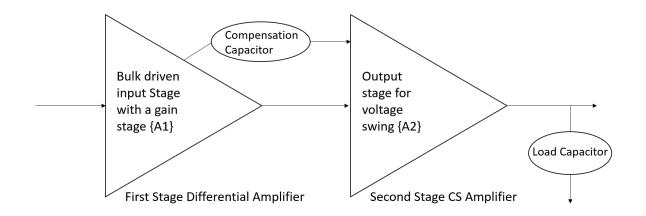

We started with the design of the first stage. We have used a differential amplifier to improve the gain. Next, is the design of the second stage which is a common-source amplifier for the maximum output voltage swing. The block diagram of the two stage OTA is shown in Figure 4.1 where a compensating capacitor (explained in section 4.2) is placed between the dominant pole of the first and second stage for frequency response.

Figure 4.1: Block diagram of the 2-stage OTA

Figure 4.2 shows the circuit diagram of the first stage which has been used for the calculation of aspect ratios of different NMOS and PMOS transistors using respective functionalities. For instance, the bulk driven input MOS transistors (M1, M2, M3, M4) are used to define the gain-bandwidth product of the first stage. Similarly, M14 and M18 are a part of the input current mirror and work alternatively in triode and saturation region to give a rail-to-rail input voltage headroom for the input MOS transistors (as explained earlier in Section 3.2). Hence, M18 and M14 is

responsible for the input common mode range ( $ICMR^+$ ,  $ICMR^-$  respectively). To explain the working of circuit, we derive the transfer function of the first stage as shown in the next section.

Figure 4.2: Circuit diagram of the first stage of OTA

## 4.2 Small-signal analysis and transfer function

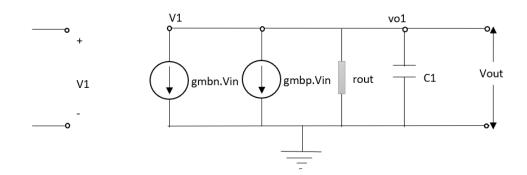

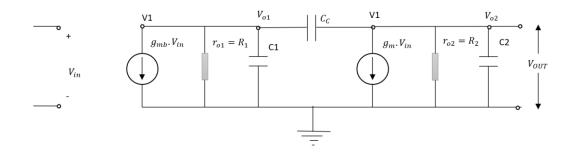

To derive the transfer function for the first stage, AC analysis is done for the proposed circuit architecture to understand the dominant poles (responsible for transconductance,  $g_{mb}$ ) in the circuit. Here, all other insignificant poles are ignored because their absence do not affect the transfer function. Fig. 4.3 shows the small signal equivalent circuit of the first stage.

Figure 4.3: Small-signal analysis of the first stage

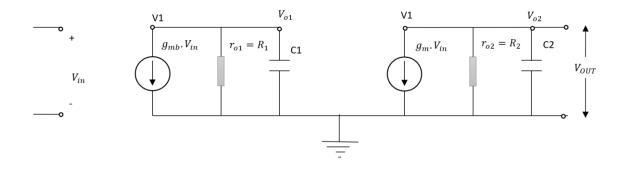

Figure 4.4: Small-signal analysis of the 2-stage OTA without the miller capacitance

Fig. 4 shows the small signal equivalent circuit of the second stage. The circuit in Figure 4.4 has two dominant poles:

$$P_1 = \frac{1}{R_1 \cdot C_1} \tag{4.1a}$$

$$P_2 = \frac{1}{R_2 \cdot C_2}$$

(4.1b)

$P_1$  is the dominant pole of the first stage whereas  $P_2$  is the pole in the second stage.  $R_1$  is the equivalent output resistance of the gain stage (first stage). Similarly,  $R_2$  is the equivalent resistance of the second stage CS amplifier. Value of these equivalent resistances will be derived later in Section 4.3.  $C_1$  is the parasitic capacitance of the NMOS and PMOS devices near the first dominant pole in the cascoded differential amplifier.  $C_2$  is the gate capacitance of the PMOS (M19) in the

second stage. Before deriving the transfer function, we should also observe that in practical applications, the circuit is designed for a purely capacitive load. Hence,  $C_2$  is parallel to the load capacitance ( $C_L$ ) which is significantly larger than the gate capacitance of M19.

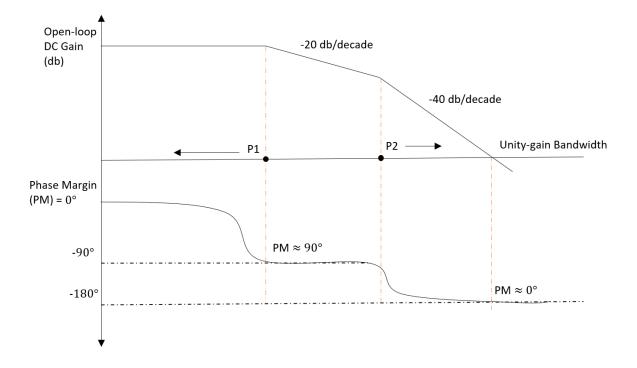

*Figure 4.5: Problems for gain and phase without compensation capacitor*

As illustrated in Figure 4.5, the bode plot for open loop gain with respect to phase shows a poor phase margin in the absence of compensation capacitor ( $C_c$ ). The first pole can give a phase margin of around 90° but as the slope of open-loop gain after the second pole falls to -40dB/decade, the phase margin at the unity-gain bandwidth can be as low as 0°. This poor phase margin can be improved by adding a large capacitance in parallel to the parasitic capacitances of the first stage (C1) to push the first pole towards the left of the bode plot. According to equation 4.1, increasing C1 will decrease the pole frequency (P1) and move the pole towards the left in the graph. Similarly, the pole P2 can be moved towards the right of the bode plot to achieve the desired phase margin. Either a compensation capacitor [34] or a or Feed-forward compensation technique [35] can be used in this type of topology. Adding a large capacitance to C1 increases the chip area and the power consumption, hence the concept of Miller effect [34] compensation method can be used to increase the capacitance.

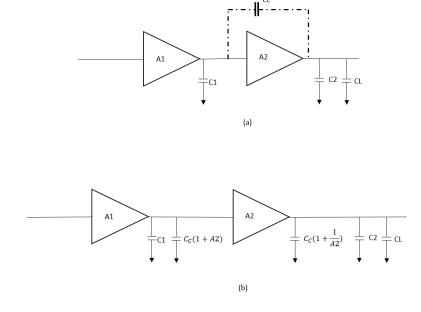

Figure 4.6 shows how the miller effect increases the capacitance without using a big capacitor. If we add a small capacitor ( $C_c$ ) as a feedback loop of the second stage OTA (Fig. 4.6a), the equivalent circuit looks like Fig 4.6b, where the effect of the capacitor  $C_c$  is multiplied by one plus the gain of the second stage. This makes capacitor C1 big compared to before.

$$P_1 = \frac{1}{R_1 \cdot C_1} = \frac{1}{R_1 [C_1 + C_c (1 + A2)]} \approx \frac{1}{R_1 C_c}$$

(4.2)

Figure 4.6: Miller-effect in the two stage OTA

According to Fig. 4.7, transfer function is calculated by the ratio of output voltage to the input voltage:

$$\frac{V_o}{V_{in}} = \frac{V_{out}}{V_1} \cdot \frac{V_1}{V_{in}}$$

Next, adding the miller capacitance as shown in Figure 4.7 and applying Kirchhoff's Current Law (KCL) to the first and the second stage in the small signal model, we find:

Figure 4.7: Small-signal analysis of the 2-stage OTA with the miller capacitance

Loop 1: First stage

$$\frac{V_{1}}{1/_{SC_{1}}} + \frac{V_{1}}{R_{1}} + g_{mb1} \cdot V_{in} + \frac{V_{1} - V_{o}}{1/_{SC_{c}}} = 0$$

$$\frac{V_{1}}{1/_{SC_{1}}} + \frac{V_{1}}{R_{1}} + \frac{V_{1}}{1/_{SC_{c}}} - \frac{V_{o}}{1/_{SC_{c}}} = -g_{mb1} \cdot V_{in}$$

$$SC_{1}R_{1}V_{1} + V_{1} + SC_{c}R_{1}V_{1} - SC_{c}R_{1}V_{o} = -g_{mb1} \cdot R_{1} \cdot V_{in}$$

$$V_{1} = \frac{V_{o} \cdot SC_{c} \cdot R_{1} - g_{mb1} \cdot R_{1} \cdot V_{in}}{1 + SR_{1}(C_{1} + C_{c})} \qquad (4.3a)$$

Loop 2: Second stage

$$\frac{V_o}{1_{SC_2}} + \frac{V_o}{R_2} + g_{m19} \cdot V_1 + \frac{V_o - V_1}{1_{SC_c}} = 0$$

$$V_{o}\left[\frac{1}{R_{2}} + s(C_{2} + C_{c})\right] = V_{1}\left(s.C_{c} - g_{m19}\right)$$

Substituting the value of  $V_1$  from Loop1:

$$V_{o} [1 + s.R_{2}(C_{2} + C_{c})] = \frac{V_{o}.sC_{c}.R_{1} - g_{mb1}.R_{1}.V_{in}}{1 + sR_{1}(C_{1} + C_{c})} R_{2} (s.C_{c} - g_{m19})$$

$$V_o[1 + sR_2(C_2 + C_c) - sC_cR_1R_2(sC_c + g_{m19})] = \frac{-g_{mb1}R_1R_2V_{in}(sC_c - g_{m19})}{1 + sR_1(C_1 + C_c)}$$

(4.3b)

Substituting the value of  $V_1$  from equation 4.3a in equation 4.3b, we get the transfer function:

$$\frac{V_o}{V_{in}} = \frac{g_{mb1} g_{m19} R_1 R_2 (1 - \frac{sC_c}{g_{m19}})}{s^2 [R_1 R_2 (C_1 C_2 + C_1 C_c + C_2 C_c)] + s [R_2 (C_2 + C_c) + R_1 (C_1 + C_c) + C_c g_{m19} R_1 R_2] + 1}$$

(4.3c)

#### 4.2.1 Simplification of the transfer function:

Equation 4.3d shown below is the standard transfer function for 2-stage system where  $A_{DC}$  is the open loop DC gain of the OTA, "s" is the frequency dependent parameter at which the gain is calculated (for DC calculations  $s = j\omega = 0$ ), "z" is the zero for the amplifier (explained later in section 4.4),  $P_1$  and  $P_2$  are pole frequencies of the first and second stage respectively.

$$\frac{V_o}{V_{in}} = \frac{A_{DC}(1 - s/z)}{(1 + s/p_1)(1 + s/p_2)}$$

(4.3d)

$$\frac{V_o}{V_{in}} = \frac{A_{DC}(1 - S/Z)}{s^2(\frac{1}{P_1 P_2}) + s(\frac{1}{P_1} + \frac{1}{P_2}) + 1}$$

(4.3e)

Since  $P_2$  ( $C_L$  is larger compared to the gate capacitance of M19) is very large, therefore,  $\frac{1}{P_2} \approx 0$  in equation 4.3e and neglected for further calculations.

$$\frac{V_o}{V_{in}} = \frac{A_{DC}(1 - s/Z)}{s^2(\frac{1}{P_1 P_2}) + s(\frac{1}{P_1}) + 1}$$

(4.3f)

Comparing the general equation for a two-stage system (equation 4.3f) with the calculated transfer function in the equation 4.3c. We achieve the following values for zeros and value for the pole frequency at the dominant poles of both the stages:

$$Z = \frac{g_{m19}}{c_c} \tag{4.4}$$

Next comparing the coefficients of "s" and " $s^2$ " from the transfer function we get the value of both the poles in this system:

$$P_1 = \frac{1}{R_1 R_2 g_{m19} C_2} \tag{4.5a}$$

$$P_2 = \frac{R_1 R_2 g_{m19} c_c}{R_1 R_2 (c_1 c_2 + c_1 c_c + c_2 c_c)}$$

(4.5b)

C1 is the parasitic capacitance of the first stage so it is smaller than C2. Hence,

$$P_2 = \frac{g_{m19}}{c_2} \tag{4.5c}$$

$$A_{DC} = g_{mb1} g_{m19} R_1 R_2 \tag{4.6}$$

Equation 4.6 shows the open loop DC gain of the OTA, where  $g_{mb}$  and  $g_m$  are the transconductance of the respective transistors, R1 and R2 are the equivalent resistances of the first and second stages respectively.

#### 4.3 Gain of the OTA

The open loop gain of an ideal operational amplifier is infinite which is practically not possible, hence, the gain of a practical amplifier is kept sufficiently large (around 80-100 dB) to ensure a stable operation. For achieving such high gain, in this work a 2-stage OTA is used instead of a single stage. This is because single stage amplifier is not sufficient for achieving such high gain around 80-100 dB. Introducing a second stage adds a better intrinsic transconductance and output impedance to the proposed OTA. Gain of a single stage is calculated by the product of intrinsic transconductance of the input MOS and the total output impedance ( $g_m$ .  $R_{out}$ ) as formulated in equation 4.6.

The total gain of the two-stage amplifier:

$$A_{\nu} = Gain \ of \ the \ First \ Stage * Gain \ of \ the \ Second \ Stage = A_{\nu 1} * A_{\nu 2}$$

(4.7)

By inspection, it can be observed that the folded-cascoded stage is responsible for the  $R_{out}$  of the first stage as shown in the half-equivalent circuit (Figure 4.8). Since the M4 and M10 are parallel to each other, therefore the equivalent resistance on the source of M8 will be  $r_{010} || r_{04}$ . In Figure 4.8b, the current coming from the output short circuit is equal to the drain current of M8 and impedance looking into the source of M8 is  $(g_{m8} + g_{mb8})^{-1} || r_{08}$  which is much lower compared to  $r_{010} || r_{04}$ . Hence,  $G_m \approx g_{mb4}$ .

Figure 4.8 a) Half equivalent circuit for gain stage b)  $G_m$  calculation c)  $R_{out}$  calculation d) Equivalent circuit for calculation for gain in second stage

According to Fig. 4.8c.:

$$R_{op} = (g_{m7} + g_{mb7}) \cdot r_{07} \cdot r_{012}$$

$$R_{out} = R_{op} || [(g_{m8} + g_{mb8}) \cdot r_{08} \cdot (r_{010} || r_{04})]$$

$$R_{out} = [(g_{m7} + g_{mb7}) \cdot r_{07} \cdot r_{012}] || [(g_{m8} + g_{mb8}) \cdot r_{08} \cdot (r_{010} || r_{04})]$$

(4.8a)

Substitute the values of the  $G_m$  and  $R_{out}$  to obtain the open loop gain of the first stage,

$$A_{v1} = g_{mb4} \cdot R_{out} = g_{mb4} \cdot \{ [(g_{m7} + g_{mb7}) \cdot r_{07} \cdot r_{012}] \mid | [(g_{m8} + g_{mb8}) \cdot r_{08} \cdot (r_{010} \mid | r_{04})] \}$$

$$(4.8b)$$

Similarly, one can calculate the gain of the second stage using the same procedure. The input transistor for the second stage is M19 and the total impedance seen from the output node in Figure 4.8d is the parallel combination of output impedances of M19 and M20.

$$G_m \approx g_{m19}$$

$R_{out} = (r_{019} || r_{020})$  (4.8c)

Gain =

$$A_{\nu 2} = g_{m19} R_{out} = g_{m19} (r_{019} || r_{020})$$

(4.8d)

Hence, the total gain can simply be calculated by multiplying the independent gain of the two stages.

$$A_v = A_{v1} * A_{v2}$$

$$= g_{mb4} \cdot \{ [(g_{m7} + g_{mb7}) \cdot r_{07} \cdot r_{012}] || [(g_{m8} + g_{mb8}) \cdot r_{08} \cdot (r_{010} || r_{04})] \} * g_{m19} \cdot (r_{019} || r_{020})$$

$$(4.8e)$$

#### 4.4 Gain-bandwidth product and phase margin

Gain and bandwidth of an amplifier are inversely proportional to each other i.e., if the gain is increased, the bandwidth decreases. Low gain with a large bandwidth ensures the stability of an amplifier. Gain-bandwidth product (GBW) is the product of DC gain and bandwidth at which the gain of the OTA is calculated. Unity-gain bandwidth (UGB) is the bandwidth of the amplifier when the gain approaches unity. GBW is equal to the UGB if there is a single dominant pole in the circuit as there is only one constant slope of -20dB/decade which makes both the factors equal. In a 2-stage amplifier, there are two dominant poles which gives two different slopes of the bode plot for gain, here the slope fall -20dB/decade every time a new dominant pole is added. Hence, the unity gain bandwidth shifts more towards the right in the bode plot and the gain bandwidth towards the left. It is also observed that some amplifiers are observed to be unstable with higher gains at the unit-gain bandwidth [21]. In this work, the gain-bandwidth product is calculated from

the total DC gain of the OTA and the pole(P1) at the first stage achieved from the transfer function calculated in Section 4.2:

$$GBW = A_{DC} * P_1 = \frac{g_{mb4} \cdot g_{m19} \cdot R_1 \cdot R_2}{R_1 \cdot R_2 \cdot g_{m19} \cdot C_c} = \frac{g_{mb4}}{C_c}$$

(4.9)

For ideal cases, the slope of the gain in Bode plot drops -20dB/decade for every stage. In case of second stage the slope will fall -40dB/decade after the second pole and goes back to 0dB/decade. This point is known as zero for the OTA (denoted by Z). We assume Z to be significantly larger than GBW (or UGB). Here, for simplification, zero (Z) is assumed to be greater than or equal to 10 times the GBW.

$$Z \ge 10.GBW \tag{4.10}$$

$$\frac{V_o}{V_{in}} = \frac{A_{DC}(1-\frac{s}{z})}{(1+s/P_1)(1+s/P_2)}$$

(4.11)

Phase Margin (PM) =

$$\lfloor \frac{V_0}{V_{in}} = -\tan^{-1}\frac{w}{z} - \tan^{-1}\frac{w}{P_1} - \tan^{-1}\frac{w}{P_2}$$

(4.12a)

When the frequency is equal to the unity-gain, it is considered as GBW. Hence, Replace the

frequency (w) by GBW and Z by 10.GBW.

$$PM = -\tan^{-1}\frac{GBW}{10.GBW} - \tan^{-1}\frac{GBW}{P_1} - \tan^{-1}\frac{GBW}{P_2}$$

(4.12b)

Substitute the value of P1 from the equation 4.5a in the equation above:

$$PM = -\tan^{-1}\frac{1}{10} - \tan^{-1}\frac{g_{mb4}g_{m19}R_1R_2C_c}{C_c} - \tan^{-1}\frac{GBW}{P_2}$$

(4.12c)

$$PM = -\tan^{-1}\frac{1}{10} - \tan^{-1}A_{DC} - \tan^{-1}\frac{GBW}{P2}$$

(4.12d)

For a maximum gain, replace  $tan^{-1}(A_{DC})$  by 90°

$$-180 + PM = -5.71 - 90 - tan^{-1} \frac{GBW}{P2}$$

$$PM = 84.29 - tan^{-1} \frac{GBW}{P2}$$

(4.12e)

Now let's calculate P2 for a good phase margin of  $60^{\circ}$ :

$$60 = 84.29 - \tan^{-1} \frac{GBW}{P_2} \tag{4.13}$$

$$P_2 \ge 2.2 \, GBW \tag{4.14}$$

$$\frac{g_{m19}}{c_2} \ge 2.2 \, \frac{g_{mb4}}{c_c} \tag{4.15}$$

Since z = 10.GBW

$$\frac{g_{m19}}{c_c} = 10.\frac{g_{mb4}}{c_c} \Longrightarrow g_{m19} = 10.g_{mb4}$$

(4.16)

Substituting the value of  $g_{m19}$  from equation 4.16 in equation 4.15, we find the value of the compensation capacitor ( $C_C$ ) with respect to the load capacitor ( $C_L$ ):

$$C_c \ge 0.22 C_L \tag{4.17}$$

Let's take  $C_L = 0.5 \ pF$

$$C_c \ge 0.22 \ C_L = 0.22 * 0.5pF = 0.11 \ pF = 110 \ fF \tag{4.18}$$

This is an important relation for tweaking the unity-gain bandwidth regardless of the transistor sizes. Increasing  $C_c$ , will move UGB to the left of the bode plot (according to equation 4.9) and vice versa.

## 4.5 Slew rate

To estimate the slew rate of the proposed circuit we have used the simplified circuit shown below in Figure 4.9.

Figure 4.9: Simplified circuit during the positive and negative slewing

Slew rate is the rate of change of an amplifier's output voltage with a change in input signal. Figure 4.6 explains the slewing operation in the proposed OTA as the rate of change of output voltage signal varies from 10% to 90% of the magnitude.

At t = 0, if  $V_{in}$  experiences a large positive signal M1 and M4 turns off. Here the slope of the waveform is towards the positive edge of the signal. This is known as positive slewing, where the compensation capacitor  $C_c$  is charged by a constant current,  $I_o$  (neglecting the parasitic capacitances at  $C_c$  due to M19 and M20). The node at the gate of M19 becomes a virtual ground due to the gain of the second stage (i.e.,  $SR^+ = \frac{I_o}{C_c} = \frac{I_{D14}}{C_c}$ ). In addition, the PMOS M19