## University of Windsor Scholarship at UWindsor

**Electronic Theses and Dissertations**

Theses, Dissertations, and Major Papers

2022

## Hardware Implementations of Spiking Neural Networks and Artificially Intelligent Systems

Alexander J. Leigh University of Windsor

Follow this and additional works at: https://scholar.uwindsor.ca/etd

Part of the Artificial Intelligence and Robotics Commons, and the Computer Engineering Commons

#### **Recommended Citation**

Leigh, Alexander J., "Hardware Implementations of Spiking Neural Networks and Artificially Intelligent Systems" (2022). *Electronic Theses and Dissertations*. 8907. https://scholar.uwindsor.ca/etd/8907

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

# Hardware Implementations of Spiking Neural Networks and Artificially Intelligent Systems

By

Alexander J. Leigh

A Dissertation

Submitted to the Faculty of Graduate Studies through the Department of Electrical and Computer Engineering in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy at the University of Windsor

Windsor, Ontario, Canada

2022

©2022 Alexander J. Leigh

# Hardware Implementations of Spiking Neural Networks and Artificially Intelligent Systems

By

Alexander J. Leigh

APPROVED BY:

S. Mirabbasi, External Examiner University of British Columbia

R. Carriveau Department of Civil & Environmental Engineering

M. Azzouz Department of Electrical & Computer Engineering

B. Balasingam Department of Electrical & Computer Engineering

R. Muscedere, Co-Advisor Department of Electrical & Computer Engineering

M. Mirhassani, Co-Advisor Department of Electrical & Computer Engineering

April  $26^{th}$ , 2022

# Declaration of Co-Authorship/Previous Publication

#### I. Co-Authorship

I hereby declare that this dissertation incorporates material that is result of joint research. Chapters 2-6 of this dissertation were completed under the supervision of Dr. Mitra Mirhassani. Additionally, Chapter 2 was completed under the additional supervision of Dr. Roberto Muscedere. Furthermore, Chapters 3-6 were completed in colaboration with Dr. Moslem Heidarpur. In all cases, the key ideas, primary contributions, experimental designs, data analysis, interpretation, statistical analysis, graphing results, and writing, were performed by the author. The contributions of the above-mentioned co-authors were primarily through the provision of checking and comments on the literature review, mathematical derivations, systems architectures, algorithms, providing feedback on refinement of ideas, editing of the manuscript, and advice on selecting peer reviewed journals for publication.

I am aware of the University of Windsor Senate Policy on Authorship and I certify that I have properly acknowledged the contribution of other researchers to my dissertation, and have obtained written permission from the supervisor to include the above material in my dissertation.

I certify that, with the above qualification, this dissertation, and the research to which it refers, is the product of my own work.

### **II.** Previous Publication

This dissertation includes 3 original papers that have been previously published/accepted for publication in peer reviewed journals and conferences as described below.

| Dissertation<br>Chapter | Publication title/full citation                                                                                                                                                                                                                                                                     | Publication<br>Status  |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| Chapter 2               | A. J. Leigh, M. Mirhassani and R. Muscedere, "An Efficient Spiking Neuron Hardware System Based on the Hardware Oriented Modified Izhikevich Neuron (HOMIN) Model," in IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 67, no. 12, pp. 3377 3381, Dec. 2020, doi: 10.1109/TCSII. | Published              |

| Chapter 3               | A. J. Leigh, M. Heidarpur and M.<br>Mirhassani,"A Resource-Efficient and<br>High-Accuracy CORDIC-Based Digital<br>Implementation of the Hodgkin-Huxley<br>Neuron", in IEEE Transactions on<br>Biomedical Circuits and Systems                                                                       | In Revision            |

| Chapter 4               | A. J. Leigh, M. Heidarpur and M.<br>Mirhassani,"The Input-DEpendent Vari-<br>able Sampling (I-DEVS) Method"                                                                                                                                                                                         | Submitted              |

| Chapter 5               | A. J. Leigh, M. Heidarpur and M. Mirhassani, "Selective Input Sparsity in Spiking Neural Networks for Pattern Classification", IEEE International Symposium on Circuits and Systems (ISCAS) 2022, May 2022                                                                                          | Accepted by ISCAS 2022 |

#### III. General

I declare that, to the best of my knowledge, this dissertation does not infringe upon anyone's copyright nor violate any proprietary rights and that any ideas, techniques, quotations, or any other material from the work of other people included in my dissertation, published or otherwise, are fully acknowledged in accordance with standard referencing practices.

I declare that this is a true copy of the dissertation, including any final revisions, as approved by the dissertation committee and the Graduate Studies office, and that this dissertation has not been submitted for a higher degree to any other University or Institution.

## Abstract

Artificial spiking neural networks are gaining increasing prominence due to their potential advantages over traditional, time-static artificial neural networks. Custom hardware implementations of spiking neural networks present many advantages over other implementation mediums. Two main topics are the focus of this work. Firstly, digital hardware implementations of spiking neurons and neuromorphic hardware are explored and presented. These implementations include novel implementations for lowered digital hardware requirements and reduced power consumption.

The second section of this work proposes a novel method for selectively adding sparsity to a spiking neural network based on training set images for pattern recognition applications, thereby greatly reducing the inference time required in a digital hardware implementation. To my grandfather

## Acknowledgments

I would like to firstly thank my advisor Dr. Mitra Mirhassani. Not only has she been an exceptional advisor throughout my entire academic career, but she is a truly great person who cares profoundly for her students. Without her guidance, I can unequivocally say that I would not be where I am today academically.

I would also like to express my gratitude to my co-advisor Dr. Roberto Muscedere. He is a wealth of technical knowledge, and his input is always invaluable and significant.

I would like to thank Dr. Moslem Heidarpur, with whom I have had the august pleasure of collaboration in research.

I would like to thank my committee members; Dr. Maher Azzouz, Dr. Bala Balasingam, and Dr. Rupp Carriveau.

I would like to thank my parents and family for their continuous love and support.

# Table of Contents

| D        | eclar | ation o | f Co-Authorship / Previous Publication                                                         | iii    |

|----------|-------|---------|------------------------------------------------------------------------------------------------|--------|

| Abstract |       | vi      |                                                                                                |        |

| D        | edica | tion    |                                                                                                | vii    |

| A        | cknov | wledgn  | nents                                                                                          | viii   |

| Li       | st of | Tables  |                                                                                                | xii    |

| Li       | st of | Figure  | S                                                                                              | xiv    |

| 1        | Intr  | oducti  | on                                                                                             | 1      |

|          | 1.1   | Elemen  | nts of Spiking Neural Networks                                                                 | 2      |

|          |       | 1.1.1   | Spiking Neuron Models                                                                          | 2      |

|          |       | 1.1.2   | Synapses and Learning                                                                          | 3      |

|          | 1.2   | Motiva  | tion $\ldots$ | 4      |

|          |       | 1.2.1   | Neuron Implementations                                                                         | 4      |

|          |       | 1.2.2   | Spiking Neural Network Implementations                                                         | 4      |

|          | 1.3   | Object  | ives                                                                                           | 5      |

|          | 1.4   | Dissert | ation structure                                                                                | 6      |

| <b>2</b> |       |         | nt Spiking Neuron Hardware System Based on the Hard                                            | lware- |

|          | Orie  | ented N | Modified Izhikevich Neuron (HOMIN) Model                                                       | 8      |

|          | 2.1   | Mathe   | matical Preparations for Hardware Implementation                                               | 10     |

|          |       | 2.1.1   | Formulation of the Hardware-Oriented Modified Izhikevich                                       |        |

|          |       |         | Neuron (HOMIN) Model                                                                           | 10     |

|          |       | 2.1.2   | Discretization of the HOMIN Model                                                              | 13     |

|          | 2.2   | FPGA    | Implementation                                                                                 | 16     |

|          |       | 2.2.1   | Hardware Resource Usage                                                                        | 19     |

|   | 2.3 | Conclu   | $\operatorname{sion}$                                      | 21        |

|---|-----|----------|------------------------------------------------------------|-----------|

| 3 | A R | lesourc  | e-Efficient and High-Accuracy CORDIC-Based Digital         |           |

|   | Imp | lement   | ation of the Hodgkin-Huxley Neuron                         | <b>22</b> |

|   | 3.1 | Introdu  | action                                                     | 22        |

|   | 3.2 | Backgr   | ound                                                       | 27        |

|   |     | 3.2.1    | The Hodgkin-Huxley Neuron Model                            | 27        |

|   |     | 3.2.2    | COordinate Rotation DIgital Computer (CORDIC) Algorithm    | 29        |

|   | 3.3 | Propos   | ed Method                                                  | 31        |

|   |     | 3.3.1    | Verification                                               | 33        |

|   |     | 3.3.2    | Error Analysis                                             | 34        |

|   |     | 3.3.3    | Bifurcation Analysis of the Hodgkin-Huxley Neuron and CORD | IC        |

|   |     |          | Implementation                                             | 36        |

|   | 3.4 | FPGA     | Hardware Implementation                                    | 39        |

|   | 3.5 | Discuss  | sion                                                       | 43        |

|   | 3.6 | Conclu   | $\operatorname{sion}$                                      | 48        |

| 4 | The | e Input- | Dependent Variable Sampling (I-DEVS) Digital Neu-          |           |

|   | ron | Implen   | nentation Method                                           | 49        |

|   | 4.1 | Introdu  | action                                                     | 49        |

|   | 4.2 | Neuron   | Modelling                                                  | 52        |

|   | 4.3 | Propos   | ed Power Reduction Methodology                             | 53        |

|   |     | 4.3.1    | Methodology                                                | 53        |

|   |     | 4.3.2    | Simulations for Validation and Design Formulation          | 54        |

|   | 4.4 | Validat  | ion in Digital Hardware                                    | 57        |

|   |     | 4.4.1    | Hardware Design                                            | 57        |

|   |     | 4.4.2    | Power Analysis                                             | 65        |

|   | 4.5 | Conclu   | $\operatorname{sion}$                                      | 67        |

| <b>5</b> | Sele  | ctive Ir | nput Sparsity for Spiking Neural Network Size Reduc- |     |

|----------|-------|----------|------------------------------------------------------|-----|

|          | tion  |          |                                                      | 68  |

|          | 5.1   | Introdu  | ction                                                | 68  |

|          | 5.2   | Backgro  | ound Simulation                                      | 70  |

|          |       | 5.2.1    | Other Explored Reduction Methods                     | 72  |

|          | 5.3   | Propose  | ed Selective Input Sparsity                          | 74  |

|          |       | 5.3.1    | The Selective Input Sparsity (SIS) Method            | 74  |

|          |       | 5.3.2    | Software Validation                                  | 76  |

|          | 5.4   | Conclus  | sion                                                 | 79  |

| 6        | Spil  | ing Ne   | ural Network Hardware Implementations                | 80  |

|          | 6.1   | Hardwa   | are Blocks                                           | 81  |

|          |       | 6.1.1    | Input Image Loading                                  | 81  |

|          |       | 6.1.2    | Output Layer Integrate and Fire Neurons              | 82  |

|          |       | 6.1.3    | Weight Application at the Time of Spike Events       | 83  |

|          |       | 6.1.4    | Output Spike Counting                                | 83  |

|          | 6.2   | Networ   | k Operation                                          | 83  |

|          | 6.3   | Results  |                                                      | 85  |

| 7        | Con   | clusion  |                                                      | 86  |

|          | 7.1   | A Sum    | mary of Conclusions                                  | 86  |

|          |       | 7.1.1    | Spiking Neuron Implementations                       | 86  |

|          |       | 7.1.2    | Spiking Neural Networks                              | 87  |

|          | 7.2   | Possible | e Future Works and Extensions                        | 88  |

| Bi       | bliog | raphy    |                                                      | 89  |

| Vi       | ta A  | uctoris  |                                                      | 101 |

## List of Tables

| 2.1 | Error Measures of the HOMIN Model for MATLAB simulations                                                                               |

|-----|----------------------------------------------------------------------------------------------------------------------------------------|

|     | conducted at I =15 $\dots \dots \dots$ |

| 2.2 | FPGA Resource Usage Comparisons Between the Implemented HOMIN                                                                          |

|     | Neuron and Previously Proposed FPGA Hardware Systems Based                                                                             |

|     | on the Izhikevich Neuron Model                                                                                                         |

| 3.1 | Hodgkin-Huxley neuron parameter sets used for testing 30                                                                               |

| 3.2 | Error evaluation for select CORDIC Algorithm iteration numbers                                                                         |

|     | for exponential, multiplication, and division terms                                                                                    |

| 3.3 | Error measurements for the proposed CORDIC implementation of                                                                           |

|     | the Hodgkin-Huxley neuron using Parameter Set 1 (PS1) and Pa-                                                                          |

|     | rameter Set 2 (PS2). The low observed error implies that the pro-                                                                      |

|     | posed CORDIC implementation closely matches the original neuron                                                                        |

|     | model                                                                                                                                  |

| 3.4 | Fixed Points and corresponding eigenvalues for the Hodgkin-Huxley                                                                      |

|     | Neuron and the CORDIC HH Neuron for varying current using                                                                              |

|     | Parameter Set 1. The proximity of the fixed points between the                                                                         |

|     | CORDIC HH and the original Hodgkin-Huxley neuron implies close                                                                         |

|     | behavioural similarity                                                                                                                 |

| 3.5 | Post implementation FPGA resource usage information for the pro-                                                                       |

|     | posed CORDIC Hodgkin Huxley Neuron and previously proposed                                                                             |

|     | FPGA implementations of the Hodgkin-Huxley Neuron. *Note:                                                                              |

|     | Modelling RMSE for [44], [43], and the proposed implementation                                                                         |

|     | was computed by evaluating the error in the membrane potential                                                                         |

|     | for the proposed implementation approximations and methods to                                                                          |

|     | the original Hodgkin-Huxley neuron model for various input cur-                                                                        |

|     | rents. See the Error Analysis subsection for detailed information                                                                      |

|     | on the error analysis                                                                                                                  |

| 4.1 | FPGA Resource Usage Information on the Xilinx Spartan 7 for                                                                                                                                                                                                   |    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | neuron implementations with and without the I-DEVS method. $\ .$ .                                                                                                                                                                                            | 62 |

| 4.2 | Dynamic Power Estimates for a 50MHz clock for ASIC and FPGA $$                                                                                                                                                                                                |    |

|     | digital implementations of the AdEx and Izhikevich neurons us-                                                                                                                                                                                                |    |

|     | ing the I-DEVS method. Note that the I-DEVS column for power                                                                                                                                                                                                  |    |

|     | reports from [69] is used to report the power consumption of the                                                                                                                                                                                              |    |

|     | CORDIC implementation.                                                                                                                                                                                                                                        | 66 |

| 5.1 | Python simulation results for all 10000 test images for baseline<br>Fully-Connected (FC) SNNs and SNNs with Selective Input Spar-<br>sity (SIS). $dt = 0.25$ and each test image was exposed for 16 time<br>steps                                             | 78 |

| 6.1 | FPGA hardware implementation resource utilization and perfor-<br>mance for 1000 test images compared to expectations from Python<br>simulations for the MNIST digits classification network. Both hard-<br>ware designs were implemented on the Kintex-7 FPGA | 84 |

|     | ware designs were implemented on the Militex-7 F1 GA                                                                                                                                                                                                          | 04 |

# List of Figures

| 2.1 | Phase portraits for the original Izhikevich model and the HOMIN                                  |    |

|-----|--------------------------------------------------------------------------------------------------|----|

|     | model for zero input current. In both phase portraits, the black line                            |    |

|     | shows the nullcline of $\frac{dv}{dt}$ , the green line shows the nullcline of $\frac{du}{dt}$ , |    |

|     | and trajectories are shown in blue.                                                              | 11 |

| 2.2 | MATLAB simulations of the membrane potential as a function of                                    |    |

|     | time. (A), (C), (E), (G) show the Izhikevich model for a constant                                |    |

|     | input current of I=150 and (B), (D), (F), (H) show the HOMIN                                     |    |

|     | model for a corresponding scaled constant input of I=15. Input                                   |    |

|     | was applied at t = 0.1ms. The values of the parameter $d$ that cor-                              |    |

|     | respond to the spiking patterns for the HOMIN model are labelled.                                |    |

|     | Regular Spiking (RS), Initial Bursting (IB), Chattering (CH), and                                |    |

|     | Low-Threshold Spiking (LTS) behaviours are shown.                                                | 15 |

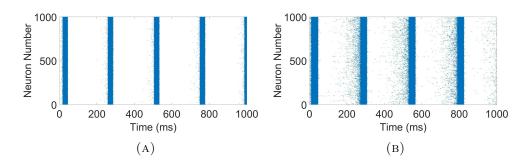

| 2.3 | Raster Plots of 1000 randomly connected excitatory neurons for (a)                               |    |

|     | an Izhikevich Neuron and (b) The HOMIN Neuron                                                    | 16 |

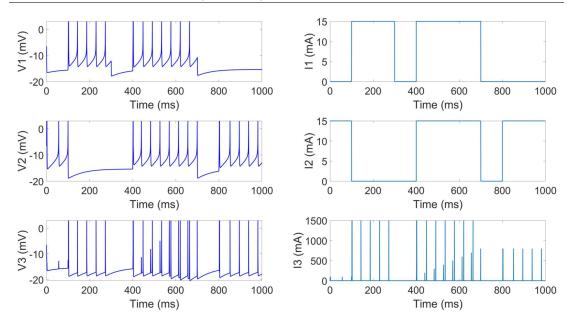

| 2.4 | A simulation of three HOMIN Neurons showing the membrane po-                                     |    |

|     | tential and corresponding input current for each neuron. After the                               |    |

|     | associative learning period, spikes from Neuron 2 are able to cause                              |    |

|     | spikes from Neuron 3                                                                             | 17 |

| 2.5 | Quartus ModelSim simulations of the implemented digital hardware                                 |    |

|     | system                                                                                           | 18 |

| 2.6 | Oscilloscope window captures of the implemented neuron for differ-                               |    |

|     | ent spiking patterns for varying values of parameter $d$ at a constant                           |    |

|     | input current of $I = 28mA$                                                                      | 20 |

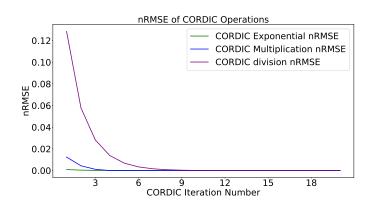

- 3.1 nRMSE of the CORDIC algorithm applied to multiplication, division, and the exponential function for 10000 trials at each CORDIC iteration number from 1 to 20. The input operands were normally distributed random numbers in the typical operand range for each operation as found in the Hodgkin-Huxley neuron model. . . . . . 25

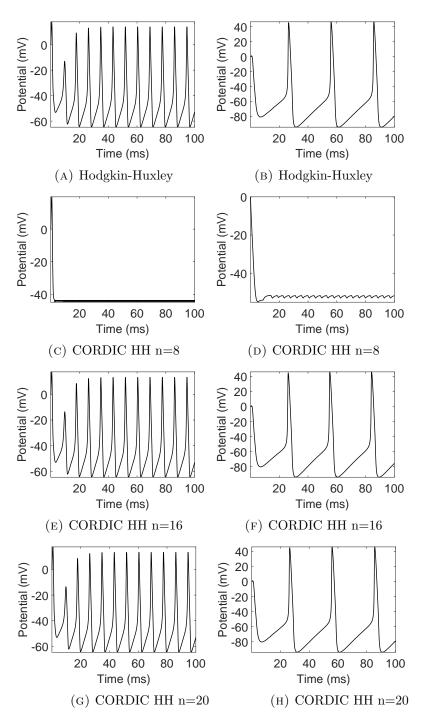

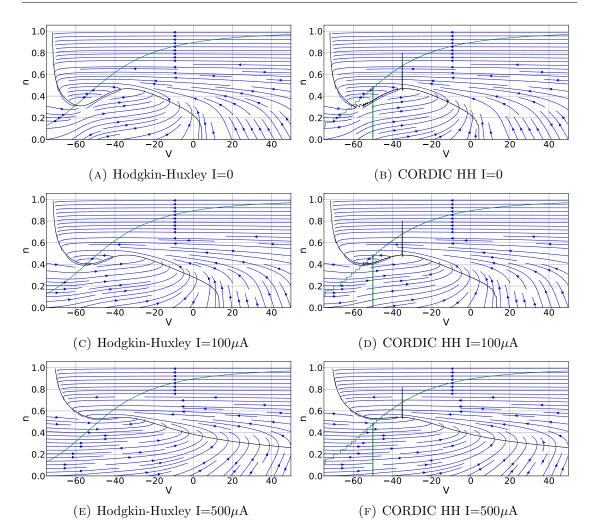

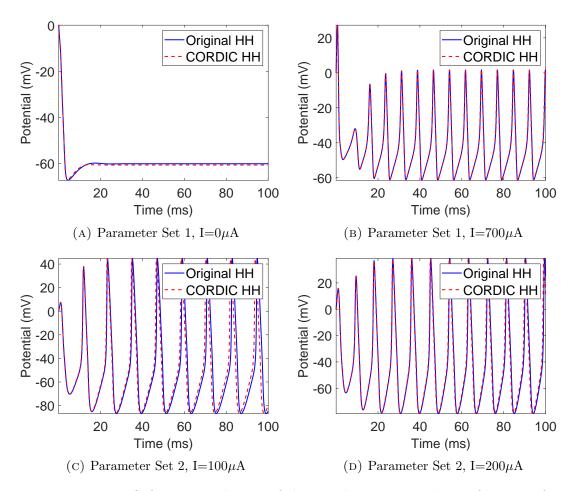

- 3.2 Software simulations of the membrane potential as a function of time of (A) and (B) the original Hodgkin-Huxley Neuron and (C), (E), (G) and (D), (F), (H) the CORDIC Hodgkin-Huxley Neuron for two different parameter and current operational points. (A), (C), (E), (G) show operation for Parameter Set 1 for a current of I = 500μA, while (B), (D), (F), (H) show operation for Parameter Set 2 for a current of I = 20μA. Between 16 and 20 iterations using the CORDIC algorithm, qualitative changes in the neuron's behaviour are not observed. Thus, an upper bound on the necessary iterations of the CORDIC algorithm exists.

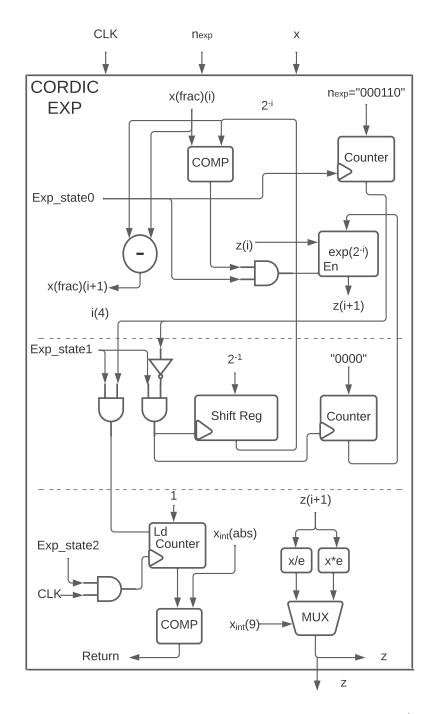

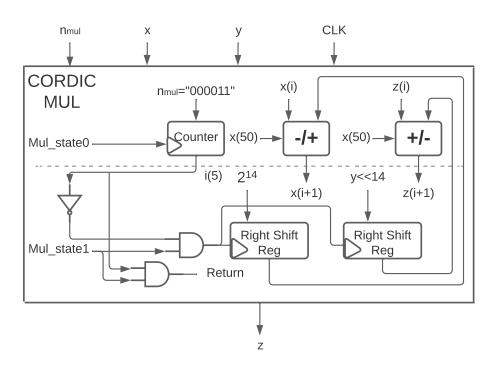

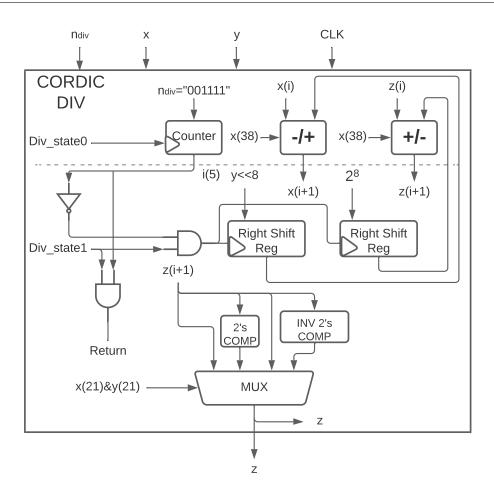

| 3.5 | A block diagram of the CORDIC exponential unit. $e^{2^{-i}}$ is imple-                                                    |    |

|-----|---------------------------------------------------------------------------------------------------------------------------|----|

|     | mented using multiplexed shift and add operations. $z$ is initially                                                       |    |

|     | set to one and conditionally updated based on the control signal                                                          |    |

|     | generated by the comparison of $x(frac)$ (the fractional part of x)                                                       |    |

|     | and $2^{-i}$                                                                                                              | 41 |

| 3.6 | A block diagram of the CORDIC multiplication unit                                                                         | 42 |

| 3.7 | A block diagram of the CORDIC division unit.                                                                              | 43 |

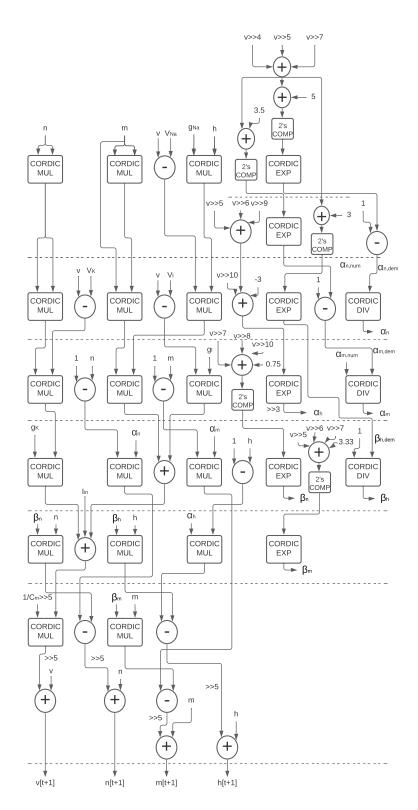

| 3.8 | An overall scheduling diagram of the proposed neuron                                                                      | 44 |

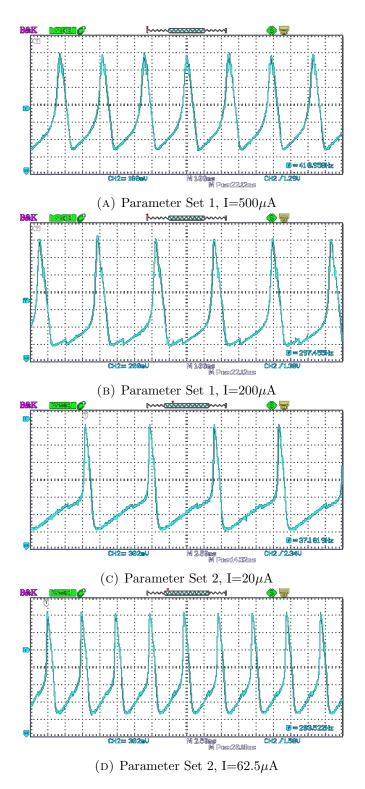

| 3.9 | Oscilloscope images showing the membrane potential of the im-                                                             |    |

|     | plemented neuron for different input synaptic currents and input                                                          |    |

|     | parameters                                                                                                                | 45 |

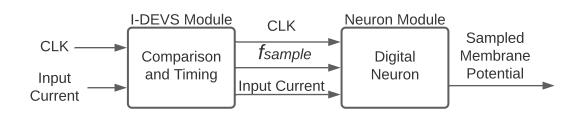

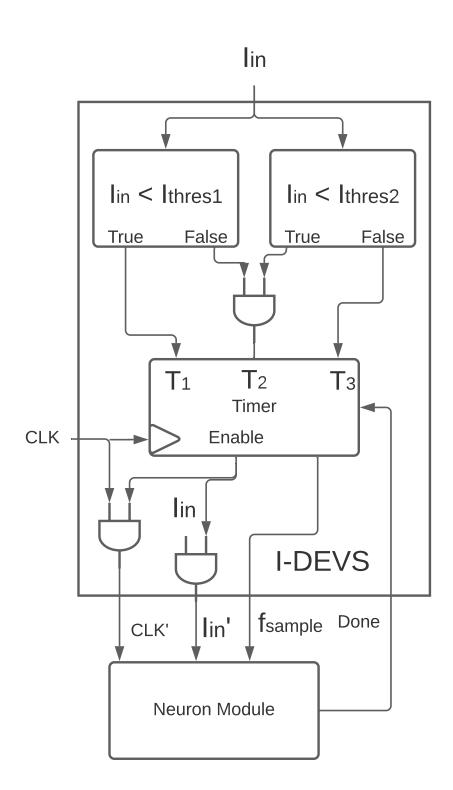

| 4.1 | A high-level block diagram of the proposed I-DEVS neuron method.                                                          | 54 |

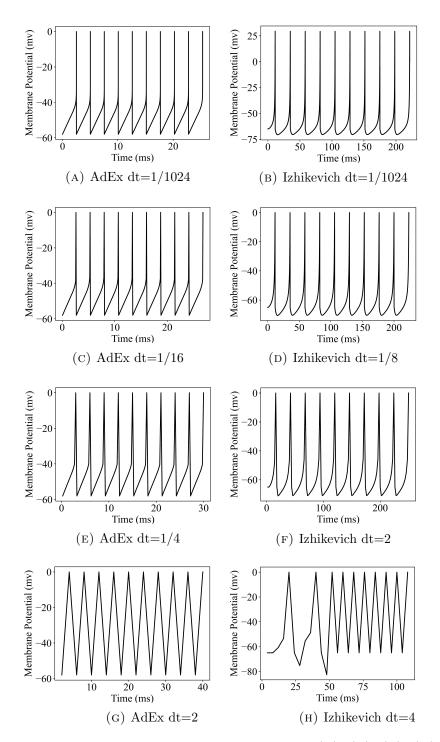

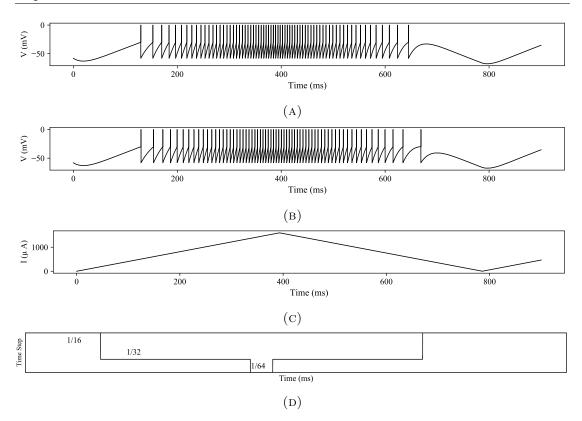

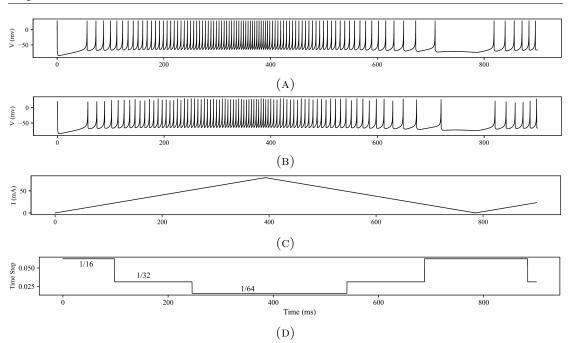

| 4.2 | Membrane potential waveform of (A), (C), (E), (G) the AdEx (B),                                                           |    |

|     | (D), (F), (H) the Izhikevich neurons for different time steps                                                             | 56 |

| 4.3 | Threshold time steps at which the (A) AdEx and (B) Izhikevich                                                             |    |

|     | neurons become unstable as function of input current                                                                      | 57 |

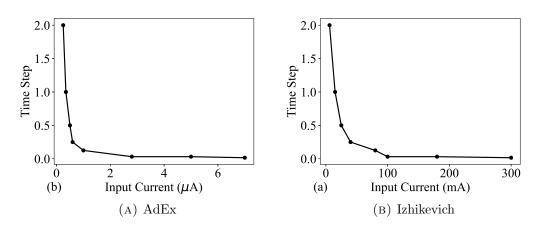

| 4.4 | Simulations of the AdEx Neuron with and without a variable time                                                           |    |

|     | step for a triangular wave current. (A) shows the membrane po-                                                            |    |

|     | tential of an AdEx neuron with a fixed timestep of $dt = 1/512$ (B)                                                       |    |

|     | shows the membrane potential of an AdEx neuron with the I-DEVS $$                                                         |    |

|     | method, (C) shows the input current, and (D) shows the value of                                                           |    |

|     | dt as a function of time                                                                                                  | 58 |

| 4.5 | Simulations of the Izhikevich Neuron with and without a variable                                                          |    |

|     | time step for a triangular wave current. (A) shows the membrane                                                           |    |

|     | potential of an Izhikevich neuron with a fixed timestep of $dt = 1/512$                                                   |    |

|     | (B) shows the membrane potential of an Izhikevich neuron with the                                                         |    |

|     | I-DEVS method, (C) shows the input current, and (D) shows the                                                             |    |

|     | value of $dt$ as a function of time $\ldots \ldots \ldots$ | 59 |

| 4.6 | A block diagram of the digital hardware implementation I-DEVS           |    |

|-----|-------------------------------------------------------------------------|----|

|     | module                                                                  | 60 |

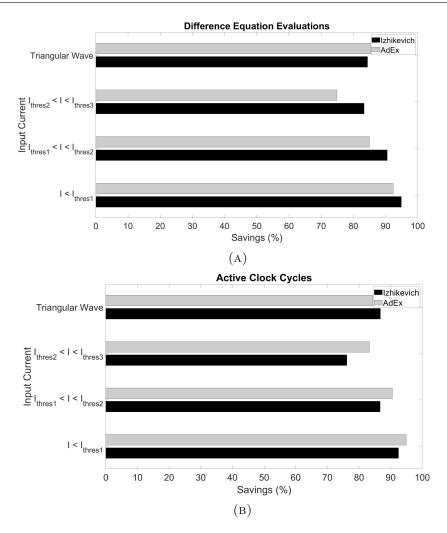

| 4.7 | Computational savings per time from the I-DEVS method com-              |    |

|     | pared to traditional implementations for the AdEx and Izhikevich        |    |

|     | neurons. (A) shows the savings in difference equation evaluations       |    |

|     | and (B) shows the savings in clock cycles for which the neuron is       |    |

|     | active                                                                  | 61 |

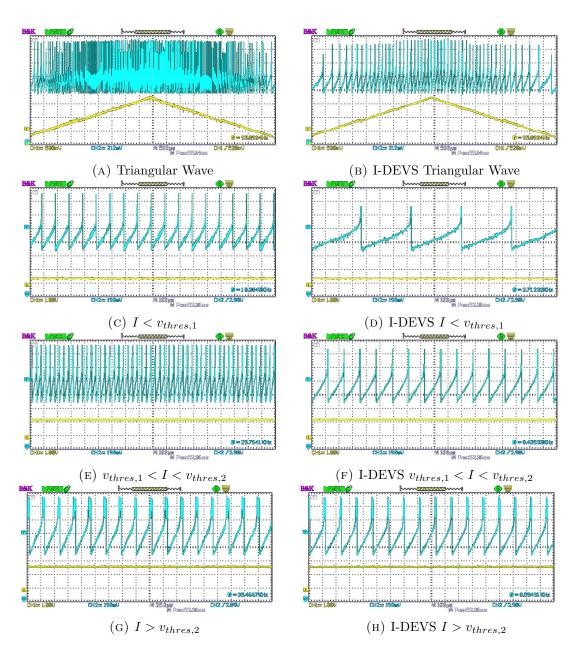

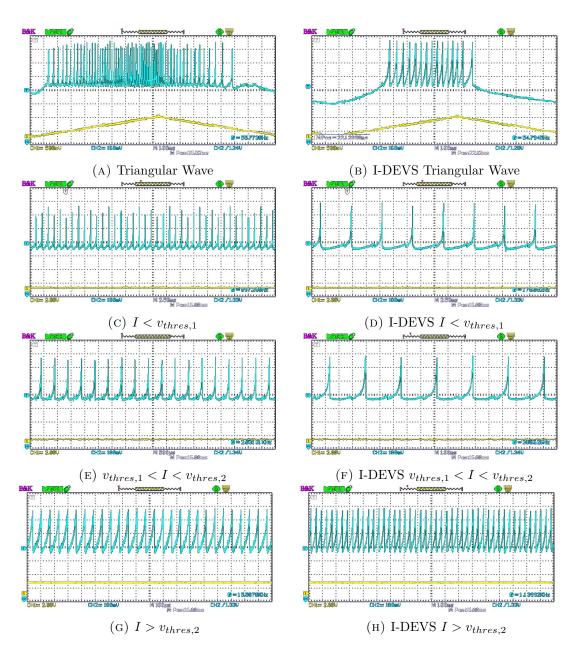

| 4.8 | Oscilloscope images for (A), (C), (E), (G) an AdEx Neuron imple-        |    |

|     | mented using traditional hardware implementation, and (B), (D),         |    |

|     | (F), (H) the same neuron implemented using the I-DEVS method.           |    |

|     | Membrane potential is shown in blue and input current is shown in       |    |

|     | yellow. Horizontally paired images show the same input current          | 63 |

| 4.9 | Oscilloscope images for (A), (C), (E), (G) an Izhikevich Neuron         |    |

|     | implemented using traditional hardware implementation, and (B),         |    |

|     | (D), (F), (H) the same digital neuron implemented using the I- $\!\!\!$ |    |

|     | DEVS method. Membrane potential is shown in blue and input              |    |

|     | current is shown in yellow. Horizontally paired images show the         |    |

|     | same input current                                                      | 64 |

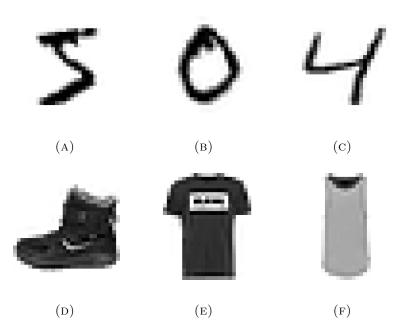

| 5.1 | Sample images from (a) - (c) the MNIST handwritten digit database       |    |

|     | [88] and (d) - (f) the Fashion MNIST database [89]                      | 70 |

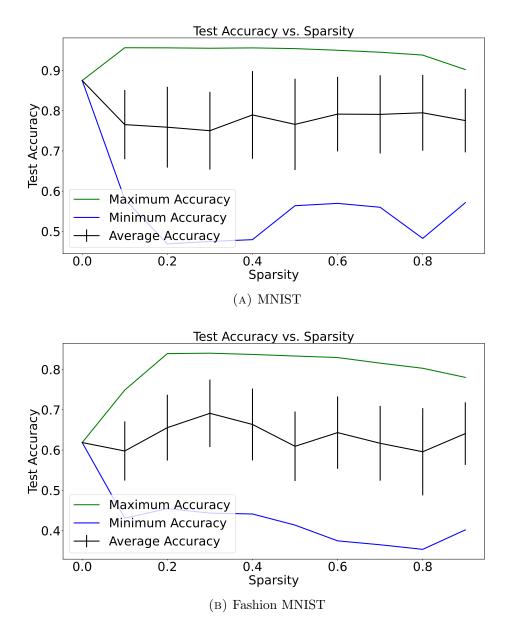

| 5.2 | Average, maximum, and minimum classification accuracy observed          |    |

|     | from 100 trials at each level of input sparsity. It is interesting to   |    |

|     | observe that the proposed experimentation does not present a clear      |    |

|     | relationship between the input sparsity and classification accuracy     | 73 |

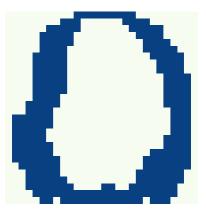

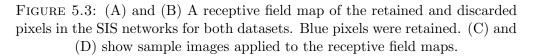

| 5.3 | (A) and (B) A receptive field map of the retained and discarded         |    |

|     | pixels in the SIS networks for both datasets. Blue pixels were re-      |    |

|     | tained. (C) and (D) show sample images applied to the receptive         |    |

|     | field maps                                                              | 76 |

# Chapter 1

# Introduction

Artificial Intelligence (AI) is currently an active and exciting field with everexpanding applications and relevance. Software and hardware AI systems have seen widespread use in various applications.

AI systems draw inspiration from naturally occurring biological neural systems [1]. The basic elements of biological neural systems are neurons and synapses. Neurons receive stimulus in the form of electric current and transmit information through spikes in their membrane potential [2]. The information is encoded in the timing and the rate of these spikes through mechanisms such as rate coding, although other methods have been proposed [3]. Neurons are connected to each other through synapses and the strength of the connection is called the synaptic weight.

Traditional Artificial Neural Networks (ANNs) use a time-static approach in which the spiking rate of the neuron is modelled by a transfer function that returns a value that is a percentage of what the spiking rate of a spiking neuron would be. Sigmoidal or linear transfer functions are common in traditional ANNs, but not obligatory [1]. Although this approach is useful, it is not a true emulation of biological systems since neurons are not linear nor time-invariant. Spiking Neural Networks (SNNs) offer a more complete replication of biological neural systems with extended applications compared to traditional ANNs.

## **1.1** Elements of Spiking Neural Networks

#### 1.1.1 Spiking Neuron Models

The spiking behaviours of biological neurons are quite diverse and many mathematical models with varying description levels have been proposed to model their behaviours. nearly all models are composed of differential equation(s) of the neuron's membrane potential.

Among the most biologically detailed models are the Hodgkin-Huxley neuron model [4] and the Morris-Lecar model [5]. Low-level, high detail models offer more accurate and meaningful descriptions of natural neurological systems. In the case of the Hodgkin-Huxley neuron model [4], all of the behavioural parameters used in the model have physiological meaning which makes the model very descriptive. Furthermore, the Hodgkin-Huxley neuron was the first conductance-based neuron model and is the basis of conductance-based neuron modeling [6]. However, the primary drawback of detailed models is their typically high computational intensity. In the case of the Hodgkin-Huxley neuron model, there are four interdependent differential equations with six parameters that depend on the state of the membrane potential. The complexity of this level of neuron model elongates software simulation and complicates potential hardware implementations.

Other models offer a less detailed description but are still able to capture all of the neuron's behaviours. These models include the Izhikevich model [7], the Adaptive-Exponential Integrate-and-Fire model [8], and the Wilson Model [9]. Models of this level of biological detail tend to be a compromise between complexity and biological parallelism. They are able to replicate the behaviours found in biological neurons,

but their modeling parameters do not necessarily directly model a physiological characteristic of a neuron.

A simpler, phenomenological description of neuronal behaviour can be found in the Leaky Integrate-and-Fire (LIF) Neuron Model [10]. This model was originally proposed in 1907 and offers a very simple explanation of the spiking behaviours observed in neurons.

Each level of biological detail clearly has advantages and drawbacks and model selection should be heavily influenced by the target application. Applications and neuron model fitness for a given application will be elaborated further subsequently.

### 1.1.2 Synapses and Learning

Many learning mechanisms have been proposed to model and explain biological learning, but among the most prominent learning mechanisms is Spike-Timing-Dependent Plasticity (STDP) [11]. STDP is a positive feedback-based learning mechanism in which the timing of the spikes in the membrane potentials of a given pre-synaptic and post-synaptic neuron pair is compared. If the pre-synaptic neuron spikes before the post-synaptic neuron, then the strength of the synaptic connection, that is, the synaptic weight, increases. In contrast, if the post-synaptic neuron spikes before the pre-synaptic neuron, then the synaptic weight decreases.

Furthermore, recent explorations have found that traditional ANNs can be trained using well defined methods, such as stochastic gradient descent, and the trained weights can be transferred to SNNs of analogous structure [12], and more complicated network structures may only require weight adjustment [13, 14]. This methodology has been used with significant success in hardware implementations of SNNs [15].

## 1.2 Motivation

#### **1.2.1** Neuron Implementations

Since the fundamental unit of a neural network is the neuron, the design of a neuron in hardware is critical. To emulate biology, the neuron must be energy-efficient and require minimal hardware resources. Additionally, the neuron model selected for a network is an important consideration. Some applications, such as neurological disease modeling require high biological parallelism from the neuron [16], while other applications may not require a high level of biological detail.

Thus, two neuron model implementations are presented in Chapters 2 and 3 with different levels of biological detail and varying accuracy/resource trade-offs as they are presented with different intended applications.

#### **1.2.2** Spiking Neural Network Implementations

Software-based AI solutions have excelled in many applications and have seen widespread use [17]. However, when compared to custom hardware solutions and/or programmable logic such as Field Programmable Gate Array (FPGA) solutions, software solutions are far slower and consume a great deal more power [17,18]. Given the incredible amounts of data generated and processed in modern machine learning and AI systems, speed and power consumption are increasingly important considerations.

Unlike traditional ANNs, SNNs are time dynamic and have extended applications in real-time control problems [19] and neuronal disease modelling [20], among other fields. Additionally, the spike-based temporally sparse operation of SNNs may lend itself to reduced power consumption in hardware implementations [12, 18, 21]. Within the realm of hardware implementation many options exist. Analog Application-Specific Integrated Circuit (ASIC) implementations typically offer the lowest power consumption and excellent speed, but require extensive design overhead, are often very inflexible after the design phase, and are typically more susceptible to error and noise [22]. Moreover, digital ASIC is more robust to noise, but again suffers from large design time and limited flexibility after fabrication. FPGA solutions offer high flexibility and rapid prototyping as well as many of the speed and power benefits of ASIC to a lesser degree.

Thus, given the potential benefits of hardware implementations of SNNs, an FPGA implementation of an SNN is a logical target. Many hardware SNNs have been proposed in academic literature [15,23,24] with various advantages and drawbacks. Many proposals focus on implementing STDP learning in hardware [25, 26], but this imposes limitations on the complexity of the problem the system can solve since these approaches, even in software require an extensive number of synapses [27,28].

Therefore, for practical applications, pre-trained SNN hardware provides an efficient solution to practical applications that require on-edge inference. The work of the second part of this dissertation presents the development of digital hardware implementations of SNNs for edge inference in pattern recognition. Simple architectures are employed and novel methods for network size reduction compared to a baseline fully-connected architecture are explored and presented and the results are compared with the baseline implementation.

## 1.3 Objectives

This dissertation has two main objectives. The first is the evaluation of hardware implementation methods and novel implementation techniques for neuromorphic hardware. The second is the development of novel methods by which the size of SNNs can be reduced to result in faster inferences and lower silicon area requirements in digital hardware.

## **1.4** Dissertation structure

The dissertation is divided into two main parts. The first part, comprised of Chapters 2 - 4 presents works that firstly target improvements to FPGA hardware implementations of spiking neurons. Several neuron models are investigated, and results are presented and discussed. Subsequently, the second part, comprised of Chapters 5 and 6 present novel methods for digital hardware resource reductions in the implementation of SNNs for on-edge inference in image pattern recognition problems and corresponding hardware implementations.

Chapter 2 presents mathematical modifications to the Izhikevich neuron model[7] that simplify the digital hardware requirements for implementation.

**Chapter 3** presents an implementation of the Hodgkin-Huxley neuron model [4], one of the most biologically meaningful neuron models, using the Co-Ordinate Rotational DIgital Computer (CORDIC) algorithm to reduce the complexity of a digital hardware implementation.

**Chapter 4** presents a sampling-based hardware implementation methodology by which the power consumption of a biologically detailed digital neuron can be reduced.

**Chapter 5** presents the concept of input sparsity applied to SNNs and its significance in reducing the hardware requirements of digital on-edge inference networks. The novel Selective Input Sparsity (SIS) method is introduced and used to implement a digital SNN.

Chapter 6 presents Field-Programmable Gate Array (FPGA) digital hardware implementations of the networks described in Chapter 5.

**Chapter 7** summarizes and broadly discusses the work to form a conclusion and suggest possible future extensions and continuations.

# Chapter 2

# An Efficient Spiking Neuron Hardware System Based on the Hardware-Oriented Modified Izhikevich Neuron (HOMIN) Model

The basic element of a neural network is a neuron, which uses voltage spikes to transmit information, and the information is transmitted primarily in the timing of these spikes [3]. Biologically accurate neuron behavioural models, most notably the Izhikevich [7] and Adaptive-Exponential Integrate-and-Fire (AdEx) [8] neuron models successfully capture the natural spiking phenomena exhibited by real neurons. However, biological neurons and accurate mathematical models are neither time-invariant nor linear, making hardware realizations of these models challenging. Many hardware implementations of Spiking Neurons in analog [31–33], digital [34–38], and mixed signal [39, 40] systems have been proposed. However,

implementations with high accuracy to the mathematical neuron model are computationally expensive. Furthermore, digital hardware realizations of a biologically accurate neuron model in its presented form would be computationally intensive, making large networks of highly accurate neurons not feasible on a single Integrated Circuit die.

Thus, it is evident that compromises must be made between the accuracy of the neuron to biological behaviour and the computational requirements of the implemented hardware system to make the neuron a practical candidate for use in a spiking ANN. The model must have a low computational cost while simultaneously maintaining a sufficient level of accuracy and performance.

Spiking Neural Networks (SNNs) are more accurate to the function of biological neural networks than conventional ANNs, implying the potential applications of SNNs is far more diverse as they show potential not only in pattern recognition but also in biomedical applications [41]. Therefore, exploration into viable hardware for improved SNNs is significant.

Many previous digital hardware implementations of spiking neurons are able to successfully replicate complex neuron behaviours [35,36]. However, to achieve their performance, they have very high resource requirements, and few optimizations are performed to lower hardware costs. Additionally, many system parameters must be externally set to change the neuron's behaviours. All these drawbacks are restrictive of the size of a potential network of such neurons.

Furthermore, biological neurons use rate coding and temporal coding, methods by which information is transmitted in the neuron's firing rate and the timing of the firings [1,3,41]. This implies that the firing rate and timing are of higher significance than the shape of the neuron's membrane voltage in the time domain.

To fulfill the required compromises, a variation of the Izhikevich Neuron Model [7] for a computationally low-cost digital hardware realization has been developed.

This Hardware-Oriented Modified Izhikevich Neuron (HOMIN) spiking neuron model modifies the original Izhikevich model, which results in an imperfect match to the Izhikevich model that still shows all cortical neuron behaviours, to greatly reduce hardware costs and required resources while simultaneously allowing for reduced projected interconnection requirements within a spiking neural network.

The formulation of the model is presented in detail, along with mathematical justification. Subsequently a hardware implementation of this new spiking neuron model is detailed, and comparisons are made.

# 2.1 Mathematical Preparations for Hardware Implementation

## 2.1.1 Formulation of the Hardware-Oriented Modified Izhikevich Neuron (HOMIN) Model

The original spiking neuron model proposed by Izhikevich in 2003 [7] is a mathematically simple approximation of biological reality that is able to reproduce a large variety of spiking patterns exhibited in real neural systems.

The model is a system of two interdependent differential equations with an auxiliary reset condition. The system is characterized by the following two equations and reset condition:

$$\frac{dv}{dt} = 0.04v^2 + 5v + 140 - u + I \tag{2.1}$$

$$\frac{du}{dt} = a(bv - u) \tag{2.2}$$

$$ifv \ge 30mV, then \begin{cases} v \to c \\ u \to u+d \end{cases}$$

(2.3)

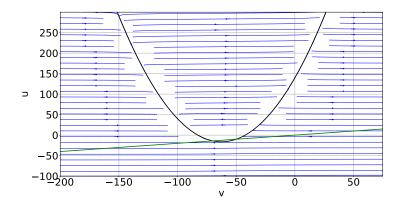

(A) Izhikevich Model for I=0 and regular spiking behaviour (a=0.02, b=0.2, c=-65, d=8).

(B) HOMIN Model for I=0 and regular spiking behaviour (d=6).

FIGURE 2.1: Phase portraits for the original Izhikevich model and the HOMIN model for zero input current. In both phase portraits, the black line shows the nullcline of  $\frac{dv}{dt}$ , the green line shows the nullcline of  $\frac{du}{dt}$ , and trajectories are shown in blue.

where v is the membrane potential of the neuron, u is the membrane recovery variable, and I is the input current to the neuron. The parameters a, b, c, and d describe the recovery variable time scale, sensitivity of the recovery variable, after-spike reset value of the membrane potential, and the after-spike reset of the recovery variable respectively.

Figure 2.1a shows the phase of the original Izhikevich Model. The neuron approaches firing when the value of u is below the curve defined by the nullcline of Equation 2.1 and to the right of the value of the membrane potential c.

To achieve different spiking behaviours, a and b experience the smallest amount of change in the Izhikevich model. Parameter c is varied to adjust the position of the reset potential on the phase portrait relative to the nullcline of Equation 2.1 and d is varied to effect the behaviour of the system when a spike and subsequent reset occurs. For spiking patterns in which spikes must occur in quick secession, cis positioned at a steeper section of the nullcline of Equation 2.1.

The proposed HOMIN model simplifies the modifications necessary to generate varying spiking patterns by holding parameters a, b, and c constant and using a relatively less steep nullcline of  $\frac{dv}{dt}$  for the system to increase the influence of parameter d on the type of spiking behaviour exhibited by the system. Since parameter ddirectly affects the reset position of the system, a less steep nullcline implies that parameter d becomes far more influential to the system's post-spike behaviour. Thus, it was found that if parameter d is set sufficiently, it can solely determine the post-spike system state such that it can determine if the system returns to a position of trajectory tending toward an eminent spike or a delayed spike. Consequently, the HOMIN model can exhibit all excitatory neuron behaviours while only varying parameter d to adjust the behaviour of the system at the time of an after-spike reset. The relative steepness of the  $\frac{dv}{dt}$  nullcline was decreased by lowering the value of the coefficient of the  $v^2$  term. Since the HOMIN model is formulated with the goal of a simple digital hardware implementation, the scaled value was selected as a power of 2, meaning it will translate into a simple arithmetic shift in fixed point operations. This reduces multiplication operations in a digital hardware implementation, making the system significantly faster and less resource intensive. Figure 2.1b shows the phase portrait of the HOMIN model. Since it is only parameter d that changes in the HOMIN model, it is noted that the phase plane of the HOMIN model, unlike the Izhikevich model, does not change depending on the firing mode since parameter d only alters the post-spike reset position of the system. It is evident from Figure 2.1 that the HOMIN model exhibits a much steeper  $\frac{dv}{dt}$  nullcline than the original Izhikevich Model.

To reduce the required representation range in digital hardware, the HOMIN model uses a scaled range for the operation of the system. All variables in the HOMIN model are scaled down by a factor of 10 compared to the Izhikevich model. Since  $v^2$ , for a scaled v, will cause reduction by a factor of 100, the coefficient of this term must be scaled up by a factor of 10 to compensate, causing this to change from 0.04 to 0.4 in the original Izhikevich model. This coefficient was then modified to  $0.25 = 2^{-2}$ , which causes a sufficient decline in steepness in the system's nullcline.

Furthermore, parameters a and b were approximated by fixed powers of 2 such that they result in shifts in digital hardware and do not require loading circuitry. After all modifications, the HOMIN model can be described by:

$$\frac{dv}{dt} = (2^{-2})v^2 + (2^2)v + v + 14 - u + I$$

(2.4)

$$\frac{du}{dt} = (2^{-6})((2^{-2})v - u) \tag{2.5}$$

$$ifv \ge 3mV, then \begin{cases} v \to c \\ u \to u+d \end{cases}$$

(2.6)

where any multiplication by a power of 2 translates into a simple arithmetic shift in a digital hardware implementation. Not only does this model greatly reduce the hardware requirements by reducing the number of multiplications, it also reduces the required loading circuitry since parameters a, b, and c are system constants instead of variable parameters as in the original Izhikevich model.

#### 2.1.2 Discretization of the HOMIN Model

To be implemented into digital hardware, the HOMIN model was discretized using Euler's method and the time step dt was selected as  $dt = 0.03125 = 2^{-5}$  for convenience in a digital hardware implementation. The final form of the discretized

HOMIN model is:

$$v[n+1] = v[n] + 2^{-5}(2^{-2}v^2 + 2^2v[n] + v[n] + 14 - u[n] + I[n])$$

(2.7)

$$u[n+1] = u[n] + 2^{-11}(2^{-2}v[n] - u[n])$$

(2.8)

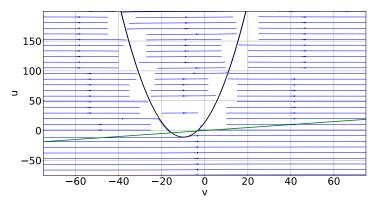

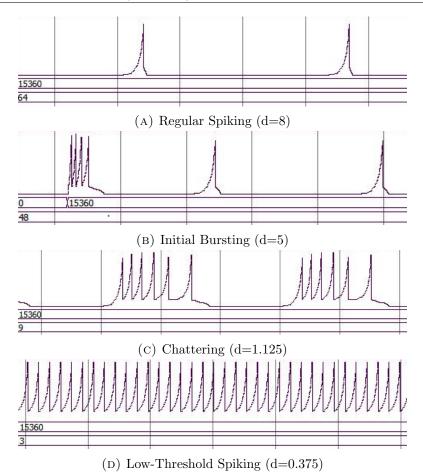

Figure 2.2 shows MATLAB simulations of voltage traces of the HOMIN model when varying only parameter d for a constant applied input current.

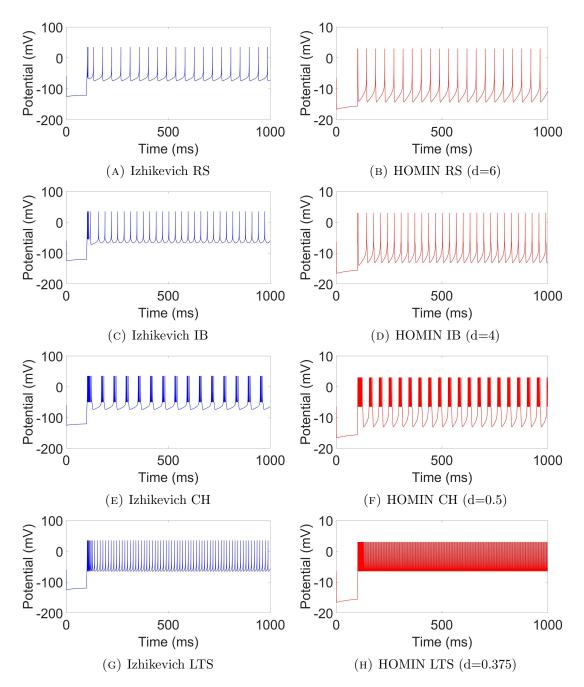

Figure 2.3 shows raster plots for both the Izhikevich Neuron and the HOMIN neuron for 1000 randomly connected excitatory neurons. It is noted from this figure that the HOMIN model exhibits a higher firing activity level at the time points in which the firing is clustered as well as between clusters. This can be attributed to a higher input sensitivity for the HOMIN model. Additionally, there is a small error in the timing of the spiking clusters between the two models. However, in a network both discrepancies could be remedied by appropriate synaptic weights.

From Figure 2.2, it is evident that the four spiking phenomena shown can be produced exclusively through variations of the value of d within a resolution that can be achieved using an 6-bit unsigned digital fixed-point value in which there are 3 integer bits and 3 fractional bits. This implies that, in a network of HOMIN neurons, the behavioural characteristics of each neuron can be controlled using only a 6-bit parameter, which is a major reduction in interconnection requirements in comparison to the original Izhikevich neuron's interconnection requirements to achieve the same spiking patterns.

Since information is encoded in the timing of the spikes in a spiking neural network [2], timing comparison was performed. Following the error analysis performed in [34], the Mean Relative Error (MRE) was used to analyse the timing performance of the HOMIN model. MRE is defined as:

$$MRE\% = \frac{\sum_{i=1}^{n} \frac{t_{HOMIN} - t_{Izh}}{t_{Izh}}}{n} 100\%$$

(2.9)

FIGURE 2.2: MATLAB simulations of the membrane potential as a function of time. (A), (C), (E), (G) show the Izhikevich model for a constant input current of I=150 and (B), (D), (F), (H) show the HOMIN model for a corresponding scaled constant input of I=15. Input was applied at t = 0.1ms. The values of the parameter d that correspond to the spiking patterns for the HOMIN model are labelled. Regular Spiking (RS), Initial Bursting (IB), Chattering (CH), and Low-Threshold Spiking (LTS) behaviours are shown.

An Efficient Spiking Neuron Hardware System Based on the Hardware-Oriented Modified Izhikevich Neuron (HOMIN) Model

FIGURE 2.3: Raster Plots of 1000 randomly connected excitatory neurons for (a) an Izhikevich Neuron and (b) The HOMIN Neuron

TABLE 2.1: Error Measures of the HOMIN Model for MATLAB simulations conducted at I =15

| Spiking Behaviour | MRE (%) |

|-------------------|---------|

| Regular Spiking   | 2.087   |

| Initial Bursting  | 2.192   |

Table 2.1 shows these error quantities. It is noted that an MRE for tonic spiking of 4.09% was reported in [36] and 1.21% in [34], implying that the error observed in the HOMIN model compared to the Izhikevich model is sufficiently small given the presented hardware resource savings.

Figure 2.4 shows a MATLAB simulation of a network of three HOMIN neurons in which the output membrane potential of Neurons 1 and 2 are used to generate the input current for Neuron 3. Initially Neuron 1 causes Neuron 3 to spike, but Neuron 2 does not. After a period of associative, unsupervised learning where Neurons 1 and 2 are stimulated together, Neuron 2 is able to cause Neuron 3 to spike after the learning period. This serves as a simple example to show that the HOMIN model is a viable candidate for unsupervised learning in a network.

#### **FPGA** Implementation 2.2

The HOMIN neuron model was realized in digital hardware. Verilog HDL was used to implement the design on a simple Altera DE0 Cyclone III FPGA board.

An Efficient Spiking Neuron Hardware System Based on the Hardware-Oriented Modified Izhikevich Neuron (HOMIN) Model 17

FIGURE 2.4: A simulation of three HOMIN Neurons showing the membrane potential and corresponding input current for each neuron. After the associative learning period, spikes from Neuron 2 are able to cause spikes from Neuron 3.

A fixed point implementation was selected with a 16-bit data path of which 1 bit is a sign bit, 6 bits represent the integer part, and 9 bits represent the fractional part. The bits were selected to best represent the relevant information for the spiking behaviour.

Since no relevant information from the neuron's behaviour is present in the low negative values of the membrane voltage, the membrane state variable was clamped to stay above -8 to prevent overflow in the multiplication involved in generating the  $v^2$  term. With the clamp in place, the multiplication was designed such that the upper bits of the product are not evaluated, and the lower bits are approximated using a rounding constant, resulting in an approximation of the product with a far lower resource usage and no full multiplier.

The parameter d was taken as an 8-bit input value to the system where 5 bits are integer part, and 3 bits are fractional part. Although MATLAB simulations showed that the value of d could be represented within the range of a 6-bit fixed point number, an increased system sensitivity to lower values in parameter d was An Efficient Spiking Neuron Hardware System Based on the Hardware-Oriented Modified Izhikevich Neuron (HOMIN) Model 18

FIGURE 2.5: Quartus ModelSim simulations of the implemented digital hardware system.

anticipated in the selected fixed point implementation, thus it was made wider to compensate.

Figure 2.5 shows simulations of the digital hardware system using Quartus Model-Sim. Each of the four behaviours shown in MATLAB simulations were successfully recreated in the digital hardware system.

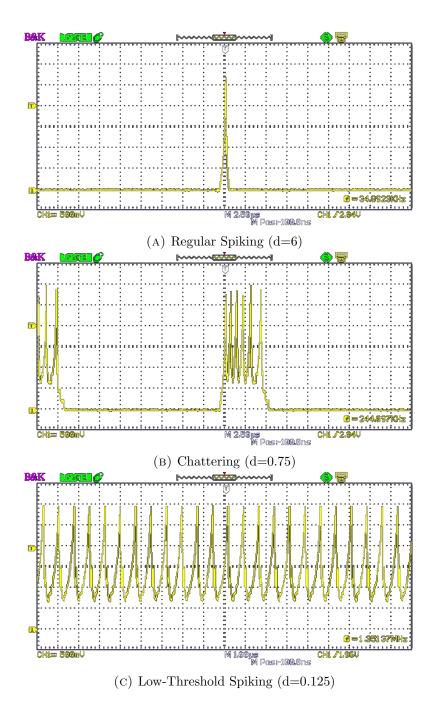

Following successful simulations of the design, the hardware was synthesized on the FPGA board. Figure 2.6 shows images of output captured on an oscilloscope. The digital output was viewed in analog form with 4-bit resolution on the oscilloscope by converting 4-bits of the membrane potential to analog using the RGB connector of the DE0 board. Before conversion, the membrane potential was translated to a

| Resource       | HOMIN | <b>MNIN</b> [34] | Izhikevich [34] |

|----------------|-------|------------------|-----------------|

| Logic Elements | 356   | 490              | 857             |

| Flip Flops     | 41    | 408              | 551             |

| 4-input LUTs   | 346   | 459              | 1268            |

| I/O Pins       | 26    | 34               | 34              |

| 8*18 MULT      | 0     | 0                | 1               |

TABLE 2.2:

FPGA Resource Usage Comparisons Between the Implemented

HOMIN Neuron and Previously Proposed FPGA Hardware Systems Based on

the Izhikevich Neuron Model

positive value domain. Any observed noise in the signal is clearly attributable to the low-resolution conversion to analog. Again, the desired spiking patterns were successfully recreated.

It was expected and observed that the implemented hardware system was less sensitive to input stimulus than the simulated MATLAB model. Additionally, it was found that the values of parameter d to achieve each of the spiking patterns were different in the hardware implementation as expected. This is due to the use of fixed point arithmetic to implement the hardware system.

#### 2.2.1 Hardware Resource Usage

As anticipated, the FPGA implementation of the HOMIN model required far fewer digital hardware resources than previously proposed hardware based on the Izhikevich neuron model. Table 2.2 shows comparisons with previously reported Izhikevich neuron model implementations. The information is taken from [34], where the reported hardware usage is based on the XILINX Vertex II Pro FPGA board. To form a reasonable comparison, a reported slice in [34] was considered equivalent to a logic element in the Altera DE0 board used to implement the HOMIN model. Additionally, a Slice Flip Flop on the XILINX Vertex II Pro was considered equivalent to a flip flop. All of the metrics are shown in Table 2.2.

FIGURE 2.6: Oscilloscope window captures of the implemented neuron for different spiking patterns for varying values of parameter d at a constant input current of I = 28mA.

As is evident from Table 2.2, the HOMIN model has substantially lower digital hardware resource requirements than the original Izhikevich model and other previously proposed Izhikevich Neuron approximations. Additionally, since this implementation simply serves to prove the advantages of the HOMIN model, the implementation does not include substantial hardware optimization.

## 2.3 Conclusion

In conclusion, modifications to the Izhikevich spiking neuron model [7] were made to create the proposed HOMIN spiking neuron model which results in a simpler digital hardware implementation while simultaneously reducing the number of required interconnections for use in an artificial neural network since the spiking behaviour of an implemented HOMIN neuron can be modified with a single parameter in contrast to the four parameter changes required by the original Izhikevich neuron. The hardware savings and connection savings allow for a larger and far more parallel neural network implementation on an FPGA as few hardware resources are used per neuron and for parameter connections. A clear extension from the proposed neuron model and implementation is the realization of a network of digital spiking neurons.

# Chapter 3

# A Resource-Efficient and High-Accuracy CORDIC-Based Digital Implementation of the Hodgkin-Huxley Neuron

## 3.1 Introduction

Real biological neural systems are among the most intricate systems that naturally exist in humans. Biological neurons exhibit many diverse spiking behaviours, through which information is transmitted in a neural system. While traditional Artificial Neural Networks (ANNs) are bio-inspired systems that use a time-static methodology for computation, Spiking Neural Networks (SNNs) more closely emulate real biological systems through dynamic time behaviour. Given their closer replication of biological behaviour, SNNs, like traditional ANNs, have shown success in image classification and speech recognition [42] and also have further potential applications such as neuronal function and disease modelling [41]. Thus, they are a topic of great research interest.

Neuromorphic engineering is a highly active field of research which includes the implementation of spiking neurons in electrical hardware with the goal of amalgamation into a spiking neural network. Since basic unit of a biological neural system is the neuron, an accurate description of the behaviour of a neuron is of great importance. Mathematical characterizations of these spiking behaviours have been proposed in many models [4, 5, 7–10], with each proposed characterization presenting advantages and drawbacks. Some models, such as the Hodgkin-Huxley Neuron Model [4] and the Morris-Lecar Model [5], are highly detailed and have true biological meaning [6] where all parameters used in the differential equation model directly represent a physical parameter observed in the neuron. Other neuron models offer a higher-level behaviour description and require fewer differential equations and model parameters, but still capture the essence of neuronal behaviour such as the Izhikevich Model, [7], the Adaptive-Exponential Integrate and Fire (AdEx) Model [8], and the Wilson Model [9], even though their parameters do not directly represent biological qualities. An even simpler description neuronal behaviour exists in the Leaky Integrate-and-Fire Neuron Model [10].

Given its relatively complex nature in comparison to the Leaky Integrate-and-Fire or Izhikevich Neuron Model due to its large array of differential equations and accompanying parameters, the Hodgkin-Huxley Neuron Model has seen limited proposed hardware implementations [20, 43–50]. However, the biological significance of the model due to its foundation on physical biological parameters makes it an excellent candidate for use in the creation of a neuromorphic system of high parallelism to a real biological neural system. Its faithful accuracy and correspondence to biological reality gives the model substantial potential for specific effectiveness in the previously mentioned application of modelling real neural systems. [20,41] Specifically, these applications include modeling real neurological systems with the intent of expanded understanding of the progression of neurological disease [16]. Although software simulations can be done, custom hardware-based systems are generally much faster that software [15], meaning that many different conditions and outcomes can be assessed quickly to expedite the collection of information. Conductance-based models, such as the Hodgkin-Huxley model, are well-suited to neural system modeling [51].

Field-Programmable Gate Array (FPGA) is an excellent medium for spiking neuron implementation due to its flexibility in comparison to Application-Specific Integrated Circuit (ASIC) digital designs. Furthermore, although analog designs typically present lower power and area consumption, they are typically less robust and more susceptible to noise and error than FPGA designs [22]. Additionally, FPGA implementations of neural networks present a major speed advantage compared to software implementations [15] at the expense of flexibility. For these reasons, the FPGA platform presents an excellent compromise between speed, performance, and flexibility [52–55].

Among the limited existing FPGA hardware proposals are several different methods. Firstly, relatively direct implementations of the Hodgkin-Huxley Neuron have been proposed [20]. The clear drawback to this approach is the exceedingly large hardware resource requirements, making large networks impractical. Other methods have proposed partial use of the COordinate Rotation DIgital Computer (CORDIC) Algorithm with Look-Up Tables (LUTs) to implement exponential terms [47]. However, aside from this improvement, the hardware requirements are still very high due to the remaining multiplication and division terms.

Moreover, some methods propose modifications to the original equations of the Hodgkin-Huxley Neuron's alpha and beta parameters [43, 44]. Although many of these proposals prove effective in reducing hardware resource requirements, error and input current limitations are often introduced compared to the original model. In [43], an accurate implementation of the Hodgkin-Huxley neuron is proposed with fixed parameters. However, the hardware resource utilization has been improved in a newer implementation [44] and the fixed parameters limit the

FIGURE 3.1: nRMSE of the CORDIC algorithm applied to multiplication, division, and the exponential function for 10000 trials at each CORDIC iteration number from 1 to 20. The input operands were normally distributed random numbers in the typical operand range for each operation as found in the Hodgkin-Huxley neuron model.

flexibility of the implementation in biomedical applications. Furthermore, in [44] an implementation with relatively low hardware requirements is proposed, again with fixed parameters but with an error accuracy. The elevated error and fixed parameters again may limit its efficacy in biomedical applications. It is important to emphasize again that all of the parameters of the Hodgkin-Huxley neuron have physiological significance and may change depending on the type of neuron cell of interest [56, 57].

An FPGA digital hardware implementation of the Hodgkin-Huxley Neuron Model is proposed using the COordinate Rotation DIgital Computer (CORDIC) Algorithm for all non-linear terms to substantially reduce the hardware resource requirements of the system while maintaining a high level of accuracy to the neuron model. Since the CORDIC Algorithm uses iterative shift and add operations, the hardware resources required to implement these terms are greatly reduced through use of this computation method. The proposed implementation shows substantial hardware resource savings compared to previously implementations.

Background information on the Hodgkin-Huxley Neuron Model and CORDIC Algorithm is presented, the iteration number determination is explained, an FPGA

FIGURE 3.2: Software simulations of the membrane potential as a function of time of (A) and (B) the original Hodgkin-Huxley Neuron and (C), (E), (G) and (D), (F), (H) the CORDIC Hodgkin-Huxley Neuron for two different parameter and current operational points. (A), (C), (E), (G) show operation for Parameter Set 1 for a current of  $I = 500\mu A$ , while (B), (D), (F), (H) show operation for Parameter Set 2 for a current of  $I = 20\mu A$ . Between 16 and 20 iterations using the CORDIC algorithm, qualitative changes in the neuron's behaviour are not observed. Thus, an upper bound on the necessary iterations of the CORDIC algorithm exists.

hardware implementation is detailed, and the achieved results are compared with the theoretical expectations from the model behaviour and with previously proposed designs.

## 3.2 Background

#### 3.2.1 The Hodgkin-Huxley Neuron Model

The Hodgkin-Huxley Neuron Model was proposed by Hodgkin and Huxley [4]. As the first conductance-based mathematical model of biological neuronal behaviour, it is one of the most significant neuron models in computational neuroscience because it has served as the basis for many conductance-based neuronal model descriptions that have followed [6]. The model consists of four differential equations, given as:

$$I = C_m \frac{dV}{dt} + g_K n^4 (V - V_K) + g_{Na} m^3 h (V - V_{Na}) + g_l (V - V_l)$$

(3.1)

$$\frac{dn}{dt} = \alpha_n (1-n) - \beta_n n \tag{3.2}$$

$$\frac{dm}{dt} = \alpha_m (1-m) - \beta_m m \tag{3.3}$$

$$\frac{dh}{dt} = \alpha_h (1-h) - \beta_h h \tag{3.4}$$

where:

$$\alpha_n = \frac{0.01(V+50)}{1-e^{-(0.1V+5)}} \tag{3.5}$$

$$\alpha_m = \frac{0.1(V+35)}{1-e^{-(0.1V+3.5)}} \tag{3.6}$$

$$\alpha_h = 0.07 e^{\frac{-(V+60)}{20}} \tag{3.7}$$

$$\beta_n = 0.125e^{\frac{-(V+60)}{80}} \tag{3.8}$$

$$\beta_m = 4e^{\frac{-(V+60)}{18}} \tag{3.9}$$

$$\beta_h = \frac{1}{e^{-(0.1V+3)} + 1} \tag{3.10}$$

where V is the membrane potential, I is the input synaptic current, and the remaining parameters are fixed for a given operation point and defined as:

- $C_m$ : membrane capacitance per area

- $V_{Na}$ : sodium equilibrium potential

- $V_K$ : potassium equilibrium potential

- $V_l$  : potential at which leakage current due to other ions is zero

- $g_{Na}$  : conductance to sodium

- $g_K$  : conductance to potassium

- $g_l$  : leakage conductance due to other ions

It is important to note that the above expressions for  $\alpha$  and  $\beta$  in Equations 3.5 - 3.10 in this work are the same in mathematical structure as the original neuron proposed by Hodgkin Huxley in [4], but use different constants. The constants used come from adjustments proposed to the Hodgkin-Huxley neuron to explain type 3 excitability in squid giant axons [56]. Experimental data was used to derive the original constants, and the constants depend on the type of neuron being studied which makes this minor difference irrelevant [57], and methods for deriving these constants for a desired behaviour have been proposed [58].

Adjustments in the parameters will affect the spiking behaviour of the neuron and result in the generation of different neuronal behaviours. The Hodgkin-Huxley model gives a detailed description of a real neuron's behaviour since all parameters have biological meaning through their direct representation of a physical quantity in a neuron [6]. Given the large number of non-linear terms in the model, the error associated with approximations of these terms for hardware implementation can impair the neuron's behaviour quickly. Thus, maintaining a relatively high level of accuracy when computing these terms is highly important for preserving the biologically significant behaviour of the model. A high-accuracy computation method in digital hardware, such as the method described subsequently would be an excellent candidate for use in implementation.

# 3.2.2 COordinate Rotation DIgital Computer (CORDIC) Algorithm

The COordinate Rotation DIgital Computer (CORDIC) Algorithm [29] is a rotationbased, iterative algorithm used to simplify digital hardware requirements when implementing more complicated functions such as the cosine function or exponential function. The algorithm involves iterative rotation of the input by angles that result from the inverse tangent of a power of 2, meaning the rotation can be performed using a simple shift operation, where the shift direction is determine through comparison of the target rotation angle and the current cumulative rotation. Since the algorithm employs only shift and add operations, the CORDIC Algorithm can be used to implement many complex functions with relatively simple hardware, while the accuracy of the implementation is determined by the number of iterations performed. Thus, a compromise between computation speed and accuracy must be made.

A CORDIC implementation of the exponential function is given by Algorithm 1. Euler's number is e, x is the exponent of e,  $x_{frac}$  and  $x_{int}$  are the fractional and integer parts of x respectively, z is the result, i is the number of iterations, and kis the CORDIC iteration number. a(i) is the *ith* value of  $e^{2^{-i}}$  in radians.

|           | $\alpha$ 1 D $/ 2$           |           |                           |

|-----------|------------------------------|-----------|---------------------------|

|           | $C_m = 1\mu F/cm^2$          |           | $C_m = 1\mu F/cm^2$       |

|           | $V_{Na} = 55.12 \mathrm{mV}$ |           | $V_{Na} = 50 \mathrm{mV}$ |

|           | $V_K = -72.14 \text{mV}$     |           | $V_K = -100 \text{mV}$    |

| Parameter | $V_l = -49.42 \text{mV}$     | Parameter | $V_l = -85 \text{mV}$     |

| Set 1     | $g_{Na} = 120 \mathrm{mS}$   | Set 2     | $g_{Na} = 50 \mathrm{mS}$ |

|           | $g_K = 36 \mathrm{mS}$       |           | $g_K = 5 \mathrm{mS}$     |

|           | $g_l = 0.3 \mathrm{mS}$      |           | $g_l = 0.1 \mathrm{mS}$   |

TABLE 3.1: Hodgkin-Huxley neuron parameter sets used for testing

Algorithm 1: The CORDIC exponential algorithm.

1 for  $i \leftarrow -k$  to -1 do // iterate n=k times if  $x_{frac}(i) > 2^{-i}$  then  $\mathbf{2}$  $x_{frac}(i+1) = x_{frac}(i) - 2^{-i}$ 3  $z(i+1) = z(i)a^i$ 4 end 5 6 end while  $x_{int}(i) \neq 0$  do 7 if  $x_{int}(i) > 0$  then 8  $z(i+1) = z(i) * e x_{int}(i) = x_{int}(i) - 1$ 9 else  $\mathbf{10}$  $z(i+1) = z(i)/e \ x_{int}(i) = x_{int}(i) + 1$ 11 end 1213 end

Multiplication is implemented using the CORDIC Algorithm according to Algorithm 2. x is the multiplicand, y is the multiplier, z is the product, i is the number of iterations, and k is the CORDIC iteration number.

Subsequently, division is performed using Algorithm 3. x is the dividend, y is the divisor, z is the quotient, i is the number of iterations, and k is the CORDIC iteration number.

Figure 3.1 shows the normalized Root-Mean Square Error (nRMSE) of the CORDIC algorithm when applied to multiplication, division, and the exponential function in the typical operational range of the Hodgkin-Huxley Neuron. It is apparent that as the number of iterations increases, the error converges to zero, making the

A Resource-Efficient and High-Accuracy CORDIC-Based Digital Implementation of the Hodgkin-Huxley Neuron 31

Algorithm 2: The CORDIC multiplication algorithm.

```

1 for i \leftarrow -l to k do

// iterate n=2k+1 times

if x(i) \ge 0 then

\mathbf{2}

x(i+1) = x(i) - 2^{-i}

3

z(i+1) = z(i) + 2^{-i}y

\mathbf{4}

else

5

x(i+1) = x(i) + 2^{-i}

6

z(i+1) = z(i) - 2^{-i}y

7

end

8

9 end

```

Algorithm 3: The CORDIC division algorithm.

```

1 for i \leftarrow -k to k do

// iterate n=2k+1 times

if x(i) > 0 then

\mathbf{2}

x(i+1) = x(i) - 2^{-i}y

3

z(i+1) = z(i) + 2^{-i}

\mathbf{4}

else

\mathbf{5}

x(i+1) = x(i) + 2^{-i}y

6

z(i+1) = z(i) - 2^{-i}

7

end

8

9 end

```

CORDIC algorithm an excellent high-accuracy method for implementing these operations in digital hardware.