# **Universidade do Minho**

Escola de Engenharia

António Maria Martinho Mendes Godinho

Power Management Circuit: Design and Comparison of Efficient Techniques for Ultra-Low-Power Analog Switch and Rectifier Circuits

## **Universidade do Minho**

Escola de Engenharia

António Maria Martinho Mendes Godinho

Power Management Circuit: Design and Comparison of Efficient Techniques for Ultra-Low-Power Analog Switch and Rectifier Circuits

Dissertação de Mestrado

Mestrado Integrado em Engenharia Eletrónica Industrial e Computadores

Instrumentação e Microssistemas Eletrónicos

Trabalho efetuado sob a orientação do

Professor Luís Gonçalves

Ph.D. Zhaochu Yang

## Despacho RT - 31 /2019 - Anexo 3

# DIREITOS DE AUTOR E CONDIÇÕES DE UTILIZAÇÃO DO TRABALHO POR TERCEIROS

Este é um trabalho académico que pode ser utilizado por terceiros desde que respeitadas as regras e boas práticas internacionalmente aceites, no que concerne aos direitos de autor e direitos conexos.

Assim, o presente trabalho pode ser utilizado nos termos previstos na licença abaixo indicada.

Caso o utilizador necessite de permissão para poder fazer um uso do trabalho em condições não previstas no licenciamento indicado, deverá contactar o autor, através do RepositóriUM da Universidade do Minho.

Licença concedida aos utilizadores deste trabalho

Atribuição CC BY

https://creativecommons.org/licenses/by/4.0/

Acknowledgments

Firstly, I am grateful to Sensovann AS for hosting me and offering all the working conditions during my

internship. Special appreciation goes to Professor Tao Dong for all his support, supervision, and always

believing in my work. His guidance was essential for the progress and conclusion of my master's thesis.

Also, I want to thank my co-supervisor at Sensovann AS, Ph.D. Zhaochu Yang, whose cooperation and

project discussion were essential for the progress of this work.

Secondly, my appreciation goes to my supervisor at the University of Minho, Professor Luís Gonçalves,

for his support to the project development, his lectures during my academic period, and his relationship

with his students.

Likewise, I want to thank Ph.D. Nuno Pires for our useful discussions and valuable advice. Also,

acknowledgment goes to Ph.D. student Gonçalo Almeida, whose project discussion was very important

to finish my master's thesis.

I also want to acknowledge the cooperation with the Chongqing Key Laboratory of Micro-Nano Systems

and Smart Transduction.

Finally, I want to thank my course colleagues and friends at the University of Minho. Together, we

overcame all the difficulties throughout our academic years.

A special thanks to my parents and brother, who were always by my side, encouraging me to follow my

dreams and surpass myself every day. Further thanks to all my family.

Thank you! Obrigado!

İν

# Statement of Integrity

I hereby declare having conducted this academic work with integrity. I confirm that I have not used plagiarism or any form of undue use of information or falsification of results along the process leading to its elaboration.

I further declare that I have fully acknowledged the Code of Ethical Conduct of the University of Minho.

#### Resumo

A presente dissertação de mestrado apresenta um estudo na área de *CMOS* em circuitos analógicos/digitais para extração e conversão de potência adequado para aplicações em *energy* harvesting.

As principais contribuições científicas deste trabalho são: o desenvolvimento de circuitos de baixo consumo energético, tais como um interruptor analógico e um retificador que podem extrair e converter eficientemente a potência de saída do *energy harvester*. Com os dois circuitos apresentados na presente dissertação, é possível alimentar um nó de uma rede de sensores sem fios. Estes circuitos foram projetados utilizando a tecnologia *CMOS* de 130 nm e as respetivas simulações foram realizadas utilizando o software *Cadence Virtuoso Analog Environment*.

Neste trabalho projetou-se novo interruptor analógico para aplicações em *energy harvesting* com especial atenção para a obtenção de um baixo consumo energético. A configuração apresentada consegue atingir uma baixa resistência, quando em condução (ON), e evitar correntes reversas indesejadas provenientes da carga. Os resultados das simulações revelam que o circuito: consome uma potência de 200.8 nW; atinge uma baixa resistência, quando em condução, de 216 Ω; gera uma baixa corrente de fuga de 44 pA. Assim sendo, é possível verificar que este circuito consegue operar com um baixo consumo, baixa tensão e com uma baixa frequência. Para além disso, o mesmo interruptor analógico consegue realizar a técnica de *up-conversion* dentro do circuito de controlo de potência, o que indica a possibilidade de o mesmo contribuir para uma aplicação real com *energy harvesters* vibracionais.

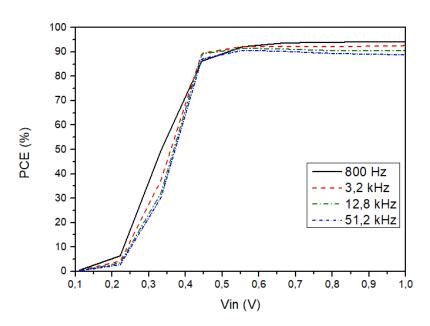

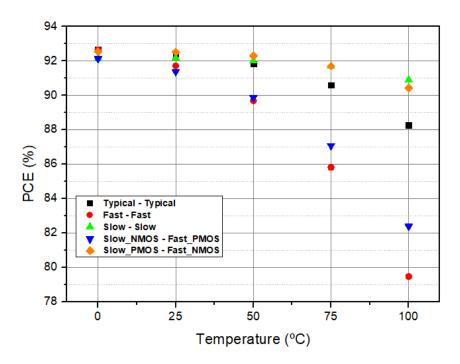

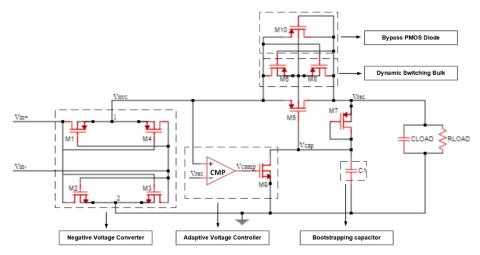

O retificador em CMOS proposto é constituído por dois estágios: um passivo com um conversor de tensão negativa; e um outro estágio com um díodo ativo controlado por um circuito de cancelamento de *threshold*. O primeiro estágio é responsável por retificar completamente o sinal de entrada com uma queda de tensão de 1 mV, enquanto que o último tem a função de reduzir a corrente reversa indesejada, o que consequentemente consegue aumentar a potência transferida para a carga. Deste modo, o circuito consegue atingir uma eficiência em tensão e potência de 99 % e 90%, respetivamente, para um sinal de entrada com 0.45 V de amplitude e para cargas resistivas de valor baixo. Ainda assim, este circuito consegue funcionar a uma banda de frequências desde os 800 Hz até 51.2 kHz, o que se revela ser promissor para a aplicação prática deste projeto.

Palavras-Chave: Energy Harvesting, circuito de controlo de potência, Analog Switch, CMOS Rectifier, circuitos de baixo consumo energético.

#### Abstract

The master dissertation presents a study in the area of mixed analog/digital CMOS power extraction and conversion circuits for Power Management Circuit (PMC) suitable for energy harvesting applications.

The main contributions of the work are the development of low power circuits, such as an Analog Switch and a Rectifier, that can efficiently extract and convert the output power of the vibrational energy harvester into suitable electric energy for powering a Wireless Sensor Network (WSN) node. The circuit components were fully designed in the standard 130 nm CMOS process, and the respective simulation experiments were carried out using the Cadence Virtuoso Analog Environment.

A new Analog Switch was designed for energy harvesting applications with special consideration for achieving low power consumption. The proposed structure can achieve a reduced ON-resistance and avoid the reverse leakage current from the load. Simulation results reveal a power consumption of about 200.8 nW, a low ON-resistance of 244.6  $\Omega$ , and a low leakage current of around 44 pA, which indicates that the analog switch has features of low power consumption, low voltage, and low-frequency operation. Furthermore, this switching circuit is suitable for performing the up-conversion technique in the PMC, which may contribute to the real application of vibrational energy harvesters.

The proposed CMOS Rectifier consists of two stages, one passive stage with a negative voltage converter, and another stage with an active diode controlled by a threshold cancellation circuit. The former stage conducts the signal full-wave rectification with a voltage drop of 1 mV while the latter reduces the reverse leakage current, consequently enhancing the output power delivered to the ohmic load. As a result, the rectifier can achieve a voltage and a power conversion efficiency of over 99 % and 90 %, respectively, for an input voltage of 0.45 V and low ohmic loads. This circuit works for an operating frequency range from 800 Hz to 51.2 kHz, which is promising for practical applications.

**Keywords:** Energy Harvesting, Power Management Circuit, Analog Switch, CMOS Rectifier, low-power consumption circuits.

# Contents

| Re | esumo     |                                             | vi   |

|----|-----------|---------------------------------------------|------|

| Αl | ostract   |                                             | viii |

| C  | ontents . |                                             | ix   |

| Αd | cronyms   | S                                           | XV   |

| 1  | Intro     | oduction                                    | 1    |

| 2  | State     | e of the Art                                | 5    |

|    | 2.1       | Analog Switch                               | 5    |

|    | 2.1.1     | 1 Switch-Induced Errors                     | 7    |

|    | 2.1.2     | 2 Previous Works                            | 9    |

|    | 2.2       | Full-wave Rectifiers                        | 13   |

|    | 2.2.1     | 1 Passive Rectifiers                        | 14   |

|    | 2.2.2     | 2 Active Rectifiers                         | 18   |

|    | 2.2.3     | 3 Threshold Cancellation Topologies         | 20   |

|    | 2.3       | Leakage current in CMOS                     | 23   |

|    | 2.3.1     | 1 Leakage Current Reduction Techniques      | 24   |

| 3  | Deve      | elopment and Results                        | 28   |

|    | 3.1       | Analog Switch                               | 28   |

|    | 3.1.1     | 1 The Switching-Bulk Technique              | 30   |

|    | 3.1.2     | 2 Back-to-Back NMOS                         | 32   |

|    | 3.1.3     | 3 Transistor Stacking on the Inverter stage | 33   |

|    | 3.1.4     | 4 Results                                   | 33   |

|    | 3.2       | CMOS Rectifier                              | 38   |

|    | 3.2.1     | 1 Negative Voltage Converter                | 39   |

|      | 3.2.2        | Active Diode                   | . 40 |

|------|--------------|--------------------------------|------|

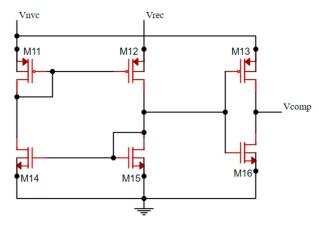

|      | 3.2.3        | Threshold Cancellation Circuit | . 41 |

|      | 3.2.4        | Results                        | . 44 |

| 4    | Conclusio    | on                             | . 51 |

| Ref  | erences      |                                | . 52 |

| Atta | achments     |                                | . 59 |

| F    | oublication: | 5                              | . 59 |

# List of Figures

| Figure 1: Schematic overview of the proposed Power Management Circuit for a piezoelectric energ                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| harvester                                                                                                                                                                   |

| Figure 2: Simplified block diagram of the PMC.                                                                                                                              |

| Figure 3: Frequency spectrum example of the up-conversion output signal proposed by P. Li et al. ( 2014                                                                     |

|                                                                                                                                                                             |

| Figure 4:Schematic of the TG                                                                                                                                                |

| Figure 5: TG's ON-resistance and Power Consumption behaviour with W variation.                                                                                              |

| Figure 6: (a) Structure of a simple analog switch and the charge injection when it is at OFF state. (b<br>Charge injection effect (Naghavi, Sharifi, and Abrishamifar 2018) |

| Figure 7: Clock feedthrough in a simple analog switch                                                                                                                       |

| Figure 8: Bootstrap analog switch (a) high level representation (b) traditional bootstrap switch represented in transistor level by Chen (2014).                            |

| Figure 9: Structure of the circuit proposed by Naghav et. al (2018)                                                                                                         |

| Figure 10: (a) A full-wave bridge rectifier (b,c) Conduction path when the input polarity is as shown, (d                                                                   |

| Output voltage Vo of the full-wave rectifier(M. Plonus 2020)14                                                                                                              |

| Figure 11: CMOS Full-wave bridge rectifiers: (a) conventional topology, (b) gate cross-coupled topology and (c) fully cross-coupled (Yeo et al. 2015).                      |

| Figure 12: Voltage doubler                                                                                                                                                  |

| Figure 13: Schematic of an active CMOS rectifier                                                                                                                            |

| Figure 14: Schematic of the active stage (Niu, Huang, and Jiang 2012)19                                                                                                     |

| Figure 15: Schematic of the ultra-low voltage rectifier (Peters et al., 2011) (a) negative voltage converte with a body-bias block; (b) input-bulk comparator.              |

| Figure 16: (a) Full-wave bootstrap rectifier (Hashemi, Sawan, and Savaria 2012); (b) Active bootstrapping rectifier (Lee, Liao, and Lee 2019).                              |

| Figure 17: Leakage power consumption behaviour with technology downscaling (Hanchate and                                                                                    |

| Figure 18: Fabrication process parameters that influence the threshold voltage (a) channel doping          |

|------------------------------------------------------------------------------------------------------------|

| concertation (b) oxide thickness (c) channel length                                                        |

| Figure 19: Transistor Stacking, (a) Stacking effect in two-input NAND gate, (b) Subthreshold leakage       |

| current using different number of stacks in OFF state (Butzen and Ribas 2007)27                            |

| Figure 20: (a) Inverter stage with Transistor Stacking used to bias the analog switch; (b) Proposed analog |

| switch with the addressed techniques                                                                       |

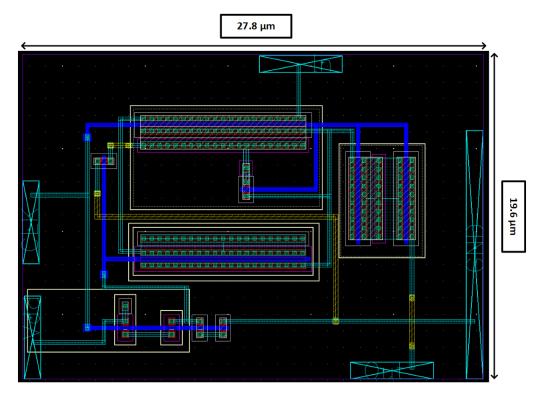

| Figure 21: Physical layout of the proposed analog switch                                                   |

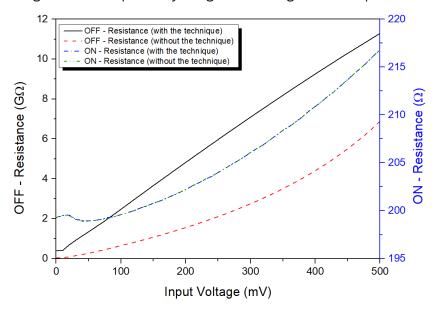

| Figure 22: ON-resistance and OFF-resistance behaviour with and without the switching bulk technique for    |

| different input voltage                                                                                    |

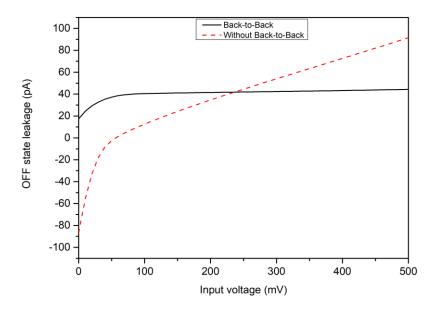

| Figure 23: OFF-state leakage current with and without the back-to-back NMOS technique                      |

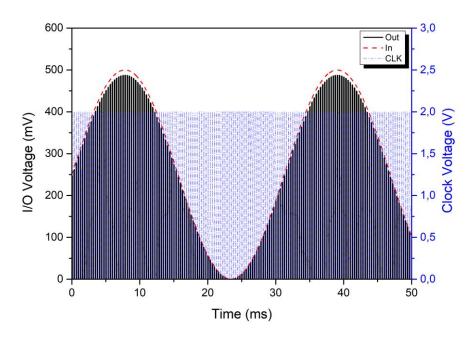

| Figure 24: Simulation of the proposed analog switch working principle, including the input voltage (In),   |

| clock signal (CLK), and the output voltage (Out)                                                           |

| Figure 26: Switching speed test: (a) Rise time of $Vout$ ; (b) $Vout$ and CLK behaviour; (c) Fall time of  |

| Vout35                                                                                                     |

| Figure 25: ON-resistance behaviour with input voltage variation for different temperatures 35              |

| Figure 27: ON-loss and OFF-isolation behaviour with input variation                                        |

| Figure 28: Schematic of the proposed active rectifier composed by an NVC and an Active diode controlled    |

| by a Threshold Cancellation Circuit                                                                        |

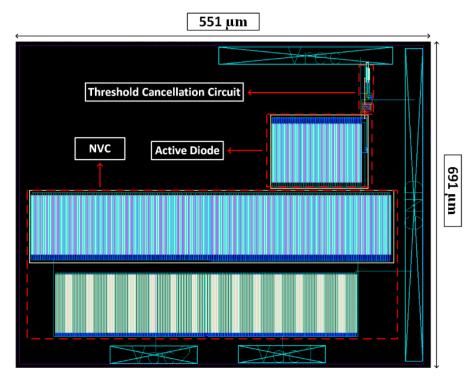

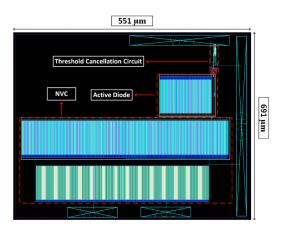

| Figure 29: Physical layout of the proposed CMOS rectifier                                                  |

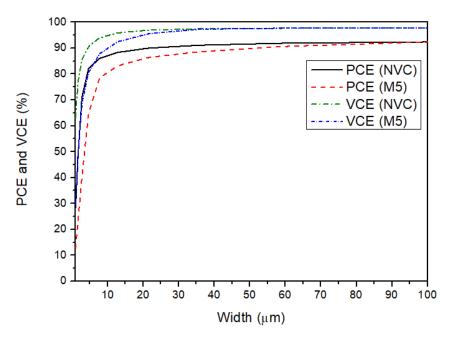

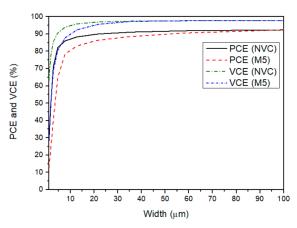

| Figure 30: PCE and VCE plot with the variation of the width of the NVC transistors and M5 (L = 130 nm).    |

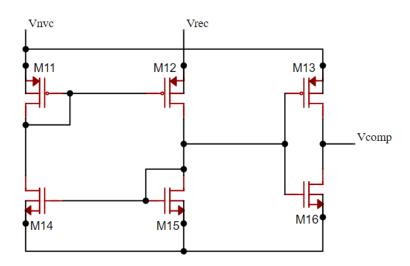

| Figure 31: Schematic of the two-input common gate comparator CMP                                           |

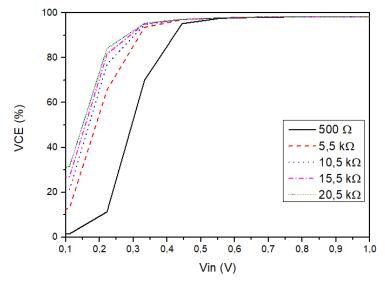

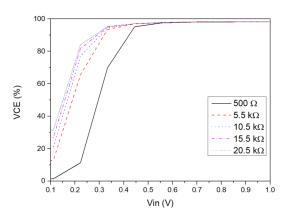

| Figure 33: VCE versus input voltage amplitude simulated for different ohmic loads                          |

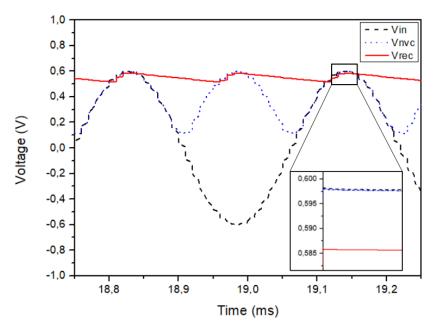

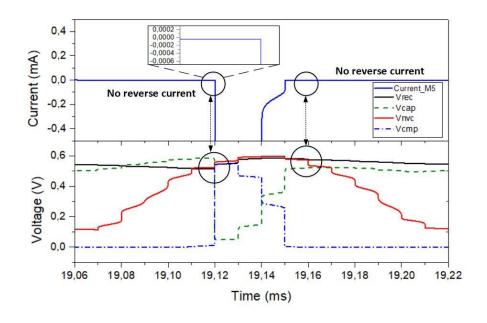

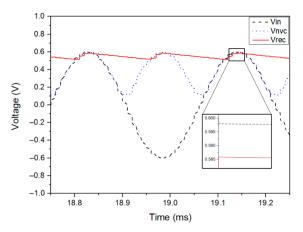

| Figure 32: Simulated waveforms of the rectifier for $RLOAD=5.5~k\Omega~$ and $CLOAD=2~\mu F45$             |

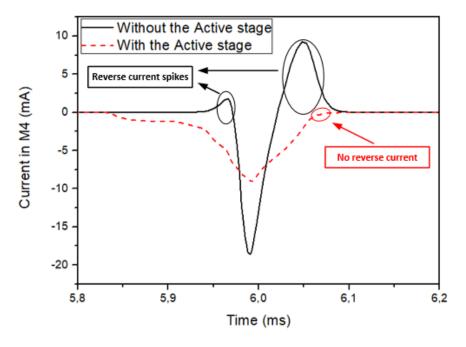

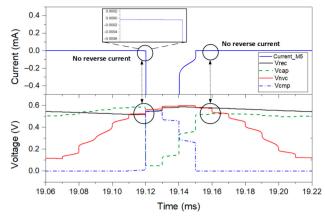

| Figure 34:. Reverse leakage current analysis in the NVC stage                                              |

| Figure 35: Simulated comparator behaviour in steady state for $RLOAD=5.5~k\Omega$ and $CLOAD=$             |

| 2 uF                                                                                                       |

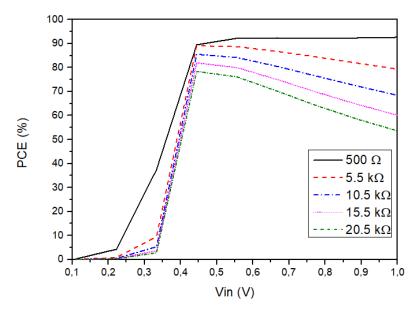

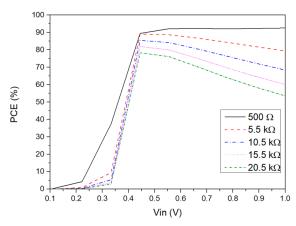

| Figure 36: PCE versus input voltage amplitude simulated for different <i>RLOAD</i> values     | 47  |

|-----------------------------------------------------------------------------------------------|-----|

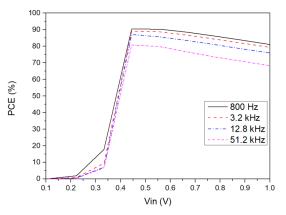

| Figure 37: PCE versus input voltage amplitude for different input frequencies.                | 48  |

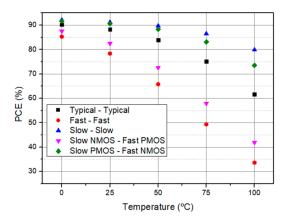

| Figure 38: PCE variation with temperature depending on the process corner variation for RLOAR | D = |

| 500 Ω                                                                                         | 49  |

# List of Tables

| Table 1: Energy Harvesting approaches adopted from Adu-Manu (2018).               | 2  |

|-----------------------------------------------------------------------------------|----|

| Table 2: Comparison of different full-wave rectifier topologies (Yeo et al. 2015) | 17 |

| Table 3: Transistor size of the Analog Switch.                                    | 30 |

| Table 4: Current and static power consumption comparison.                         | 33 |

| Table 5: Analog Switches performance summary and comparison.                      | 37 |

| Table 6: Circuit transistor sizes.                                                | 44 |

| Table 7: Research Comparison on CMOS Rectifiers.                                  | 50 |

| Acronyms |                                                    |

|----------|----------------------------------------------------|

| Α        |                                                    |

| AC       | Alternating Current.                               |

| AVC      | Adaptive Voltage Controller.                       |

| С        |                                                    |

| CMOS     | Complementary Metal-Oxide-Semiconductor.           |

| D        |                                                    |

| DC       | Direct Current.                                    |

| DIBL     | Drain-Induced Barrier Lowering                     |

| DSB      | Dynamic Switching Bulk.                            |

| 1        |                                                    |

| IC       | Integrated Circuit.                                |

| M        |                                                    |

| MEMS     | Microelectromechanical Systems.                    |

| MOSFET   | Metal-Oxide-Semiconductor Field-Effect Transistor. |

| N        |                                                    |

| NMOS     | N-type Metal-Oxide-Semiconductor                   |

NVC Negative Voltage Converter. Ρ PCE Power Conversion Efficiency. **PMC** Power Management Circuit P-type Metal-Oxide-Semiconductor **PMOS** R RF Radio Frequency. Т TG Transmission Gate. THD Total Harmonic Distortion. ٧ VCE Voltage Conversion Efficiency. VLSI Very Large-Scale Integration. W

Wireless Sensor Network.

WSN

#### 1 Introduction

During the past years, WSNs have been crucial in supporting continuous environmental monitoring, where sensor nodes are spatially distributed and must remain operational to collect and transfer data from the environment to a base station. As a result, these WSNs have been gaining popularity in many applications, such as environmental monitoring, animal tracking, earth disasters, and health monitoring of civil structures such as bridges and buildings (Fong 2016; Sharma et al. 2010).

WSNs often consist of many sensor nodes distributed in the environment and a gateway node that collects all the data for storage or transmit to a remote server (Fong 2016; Silva, Khan, and Han 2018). In these systems, the sensor nodes are battery-operated devices with the ability to sense the specific environmental parameter required by the application. Then, the device transfers the collected data to the local gateway in order to further process and store it (Adu-Manu et al. 2018). However, throughout this communication process, these nodes consume a high energy level, which reduces its lifetime if using a small battery as the primary supply unit (Chew, Ruan, and Zhu 2019). Furthermore, batteries have been revealed to be a bottleneck to electronic demands and environmental nightmares since some nodes are in hard-to-reach places, leading to high maintenance costs regarding battery replacement. Thus, using a more reliable energy source is vital to efficiently extend the WSN operation time (Ruan, Chew, and Zhu 2017).

Energy harvesting urges as a promise and reliable technology to power these low-power sensor networks (Chew, Ruan, and Zhu 2019). It can power up a self-sustainable WSN by scavenging the necessary power supply from environmentally friendly sources, making it an innovative technology that allows for clean and renewable energy production. It can also be compatible with the current trends and the ongoing depletion of natural resources. Several sources can be used to harvest energy, such as radiant, mechanical, and thermal. Table 1 illustrates the energy-harvesting sources and their corresponding power densities. It can be noticed that the highest power density comes from outside solar cells. However, sensor nodes might be deployed under shaded areas that do not receive much sunlight even during the day and receive no sunlight during the night. This issue affects the operational cycle of the sensor nodes. Furthermore, due to the existence of mechanical vibrations almost everywhere at any time, this type of energy source is an attractive candidate to power these systems (Toshiyoshi et al. 2019).

Table 1: Energy Harvesting approaches adopted from Adu-Manu (2018).

| Energy Sources | Types               | Energy-Harvesting<br>Method        | Power density      |

|----------------|---------------------|------------------------------------|--------------------|

|                | Solar               | Solar cells (indoors)              | <10μW/cm²          |

|                |                     | Solar cells (outdoors, sunny days) | 15mW/cm²           |

| Radiant        | RF                  | Electromagnetic<br>conversion      | 0.1μW/cm² (GSM)    |

|                |                     | Electromagnetic conversion         | 0.01μW/cm² (Wi-Fi) |

|                | Wind Flow and Hydro | Electromechanical conversion       | 16.2μW/cm³         |

| Mechanical     | Acoustic Noise      | Piezoelectric                      | 960nW/cm³          |

|                | Motion              | Piezoelectric                      | 330μW/cm³          |

| Thermal        | Body heat           | Thermoelectric                     | 40μW/cm²           |

Since it is intended to integrate all these systems (energy harvester + electronic system) in a single chip, the solution is to incorporate MEMS and CMOS (Shu *et al.*, 2006). Therefore, due to their MEMSs compatibility, mechanical vibration energy is commonly explored since it is available in small-scale systems (Guyomar *et al.*,2011). Moreover, due to the high energy density and integration potential, piezoelectric energy harvesters are the most viable approach for designing self-powered small-scale devices (Shu and Lien 2006; N. Chen et al. 2017; Adu-Manu et al. 2018). Nevertheless, in real-world applications, ambient vibrations are unpredictable, time-varying, and low amplitude, which can be concluded that the scavenged energy cannot be directly applied to WSN (Dong et al. 2019; Guyomar et

al. 2007). Thus, some concerns must be taken to the energy harvester's output signal's properties when powering electronic systems or charging batteries, such as low-power signals, random fluctuations, and AC output signals.

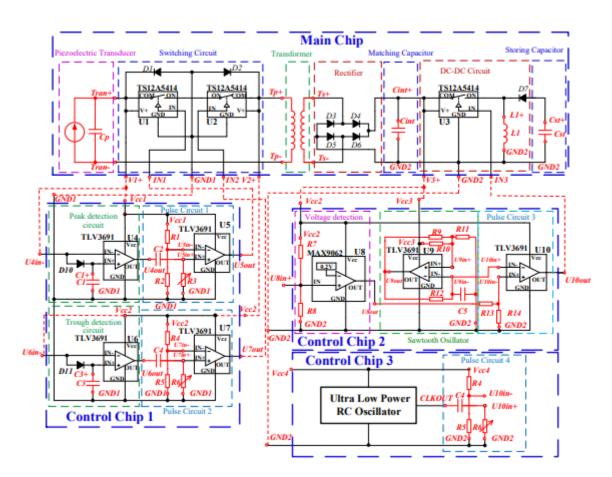

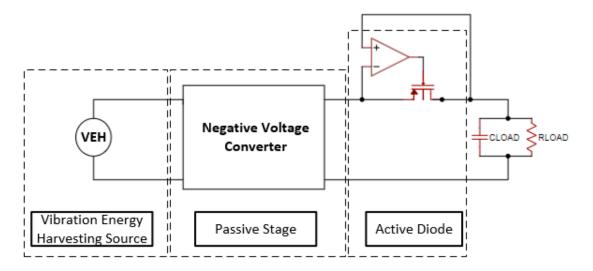

Considering the characteristics mentioned above that restrict the available power of the energy harvesting system, a PMC, as shown in Figure 1, was proposed to overcome these limitations (P. Li et al. 2014; 2019). This PMC needs to extract efficiently, convert, store, regulate and manage the scavenged energy from the harvester to maximize the amount of energy transferred under various ambient conditions (Chew, Ruan, and Zhu 2019). The overall aim of this circuit is to extend the lifetime of the sensor networks while having a low power consumption.

Figure 1: Schematic overview of the proposed Power Management Circuit for a piezoelectric energy harvester.

The main goal of this research work, proposed by Sensovann AS, is to design an Analog Switch and a Rectifier to be placed in the main chip of the PMC shown in Figure 1. To surpass all the harvesting limitations, designing these two circuits in CMOS technology is highly desirable to decrease the device's form factor, easily integrate with the energy harvester, achieve low power consumption, and mitigate the

unwanted leakage current (Colomer-Farrarons et al. 2008). Since the low frequency of the environmental sources does not match with the resonant frequency of the deployed energy harvester, the Analog Switch is designed to fulfil this gap by performing the up-conversion technique (P. Li et al., 2014). This method allows the energy harvester to reach the resonant frequency, ensuring that the maximum output power is transferred to the PMC. With the Analog Switch, it can be produced a higher frequency signal and a wide bandwidth to generate a higher output power under a weak vibration environment. In addition, due to the AC signal properties of the vibrational energy harvester, the Rectifier is designed to perform the AC/DC conversion in order to charge the supply unit properly. For the desired application, the key features of this work are high VCE and PCE.

#### 2 State of the Art

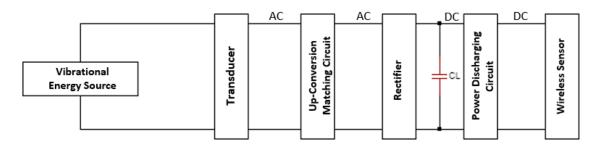

The electrical characteristics of the environmental sources are not ideal for being transferred directly to electronic devices. Its signal variability leads to innovative approaches to performing a dynamic electrical matching between the energy harvesting system and the natural sources (Ruan, Chew, and Zhu 2017). Nevertheless, the vibrational energy harvesters have a working operation that does not match the environmental sources (Chew, Ruan, and Zhu 2019). To ensure maximum transferred power to the energy harvesting system, a technique needs to be employed to increase the low frequency of the environmental sources to match the resonant frequency of the deployed energy harvester, see Figure 2. Thus, section 2.1 describes the up-conversion technique and state of the art on analog switches and their respective switch-induced errors.

Since the vibrational energy sources produce AC signals, scavenging such vibrational energy requires a full-wave rectifier as a key circuit inside the PMC, which allows the AC/DC conversion to power the WSNs properly. In this way, section 2.2 presents the state of the art on the previous CMOS full-wave rectifiers for energy harvesting applications. Furthermore, since the leakage current is one of the main problems concerning the technology downscaling, it is important to be aware of it while designing a CMOS circuit. Thus, section 2.3 presents the leakage current in CMOS and some techniques to reduce it.

#### 2.1 Analog Switch

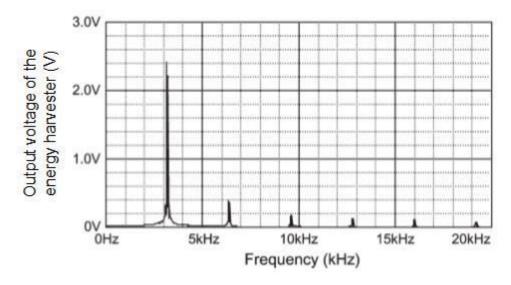

The up-conversion technique aims to fulfil this gap in energy harvesters by reaching, in this application, the resonant frequency of the piezoelectric device (P. Li et al., 2014). Since the environmental frequencies and amplitude of the signals are very low, the operational frequency of the PMC needs to be increased in order to reach the harvester's resonant frequency. This frequency achievement produces a higher output power on the transducer. The analog switch is a possible solution to attend to this demand because it can receive low-frequency signals from the harvester in the Hz range and convert them into higher

Figure 2: Simplified block diagram of the PMC.

frequencies in the kHz range (P. Li et al. 2014). Figure 3 shows an example of the frequency spectrum of the up-conversion output signal. According to P. Li *et al.* (2014), the resonant frequency of this vibrational energy harvester is at 3.2 kHz, as shown in the mentioned figure.

Figure 3: Frequency spectrum example of the up-conversion output signal proposed by P. Li et al. (2014)

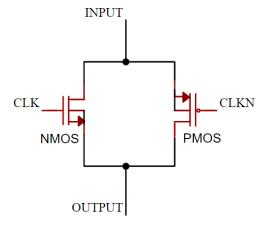

Analog switches are a common building block in analog signal processing. When turned ON, they can conduct both analog and digital signals from the input to the output, regardless of the signal traveling direction. The structure of the conventional analog switch, known as TG, is presented in Figure 4. This circuit consists of an NMOS in parallel with a PMOS. While turned ON, it allows the signal to pass in either direction. When the circuit is OFF, it isolates the output from the input. The switch mechanism is controlled by an inverter or NOT gate, in which the input and output bias the gate of NMOS and PMOS, respectively. The working principle is simple: when CLK is high, and CLKN is low, NMOS and PMOS will be ON, and the current can flow through them. When the opposite happens, the circuit blocks the current

Figure 4:Schematic of the TG.

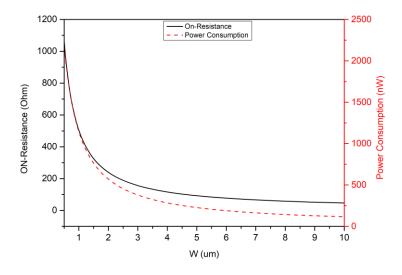

and isolates the output from the input (Baker 2019). Nevertheless, when the switch is ON, since the two transistors are in the deep-triode region, which means that  $V_{DS} < 0.2 \cdot (V_{GS} - V_{th})$  (Sharroush and Abdalla 2021), the output voltage is highly dependent on the ON-resistance. As it is shown in Equation 1, the ON-resistance is dependent on the electron mobility  $\mu$ , the unit capacitance of the oxide of the gate  $C_{ox}$ , the ratio of the width to length  $\left(\frac{w}{L}\right)$ , the voltage between the gate and the source  $V_{GS}$ , and the threshold voltage  $V_{th}$  (Chiranu et al. 2019). Therefore, it is important to manage these parameters in order to increase the efficiency of the analog switch. Figure 5 shows the power consumption of the TG with the W variation. As mentioned before, this analog circuit works as a frequency converter or frequency changer, which converts as AC signal of a specific frequency to an AC signal with another frequency. However, this structure presents some switch-induced errors that affect the performance of the Analog Switch. These errors will be presented in the next subsection.

$$R_{ON} = \frac{1}{\mu C_{ox} \frac{W}{L} (V_{GS} - V_{th})}$$

Figure 5: TG's ON-resistance and Power Consumption behaviour with W variation.

#### 2.1.1 Switch-Induced Errors

The main problem of this type of circuit is the switch-induced errors. Thus, this subsection illustrates the main errors that affect the performance of analog switches, such as charge injection and clock feedthrough.

#### 2.1.1.1 Charge Injection

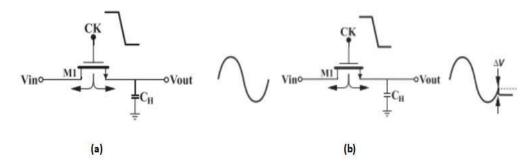

The structure of the sample and hold set by a simple NMOS switch is presented in Figure 6 (a). If a clock signal (CK) is applied to the gate of the NMOS transistor (M1), the gate-to-source voltage will be greater than the threshold voltage. Therefore, the transistor is switched on and starts operating in the triode region with approximately zero voltage across its drain and source terminals (George Wegmann, Yittoz, and Rahali 1987). During the time when the transistor is at ON state, it holds mobile charges in its channel. Equation 2 illustrates the amount of the charge  $(Q_{ch})$  that the transistor can hold during its operation, where  $W_1$  and  $L_1$  are the effective channel width and length of the transistor, respectively,  $C_{ox}$  is the gate capacitance per unit area, and  $V_{th}$  is the threshold voltage.

Figure 6: (a) Structure of a simple analog switch and the charge injection when it is at OFF state. (b) Charge injection effect (Naghavi, Sharifi, and Abrishamifar 2018).

$$Q_{ch} = W_1 L_1 C_{ox} (V_{DD} - V_{in} - V_{th})$$

2

Subsequently, once the switch is turned off, the mobile charges flow out through the source and drain terminals since there is no longer an electrical force to attract the channel charge.

The charge injected to the drain terminal presented in Figure 6 (b) is absorbed by the input voltage source since the impedance is lower than the output; therefore, any error value is produced on the holding capacitor. On the other hand, there are always a few charges injected into the source terminal, which affects the stored value on the holding capacitor and produces an error voltage (G Wegmann, Vittoz, and Rahali 1987). Equation 3 presents the resulting error voltage due to charge injection if it is assumed that the fraction  $\alpha$  of  $Q_{ch}$  is eventually stored in the holding capacitor ( $C_H$ ).

$$\Delta V_{CI} = \frac{\alpha Q_{ch}}{C_H} = \frac{\alpha W_1 L_1 C_{OX} (V_{DD} - V_{in} - V_{th})}{C_H}$$

As presented in the previous equation, the charge injection error voltage is signal-dependent and causes nonlinear distortions (Patel and Sadiwala 2021). For instance, Figure 6 (b) shows that the error for an NMOS switch appears as a negative spike at the output.

#### 2.1.1.2 Clock feedthrough

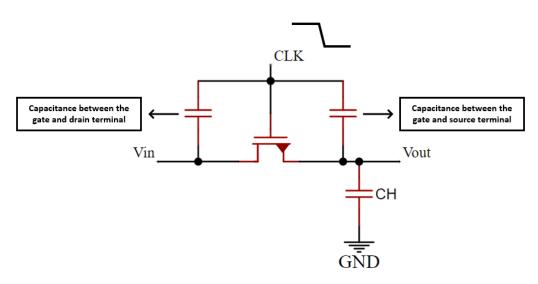

Besides charge injection, clock feedthrough is also an error to be aware of while the analog switch is being designed. A MOS switch couples the clock transitions to the holding capacitor ( $C_H$ ) through its gate-source or gate-drain overlap capacitance.

As shown in Figure 7, this phenomenon introduces an error in the output voltage as a result of this overlap capacitance. Assuming that this capacitance is constant, the error voltage due to the clock feedthrough can be stated by Equation 4, where  $C_{OV}$  is the overlap capacitance per unit width. The equation shows that the output error is independent of the input voltage. Therefore, it can be concluded that the offset value is directly proportional to the clock signal amplitude (Xu and Friedman 2002).

$$\Delta V_{CFT} = V_{CLK} \frac{W_1 C_{OV}}{W_1 C_{OV} + C_H}$$

Figure 7: Clock feedthrough in a simple analog switch.

#### 2.1.2 Previous Works

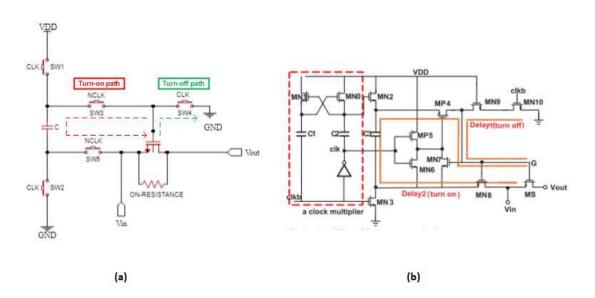

For low input voltage and low input frequency applications, analog switches must have a good performance, low power consumption, high linearity, and a low-frequency operation. Several works have been proposed to improve the performance characteristics of analog switches. Yang (2005) proposed a

low-voltage and low distortion switch due to a low THD. Then, the bootstrap technique was proposed to alleviate the problem with poor conduction and varying ON-resistance (H. Chen et al. 2014). This technique aims to control the switching operation with two non-overlapping clock signals (CLK and NCLK). The concept of this type of analog switch is illustrated in Figure 8 (a). During the standby operation (CLK is high, NCLK is low, SW1, SW2, and SW4 are on), the capacitor  $C_1$  is charged to  $V_{dd}$  and likely acts as a floating battery in order to bootstrap the gate voltage. Then, in the active mode (CLK is low, NCLK is high, SW3 and SW5 are on), the input signal charges the gate voltage of the switch equal to  $V_{dd} + V_{in}$ , resulting in an overdrive voltage nearly constant over the input signal voltage range.

Figure 8 (b) shows the traditional bootstrap switch implemented at the transistor level. During the OFF state, when clkb is high, MN2 is ON due to the action of the voltage doubler and charges the capacitor  $C_3$ , together with MN3. Then, transistor MP5 forces MP4 to turn off, and MN10 also forces MS, MN8 and MN7 to turn off. Nevertheless, parasitic capacitances of transistors MP4, MN7, MN9, and MN10 share the charge from  $C_3$ , which makes  $V_{gs}$  less than  $V_{dd}$ . During the active state, when clkb is low, MN6 will turn on, pulling down the gate of transistor MP4, supplying the MN8 and MS gates. Since MN8 is ON, it tracks the input signal  $V_{in}$  and then MS gate and its gate will have a voltage closer to  $V_{in} + V_{dd}$ . Thus, MS will have enough gate voltage to turn on during the active state.

To improve the characteristics mentioned above of the traditional bootstrap switch, Chen (2014) proposed another bootstrap switch with high speed, low nonlinear, and lower ON-resistance. Also, in order to reduce the number of transistors on-chip, Nazzal (2016) projected a bootstrap analog switch without a clock multiplier circuit and with low power consumption and low distortion caused by a low THD.

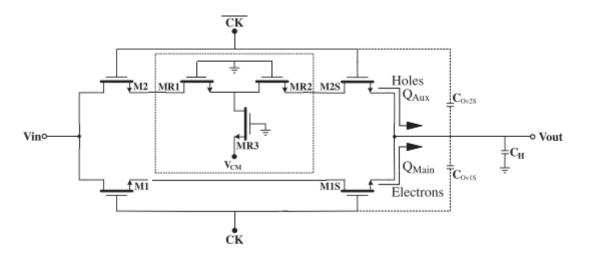

To eliminate the switch imperfections on the last subsection, Naghavi *et al.* (2018) proposed the structure of an analog switch presented in Figure 9. The elimination of the switch-induced errors in the proposed design is provided through an auxiliary path in parallel with the main signal path similar to the complementary switch. The novelty of this research work is using NMOS devices to avoid mismatches of different types of transistors. As shown in Figure 9, the main signal path of the proposed switch is formed by the transistors M1 and M1S. During the ON phase, when the clock signal CK is high, these transistors are in on-state. In this phase, a low-resistance path is provided, and the output follows the input voltage. The OFF-resistance is extremely high during the OFF phase due to a pseudo-resistor (MR1, MR2, and MR3), which is also a novelty of this work. Equation 5 proves that this circuit can eliminate the charge injection and clock feedthrough by connecting MS1 and MS2 in parallel.

$$+V_{CK}\frac{WC_{ov1S}}{WC_{ov1S} + C_H} - V_{CK}\frac{WC_{ov2S}}{WC_{ov2S} + C_H} = 0$$

Figure 8: Bootstrap analog switch (a) high level representation (b) traditional bootstrap switch represented in transistor level by Chen (2014).

Figure 9: Structure of the circuit proposed by Naghav et. al (2018).

However, besides the aforementioned characteristics, those circuits are mostly designed for analog-to-digital converters, with high operational frequencies, in MHz or GHz range, and low signal distortion are highly demanded. Therefore, those circuits cannot be used for this type of application due to different demands of working principles such as low input frequency, the ability to increase the operating frequency and receive nonlinear signals.

#### 2.2 Full-wave Rectifiers

Rectifiers essentially convert AC to unregulated DC in electrical power processing systems. The purpose of a rectifier in a micropower energy harvesting system is to efficiently process and transfer the small amount of ambient energy extracted by the vibrational energy harvesters in AC form to predominantly DC microelectronic load. This efficient conversion should involve a device that only allows one way of current flow. Otherwise, the capacitor load cannot be charged properly. Also, it must block or mitigate any reverse leakage current from the capacitor load to avoid undesired power losses.

The rectifier requires a low input voltage operation as practical micropower energy harvesters typically produce voltage levels around hundreds of millivolts (Toshiyoshi et al. 2019). Furthermore, the DC loads are generally in the form of a handheld, wearable, implantable, or wireless sensing devices that will require a battery-free small form factor to operate unobtrusively. Therefore, this energy autonomy requires ultra-low power rectifier operation and hence a high PCE to maximize the transfer to the load capacitor. These considerations resulted in various rectifier designs focusing on circuit topology and switch parameters for specific energy harvesting applications.

Conventional rectifiers are designed by using diodes and capacitors. The full-wave rectifier with a diode bridge is suitable for high voltage applications since the diode forward voltage drop from 0.7 V to 1 V (Q. Li, Wang, Niu, et al. 2014). However, this cannot be accepted in a low voltage energy harvesting system.

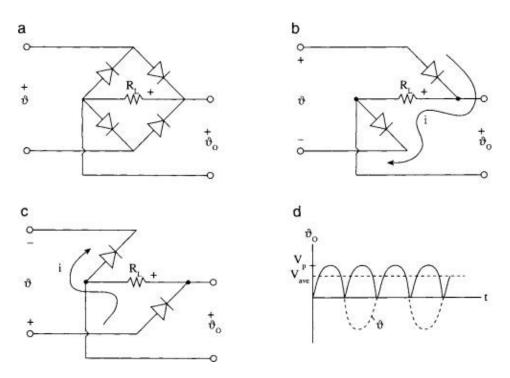

Firstly, it is important to see how the full-wave rectifier works. The full-wave rectifier presented in Figure 10 (a) must be employed when it is necessary to rectify both half-cycles of the input voltage. This circuit consists of four diodes and stands out for giving small output ripple voltage, commonly used in high voltage applications, where the diode forward voltage is between 0.7 V and 1 V. For low-voltage applications, these values result in large voltage losses, reducing the PCE significantly.

Current flows in the same direction through the load resistor for both polarities of the input voltage by using two forward-biased diodes in series with  $R_L$  at any time, as presented in Figures 10 (b) and (c). In Figure 10 (b), the input voltage has a polarity that makes the top input terminal positive; hence, only the two diodes shown are forward biased and are conducting. As the input voltage reverses, the bottom terminal becomes positive. Then, the remaining two diodes conduct, while the previous two are open-circuited, as shown in Figure 10 (c). The result is that current flows through  $R_L$  at all times, as shown in Figure 10 (d). However, these conventional full-wave rectifier structures present a forward voltage drop

around 0.7 V. Therefore, since the output power of the energy harvester is low, the high forward voltage drop required by the full-wave diode bridge and Schottky diodes rectifiers limits their use on these low power applications (Hashemi, Sawan, and Savaria 2012).

Figure 10: (a) A full-wave bridge rectifier (b,c) Conduction path when the input polarity is as shown, (d) Output voltage Vo of the full-wave rectifier (M. Plonus 2020).

Several CMOS rectifiers have been proposed throughout the last years to overcome the high forward voltage drop issue mentioned before. Diode-connected MOS transistors came up to replace diodes in standard CMOS processes, which is revealed to be a solution to make fully integrated low input voltage rectifiers (Gomez-Casseres et al. 2016). CMOS rectifiers can be classified into either passive or active configurations. On the one hand, passive rectifiers perform the full-wave rectification without controlling the reverse leakage current that comes from the load. On the other hand, active rectifiers use passive configurations to achieve the rectification while attaching them with an extra circuit to control the reverse leakage current depending on the input and output voltage conditions. Thus, the following sections present the state of the art of these two configurations.

#### 2.2.1 Passive Rectifiers

As it was previously mentioned, classical full-wave rectifier circuit topologies use diodes for switching. Since their forward voltage drops are high (typically 0.7 V), this topology cannot be applied for energy harvesting applications. Therefore, different standard CMOS passive rectifier techniques were proposed

to reduce the diode forward voltage drop, which the goal was to improve the power and voltage conversion efficiency. This subsection presents the description of different types of rectifier topologies and the comparison between them.

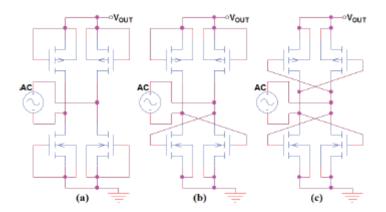

### 2.2.1.1 Gate Cross-Coupled Full-Wave Rectifier

Conventional full-wave bridge rectifiers introduced by Rakers  $et\,al.$  (2001) use four switches to create two conduction paths that an AC input produces a DC output,  $V_{out}$  (Figure 11). These are two diode drops in each conduction path thereby reducing the useful input voltage range. This can be achieved by reducing the threshold voltage drop of the diode-tied connection in the conduction path from the threshold voltage to the voltage drop across the diode during the forward conduction (Hashemi, Sawan, and Savaria 2012). Colomer-Farrarons  $et\,al.$  (2008) proved that PCE improves to around 70% compared to the conventional topology bridge PCE of about 50% with a piezoelectric micro-generator with 2.5V open-circuit voltage. This is caused by the cross-connection of gates, which generates the gate voltage swing to be larger than the diode-tied connections, leading to an increase in the overall forward current. However, this topology still lacks efficiency due to the threshold voltage drop across the diode-connected in each conduction path (Gomez-Casseres et al. 2016).

Figure 11: CMOS Full-wave bridge rectifiers: (a) conventional topology, (b) gate cross-coupled topology, and (c) fully cross-coupled (Yeo et al. 2015).

## 2.2.1.2 Fully Cross-Couple Full-Wave Rectifier

Since the one threshold voltage drop still occurs in the previous topology, the fully cross-coupled full-wave rectifier was proposed in order to reduce this voltage drop of all the diodes in the conduction path (Colomer-Farrarons et al. 2008; Wahab et al. 2017), see Figure 11 (c). Therefore, the voltage and power efficiency also increase with this improvement.

Furthermore, to improve the linearity of the ON-resistance in PMOS, the body bias technique was added to the NVC in Yoon *et al.* (2017) with wide operation voltage where the bulk terminal of PMOS was connected to a beta-multiplier voltage reference. This technique proved to improve the NVC efficiency in the low input voltage region.

#### 2.2.1.3 Voltage Multiplier

This topology can rectify a low-voltage AC to a higher voltage DC using self-commutating switched-capacitors for charge storage and transfer. As shown in Figure 12, this half-wave voltage doubler doubles the input voltage by clamping a capacitor voltage to the input voltage. During the negative half cycle of the input, the capacitor is charged to the input peak voltage minus the threshold voltage of the diode in the charging path. In the positive half-cycle, the capacitor acts as a DC source in series with the input. Assuming that the capacitor is large enough to keep the output voltage almost constant throughout the discharging in the positive half-cycle, the output voltage of this topology is twice the input voltage minus two diode threshold voltage drops, one each in charge storing and charge transfer phase. Increasing the capacitor value leads to an increase in the charge transfer, producing a larger voltage across an output load due to the reduction of the capacitive reactance. Even though this topology can get a higher output voltage, the current will be lower due to this voltage amplification. Also, large capacitors are not suitable for fully integrated designs and will need to be off-chip. Therefore, this topology is not suitable for energy harvesting applications.

Figure 12: Voltage doubler.

Table 2 presents the performance comparison between all the previous topologies that Yeo et al. (2015) presented. The features of VCE and PCE were calculated according to Equations 6 and 7. It can be concluded that the topology that showed the best features for harvesting applications was the fully gate cross-coupled since the voltage operation is lowest compared to the other topologies. Besides that, this rectifier presented a higher PCE, which means that the efficiency of the circuit is the highest.

$$VCE = \frac{V_{OUT}}{V_{IN}} \cdot 100\%$$

$$PCE = \frac{\int_{t}^{t+T} V_{OUT}(t) \cdot I_{OUT}(t) dt}{\int_{t}^{t+T} V_{IN}(t) \cdot I_{IN}(t) dt} \cdot 100\%$$

7

Table 2: Comparison of different full-wave rectifier topologies (Yeo et al. 2015).

|                                    | Performance Metrics |         |                               |  |

|------------------------------------|---------------------|---------|-------------------------------|--|

| CMOS Passive Rectifier<br>Topology | PCE (%)             | VCE (%) | Minimum input<br>voltage (mV) |  |

| Conventional full-bridge           | 27.74               | 7.21    | 500                           |  |

| Gate cross-coupled                 | 57.43               | 23.76   | ~50                           |  |

| Fully cross-coupled                | 82.12               | 40.75   | ~20                           |  |

Moreover, these passive rectifiers present a critical disadvantage. It is impossible to control the reverse leakage current when a capacitor is used as a load, damaging the overall device. Thus, it is required to use an active stage to control this unwanted reverse leakage current.

### 2.2.2 Active Rectifiers

Active rectifiers increase efficiency throughout active signal control mechanisms that interfere with the rectification process. Those use controlled switches (working as an ideal diode) and high-gain comparators, providing reduced forward voltage compared to other mechanisms described above. Nevertheless, these control circuits constitute an additional power consumption for the system, in some situations, can require a limited power supply. Therefore, low power consumption and low voltage operations are basic needs for active rectifiers (Niu, Huang, and Jiang 2012). Furthermore, these circuits aim to behave as an ideal diode, implying no forward voltage drop and no reverse current.

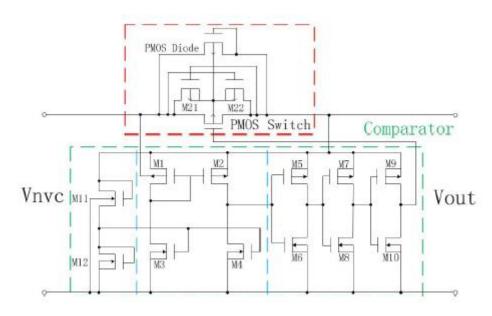

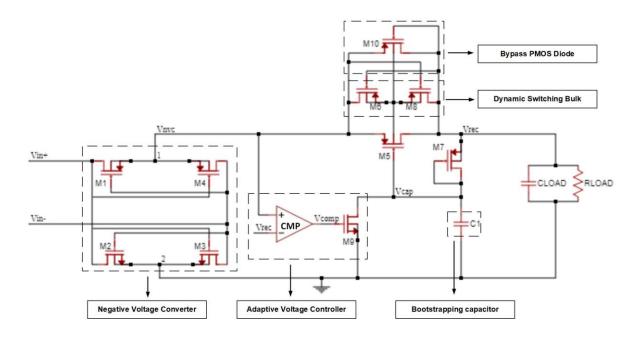

An active rectifier is proposed in (Niu, Huang, and Jiang 2012) with a body input comparator and a body bias technique used to allow low voltage operation and high voltage and power conversion efficiency, see Figure 13. This circuit is composed of a passive stage (NVC) to convert the AC signal into a DC and an active diode, with a body comparator that controls its switching action. This comparator receives as an input the output signal from the NVC and the capacitor, then if  $V_{out} < V_{NVC}$ , the comparator keeps the diode at ON state. However, if  $V_{out} > V_{NVC}$ , the comparator turns off the diode, which blocks the reverse current from the load. This rectifier can achieve a peak voltage efficiency of over 96% and the maximum power efficiency of over 94%.

Figure 13: Schematic of an active CMOS rectifier.

Figure 14 presents the schematic of the active stage of the rectifier proposed by Niu *et al.* (2012). This comparator consists of three parts: the bias circuit part (M11 and M12), body-input circuit part (M1-M4), and inverter output circuit (M5-M10). Moreover, it was added to the PMOS switch (active diode) a body bias technique (M21 and M22) to restrain latch-up and a MOSFET bypass diode to ensure a safe start-up of M1.

Figure 14: Schematic of the active stage (Niu, Huang, and Jiang 2012).

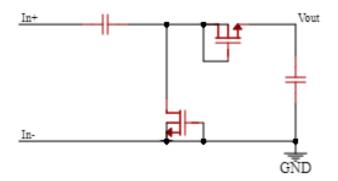

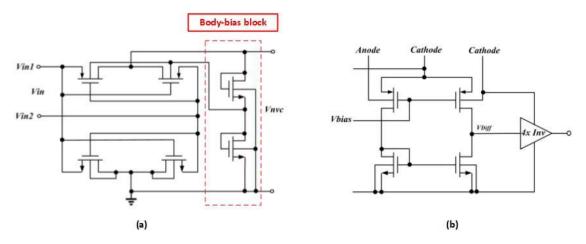

Peters *et al.* (2011) proposed an active rectifier with a bulk-input comparator technique for ultra-low-voltage energy harvesting systems. This rectifier was designed to work with input source amplitudes around 0.5 V. This structure is composed of two stages: the NVC and the active diode. In addition, the authors added a body bias block in the negative voltage converter stage (Figure 15 (a)) to reduce the threshold voltage of PMOS, which reduces the minimum operation voltage to 0.3 V since the transistors will only turn on when the input voltage is higher than the threshold voltage. Figure 15 (b) shows the structure of the bulk-input comparator. This comparator uses only two stacked transistors, and no tail source is used in this circuit (Peters et al. 2011). However, when the input voltage is higher than the output voltage, the PN junctions between the bulk and source terminal of the input transistor will be turned on. Consequently, the bulk leakage current will increase, which compromises the efficiency of the circuit (Q. Li, Wang, Ding, et al. 2014). In addition, the proposed rectifier in Peters et al. (2011) has a frequency band not suitable for the application of this work.

Figure 15: Schematic of the ultra-low voltage rectifier (Peters et al., 2011) (a) negative voltage converter with a body-bias block; (b) input-bulk comparator.

In contrast, the frequency bandwidth in the following research papers (Q. Li, Wang, Ding, et al. 2014; Guo and Lee 2009; R. C.-H. Chang et al. 2020; Oh et al. 2017) corresponds to the desired application. The authors use two active diodes to control the reverse current that flows through the two NMOS in each input cycle and two PMOS in cross-coupled to provide the conduction path. However, the dynamic range does not meet the requirements to achieve a low-power consumption. Furthermore, the proposed rectifiers cannot work for input voltages lower than 1 V, which is critical for energy harvesting applications(Q. Li, Wang, Ding, et al. 2014). In R. C. H. Chang *et al.* (2017), the authors designed a fully active configuration using NMOS and PMOS to ensure that the reverse leakage current through the PMOS input source is zero. The main disadvantage of this configuration is when the NMOS devices turn on simultaneously, which leads to power losses. Therefore, Chang *et al.* (2020) proposed a rectifier with a third comparator to eliminate the oscillations of NMOS, which avoids the two active diodes turning on/off simultaneously. Nevertheless, the PCE is only high for an input voltage around 4.88 V.

However, the main limitation of these configurations is that they cannot decrease the  $V_{SG}$  of the main transistor, and thus enhancing the output voltage stored on the load capacitor. Therefore, an extra circuit is demanded to smooth the threshold voltage effect of this transistor to overcome these drawbacks.

#### 2.2.3 Threshold Cancellation Topologies

Several threshold cancellation topologies were proposed to enhance the output voltage by reducing the threshold voltage effect of the main transistor of the rectifier (Koji Kotani and Ito 2007; K Kotani and Ito 2009; Khan and Choi 2017). The threshold voltage is a process parameter dependent on the type and thickness of oxide (Hashemi, Sawan, and Savaria 2012). Low threshold voltage MOSFETs present a high leakage current caused by the low substrate doping, which leads to an increase in power consumption

and reliability problems. Thus, these threshold cancellation techniques are used to avoid those types of MOSFETs since it is only needed to smooth the threshold voltage effect when the main pass transistor is ON.

Hashemi *et al.* (2012) proposed a low-voltage CMOS rectifier to perform this technique using the bootstrap technique, see Figure 16 (a). This bootstrap circuit can achieve high voltage conversion efficiency by reducing the voltage drop. In this structure, M5 works as a diode and provides the current through M7 to charge the bootstrapping capacitor ( $C_{B1}$ ) at the start up state. Then, the power stored at  $C_{B1}$  will be applied to the gate of M3, which works as a switch. When the input voltage is larger than the output voltage by one threshold voltage, M5 will be turned on and the current flows through M5 and M7 to charge the boostrapping capacitor. By increasing the voltage helded on the gate of M3, the threhsold voltrage effect will be reduced, which leads to a voltage drop reduction. However, even if the minimum operation voltage can be as smal as 0.8 V, VCE and PCE are not high enough, especially the power efficiency, which is only around 30% when the input voltage is lower than 0.8 V. This low PCE is caused by the high reverese leakage current, which degrades the overall performance of the system.

An active bootstrapping rectifier is presented in (Lee, Liao, and Lee 2019) to overcome the issues of the previous work, see Figure 16 (b). This topology uses two active diodes to control the conduction path for each input cycle and a bootstrap technique to reduce the threshold voltage of both main pass PMOS. Also, an AVC is set in this work to adjust the gate voltage of the main pass PMOS, which reduces the voltage drop by reducing the ON-resistance. Besides reducing the reverse leakage current, the PCE of this configuration can still be improved for input voltages smaller than 1 V. To overcome the drawbacks mentioned above, in Vithya Lakshmi *et al.* (2021), a dual switching technique replaced the two active

Figure 16: (a) Full-wave bootstrap rectifier (Hashemi, Sawan, and Savaria 2012); (b) Active bootstrapping rectifier (Lee, Liao, and Lee 2019).

diodes. This approach can maintain a constant gate bias on the two main NMOS transistors, avoid the reverse leakage current, reduce the area on-chip, and enhance the PCE for low voltage applications. However, high values for PCE can only be obtained for input frequencies around 20 kHz.

### 2.3 Leakage current in CMOS

Initially, in the CMOS process, the high voltage supply value caused the electric field to rise, reducing the device's reliability. By decreasing the channel length, the MOSFET can operate with lower voltages due to lowering the threshold voltage, and thus the low power demands can be reached. However, the downscaling of the channel length has led to new challenges such as short-channel effects, high leakage current, and static power dissipation, which deteriorates the circuit frequency and performance. Therefore, it is necessary to raise the performance to an acceptable level. To reach low power consumption, further minimization of power supply and channel dimensions must occur, approaching the voltage supply value towards the threshold voltage. Since a significant portion of the total power consumption is related to leakage current, it must be managed and used as the primary operational current to satisfy low power requirements.

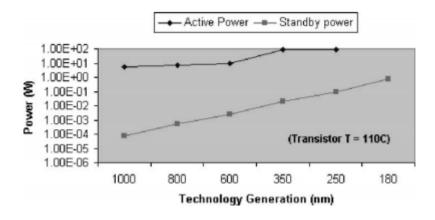

As the transistor length decreases in size, at the same time, some challenges emerge, such as short-channel effects, high leakage current, and static power dissipation. Therefore, designing a CMOS circuit with reduced technology involves a trade-off between chip area, the performance of the circuit, and dynamic power dissipation. However, special attention must also be given to static power consumption since it is ideally expected that the CMOS circuit does not consume power while it is at OFF state. Figure 17 shows the leakage power consumption trend with the technology downscaling. Thus, it is important to manage these metrics to maximize these deep submicron levels (Bohr and Young 2017).

$$P_{Dynamic} = \alpha \cdot C_L \cdot V_{DD}^2 \cdot f_0$$

8

$$P_{Static} = I_{leakage} \cdot V_{DD}$$

9

Figure 17: Leakage power consumption behaviour with technology downscaling (Hanchate and Ranganathan 2004).

According to Equation 8,  $P_{Dynamic}$  is defined as the power dissipation when the circuit is working (active mode), where  $\alpha$  is the switching activity,  $C_L$  is the gate capacitance,  $V_{DD}$  is the voltage supply, and  $f_0$  is the operating frequency.  $P_{Dynamic}$  results from charging and discharging the capacitances as a result of the switching activity of the transistor. On the other hand, the continuous scaling of the MOSFET to deep sub-micron channel length has delivered lesser area and low capacitance effects leading to negligible dynamic power dissipation (Gupta and Kahng 2003).

$P_{Static}$  is the power consumption when the circuit is at OFF state, where  $I_{leakage}$  is the off-state leakage current and  $V_{DD}$  is the voltage supply, see Equation 9.  $P_{Static}$  is mainly the off-state leakage current that leaks through the transistor even in the inactive mode (Kim et al. 2003). This power consumption is an important feature to consider when CMOS technology is scaling down since its dominance increases with the shrinking of the processor technology. Unfortunately, smaller geometries increase the leakage current, and therefore, static power begins to dominate the power consumption equation in chip design (Kim et al. 2003).

This off-state current is influenced by many parameters, such as the threshold voltage, channel length, channel/surface doping profile, drain/source junction depth, gate oxide thickness, and  $V_{DD}$  (Roy, Mukhopadhyay, and Mahmoodi-Meimand 2003). When CMOS circuits are being designed using short-channel transistors, low power supply levels are required to reduce the static power consumption, influencing the weak inversion state (or subthreshold region). Since the threshold voltage is also downscaled, it consequently increases the portion of off-state leakage current (De and Borkar 2000). Moreover, as the drain voltage increases, the channel depletion region widens, which results in a significant increase in the drain current. Thus, from this point of view, the off-state leakage current is caused by the DIBL, which is an undesirable field penetration among the source and drain that generates the unwanted current through the channel (Qu et al. 2011). This unwanted current destroys the classical infinite input impedance assumption of the MOSFET and affects the efficiency of the circuit by increasing the overall power consumption (Roy, Mukhopadhyay, and Mahmoodi-Meimand 2003). Therefore, leakage current reduction techniques must be addressed to improve the performance of the CMOS circuits.

### 2.3.1 Leakage Current Reduction Techniques

As technology scales down to deep submicron levels, leakage power consumption has proved to be a major concern in designing CMOS VLSI circuits due to the reduced threshold voltage and device form

factor. The voltage supply needed to be scaled to overcome the dynamic power and reliability issues. To keep an acceptable level of circuit performance, the threshold voltage also needs to be scaled. This reduction leads to an exponential rise of the leakage power consumption to a level that might overwhelm the dynamic power consumption (Chun and Chen 2010; Lahbib et al. 2015). Therefore, it is demanded to be aware of some existent approaches to minimize and estimate this unwanted current in both ON and OFF state in MOS transistors (Agarwal et al. 2004). The reduction in leakage current can be achieved in two ways: process and circuit-level techniques. The first one is achieved by regulating the transistor dimensions (length, oxide thickness, junction depth, etc.) and the doping profile. Threshold voltage and leakage current can be managed at the circuit level by applying different techniques to control the transistor voltage terminals (source, drain, gate, and bulk) (Roy, Mukhopadhyay, and Mahmoodi-Meimand 2003).

This subsection presents some circuit-level approaches proposed to minimize the leakage current, such as multi-threshold voltage designs, voltage supply scaling, and transistor stacking.

### 2.3.1.1 Multi-threshold voltage designs

This process-level approach minimizes the subthreshold leakage current, which provides both high and low threshold voltage transistors in a single chip (see Equation 10). Thus, the high-threshold transistor mitigates the subthreshold leakage, while the low threshold transistors are used to achieve high performance depending on the circuit's behaviour (Roy, Mukhopadhyay, and Mahmoodi-Meimand 2003).

$$I_D = I_{D0} \cdot \frac{W}{L} \cdot \exp\left(\frac{V_{GS} - V_{th}}{n \cdot V_T}\right)$$

10

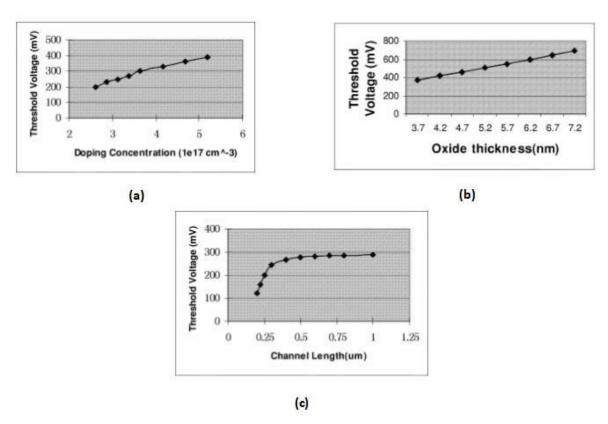

Multiple-threshold voltages values can be achieved by varying different parameters regarding the fabrication processes, see Figure 18. Thus, threshold voltage depends on the channel doping profile, gate oxide thickness, and channel length.

This technique is mainly used to keep higher performance levels while decreasing the leakage power consumption during standby and active operation modes. The advantage of this technique is that it avoids additional circuits, delays, and extra area on-chip(Kim et al. 2003). One practical example is on CMOS rectifiers since the high threshold transistors can be used on non-critical paths to reduce the leakage current. At the same time, the performance is reached with low threshold transistors to decrease the overall voltage drop of the circuit. Further disadvantages of applying this technique in the proposed circuits will be given in section 3.2.

Figure 18: Fabrication process parameters that influence the threshold voltage (a) channel doping concertation (b) oxide thickness (c) channel length.

# 2.3.1.2 Supply Voltage Scaling

This technique is used to reduce the dynamic power consumption and the leakage current, which consequently reduces the leakage power consumption (Butzen and Ribas 2007) (Gonzalez, Gordon, and Horowitz 1997). This method is considered effective in reducing the power consumption of the CMOS circuits due to the quadratic dependence of the switching power concerning the supply voltage, see the previous Equation 1. Besides the supply voltage scaling providing leakage power saving, it exponentially

reduces the leakage current that results from the DIBL effect due to the technology down-scaling (Roy, Mukhopadhyay, and Mahmoodi-Meimand 2003).

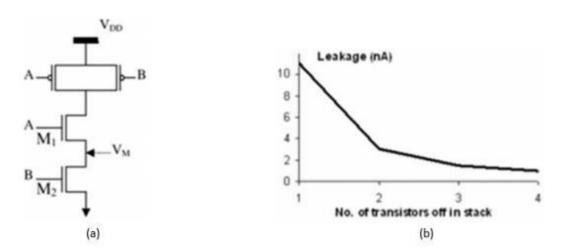

#### 2.3.1.3 Transistor Stacking

The leakage current flowing through a stack of series-connected transistors is reduced when more than one transistor in the stack is turned off (Butzen and Ribas 2007). This effect is known as the "stacking effect" or "self-reverse bias". As shown in Figure 19 (b), the leakage of a two-transistor stack in order of magnitude is less than the leakage in a single transistor. However, when more than two stacking transistors are used, the leakage current tends to be constant, as seen in the illustrated plot. Figure 19 (a) presents a NAND topology with transistor stacking. If the NMOS M1 and M2 are OFF, the voltage at the intermediate node ( $V_M$ ) will be slightly positive due to the small drain current (Nagar and Parmar 2014). This positive source potential created by the transistor stacking will turn the potential between the gate and source negative. The positive potential at  $V_M$  has three effects such as (Butzen and Ribas 2007; Nagar and Parmar 2014):

- 1. The leakage current is substantially reduced due to the intermediate point's negative gate-to-source positive source potential, which is caused by the positive source potential.

- 2. Since  $V_M$  is positive, the body-to-source potential of transistor M1 becomes negative, resulting in a body effect increase of M1, thus reducing the leakage current that flows through this transistor.

- 3. The DIBL effect is mitigated due to the decrease of the drain to source potential of M1 caused by the positive  $V_M$ . Consequently, the leakage current is also reduced.

Figure 19: Transistor Stacking, (a) Stacking effect in two-input NAND gate, (b) Subthreshold leakage current using different number of stacks in OFF state (Butzen and Ribas 2007).

### 3 Development and Results

### 3.1 Analog Switch

One of the main bottlenecks of the vibrational energy harvesters is the piezoelectric's operational resonant frequency that contrasts with the low frequency of the vibrational environmental sources. An efficient matching circuit is required to increase the transferred energy to the storage unit to maximize the scavenged power. A frequency up-conversion technique is needed to increase the operating frequency to overcome these disadvantages. By increasing the working frequency, a matching circuit can be more efficient, the size of the passive components decreases compared to traditional matching circuits. Also, as the dimension decreases, producing these passive matching components in CMOS technology, its reliability increases and decreases related intrinsic noise.

Even though the single TG improves the switch's characteristics, managing the MOSFETs' threshold voltage inside it is still important. This bulk voltage management is essential because low ON-resistance is needed to avoid power losses when the switch is ON. On the other side, when the switch is OFF, a high OFF resistance is required to isolate the piezoelectric device's output.

Another problem related to the TG is the unwanted reverse current when a capacitor or an inductor is added as a load. When an input sinusoidal signal is applied, the output voltage would be slightly higher than the input voltage in several time intervals, leading to a change of the current direction. Therefore, it is essential to create a technique to block the reverse current. This unwanted reverse current decreases the performance of the circuit and is a potential hazard to the device.

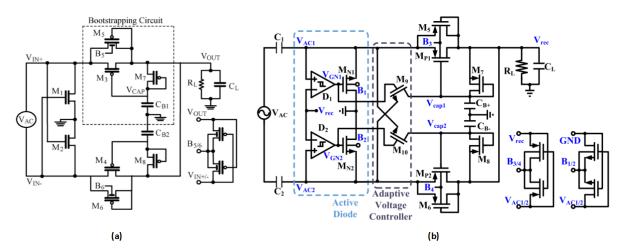

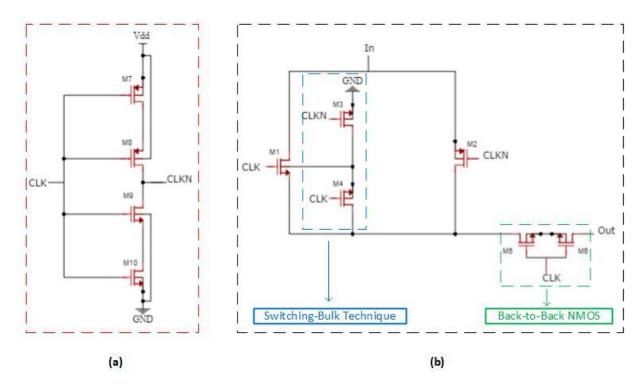

Hence, a new topology was designed to fix these issues, and it is presented in Figure 20. This design also has a TG as the primary switch device. Compared with the single TG, this circuit presents a constant and low ON-resistance and a high OFF-resistance, which leads to an increase in its performance. Besides that, it prevents reverse current from the RC load. Therefore, this circuit is composed of an inverter with a transistor stacking technique to bias the switch, a TG with the switching-bulk technique applied to the

Figure 20: (a) Inverter stage with Transistor Stacking used to bias the analog switch; (b) Proposed analog switch with the addressed techniques.

NMOS transistor, and a Back-to-Back NMOS configuration that connects the TG to the RC load. The size of the transistors used in the Analog Switch design is displayed in Table 3. Furthermore, the physical layout of the proposed analog switch is presented in Figure 21.

During the ON phase, the inverter biases the TG NMOS with CLK at high state and PMOS with CLKN at a low state, making the output signal tracking the input signal with high voltage efficiency low switch's ON-resistance. During the OFF phase, CLK is low, and CLKN is high, making the TG turn off, and the output voltage drops to almost 0 V.

The following subsections present the techniques added to the analog switch to improve the linearity, threshold voltage, ON-resistance, OFF-resistance, and avoid the unwanted reverse current.

Table 3: Transistor size of the Analog Switch.

| MOSFET        | Unit Size (μm/μm) |  |  |

|---------------|-------------------|--|--|

| M1/2          | 10/0.13           |  |  |

| M3/4/7/8/9/10 | 0.15/0.13         |  |  |

| M5/6          | 5/0.13            |  |  |

Figure 21: Physical layout of the proposed analog switch.

# 3.1.1 The Switching-Bulk Technique

Due to high threshold variations on the TG when the bulk terminal is connected to the power supply for PMOS, and to the ground for NMOS, a switching-bulk NMOS technique was added in order to fix this issue. It consists of two auxiliaries NMOS, M3 and M4, that switch the main NMOS bulk between GND, during the OFF phase, and the source voltage, during the ON phase. For this application, this technique is revealed to be useful because, on the one hand, the TG's resistance becomes lower and constant

during the ON phase due to the threshold voltage reduction. On the other hand, during the OFF phase, the resistance increases due to the threshold voltage's increase, leading to a better switch's conductance and performance.

However, for this application, this technique cannot be added to the PMOS transistor because, due to its bulk voltage being varied between the input voltage and the voltage supply, the bulk voltage would be higher than the input voltage when the switch is at OFF state. Therefore, it would generate a reverse current flowing from the bulk to the input voltage. The bulk terminal was connected to the source for this transistor to keep the threshold voltage almost constant due to body effect cancellation. With this technique, the difference between PMOS and NMOS threshold voltage was reduced, which improves the unavoidable charge injection error.

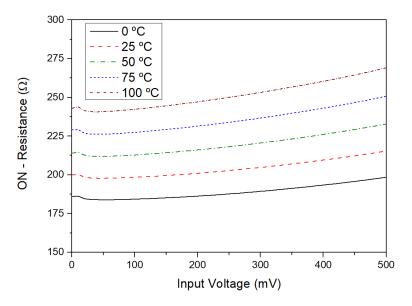

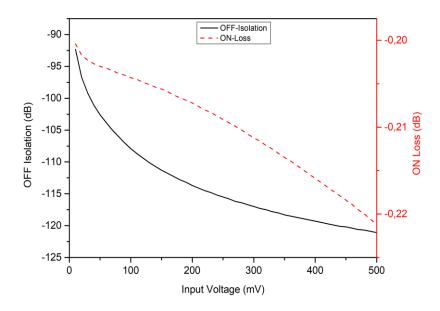

To prove the efficiency of the switching bulk technique, Figure 22 shows the ON-resistance and OFF-resistance behavior with the input voltage variation with and without this technique. As shown in the presented figure, the ON-resistance is low and constant for the two cases since the bulk terminal of M1 is connected to the drain by M4. At an input voltage amplitude of 500 mV, the ON-resistance is 216  $\Omega$ , which is revealed to be low. However, when the analog switch is not working, the OFF-resistance is higher when this technique is used because M3 connects the bulk terminal of M1 to 0 V. Since the bulk voltage is different from the drain one, the OFF-resistance is increased due to the body effect in M1, which is good for isolating the load from the input. Therefore, it can be concluded that the mentioned overall features of the analog switch are improved by using the switching bulk-technique.

Figure 22: ON-resistance and OFF-resistance behaviour with and without the switching bulk technique for different input voltage.

#### 3.1.2 Back-to-Back NMOS

As explained before, one of the problems of the analog switch is the reverse leakage current associated with the load when the output voltage is slightly higher than the input voltage. Thus, since the NMOS impedance between drain and source is lower than in PMOS, a back-to-back NMOS configuration was added after the TG, consisting of two NMOS transistors, M5 and M6, with both source terminals connected. This configuration is useful because it eliminates all the blocking diodes and replaces them with a pair of NMOS with their internal body diodes pointing away from each other to block the unwanted reverse current flow. Besides that, this technique decreases the circuit's current consumption due to leakage current reduction, which enhances this circuit's power efficiency. Even though this technique reduces voltage efficiency, the voltage drop across the two NMOS is low, so it is not significant.

Since the OFF-state leakage current is an important parameter that influences static power consumption (Jayakumar et al. 2010), this current was measured with the input voltage variation with the back-to-back technique and without it. In Figure 23, it is proved that the back-to-back NMOS avoids reverse current and mitigates the OFF-state leakage current due to the high impedance path generated by the two NMOS transistors. Also, this OFF-state leakage current is lower than the prior state of the art on analog switches, as shown in section 3.1.4.

Figure 23: OFF-state leakage current with and without the back-to-back NMOS technique.

### 3.1.3 Transistor Stacking on the Inverter stage

Finally, Figure 20 (a) presents the inverter stage with transistor stacking. It is essential to add this stage to bias the MOSFETs inside the TG. Therefore, it is imperative to manage the leakage current and the power dissipation at this stage. A transistor stacking was added to this stage by connecting M7 and M10 to decrease these features. These two transistors present a high threshold voltage caused by the body effect. Consequently, the overall static power consumption is reduced due to the decrease of both static current and OFF-state leakage current.

Table 4 shows the current that the power source needs to bias to the inverter during the ON and OFF state with and without the transistor stacking. As expected, this technique mitigates the current consumption of the inverter, which consequently reduces its static power consumption.

Table 4: Current and static power consumption comparison.

| Features                             | With Transistor Stacking | Without Transistor Stacking |  |  |

|--------------------------------------|--------------------------|-----------------------------|--|--|

| $I_{ON}$ ( $\mu$ A)                  | 17.40                    | 36.10                       |  |  |

| $I_{OFF}$ (nA)                       | 71.41                    | 133.33                      |  |  |

| $P_{Static}$ (nW) for $V_{DD} = 2 V$ | 142.80                   | 266.66                      |  |  |

#### 3.1.4 Results

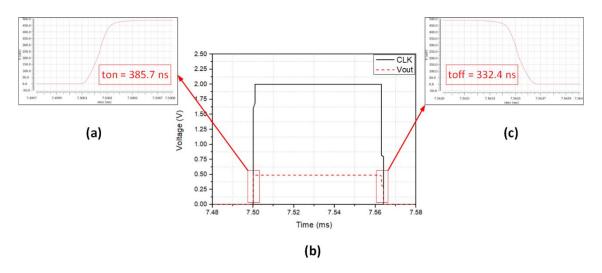

The proposed analog switch was simulated in the Cadence Virtuoso Analog Design Environment using 130 nm CMOS technology. The input voltage is a sine wave with 500 mVp-p amplitude, and the power supply voltage is a DC source with 2 V. The input frequency was set in 32 Hz, which simulates the harvester output frequency. Since an external oscillator circuit generates the clock signal, a square wave source was used to simulate its behavior. The amplitude signal was varied from 0 V to 2 V with a frequency of 3.2 kHz and a duty cycle of 20 %. A load resistor and capacitor were added with 10 k $\Omega$  and 1 pF, respectively, in the output to study the circuit's performance.

Figure 24 shows the sampled output voltage and the input voltage signal for the proposed analog switch. As observed, when the CLK signal reaches the high value, the analog switch is ON, which allows the current to flow, and the output voltage almost reaches the input one. In the opposite state, the analog switch isolates the input terminal from the output, which drops the output signal to 0 V. As expected, the output frequency increases from 32 Hz to 3.2 kHz. Furthermore, it is possible to notice that, when the input is at 500 mV of amplitude, the voltage drop of the analog switch is higher due to the increase of the ON-resistance and current, as presented in Figure 25. According to Equation 4, the rise of the ON-resistance is caused by the increase of the source terminal, which reduces  $V_{GS}$ .

Figure 24: Simulation of the proposed analog switch working principle, including the input voltage (In), clock signal (CLK), and the output voltage (Out).

In addition, Figure 25 shows the ON-resistance behaviour for different temperature values. It can be observed that the ON-resistance increases for higher temperatures since the threshold voltage is directly proportional to the temperature. Nonetheless, the ON-resistance is still low for higher temperatures, which proves the analog switch's robustness to temperature variations.