## Western University Scholarship@Western

**Digitized Theses**

**Digitized Special Collections**

2009

## A New ZCS-PWM Full-Bridge Boost Converter

Ahmad Mousavi

Follow this and additional works at: https://ir.lib.uwo.ca/digitizedtheses

#### **Recommended Citation**

Mousavi, Ahmad, "A New ZCS-PWM Full-Bridge Boost Converter" (2009). *Digitized Theses*. 3770. https://ir.lib.uwo.ca/digitizedtheses/3770

This Thesis is brought to you for free and open access by the Digitized Special Collections at Scholarship@Western. It has been accepted for inclusion in Digitized Theses by an authorized administrator of Scholarship@Western. For more information, please contact wlswadmin@uwo.ca.

# A New ZCS-PWM Full-Bridge Boost Converter

(Thesis Format: Monograph)

by

Ahmad Mousavi

Faculty of Engineering Department of Electrical and Computer Engineering Graduate Program in Engineering Science

> A thesis submitted in partial fulfillment of the requirements for the degree of Master of Engineering Science

School of Graduate and Postdoctoral Studies The University of Western Ontario London, Ontario, Canada

© Ahmad Mousavi 2009

## ABSTRACT

The objective of this thesis is to propose, analyze, design, implement, and experimentally confirm the operation of a new Zero-Current-Switching PWM dc-dc fullbridge boost converter that does not have the drawbacks of previously proposed circuits of the same type. In this thesis, the general operating principles of the converter are reviewed, and the converter's operation is discussed in detail and analyzed mathematically. As a result of the mathematical analysis, key voltage and current equations that describes the operation of the auxiliary circuit and other converter devices have been derived. The steady state equations of each mode of operation are used as the basis of a MATLAB program that is used to generate steady-state characteristic curves that shows the effect that individual circuit parameters have on the operation of the auxiliary circuit and the boost converter.

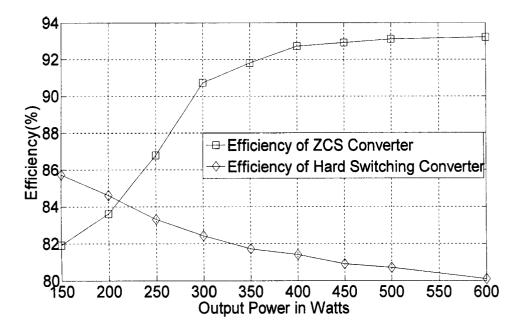

Observations as to their steady-state characteristics are made and the curves are used as part of a design procedure to select the components of the converter, especially those of the auxiliary circuit. An experimental full-bridge PWM dc-dc boost converter prototype is built based on the converter design and typical waveforms are presented. The efficiency of the proposed converter operating with the auxiliary circuit is compared to that of a standard PWM dc-dc full-bridge boost converter and the increased efficiency of the proposed converter is confirmed.

## ACKNOWLEDGEMENTS

I wish to express my most sincere gratitude to my supervisor Dr. G. Moschopoulos under whose supervision this Masters dissertation was conducted throughout all stages of the thesis. I really admire his extraordinary support throughout my studies as an M.E.Sc student.

Sincere thanks are also given to my good friend Mr. Pritam Das for his great help and contribution during the research work.

I am also thankful to Mr. Djilali Hamza at Queens University for his help and guidance during the experimental work. In addition, I would like to thank all my friends at the Electrical and Computer Engineering Department at the University of Western Ontario and Queens University for the enjoyable experience.

Finally, I would like to thank my parents, M.R.Moussavi and R.Kalantari for their support and encouragement during my studies.

London, Ontario April 2009

Ahmad Mousavi

## Contents

| Certificate of examination                                              | ii  |  |

|-------------------------------------------------------------------------|-----|--|

| Abstract                                                                | iii |  |

| Acknowledgements                                                        | iv  |  |

| Contents                                                                | v   |  |

| List of figures                                                         | vii |  |

| Nomenclature                                                            | x   |  |

| Chapter1 Introduction                                                   | 1   |  |

| 1.1 General Introduction                                                | 1   |  |

| 1.1.1 Power Electronics                                                 | 1   |  |

| 1.1.2 High Switching Frequency Operation in Power Electronic Converters | 3   |  |

| 1.1.3 Losses in Semiconductor Switches                                  | 4   |  |

| 1.1.4 Diode Reverse-Recovery Current                                    | 7   |  |

| 1.1.5 Soft Switching                                                    | 8   |  |

| 1.2 Dc-dc Converters                                                    |     |  |

| 1.3 Full-Bridge Boost Converter                                         |     |  |

| 1.4 Literature Review                                                   |     |  |

| 1.5 Thesis Outline                                                      | 23  |  |

| Chapter2 A New ZCS-PWM Full-Bridge Boost Converter                      | 25  |  |

| 2.1 Introduction                                                        | 25  |  |

| 2.2 Converter Operation                                                 | 27  |  |

| 2.3 Conclusion                                                          | 37  |  |

| Chapter3 Circuit Analysis of the Proposed Boost Converter               | 38  |  |

| 3.1 Introduction                                                        | 38  |  |

| 3.2 Circuit Analysis                                                    |     |  |

| 3.3 Summary of Key Equations                                            |     |  |

| 3.4 Conclusion                                                          | 48  |  |

| Chapter4 Design Procedure and Example                                   | 49  |  |

| 4.1 Introduction                                                      | 49 |  |

|-----------------------------------------------------------------------|----|--|

| 4.2 Conditions for ZCS Turn-Off in the Proposed Full-Bridge Converter |    |  |

| 4.3 Characteristics of the Proposed Boost Converter                   | 53 |  |

| 4.3.1 Design Example                                                  | 62 |  |

| 4.3.2 Power Circuit Design                                            | 63 |  |

| 4.3.3 Designing Input Inductor L <sub>in</sub>                        | 63 |  |

| 4.3.4 Designing Output Capacitor Co                                   | 64 |  |

| 4.3.5 Designing Main Switches Q <sub>1-4</sub>                        | 65 |  |

| 4.4 Auxiliary Circuit Design                                          | 66 |  |

| 4.5 Simulation Results                                                | 71 |  |

| 4.6 Conclusion                                                        | 75 |  |

| Chapter5 Experimental Results                                         | 76 |  |

| 5.1 Introduction                                                      | 76 |  |

| 5.2 Experimental Results                                              | 76 |  |

| 5.3 Conclusion From the Experimental Results                          | 81 |  |

| 5.4 Efficiency Results                                                | 82 |  |

| 5.5 Conclusion                                                        | 84 |  |

| Chapter6 Conclusion of the Thesis                                     |    |  |

| 6.1 Introduction                                                      | 85 |  |

| 6.2 Summary                                                           | 85 |  |

| 6.3 Conclusion                                                        | 86 |  |

| 6.4 Contribution                                                      | 87 |  |

| 6.5 Proposal for Future Work                                          | 88 |  |

| Appendix 1                                                            | 90 |  |

| Appendix 2                                                            | 91 |  |

| Appendix 3                                                            | 92 |  |

| References                                                            |    |  |

| Curriculum Vitae                                                      |    |  |

## **List of Figures**

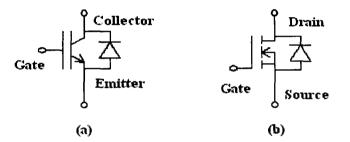

| Fig.1.1                                                                              | (a) Schematic diagram of an IGBT. (b) Schematic diagram of a power MOSFET                                                                                                                                                                                                                   | 3  |  |

|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

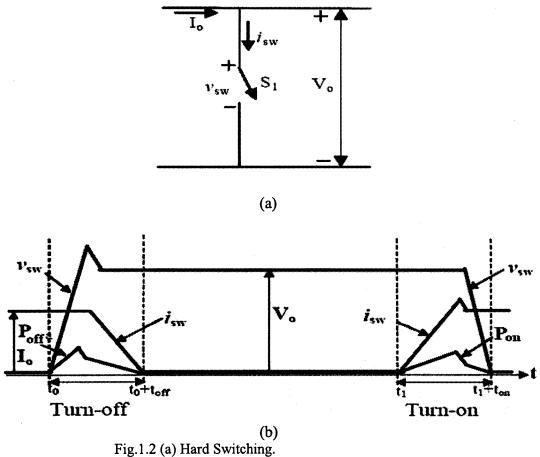

| Fig.1.2                                                                              | Fig.1.2 (a) Hard Switching. (b) Loss of Power during hard switching                                                                                                                                                                                                                         |    |  |

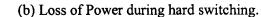

| Fig.1.3                                                                              | Fig.1.3 Reverse recovery current in a diode                                                                                                                                                                                                                                                 |    |  |

| Fig.1.4                                                                              | Fig.1.4 ZVS MOSFET implementation                                                                                                                                                                                                                                                           |    |  |

| Fig.1.5                                                                              | Fig.1.5 ZCS IGBT implementation                                                                                                                                                                                                                                                             |    |  |

| Fig.1.6                                                                              | Fig.1.6 A dc-dc boost converter                                                                                                                                                                                                                                                             |    |  |

| Fig.1.7                                                                              | <ul> <li>Fig.1.7 (a)Waveform of the voltage across input inductance L<sub>in</sub> of a boost converter.</li> <li>(b)Waveform of the voltage at the gate of the switch in a boost converter.</li> <li>(c) Waveform of current through the input inductance in a boost converter.</li> </ul> |    |  |

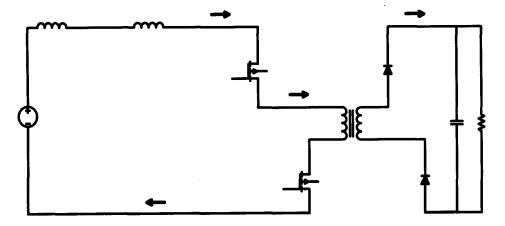

| Fig.1.8                                                                              | Current-fed PWM full-bridge boost converter                                                                                                                                                                                                                                                 | 14 |  |

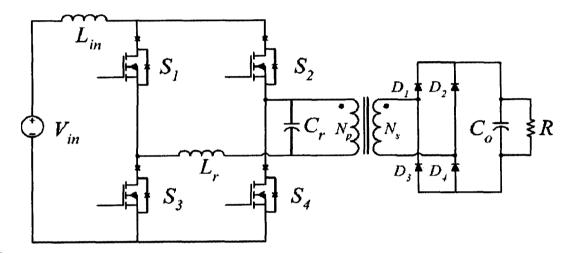

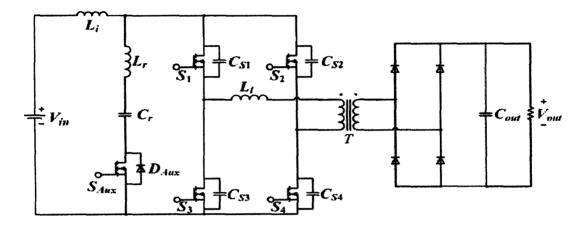

| Fig.1.9                                                                              | Fixed frequency resonant ZCS current fed converter proposed in [11]                                                                                                                                                                                                                         | 16 |  |

| Fig.1.10                                                                             | (a), (b) Variable frequency resonant ZCS current fed converter                                                                                                                                                                                                                              | 16 |  |

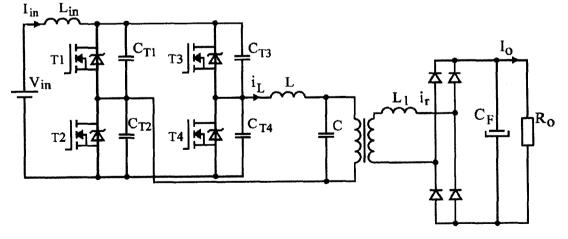

| Fig.1.11                                                                             | ZCS full-bridge PWM boost converter                                                                                                                                                                                                                                                         | 19 |  |

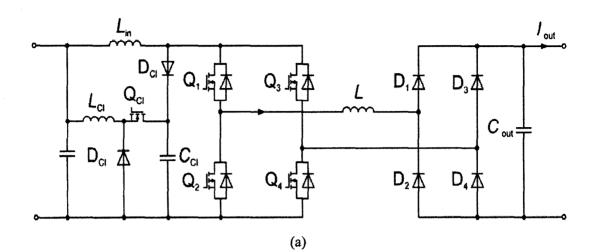

| Fig.1.12 Current-fed converters with parallel auxiliary circuit (a) [16] (b) [15] 20 |                                                                                                                                                                                                                                                                                             |    |  |

| Fig.1.13                                                                             | Current fed full-bridge converter proposed in [13]                                                                                                                                                                                                                                          | 21 |  |

| Fig.1.14                                                                             | Full-bridge boost converter with current-blocking diodes proposed in [14]                                                                                                                                                                                                                   | 22 |  |

| Fig.2.1                                                                              | The auxiliary circuit used in the proposed converter                                                                                                                                                                                                                                        | 26 |  |

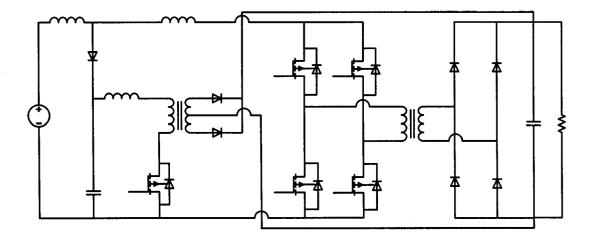

| Fig.2.2                                                                              | Proposed ZCS full-bridge boost converter                                                                                                                                                                                                                                                    | 27 |  |

| Fig.2.3                                                                              | Voltage and current waveforms for different circuit components of a boost                                                                                                                                                                                                                   | 33 |  |

|                                                                                      | converter with proposed auxiliary circuit operating in steady state                                                                                                                                                                                                                         |    |  |

| Fig.2.4                                                                              | (a) Current flow in Mode 0 (b) Current flow in Mode 1 (c) Current flow in Mode 2                                                                                                                                                                                                            | 34 |  |

| Fig.2.4                                                                              | (d) Current flow in Mode 3 (e) Current flow in Mode 4 (f) Current flow in Mode 5                                                                                                                                                                                                            | 35 |  |

| Fig.2.4                                                                              | (g) Current flow in Mode 6 (h) Current flow in Mode 7 (i) Current flow in Mode 8                                                                                                                                                                                                            | 36 |  |

| Fig.3.1                                                                              | Current flow in mode 1                                                                                                                                                                                                                                                                      | 39 |  |

| Fig.3.2                                                                              | Current flow in mode2                                                                                                                                                                                                                                                                       | 40 |  |

| Fig.3.3                                                                              | Current flow in active part of auxiliary circuit in mode2                                                                                                                                                                                                                                   | 40 |  |

| Fig.3.4                                                                              | Reduced equivalent circuit of the auxiliary circuit in mode2                                                                                                                                                                                                                                | 41 |  |

| Fig.3.5                                                                              | Current flow during mode 3                                                                                                                                                                                                                                                                  | 42 |  |

| Fig.3.6                                                    | Reduced equivalent circuit of mode 3                                                                 | 43 |  |  |

|------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----|--|--|

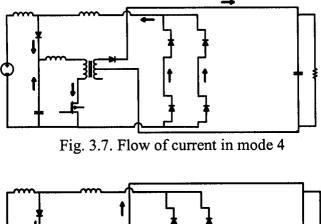

| Fig.3.7                                                    | Flow of current in mode 4                                                                            | 43 |  |  |

| Fig.3.8                                                    | Current flow in mode 5                                                                               | 43 |  |  |

| Fig.3.9                                                    | Current flow in mode 7                                                                               | 46 |  |  |

| Fig.4.1                                                    | PWM DC-DC boost converter with the proposed auxiliary circuit                                        | 50 |  |  |

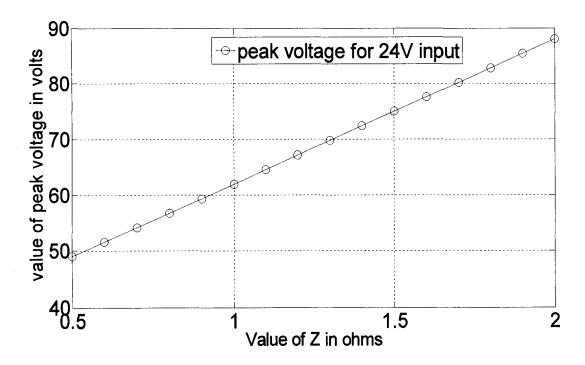

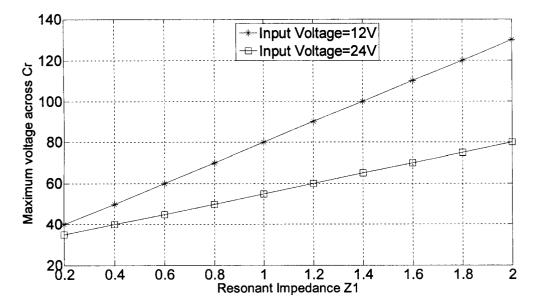

| Fig.4.2                                                    | Variation of capacitor $C_r$ Peak voltage for different values of $Z_1$                              | 57 |  |  |

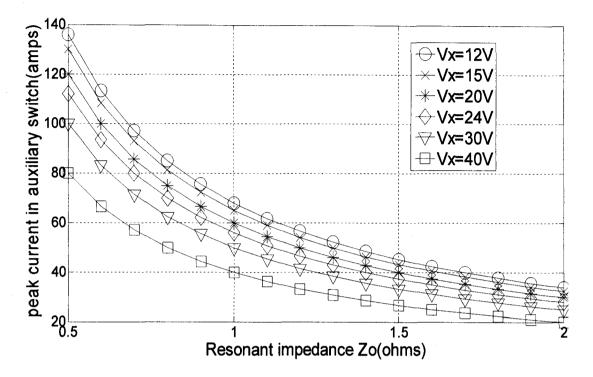

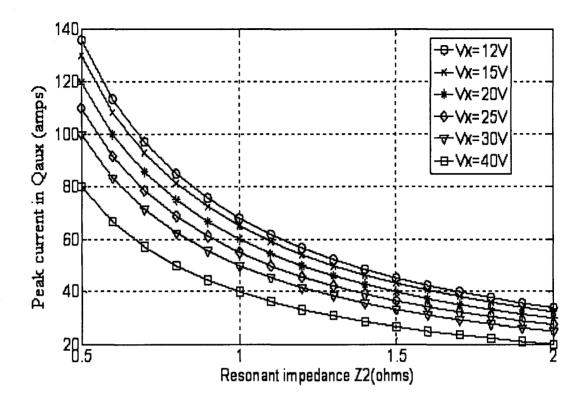

| Fig.4.3                                                    | Variation of Peak current in auxiliary switch for different values of $Z_o$                          | 59 |  |  |

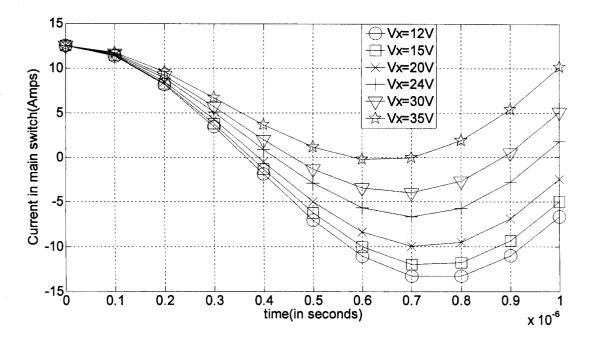

| Fig.4.4                                                    | Variation of the duration in which bridge switch currents reduce to zero and go                      | 61 |  |  |

|                                                            | negative during Modes 3-5 for different values of $N_x$                                              |    |  |  |

| Fig.4.5                                                    | Variation of the duration in which bridge switch currents reduce to zero and go                      | 61 |  |  |

|                                                            | negative during Modes 3-5 for different values of $N_x$                                              |    |  |  |

| Fig.4.6                                                    | Maximum voltage across the auxiliary capacitor vs. resonance impedance of the                        | 66 |  |  |

|                                                            | circuit for input voltages of 12 and 24 Volts                                                        |    |  |  |

| Fig.4.7                                                    | Peak current in the auxiliary switch vs. Resonance impedance                                         | 68 |  |  |

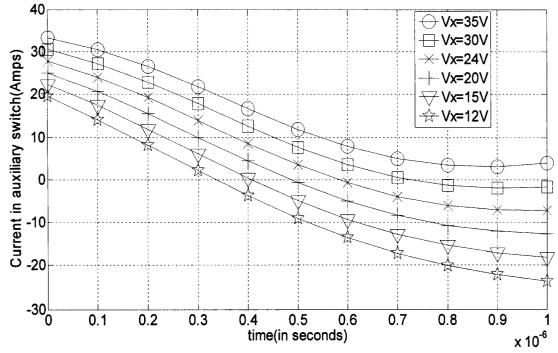

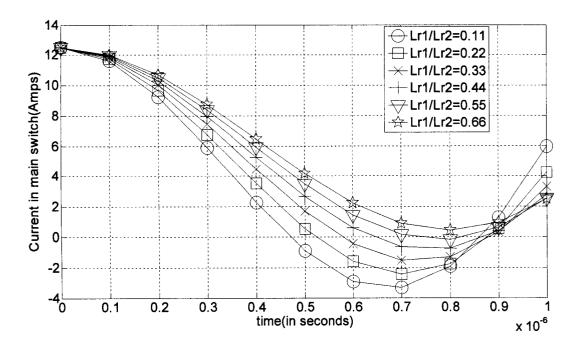

| Fig 4.8                                                    | (a) Current flowing through the main switches for different ratios of $L_{r1}/L_{r2}$                | 69 |  |  |

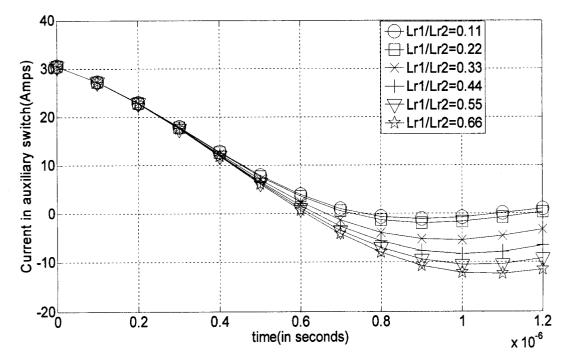

| Fig 4.8                                                    | (b) Current flowing in the auxiliary switch for different ratios of $L_{r1}/L_{r2}$                  | 69 |  |  |

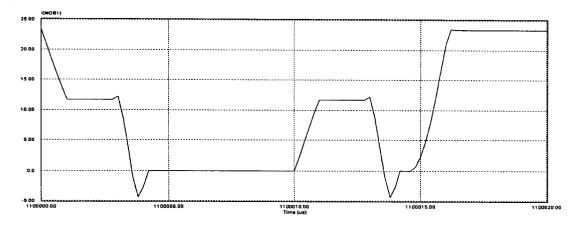

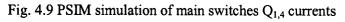

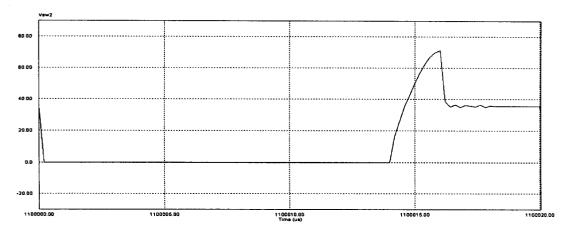

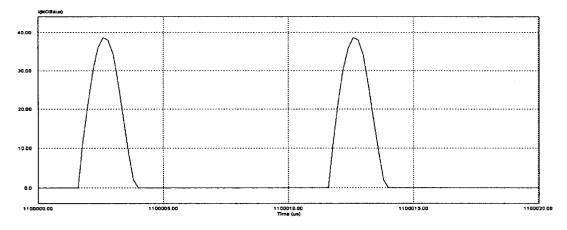

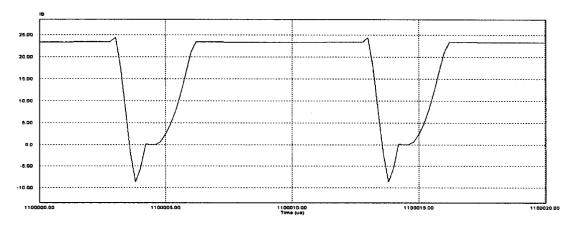

| Fig. 4.9                                                   | PSIM simulation of main switches Q <sub>1,4</sub> currents                                           | 71 |  |  |

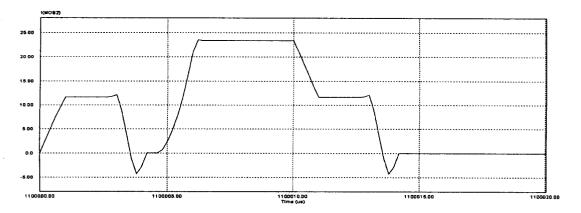

| Fig. 4.10 PSIM simulation of Main switches Q2,3 Currents71 |                                                                                                      |    |  |  |

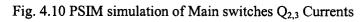

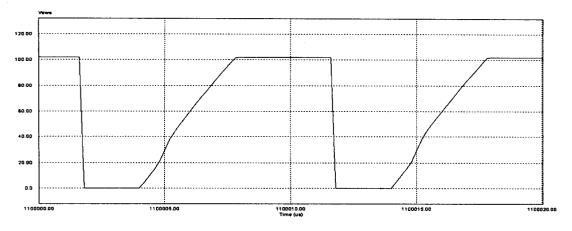

| Fig 4.11                                                   | <b>PSIM</b> simulation of the voltage across $Q_1$ and $Q_4$                                         | 71 |  |  |

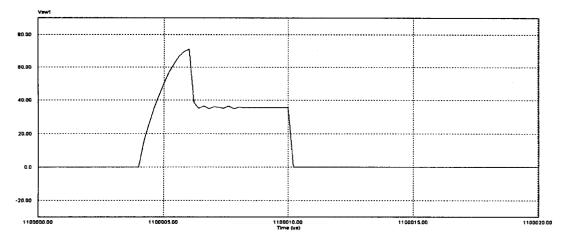

| Fig 4.12                                                   | PSIM simulation of the voltage across $Q_2$ and $Q_3$                                                | 72 |  |  |

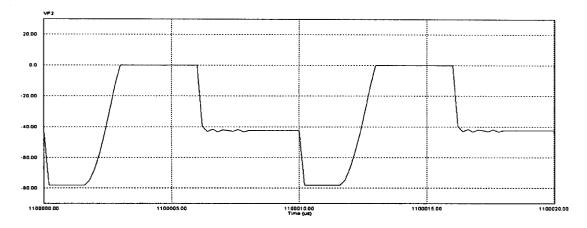

| Fig.4.13                                                   | PSIM simulation of resonant capacitor voltage                                                        | 72 |  |  |

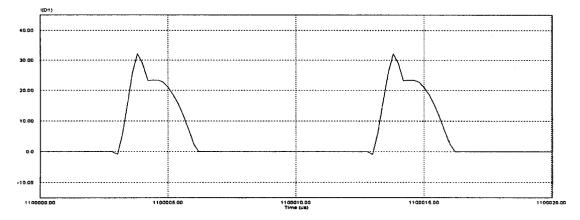

| Fig.4.14                                                   | PSIM simulation of auxiliary switch current                                                          | 72 |  |  |

| Fig.4.15                                                   | PSIM simulation of the voltage across Q <sub>aux</sub>                                               | 73 |  |  |

| Fig.4.16                                                   | PSIM Simulation of the bridge input current $I_{Lr1}$                                                | 73 |  |  |

| Fig.4.17                                                   | PSIM simulation of auxiliary diode current                                                           | 73 |  |  |

| Fig.4.18                                                   | PSIM simulation of the auxiliary diode voltage                                                       | 74 |  |  |

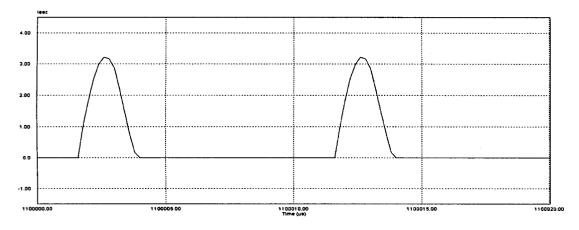

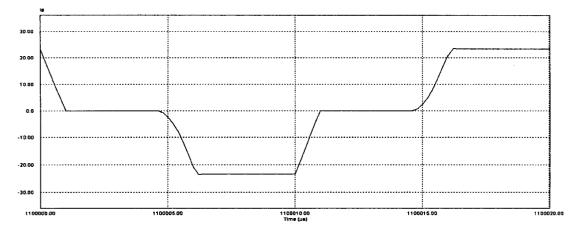

| Fig.4.19                                                   | PSIM simulation of the auxiliary transformer secondary current                                       | 74 |  |  |

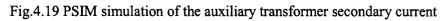

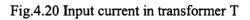

| Fig.4.20                                                   | Input current in transformer T                                                                       | 74 |  |  |

| Fig.5.1                                                    | Experimental prototype boost converter circuit with the proposed Auxiliary circuit                   | 78 |  |  |

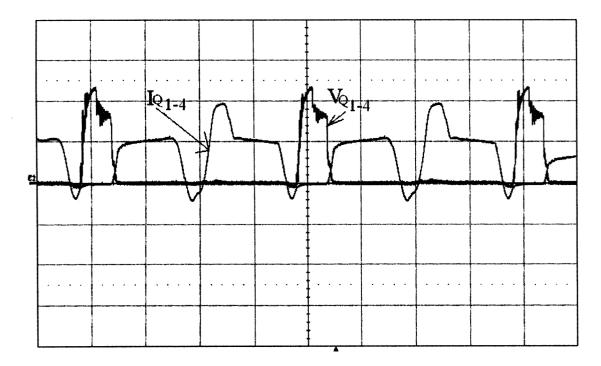

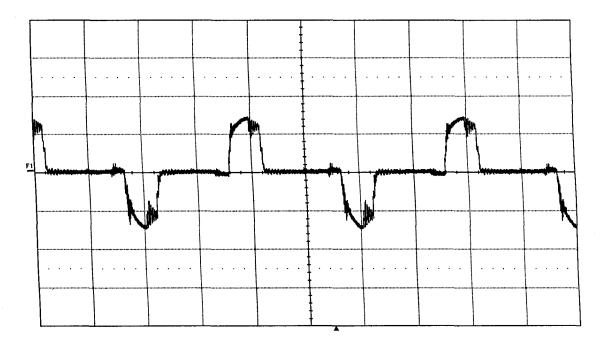

| Fig.5.2                                                    | Main Switches Q <sub>1-4</sub> Current and Voltage waveforms: (V: 30V/div, I: 15Amps/div, t:5µs/div) | 78 |  |  |

and internet

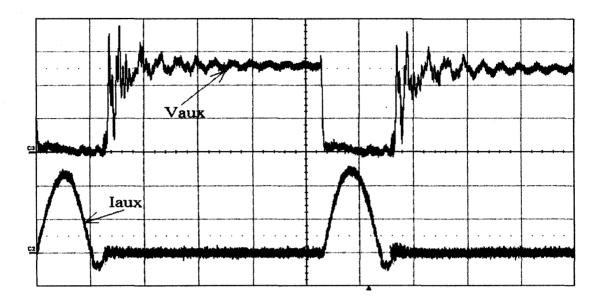

| Fig.5.3 | Current and voltage in auxiliary switch over one switching period (V: $30V/div$ , I: 15A/div, t:2 $\mu$ s/div)                          | 79         |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------|------------|

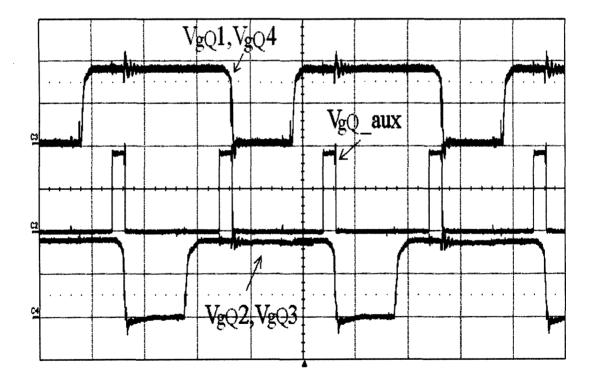

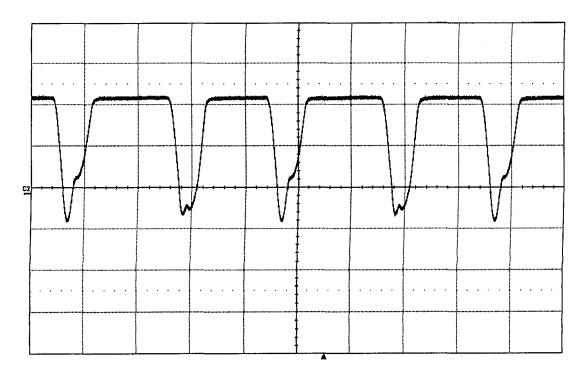

| Fig.5.4 | Gate pulses of the main and the auxiliary switches (V: 10V/div, t: $5\mu$ s/div)                                                        | 7 <b>9</b> |

| Fig.5.5 | Transformer Primary Voltage Waveform (V: 50V.div, t:5 µs/div)                                                                           | 80         |

| Fig.5.6 | Bridge input current I <sub>Lr1</sub> (I: 10A/div, t: 5 µs/div)                                                                         | 80         |

| Fig.5.7 | Efficiency measurements for the proposed converter and the conventional hard switching converter with 24V input and varying output load | 84         |

## NOMENCLATURE

| AC     | Alternative Current                               |

|--------|---------------------------------------------------|

| EMI    | Electromagnetic Interference                      |

| ESR    | Equivalent Series Resistor                        |

| DC     | Direct Current                                    |

| LC     | Inductor and Capacitor                            |

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor |

| PFC    | Power Factor Correction                           |

| PWM    | Pulse Width Modulation                            |

| SSC    | Soft-Switching-Cell                               |

| UPS    | Uninterruptible Power Supply                      |

| ZCS    | Zero Current Switching                            |

| ZVS    | Zero Voltage Switching                            |

| ZVT    | Zero Voltage Transition                           |

### **Chapter 1**

### **1.1 General Introduction**

#### **1.1.1 Power Electronics**

It is generally the task of power electronics to convert the electric power available from a power source to the form best suited for the user loads, and some sort of power processor or converter is required to serve as an interface between power source and load. The load may be ac or dc, single-phase or three-phase, and may or may not require transformer isolation from the power source. The power source could be a single-phase or three-phase ac source with line frequency of 50 or 60 Hz; it can be an electric battery, a solar panel or a commercial power supply. This source feeds the input of the power converter, which converts the power to the required form. The converter can be an ac-dc converter, a dc-dc converter, a dc-ac converter or an ac-ac converter.

Power converters typically consist of semiconductor devices such as transistors and diodes, energy storage elements such as inductors and capacitors, and some sort of controller to regulate the output voltage. Transistor type devices like BJTs (Bipolar Junctions Transistors), MOSFETs (Metal Oxide Silicon Field Effect Transistors) and IGBTs (Insulated Gate Bipolar Transistors) are used as switches in power electronic converters and are made to operate as switches that are either fully on or fully off at any given moment in time. These devices can be operated at higher switching frequencies than thyristor based devices, which helps reduce converter size. While BJTs and MOSFETs are basic devices, IGBTs are hybrid devices that have an insulated gate like a MOSFET but a conduction region that is the same as a BJT.

BJTs were used as switches in SMPS (Switch Mode Power Supplies) in the late 1970's-early 1980's, but since they are current-controlled devices, they are no longer used in SMPS where switches need to be turned on and off at very high frequencies in the kHz range. The MOSFET, being a charge controlled device, is faster than a BJT. When turned on, a MOSFET is equivalent to a resistance between its source and drain ( $R_{DS,on}$ ), while the BJT when fully on is equivalent to a voltage source equal to the saturation voltage between collector and emitter ( $V_{CE,sat}$ ). Thus the conduction losses in MOSFETs are proportional to the square of the on-state current that it is conducting while these losses in a BJT is proportional to the on-state current it is conducting.

The IGBT is a hybrid device that incorporates an insulated gate so that it turns on like a MOSFET and conducts like a BJT in saturation, hence the name IGBT. The IGBT undergoes a MOSFET type turn on, faster than a conventional BJT but its turn off is dependent on the minority carriers present in it during its on state (i.e it undergoes a turn off similar to that of a BJT and has a current tail during its turn off). The IGBT is therefore faster than a conventional BJT but slower than a MOSFET.

MOSFETs are used for lower power applications (typically a few kilowatts) and have lower current and lower voltage ratings (typically a few hundreds of volts) but

higher frequency well in a range of hundreds of kHz while the IGBT is used in higher power applications, they have high voltage and current ratings, but operate at lower frequencies (up to 100kHz).

IGBTs and MOSFETs are widely used in Power Electronic applications such as high frequency inverters used at the front ends of high efficiency ac motor drives, high and very high frequency dc-dc converters, power factor correction modules etc. Diagrams of a N-P-N IGBT and a N-channel MOSFET are shown in Fig.1.1.

Fig.1.1 (a) Schematic diagram of an IGBT. (b) Schematic diagram of a power MOSFET.

## 1.1.2 High Switching Frequency Operation in Power Electronic Converters

The size of the energy storage components of a power electronic converter, such as inductors (L) and capacitors (C), accounts for much of the overall size of the converter. These components are needed to store and transfer energy from the input power supply to the output load in the converter. Their values depend on the frequency that the converter switch is turned on and off. As the switching frequency is increased, the values of the inductors and capacitors decrease and so do their physical size and weight; therefore the higher the converter switching frequency, the smaller is the converter size.

Higher switching frequency operation, however, results in increased switching losses and Electro Magnetic Interference (EMI) noise emissions, which are described in the next section. Problems associated with switching losses and EMI caused by sudden switching transitions can offset the advantages achieved by operating a converter with a high switching frequency.

#### **1.1.3 Losses in Semiconductor Switches**

The semiconductor switches used in power converters are not ideal and are a source of energy losses. The main losses that are associated with these switches are conduction losses and switches losses, which will be described in more detail below.

#### a) Conduction losses

The conduction losses of MOSFETs are due to their behavior as a resistor when fully on - the resistance being equal to  $R_{DS,on}$ , the on state drain to source resistance. The conduction losses of an IGBT are related to the amount of current flowing in the device and  $V_{CE,sat}$ , the saturation voltage between collector and emitter.

#### b) Switching losses

In a real semiconductor switch, the switch voltage or switch current do not go to zero instantaneously at the instant of turn-on or turn-off. There is a duration of time during any switching transition (i.e. switch turn-on and turn-off) when there is both voltage across and current through the switch. The corresponding power loss during each switching instant is the overlapped area of the switch current and voltage waveforms at the instant of turn-on or turn-off of the switch. Since the average power is energy divided by the period, higher switching frequencies lead to higher switching losses. Sharp and sudden switching transitions are also sources of electromagnetic interference (EMI) noise that can affect the performance of a converter and/or other surrounding electrical equipment.

Both the IGBT and MOSFET have anti-parallel body diodes. A MOSFET has a much higher output capacitance between its drain and source than that between collector and emitter of an IGBT. This output capacitance charges up to the off state voltage that the MOSFET is subjected to while the IGBT has a current tailing after it is actually turned off.

In a MOSFET, the main switching losses are caused by the charging and discharging of the output capacitance to and from the off state voltage that the MOSFET is subjected to, while the tailing of current is the primary cause of switching losses in IGBTs. Turning on and turning off the power electronic switches with such switching losses is known as "hard switching". Fig. 1.2 shows the hard switching of power electronic switches in a circuit and the power losses associated with doing so.

Fig. 1.2(a) shows a power electronic switch  $S_1$  that conducts current  $i_{sw}$  when turned on; when turned off the voltage across it is  $V_0$ . Fig. 1.2(b) shows the typical current and voltage graphs of the switch  $S_1$  during a whole switching cycle. At  $t_0$ , the driving pulse of  $S_1$  is removed so that it gets turned off.  $S_1$  takes time  $t_{off}$  to turn off fully. During this time, due to the overlap of the current and voltage waveforms, there occurs a turn off loss represented by the area under the graph  $P_{off}$ . At  $t_1$ , the driving pulse is applied to the switch  $S_1$  so that it gets turned on. The switch  $S_1$  takes time  $t_{on}$  to get turned on. During this time  $t_{on}$ , due to overlap of the current and voltage waveforms of S<sub>1</sub>, there occurs a turn-on loss represented in Fig. 1.2(b) by P<sub>on</sub>.

#### 1.1.4 Diode Reverse-Recovery Current

In addition to semiconductor switches, power electronic converters also contain diodes. A diode is a semiconductor device that allows current to flow in only one direction, from its anode to its cathode, but does not allow current to flow in the negative direction, from its cathode to its anode. An ideal diode will not conduct any negative current, regardless of whatever negative voltage is placed across it, as long as this voltage does not exceed its maximum rated voltage. In reality, however, whenever the current flowing through a diode is decreased to zero, it may momentarily become negative before finally becoming zero, as shown in Fig 1.3.

This negative current is referred to as reverse-recovery current in the power electronics literature since it flows through the device during the time  $t_{rr}$  needed by the diode to "recover" from its previous current conduction state. The reverse-recovery current can lead to power losses in the diode and also creates electromagnetic interference (EMI) noise. Fast-recovery diodes with short reverse recovery times ( $t_{rr}$ ) are therefore widely used in high-frequency converters.

Fig.1.3. Reverse recovery current in a diode.

#### 1.1.5 Soft Switching

The problems of switching losses and EMI associated with hard-switching converter operation can be reduced by using soft-switching. The term "softswitching" in the power electronics literature refers to various techniques where the switching transitions are made to be more gradual to force either the voltage or current to be zero while the switching transition is being made. EMI is reduced by soft-switching because the switching transitions from on to off and vice versa is gradual and not sudden. Switching losses are reduced since the power dissipated in a switch while a switching transition made is proportional to the overlap of the voltage across the switch and the current flowing through it.

Soft-switching forces either the voltage or the current to be zero during the time of transition; there is therefore no overlap between voltage and current and therefore (ideally) no switching loss. There are, therefore, two types of soft-switching: zerovoltage switching (ZVS) and zero-current switching (ZCS). Although there are many ZVS and ZCS techniques, there are general principles associated with each type.

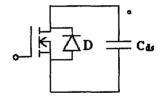

For power converters operating with high switching frequencies, the MOSFET is the semiconductor device that is most commonly used. The circuit symbol for a MOSFET is shown in Fig.1.4, along with an anti-parallel diode (which is the body diode that is internal to the device) and a capacitor  $C_{ds}$  that is across the device's drain and source.  $C_{ds}$  usually consists of an internal capacitance associated with the device and an additional external capacitor. The MOSFET can turn on with ZVS if it is somehow ensured that current is flowing through the body diode to clamp the drainsource voltage to zero just before turn-on. The MOSFET can turn off with ZVS because  $C_{ds}$  prevents the voltage from rising abruptly as the device is turned off.

Fig.1.4 ZVS MOSFET implementation

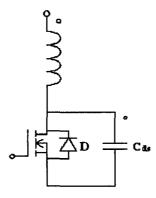

A MOSFET can be made to operate with ZCS if an inductor is added in series to it as shown in Fig. 1.5. The MOSFET can turn on with ZCS because the inductor limits the rise in current so that the current flowing through the MOSFET is almost zero as the device is being turned on. The MOSFET can turn off with ZCS if a negative voltage is somehow impressed across the inductor-MOSFET combination so that current falls to zero at a gradual rate due to the inductor.

Fig.1.5 ZCS IGBT implementation.

Although both ZVS and ZCS operations can reduce the switching losses of a MOSFET, ZVS is preferred because ZVS can substantially reduce the losses caused by the discharging of  $C_{ds}$  into the device when it is turned on whereas ZCS cannot.

It should be noted that although soft-switching can reduce switching losses, conduction losses that exist when current flows through a MOSFET/IGBT/ Diode will still exist.

#### **1.2 DC-DC Converters**

Dc-dc converters convert an available unregulated dc input voltage into a regulated dc output voltage of a different magnitude and/or polarity as required by a particular load. Most dc-dc converters are switch-mode converters that operate with active semiconductor devices like MOSFETs and IGBTs, acting as on-off switches. These switches are required to undergo repetitive and periodic turn on and turn off. The output dc voltage in such converters are dependent on the duty cycle D (<1)

which is defined as the length of time that the switch is on  $(t_{on})$  over the duration of the switching cycle  $(T_{sw}=1/f_{sw})$ .

$$D = t_{on}/T_S$$

(1-1)

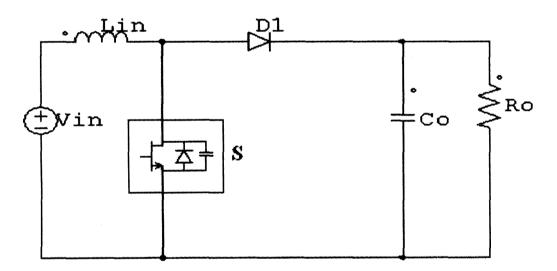

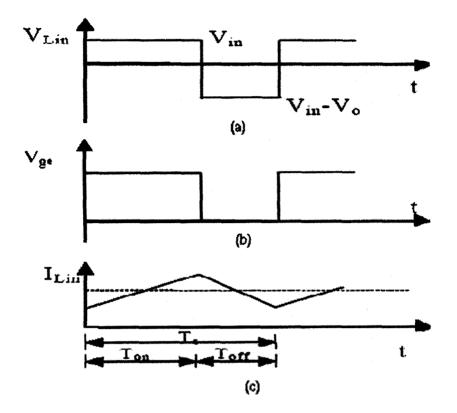

The two most basic types of dc-dc converters are the buck converter (Output voltage is a stepped down value of the input voltage) and boost converter (Output voltage is a stepped up value of the input voltage). Other types of dc-dc converters are buckboost, Cuk, Sepic and Zeta etc. The circuit diagram of a boost converter is shown in Fig.1.6 along with the typical voltage and current waveforms in Fig1.7.

Fig.1.6 A dc-dc boost converter

The converter shown has a MOSFET as the power electronic switch since it is best suited for high switching frequency converters. In steady state, after the switches are turned on, the whole input voltage is applied across the input inductor  $L_{in}$  and it stores up energy. When the switches are turned off, a negative voltage equal to  $(V_{in} - V_o)$  is applied across the inductor and the energy stored in the inductor is delivered to the output capacitance  $C_0$ . The steady state output voltage of the boost inductor must always be greater than the input voltage as the ratio of the output to input voltage is:

$$\frac{V_o}{V_{in}} = \frac{1}{1 - D}$$

(1-2)

In order to operate the MOSFET switches in the boost converter, a periodic pulse ( $V_{ge}$ ) such as shown in Fig.1.7(b) must be applied between the gate(g) and the emitter(E) of the device through a drive circuit. The MOSFET is on when the pulse  $V_{ge}$  is high and off when it is low. Since  $T_{on} = DT_{sw}$ , the duty cycle of the converter and hence the ratio of the output to input voltage, is determined by the width of the pulse  $V_{ge}$  so that it is the pulse width that is ultimately used to control and regulate the output voltage. This method of controlling the converter output, which is frequently used, is known as pulse width modulation control or PWM control.

Fig.1.7 a)Waveform of the voltage across input inductance L<sub>in</sub> of a boost converter.

b)Waveform of the voltage at the gate of the switch in a boost converter.

c) Waveform of current through the input inductance in a boost converter.

#### **1.3 Full-Bridge Boost Converters**

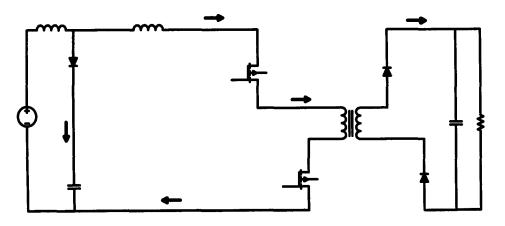

Full-bridge boost converters like the one shown in Fig.1.8 are very attractive for applications where an output dc voltage that is considerably larger than the input voltage is needed. Such applications include fuel cell power conversion, medical power supplies, and power supplies for electrostatic applications. These converters are essentially boost converters that contain a step-up transformer so that they can do additional voltage "boosting" without the very large duty ratios (D) needed with the boost converter shown in Fig.1.8.

The converter operates like a boost converter as the current in inductor Lin is increased whenever switches from the same leg are on and it is decreased whenever a pair of diagonally opposed switches is on as energy is transferred to the output through the transformer and the output diodes. It should be noted that there must always be a path for the input inductor current to flow through the full bridge switches at all times.

Fig.1.8 Current-fed PWM full-bridge boost converter

A full-bridge boost converter can be implemented with either zero-voltage switching (ZVS) or zero-current switching (ZCS) depending on the application. ZVS is implemented in applications where the input voltage is high, the input current is low or medium, and switch turn-on switching losses are dominant. ZCS is implemented in applications where the input current is high (regardless of what the input voltage is) and conduction losses are dominant. The focus of the thesis will be on ZCS full-bridge boost converters.

#### **1.4 Literature Review**

The first ZCS full-bridge converters that were proposed were resonant converters [11], [17], [18]. ZCS resonant converters use an inductive – capacitive (L-C) circuit to create oscillatory (usually sinusoidal) switch current waveforms so that ZCS turn-on and turn-off conditions can be achieved for the power switches. The converter shown in Fig. 1.9 is the conventional full-bridge boost converter with added L and C component to create the resonant circuit.

Most resonant converters, however, suffer from high peak switch voltage or current stresses in comparison to conventional PWM converters. This leads to higher conduction losses and higher voltage and current ratings for the power switches and other circuit components. Another disadvantage is that most resonant converters operate with variable switching frequency control (the output voltage is controlled by varying the converter switching frequency). If operation over a wide range in input voltage and output load is required, most resonant converters must operate with a wide switching frequency range. This makes it difficult to optimize the design of the converter and its control.

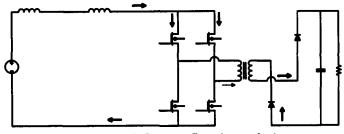

In the circuit proposed in [11] the converter is a fixed frequency resonant ZCS current fed converter (Fig.1.9) or a variable frequency resonant converter in [17]-[18] that generates a considerable amount of circulating current in the full bridge so that the switches can turn off with ZCS. Examples of variable frequency resonant converters are shown in Fig.1.10 (a),(b). It should be noted that the circulating

current is not transferred to the load and does little but add to the conduction losses of the converter. Although the converter is more efficient than it would be if ZCS was not implemented, the gains in efficiency are not as much as what they could be due to these losses.

Fig.1.9 Fixed frequency resonant ZCS current fed converter proposed in [11]

Fig.1.10 (a)

Fig.1.10 (b)

Fig.1.10 (a), (b) Variable frequency resonant ZCS current fed converter

Most recent soft-switched full-bridge boost converters can be classified as being resonant-transition converters, and have the advantages of conventional PWM converters and resonant converters. They use an additional or auxiliary circuitry that is not a part of the main power circuit to help the main converter switch turn on and off with ZCS. This auxiliary circuit typically consists of an active power switch and passive elements such as diodes, inductors, and capacitors. The operation of the auxiliary circuit only occurs during the turn-on and turn-off of the main converter switch and only a very small portion of switching cycle.

To realize ZCS for the main switch, the basic idea behind this type of auxiliary circuit is to activate the circuit by turning on an auxiliary switch placed properly in the circuit for a small fraction of the switching cycle and just before the semiconductor switch has to be turned off. By activating the circuit, a capacitor placed in the circuit is forced to undergo resonance with some inductance properly

placed with the switch so that the capacitor, under resonance, creates a counter voltage across the inductor-switch pair thus forces the current in the switch to be reduced to zero before the pulse at the gate of the switch is removed. Eventually the switch will be turned off with zero current.

Since the auxiliary circuit is active for only a small portion of the switching cycle, the circuit behaves almost exactly like a conventional PWM converter, but with smoother voltage and current waveforms especially during switching transitions. The components in the auxiliary circuit handle a fraction of the power than the main power circuit components must handle, thus allowing small components to be used. This is especially true of the auxiliary switch, which can be a device with ratings smaller than that of the main power switch and therefore operate with fewer switching losses, so that whatever new switching losses that are created by the auxiliary switch. Numerous auxiliary circuits for ZCS-PWM full-bridge converters have been proposed in the power electronics literature [12]-[16].

One of the basic and early versions of such a circuit is shown in Fig.1.11. The auxiliary circuit is simple as it incorporates only one extra inductor and a capacitor and one auxiliary switch, but its drawback is the high current peak in main switches. This high current peak in the main switches calls for the need of switches with higher current ratings, and such switch tends to have higher conduction losses. Also high current peaks tend to create additional unwanted conduction losses. Moreover, due to the resonant capacitor charging to as high as twice the output voltage during the

operation of the auxiliary circuit, there is a need for a resonant capacitor with bigger size since a capacitor's physical size is dependent on its voltage ratings.

Fig.1.11 ZCS full-bridge PWM boost converter

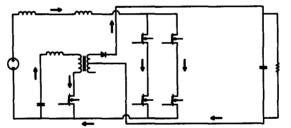

In some cases the converter uses an active auxiliary circuit that is connected in parallel to the full-bridge and used to divert current away from the switches in the bridge before they are to be turned off to realize ZCS turn off of devices [13]-[18]. This circuit is activated just before any switches are to be turned off and is deactivated shortly afterwards. Since the circuit is active for only a short length of time, there is less circulating current compared to the fixed frequency resonant converters, but this current is still significant. All the energy from this current is trapped in the primary side of the converter and it contributes to losses. Examples of such converters were proposed in [15] and [16] and are shown in Fig.1.12 (a), (b) respectively. Both converters have an auxiliary circuit connected to the full-bridge in parallel.

Fig.1.12 Current-fed converters with parallel auxiliary circuit (a) [16] (b) [15]

The additional circulating current also contributes to increased peak current stresses in the full-bridge switches as these switches must conduct the current that they are supposed to conduct, to feed the load and the circulating current. Devices that can withstand higher peak current stresses than those found in conventional boost full-bridge converters are needed as the converter switches [13]-[16].

Fig.1.13 shows the circuit proposed in [13]. In the paper, high rated switches have been used for the experimental results, so the switches can stand the current peak that occurs because of the additional circulating current.

Fig.1.13. Current fed full-bridge converter proposed in [13]

In some other proposed converters, diodes are placed in series with the switches so that current does not flow through the body-diodes of the switches and circulating current is reduced [14]. The circuit proposed in [14] is shown in Fig.1.14. Although conduction losses are increased, they may be smaller than what they would be if the diodes were not added, but this is at the cost of the additional diodes. Some converters avoid using diodes by using reverse blocking IGBTs [12], but they are more expensive than regular IGBTs and not appropriate for low voltage input applications.

Fig.1.14. Full-bridge boost converter with current-blocking diodes proposed in [14]

Other drawbacks that can be found in previously proposed ZCS full-bridge boost converters include the need for a high side driver [15] for the auxiliary circuit switch(es), which makes the driving of this switch(es) more complicated and the appearance of voltage spikes and/or the significant voltage ringing that can appear across the main converter switches [11]-[18]. The later is due to the output capacitances of the switches resonating with the leakage inductance of the main transformer during their turn off. The spikes and ringing will appear across the secondary diodes as well. This creates a need for higher voltage rated devices, which will increase the cost and the losses in the converter.

#### **1.5 Thesis Outline**

This thesis is organized as follows:

In Chapter 2, a new auxiliary circuit that allows the main power switches in ZCS-PWM full-bridge dc-dc boost converters to operate with soft-switching is proposed and its operation is described.

In Chapter 3, the circuit analysis of a ZCS-PWM full-bridge dc-dc boost converter operating with the proposed auxiliary circuit is presented for the various modes of operation that the converter goes through during a switching cycle, as described in Chapter 2. Important mathematical equations describing voltages and currents of different circuit components during the modes of operation are derived.

In Chapter 4, the conditions that ensure the soft switching of the main switches in the converter are derived with the help of the mathematical equations derived in Chapter 3. Also, characteristics curves showing the behavior of the converter with respect to the variation of different passive components are presented. An experimental prototype is designed using these characteristic curves. Converter component values are chosen using a design procedure that will be presented and demonstrated with an example.

In Chapter 5, experimental voltage and current waveforms for the prototype designed in Chapter 4 are presented to validate the concept of the proposed auxiliary circuit. Efficiency graphs for a full-bridge boost converter with and without the proposed auxiliary circuit are presented to demonstrate the effectiveness of the circuit in increasing converter efficiency.

In Chapter 6, the contributions and conclusions of this thesis are presented and suggestions for future work are given.

•

### **Chapter 2**

## A New ZCS-PWM Full-Bridge Boost Converter

#### **2.1 Introduction**

It was seen in Chapter 1 that previously proposed auxiliary circuits applied to ZCS-PWM full bridge converters introduce additional current and voltage stresses on the converter devices. These stresses can cause additional conduction losses in the devices that can reduce the savings of energy realized by the soft-switching of the main switches. For example, the circulating energy that exists when the auxiliary circuit of some ZCS-PWM converters is operating is trapped in the circuit and creates additional losses.

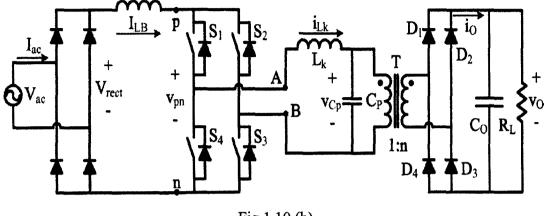

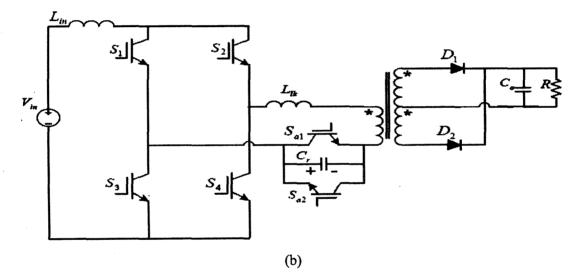

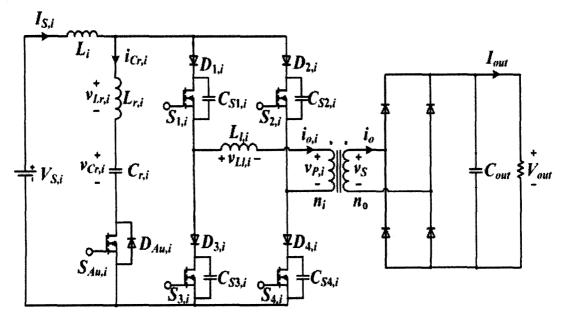

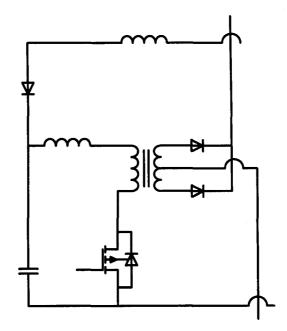

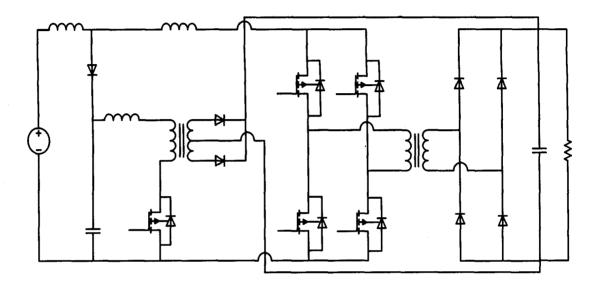

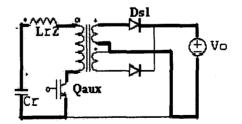

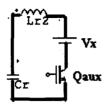

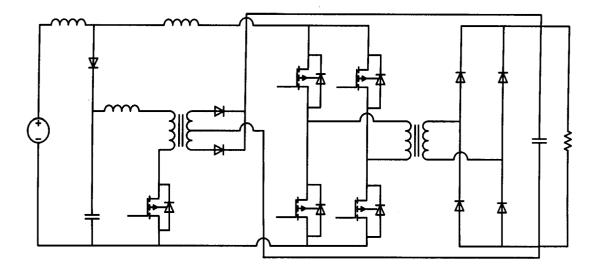

With these issues in consideration, the auxiliary circuit shown in Fig. 2.1 is proposed. The circuit consists of auxiliary diode  $D_{aux}$ , inductor  $L_{r2}$ , energy feed-forward transformer  $T_{aux}$ , auxiliary switch  $Q_{aux}$ , diodes  $D_{S1}$  and  $D_{S2}$  placed at the secondary and the tertiary windings of the transformer  $T_{aux}$  and inductor  $L_{r1}$  placed in series with the main switches  $Q_{1-4}$  (shown in Fig.2.2).

The main concept behind this auxiliary circuit is to add a transformer to create a counter voltage in the circuit to reduce the peak value of the resonating capacitor voltage ( $V_{Cr}$ ), which is the main cause of the increased peak current in the auxiliary switch. Clamping the primary of the energy feed-forward transformer with a suitable stepped down value of the output voltage imposes this counter voltage. Adding the transformer also creates a path to take out the circulating energy in the auxiliary

circuit and transfer to the output, thus increasing the overall efficiency of the converter. This energy feed-forward is accomplished by suitably connected diodes at the transformer secondary and tertiary windings.

Fig.2.1. The auxiliary circuit used in the proposed converter

The placement of the proposed auxiliary circuit in a ZCS-PWM dc-dc full-bridge boost converter is proposed in this section and shown in Fig. 2.2. The proposed converter is well-suited in low input voltage / high output voltage PWM dc-dc fullbridge boost converters. This auxiliary circuit is the most efficient when compared to several others implemented in a conventional PWM boost converter. Most other auxiliary circuits (i.e. [19]-[24]), however, cannot be adapted for use in ZCS-PWM isolated boost converters (i.e. fuel cell converters) due to their circuit structure or the fact that they create unwanted current and voltage stresses on the main devices and undergo high circulating current losses

Fig. 2.2. Proposed ZCS full-bridge boost converter

#### **2.2** Converter Operation

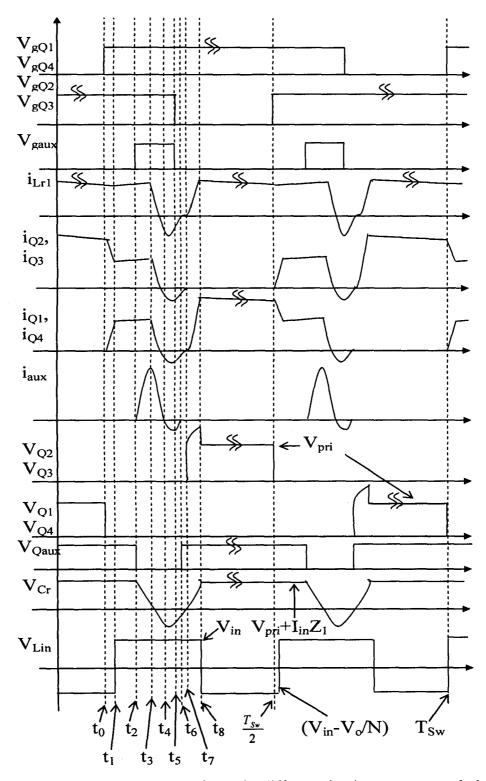

In this section, the steady state operation of the proposed full-bridge boost converter will be explained in terms of the different modes or phases that the converter undergoes over a steady-state switching cycle. These modes are distinct from each other in terms of flow of current and voltage across different circuit components. By steady state operation of the converter, it is implied that, at the beginning of each switching cycle, the components of the converter are at the same state with respect to their voltages and currents as they were in the previous switching cycle, or in other words, the voltage and current waveforms of all components of the converter are identical for every switching cycle in steady state.

The voltage and current waveforms of the different components of the converter during each mode over a switching cycle in steady state will be shown to illustrate the operation of the converter. These modes of operation are important for deriving mathematical equations through circuit analysis that will describe the steady state operation of the converter mathematically. These mathematical equations will be needed to derive the characteristics of the converter with respect to different circuit components and help in designing a prototype.

The following assumptions are made regarding different circuit components while analyzing the proposed boost converter topology:

- 1) Input boost inductor  $L_{r1}$  is large enough to be considered as a constant current source.

- Output capacitor C<sub>o</sub> is large enough to be considered as a voltage source equal to the desired output voltage.

- 3) All semiconductor switches are ideal *i.e.*, they have zero voltage drop across them while they are on and they have no output capacitance across them.

- 4) The recovery time of each diode is zero.

- 5) The energy feed-forward transformer is ideal *i.e* it has infinite magnetizing inductance, zero leakage inductance and no lossy components associated with it.

The boost converter with the proposed auxiliary circuit undergoes nine different modes of operation over one switching cycle at steady state. In the following section, different modes of operation of the boost converter along with the proposed auxiliary circuit are described:

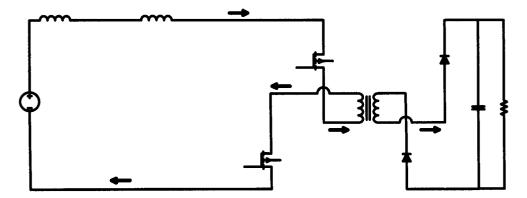

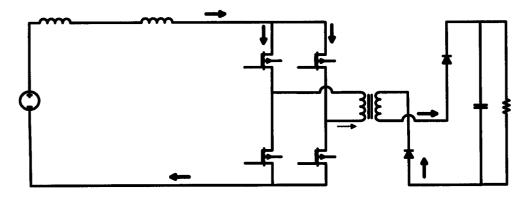

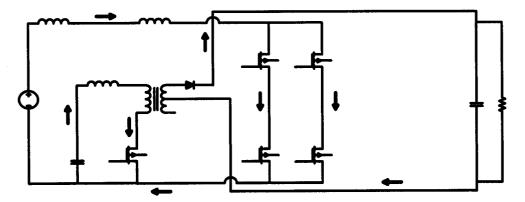

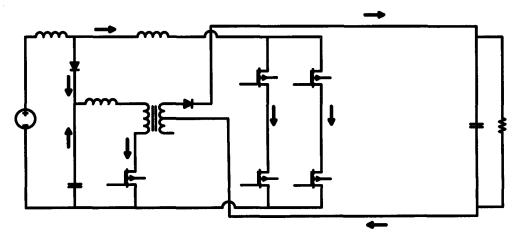

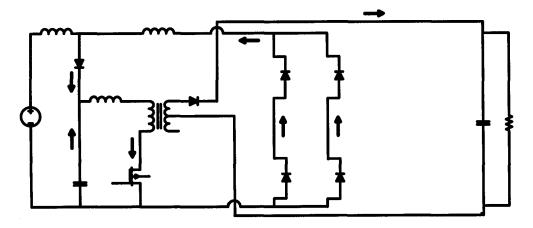

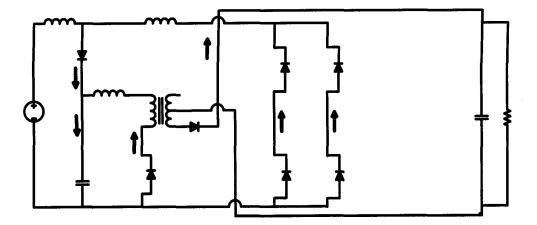

Mode 0 ( $t < t_0$ ) (Fig.2.4(a)): Input current I<sub>in</sub> flows through switches Q<sub>3</sub> and Q<sub>2</sub>, and energy is transferred to the load through diodes D<sub>2</sub> and D<sub>3</sub>.

Mode 1 ( $t_0 < t < t_1$ ) (Fig.2.4(b)): At time t = t<sub>0</sub>, both Q<sub>1</sub> and Q<sub>4</sub> are turned on. Due to the primary transformer leakage inductance, the transfer of current to these switches is gradual so that they turn on with ZCS, and some energy continues to be transferred to the output. Eventually, no current flows in the transformer primary except the magnetizing current (which is neglected here), and the dc bus is shorted with half of I<sub>in</sub> flowing through one full-bridge leg and the other half flowing though the other leg. Since the current splits between two legs of the bridge, losses will be half the case where only one leg is shorted.

Mode 2  $(t_1 < t < t_2)$  (Fig.2.4(c)): At t = t<sub>1</sub>, the auxiliary switch Q<sub>aux</sub> is turned on and C<sub>r</sub> begins to resonate with L<sub>r2</sub> and discharge. The auxiliary transformer primary voltage is clamped to  $V_x = V_0 \frac{N_1}{N_2}$  from time t<sub>2</sub> to t<sub>4</sub> and the secondary diode D<sub>s1</sub> is forward biased. Circulating energy from the auxiliary circuit is transferred to the

output during this time through  $T_{aux}$  and  $D_{s1}$ . This mode ends when the voltage of Cr (V<sub>Cr</sub>), reaches zero and diode  $D_{aux}$  turns on.

Mode 3 ( $t_2 < t < t_3$ ) (Fig.2.4(d)): At t = t<sub>2</sub>, the voltage across C<sub>r</sub> reaches zero and D<sub>aux</sub> starts to conduct as C<sub>r</sub> continues to resonate with L<sub>r2</sub> and the voltage across it becomes negative. This negative voltage appears across the dc bus and thus current begins to be diverted away from the full-bridge switches.

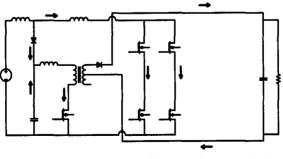

Mode 4 ( $t_3 < t < t_4$ ) (Fig.2.4(e)): At t = t<sub>3</sub>, the current through the main switches becomes zero and begins reversing direction by flowing through the body diodes of the switches. Switches Q<sub>2</sub> and Q<sub>3</sub> can be turned off softly at any time while current is flowing in their body diodes. Current in the auxiliary circuit is positive but decreasing.

Mode 5 ( $t_4 < t < t_5$ ) (Fig.2.4(f)): At t = t<sub>4</sub>, the body diode of Q<sub>aux</sub> starts conducting and the switch can be turned off softly after this instant. During this mode, all the body diodes of all converter switches conduct current and the current coming out of the bridge flows through L<sub>r1</sub> and D<sub>aux</sub> while charging C<sub>r</sub>. Energy is transferred from the auxiliary circuit to the load through T<sub>aux</sub> and D<sub>s2</sub>.

Mode 6 ( $t_5 < t < t_6$ ) (Fig. 2.4(g)): At t = t<sub>5</sub>, the current in the body diode of Q<sub>aux</sub> goes to zero. During this mode, the voltage across C<sub>r</sub> increases in resonance with L<sub>r1</sub> while

the current flows through the body diodes of the full-bridge switches. At the end of this mode the voltage across  $C_r$  reaches  $V_{pri} = V_o/N$ .

*Mode* 7 ( $t_6 < t < t_7$ ) (*Fig.2.4(h*)): At t = t<sub>6</sub>, the current in the body diodes of the fullbridge switch becomes zero, and some input current starts to flow through L<sub>r1</sub>, Q<sub>1</sub> and Q<sub>4</sub>. The remaining input current continues to charge C<sub>r</sub> and the voltage across it rises. Energy begins to be transferred to the load through D<sub>1</sub> and D<sub>4</sub>. At the end of this mode the voltage across C<sub>r</sub> charges up to V<sub>Cr0</sub>.

Mode 8 ( $t_7 < t < t_8$ ) (Fig.2.4(i)): At t = t<sub>7</sub>, all the input current flows through the bridge and none through C<sub>r</sub>. The converter is in an energy transfer mode.

The proposed ZCS-PWM full-bridge boost converter has the following features:

- (i) The presence of a transformer in the auxiliary circuit provides a path for energy that would otherwise be trapped in the auxiliary circuit. Energy can be transferred to the output instead of contributing to conduction losses.

- (ii) The auxiliary circuit is adaptive as greater the energy that would otherwise be trapped in the circuit, greater the energy that is transferred to the output, since trapped auxiliary circuit energy is a cause of circulating current. This means that the converter can be made to operate with little additional circulating current regardless of whether it is operating with a light load or a heavy load. This property does not exist in most other ZCS-PWM full-bridge boost converters as

they have a considerable amount of circulating current when operating under light load conditions.

- (iii) Since the proposed converter has little additional circulating current regardless of load, it does not need additional diodes connected in series with the full bridge switches to prevent current flowing through their body diodes. There are therefore no conduction losses due to series blocking diodes unlike several other ZCS-PWM full-bridge boost converters.

- (iv) The peak current stress of the switches is the same as that of a switch in a conventional PWM boost full-bridge converter, as  $D_{aux}$  blocks any auxiliary circuit current from flowing into the full-bridge.

- (v) One of the drawbacks of a conventional current-fed full bridge converter is that it lacks a DC bus capacitor across the full bridge section so that there can be uncontrolled voltage spikes during turn off of the bridge devices owing to resonance between their output capacitance and leakage inductance which can damage the bridge devices. It can be seen from Fig. 2.3 that the full bridge switches do have an additional voltage stress in the form of a controlled voltage hump and not a voltage spike. The rise of this voltage hump is restricted by the size of  $C_r$ ,  $L_{r1}$  and  $L_{lk}$ . This allows lower rated devices to be used as the full bridge switches.

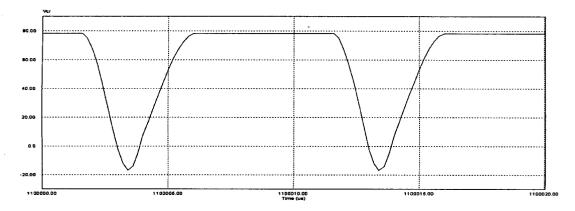

Voltage and current waveforms of different converter components are shown in Fig. 2.3 and the flow of currents in the circuit during a whole switching cycle is shown in Fig. 2.4(a) to Fig. 2.4(i).

32

Fig.2.3 Voltage and current waveforms for different circuit components of a boost converter with proposed auxiliary circuit operating in steady state.

Circuit diagrams showing current flow in different modes of operation:

Fig. 2.4(a) Current flow in Mode 0

Fig. 2.4(b) Current flow in Mode 1

Fig. 2.4(c) Current flow in Mode 2

Fig. 2.4(d) Current flow in Mode 3

Fig. 2.4(e) Current flow in Mode 4

Fig. 2.4(f) Current flow in Mode 5

Fig. 2.4(g) Current flow in Mode 6

Fig. 2.4(h) Current flow in Mode 7

Fig. 2.4(i) Current flow in Mode 8

#### **2.3 Conclusion**

In this chapter a new auxiliary circuit for ZCS-PWM full-bridge converters was proposed. The basic operation of a full-bridge boost converter with the proposed auxiliary circuit was shown along with the current and voltage waveforms of different circuit components during different stages or modes of operation of the converter in steady state over a switching cycle. From the discussions presented in this chapter it can be seen that the proposed boost converter operates as a PWM DC-DC boost converter except for the very small instant of time as compared to the whole switching cycle when the auxiliary switch is on facilitating ZCS turn-off of the main switches.

#### Chapter 3

### **Circuit Analysis of the Proposed Boost Converter**

### **3.1 Introduction**

In the previous chapter, the different modes of steady state operation of a fullbridge boost converter implemented with the proposed auxiliary circuit and operating over a switching cycle were described. In this chapter, an analysis of the boost converter is performed and key mathematical equations are derived based on these modes of operation. These equations are important for understanding the characteristic behavior of the converter with respect to the variation of certain key circuit component values and will help in designing a boost converter with the proposed auxiliary circuit.

## **3.2 Circuit Analysis**

The following assumptions are made regarding different circuit components while analyzing the proposed boost converter topology for analyzing the boost converter circuit:

1) The input inductor is large enough to be considered as a constant current source.

- 2) The output capacitor is large enough to be considered as a voltage source

- All semiconductor switches are ideal *i.e* while they are on, they have zero voltage drop across them and that they have no output capacitance across them

4) The reverse recovery time for each diode is zero.

- 5) The energy feedforward Transformer (T) is ideal *i.e.* it has infinite magnetizing inductance, zero leakage inductance and no lossy components associated with it.

- 6) From time  $t_2$  to  $t_4$  the auxiliary transformer primary winding is clamped to  $V_x = V_o (N_1 / N_2)$  and diode  $D_{S1}$  is forward biased, which allows the transfer of the circulating energy from the auxiliary circuit to the output to occur.

- 7) From time  $t_4$  to  $t_6$  the transformer primary is clamped to  $-V_x = -V_o (N_1 / N_2)$ and the diode  $D_{S2}$  is forward biased, which allows the transfer of the circulating energy from the auxiliary circuit to the output to occur.

The description of each mode of operation was presented in Chapter 2, and the reader is referred to this chapter for the detailed description of each mode.

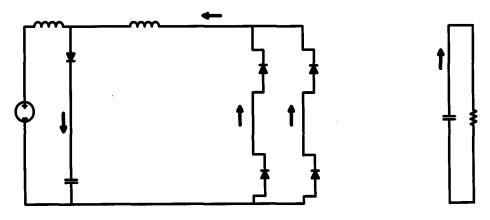

The equivalent circuit for Mode 1 is shown in Fig. 3.1. Based on this circuit, the following equation can be derived:

$$V_o N = L_{ik} \frac{di_{in}(t)}{dt}$$

(3-1)

where  $N = \frac{N_1}{N_2}$

Fig. 3.1 Current flow in mode 1

In this mode, the leakage current  $L_{ik}$  drops from  $I_{in}$  to zero. Integrating from time  $t_0$  to  $t_1$ ,  $Q_{1,4}$  switches current can be written as

$$I_{Q1-4}(t) = Iin - \frac{V_o N}{L_{ik}}(t-t_0)$$

for time  $t_0 < t < t_1$  (3-2)

The converter enters Mode 2 (t = t<sub>1</sub>) of operation when the auxiliary switch Q<sub>aux</sub> is turned on and C<sub>r</sub> begins to resonate with L<sub>r2</sub> and discharge. The transformer primary voltage is clamped to  $V_x = V_o \frac{N'_1}{N'_2}$  from time t<sub>2</sub> to t<sub>4</sub> and the secondary diode

D<sub>s1</sub> is forward biased.

The equivalent circuit diagram for this mode is shown in Fig. 3.2, which can be simplified in Fig 3.4.

Fig.3.2 Current flow in mode2

Fig.3.3 Current flow in active part of auxiliary circuit in mode2

Fig.3.4 Reduced equivalent circuit of the auxiliary circuit in mode2

Voltage  $V_{Cr}$  and current  $I_{Lr2}$  can be expressed according to the following equations:

$$V_{Cr}(t) = L_{r2} \frac{di_{Lr2}(t)}{dt} + V_{x}$$

(3-3)

$$i_{Lr2}(t) = i_{Cr}(t) = -C_r \frac{dV_{Cr}(t)}{dt}$$

(3-4)

$$V_{Cr}(t) = -L_{r2}C_{r}\frac{d^{2}}{dt^{2}} V_{Cr}(t) + V_{x}$$

(3-5)

The differential equation (3-5) has the following initial conditions:  $V_{cr}(0)$  is the initial capacitor voltage for this mode and  $V_{cr}'(0)$  is the initial time derivative of the capacitor voltage for this mode. Since the initial current in  $L_{r2}$  is zero, therefore equation (3-6) can be written as

$$\left[\frac{d}{dt}V_{\rm Cr}(t)\right]_{t=0} = -(1/C_{\rm r})\left[\frac{d}{dt}q_{\rm Cr}(t)\right]_{t=0} = (1/C_{\rm r})\left[i_{\rm Lr2}(t)\right]_{t=0} = 0$$

(3-6)

and the solution to this equation is

$$V_{Cr}(t) = V_x + (V_{Cr}(0) - V_x) \cos \omega_2 t$$

for  $t_2 < t < t_3$  (3-7)

From the initial conditions of Mode 2,  $i_{Lr2}(t)=i_{Cr}(t)$  for  $t_2 < t < t_3$  and

$$i_{Lr2}(t) = i_{Cr}(t) = -C_r \frac{d}{dt} V_{Cr}(t) = C_r (V_{Cr}(0) - V_x) \omega_2 \sin \omega_2 t$$

$$= [(V_{Cr}(0) - V_x)/Z_2] \sin \omega_2 t \text{ for } t_1 \le t \le t_2$$

(3-8)

where  $\omega_2^2 = 1/L_{r2}C_r$  and  $Z_2 = \sqrt{\frac{Lr^2}{C_r}}$  is characteristic impedance of the auxiliary circuit. Since this mode ends when the voltage across Cr is zero, the duration of this mode can be determined from equ.(3-7) to be

$$t_2 - t_1 = [\cos^{-1}(-V_x/(V_{Cr}(0) - V_x)]/\omega_2 = \gamma$$

(3-9)

so that

$$i_{Lr2}(t) = i_{Lr2}(t_4) = [(V_{Cr}(0) - V_x)/Z_2] \sin\omega_2 \gamma$$

(3-10)

At the end of Mode 2, since  $V_{Cr}(0) >> V_x$ , then  $\gamma \approx \pi/2$  according to equation (3-9) and (3-10) can be approximated as:

$$i_{Lr2}(t_4) \approx (V_{Cr}(0) - V_x)/Z_2$$

(3-11)

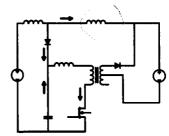

Mode 3 of the operation starts at  $t_2$  when  $D_{aux}$  starts conducting. The equations that define this mode also define Modes 4 and 5; this can be seen by considering the equivalent circuit diagrams for each mode. Fig 3.5 shows the equivalent circuit diagram of Mode 3 and the reduced equivalent circuit diagram for this mode is shown in Fig. 3.6. Similar diagrams are shown in Figure 3.7 and 3.8 for Modes 4 and 5.

Fig. 3.5 Current flow during mode 3

Fig.3.6 Reduced equivalent circuit of mode 3

Fig. 3.8. Current flow in mode 5

It can be seen from Figures 3.5 to 3.8 that the flow of current is not interrupted by any switching action so that it is continuous; therefore Modes 3-5 can be considered as a single mode of operation for the purpose of analysis.

By applying Kirchoff's current law to the equivalent circuit in Fig.3.8, the following relation is found:

$$I_{s}=i_{Lr1}(t)+i_{Lr2}(t)+i_{Cr}(t)$$

(3-12)

The initial conditions for the combined modes are  $i_{Lr1}(t_3)=I_s$ ,  $V_{Cr}(t_3)=0$  and

$$i_{Lr2}(t_3) \approx (V_{Cr}(0) - V_x)/Z_2$$

(3-13)

Since diode  $D_2$  is conducting, the following equation can be written:

$$V_{Lr1} = V_{Cr} = V_{Lr2} + V_x$$

(3-14)

Differentiating equation (3-12) with respect to time gives the following:

$$0 = \frac{d}{dt} i_{Lr1}(t) + \frac{d}{dt} i_{Lr2}(t) + \frac{d}{dt} i_{Cr}(t)$$

(3-15a)

The time derivative of  $I_{in}$  is zero because it is the input current, which is assumed to be constant when the auxiliary circuit is active. Substituting equation (3-14) in equation (3-15a) results in

$$0 = V_{Cr}(t)/L_{r1} + [V_{Cr}(t) - V_x]/L_{r2} + C_r \frac{d^2}{dt^2} V_{Cr}(t)$$

(3-15b)

which can be rewritten as

$$0 = V_{Cr}(t)/L_{eq} - V_x/L_{r2} + C_r \frac{d^2}{dt^2} V_{Cr}(t)$$

(3-15c)

where  $L_{eq} = L_{r1}L_{r2}/(L_{r1}+L_{r2})$ . Equ. (3-15c) can be rearranged to give

$$-C_{\rm r} \frac{d^2}{dt^2} V_{\rm Cr}(t) = V_{\rm Cr}(t)/L_{\rm eq} - V_{\rm x}/L_{\rm r2}$$

(3-15d)

Dividing both sides of (3-15d) by C<sub>r</sub> results in

$$-\frac{d^{2}}{dt^{2}}V_{Cr}(t) = V_{Cr}(t)/L_{eq}C_{r} - V_{x}/L_{r2}C_{r}$$

(3-15e)

Substituting  $\omega_{eq}^2 = 1/L_{eq}C_r$  and  $\omega_2^2 = 1/L_{r2}C_r$  into this equation gives

$$-\frac{d^{2}}{dt^{2}}V_{Cr}(t) = V_{Cr}(t)\omega_{eq}^{2} - V_{x}\omega_{2}^{2}$$

(3-15f)

For the combined mode 3-5 of operation, the initial resonance capacitor voltage is

$$V_{\rm Cr}(0)=0$$

(3-16)

and its initial time derivative is

$$\left[\frac{d}{dt} V_{cr}(t)\right]_{t=0} = -(1/C_{r}) \left[\frac{d}{dt} q_{cr}(t)\right]_{t=0}$$

$$= -(1/C_{r}) \left[i_{Lr2}(t)\right]_{t=0} \approx -(V_{Cr}(0) - V_{x})/Z_{2}C_{r}$$

(3-17)

Applying the initial conditions given by (3-16) and (3-17), the solution of the differential equation (3-15f) is given by:

$$V_{Cr}(t) = -[(V_{Cr}(0) - V_x)/\sqrt{(1 + Lr^2/Lr^1)}]\sin\omega_{eq}t + V_x\omega_2^2[1 - \cos\omega_{eq}t]/\omega_{eq}^2 \qquad (3-18)$$

From the equivalent circuit diagrams shown in Figs. 3.5-3.8 the following equation can be written

$$V_{Lr1}(t) = V_{Cr}(t) = L_{r1} \frac{d}{dt} i_{Lr1}(t) = L_{r2} \frac{d}{dt} i_{Lr2}(t) + V_x$$

(3-19a)

which can be rewritten as

$$V_{Cr}(t)/L_{rl} = \frac{d}{dt} i_{Lrl}(t)$$

(3-19b)

and simplified to

$$[V_{Cr}(t)/L_{r1}]dt=d(i_{Lr1}(t))$$

(3-19c)

Integrating from the initial stage t = 0 for this mode to any intermediate time  $t < t_6$ , then using the initial value of  $i_{Lr1}(t)$  and simplifying results in

$$i_{Lr1}(t) = I_{S} - [(V_{Cr}(0) - V_{x})L_{eq}/Z_{2}L_{r1}][1 - \cos\omega_{eq}t] + V_{x}\omega_{2}^{2}[t - \sin\omega_{eq}t/\omega_{eq}]/\omega_{eq}^{2}L_{r1}$$

for

$$t_2 < t < t_6$$

(3-19d)

From equ.(3-19a), it can be written that

$$V_{Cr}(t) = L_{r2} \frac{d}{dt} i_{Lr2}(t) + V_x$$

(3-20a)

Integrating and simplifying this equation with an initial condition of  $i_{Lr2}(t)$ approximately equals to  $(V_{Cr}(0)-V_x)/Z_2$  which results in

$$i_{Lr2}(t) = (V_{Cr}(0) - V_x)/Z_2 - [(V_{Cr}(0) - V_x)L_{eq}/Z_2L_{r2}][1 - \cos\omega_{eq}t] + V_x\omega_2^2[t - \sin\omega_{eq}t/\omega_{eq}]/\omega_{eq}^2L_{r2}$$

-  $V_x t/L_{r2}$  for  $t_2 < t < t_6$  (3-20b)

At  $t = t_6$ , the current in the body diodes of the full-bridge switch becomes zero (as shown in Fig. 3.9), and some input current starts to flow through  $L_{r1}$ ,  $Q_1$  and  $Q_4$ . The remaining input current continues to charge  $C_r$  and the voltage across it rises. Energy begins to be transferred to the load through  $D_1$  and  $D_4$ . At the end of this mode the voltage across  $C_r$  charges up to  $V_{Cr0}$ . The differential equations describing this mode are

$$I_{in} = C_r \frac{dv_{Cr}(t)}{dt} + i_{Lr1}$$

(3-21)

$$V_{Cr}(t) = L_{r1} \frac{di_{Lr1}(t)}{dt} + \frac{V_o}{N}$$

(3-22)

which have the following initial conditions:  $V_{Cr}(0)=V_0/N$ ,  $i_{Lr}(0)=0$ ,  $i_{Cr}(0)=I_{in}$ .

Fig.3.9 Current flow in mode 7

Applying these initial conditions the capacitor voltage in this mode is given by

$$i_{Lr1}(t) = I_{in}(1 - \cos \omega_1 t)$$

(3-23)

$$V_{cr}(t) = \frac{Vo}{N} + I_{in} Z_{1} \sin \omega_{1} t \qquad (3-24)$$

where

$$\omega_1 = \frac{1}{\sqrt{(L_{r1} + L_{lk})C_r}}$$

(3-25)

and

$$Z_1 = \sqrt{\frac{L_{r1} + L_{lk}}{C_r}}$$

(3-26)

where  $L_{lk}$  is the transformer leakage inductance.

At the end of this mode the capacitor voltage  $V_{Cr}$  reaches its initial value  $V_{Cr}(0)$

given by:

$$V_{Cr}(0) = \frac{Vo}{N} + I_{in}Z_1$$

(3-27)

#### **3.3 Summary of Key Equations**

In this section the equations describing the current and voltage of different components of the converter during one switching cycle which will prove important for designing circuit components are presented and will be referred while designing a specific boost converter with the proposed auxiliary circuit in Chapter 4.

Initial resonant capacitor voltage  $V_{Cr}(0) = \frac{Vo}{N} + I_{in}Z_{1}$

Resonant capacitor voltage during mode-2:  $V_{Cr}(t) = V_x + (V_{Cr}(0) - V_x) \cos \omega_2 t$ Resonant Inductor  $L_{r2}$  current during mode-2:  $i_{Lr2}(t) = [(V_{Cr}(0) - V_x)/Z_2] \sin \omega_2 t$  Resonant Inductor  $L_{r2}$  current during mode-2 to mode-6:

$$i_{Lr2}(t) = (V_{Cr}(0) - V_x)/Z_2 - [(V_{Cr}(0) - V_x)L_{eq}/Z_2L_{r2}][1 - \cos\omega_{eq}t] + V_x\omega_2^2[t - \sin\omega_{eq}t/\omega_{eq}]/\omega_{eq}^2L_{r2}$$

$$-V_xt/L_{r2} \qquad \qquad \text{for } t_2 < t < t_6$$

Resonant Inductor  $L_{r1}$  current during mode-2 to mode-6:

$$i_{Lr1}(t) = I_{S} - [(V_{Cr}(0) - V_{x})L_{eq}/Z_{2}L_{r1}][1 - \cos\omega_{eq}t] + V_{x}\omega_{2}^{2}[t - \sin\omega_{eq}t/\omega_{eq}]/\omega_{eq}^{2}L_{r1} \qquad \text{for } t_{2} < t < t_{6}$$

### **3.4 Conclusion**

In this chapter, the circuit analysis of a PWM dc-dc boost converter operating with an energy feed-forward auxiliary circuit with reduced conduction losses and switch stresses was presented. The various modes of operation that the converter goes through during a switching cycle were presented, and a mathematical analysis of each mode was performed. The results of the analysis will be used to examine the steady-state characteristics in the next chapter of the thesis that will be needed for designing an experimental prototype of such a converter.

## Chapter 4

## **Design Procedure and Example**

#### **4.1 Introduction**

In this chapter, the results of the mathematical analysis performed on the fullbridge PWM dc-dc boost converter with the proposed auxiliary circuit in the previous chapter will be used to determine the steady-state characteristics and properties of the converter. After these have been determined, they will be used as part of a procedure to design the converter by selecting appropriate converter component values. The procedure will be demonstrated with an example in this chapter and can be used to design other PWM converters with the same auxiliary circuit.

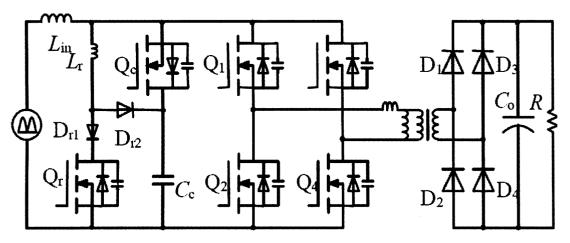

# 4.2 Conditions for ZCS Turn-Off in the Proposed Full-Bridge Converter

In this section, the conditions for achieving the ZCS of both the main switch and auxiliary switch of the converter with the proposed auxiliary circuit, shown in Fig. 4.1, are analyzed.