### Western University Scholarship@Western

**Digitized Theses**

**Digitized Special Collections**

2009

### A Low-Power Low-Voltage Bandgap Reference in CMOS

Na Sun

Follow this and additional works at: https://ir.lib.uwo.ca/digitizedtheses

#### **Recommended Citation**

Sun, Na, "A Low-Power Low-Voltage Bandgap Reference in CMOS" (2009). *Digitized Theses*. 3769. https://ir.lib.uwo.ca/digitizedtheses/3769

This Thesis is brought to you for free and open access by the Digitized Special Collections at Scholarship@Western. It has been accepted for inclusion in Digitized Theses by an authorized administrator of Scholarship@Western. For more information, please contact wlswadmin@uwo.ca.

# A Low-Power Low-Voltage Bandgap Reference in CMOS

(Spine title: A Low-Power Low-Voltage Bandgap Reference in CMOS) (Thesis format: Monograph)

by

Na <u>Sun</u>

1

Graduate Program in Engineering Science Electrical and Computer Engineering

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Engineering Science

School of Graduate and Postdoctoral Studies The University of Western Ontario London, Ontario, Canada

© Na Sun 2009

# A Low-Power Low-Voltage Bandgap Reference in CMOS

(Spine title: A Low-Power Low-Voltage Bandgap Reference in CMOS) (Thesis format: Monograph)

by

Na <u>Sun</u>

!

Graduate Program in Engineering Science Electrical and Computer Engineering

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Engineering Science

School of Graduate and Postdoctoral Studies The University of Western Ontario London, Ontario, Canada

© Na Sun 2009

# A Low-Power Low-Voltage Bandgap Reference in CMOS

(Spine title: A Low-Power Low-Voltage Bandgap Reference in CMOS)

(Thesis format: Monograph)

by

Na <u>Sun</u>

1

Graduate Program in Engineering Science Electrical and Computer Engineering

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Engineering Science

School of Graduate and Postdoctoral Studies The University of Western Ontario London, Ontario, Canada

© Na Sun 2009

### Abstract

Bandgap reference plays a substantial role in integrated circuit. Traditionally, it provides a constant reference voltage of 1.205V for other blocks in the circuit while itself is independent of temperature and power supply. However, the development of CMOS technology has brought us into a new era of high integration and ultra-low power consumption. As the gate length scales down, it is crucial to build circuits that are able to work under a very low voltage power supply, for instance, lower than the bandgap voltage of 1.205V. Building bandgap circuits to generate the conventional bandgap voltage under a low voltage power supply such as 1.2V or 1V is no longer practical nor useful. Thus, bandgap references working under low-voltage and consuming low-power is becoming the trend of research and development nowadays.

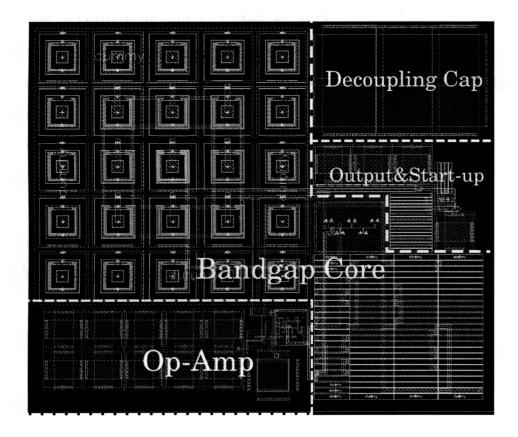

In this thesis work, the potential structure of a low-voltage low-power bandgap reference is proposed, which is based on extracting a current that is a fraction of the traditional bandgap voltage. All the necessary blocks are designed to achieve the high accuracy bandgap reference, including bandgap core circuit, op-amp, start-up circuit and output stage. As a result, the designed bandgap reference is able to work under 1.2V power supply and provides an output reference voltage of 584.7mV. It has a variation of only 244.38 $\mu$ V for the temperature range of 0°C ~ 125°C and has a variation of only 1.1mV for a power supply range of 1.08V ~ 1.32V. The layout design for the bandgap reference structure is also done carefully at the late stage, with an area of 100 $\mu$ m × 85 $\mu$ m.

Keywords: Bandgap Reference, Low-Voltage, Low-Power, Op-Amp, Start-Up, Output Stage, Layout.

### Abstract

Bandgap reference plays a substantial role in integrated circuit. Traditionally, it provides a constant reference voltage of 1.205V for other blocks in the circuit while itself is independent of temperature and power supply. However, the development of CMOS technology has brought us into a new era of high integration and ultra-low power consumption. As the gate length scales down, it is crucial to build circuits that are able to work under a very low voltage power supply, for instance, lower than the bandgap voltage of 1.205V. Building bandgap circuits to generate the conventional bandgap voltage under a low voltage power supply such as 1.2V or 1V is no longer practical nor useful. Thus, bandgap references working under low-voltage and consuming low-power is becoming the trend of research and development nowadays.

In this thesis work, the potential structure of a low-voltage low-power bandgap reference is proposed, which is based on extracting a current that is a fraction of the traditional bandgap voltage. All the necessary blocks are designed to achieve the high accuracy bandgap reference, including bandgap core circuit, op-amp, start-up circuit and output stage. As a result, the designed bandgap reference is able to work under 1.2V power supply and provides an output reference voltage of 584.7mV. It has a variation of only 244.38 $\mu$ V for the temperature range of 0°C ~ 125°C and has a variation of only 1.1mV for a power supply range of 1.08V ~ 1.32V. The layout design for the bandgap reference structure is also done carefully at the late stage, with an area of 100 $\mu$ m × 85 $\mu$ m.

Keywords: Bandgap Reference, Low-Voltage, Low-Power, Op-Amp, Start-Up, Output Stage, Layout.

### Acknowledgement

First I would like to thank The University of Western Ontario for granting me the opportunity to study and finish this work in such a nice environment.

I am extremely grateful for the help and support from my supervisor, Dr. Robert Sobot during the past two years, both for this thesis research work guidance and in every aspect of my studies at The University of Western Ontario.

I also would like to express my thanks to my present and former colleagues in our research group for their care and help. In particular, I would like to thank Sneha for proofreading this work.

My special appreciation goes to Tiam, for all his concerns for me and for all the memorable supports he gave me during this thesis work and the school days.

Last but not the least, I would like to express my deepest gratitude to my family– my parents for their unconditional love, constant encouragement and support for me to study abroad, my uncle and my aunt for their inspiration and insightful suggestions during my studies, and my other family members for their optimistic outlook.

iv

3.36

| A  | ostra           | ct                                                                                    |   |  |  |  |

|----|-----------------|---------------------------------------------------------------------------------------|---|--|--|--|

| A  | Acknowledgement |                                                                                       |   |  |  |  |

| Li | st of           | tables                                                                                |   |  |  |  |

| Li | st of           | figures                                                                               |   |  |  |  |

| 1  | Intr            | $\mathbf{roduction}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ |   |  |  |  |

|    | 1.1             | Review of The Bandgap Reference Circuits                                              |   |  |  |  |

|    | 1.2             | Motivation and Research Objectives                                                    |   |  |  |  |

|    | 1.3             | Organization of The Thesis                                                            |   |  |  |  |

| 2  | Ban             | dgap Voltage Reference                                                                |   |  |  |  |

|    | 2.1             | Introduction to Bandgap Reference                                                     |   |  |  |  |

|    | 2.2             | Temperature Independent Reference    9                                                |   |  |  |  |

|    |                 | 2.2.1 Negative Temperature Coefficient                                                |   |  |  |  |

|    |                 | 2.2.2 Positive Temperature Coefficient                                                |   |  |  |  |

|    | 2.3             | Bandgap Reference                                                                     |   |  |  |  |

|    | 2.4             | Example of Bandgap Circuits                                                           |   |  |  |  |

|    |                 | 2.4.1 Simple Bandgap Circuits Without Op-amp                                          |   |  |  |  |

|    |                 | 2.4.2 Bandgap Circuits With Op-amp                                                    |   |  |  |  |

|    | 2.5             | Start-Up Circuit                                                                      |   |  |  |  |

|    | 2.6             | Summary                                                                               |   |  |  |  |

| 3  | Pro             | posed Bandgap Circuit                                                                 |   |  |  |  |

|    | 3.1             | Low-Voltage Bandgap Core Circuit                                                      |   |  |  |  |

|    |                 | 3.1.1 NPN Model Characterization                                                      |   |  |  |  |

|    |                 | 3.1.2 Bandgap Voltage Generating Circuit                                              |   |  |  |  |

|    |                 | 3.1.3 Sensitivity to Power Supply Variation                                           |   |  |  |  |

|    | 3.2             | The Design of Op-Amp for Use in Bandgap Reference                                     |   |  |  |  |

|    |                 | 3.2.1 Op-amp Blocks and Two Stage Op-Amp Circuits 27                                  |   |  |  |  |

|    |                 | 3.2.2 Op-Amp Design Considerations                                                    |   |  |  |  |

|    |                 | 3.2.3 Frequency Response and Compensation for the Proposed Op-Amp                     |   |  |  |  |

|    | 3.3             | Start-Up Circuit                                                                      |   |  |  |  |

|    | 3.4             | The Output Stage                                                                      |   |  |  |  |

|    | 3.5             | Summary                                                                               | ) |  |  |  |

A DATE OF A

| Abstract |                 |                                                                   |   |  |  |

|----------|-----------------|-------------------------------------------------------------------|---|--|--|

| A        | Acknowledgement |                                                                   |   |  |  |

| Li       | st of           | tables                                                            |   |  |  |

| Li       | st of           | figures                                                           |   |  |  |

| 1        | Intr            | $\mathbf{r}$ oduction                                             |   |  |  |

|          | 1.1             | Review of The Bandgap Reference Circuits                          |   |  |  |

|          | 1.2             | Motivation and Research Objectives                                |   |  |  |

|          | 1.3             | Organization of The Thesis 4                                      |   |  |  |

| 2        | Ban             | dgap Voltage Reference                                            |   |  |  |

|          | 2.1             | Introduction to Bandgap Reference                                 |   |  |  |

|          | 2.2             | Temperature Independent Reference                                 |   |  |  |

|          |                 | 2.2.1 Negative Temperature Coefficient                            |   |  |  |

|          |                 | 2.2.2 Positive Temperature Coefficient                            |   |  |  |

|          | 2.3             | Bandgap Reference                                                 |   |  |  |

|          | 2.4             | Example of Bandgap Circuits                                       | : |  |  |

|          |                 | 2.4.1 Simple Bandgap Circuits Without Op-amp                      | : |  |  |

|          |                 | 2.4.2 Bandgap Circuits With Op-amp                                |   |  |  |

|          | 2.5             | Start-Up Circuit                                                  |   |  |  |

|          | 2.6             | Summary                                                           | I |  |  |

| 3        | Pro             | posed Bandgap Circuit                                             |   |  |  |

|          | 3.1             | Low-Voltage Bandgap Core Circuit                                  |   |  |  |

|          |                 | 3.1.1 NPN Model Characterization                                  |   |  |  |

|          |                 | 3.1.2 Bandgap Voltage Generating Circuit                          |   |  |  |

|          |                 | 3.1.3 Sensitivity to Power Supply Variation                       |   |  |  |

|          | 3.2             | The Design of Op-Amp for Use in Bandgap Reference                 |   |  |  |

|          |                 | 3.2.1 Op-amp Blocks and Two Stage Op-Amp Circuits                 |   |  |  |

|          |                 | 3.2.2 Op-Amp Design Considerations                                |   |  |  |

|          |                 | 3.2.3 Frequency Response and Compensation for the Proposed Op-Amp |   |  |  |

|          | <b>3.3</b>      | Start-Up Circuit                                                  |   |  |  |

|          | 3.4             | The Output Stage                                                  |   |  |  |

|          | 3.5             | Summary                                                           | , |  |  |

| A۱ | Abstract        |                                                                             |  |  |  |  |

|----|-----------------|-----------------------------------------------------------------------------|--|--|--|--|

| A  | Acknowledgement |                                                                             |  |  |  |  |

| Li | st of           | tables                                                                      |  |  |  |  |

| Li | st of           | figures                                                                     |  |  |  |  |

| 1  | Intr            | oduction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $1$ |  |  |  |  |

|    | 1.1             | Review of The Bandgap Reference Circuits                                    |  |  |  |  |

|    | 1.2             | Motivation and Research Objectives                                          |  |  |  |  |

|    | 1.3             | Organization of The Thesis                                                  |  |  |  |  |

| 2  | Ban             | dgap Voltage Reference                                                      |  |  |  |  |

|    | 2.1             | Introduction to Bandgap Reference                                           |  |  |  |  |

|    | 2.2             | Temperature Independent Reference    9                                      |  |  |  |  |

|    |                 | 2.2.1 Negative Temperature Coefficient                                      |  |  |  |  |

|    |                 | 2.2.2 Positive Temperature Coefficient                                      |  |  |  |  |

|    | 2.3             | Bandgap Reference                                                           |  |  |  |  |

|    | -2.4            | Example of Bandgap Circuits                                                 |  |  |  |  |

|    |                 | 2.4.1 Simple Bandgap Circuits Without Op-amp                                |  |  |  |  |

|    |                 | 2.4.2 Bandgap Circuits With Op-amp                                          |  |  |  |  |

|    | 2.5             | Start-Up Circuit                                                            |  |  |  |  |

|    | 2.6             | Summary                                                                     |  |  |  |  |

| 3  | Pro             | posed Bandgap Circuit                                                       |  |  |  |  |

|    | 3.1             | Low-Voltage Bandgap Core Circuit                                            |  |  |  |  |

|    |                 | 3.1.1 NPN Model Characterization                                            |  |  |  |  |

|    |                 | 3.1.2 Bandgap Voltage Generating Circuit                                    |  |  |  |  |

|    |                 | 3.1.3 Sensitivity to Power Supply Variation                                 |  |  |  |  |

|    | 3.2             | The Design of Op-Amp for Use in Bandgap Reference                           |  |  |  |  |

|    |                 | 3.2.1 Op-amp Blocks and Two Stage Op-Amp Circuits                           |  |  |  |  |

|    |                 | 3.2.2 Op-Amp Design Considerations                                          |  |  |  |  |

|    |                 | 3.2.3 Frequency Response and Compensation for the Proposed Op-Amp 42        |  |  |  |  |

|    | 3.3             | Start-Up Circuit                                                            |  |  |  |  |

|    | 3.4             | The Output Stage         47                                                 |  |  |  |  |

|    | 3.5             | Summary                                                                     |  |  |  |  |

| Abstract |                 |                                                                                                                     | iii |  |  |

|----------|-----------------|---------------------------------------------------------------------------------------------------------------------|-----|--|--|

| A        | Acknowledgement |                                                                                                                     |     |  |  |

| Li       | st of           | $tables \ldots v$ | iii |  |  |

| Li       | st of           | figures                                                                                                             | ix  |  |  |

| 1        | Intr            | $\mathbf{roduction}$                                                                                                | 1   |  |  |

|          | 1.1             | Review of The Bandgap Reference Circuits                                                                            | 1   |  |  |

|          | 1.2             | Motivation and Research Objectives                                                                                  | 3   |  |  |

|          | 1.3             | Organization of The Thesis                                                                                          | 4   |  |  |

| 2        | Bar             | ndgap Voltage Reference                                                                                             | 6   |  |  |

|          | 2.1             | Introduction to Bandgap Reference                                                                                   | 6   |  |  |

|          | 2.2             | Temperature Independent Reference                                                                                   | 9   |  |  |

|          |                 | 2.2.1 Negative Temperature Coefficient                                                                              | 9   |  |  |

|          |                 | <u>+</u>                                                                                                            | 11  |  |  |

|          | 2.3             |                                                                                                                     | 12  |  |  |

|          | 2.4             | I                                                                                                                   | 14  |  |  |

|          |                 |                                                                                                                     | 14  |  |  |

|          |                 |                                                                                                                     | 17  |  |  |

|          | 2.5             |                                                                                                                     | 19  |  |  |

|          | 2.6             | Summary                                                                                                             | 20  |  |  |

| 3        | Pro             |                                                                                                                     | 21  |  |  |

|          | 3.1             | 0 0 1                                                                                                               | 21  |  |  |

|          |                 |                                                                                                                     | 21  |  |  |

|          |                 |                                                                                                                     | 23  |  |  |

|          |                 |                                                                                                                     | 25  |  |  |

|          | 3.2             |                                                                                                                     | 27  |  |  |

|          |                 |                                                                                                                     | 27  |  |  |

|          |                 |                                                                                                                     | 35  |  |  |

|          |                 | 3.2.3 Frequency Response and Compensation for the Proposed Op-Amp                                                   |     |  |  |

|          | 3.3             |                                                                                                                     | 44  |  |  |

|          | 3.4             |                                                                                                                     | 47  |  |  |

|          | 3.5             | Summary                                                                                                             | 48  |  |  |

| 4 | Lay  | out Design                                                                                                                        |

|---|------|-----------------------------------------------------------------------------------------------------------------------------------|

|   | 4.1  | Layout Issues                                                                                                                     |

|   |      | 4.1.1 Using Unit Elements                                                                                                         |

|   |      | 4.1.2 Common-Centroid Layout                                                                                                      |

|   |      | 4.1.3 Dummy Elements                                                                                                              |

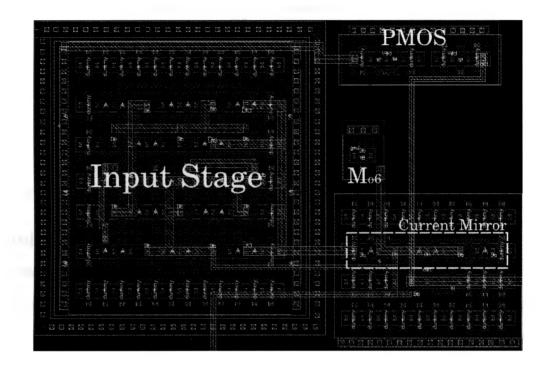

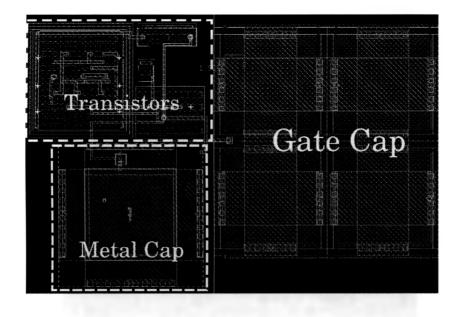

|   | 4.2  | Block Design                                                                                                                      |

|   |      | 4.2.1 Op-Amp Layout                                                                                                               |

|   |      | 4.2.2 Bandgap Core Resistor Array Layout                                                                                          |

|   |      | 4.2.3 BJT Array Layout                                                                                                            |

|   |      | 4.2.4 Bandgap Core PMOS Current Sources Array Layout 59                                                                           |

|   |      | 4.2.5 Output Stage and Start-Up Circuit Layouts                                                                                   |

|   | 4.3  | The Top Level Layout                                                                                                              |

|   |      | 4.3.1 Placement of The Blocks                                                                                                     |

|   |      | 4.3.2 The Power Lines Layout                                                                                                      |

|   | 4.4  | Summary                                                                                                                           |

|   |      | •                                                                                                                                 |

| 5 | Cir  | cuit Characterization                                                                                                             |

|   | 5.1  | Characterization of Op-amp                                                                                                        |

|   |      | 5.1.1 The Open-Loop Gain and Frequency Response                                                                                   |

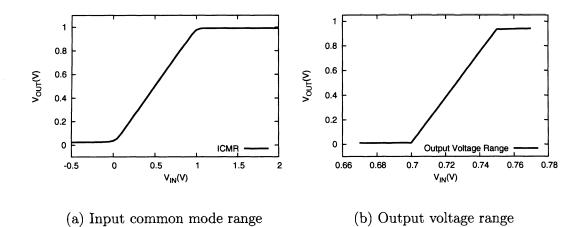

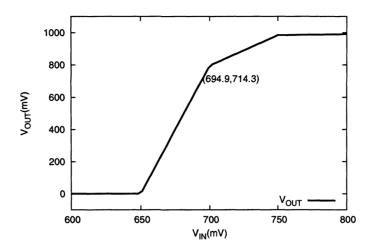

|   |      | 5.1.2 ICMR and Output Voltage Range                                                                                               |

|   |      | 5.1.3 Input-Offset Voltage                                                                                                        |

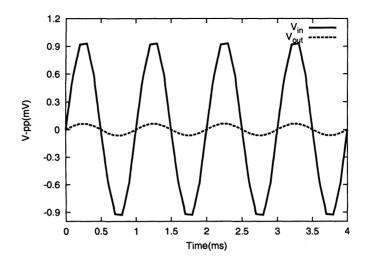

|   |      | 5.1.4 Common Mode Gain and CMRR                                                                                                   |

|   |      | 5.1.5 Power Supply Rejection Ratio                                                                                                |

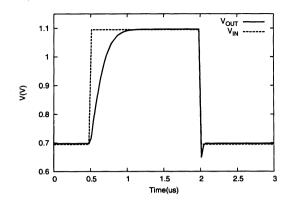

|   |      | 5.1.6 Slew Rate and Settling Time                                                                                                 |

|   |      | 5.1.7 Output Impedance                                                                                                            |

|   | 5.2  | Characterization of The Bandgap Voltage Reference                                                                                 |

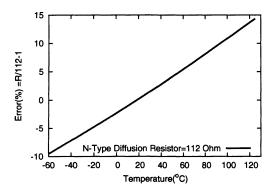

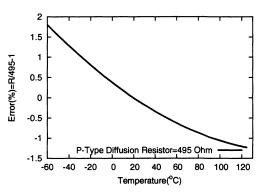

|   |      | 5.2.1 Temperature Independent Resistor in Bandgap Core 70                                                                         |

|   |      | 5.2.2 The Replacement of Ideal Capacitors                                                                                         |

|   |      | 5.2.3 The Noise Analysis                                                                                                          |

|   |      | 5.2.4 The Resistive Load Limitation                                                                                               |

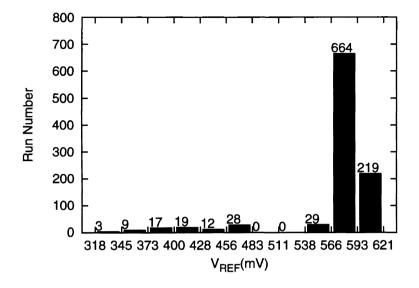

|   | 5.3  | Monte Carlo Analysis of Process Variation and Component Mismatch 77                                                               |

|   | 5.4  | Summary                                                                                                                           |

|   |      |                                                                                                                                   |

| 6 |      | $1 \text{ clusion } \dots $ |

|   | 6.1  | The Contribution of The Thesis                                                                                                    |

|   | 6.2  | Future Work                                                                                                                       |

| D | hlia | graphy                                                                                                                            |

| D | UUUO | graphy                                                                                                                            |

|   |      |                                                                                                                                   |

### Appendices

- characteristic of the second

-----

| A | Frequency | Response and Compensation of Op-Amp               | 85 |

|---|-----------|---------------------------------------------------|----|

|   | A.0.1     | Frequency Response and The Problem of Instability | 85 |

|   | A.0.2     | Miller Compensation of the Two-Stage Op-Amp       | 87 |

## List of Tables

| 3.1 | The effect of different $V_{GS}$ on power supply variation $\ldots \ldots \ldots$ | 27 |

|-----|-----------------------------------------------------------------------------------|----|

| 5.1 | Comparison between this work and the referred paper work $[1]$                    | 78 |

## List of Figures

| 2.1        | Circuit diagram showing the demand for bandgap reference                      | 8  |

|------------|-------------------------------------------------------------------------------|----|

| 2.2        | PTAT voltage generation circuit diagram                                       | 11 |

| 2.3        | Bandgap-reference generating circuit diagram                                  | 13 |

| <b>2.4</b> | Example of an simple bandgap circuit diagram                                  | 15 |

| 2.5        | Simple bandgap with three Bipolar transistors circuit diagram                 | 15 |

| 2.6        | Simulation results of currents of the simple bandgap                          | 16 |

| 2.7        | Simulation result of the simple bandgap output voltage                        | 16 |

| 2.8        | Simulation result of simple bandgap with three Bipolar transistors            | 17 |

| 2.9        | Schematic of bandgap reference with op-amp                                    | 18 |

| 2.10       | Simulation result of bandgap with op-amp output voltage                       | 18 |

| 2.11       | The two stable operating points in bandgap reference circuits                 | 20 |

| 3.1        | Simulation results showing the dependence of $V_{BE}$ on temperature .        | 23 |

| 3.2        | Bandgap voltage generating circuit diagram                                    | 24 |

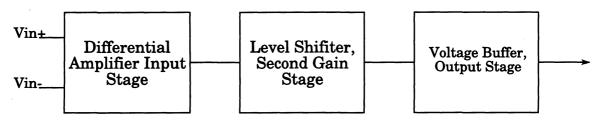

| 3.3        | Blocks of a general op-amp                                                    | 28 |

| 3.4        | A conventional op-amp circuit diagram                                         | 29 |

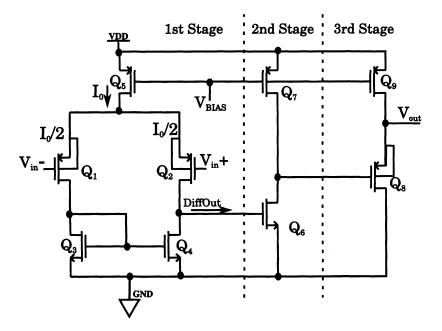

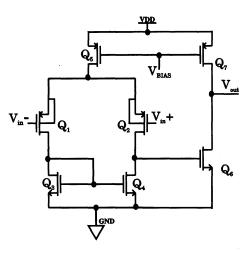

| 3.5        | A two stage op-amp circuit diagram                                            | 31 |

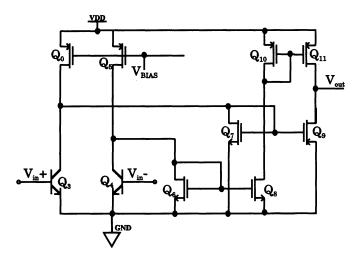

| 3.6        | Circuit diagram of the op-amp proposed in [1]                                 | 31 |

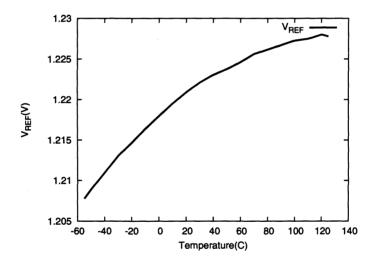

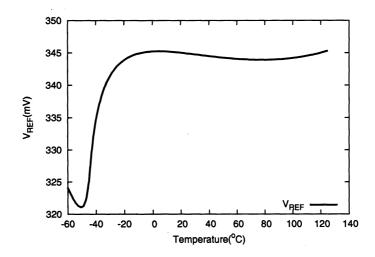

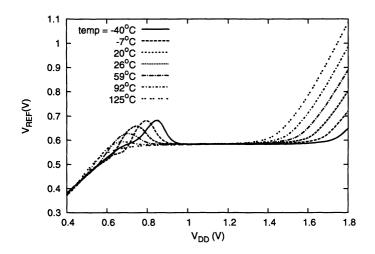

| 3.7        | $V_{REF}$ vs. temperature using the op-amp proposed in [1]                    | 33 |

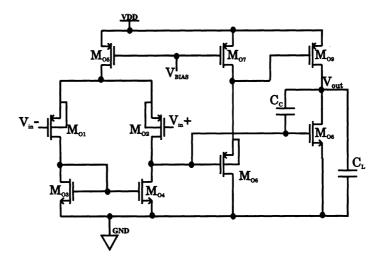

| 3.8        | Proposed two stage op-amp circuit diagram                                     | 33 |

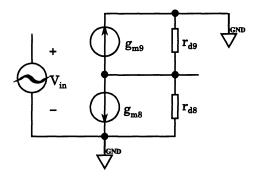

| 3.9        | Low-frequency small-signal analysis of the output stage in Fig. 3.8.          | 34 |

| 3.10       | Simulation results for op-amp gain determination                              | 38 |

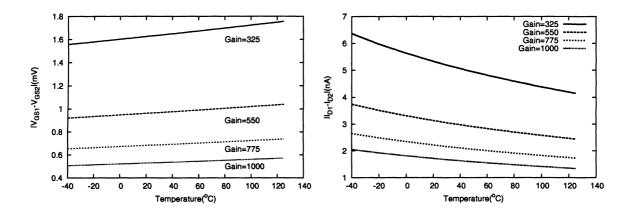

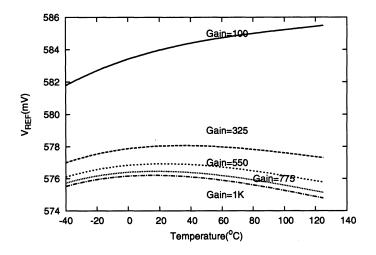

| 3.11       | $V_{REF}$ varies with gain                                                    | 39 |

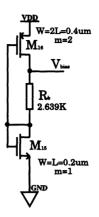

|            | Biasing circuit diagram for the proposed op-amp                               | 40 |

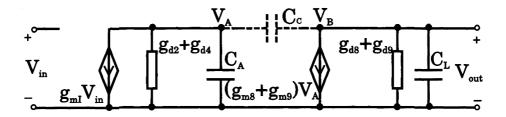

|            | Small signal analysis of Fig. 3.8                                             | 41 |

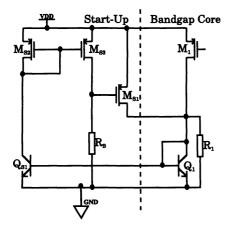

| 3.14       | Start-up circuit diagram in design [1]                                        | 44 |

|            | Improved start-up circuit diagram                                             | 44 |

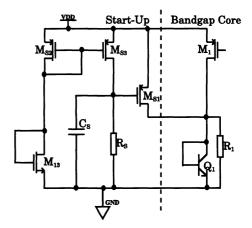

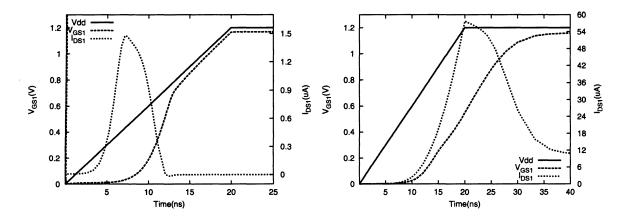

| 3.16       | The difference in setting-up of $M_5$ caused by the capacitor $\ldots \ldots$ | 45 |

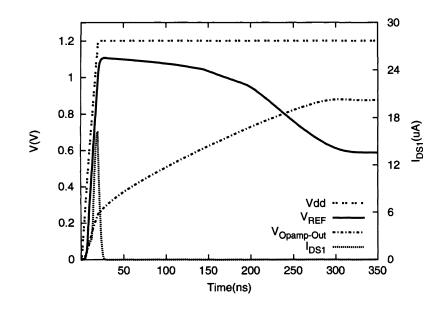

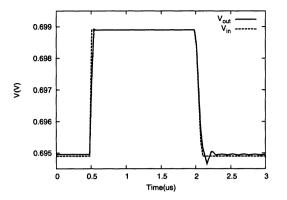

|            | The response of $V_{REF}$ and op-amp output when powering up $\ldots$         | 46 |

| 3.18       | The output stage of bandgap circuit diagram                                   | 47 |

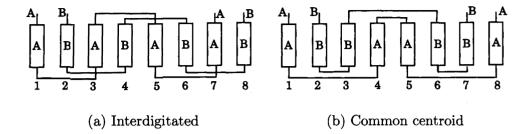

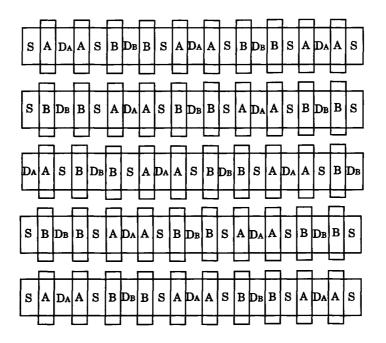

| 4.1        | The layout types illustration diagram                                         | 50 |

| 4.2        | The n-type diffusion resistor array diagram                                   | 52 |

| 4.3        | The resistor array layout including both diffusion types                      | 53 |

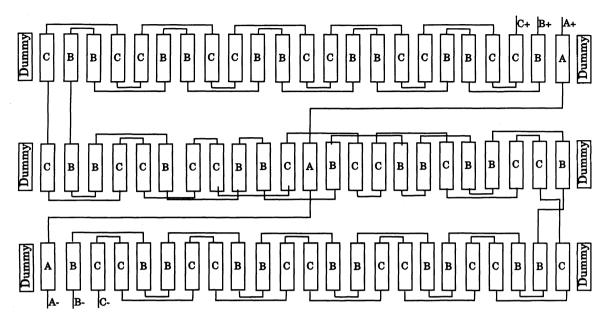

| 4.4        | The differential input transistor array diagram                               | 55 |

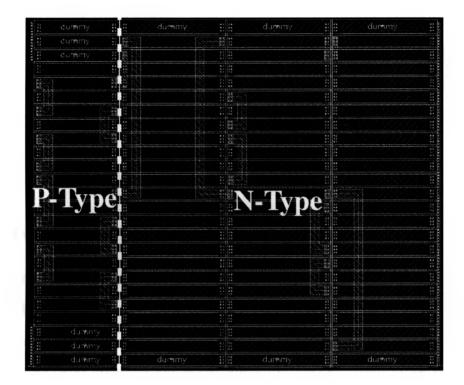

| 4.5        | Op-amp circuit layout without capacitors                                      | 56 |

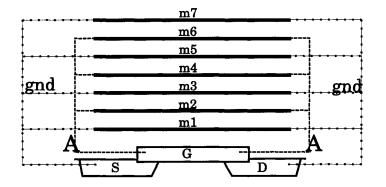

| 4.6        | Cross section diagram of a unity coin gate capacitor                          | 57 |

| 4.7        | Op-amp layout (with four coins of gate capacitor visuable)                    | 58 |

# List of Figures

| 2.1  | Circuit diagram showing the demand for bandgap reference               | 8  |

|------|------------------------------------------------------------------------|----|

| 2.2  | PTAT voltage generation circuit diagram                                | 11 |

| 2.3  | Bandgap-reference generating circuit diagram                           | 13 |

| 2.4  | Example of an simple bandgap circuit diagram                           | 15 |

| 2.5  | Simple bandgap with three Bipolar transistors circuit diagram          | 15 |

| 2.6  | Simulation results of currents of the simple bandgap                   | 16 |

| 2.7  | Simulation result of the simple bandgap output voltage                 | 16 |

| 2.8  | Simulation result of simple bandgap with three Bipolar transistors     | 17 |

| 2.9  | Schematic of bandgap reference with op-amp                             | 18 |

| 2.10 |                                                                        | 18 |

| 2.11 |                                                                        | 20 |

| 3.1  | Simulation results showing the dependence of $V_{BE}$ on temperature . | 23 |

| 3.2  | Bandgap voltage generating circuit diagram                             | 24 |

| 3.3  | Blocks of a general op-amp                                             | 28 |

| 3.4  | A conventional op-amp circuit diagram                                  | 29 |

| 3.5  | A two stage op-amp circuit diagram                                     | 31 |

| 3.6  | Circuit diagram of the op-amp proposed in [1]                          | 31 |

| 3.7  | $V_{REF}$ vs. temperature using the op-amp proposed in [1]             | 33 |

| 3.8  | Proposed two stage op-amp circuit diagram                              | 33 |

| 3.9  | Low-frequency small-signal analysis of the output stage in Fig. 3.8    | 34 |

| 3.10 | Simulation results for op-amp gain determination                       | 38 |

| 3.11 | $V_{REF}$ varies with gain                                             | 39 |

| 3.12 | Biasing circuit diagram for the proposed op-amp                        | 40 |

|      | Small signal analysis of Fig. 3.8                                      | 41 |

|      | Start-up circuit diagram in design [1]                                 | 44 |

|      | Improved start-up circuit diagram                                      | 44 |

|      | The difference in setting-up of $M_5$ caused by the capacitor $\ldots$ | 45 |

|      | The response of $V_{REF}$ and op-amp output when powering up $\ldots$  | 46 |

|      | The output stage of bandgap circuit diagram                            | 47 |

| 4.1  | The layout types illustration diagram                                  | 50 |

| 4.2  | The n-type diffusion resistor array diagram                            | 52 |

| 4.3  | The resistor array layout including both diffusion types               | 53 |

| 4.4  | The differential input transistor array diagram                        | 55 |

| 4.5  | Op-amp circuit layout without capacitors                               | 56 |

| 4.6  | Cross section diagram of a unity coin gate capacitor                   | 57 |

| 4.7  | Op-amp layout (with four coins of gate capacitor visuable)             | 58 |

1

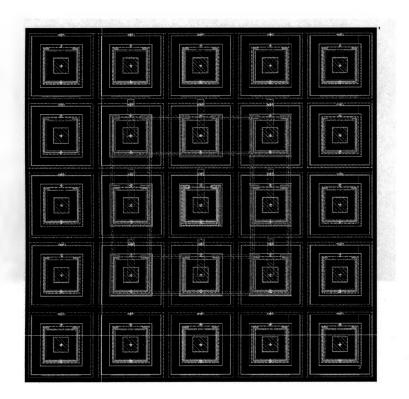

| 4.8  | BJT array layout                                                                               | 59 |

|------|------------------------------------------------------------------------------------------------|----|

| 4.9  | PMOS current sources array layout                                                              | 60 |

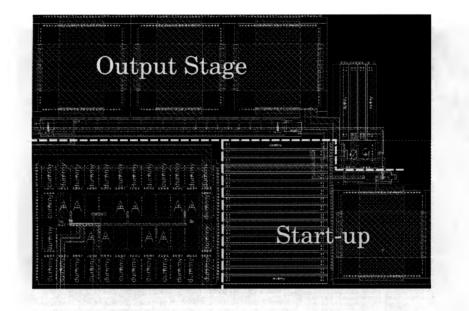

| 4.10 | Output stage and start-up circuit layout                                                       | 61 |

| 4.11 | The finished layout                                                                            | 62 |

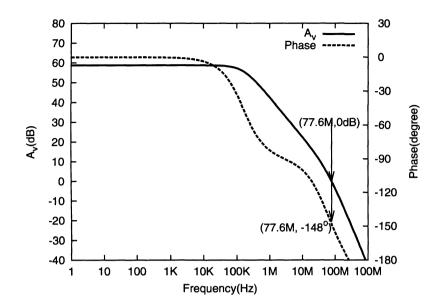

| 5.1  | Frequency response bode plot of the op-amp                                                     | 65 |

| 5.2  | Simulation results of input common mode range and output swing                                 | 66 |

| 5.3  | Simulation result to determine the input-offset voltage                                        | 67 |

| 5.4  | Common mode gain measurement through transient analysis                                        | 68 |

| 5.5  | Simulation result of slew rate measurement                                                     | 69 |

| 5.6  | Simulation result of the settling time measurement                                             | 69 |

| 5.7  | The slope of voltage vs. current determines the output impedance                               | 69 |

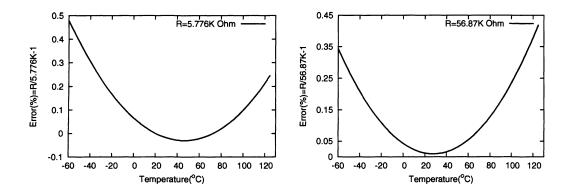

| 5.8  | Characterization results of the poly resistors in the technology                               | 70 |

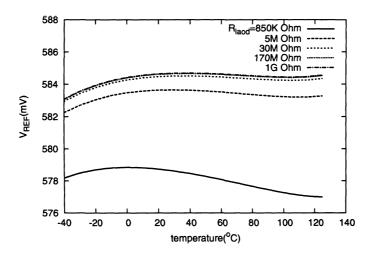

| 5.9  | Characterization results of the temperature independent resistors                              | 71 |

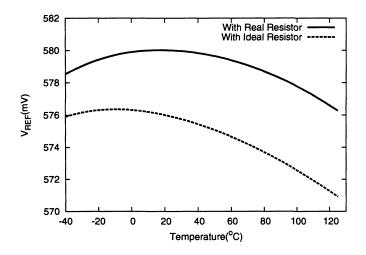

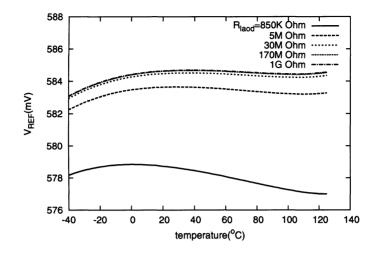

| 5.10 | Dependence of $V_{REF}$ on the replacement of the ideal resistors $\ldots$                     | 72 |

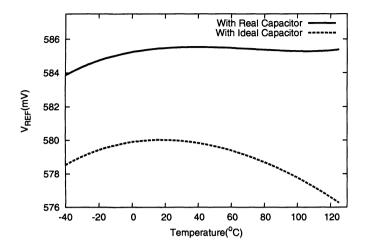

| 5.11 | Dependence of $V_{REF}$ on the replacement of the ideal capacitor                              | 73 |

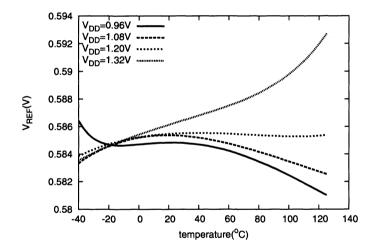

| 5.12 | The simulation result of output voltage with different $V_{dd}$                                | 73 |

| 5.13 | Simulation result of the output voltage against $v_{dd}$ variation $\ldots$ $\ldots$           | 74 |

| 5.14 | Dependence of $V_{REF}$ vs. load resistance $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 76 |

| 5.15 | Output voltage histogram on 1000 Monte Carlo simulation runs                                   | 77 |

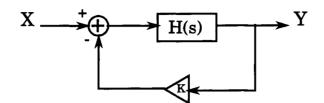

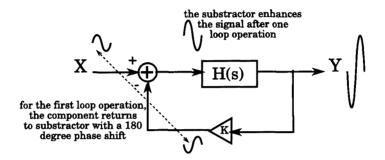

| A.1  | Closed loop system diagram                                                                     | 86 |

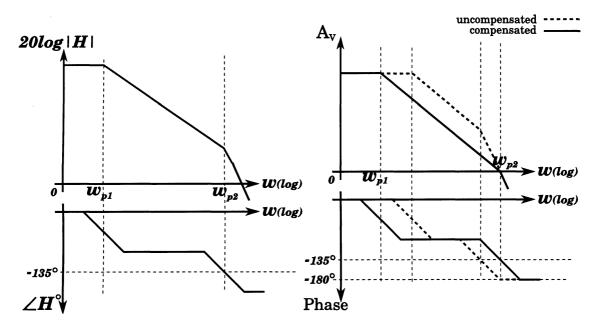

| A.2  | Bode plot of a closed loop system                                                              | 87 |

| A.3  | Bode plot of Miller compensation                                                               | 87 |

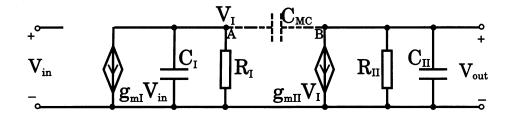

| A.4  | Small signal analysis of Miller compensation for two-stage op-amp                              | 88 |

:

## List of Symbols and Abbreviations

| ADC            | Analog–to–Digital Converter                       |

|----------------|---------------------------------------------------|

| DAC            | Digital-to-Analog Converter                       |

| $\mathbf{PLL}$ | Phase-locked-Loop                                 |

| $\mathbf{BJT}$ | Bipolar Junction Transistor                       |

| MOSFET         | Metal-Oxide-Semiconductor Field-Effect Transistor |

| DTMOST         | Dynamic-Threshold MOS Transistor                  |

| BiCMOS         | Bipolar Complementary Metal-Oxide-Semiconductor   |

| CMOS           | Complementary Metal-Oxide-Semiconductor           |

| DC             | Direct Current                                    |

| IC             | Integrated Circuit                                |

| TC             | Temperature Coefficient                           |

| PTAT           | Proportional To Absolute Temperature              |

| <b>OP-AMP</b>  | Operational Amplifier                             |

| CMRR           | Common-Mode Rejection Ratio                       |

| VCCS           | Voltage-Controlled Current Source                 |

| OTA            | Operational-Transconductance Amplifier            |

| PMOS           | P-Channel MOSFET                                  |

| NMOS           | N-Channel MOSFET                                  |

| DRC            | Design Rule Checking                              |

| LVS            | Layout Versus Schematic                           |

| ICMR           | Input Common Mode range                           |

| CMRR           | Common Mode Rejection Ratio                       |

| PSRR           | Power Supply Rejection Ratio                      |

| $\mathbf{SR}$  | Slew Rate                                         |

| MIM            | Metal Insulator Metal                             |

| $V_{in,CM}$  | Common Mode Input                            |

|--------------|----------------------------------------------|

| $V_{Dsat}$   | Saturation Voltage                           |

| $v_{out}$    | AC Output Voltage                            |

| $v_{in}$     | AC Input Voltage                             |

| $v_{in}$     | Input Difference in Differential Input Stage |

| $\omega$     | Frequency in Radians                         |

| $C_L$        | Load Capacitance                             |

| $C_C$        | Compensation Capacitance                     |

| $C_{A}$      | Capacitance at Point A                       |

| p            | Pole in Frequency Response                   |

| z            | Zero in Frequency Response                   |

| $C_{load}$   | Load Capacitor                               |

| G(A)         | Variation Gradient of A                      |

| $V_{OS}$     | Offset Voltage                               |

| $A_{CM}$     | Common Mode Gain                             |

| $V_{dd-pp}$  | Power Supply Peak-to-Peak Voltage            |

| $V_{out-pp}$ | Output Peak-to-Peak Voltage                  |

| $A_V$        | Gain                                         |

| $g_m$        | Transconductance                             |

| $V_{GS}$     | Gate to Source Voltage                       |

| $V_{DS}$     | Drain to Source Voltage                      |

| $I_D$        | Drain Current                                |

| $V_{DD}$     | Positive Power Supply Rail                   |

| $V_{SS}$     | Negative Power Supply Rail                   |

| $I_R$        | Current Through R                            |

| R            | Resistor/Resistance                          |

| $I_{REF}$    | Reference Current                            |

| $V_{REF}$    | Reference Voltage                            |

| $V_{BG}$     | Bandgap Voltage                              |

| $V_{BE}$     | Base Emitter Voltage                         |

| $V_T$        | Thermal Voltage                              |

| q            | Electron Charge                              |

| $I_C$        | Collector Current                            |

| $I_S$        | Saturation Current                           |

\_\_\_\_

- T Absolute Temperature

- $\mu$  Mobility of Minority Carriers

*n<sub>i</sub>* Intrinsic Minority Carrier Concentration

$E_q$  Bandgap Energy

$\Delta V_{BE}$  Base Emitter Voltage Difference

D Current Density

k Boltzmann Constant

W Channel Width of Transistor

L Channel Length of Transistor

$\lambda$  Channel Length Modulation Parameter

$V_{th}$  Threshold Voltage

$V_{thn}$  Threshold Voltage for NMOS

$V_{thp}$  Threshold Voltage for PMOS

(W/L) Width to Length Ratio

m Number of Elements in Parallel

Vout Output Voltage

$A_{diff}$  Gain of Differential Stage

$r_o$  Output Impedance

$A_{vcs}$  Gain of Common Source Stage

$g_d$  Channel Conductance of Transistor

$A_{Vpush-pull}$

Gain of Push-Pull Stage

+SR Slew Rate at Rising Edge

-SR Slew Rate at Falling Edge

$S_v$  Thermal Noise

f Frequency

$V_{REF-pp}$  Peak-to-Peak Reference Voltage

# Chapter 1 Introduction

In integrated circuits nowadays, the bandgap voltage reference circuit, which has a very low dependence upon temperature and power supply, is used to provide a voltage reference for other blocks in the circuits. The requirement for a stable reference voltage is one of the most important issues in micro-electronic design as it is always a necessary part in many analog and mixed-signal integrated circuits such as ADC, DAC, PLL and memories.

As the technology has developed rapidly during the past several decades, the power supply voltage is required to scale down (for example, the power supply needs to be as low as 1.2V or even sub-1V) due to the shrinking gate lengths and the increased demand for low-power portable equipment in today's electronic applications. Therefore, it is critical to develop low-power consumption bandgap references working under low-voltage supply that are compatible to almost all the technologies at present.

In this chapter, a review of the bandgap reference is given and the research objective and the organization of this thesis are followed.

### 1.1 Review of The Bandgap Reference Circuits

The first bandgap reference circuit based on Bipolar Junction Transistor (BJT) was introduced in the early 1970s. It was in 1971 that the expensive Zener diode reference device was replaced by a bandgap reference circuit based on BJT in an integrated circuit. By the concept introduced in [2], the bandgap voltage reference started a new era of development on chip. In 1973, a precision reference voltage source [3] was presented to replace the Zener diode as a discrete component, providing a 10V output voltage. A year later, A. Paul Brokaw illustrated a three-terminal bandgap reference with a much lower temperature coefficient, which is  $5ppm/^{\circ}C$  over a much wider temperature range [4]. Later on, the bandgap voltage reference continuously improved according to the temperature stability by innovative circuitry such as curvature compensation, laser trimming [3, 4, 5, 6] and op-amp offset cancellation [7].

In the 1990s, the dynamic-threshold MOS transistors (DTMOST) were implemented to replace the normal diodes in technologies. These DTMOSTs have an interconnected gate and backgate [8, 9] and the lateral bipolar structure [10, 11]. As a result of this architecture, the power supply for bandgap voltage reference circuit is reduced to 1.8V or lower and consumes only several micro-watts [9].

With the development of technology, the lower-voltage power supply bandgap circuits, which can even work under supply voltage of lower than 1.205V were required for application purposes. In [12], a 1V output was produced by a bandgap reference circuit working under 1.2V, and the power-supply voltage was even lower (minimum 1V) in a bandgap reference, which used standard bipolar process with base-diffused resistors [13]. The authors in [14] illustrated a very high accuracy bandgap reference with a temperature coefficient of  $15ppm/^{\circ}C$ , in the absence of a low threshold voltage device, it was able to operate under 0.98V power supply. Since then, the bandgap voltage reference started another page of low power low voltage, sub-1V bandgap references were developed in different technologies and with various compensation and trimming techniques [15, 16, 17, 18].

In the near past, the authors in [19] used the same technology as this thesis and by the time the thesis project was finished, a 1V bandgap reference without an op-amp was developed by Lee, Edward K.F. [20]. The authors in [21] also demonstrated a novel bandgap reference circuit that is suitable for fabrication in any digital CMOS technology by eliminating resistors or operational amplifiers.

This work is based on the concept of introducing a fraction of original bandgap voltage, for example a temperature independent current, which was introduced by H.Banba et al. [22]. The concept was further applied and improved in the works of P. Malcovati et al. [1, 23]. The authors in [1] discussed a bandgap architecture capable of operating at 1V voltage-supply, while using a conventional BiCMOS technology to generate a reference voltage of 0.54V, and this architecture consumes  $92\mu W$  at room temperature. By correcting the curvature error, the voltage variation got  $7.5ppm/^{\circ}C$  in the temperature range from  $0^{\circ}C$  to  $80^{\circ}C$  and 212ppm/V of supply voltage dependence. Lower power consumption was achieved in [23] and the performance comparison of low-power bandgap voltage references was given.

#### **1.2** Motivation and Research Objectives

The aim of this thesis is to develop a low-voltage bandgap voltage reference by using CMOS 90nm technology with optimized operational amplifier. The designed bandgap is also aimed for low power consumption, low noise and high temperature independence. The objective of this thesis are:

• To meet the demand of the low-voltage power supply in recent applications, the circuit is aimed to work under 1.2V. The new technology may provide partial help, however, in order to achieve the goal, the main task should be focused on designing a bandgap circuit architecture that works under low-voltage power supply.

- To fully understand the available technology, especially the lateral BJT models, which will eventually determine the output results, characterization for the BJT transistors is required, including the characterization of their performance according to temperature change.

- To obtain a precise output voltage, the bandgap circuit architecture that contains an op-amp is implemented. Thus, an op-amp that is able to work under low voltage power supply with a moderate gain bandwidth product (as the circuit is mostly needed for DC voltage) is demanded.

- To get the right powering-up behavior in the circuit, a start-up circuit is necessary for breaking the zero operating point of the circuit and bringing it into the designed operating point.

- To achieve a voltage of high precision at the output node, an output stage whose behavior is independent of changes in temperature and power supply change should be developed.

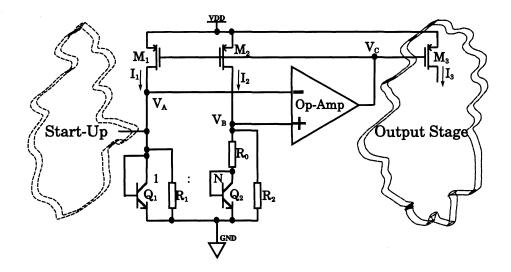

As a result, the design includes an improved start-up block compared to [1], a bandgap core circuit, a high-quality two stage operational amplifier, and an output buffer sub-circuit.

### **1.3** Organization of The Thesis

In this thesis, a high accuracy bandgap voltage reference circuit is developed based on 90nm CMOS technology and its characterization is done by using IC design tools.

In chapter 2, the basic concept of building a bandgap reference is presented and several bandgap references are investigated as examples. In chapter 3, the proposed bandgap voltage reference is described block by block in details. The schematic of each block is demonstrated and the further optimization is discussed.

In chapter 4, the layout for the proposed bandgap voltage reference is developed. As a result, the final bandgap voltage reference layout appears square and consumes considerably small area.

In chapter 5, a complete characterization is provided for the whole bandgap circuit as well as the composing blocks, and a comparison of the results is given at the end of the chapter.

In chapter 6, the conclusion and potential future work are presented.

# Chapter 2 Bandgap Voltage Reference

In the previous chapter, the background of bandgap reference was introduced and the development of bandgap reference circuits was reviewed. The research objective, including the potential circuit blocks was also presented in the last chapter. In this chapter, the necessity of bandgap reference in applications is explained and the basic concept for building the bandgap circuit is discussed, followed with some case studies.

#### 2.1 Introduction to Bandgap Reference

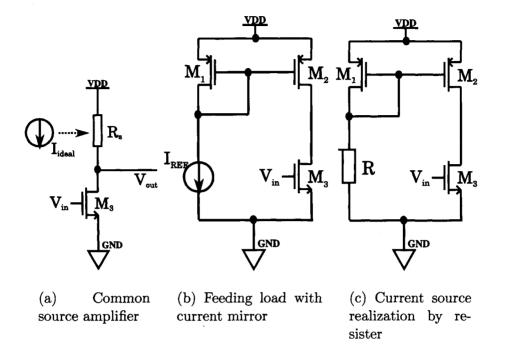

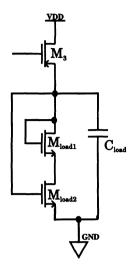

As it was demonstrated in Chapter 1, bandgap reference is a very important part in every single chip. A simple example can be found in Fig. 2.1(a). In this simple one-transistor Common Source amplifier configuration, the gain of the circuit is  $A_V = R_s g_m$ . To get the largest gain, one approach is to increase  $g_m$  and the other one is to increase  $R_s$ . The transconductance  $g_m$  can not be increased infinitely because the transistor must be guaranteed to stay in saturation region. To increase  $R_s$ , the best way is to use an ideal current source that has an infinite impedance.

Fig. 2.1(b) gives an example of feeding the load of the amplifier using a current mirror. In this figure  $V_{GS1} = V_{GS2}$ , therefore,  $I_{D1} = I_{D2}$ . In other words, if transistor  $M_1$  is identical to  $M_2$ ,  $M_2$  copies the current from  $M_1$ . In Fig. 2.1(b), a current source is used for generating and stablizing the current through  $M_1$ , so that both transistors of the current mirror can operate in saturation region. A resistor can be used to realize the current source, as shown in Fig. 2.1(c). However, the resistor value varies a lot as the temperature changes. In addition, since  $I_R = (V_{DD} - V_{GS1})/R$ , the current it produces is related to the power supply. Thus, any disturbance of the power supply can influence its current. In the end, the resistor, as most of the electronic elements, is process dependent. All these limitations discussed above generates an unstable current in Fig. 2.1(c). This situation means that there is a chance that the saturation region lock will be lost.

In summary, it is essential to have a very stable current source  $(I_{REF})$ , which is independent of temperature, power supply and process, to make the circuit operate properly. This current can be obtained by either developing a current reference or by generating a current fraction from a voltage reference  $V_{REF}$ . Thus, voltage and current references are made with little dependence on temperature. What's more, less temperature dependence also reduces process dependence since most process parameters are related to temperature variations [24].

One of the simplest ways is to generate a voltage reference from the power supply by utilizing a voltage divider. However, the output voltage would be a fraction of the power supply voltage, which means it varies according to any variations on the power supply voltage if any disturbance takes place [25]. There are many other more complex approaches to realize current or voltage references that are independent of temperature variation and power supply disturbance, such as making use of a zener diode, applying the difference in the threshold voltage between an enhancement transistor and a depletion transistor, and trying to cancel the temperature dependence of bipolar transistors in a bandgap reference circuit [26]. The most commonly used method nowadays is the third one as the bandgap reference circuit provides high accuracy and is available in most technologies.

The term "bandgap" comes from bandgap energy, which represents for the energy

Figure 2.1: Circuit diagram showing the demand for bandgap reference

difference between the top of the valence band and the bottom of the conduction band. In other words, an electron requires this amount of energy to jump from one covalent band to another. The bandgap voltage for reference circuits specifically refers to the bandgap voltage of silicon, which can be modeled as a function of temperature:

$$V_{BG} = 1.17 - \frac{4.73 \times 10^{-4} T^2}{T + 635}.$$

(2.1)

For the temperature concerned in most applications, this voltage can be further linearized as  $1.20585 - 2.745 \times 10^{-4}T$ . Obviously, at absolute temperature of 0K, the bandgap voltage of silicon becomes a constant, 1.20585V [27].

### 2.2 Temperature Independent Reference

There are two kinds of temperature coefficients (TC), positive coefficient and negative coefficient. Summing the opposite TC voltage or current values with a suitable ratio, for example if

$$k_1 \oplus +k_2 \ominus = 0 \tag{2.2}$$

(here  $\oplus$  represents a positive temperature coefficient value, and  $\ominus$  represents a negative temperature coefficient value), then the final value is zero TC. For example, if there are two currents with the opposite TC direction, picking  $k_1$  and  $k_2$  will make

$$k_1 \frac{\partial I_1}{\partial T} + k_2 \frac{\partial I_2}{\partial T} = 0$$

(Here  $\partial I_1/\partial T = \oplus$ , and  $\partial I_2/\partial T = \oplus$ ), so that the final value  $I_{REF} = k_1I_1 + k_2I_2$ is independent of temperature variation.

#### 2.2.1 Negative Temperature Coefficient

The base-emitter voltage (  $V_{BE}$  ) of a bipolar-transistor has a negative TC. It is known that,

$$I_c = I_s e^{\frac{V_{BE}}{V_T}}$$

where  $V_T$  is the thermal voltage,  $I_s$  is the saturation current and  $V_{BE}$  is the base-emitter voltage of BJT. Voltage  $V_T = kT/q$ , in which k is the Boltzmann constant ( $k = 1.3806503 \times 10^{-23} m^2 kg s^{-2} K^{-1}$ ), T is the absolute temperature in K (Kelvin), and q is the electron charge ( $q = 1.602 \times 10^{-19}C$ ). Current  $I_s \propto \mu kT n_i^2$ , in which  $\mu$  is the mobility of minority carriers and  $n_i$  is the intrinsic minority carrier concentration of silicon. The mobility of minority carriers  $\mu \propto \mu_0 T^m (m \approx -\frac{3}{2})$ , and  $n_i^2 \propto T^3 \exp\left[-E_g/(kT)\right]$ . Symbol  $E_g$  is the bandgap energy of silicon, which approximately equals to 1.12eV. Thus,

$$I_s = bT^{4+m} \exp\left[-E_g/(kT)\right]$$

(2.3)

where b is a proportionality factor [24]. Also,

$$V_{BE} = V_T \ln \frac{I_c}{I_s} \tag{2.4}$$

Under the condition that the dependence on temperature of  $I_s$  is much more significant than that of  $I_c$ , the derivative of  $V_{BE}$  with respect to T can be taken by assuming  $I_c$  is constant, in other words, computing the temperature coefficient of  $V_{BE}$ :

$$\frac{\partial V_{BE}}{\partial T} = \frac{\partial V_T}{\partial T} \ln \frac{I_c}{I_s} - \frac{V_T}{I_s} \frac{\partial I_s}{\partial T}$$

(2.5)

With the derivative of  $I_s$  with respect to T from (1.1) and the definition of  $V_{BE}$  in (1.2), we can get the final derivative of  $V_{BE}$  [24]:

$$\frac{\partial V_{BE}}{\partial T} = \frac{\partial V_T}{\partial T} \ln \frac{I_c}{I_s} - (4+m)\frac{V_T}{T} - \frac{E_g}{kT^2}V_T$$

$$= \frac{V_{BE} - (4+m)V_T - E_g/q}{T}$$

(2.6)

It can be noticed that the  $V_{BE}$  temperature coefficient also depends on its magnitude. Assume  $V_{BE} \approx 750 mV$ , at temperature of 300K,  $\frac{\partial V_{BE}}{\partial T} \approx -1.5 mV/K$

Figure 2.2: PTAT voltage generation circuit diagram

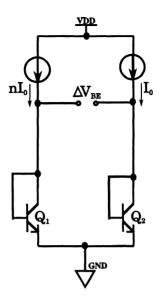

#### 2.2.2 Positive Temperature Coefficient

In bandgap references, the positive temperature coefficient is realized by generating a Proportional to Absolute Temperature (PTAT) voltage. When different current densities are used, the voltage difference between two bipolar transistors' base-emitter voltages can be considered as a PTAT voltage, Fig. 2.2 [24]. Here two identical bipolar transistors are used, and the current through these two transistors has a ratio of n, which means, the ratio of current densities is n. The voltage difference between the two output nodes is  $\Delta V_{BE}$ :

$$\Delta V_{BE} = V_{BE1} - V_{BE2}$$

$$= V_T \ln \frac{nI_0}{I_s} - V_T \ln \frac{I_0}{I_s}$$

$$= V_T \ln n$$

(2.7)

The temperature coefficient of  $\Delta V_{BE}$  can be

$$\frac{\partial \Delta V_{BE}}{\partial T} = \left(\frac{kT}{q}\right) / \ln n = \frac{k}{q} \ln n \tag{2.8}$$

As k, q and  $\ln n$  are all positive,  $\frac{\partial \Delta V_{BE}}{\partial T}$  will result in a positive number, and as shown in the equation, it is proportional to absolute temperature.

With positive temperature coefficient and negative temperature coefficient, a voltage value with zero temperature coefficient can be obtained,  $\frac{\partial V_{BE}}{\partial T} + m \frac{\partial \Delta V_{BE}}{\partial T} = 0$ . For example, if  $V_{BE}$ 's temperature coefficient is -1.5mV/K, in order for the total temperature coefficient to equal to zero, n needs to be 8 with m of approximately 9.

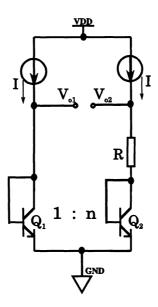

#### 2.3 Bandgap Reference

As discussed previously, summing the negative and positive temperature coefficient (TC) voltages together, a voltage reference that is independent of temperature variation can be obtained. In other words, 0 TC voltage:

$$V_{REF} = \alpha_1 V_{BE} + \alpha_2 [V_T \ln n] \tag{2.9}$$

where  $V_T \ln n$  is the difference between the base-emitter voltages of two bipolar transistors operating at different current densities. As mentioned in the last section, for example, if the environment is set to 300K,  $V_{BE} \approx 750mV$ , the temperature coefficient of  $V_{BE}$  is approximately -1.5mV/K, and  $\frac{\partial V_T}{\partial T} \approx 0.081mV/K$ . By setting  $\alpha_1=1$ ,

$$\alpha_1 \frac{\partial V_{BE}}{\partial T} + 0.081 \alpha_2 \ln n = 0 \tag{2.10}$$

Figure 2.3: Bandgap-reference generating circuit diagram

it can be calculated that  $\alpha_2 \ln n = 18.51$ , so that

$$V_{REF} = V_{BE} + 18.51 V_T = 1.228 V \tag{2.11}$$

where  $V_T = 25.85mV$  at absolute temperature of 300K.

The determination of the remaining variables  $\alpha_2$  and n is shown by the following example.

In Fig. 2.3,  $Q_2$  has a junction area of n times as that of  $Q_1$ , so that the current density of  $Q_2$  is n times less than that of  $Q_1$ . Suppose  $V_{o1} = V_{o2}$  is forced true, then  $V_{BE1} = V_{BE2} + RI$ , where  $RI = V_T \ln n$ . If  $\alpha_2 = 1$ , then  $\ln n = 18.51$ .

$V_{o2}$  can produce the exact voltage value demanded. However, there are two problems to be solved. First,  $V_{o1} = V_{o2}$  must be forced true; second,  $\ln n = 18.51$  is not practical as n should be  $e^{18.51}$ , a very high value in order to meet the demand of  $\ln n = 18.51$ . In this manner, an op-amp can solve the first problem while ratio circuit to increase  $\alpha_2$  is needed for solving the second problem.

### 2.4 Example of Bandgap Circuits

To further understand the bandgap reference circuits, two of the commonly used bandgap structures are shown in this section.

#### 2.4.1 Simple Bandgap Circuits Without Op-amp

The simplest compensation for temperature dependence is first-order compensation, which happens when the difference between  $V_{BE}$  of the two bipolar transistors biased in different current densities is added to the base-emitter voltage of a bipolar transistor.

A simple implementation without an op-amp is shown in Fig. 2.4, [28]. Transistor  $Q_3$  is n times larger than  $Q_4$  in size and  $Q_2$  is r times larger than  $Q_1$ . For  $Q_3$  and  $Q_4$ , they form a current mirror that produces a current of  $I_{Q_3}/I_{Q_4} = n$ ; while the density ratio between  $Q_1$  and  $Q_2$  is

$$\frac{D(Q_1)}{D(Q_2)} = rn$$

(2.12)

The voltage on  $R_2$  is

$$\Delta V_{BE} = V_{BE1} - V_{BE2} = \frac{kT}{q} \ln(nr)$$

(2.13)

The output then will be

$$V_{REF} = V_{BE1} + V_C$$

=  $V_{BE1} + nI_{R_2}R_1$

=  $V_{BE1} + n\frac{\Delta V_{BE}}{R_2}R_1$

=  $V_{BE1} + n\frac{R_1}{R_2}\frac{kT}{q}\ln(nr)$  (2.14)

Figure 2.4: Example of an simple bandgap circuit diagram

Figure 2.5: Simple bandgap with three Bipolar transistors circuit diagram

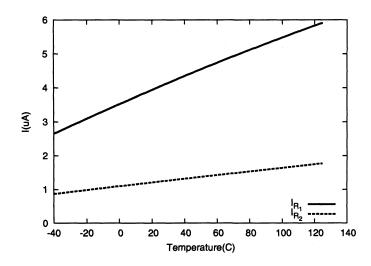

The simulation was done in Spice. With  $R_1 = 40k\Omega$  and  $R_2 = 102k\Omega$ , the currents were set to  $I_{Q_1} \approx 4\mu A$  and  $I_{Q_2} \approx 1.03\mu A$  at 0°C. Also because of this difference between the currents, the base-emitter voltages for  $Q_1$  and  $Q_2$  were different, forming  $\Delta V_{BE}$  for this configuration. For example, in Fig. 2.4,  $V_{BE2} \approx 0.74V$  and  $V_{BE3} \approx 0.8V$  at 0°C. In addition, the currents will vary according to the temperature variation, they are proportional to absolute temperature (PTAT) factors as can be seen in the simulation plot, Fig. 2.6.

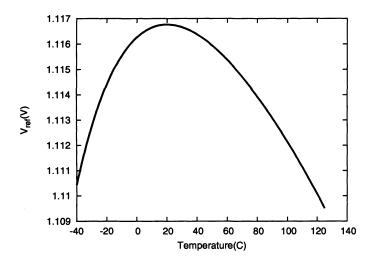

Temperature dependance of reference voltage generated by circuit shown in Fig. 2.4 is shown in Fig. 2.7.

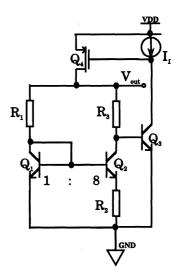

Another simple bandgap reference is shown in Fig. 2.5 [29]. The current source here produces a current for  $Q_3$  so that  $V_{BE3}$  can be fixed as  $I_{C3}$  is fixed. The output voltage is the summation of  $V_{BE3}$  and the voltage across  $R_3$ . As the current through  $R_3$  is a PTAT current, which has the positive temperature coefficient, the voltage across  $R_3$  is a PTAT voltage, which can compensate for the negative temperature coefficient of  $V_{BE3}$ . The size ratio of the three bipolar transistors is  $Q_1: Q_2: Q_3 =$

Figure 2.6: Simulation results of currents of the simple bandgap

Figure 2.7: Simulation result of the simple bandgap output voltage

1:8:1. Then  $\Delta V_{BE} = V_{R2} = \frac{kT}{q} \ln 8 = 46.06 mV$  (at 0°C).

As the *npn* bipolar model study showed, for a constant  $I_{CQ3}$ , for example  $15\mu A$ ,  $V_{BE3}$  will have approximately a -1.45389mV/K temperature dependence around room temperature. In Spice simulation,  $R_1 = R_3 = 12k\Omega$  and  $R_2 = 1.5k\Omega$  were applied, thus  $R_3/R_2 = 12k\Omega/1.5k\Omega = 8$ . As  $\Delta V_{BE}/273K = 46.06mV/273K =$ 0.1797mV/K (at 0°C), the PTAT part of the output has a positive temperature

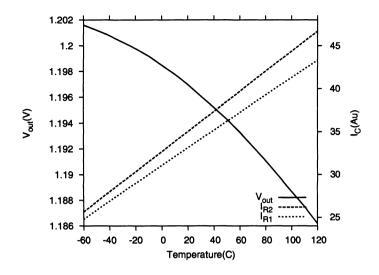

Figure 2.8: Simulation result of simple bandgap with three Bipolar transistors

dependence of  $V_{R3}/273K = \frac{\Delta V_{BE}}{R_2}R_3/273K = 0.1797mV/K \times 8 = 1.4376mV/K$ , which meets the demand for compensating the negative temperature dependence of  $V_{BE3}$  well. Figure 2.8 shows the output voltage of the circuit in Fig. 2.5 and the currents on  $R_1$  and  $R_2$ . Voltage  $V_{out}$  varies from 1.205V to 1.186V with the temperature of  $-60^{\circ}C \sim 125^{\circ}C$ , while the two currents are slightly different.

### 2.4.2 Bandgap Circuits With Op-amp

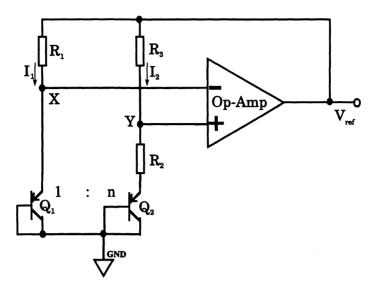

The most common configuration of a bandgap is composed of op-amp and ratio circuits, as Fig. 2.9 shows [26].

Points X, Y are at the same potential as the two inputs of the op-amp have the same DC voltage. In this way,

$$V_{REF} = V_{BE2} + (R_2 + R_3)I_2$$

$$I_2 = \frac{V_{BE1} - V_{BE2}}{R_2} = \frac{V_T \ln n}{R_2}$$

$$V_{REF} = V_{BE2} + (R_2 + R_3)\frac{V_T \ln n}{R_2}$$

(2.15)

Figure 2.9: Schematic of bandgap reference with op-amp

Figure 2.10: Simulation result of bandgap with op-amp output voltage

thus  $\alpha_2$  in (2.7) equals to  $\frac{R_2+R_3}{R_2} = \frac{R_3}{R_2} + 1$  forms the ratio circuit. Figure 2.10 shows the simulation of the output of the circuit in Fig. 2.9

The *pnp* transistor model in the simulation for this circuit has a  $V_{BE}$  with a TC of -2.0mV/K and  $V_{BE} \approx 565mV$ ,  $\alpha_2 \ln n = 24.69$  can be easily calculated. To minimize layout mismatch, the junction areas are chosen with a ratio of 1 : 8 so that when the same currents pass through the two BJTs, their current density ratio

is 8 : 1. In this case, only when  $\alpha_2 = 12$ ,  $\alpha_2 ln 8 \frac{\partial \Delta V_{BE}}{\partial T} \approx 2.0 mV/K$ . This value can perfectly compensate for  $V_{BE}$ 's negative temperature coefficient. In order to meet the demand of  $\alpha_2 = 12$  and to simplify the situation, the current was set to approximately 1mA by choosing  $R_1 = R3 = 7.375k\Omega$  and  $R_2 = 0.6676k\Omega$  respectively for ideal simulation in Spice. Here  $R_1 = R3$  guarantees the currents through  $Q_1$  and  $Q_2$  are the same. However, in practical CMOS design, a limit of 0.1mA exists for the maximum current through the transistor, this limit is to minimize the errors due to the high base resistance caused by the large lateral dimension between the base contact and the effective emitter region [26].

In Fig. 2.10 as the temperature varies from  $-55^{\circ}C$  to  $125^{\circ}C$ , the output voltage error is only 20mV (1.2275V - 1.2075V = 0.02V), which is good for this simple configuration. The bandgap circuit with op-amp is expected to produce more accurate results. However, the simulation results in Fig. 2.7 and Fig. 2.8 had slightly better accuracy because the newer technology was used for the simulation in those bandgap circuits without op-amp while in the simulation for the circuit in Fig. 2.9, older technology and imprecise bipolar transistor models were used.

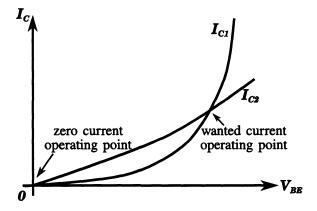

# 2.5 Start-Up Circuit

The common problem in all the references from the previous section is that there is a stable state at zero current point even if a power supply is provided. The bandgap circuit has two stable operating points. One is at zero current and the other one is at the desired current in the loop, Fig. 2.11. When there is zero current through the BJTs, the voltages at the input of the op-amp will also be at zero, plus there will not be any considerable difference between the two op-amp input voltages. This way the op-amp will not see any differential input and it will try to suppress any

Figure 2.11: The two stable operating points in bandgap reference circuits

disturbance that may bring it out of the zero current state. That means the bandgap circuit can be locked in the zero-state forever if it is not forced out of it by an extra circuit. Although parasitic capacitance associated with every node may help to bring the circuit out of the zero current state, it is unpredictable. To avoid such unpredictability, a start-up circuit is used, which for sure prevents the circuit from getting locked in the zero current state [30]. In other words, an extra start-up circuit is needed for proper operation.

For further discussion on the start-up sub-circuit, please refer to Chapter 3.

# 2.6 Summary

In this chapter, an example is given for illustration of the bandgap reference's importance. The term of "bandgap" is explained and the concept of building a bandgap circuit is presented, which involves adding voltages that have opposite temperature coefficients. The case studies show the results of both the simple bandgap circuits and bandgap circuit architectures with op-amp. Also, the need of a start-up circuit in the design is presented. Next chapter gives further discussion on a specific bandgap circuit configuration and the details to build it are followed.

# Chapter 3 Proposed Bandgap Circuit

In the previous chapter, bandgap voltage theory was presented and different bandgap voltage reference circuits were discussed. In this chapter, an accurate bandgap voltage reference working under 1.2V power supply is presented. The bandgap core circuit, the op-amp implementation, the start-up circuit and the output stage are discussed respectively.

# 3.1 Low-Voltage Bandgap Core Circuit

As it was presented in Chapter 2, the bandgap core circuit, nowadays, is usually composed by two or more bipolar-transistors. Thus, the analysis of BJT models in the available technology should be the first step to establish a whole circuit and the precise characterization and careful decision in choosing models guarantee the accuracy of the final output reference voltage. After choosing the model, two main concerns during the building of the circuit are the output's dependence on temperature change and power supply variation.

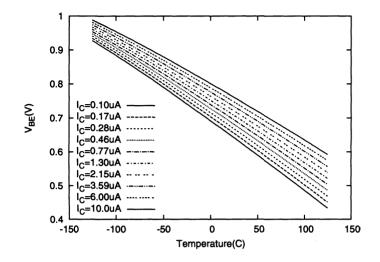

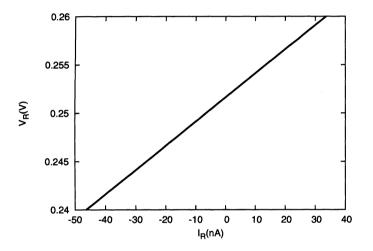

#### 3.1.1 NPN Model Characterization

In CMOS90nm technology, there are two kinds of lateral npn bipolar-transistor available. One has an emitter area of  $2\mu m \times 2\mu m$ , and the other one has an emitter area of  $5\mu m \times 5\mu m$ . Though the smaller one consumes much less area on chip, the bipolartransistor, which is comparatively larger was chosen for its better characterization in accordance to temperature change. Figure 3.1 shows the base-emitter voltage  $V_{BE}$ variation with the temperature change when different collector currents are implemented. One can see that for higher temperature, the transistor has a lower  $V_{BE}$ . In other words, the bipolar transistor base-emitter voltage has a negative temperature coefficient, as it was previously mentioned. A family of curves with different current in Fig. 3.1 also shows that with higher  $I_C$ ,  $V_{BE}$  is higher, 3.1.

$$V_{BE} = \frac{k}{q} T ln(\frac{I_c}{I_s}) \tag{3.1}$$

Also in this equation, it appears that  $V_{BE}$  should increase as temperature increases. However,  $V_{BE}$  acts oppositely because of the high temperature dependence of  $I_S$ .

It can be easily seen in Fig. 3.1, for different  $I_c$ ,  $V_{BE}$  exhibits different temperature coefficient. For example, with a current of  $1\mu A$ ,  $V_{BEtc} = (786.214mV - 459.27mV)/(-40^{\circ}C - 125^{\circ}C) = -1.98148mV/^{\circ}C$ ; while with a current of  $10\mu A$ ,  $V_{BEtc} = (832.936mV - 538.652mV)/(-40^{\circ}C - 125^{\circ}C) = -1.78354mV/^{\circ}C$ . In the available IC Design tool, the lowest temperature can be simulated is  $-40^{\circ}C$ , however, if an extended temperature of  $-273^{\circ}C$  can be investigated, all those family curves with different  $I_C$  should converge to a single point, which has a  $V_{BE}$  of 1.205V. This model, which is  $5\mu m \times 5\mu m$  was chosen because with reference to the simulation, the manual calculation result of  $V_{BE}$  at temperature of 0K is closer to 1.205V than  $V_{BE}$  of the other model, which may provide more accurate results during the circuit development.

For a higher  $I_c$ ,  $V_{BE}$  has a lower absolute temperature coefficient. While the current can not be infinitely high as low power consumption is demanded,  $I_C = 10\mu A$  is

Figure 3.1: Simulation results showing the dependence of  $V_{BE}$  on temperature chosen as the operating point of the bipolar transistors in the bandgap voltage reference circuit. Accordingly, the negative temperature coefficient to be compensated is fixed at  $-1.78354mV/^{\circ}C$ .

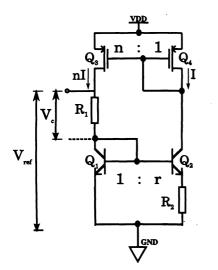

#### 3.1.2 Bandgap Voltage Generating Circuit

Given the intention that the nominal power supply should be at 1.2V in this lowvoltage circuit design, it would be impractical to design a traditional bandgap whose output voltage is around 1.205V (Refer to Chapter 2.1). However, the temperatureindependent output voltage can be realized by taking a fraction of the original bandgap voltage, specifically, using current terms proportional to it. In Fig. 3.2,  $V_A$  and  $V_B$  are forced equal by the op-amp. The voltage across  $R_0$  is a PTAT voltage as  $V_{R0} = \Delta V_{BE} = V_{BE1} - V_{BE2}$ . Thus, the current through  $R_0$  is PTAT (assuming  $R_0$  is temperature independent). The voltage value across  $R_1$  and  $R_2$  equals to the base-emitter voltage of the diode connected BJT transistor  $Q_1$ , which has a negative temperature coefficient. The current through  $M_2$  (also  $M_1$ , because  $I_1 = I_2$ as  $M_1$  and  $M_2$  are identical and have the same  $V_{GS}$  and  $V_{DS}$ ) can be temperature

Figure 3.2: Bandgap voltage generating circuit diagram

independent, as follows:

$$I_1 = I_2 = \frac{V_{BE}}{R_2} + \frac{V_T \ln N}{R_0} = \frac{1}{R_2} (V_{BE} + \frac{R_2}{R_0} V_T \ln N)$$

(3.2)

$I_3$  can be slightly different, depends on the size of  $M_3$  and the load. (Refer to Chapter 1.4) However,  $I_3$  should be proportional to  $I_1$  and  $I_2$ , since the gate of  $M_3$  is controlled by the same op-amp output. Assuming the load is a temperature independent resistor at this time, the output voltage is as follows,

$$V_{REF} = I_3 R_{load} = k I_1 R_{load} = \frac{k R_{load}}{R_2} [V_{BE} + \frac{R_2}{R_0} V_T \ln N]$$

(3.3)

If  $V_T = kT/q$  is used to obtain a PTAT voltage, it is well known that  $V_T$  has to be multiplied by approximately 22 to compensate for the temperature dependence of the diode voltage [31]. Thus,

$$\frac{R_2}{R_0} \ln N = 22 \tag{3.4}$$

For the sake of BJT transistor layout matching issues, N = 8 is used. (Refer to Chapter 4)  $R_2/R_0$ , therefore, should be around 10. According to the current needed in the two bandgap core branches,  $R_0$  and  $R_2(R_1)$  can be determined. The decision of current is also related to the power change tolerance of the circuit, which is discussed in the next section.

#### 3.1.3 Sensitivity to Power Supply Variation

ί.

In Fig. 3.2, the bandgap voltage generating circuit,  $M_1$ ,  $M_2$  should be large enough to tolerate the power change. The saturation current equation shows:

$$I_{D1,2} = \frac{1}{2} K'_p \frac{W}{L} (V_{GS1,2} - V_{th})^2 (1 + \lambda V_{DS1,2})$$

(3.5)