#### Western University

#### Scholarship@Western

**Digitized Theses**

**Digitized Special Collections**

2009

# A Three-Phase Single-Stage AC-DC ZVZCS PWM Full-Bridge Converter

Dunisha Savindri Wijeratne

Follow this and additional works at: https://ir.lib.uwo.ca/digitizedtheses

#### **Recommended Citation**

Wijeratne, Dunisha Savindri, "A Three-Phase Single-Stage AC-DC ZVZCS PWM Full-Bridge Converter" (2009). *Digitized Theses*. 3759.

https://ir.lib.uwo.ca/digitizedtheses/3759

This Thesis is brought to you for free and open access by the Digitized Special Collections at Scholarship@Western. It has been accepted for inclusion in Digitized Theses by an authorized administrator of Scholarship@Western. For more information, please contact wlswadmin@uwo.ca.

# A Three-Phase Single-Stage AC-DC ZVZCS PWM Full-Bridge Converter

(Spine title: A Novel Three-Phase ZVZCS Full-Bridge Converter)

(Thesis format: Monograph)

by

Dunisha Savindri Wijeratne

Graduate Program

in

Engineering Science

Department of Electrical and Computer Engineering

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Engineering Science

School of Graduate and Postdoctoral Studies

The University of Western Ontario

London, Ontario, Canada

© Dunisha S. Wijeratne 2009

# **Certificate of Examination**

# THE UNIVERSITY OF WESTERN ONTARIO SCHOOL OF GRADUATE AND POSTDOCTORAL STUDIES CERTIFICATE OF EXAMINATION

| Chief Advisor:         | Examining Board:                             |

|------------------------|----------------------------------------------|

| Dr. Gerry Moschopoulos | Dr. Jagath Samarabandu                       |

| Advisory Committee:    | Dr. Kazimierz Adamiak                        |

|                        | Dr. Mile Ostojic                             |

|                        |                                              |

|                        | thesis by                                    |

|                        | vindri Wijeratne                             |

|                        | titled: C ZVZCS PWM Full-Bridge Converter    |

|                        | rtial fulfillment of the                     |

|                        | for the degree of                            |

| •                      | gineering Science                            |

|                        |                                              |

| Date:                  |                                              |

|                        | Chair of Examining Board<br>Dr. Abbas Samani |

#### Abstract

It is standard practice to use two separate power converters to convert an ac input voltage to a desired and isolated dc output voltage. A front-end ac-dc converter is used to convert the input ac voltage into an intermediate dc voltage which is then fed into a dc-dc converter with transformer isolation. The front-end converter also performs input power factor correction (PFC) to shape the input currents to be sinusoidal and in phase with the input voltages to maximize the use of the available source power.

Conventional two-stage power conversion, however, requires two power converters and there has been considerable interest to try to integrate the PFC and dc-dc conversion functions in a single power converter to reduce cost and complexity. Although many of these single-stage converters have been proposed for low power, single-phase applications, there have been relatively few higher power three-phase converters that have been proposed. This is due to the challenges faced when trying to perform PFC and dc-dc conversion for a wider load range.

A new three-phase, single-stage ac-dc full-bridge converter is proposed in this thesis. The outstanding features of the new converter are that it is relatively simple and it can perform PFC using standard phase-shift pulse width modulation (PWM). In the thesis, derivation of the converter is discussed and its general operation is reviewed. The modes of operation of the converter are explained in detail and analyzed and the results of the analysis are used to develop guidelines for its design. The feasibility of the proposed converter is confirmed with experimental results that were obtained from a prototype and are presented in this thesis.

KEY WORDS: Three-Phase Ac-Dc Rectifiers, Power Factor Correction, Zero Voltage Zero Current Switching.

## Acknowledgements

I would like to acknowledge and thank my supervisor Dr. Gerry Moschopoulos for his encouragement, very valuable analytical, practical and academic guidance and advice throughout in all aspect of my research and in writing and publishing of thesis. I am also thankful to the members of my examination committee, Dr. Jagath Samarabandu, Dr. Kazimierz Adamiak and Dr. Mile Ostojic.

I also appreciate the support given by Dr. S. Kumarawadu and Dr. J. Samarabandu from the very initial stage of academic life.

Further I wish to recognize and admire the guidance and support given by especially, Eugen Porter in the Machines Shop and many others, e.g. Dr. Sondeep Bassan, administrative staff of the ECE department of UWO and the ePEARL laboratory engineer in Queens University of Kingston.

Finally I would like to record my deepest gratitude to my late-father Indra for his unrelenting encouragement and help for me to continue my higher education, sincere thanks to my good friend Niroshan, to my uncles Chandra and Sam for motivating and encouraging me to finalize my masters.

And last but not least, I am thankful to my loving mother Indira and to Aunt Sandya for the endless love given to me.

# Dedication

This Thesis is dedicated to my loving Father. Without his love, wisdom, and guidance, I would not have the realized my goals to make my dreams come true!!!

# Table of Contents

| C  | ertific | cate of | Exam    | ina    | tio                  | n    | •                | •   | •   | •  | •    |     | •   | •  | •   | •  | • |     | • | • | • | • | • | • | • | • | • | • | • | ii  |

|----|---------|---------|---------|--------|----------------------|------|------------------|-----|-----|----|------|-----|-----|----|-----|----|---|-----|---|---|---|---|---|---|---|---|---|---|---|-----|

| A۱ | bstra   | ct      |         | • •    |                      |      | •                |     | •   | •  | •    |     |     | •  |     |    | • |     | • | • |   |   |   |   | • | • | • | • |   | iii |

| A  | cknov   | vledge  | ments   | •      |                      |      |                  |     | •   |    | •    |     | •   | •  |     | •  |   | • • |   | • |   |   | • |   |   | • | • | • |   | iv  |

| D  | edica   | tion .  |         | •      |                      |      |                  |     |     |    | •    |     | •   | •  | •   | •  | • |     |   | • |   |   | • |   |   |   | • |   |   | v   |

| Li | st of   | Figure  | es      | •      |                      |      |                  |     |     | •  |      |     | •   |    | •   | •  |   |     | • |   | • |   | • |   | • |   | • | • | • | ix  |

| A  | crony   | ms .    |         | •      |                      |      | •                |     | •   |    |      |     | •   |    |     |    | • |     |   | • | • |   |   | • |   |   |   | • |   | xii |

| N  | omen    | clatur  | e       | • •    |                      |      |                  |     | •   |    |      |     | •   | •  |     |    |   |     |   |   | • |   |   | • | • | • | • | • |   | xiv |

| 1  | Intr    | oducti  | on      |        |                      |      |                  |     |     |    |      |     |     |    |     | •  |   |     |   |   |   |   |   |   |   |   |   |   |   | 1   |

|    | 1.1     | Introd  | uction  | to I   | ow                   | er   | Εl               | .ec | tre | on | ics  | · . |     |    |     |    |   |     |   |   |   |   |   |   |   |   |   |   |   | 1   |

|    | 1.2     | Semico  | onducto | or D   | evi)                 | .ces | ι.               |     |     |    |      |     |     |    |     |    |   |     |   |   |   |   |   |   |   |   |   |   |   | 2   |

|    |         | 1.2.1   | MOSE    |        |                      |      |                  |     |     |    |      |     |     |    |     |    |   |     |   |   |   |   |   |   |   |   |   |   |   | 2   |

|    |         | 1.2.2   | IGBT    | s.     |                      |      |                  |     |     |    |      |     |     |    |     |    |   |     |   |   |   |   |   |   |   |   |   |   |   | 4   |

|    | 1.3     | Switch  | ing Ch  | ara    | cter                 | rist | ics              | s . |     |    |      |     |     |    |     |    |   |     |   |   |   |   |   |   |   |   |   |   |   | 5   |

|    | 1.4     | Two-S   | tage A  | c-D    | cР                   | ow   | er               | C   | on  | ve | rsi  | ion |     |    |     |    |   |     |   |   |   |   |   |   |   |   |   |   |   | 7   |

|    |         | 1.4.1   | Full-B  | rid    | ge (                 | Cor  | ıve              | ert | er  | C  | ре   | era | tic | n  |     |    |   |     |   |   |   |   |   |   |   |   |   |   |   | 8   |

|    |         | 1.4.2   | Ac-Do   | Fr     | $\operatorname{ont}$ | -Er  | $^{\mathrm{nd}}$ | C   | on  | νe | erte | ers |     |    |     |    |   |     |   |   |   |   |   |   |   |   |   |   |   | 11  |

|    | 1.5     | Three-  | Phase   | $\sin$ | gle-                 | Sta  | age              | e A | ٩c  | -D | c (  | Со  | nv  | er | te: | rs |   |     |   |   |   |   |   |   |   |   |   |   |   | 15  |

|    | 1.6     | Thesis  | Objec   | tive   | s.                   |      |                  |     |     |    |      |     |     |    |     |    |   |     |   |   |   |   |   |   |   |   |   |   |   | 17  |

|    | 1.7     | Thesis  | Outlin  | ie.    |                      |      |                  |     |     |    |      |     |     |    |     |    |   |     |   |   |   |   |   |   |   |   |   |   |   | 18  |

### Table of Contents

| 2 | Fun | damental Principles                                                          | 21 |

|---|-----|------------------------------------------------------------------------------|----|

|   | 2.1 | Introduction                                                                 | 21 |

|   | 2.2 | Fundamental Principles - Ac-Dc Three-Phase Single-Switch Buck Con-           |    |

|   |     | verter                                                                       | 21 |

|   | 2.3 | Fundamental Principles - Dc-Dc Zero-Voltage-Zero-Current Switching           |    |

|   |     | (ZVZCS) Full-Bridge Converter                                                | 25 |

|   | 2.4 | Conclusion                                                                   | 33 |

| 3 | AN  | New Three-Phase Single-Stage Ac-Dc Converter                                 | 34 |

|   | 3.1 | Introduction                                                                 | 34 |

|   | 3.2 | General Operating Principles                                                 | 34 |

|   | 3.3 | Modes of Operation                                                           | 36 |

|   | 3.4 | Converter Features                                                           | 48 |

|   | 3.5 | Conclusion                                                                   | 49 |

| 4 | Cor | nverter Analysis                                                             | 50 |

|   | 4.1 | Introduction                                                                 | 50 |

|   | 4.2 | Input Capacitor Relations                                                    | 50 |

|   |     | 4.2.1 Relation Between Input Capacitor Value and Peak Switch Voltage         | 50 |

|   |     | 4.2.2 Relation Between Input Capacitor Value and Output Dc Voltage           | 53 |

|   |     | 4.2.3 Relation Between Input Capacitors $C_a$ , $C_b$ , $C_c$ and Duty Ratio |    |

|   |     | $D \ldots \ldots \ldots \ldots$                                              | 54 |

|   |     | 4.2.4 Converter Input Resistance                                             | 57 |

|   |     | 4.2.5 Output to Input Voltage Ratio                                          | 63 |

|   | 4.3 | Input Inductors $(L_a, L_b \text{ and } L_c)$                                | 68 |

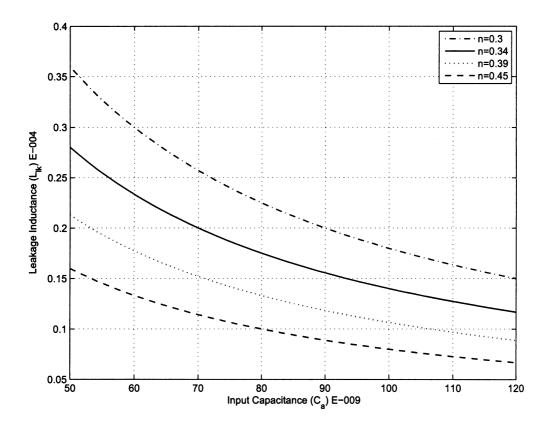

|   | 4.4 | Transformer Leakage Inductance $(L_{lk})$                                    | 71 |

|   | 4.5 | Auxiliary Capacitor $(C_x)$                                                  | 73 |

|   | 4.6 | Conclusion                                                                   | 75 |

| 5                | Co     | nverte | r Design and Experimental Results                                       | 76  |

|------------------|--------|--------|-------------------------------------------------------------------------|-----|

|                  | 5.1    |        | duction                                                                 | 76  |

|                  | 5.2    | Desig  | n Example                                                               | 76  |

|                  |        | 5.2.1  | Transformer Turns Ratio n and Duty Ratio $D$                            | 78  |

|                  |        | 5.2.2  | Input Capacitors $(C_a, C_b, \text{ and } C_c)$ and Peak Switch Voltage |     |

|                  |        |        | Stress $V_{sw,pk}$                                                      | 80  |

|                  |        | 5.2.3  | Input Inductors $(L_a, L_b \text{ and } L_c) \dots \dots \dots \dots$   | 82  |

|                  |        | 5.2.4  | Transformer Leakage inductance $(L_{lk})$                               | 83  |

|                  |        | 5.2.5  | Auxiliary Capacitor $(C_x)$                                             | 83  |

|                  | 5.3    | Exper  | rimental Results                                                        | 84  |

|                  |        | 5.3.1  | ZVS Leg Switching Waveforms                                             | 85  |

|                  |        | 5.3.2  | ZCS Leg Switching Waveforms                                             | 86  |

|                  |        | 5.3.3  | Input Voltage and Current Waveforms                                     | 87  |

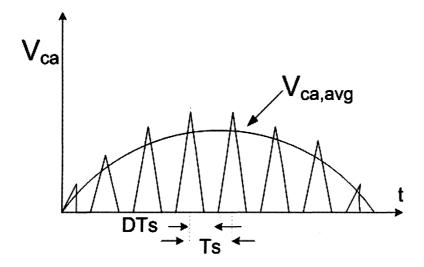

|                  |        | 5.3.4  | Input Capacitor Voltage Waveforms                                       | 88  |

|                  | 5.4    | Concl  | usion                                                                   | 88  |

| 6                | Cor    | clusio | n                                                                       | 93  |

|                  | 6.1    |        | luction                                                                 | 93  |

|                  | 6.2    |        | nary                                                                    | 93  |

|                  | 6.3    |        | usion                                                                   | 94  |

|                  | 6.4    |        | ibutions                                                                | 95  |

|                  | 6.5    |        | sal for Future Work                                                     | 96  |

| $\mathbf{A}_{]}$ | ppen   | dices  |                                                                         |     |

| A                | Mat    | lab Co | $\operatorname{odes}$                                                   | 102 |

|                  | A.1    | Codes  | for Programs in Chapter 4                                               | 102 |

|                  |        | A.1.1  | Equations Solutions-4.42                                                | 102 |

|                  |        | A.1.2  | Figure 4.5                                                              | 104 |

|                  |        | A.1.3  | Figure 4.6                                                              | 106 |

|                  |        | A.1.4  | Figure 4.7                                                              | 108 |

|                  |        | A.1.5  |                                                                         | 110 |

|                  |        | A.1.6  | Figure 4.10                                                             | 112 |

| Cı               | ırricı | սևստ Ն | Vitae                                                                   | 114 |

# List of Figures

| 1.1  | Block diagram of a power electronics system                              | 2  |

|------|--------------------------------------------------------------------------|----|

| 1.2  | Power MOSFET symbol                                                      | 3  |

| 1.3  | IGBT symbol                                                              | 5  |

| 1.4  | Non-ideal switching characteristics of a semiconductor device            | 5  |

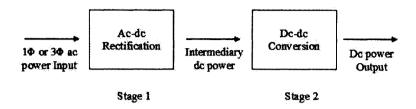

| 1.5  | Block diagram of Two-Stage ac-dc converters                              | 8  |

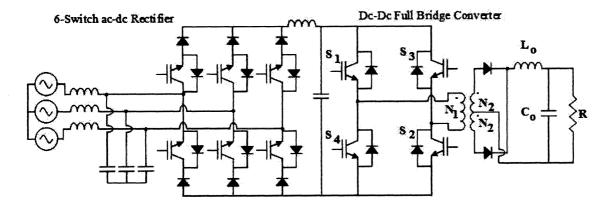

| 1.6  | Three-phase ac-dc six switch two-stage full-bridge converter             | Ö  |

| 1.7  | Dc-dc full-bridge converter                                              | Ć  |

| 1.8  | Typical dc-dc full-bridge waveforms                                      | 12 |

| 1.9  | Three-phase ac-dc converter using three single-phase modules             | 13 |

| 1.10 | Three-phase ac-dc converter with four switches                           | 14 |

| 1.11 | Three-phase ac-dc single-switch PFC front-end boost converter            | 15 |

| 1.12 | Input line current waveform of a three-phase ac-dc single-switch boost   |    |

|      | converter (half-line cycle)                                              | 15 |

| 1.13 | Three-phase ac-dc single-switch PFC front-end buck converter             | 16 |

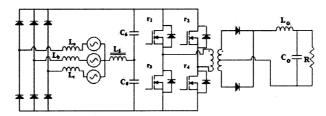

| 1.14 | Examples of three-phase, single-stage converters                         | 20 |

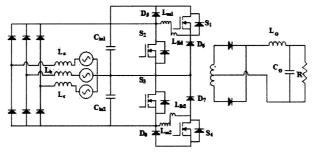

| 2.1  | Ac-dc converter with single-switch buck rectifier and dc-dc full-bridge  |    |

|      | converter                                                                | 22 |

| 2.2  | Three-phase ac-dc single-switch PFC buck converter                       | 22 |

| 2.3  | Steady state modes of the three-phase single-switch buck converter       | 24 |

| 2.4  | Input capacitor voltage of a three-phase, single-switch, ac-dc buck con- |    |

|      | verter (half-line cycle)                                                 | 26 |

| 2.5  | Three-phase single-stage ac-dc converter with conventional full-bridge.  | 26 |

| 2.6  | Dc-dc PWM ZVZCS full-bridge converter                                    | 28 |

| 2.7  | Modes of operation of dc-dc ZVZCS full bridge PWM converter              | 31 |

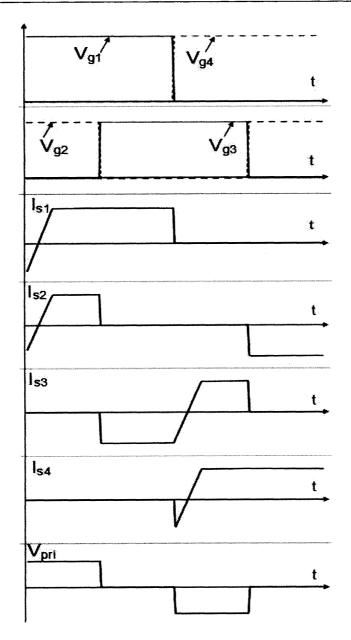

| 2.8  | Steady state waveforms of dc-dc ZVZCS full bridge PWM converter          | 32 |

| 3.1  | Proposed three-phase single-stage ac-dc converter with ZVZCS full-       |    |

|      | bridge                                                                   | 35 |

| 3.2  | Comparison of the proposed converter to a three-phase single switch                                     |    |

|------|---------------------------------------------------------------------------------------------------------|----|

|      | buck converter                                                                                          | 36 |

| 3.3  | Modes of converter operation                                                                            | 38 |

| 3.4  | Proposed converter typical waveforms                                                                    | 39 |

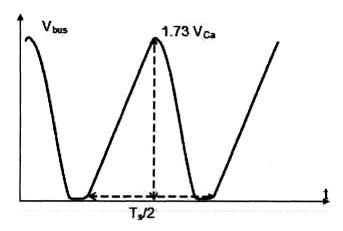

| 4.1  | Bus voltage of the proposed converter when input capacitors in DVM.                                     | 52 |

| 4.2  | Dc-dc full bridge converter with L-C filter                                                             | 56 |

| 4.3  | Steady state modes of operation of the single-phase equivalent circuit.                                 | 56 |

| 4.4  | Proposed converter                                                                                      | 60 |

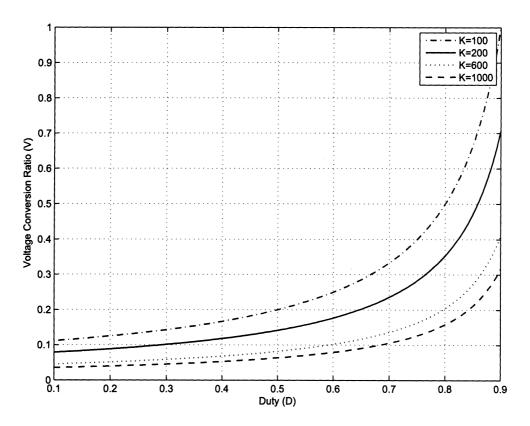

| 4.5  | V vs. $D$ for selected $K$ values                                                                       | 65 |

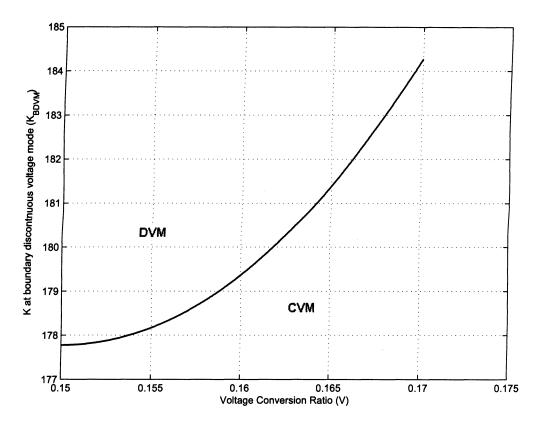

| 4.6  | The curve of $K_{BDVM}$ vs. $V_{BDVM}$                                                                  | 68 |

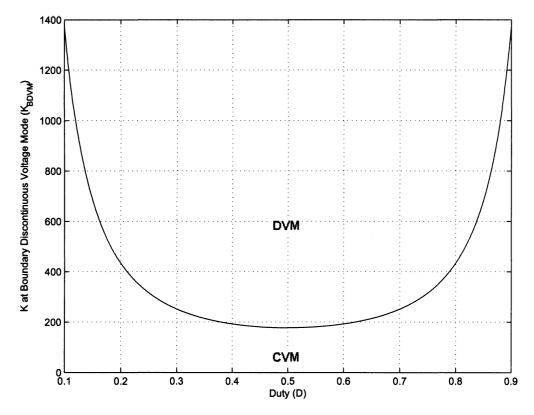

| 4.7  | $K_{BDVM}$ vs. D- $K_{BDVM}$ for BDVM operation for the selected duty                                   |    |

|      | range                                                                                                   | 69 |

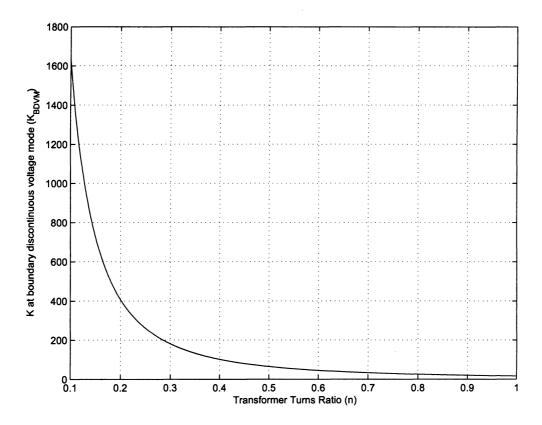

| 4.8  | $K_{BDVM}$ vs. $n$ for BDVM operation                                                                   | 70 |

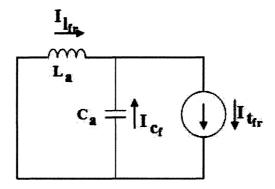

| 4.9  | Single-phase equivalent input filter diagram                                                            | 70 |

| 4.10 | Curves of $L_{lk}$ vs. $C_a$ for different values of $n$                                                | 73 |

| 5.1  | Triangular input capacitor voltage and sinusoidal envelope                                              | 80 |

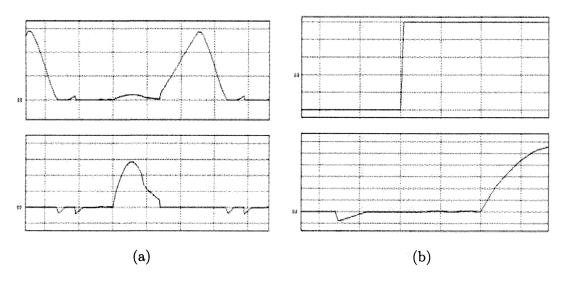

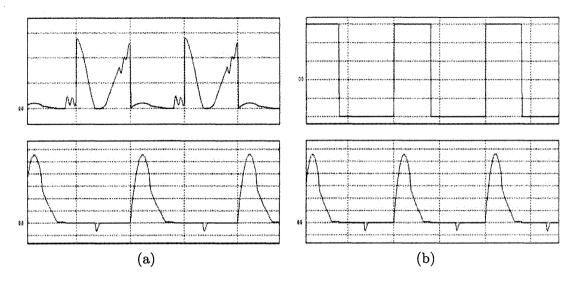

| 5.2  | Simulation results of typical (a) ZVS switch voltage (top) and switch                                   |    |

|      | current (bottom) [V: 250V/div, I: $10A/div$ , t: $5\mu s/div$ ], (b) Gate pulse                         |    |

|      | (top) and switch current (bottom) [V: $5V/\text{div}$ , I: $10A/\text{div}$ , t: $1\mu s/\text{div}$ ]. | 86 |

| 5.3  | Experimental results of (a) ZVS switch voltage (top) and switch current                                 |    |

|      | (bottom) [V: $500V/\text{div}$ , I: $25A/\text{div}$ , t: $2.5\mu\text{s/div}$ ], (b) Gate pulse (top)  |    |

|      | and switch current (bottom) [V: 25V/div, I: 25A/div, t: $1\mu$ s/div]                                   | 87 |

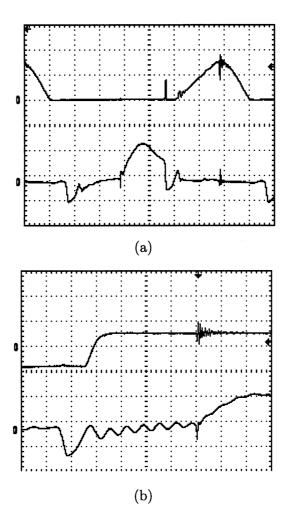

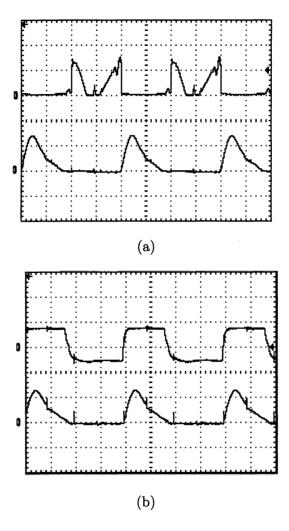

| 5.4  | Simulated waveforms of (a) ZCS switch voltage (top) and switch cur-                                     |    |

|      | rent (bottom) [V: 250V/div, I: 5A/div, t: $5\mu$ s/div]. (b) Gate pulse                                 |    |

|      | (top) and switch current (bottom) [V: $5V/\text{div}$ , I: $10A/\text{div}$ , t: $5\mu s/\text{div}$ ]. | 88 |

| 5.5  | Experimental waveforms of(a) ZCS switch voltage (top) and switch                                        |    |

|      | current (bottom) [V: $500V/\text{div}$ , I: $25A/\text{div}$ , t: $5\mu s/\text{div}$ ]. (b) Gate       |    |

|      | pulse (top) and switch current (bottom) [V: 25V/div, I: 10A/div, t:                                     |    |

|      | $5\mu \mathrm{s/div}$ ]                                                                                 | 89 |

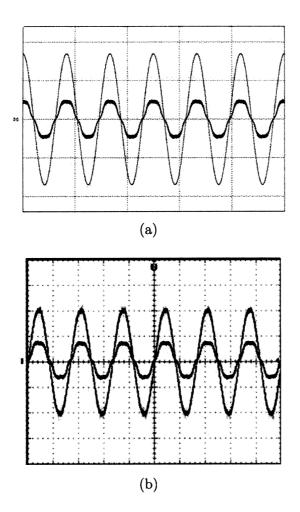

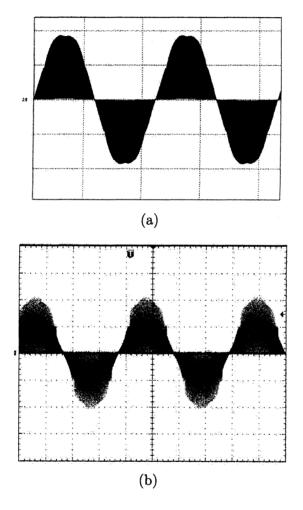

| 5.6  | (a) Simulation of input phase voltage and input line current [V: 100V/-                                 |    |

| 2.0  | div, I: 20A/div, t: 8ms/div]., (b) Experimental input phase voltage                                     |    |

|      | and input line current [V: 75V/div, I: 10A/div, t: 8ms/div]]                                            | 90 |

| List | of | <b>Figures</b> |

|------|----|----------------|

|      | ~, | - 19 w. cc     |

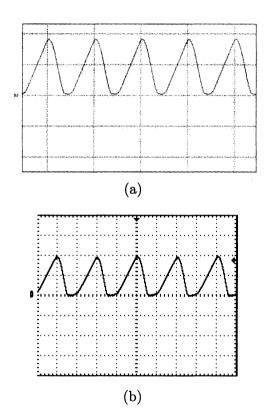

| 5.7 | (a) Simulated voltage waveform of input capacitor $C_a$ (b) Experimental |    |

|-----|--------------------------------------------------------------------------|----|

|     | input capacitor voltage across $C_a$ [V: 200V/div, t=5ms/div]            | 91 |

| 5.8 | (a) Simulation results of the input capacitor voltage measured across    |    |

|     | $C_a$ (b) Experimental results of the input capacitor voltage measured   |    |

|     | across $C_a$ [V: 200V/div, t=4ms/div]]                                   | 92 |

## Acronyms

Ac Alternate current

BDVM Boundary Discontinuous Voltage Mode

**BJT** Bipolar Junction Transistor

C Collector

CVM Continuous Voltage Mode

Dc Direct current

**D** Drain

**DVM** Discontinuous Voltage Mode

$egin{array}{ll} {f E} & & Emitter \ {f G} & & Gate \end{array}$

IGBT Insulated Gate Bipolar Transistor

L-C Inductive-Capacitive

MOSFET Metal Oxide Semiconductor Field Effect Transistor

PFC Power Factor Correction

PWM Pulse Width Modulation

rms root mean square

S Source

tf Transformer

ZCS Zero Current Switching

ZVS Zero Voltage Switching

**ZVZCS** Zero Voltage Zero Current Switching

# Nomenclature

| C                 | Input capacitor of single-phase equivalent circuit with L-C |

|-------------------|-------------------------------------------------------------|

|                   | filter                                                      |

| $C_a$             | Input capacitor of phase-a                                  |

| $C_b$             | Input capacitor of phase-b                                  |

| $C_{BDVM}$        | Input capacitor at boundary discontinuous voltage mode      |

| $C_c$             | $Input\ capacitor\ of\ phase-c$                             |

| $C_o$             | Output filter capacitor                                     |

| $C_{sw}$          | Switch capacitance between drain/collector and source/emit- |

|                   | ter                                                         |

| $C_x$             | Auxiliary Capacitor                                         |

| D                 | $Duty \ ratio$                                              |

| D1                | Rectifier diode in dc-dc PWM full-bridge converter          |

| $D_1$             | Normalized discharging time of $C$                          |

| D2                | Rectifier diode in dc-dc PWM full-bridge converter          |

| $D_{b}$           | Diode in three-phase single switch buck converter           |

| $D_c$             | Auxiliary circuit charging diode                            |

| $D_d$             | Auxiliary circuit discharging diode                         |

| $E_1$             | Energy fed to load by $C_x$                                 |

| $E_2$             | Energy given to discharge $L_{lk}$ by $C_x$                 |

| $E_a$             | Energy input by Phase-a for $\frac{\pi}{6}$                 |

| $E_b$             | Energy input by Phase-b for $\frac{\pi}{6}$                 |

| $E_c$             | Energy input by Phase-c for $\frac{\pi}{6}$                 |

| $E_{C_x}$         | Energy stored in $C_x$                                      |

| $E_{in}$          | Total input energy                                          |

| $E_{out}$         | Output Energy                                               |

| $f_l$             | Line frequecny                                              |

| $f_r$             | Dominant harmonic frequency (sideband)                      |

| $f_{\mathcal{S}}$ | Switching frequency                                         |

| $I_{a,pk}$        | Phase-a peak current                                        |

| $I_a$             | Phase-a current                                             |

|                   |                                                             |

| $I_C$                           | Current through C                                 |

|---------------------------------|---------------------------------------------------|

| $I_{C_a}$                       | Current through $C_a$                             |

| $I_{c_{fr}}$                    | Harmonic current in C                             |

| $I_{C_x}$                       | Current through $C_x$                             |

| $I_d$                           | Current through switch body diode                 |

| $I_{in}$                        | Input current in equivalent single-phase circuit  |

| $IL_{a,ave}$                    | Average Input Line Current                        |

| $I_{L_{oldsymbol{a}}}$          | Current in $L_a$                                  |

| $I_{l_{f_r}}$                   | $Harmonic\ current\ in\ L$                        |

| $I_{L_{lk}}$                    | Current in $L_{lk}$                               |

| $I_{L_o}$                       | Average L <sub>o</sub> current                    |

| $I_{mag}$                       | Maganetizing current                              |

| $I_{o}$                         | Load current                                      |

| $I_{pri}$                       | Transformer primary current                       |

| $I_{S1}$                        | Current in $S_1$                                  |

| $I_{S2}$                        | Current in $S_2$                                  |

| $I_{S3}$                        | Current in $S_3$                                  |

| $I_{S4}$                        | Current in $S_4$                                  |

| $\emph{\textbf{\emph{i}}}_{T-}$ | Transient switch current from on/off or off/on    |

| $I_{t_{f_r}}$                   | Total harmonic current of frequency $f_r$         |

| K                               | Circuit parameter                                 |

| $K_{BDVM}$                      | $K\ at\ boundary\ discontinuous\ voltage\ mode$   |

| L                               | input inductor in equivalent single-phase circuit |

| $L_a$                           | Input filter indcutor-phase-a                     |

| $L_{m{b}}$                      | Input filter indcutor-phase-b                     |

| $L_{oldsymbol{c}}$              | $Input\ filter\ indcutor-phase-c$                 |

| $L_{lk,min}$                    | Minimum leakage inductance                        |

| $L_{lk}$                        | Leakage inductor                                  |

| $L_{o}$                         | Output filter indcutor                            |

| n                               | Transformer turns ratio                           |

| N1                              | Number of primary turns                           |

| N2                              | Number of secondary turns                         |

$P_{T-}$  Power loss during the switch transition

R Resistive load

$R_a$  Input resistance, phase-a

rads Radians

R<sub>in</sub> Input resistance, equivalent single-phase circuit

t time

TC Time constant  $T_s$  Switching period

V dc output to ac input voltage ratio

$egin{array}{lll} V_a & Instantaneous\ phase-a\ voltage \ V_b & Instantaneous\ phase-b\ voltage \ \end{array}$

$V_{BDVM}$  Voltage at boundary discontiunous voltage mode

$egin{array}{lll} V_{bus,ave} & Average \ bus \ voltage \ V_{bus,vk} & Peak \ bus \ voltage \ \end{array}$

$egin{array}{lll} V_{bus} & & & Instantaneous \ bus \ voltage \ & V_{C,pk} & & Peak \ voltage \ & across \ C \ & V_{C} & & Input \ Capacitor \ Voltage \ \end{array}$

$V_c$  Instantaneous phase-c Voltage

$egin{array}{ll} V_{C_{a,avg}} & Average\ voltage\ across\ C_a \ V_{C_{a,nk}} & Peak\ voltage\ across\ C_a \ \end{array}$

$V_{C_a}$  Instantaneous voltage across  $C_a$

$V_{C_{x,min}}$  Minimum voltage of  $C_x$

$V_{C_{x,pk}}$  Peak voltage of  $C_x$

$V_{C_x}$  Instantaneous voltage of  $C_x$

$V_d$  Source Voltage

$V_{fb}$  Instantaneous full-bridge input voltage

$egin{array}{lll} V_{g1} & Gate\ voltage\ pulse,\ S_1 \ V_{g2} & Gate\ voltage\ pulse,\ S_2 \ V_{q3} & Gate\ voltage\ pulse,\ S_3 \ \end{array}$

$\omega_l$

$V_{a4}$ Gate voltage pulse,  $S_4$  $V_{qs}$ Gate-Source voltage Input voltage to equivalent single-phase circuit  $V_{in}$  $V_l$ Line-to-line peak Voltage line-to-line rms volateg  $v_{ll,rms}$  $V_{L_{lk}}$ Voltage across  $L_{lk}$ Output voltage  $V_{o}$ Average tf primary voltage  $V_{p,ave}$  $V_p$ tf primary voltage Peak phase voltage  $V_{ph,pk}$ Peak Phase voltage-equivalent single-phase circuit  $V_{pk}$  $V_{pri}$ Tf primary voltage Average secondary rectifier voltage  $V_{rec,ave}$ secondary rectifier voltage  $V_{rec}$ Tf secondary side average voltage  $V_{s,ave}$ Transformer Secondary Voltage  $V_s$ Switch 1- High side MOSFET  $V_{S1}$  $V_{S1}$ Switch 2- Low side IGBT Switch 3- High side IGBT  $V_{S1}$ Switch 4- Low side MOSFET  $V_{S1}$ Voltage of  $S_1$  $V_{Sw1}$  $V_{Sw2}$ Voltage of  $S_2$ Peak switch voltage  $V_{sw,pk}$ Instantaneous switch voltage  $V_{sw}$ Transient switch voltage from on/off or off/on  $v_{T-}$ Gate-Source threshold voltage  $V_{th}$ YStar Connection **Efficiency**  $\eta$

line frequency in rad/s

## Chapter 1

### Introduction

#### 1.1 Introduction to Power Electronics

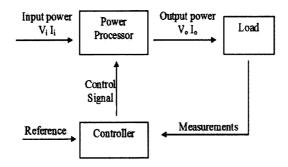

Power electronics is the field of electrical engineering related to the use of semiconductor devices to convert power from the form available from a source to that required by a load. A block diagram of a typical power electronic system is shown in Figure 1.1 ([1]). The power source may be a dc source or a single-phase/three-phase ac source with line frequency of 50 to 60 Hz or 400Hz; it may be an electric battery, a solar panel, an electric generator or a commercial power supply. The source feeds the input of the power converter or processor, which converts the input power to the required form for a load. The load may be dc or ac, single-phase or three-phase, and may or may not need transformer isolation from the power source.

The power converter can be an ac/dc converter, a dc/dc converter, a dc/ac inverter or an ac/ac converter depending on the application. Feedback control is used to ensure that the required output voltage and/or current are provided to the load. This is done by sensing the output voltages and currents and feeding the information into the controller so that the controller can send information to the power processor, which makes the necessary adjustments.

Figure 1.1: Block diagram of a power electronics system.

#### 1.2 Semiconductor Devices

The semiconductor devices that are typically used in a power converter are diodes, MOSFETs and IGBTs. Devices such as thyristors are used in very high power converters and will not be discussed here. Diodes are uncontrolled switches as they are on and conduct current when they are forward-biased and are off when they are reverse-biased. Current cannot be interrupted in a diode and some action external to the diode must be taken to divert current away from it and make it reverse biased.

MOSFETs and IGBTs are controllable switches and can be turned on and off by feeding a control signal to their gate then removing it. The basic characteristics of each device are discussed in further detail below.

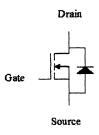

#### 1.2.1 MOSFETs

A MOSFET is a metal oxide semiconductor field effect transistor and is typically depicted as shown in Figure 1.2. It has three terminals - a gate, a drain, and a source. The switch is on when current is fed to the gate and its gate-source capacitance is charged to a threshold voltage  $V_{th}$ , which creates a field that opens the drain-source channel and allows current to flow from drain to source. Current does not have to

be continuously fed to the gate to keep the device on; the device is on as long as the voltage across the gate-source capacitance  $V_{gs}$  is greater than  $V_{th}$  and the field that keeps the channel open exists.

The MOSFET has three main regions of operation: triode, saturated, and cut-off. Since controllable semiconductor devices in almost all power electronics applications function as switches that are either fully on or fully off, a MOSFET in a power converter operates either in the triode region (fully on) or in the cut-off region (fully off). When a MOSFET is on, however, it is not an ideal switch as it has some resistance  $R_{ds,on}$  between its drain and source, which contributes to energy loss when current flows through the device.

Figure 1.2: Power MOSFET symbol.

Since MOSFETs are turned on and off due to the generation and removal of an electric field, they can be turned on and off very quickly and are the fastest semiconductor devices in terms of switching. They are the devices of choice in applications such as low power applications as their fast switching characteristics allows them to be implemented in converters that operate with high switching frequencies (> 100kHz) to reduce the size of their passive elements (inductors, capacitors, transformers). They are not suitable for higher power applications due to their  $R_{ds,on}$  and the conduction losses created by this parameter.

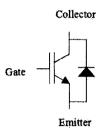

#### 1.2.2 IGBTs

An IGBT is an insulated gate bipolar transistor and gets its name from the fact that it has the characteristics of both BJTs and MOSFETs. It is typically depicted as shown in Figure 1.3. It has three terminals - a gate, a collector and an emitter. The term "gate" comes from the MOSFET part of the device while the terms "collector" and "emitter" comes from the BJT part of the device.

A BJT is a bipolar junction transistor and is a minority-carrier device. This means that unlike a MOSFET, which is turned on by generating an electric field that can be very quickly removed, the BJT is turned on by feeding a continuous current to its base (the "gate" of the device). The advantage that the BJT has over the MOSFET is that is has a fixed voltage drop across its collector-emitter terminals when the device is on, whereas the MOSFET has a variable voltage drop because it depends on the product of the current flowing through the device and its  $R_{ds,on}$ . The BJT is therefore better suited for high power applications than the MOSFET because its lower voltage drop results in lower conduction losses.

The BJT, however, turns on and off very slowly because it is a minority-carrier device that depends on the presence of a continuous base current. It cannot match the switching speed of a MOSFET as it is easier to generate and remove an electric field than it is to inject and remove electrons. In order to improve the switching times of the BJT, its base was made into a MOSFET gate and thus the IGBT with its insulated gate was created. Although the IGBT turns on and off more quickly than a BJT, its switching speed cannot match that of a MOSFET, which can operate with switching speeds in the MHz range. The IGBT, however, still has the voltage drop characteristics of the BJT and is thus preferred over the MOSFET in higher

power applications.

Figure 1.3: IGBT symbol.

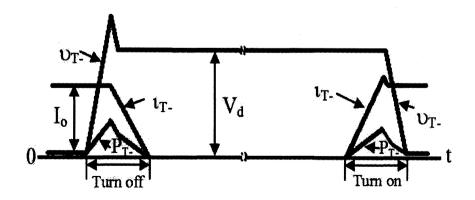

### 1.3 Switching Characteristics

The switching of a MOSFET or an IGBT is not ideal. An ideal switch would turn on and off instantaneously and there would be no overlap between the voltage across a device and the current through it, and, therefore, no power loss as the power lost due to switching is related to product of the two. In reality, however, such overlaps do exist whenever the device is in a switching transition, going from on to off or vice versa. An example of the overlap of voltage and current that can be encountered by a device is shown in Figure 1.4 ([1]).

Figure 1.4: Non-ideal switching characteristics of a semiconductor device.

The switching losses generated by a MOSFET or an IGBT is related to its switching frequency - the faster it is turned on and off, the more switching losses will be generated. Switching losses, however, can be reduced if either the voltage or the current is made to be zero during the time that a switching transition takes place so that there is no voltage and current overlap and thus no power lost. Techniques for ensuring that this occurs can be classified as either zero-voltage switching (ZVS) techniques or zero-current switching (ZCS) techniques; these two types of techniques are generally referred to as soft-switching techniques while hard-switching refers to the case when such techniques are not used. Both ZVS and ZCS are briefly reviewed here.

ZVS techniques are techniques that force the voltage across a switch to be zero just before it is turned on or off and keep this voltage zero while a switching transition occurs. Both MOSFETs and IGBTs have anti-parallel diodes that are built into the "body" of each device that allows current to flow from source to drain in a MOSFET and from emitter to collector in an IGBT. A ZVS turn-on in MOSFETs and IGBTs is therefore done by forcing current through the body-diode of the devices just before they are turned on. This clamps the voltage across the device to a single diode drop (which is a negligible voltage) during a switching transition so that turn-on switching losses are greatly reduced. A ZVS turn-off is achieved by slowing down the rate of voltage rise across a switch when it is turned off by adding some capacitance across the switch; this limits the overlap between voltage and current.

ZCS techniques are techniques that force the current through a switch to be zero just before it is turned on or off and keep this current zero while a switching transition occurs. A ZCS turn-off is achieved by diverting current away from the switch into the rest of the power converter before the switch is turned off. This is typically done by providing a path of negative voltage potential to the switch or by imposing a negative voltage somewhere in the current path. A ZCS turn on can be done by adding an inductor in series with the switch that slows down the rate of current rise when the switch is turned on; this limits the overlap in voltage and current.

Since MOSFETs are used in low current, high switching frequency applications and have a significant drain-source capacitance, they are usually implemented with some ZVS technique. The drain-source capacitance is often sufficient to ensure that the device can be turned-off with ZVS and negative current is used to discharge this capacitance and flow into the body-diode so that the device can turn on with ZVS. Since IGBTs are used in high current applications and have a slower turn-off due to their being minority-carrier devices, they are usually implemented with ZCS. They have smaller collector-emitter capacitances than MOSFETs and it is the turn-off losses that must be dealt with.

## 1.4 Two-Stage Ac-Dc Power Conversion

The main type of power electronics converters that will be the focus of this thesis are power converters that convert a three-phase ac input voltage into a stepped down and transformer isolated dc output voltage. This is typically done using two switch-mode converters (as opposed to completely passive converters made up of diodes and no active switches). As shown in the block diagram in Figure 1.5, an ac-dc converter or rectifier is used to convert the ac input voltage into an intermediate dc bus voltage and is then fed to a second converter that converts it into the desired, isolated, dc

voltage.

Figure 1.5: Block diagram of Two-Stage ac-dc converters.

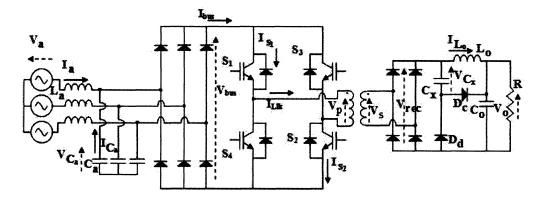

An example of a two-stage ac-dc converter is shown in Figure 1.6. The ac-dc converter is typically a six-switch converter that performs input power factor correction (PFC) while it is performing ac-dc power conversion. Input PFC shapes the input line currents so that they are sinusoidal and in phase with the line voltages to maximize the use of available power from the source. Input PFC is now a standard feature in ac-dc converters as consumer demands and the resulting proliferation of electric equipment has resulted in the need to satisfy stringent regulatory limits on the harmonics that can be injected into the ac mains. The dc-dc converter is typically a four-switch full-bridge converter for higher power applications where a three-phase source instead of a single-phase source is used.

In this section of the thesis, the operation of the full-bridge and alternatives to the six-switch converter are reviewed.

#### 1.4.1 Full-Bridge Converter Operation

A dc-dc full-bridge converter is shown in Figure 1.7. It can be seen that the converter consists of four switches, a transformer, two output diodes, an inductor and a capacitor; the load is represented as a resistor. The converter works as follows:

Figure 1.6: Three-phase ac-dc six switch two-stage full-bridge converter.

Voltage is impressed across the primary of the transformer winding whenever a diagonally opposite pair of switches are on  $(S_1 \text{ and } S_2 \text{ or } S_3 \text{ and } S_4)$ ; the polarity of the voltage depends on the pair of switches that is on. No voltage is impressed across the transformer primary whenever current flows through two top switches (or their body-diodes) or two bottom switches (or their body diodes).

Figure 1.7: Dc-dc full-bridge converter.

The converter can be said to be in an energy-transfer mode whenever a voltage is impressed across the transformer primary and appears at the secondary, and to be in a freewheeling mode when there is no voltage across either transformer winding and current just flows ("freewheels") throughout the converter. Since the voltage across

the transformer is a symmetrical ac square voltage with zero voltage sections, two diodes are needed at the secondary to rectify this voltage and a low-pass inductor-capacitor (L-C) filter is needed to smooth out the voltage and make it almost purely dc.

Starting from a state when  $S_1$  and  $S_2$  are on, the typical sequence of operation during a half switching cycle is as follows:

- $S_1$  and  $S_2$  are on and conduct current;

- $S_2$  is turned off and the current in the transformer primary flows through the anti-parallel body-diode of  $S_3$  (which allows  $S_3$  to turn on with ZVS);

- $S_1$  is turned off and current in the transformer primary flows through the body-diode of  $S_3$  and  $S_4$  (which allows  $S_4$  to turn on with ZVS):

- Current in  $S_3$  and  $S_4$  eventually reverses direction so that it flows through the switches instead of the body-diodes

The next half switching cycle begins when  $S_3$  is turned off and current starts flowing in the body diode of  $S_2$ . If a switch is considered to be on regardless of current flowing through the switch itself or through its body-diode, then the switching sequence over a full switching cycle is as follows:

- $\bullet$   $S_1$ - $S_2$  on (energy-transfer mode/transformer voltage +ve polarity)

- $\bullet$   $S_1\text{-}S_3$  on (free wheeling mode/transformer voltage zero)

- $S_3$ - $S_4$  on (energy-transfer mode/transformer voltage -ve polarity)

- $\bullet$   $S_2\text{-}S_4$  on (free wheeling mode/transformer voltage zero)

The signal voltage pulses that are fed to the gates of each switch (gating signals) are high for 50% of the switching cycle (switch on) and low during the rest of the cycle (switch off). The gating signal of any switch is complementary to that of the switch in the same leg so that two switches in the same leg (i.e.  $S_1$  and  $S_4$  or  $S_3$  and  $S_2$ ) are never on simultaneously, which would result in a short circuit. Typical dc-dc full-bridge waveforms are demonstrated in Figure 1.8.

The output dc voltage level can be controlled by controlling the width of the positive and negative voltage pulses relative to the zero voltage portions of the transformer. This can be done by shifting the gating signal pulses of the switches in one leg, relative to those of the switches in the other leg. If  $S_1$  and  $S_2$  are always on simultaneously and  $S_3$  and  $S_4$  are always on simultaneously, then the converter will always be in an energy-transfer mode and the output voltage will be at its maximum possible value. If  $S_1$  and  $S_2$  are never on simultaneously and  $S_3$  and  $S_4$  are never on simultaneously, then the converter will never be in an energy-transfer mode and the output voltage will be zero. This method of controlling the output dc voltage is called phase shift pulse width modulation (phase shift PWM) and is considered to be the standard method of controlling a dc-dc full-bridge converter.

#### 1.4.2 Ac-Dc Front-End Converters

The three-phase six-switch ac-dc rectifier converter that is the front-end converter of the two-stage converter shown in Figure 1.6 is considered to be the standard converter in this setting (either with low pass L-C filter, as shown in Figure 1.6 or with just a C filter). This converter, however, is expensive as it requires six active switches along with associated gate drive and control circuitry and requires sophisticated con-

Figure 1.8: Typical dc-dc full-bridge waveforms.

trol methods to perform input PFC. Power electronics researchers, therefore, have been motivated to find simpler and cheaper alternatives to the standard six-switch converter.

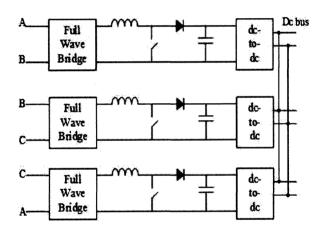

One approach to three-phase ac-dc conversion is to use three separate single-

phase boost PFC converter modules as shown in Figure 1.9 [2]. Each module in Figure 1.9 is a two-stage converter consisting of PFC boost converter followed by a dc-dc converter to get the desired bus voltage. The main advantage is that existing single-phase modules can be used, which are popular and widely available and do not require knowledge of sophisticated three-phase control. The main disadvantages are the need to synchronize the operation of each individual module to the others and the presence of triplen harmonics (these are odd multiples of the 3rd harmonic, 3rd, 9th, 15th etc.) due to parametric variations in the modules.

Figure 1.9: Three-phase ac-dc converter using three single-phase modules.

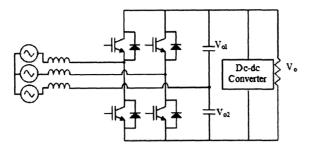

Another approach is to use reduced switch rectifiers that contain only three or four switches [2] instead of six as the front-end ac-dc converter. An example of such a rectifier is shown in Figure 1.10. Although the number of switches has been reduced, the overall two-stage converter still requires seven or eight switches and the control methods needed to perform PFC and ac-dc conversion remain very sophisticated.

A third approach is to use a three-phase single-switch ac-dc rectifier as the

Figure 1.10: Three-phase ac-dc converter with four switches.

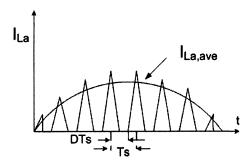

front-end converter [3]-[4]. This approach is most suitable for applications of about 2kW - 6kW power, which is just above the range where single-phase converters are more attractive than three-phase converters. There are two types of three-phase single switch rectifiers: the boost (step-up) converter [4] and the buck (step-down) converter [3]-[4]; the boost converter is shown in Figure 1.11. Its operation is as follows: When the boost converter switch is turned on, current in each line inductor rises to a peak value proportional to the voltage applied in that switch cycle. When the switch is off, currents in those inductors fall to zero as energy is transferred to the output capacitor. As a result, each input line current is discontinuous and is bounded by a sinusoidal envelope so that it is essentially a sinusoid with high frequency components that can be filtered out with some additional filtering. A typical line current waveform for a half line cycle is shown in Figure 1.12.

Figure 1.13 shows the three-phase single-switch buck converter. It operates in similar manner to boost converter, but, in this case, it is the voltages across input capacitors  $(C_a, C_b \text{ and } C_c)$  that must be discontinuous so that they are essentially sinusoidal in nature. Since these voltages are sinusoidal and the input voltages are sinusoidal, the input inductor currents will also be sinusoidal, but unlike those of the boost converter, they will be continuous.

Figure 1.11: Three-phase ac-dc single-switch PFC front-end boost converter.

Figure 1.12: Input line current waveform of a three-phase ac-dc single-switch boost converter (half-line cycle).

Both types of single switch, three-phase converters are very attractive because they are simple. They are, however, limited in power because all the power being converted must be processed by a single active switch.

#### 1.5 Three-Phase Single-Stage Ac-Dc Converters

Regardless of whichever of the above-mentioned ac-dc rectifier converters is used as the front-end converter of a two-stage ac-dc converter with ac-dc front-end and dc-dc full-bridge stages, two separate switch-mode converters need to be implemented. In

Figure 1.13: Three-phase ac-dc single-switch PFC front-end buck converter.

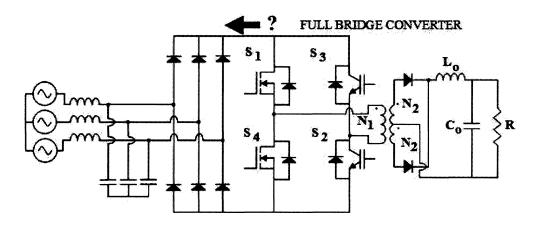

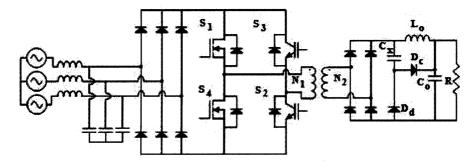

order to reduce the cost and complexity associated with implementing two switch-mode converters, power electronics researchers have tried to combine the PFC function of the ac-dc front-end converter with the dc-dc conversion function of the full-bridge converter in a single converter [5]-[13]. Power converters of this type are referred to as single-stage converters in the power electronics literature. Several examples of three-phase, single-stage converters are shown in Figure 1.14.

There has been considerable research on low power, single-phase, single-stage ac converters, but there has been relatively little research on three-phase, single-stage converters. This is because of the challenges involved in simultaneously performing both PFC and dc-dc conversion over a much wider load range than what the low power single-stage converters encounter. The few three-phase single-stage converters that have been proposed have at least one of the following drawbacks:

- The converter uses a three single-phase full-bridge modular approach [13] (i.e. Figure 1.14(a)). This is expensive and it is not easy to synchronize the operation of all three converters to produce sinusoidal input currents.

- The input currents are distorted and contain a significant amount of low fre-

quency harmonics [6] (i.e. Figure 1.14(b)) as the converter has difficulty performing PFC and dc-dc conversion simultaneously; thus compromising the quality of the input waveforms and power factor.

- The input currents must become zero during each switching cycle (discontinuous input currents) in order for input PFC to be achieved. Converters shown in Figures 1.14(a) 1.14(d) ([6], [14]) incorporate the principles of the three-phase single-switch boost converter (which was originally proposed in [5]) into their topologies. Although an excellent input power factor may be achieved, the peak current stress of the semiconductor devices is very high. Moreover, additional and significant filtering is required to attenuate the large amount of high frequency noise fed back to the line.

- The converter must be controlled using very sophisticated techniques. This is especially true of multilevel converters shown in Figure 1.14(c) ([8], [10]) where the need to balance the voltages on the split capacitors at the dc bus is critical.

#### 1.6 Thesis Objectives

The main objectives of this thesis are as follows:

1. To propose a new three-phase, ac-dc, single-stage, PWM converter that can operate with an excellent input power factor i.e., the the line current harmonics are well below the standard specification and that does not have the disadvantages of the above-mentioned three-phase single-stage converters.

- 2. To analyze its steady-state operation and to determine its steady-state characteristics.

- 3. To develop guidelines and a procedure for designing the proposed converter so that it can operate properly.

- 4. To confirm its feasibility with results obtained from a working, experimental prototype.

The above objectives were achieved and will be elaborated in the chapters to come.

#### 1.7 Thesis Outline

The thesis is comprised of the following six chapters. Following is a briefing of each chapter following;

- Chapter 2: The derivation of the proposed three-phase, single-stage, ac-dc converter is discussed in detail in this chapter. Since the proposed single-stage converter is based on the combination of a single-switch three-phase buck converter with a dc-dc zero-voltage-zero-current switched (ZVZCS) full-bridge converter, the basic operation of both these converters and their modes of operation are explained. It is then shown how these two converters can be combined to form the proposed three-phase single-stage converter.

- Chapter 3: The proposed three-phase single-stage ac-dc converter is introduced in this chapter and its operation is discussed. The modes of operation that the converter goes through are explained in detail, the key equations that define its

operation during these modes are derived and the attractive features of the new converter are stated.

- Chapter 4: A steady-state analysis of the proposed converter is performed in this chapter. The purpose of the analysis is to derive expressions and determine relations of key converter parameters to understand the steady-state characteristics of the converter and to help establish a procedure for its design, which will be done in Chapter 5.

- Chapter 5: The design of the converter is discussed in this chapter. An example is given to demonstrate how the most important converter parameters can be selected using the results of the analysis performed in Chapters 3 and 4. The results of the design process will be used in the implementation of an experimental prototype converter that will confirm the feasibility of the converter.

- Chapter 6: In this chapter, the contents of the thesis are summarized, the conclusions that have been reached as a result of the work performed in thesis are presented, and the main contributions of the thesis are stated. The chapter concludes by suggesting potential future research that can be done based on the thesis work.

(a) Converter with three single-phase modules ([13])

(b) Compromising between voltage regulation and PFC ([6])

(c) A multi-level converter ([10])

(d) A front-end boost converter technique is used for PFC ([14])

Figure 1.14: Examples of three-phase, single-stage converters.

### Chapter 2

# **Fundamental Principles**

#### 2.1 Introduction

The derivation of the proposed three-phase, single-stage, ac-dc converter is discussed in detail in this chapter. Since the proposed single-stage converter is based on the combination of a single-switch three-phase buck converter with a dc-dc zero-voltage-zero-current switched (ZVZCS) full-bridge converter, the basic operation of both these converters and their modes of operation are explained in this chapter. It is then showed how these two converters can be combined to form the proposed three-phase single-stage converter.

# 2.2 Fundamental Principles - Ac-Dc Three-Phase Single-Switch Buck Converter

Before presenting and discussing the proposed three-phase, single-stage converter, the general fundamental principles behind its derivation and operation will be discussed first in this chapter. Consider the two-stage, three-phase ac-dc converter shown in

Figure 2.1. This converter has a single-switch buck (step down) ac-dc front-end rectifier as the front-end, followed by a dc-dc full-bridge converter. The objective in deriving a new three-phase, ac-dc single-stage converter is to combine these two converters into one to form the proposed single-stage converter. In order to understand how this can be done, the operation of the ac-dc single switch front-end converter is reviewed first in detail in this section. The converter is shown with a resistive load in Figure 2.2.

Figure 2.1: Ac-dc converter with single-switch buck rectifier and dc-dc full-bridge converter.

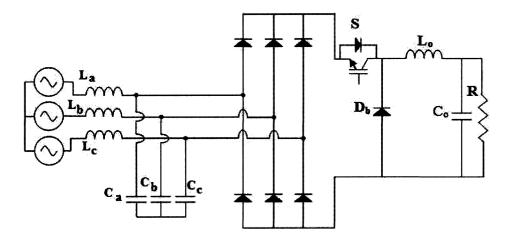

Figure 2.2: Three-phase ac-dc single-switch PFC buck converter.

The converter consists of three input inductors, three input capacitors, a three-phase diode rectifier and a standard buck converter section comprised of a switch, a diode, and a low pass L-C filter. During a typical switching cycle (which is a small fraction of the input ac line cycle), the converter goes through the following modes of operation, as shown in Figure 2.3:

Mode 1

$$(t_0 < t < t_1)$$

Figure 2.3(a)

At  $t = t_0$ , the switch, S, is turned on. The input capacitors  $C_a$ ,  $C_b$ , and  $C_c$  begin to discharge as current flows through the diode rectifier bridge to the output converter section. The diode,  $D_b$ , is reverse biased during this mode as the rectifier output voltage (which is the rectification of the input capacitor voltage) is placed across it. By the end of this mode, the input capacitors are fully discharged.

Mode 2

$$(t_1 < t < t_2)$$

Figure 2.3(b)

The input capacitors remain discharged during this mode and only the line currents flow through the diode bridge rectifier to the output section. Since the input capacitors have no voltage across them, the voltage across the diode bridge rectifier output is zero, which makes  $D_b$  forward biased. The current that  $D_b$  conducts is the difference between the current flowing from the input section of the converter and the current flowing through output inductor  $L_o$ . The mode ends at  $t = t_2$  when S is turned off.

Mode 3

$$(t_2 < t < t_3)$$

Figure 2.3(c)

After S is turned off, the path of current flow from the input section to the output section of the converter is broken; therefore the line currents begin to

charge the input capacitors. All the current in  $L_o$  flows through  $D_b$  and the converter is in a freewheeling mode of operation, much like that found in a standard dc-dc buck converter. At  $t=t_3$ , S is turned on again to start the next switching cycle.

Figure 2.3: Steady state modes of the three-phase single-switch buck converter.

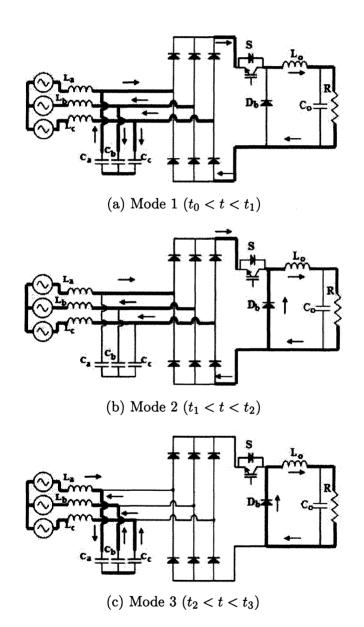

The input inductor currents can be sinusoidal and in phase with the input line

voltages as long as the input capacitors voltages can be fully discharged after Mode 1 for all switching cycles throughout the line cycle. If there is a significant number of switching cycles during which the input capacitors cannot be fully discharged, then the input capacitor voltages will not look like the voltage waveform shown in Figure 2.4, which is essentially sinusoidal, but will contain low frequency harmonic components. These components will cause the input inductor currents to become distorted, which will lead to a reduction in input power factor.

# 2.3 Fundamental Principles - Dc-Dc Zero-Voltage-Zero-Current Switching (ZVZCS) Full-Bridge Converter

A conventional dc-dc full-bridge converter, like the one shown as the second converter stage of the two-stage ac-dc converter in Figure 2.1, is considered to be a buck converter, but with transformer isolation. It would be, therefore, possible to replace the switch of the front-end ac-dc rectifier in Figure 2.2 with a full-bridge converter so that the two converters stages can be made into one, as shown in Figure 2.5. There is however, a catch. A path for the transformer primary-side current must be provided when the converter exits a freewheeling mode of operation.

It should be noted that the switches in one leg of the full-bridge converter are MOSFETs and the switches in the other leg are IGBTs. This is because the switches in one leg operate with ZVS and those of the other leg operate with ZCS. MOSFETs are preferred devices for ZVS operation and IGBTs are the favorable devices for ZCS functioning.

Figure 2.4: Input capacitor voltage of a three-phase, single-switch, ac-dc buck converter (half-line cycle).

Figure 2.5: Three-phase single-stage ac-dc converter with conventional full-bridge.

Consider the operation of a dc-dc full-bridge converter, assuming that switches  $S_1$  and  $S_2$  are on (section 1.4.1). There is voltage from the dc bus capacitor that is impressed across the transformer primary and energy is being transferred from the primary to the secondary and the output. When switch  $S_1$  is turned off, the current that was flowing in this switch is transferred to the anti-parallel diode of  $S_4$  and this switch can be turned on with zero-voltage switching. The converter operates in a freewheeling mode with current circulating through  $S_2$  and  $S_4$  in the primary-side of the converter. When  $S_2$  is turned off, current flows through the anti-parallel diodes of  $S_3$  and  $S_4$  and through the dc bus capacitor that is connected across the full-

bridge input. It is important to note that a typical full-bridge converter has modes of operation where primary current flows in the reverse direction out of the converter and back into the source.

If a full-bridge converter is to replace the switch in the buck front-end rectifier, then there must be little if any of this reverse current. This can be done if the full-bridge converter is a zero-voltage-zero-current switching (ZVZCS) converter ( as the ones proposed in [15] - [18]). A ZVZCS converter has the property that most of the transformer primary current that circulates in the converter when it is in a freewheeling mode can be extinguished so that there is little "backwards" current that flows through the anti-parallel diodes of the switches when the converter exits a freewheeling mode of operation. The elimination of the reverse current means that the dc bus capacitor can be removed so that the converter shown in Figure 2.5 can become reality. Another option is to keep the reverse current and use it to feed an auxiliary power supply, as has been suggested for the two-switch forward converter in [12], but this is cumbersome and impractical for many applications.

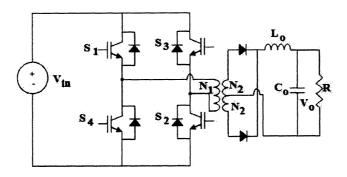

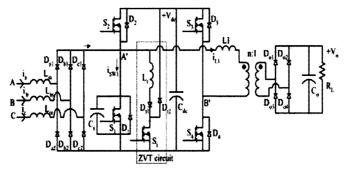

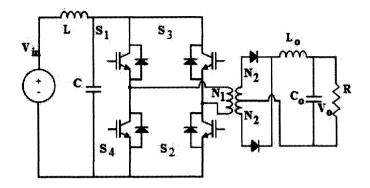

An example of a ZVZCS dc-dc full-bridge converter is shown in Figure 2.6. The converter is almost the same as a conventional dc-dc full-bridge converter except that a small passive auxiliary circuit consisting of capacitor  $C_x$ , and diodes  $D_c$  and  $D_d$  has been added. The purpose of this circuit is to impress a counter voltage across the transformer primary whenever the converter is in a freewheeling mode to extinguish the circulating current that flows in the converter during that time.

Equivalent circuit diagrams showing the flow of current in the converter during a half switching cycle are shown in Figure 2.7 and typical converter waveforms are

Figure 2.6: Dc-dc PWM ZVZCS full-bridge converter.

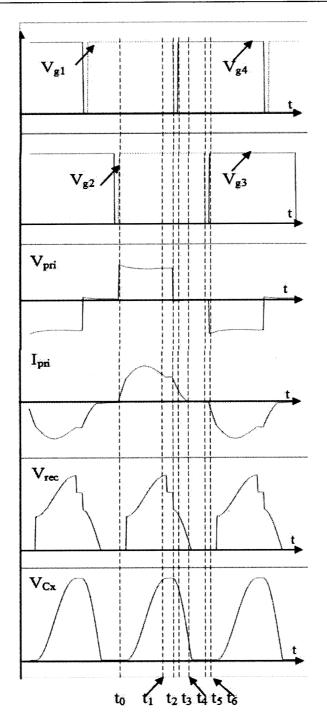

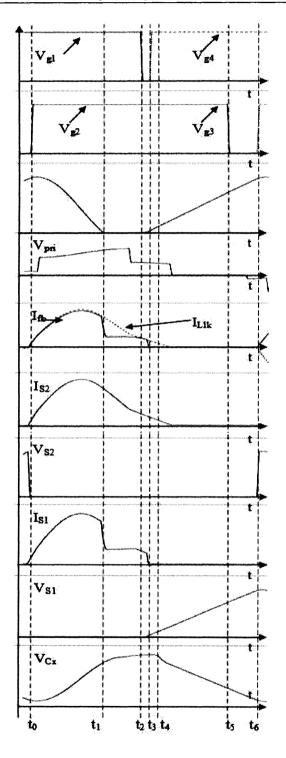

shown in Figure 2.8. Prior to  $t = t_0$ , switch  $S_1$  of the full-bridge is on, switches  $S_2$ ,  $S_3$  and  $S_4$  are off, and there is no current in the primary side of the full-bridge transformer. On the secondary side, the auxiliary circuit  $(C_x, D_d, \text{ and } D_c)$  does not conduct current and current from the output inductor  $L_o$  is freewheeling though the two diodes  $D_1$  and  $D_2$ , connected to the secondary winding of the transformer. The converter's modes of operation are as follows:

#### Mode 1 $(t_0 < t < t_1)$ Figure 2.7(a)

Mode 1 starts at  $t = t_0$  when  $S_2$  is turned on. Current from the dc source flows through switches  $S_1$ ,  $S_2$  and voltage is impressed across the primary winding of the transformer. Voltage appears across the secondary winding and  $C_x$  begins to be charged through diode  $D_c$ ; there is an interaction between  $C_x$  and the transformer's leakage inductance that limits the current charging this capacitor. Current from the output inductor  $L_o$  also flows through the load; and the primary current is the sum of the reflected currents through  $L_o$  and  $C_x$ . Mode 1 ends when  $D_c$  stops conducting and  $V_{C_x}$  is at its peak. The converter is in an energy transfer mode during Mode 1.

Mode 2  $(t_1 < t < t_2)$  Figure 2.7(b)

Mode 2 is identical to Mode 1 except that no current flows through  $C_x$ . The transformer primary current is equal to the reflected current flowing through  $L_o$  during this mode.

Mode 3

$$(t_2 < t < t_3)$$

Figure 2.7(c)

Switch  $S_1$  is turned off at  $t=t_2$ . The current that was flowing through  $S_1$  charges and discharges the capacitances across  $S_1$  and  $S_4$  respectively. These capacitances (shown only in the Figure 2.7(c) diagram for emphasis) are placed across these switches to limit the rise in voltage across them when they are turned off, as they carry the full transformer primary current during this switching transition. As the voltage across the transformer primary decreases from  $V_{in}$  to zero, the voltage at the secondary also decreases and settles at  $V_{C_x}$ , which is constant during this mode. The mode ends when the capacitances across  $S_1$  and  $S_4$  have been fully charged and discharged respectively.

Mode 4

$$(t_3 < t < t_4)$$

Figure 2.7(d)

At  $t = t_3$ , current starts flowing in the anti-parallel body diode of  $S_4$ . Once this happens,  $S_4$  can be turned on with ZVS at any time during this mode because the voltage across this switch is clamped to almost zero. Current circulates through  $S_2$  and  $S_4$  and the voltage impressed across the transformer primary is zero; the converter is in a freewheeling mode with no power being transferred from the dc source to the load. On the secondary side of the transformer,  $C_x$  starts to discharge through  $D_d$  at  $t = t_3$ , and  $V_{C_x}$  begins to decrease. Although the primary voltage of the transformer is zero, the voltage on the secondary

side is due to  $C_x$ . This creates a difference between the voltages of the two windings of the transformer that appears across the primary leakage inductance as a counter voltage. In essence, this counter voltage is like a dc source that appears in the path of the primary current that causes the primary current to decrease. This is the mechanism by which the transformer primary current can be extinguished.

Mode 5  $(t_4 < t < t_5)$  Figure 2.7(e)

At  $t = t_4$ , there is no current flowing in the primary side of the transformer as it has been completely extinguished. On the secondary side,  $C_x$  continues to discharge via  $D_d$  until  $V_{C_x}$  becomes zero. Load current will now start to freewheel through the rectifier diodes  $D_1$  and  $D_2$  on the secondary side.

Mode 6  $(t_5 < t < t_6)$  Figure 2.7(f)

At  $t=t_5$ ,  $S_2$  is turned off with ZCS as there is no current flowing in the transformer primary. After  $S_2$  is completely off,  $S_3$  is turned on with ZCS as well, since the leakage inductance of the transformer limits the rise of current in the switch. Current flows through  $S_3$  and  $S_4$  during this mode and the converter is in an energy transfer mode as another half-cycle begins.

The ZVZCS dc-dc full-bridge converter has the following characteristics, which should be noted:

• The converter can operate with the same phase shift PWM control method as the standard dc-dc PWM full-bridge converter. The output voltage is controlled

Figure 2.7: Modes of operation of dc-dc ZVZCS full bridge PWM converter.

by phase-shifting the gating signals of the switches in one leg relative to those of the switches in the other.

- The switches in the leading converter leg operate with ZVS and those in lagging leg operate with ZCS. The leading leg is the leg whose switches turn on first during a half switching cycle and the lagging leg is the leg whose switches turn on second. In the modal sequence explained above, the leg with  $S_1$  and  $S_4$  is the leading leg and the leg with  $S_2$  and  $S_3$  is the lagging leg.

- Since the transformer primary current is extinguished when the converter is in a freewheeling mode, when there is no energy transfer taking place, energy losses caused by the current circulating in the primary during this time are eliminated.

Figure 2.8: Steady state waveforms of dc-dc ZVZCS full bridge PWM converter.

#### 2.4 Conclusion

In order to derive a three-phase single-stage ac-dc converter, the ac-dc front-end and the dc-dc full-bridge converters of a two-stage ac-dc converter must be combined. It was proposed that this be done by combining a three-phase, single switch, ac-dc buck converter with a dc-dc full-bridge converter and have the full-bridge converter act like the buck switch.

The conventional dc-dc full-bridge converter, however, is not suitable for this purpose because it has reverse current flowing through the anti-parallel diodes of its switches to the dc source whenever it exits a freewheeling mode of operation. Such a path cannot exist in a single-stage converter because there is no dc source across the input of the full-bridge section. A converter that does not have this issue is the zero-voltage-zero-current switching (ZVZCS) and it is this converter that will be combined with the ac-dc single switch buck converter to form the new three-phase, single-switch converter.

In this chapter, the operation of both the three-phase, single switch, ac-dc buck converter and that of a dc-dc zero-voltage-zero-current switched (ZVZCS) full-bridge converter were explained. This was done in preparation of the proposed three-phase single-stage converter, which will be presented in the next chapter of this thesis.

## Chapter 3

# A New Three-Phase Single-Stage Ac-Dc Converter

#### 3.1 Introduction

In this chapter, the proposed three-phase single-stage ac-dc converter is introduced and its operation is discussed. The modes of operation that the converter goes through are explained in detail, the key equations that define its operation during these modes are derived, and the attractive features of the new converter are stated.

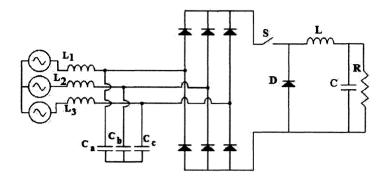

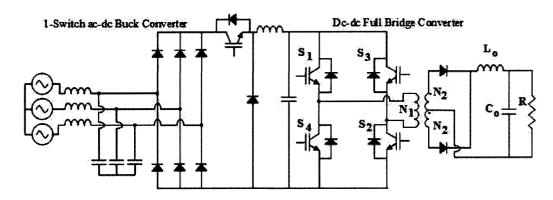

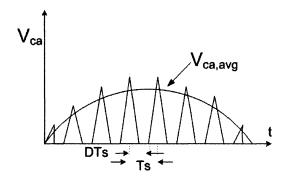

#### 3.2 General Operating Principles

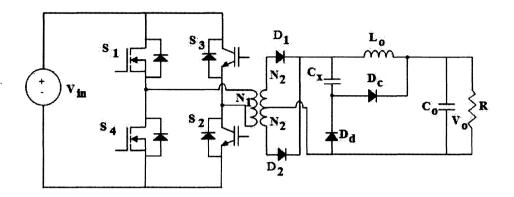

The converter shown in Figure 3.1 is the proposed single-stage ac-dc converter. It is basically a three-phase diode bridge rectifier with a three-phase L-C filter attached to a ZVZCS full-bridge converter with the full-bridge converter acting as the buck switch in a three-phase, single-switch buck rectifier. The ZVZCS full-bridge is almost the same as the conventional full-bridge converter except that it also has a passive circuit

that consists of a capacitor and two diodes that helps extinguish the transformer primary current.

Figure 3.1: Proposed three-phase single-stage ac-dc converter with ZVZCS full-bridge.

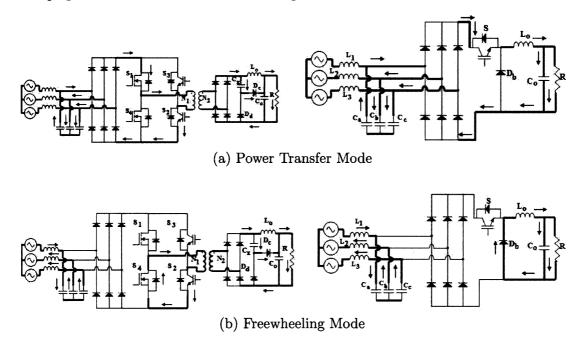

The most important thing to note is that the full-bridge acts like the switch in the three-phase, single switch, ac-dc buck converter discussed in chapter 2. It can be seen in Figure 3.2 how the functioning of the full-bridge is analogous with the buck converter. When a diagonal pair of switches in the full-bridge is on it is considered as a power transfer mode and this is equivalent to the switch being on in the buck converter. This can be explained by the flow of currents of the converters as depicted in Figure 3.2(a).

A mode of operation when no energy is transfer from input to output in the full-bridge can be considered a freewheeling mode and it's analogous to the switch in a buck converter being off. Input capacitors are charging with line currents and the freewheeling of the dc current is observable in both converters. Therefore the full-bridge section of the proposed converter can act as a buck switch because it is a ZVZCS converter that does not send reverse current back to the dc bus.

It should be noted that switches  $S_1$  and  $S_4$  are as being implemented with

MOSFETs in Figure 3.1 and switches  $S_2$  and  $S_3$  are shown as being implemented with IGBTs. This is because switches  $S_1$  and  $S_4$  operate with ZVS and switches  $S_2$  and  $S_3$  operate with ZCS. This will be explained in more detail in this thesis.

Figure 3.2: Comparison of the proposed converter to a three-phase single switch buck converter.

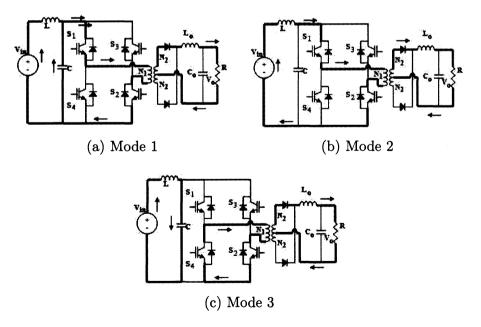

#### 3.3 Modes of Operation

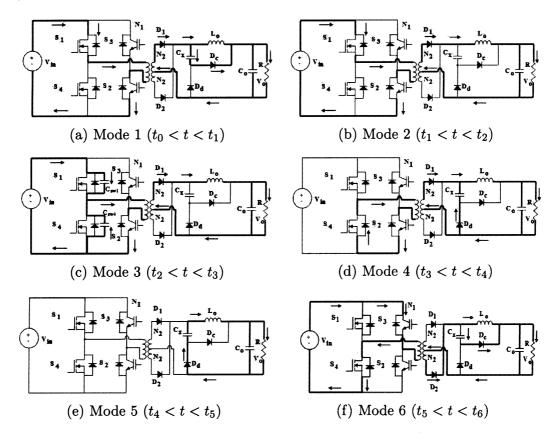

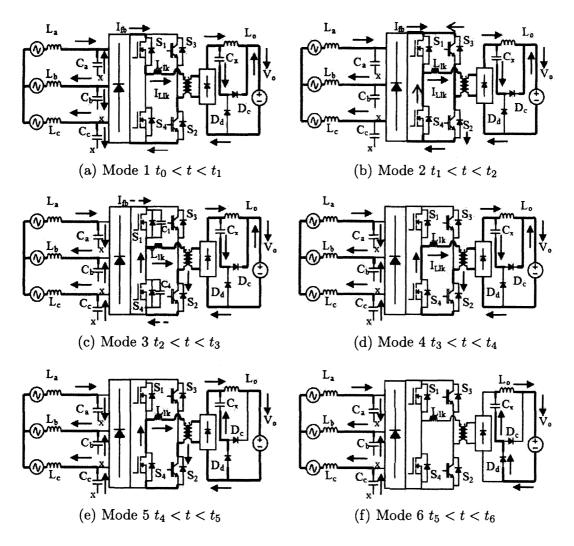

The proposed converter goes through six significant modes of operation at steady state during a half switching cycle. The modes are explained with the circuit diagrams shown in Figure 3.3 and the waveforms shown in Figure 3.4. The following assumptions are made for simplicity.

• The switching cycle where  $V_a = V_{ph,pk}$  (peak phase voltage),  $V_b = V_c = -V_{ph,pk}/2$  is considered.

- When equations are stated for input side, only phase-a is considered from which phases b and c relationships can be derived easily.

- The line frequency is lower with respect to the switching frequency; therefore, line currents and voltages are constants during the switching cycle.

- The magnetizing current in the transformer is negligible.

- The output capacitor and resistive load are combined, and it is shown as a voltage source.

- The current in the output filter  $L_o$  is ripple free.

$Mode1(t_0 < t < t_1)$  Figure: 3.3(a)

Before  $t=t_0$ ,  $S_1$  is on and all other switches are off, the input capacitors are being charged, the auxiliary circuit capacitor  $C_x$  is at its minimum voltage  $V_{C_x,min}$  and there is no current flowing in the full-bridge. At  $t=t_o$ ,  $S_2$  is turned on with ZCS and current  $I_{fb}$ , starts flowing into the full-bridge. This current is the result of the discharging of the input capacitors through the switches and the transformer primary  $I_{L_{lk}}$ . The transformer secondary current also charges the auxiliary circuit capacitor,  $C_x$  through diode  $D_c$  during this mode.

The input capacitors discharge during Mode 1 from its initial value  $V_{C_{a0}}$  until  $V_{C_a}$  reaches zero at  $t=t_1$ . The difference between the current in the leakage inductor  $L_{lk}$  and line current gives the time varying current injected by input capacitor  $C_a$ . The discharging of input capacitor  $C_a$  can be expressed as

$$I_{L_{lk}} - I_a = C_a \frac{dV_{C_a}}{dt} \tag{3.1}$$

Figure 3.3: Modes of converter operation.

$V_{Ca}$  is zero by the end of this mode.  $L_{lk}$  interacts with the input capacitors, and if the voltage across it is  $V_{L_{lk}}$  then the voltage-current relationship of  $L_{lk}$  is given by

$$V_{L_{lk}} = L_{lk} \frac{dI_{L_{lk}}}{dt} \tag{3.2}$$

The voltages that are impressed across the dc bus of the full bridge and across

Figure 3.4: Proposed converter typical waveforms.

the primary winding are  $V_{fb}$  and  $V_p$  respectively where  $V_{fb}$  is the triangular dc input voltage to the full-bridge. The difference between  $V_{fb}$  and  $V_p$  is  $V_{L_{lk}}$  according to Kirchoff's law and given in equation (3.3).

$$V_{fb} - V_p = L_{lk} \frac{dI_{L_{lk}}}{dt} \tag{3.3}$$