#### NATIONAL AND KAPODISTRIAN UNIVERSITY OF ATHENS

# SCHOOL OF SCIENCES DEPARTMENT OF INFORMATICS AND TELECOMMUNICATIONS

#### **PROGRAM OF POSTGRADUATE STUDIES**

#### PhD THESIS

# A GPU performance estimation model based on micro-benchmarks and black-box kernel profiling

Elias N. Konstantinidis

**ATHENS**

**JULY 2017**

#### ΕΘΝΙΚΟ ΚΑΙ ΚΑΠΟΔΙΣΤΡΙΑΚΟ ΠΑΝΕΠΙΣΤΗΜΙΟ ΑΘΗΝΩΝ

#### ΣΧΟΛΗ ΘΕΤΙΚΩΝ ΕΠΙΣΤΗΜΩΝ ΤΜΗΜΑ ΠΛΗΡΟΦΟΡΙΚΗΣ ΚΑΙ ΤΗΛΕΠΙΚΟΙΝΩΝΙΩΝ

#### ΠΡΟΓΡΑΜΜΑ ΜΕΤΑΠΤΥΧΙΑΚΩΝ ΣΠΟΥΔΩΝ

#### ΔΙΔΑΚΤΟΡΙΚΗ ΔΙΑΤΡΙΒΗ

Ένα μοντέλο εκτίμησης απόδοσης επεξεργαστή γραφικών (GPU) βασισμένο σε μετροπρογράμματα και καταγραφή μετρικών με προσέγγιση «μαύρο-κουτί»

Ηλίας Ν. Κωνσταντινίδης

AOHNA

ΙΟΥΛΙΟΣ 2017

#### PhD THESIS

A GPU performance estimation model based on micro-benchmarks and black-box kernel profiling

#### Elias N. Konstantinidis

SUPERVISOR: Yiannis Cotronis, Associate Professor NKUA

#### THREE-MEMBER ADVISORY COMMITTEE:

Yiannis Cotronis, Associate Professor NKUA Elias Manolakos, Professor NKUA Nectarios Koziris, Professor NTUA

#### **SEVEN-MEMBER EXAMINATION COMMITTEE**

Yiannis Cotronis, Elias Manolakos, Associate Professor NKUA Professor NKUA

Nectarios Koziris, Nikolaos Missirlis, Professor NTUA Professor NKUA

Dimitris Gizopoulos, Dimitrios Soudris,

Professor NKUA Associate Professor NTUA

Filippos Tzaferis, Assistant Professor NKUA

**Examination Date: July 3, 2017**

#### ΔΙΔΑΚΤΟΡΙΚΗ ΔΙΑΤΡΙΒΗ

Ένα μοντέλο εκτίμησης απόδοσης επεξεργαστή γραφικών (GPU) βασισμένο σε μετροπρογράμματα και καταγραφή μετρικών με προσέγγιση «μαύρο-κουτί»

#### Ηλίας Ν. Κωνσταντινίδης

ΕΠΙΒΛΕΠΩΝ ΚΑΘΗΓΗΤΗΣ: Ιωάννης Κοτρώνης, Αναπληρωτής Καθηγητής ΕΚΠΑ

#### ΤΡΙΜΕΛΗΣ ΕΠΙΤΡΟΠΗ ΠΑΡΑΚΟΛΟΥΘΗΣΗΣ:

**Ιωάννης Κοτρώνης**, Αναπληρωτής Καθηγητής ΕΚΠΑ **Ηλίας Μανωλάκος**, Καθηγητής ΕΚΠΑ **Νεκτάριος Κοζύρης**, Καθηγητής ΕΜΠ

#### ΕΠΤΑΜΕΛΗΣ ΕΞΕΤΑΣΤΙΚΗ ΕΠΙΤΡΟΠΗ

Ιωάννης Κοτρώνης, Αναπληρωτής Καθηγητής ΕΚΠΑ

Ηλίας Μανωλάκος, Καθηγητής ΕΚΠΑ

Νεκτάριος Κοζύρης, Καθηγητής ΕΜΠ Νικόλαος Μισυρλής, Καθηγητής ΕΚΠΑ

Δημήτρης Γκιζόπουλος, Καθηγητής ΕΚΠΑ

Δημήτριος Σούντρης, Αναπληρωτής Καθηγητής ΕΜΠ

Φίλιππος Τζαφέρης, Επίκουρος Καθηγητής ΕΚΠΑ

Ημερομηνία Εξέτασης: 3 Ιουλίου 2017

#### **ABSTRACT**

Over the last decade GPUs have been established in the High Performance Computing sector as compute accelerators. The primary characteristics that justify this modern trend are the exceptionally high compute throughput and the remarkable power efficiency of GPUs. However, GPU performance is highly sensitive to many factors, e.g. the type of memory access patterns, branch divergence, the degree of parallelism and potential latencies. Consequently, the execution time of a kernel on a GPU is a difficult to predict measure. Unless the kernel is latency bound, a rough estimate of the execution time on a particular GPU could be provided by applying the roofline model, which is used to map the program's operation intensity to the peak expected performance on a particular processor. Though this approach is straightforward, it cannot not provide accurate prediction results.

In this thesis, after validating the roofline principle on GPUs by employing a micro-benchmark, an analytical throughput oriented performance model is proposed. In particular, this improves on the roofline model following a quantitative approach and a completely automated GPU performance prediction technique is presented. In this respect, the proposed model utilizes micro-benchmarking and profiling in a "black-box" fashion as no inspection of source/binary code is required. The proposed model combines GPU and kernel parameters in order to characterize the performance limiting factor and to predict the execution time on target hardware, by taking into account the efficiency of beneficial computational instructions. In addition, the "quadrant-split" visual representation is proposed, which captures the characteristics of multiple processors in relation to a particular kernel.

The experimental evaluation combines test executions on stencil computations (red/black SOR, LMSOR), matrix multiplication (SGEMM) and a total of 28 kernels of the Rodinia benchmark suite, all applied on six CUDA GPUs. The observed absolute error in predictions was 27.66% in the average case. Special cases of mispredicted results were investigated and justified. Moreover, the aforementioned micro-benchmark was used as a subject for performance prediction and the exhibited results were very accurate. Furthermore, the performance model was also examined in a cross vendor configuration by applying the prediction method on the same kernel source codes through the HIP programming environment supported on the AMD ROCm platform. Prediction errors were comparable to CUDA experiments despite the significant architectural differences evident between different vendor GPUs.

**SUBJECT AREA**: Parallel computing

**KEYWORDS**: performance model, GPU, roofline model

#### ΠΕΡΙΛΗΨΗ

Κατά την τελευταία δεκαετία, οι επεξεργαστές γραφικών (GPUs) έχουν εδραιωθεί στον τομέα των υπολογιστικών συστημάτων υψηλής απόδοσης ως επιταχυντές υπολογισμών. Τα βασικά χαρακτηριστικά που δικαιολογούν αυτή τη σύγχρονη τάση είναι η εξαιρετικά υψηλή υπολογιστική απόδοση τους και η αξιοσημείωτη ενεργειακή αποδοτικότητα τους. Ωστόσο, η απόδοση τους είναι πολύ ευαίσθητη σε πολλούς παράγοντες, όπως π.χ. τον τύπο των μοτίβων πρόσβασης στη μνήμη (memory access patterns), την απόκλιση διακλαδώσεων (branch divergence), τον βαθμό παραλληλισμού και τις δυνητικές καθυστερήσεις (latencies). Συνεπώς, ο χρόνος εκτέλεσης ενός πυρήνα (kernel) σε ένα επεξεργαστή γραφικών είναι ένα δύσκολα προβλέψιμο μέγεθος. Στην περίπτωση που η απόδοση του πυρήνα δεν περιορίζεται από καθυστερήσεις, μπορεί να παρασχεθεί μια χονδρική εκτίμηση του χρόνου εκτέλεσης σε ένα συγκεκριμένο επεξεργαστή εφαρμόζοντας το μοντέλο γραμμής-οροφής (roofline), το οποίο χρησιμοποιείται για να αντιστοιχίσει την ένταση υπολογισμών του προγράμματος στην μέγιστη αναμενόμενη απόδοση για ένα συγκεκριμένο επεξεργαστή. Αν και αυτή η προσέγγιση είναι απλή, δεν μπορεί να παρέχει ακριβή αποτελέσματα πρόβλεψης.

Σε αυτή τη διατριβή, μετά την επαλήθευση της αρχής του μοντέλου γραμμής-οροφής σε επεξεργαστές γραφικών με τη χρήση ενός μικρο-μετροπρογράμματος, προτείνεται ένα αναλυτικό μοντέλο απόδοσης. Συγκεκριμένα, βελτιώνεται το μοντέλο γραμμής-οροφής ακολουθώντας μια ποσοτική προσέγγιση και παρουσιάζεται μία πλήρως αυτοματοποιημένη μέθοδος πρόβλεψης απόδοσης σε επεξεργαστή γραφικών. Από αυτή την άποψη, το προτεινόμενο μοντέλο χρησιμοποιεί την αξιολόγηση μέσω μικρο-μετροπρογραμμάτων και την καταγραφή μετρικών με μέθοδο «μαύρου κουτιού», καθώς δεν απαιτείται διερεύνηση του πηγαίου/δυαδικού κώδικα. Το προτεινόμενο μοντέλο συνδυάζει τις παραμέτρους του επεξεργαστή γραφικών και του πυρήνα για να χαρακτηρίσει τον παράγοντα περιορισμού της απόδοσης και να προβλέψει το χρόνο εκτέλεσης στο στοχευόμενο υλικό, λαμβάνοντας υπόψη την αποδοτικότητα των ωφελίμων υπολογιστικών εντολών. Επιπλέον, προτείνεται η οπτική αναπαράσταση «διαμοιρασμού-τεταρτημορίου» ("quadrant-split"), η οποία αποδίδει τα χαρακτηριστικά πολλών επεξεργαστών σε σχέση με έναν συγκεκριμένο πυρήνα.

Η πειραματική αξιολόγηση συνδυάζει δοκιμαστικές εκτελέσεις σε υπολογισμούς μορίων (κόκκινο/μαύρο SOR, LMSOR), πολλαπλασιασμό πινάκων (SGEMM) και ένα σύνολο 28 πυρήνων της σουίτας μετροπρογραμμάτων Rodinia, όλα εφαρμοσμένα σε έξι επεξεργαστές γραφικών CUDA. Το παρατηρηθέν απόλυτο σφάλμα στις προβλέψεις ήταν 27,66% στη μέση περίπτωση. Διερευνήθηκαν και αιτιολογήθηκαν ιδιαίτερες περιπτώσεις εσφαλμένων προβλέψεων. Επιπλέον, το προαναφερθέν μικρο-μετροπρόγραμμα χρησιμοποιήθηκε ως αντικείμενο για την πρόβλεψη απόδοσης και τα αποτελέσματα ήταν πολύ ακριβή. Προσθέτως, το μοντέλο απόδοσης εξετάστηκε σε σύνθετο περιβάλλον μεταξύ διαφορετικών κατασκευαστών, εφαρμόζοντας τη μέθοδο πρόβλεψης στους ίδιους πηγαίους κώδικες πυρήνων μέσω του περιβάλλοντος προγραμματισμού HIP που υποστηρίζεται από την πλατφόρμα AMD ROCm. Τα σφάλματα πρόβλεψης ήταν συγκρίσιμα αυτών των πει-

#### **ACKNOWLEDGEMENTS**

The accomplishment of this thesis would not be possible without the great assistance and guidance of my advisor, Dr. Yiannis Cotronis. He has always been encouraging and supportive on my every single step during all these years of my PhD. His support has been valuable even in cases when I needed psychological encouragement.

However, this thesis required significant support by more than one persons. I could never reach to success without the constant support and enduring patience of my loving wife, Gina Gelasi. In addition, Nikos, my two and a half years old son, is another important person in my life who inadvertently helped me reach my goal. I also want to thank my parents for their support and for shaping me up to the person I've become.

I also want to thank the rest of my advisory committee, Dr. Nektarios Kozyris and Dr. Elias Manolakos, who have been helpful with their advice and commentary. Their suggestions and guidance helped me improve the orientation of this thesis and correct my defense presentation in various aspects.

I also want to personally thank the generous support of the manager of the Radeon Open Compute department of AMD, Greg Stoner, for his support through the donation of the Radeon graphic cards used in the experiments of this thesis.

Finally, I would like to thank Dr. Nectarios Koziris and Dr. Dimitris Gizopoulos to use their NVidia Tesla M2050 and NVidia Tesla K20c installations, respectively, for the purpose of the experiments of this thesis.

#### ΣΥΝΟΠΤΙΚΗ ΠΑΡΟΥΣΙΑΣΗ ΤΗΣ ΔΙΔΑΚΤΟΡΙΚΗΣ ΔΙΑΤΡΙΒΗΣ

#### 1. Εισαγωγή

Οι επεξεργαστές γραφικών (GPUs) στην σημερινή τους μορφή, εκτός από την κλασσική τους χρήση στην ρεαλιστική απεικόνιση τρισδιάστατων μοντέλων, έχουν υιοθετηθεί και για την επίλυση δύσκολων υπολογιστικών προβλημάτων γενικού σκοπού. Τα χαρακτηριστικά υψηλής απόδοσης για υπολογιστικό φόρτο μεγάλης παραλληλίας από τους επεξεργαστές γραφικών τους έχει καταστήσει ιδιαίτερα ελκυστικούς στην κοινότητα υπολογισμών υψηλής απόδοσης (High Performance Computing - HPC). Ταυτόχρονα, επιδεικνύουν υψηλούς δείκτες αποδοτικότητας σε σχέση με την ενεργειακή τους κατανάλωση. Για την εκμετάλλευσή τους αναπτύχθηκαν προγραμματιστικά περιβάλλοντα αμιγώς γενικού σκοπού. Οι παραπάνω λόγοι τους έχουν καταστήσει ως ιδανικούς επιταχυντές για την επίλυση μεγάλων υπολογιστικών προβλημάτων.

Η δημιουργία αυτού του νέου πεδίου εκμετάλλευσης των επεξεργαστών γραφικών δημιούργησε νέες ανάγκες στην μελέτη της απόδοσης τους, σε σχέση με την επίλυση υπολογιστικών προβλημάτων. Ωστόσο, ο προγραμματισμός τους τείνει να είναι επιρρεπής στην συχνή εμφάνιση προβλημάτων απόδοσης, συγκριτικά με τον προγραμματισμό των επεξεργαστών γενικού σκοπού. Η εμπειρία έχει δείξει ότι η απόδοση τους είναι πολύ πιο ευαίσθητη στην ορθή χρήση των πόρων και επομένως είναι πιο δύσκολο να εκτιμηθεί η τελική τους απόδοση. Για το σκοπό αυτό επινοήθηκαν διάφορα μοντέλα απόδοσης από την επιστημονική κοινότητα, προσανατολισμένα στις ιδιαιτερότητες των επεξεργαστών γραφικών. Πολλά από τα μοντέλα αυτά είναι αναλυτικής φύσεως, ενώ άλλα ακολουθούν την προσέγγιση της προσομοίωσης του επεξεργαστή γραφικών. Κάθε προσέγγιση έχει διαφορετικά πλεονεκτήματα και μειονεκτήματα. Η προσέγγιση της προσομοίωσης μπορεί να είναι εξαιρετικά ακριβής αλλά ταυτόχρονα και μια χρονοβόρος διαδικασία. Αντιθέτως, τα αναλυτικά μοντέλα τείνουν να είναι αρκετά γρηγορότερα στην εφαρμογή τους, ενώ παράλληλα τείνουν να παρέχουν καλύτερη αίσθηση πάνω στα χαρακτηριστικά υψηλού επιπέδου της εφαρμογής που μπορούν να επηρεάσουν τις επιδόσεις

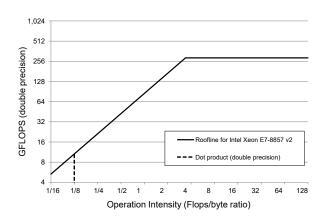

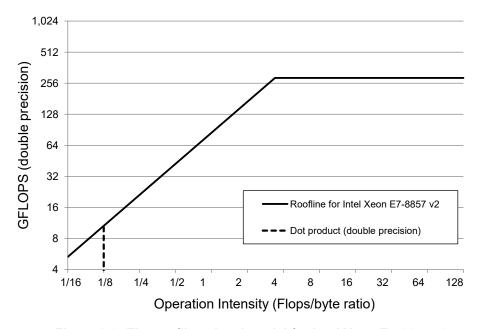

Ένα από τα κλασσικά αναλυτικά μοντέλα απόδοσης είναι το μοντέλο γραμμής-οροφής (roofline). Το μοντέλο αυτό είναι ένα οπτικό μοντέλο που παρέχει ενόραση στην μέγιστη αναμενόμενη απόδοση ενός πυρήνα, λαμβάνοντας υπόψη τις ανάγκες τόσο σε καθαρούς υπολογισμούς, όσο και στην κίνηση από/προς τη μνήμη. Βασίζεται στην υπόθεση ότι περιοριστικό παράγοντα της απόδοσης αποτελεί είτε η ρυθμαπόδοση υπολογισμών, είτε το εύρος ζώνης της μνήμης του επεξεργαστή. Ο προσδιορισμός της εκάστοτε περίπτωσης προσδιορίζεται με βάση τις σχετικές απαιτήσεις πράξεων της εφαρμογής. Ο λόγος υπολογισμών προς μετακινήσεων μνήμης εκφράζεται με το μέτρο της έντασης πράξεων (operation intensity), το οποίο εκτιμάται σε μονάδες flop/byte και χρησιμοποιείται για τον προσδιορισμό του παράγοντα περιορισμού της απόδοσης σε ένα συγκεκριμένο επεξεργαστή. Η εκτίμηση της εντάσεως πράξεων ενός προγράμματος προσδιορίζεται μέσω της

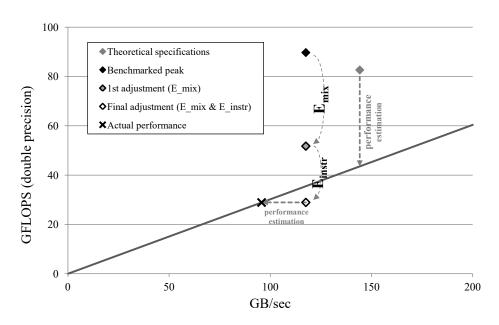

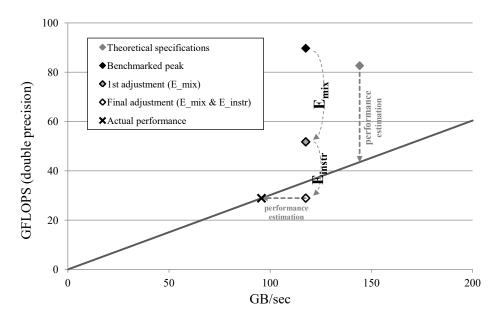

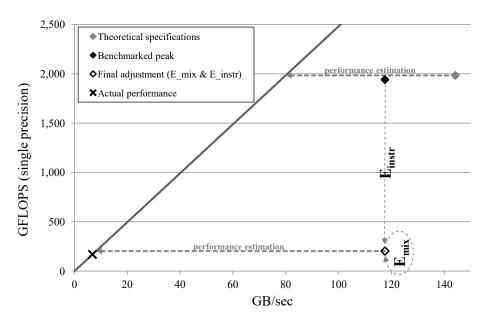

εξίσωσης (1). Για παράδειγμα, στο σχήμα 1 απεικονίζεται η γραμμή που εκφράζει τις προδιαγραφές ενός επεξεργαστή. Το διακεκομμένο κάθετο ευθύγραμμο τμήμα εκφράζει την ένταση πράξεων μιας εφαρμογής και το σημείο στο οποίο συναντά η τελευταία το γράφημα του επεξεργαστή ορίζει την μέγιστη αναμενόμενη απόδοση.

$$O_{kernel} = \frac{Operations_{(compute)}}{Traffic_{(memory)}} \tag{1}$$

Σχήμα 1: Το μοντέλο γραμμής-οροφής για τον Intel Xeon E7-8857 v2.

Το μοντέλο γραμμής-οροφής έχει εφαρμοστεί σε πληθώρα μελετών και εφαρμογών λόγω της απλότητάς του και της γενικότητάς του. Η ικανότητά του να αποδίδει με οπτικό τρόπο την μέγιστη δυνατή απόδοση ενός πυρήνα (kernel) σε ένα επεξεργαστή αποτελεί ένα από τα σημαντικότερα προτερήματα του. Ωστόσο, το μοντέλο είναι σε μεγάλο βαθμό αφαιρετικό και στις περισσότερες περιπτώσεις δεν επιτρέπει την διενέργεια ρεαλιστικών προσεγγίσεων παρά μόνο την εκτίμηση ενός άνω φράγματος απόδοσης.

# 2. Το μοντέλο γραμμής-οροφής σε επεξεργαστή γραφικών και η αναπαράσταση διαμοιρασμού-τεταρτημορίου

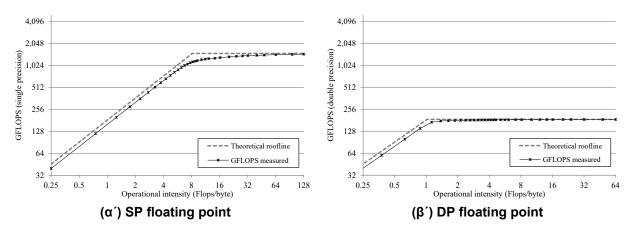

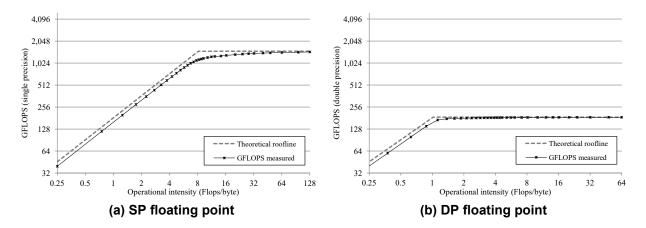

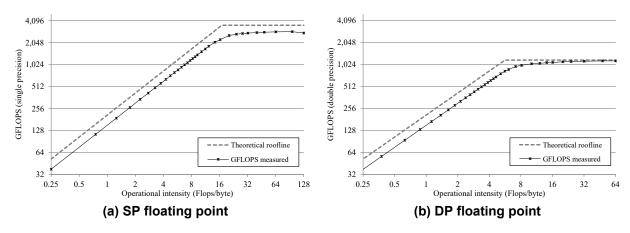

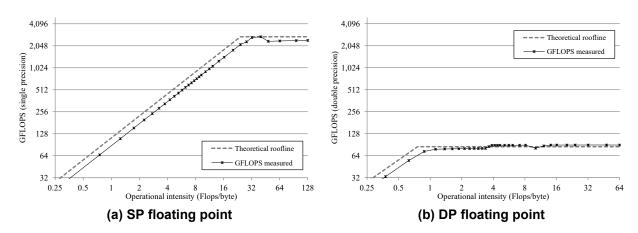

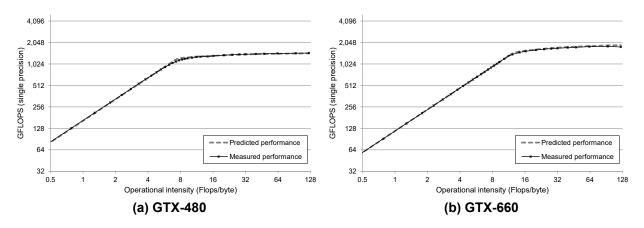

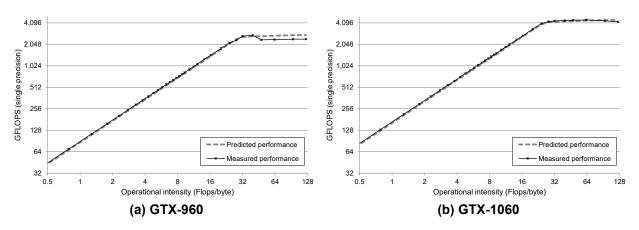

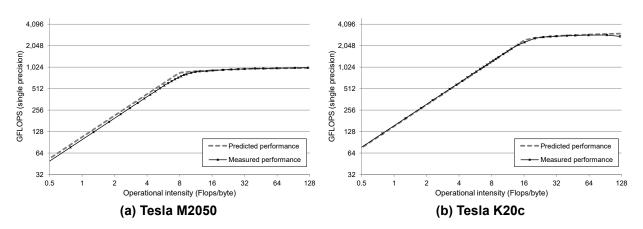

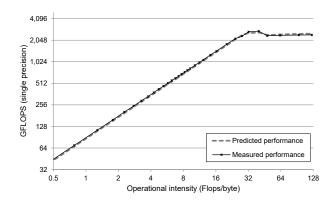

Αρχικά, σε αυτή τη διατριβή μελετάται η εφαρμοσιμότητα του μοντέλου γραμμής-οροφής στους επεξεργαστές γραφικών. Η μελέτη πραγματοποιείται μέσω ειδικού μετροπρογράμματος που αναπτύχθηκε για αυτό το σκοπό, το οποίο εκτιμά την απόδοση των επεξεργαστών γραφικών πειραματικά σε μικτό φόρτο υπολογισμών και μεταφορών μνήμης, σε ένα εύρος τιμών έντασης πράξεων. Μέσω του μετροπρογράμματος πραγματοποιήθηκε πειραματική προσέγγιση της θεωρητικής γραμμής-οροφής για 3 επεξεργαστές γραφικών, σε πράξεις κινητής υποδιαστολής μονής και διπλής ακρίβειας. Ενδεικτικά, στο σχήμα 2 απεικονίζεται η απόδοση του επεξεργαστή γραφικών GTX-480. Η διακεκομμένη γραμμή αναπαριστά την θεωρητική μέγιστη απόδοση με βάση τις προδιαγραφές του επεξεργαστή γραφικών. Οι παρατηρούμενη απόδοση ακολουθεί ένα παραπλήσιο μοτίβο της θεωρητικής απεικόνισης όπως περιγράφεται από την γραμμή-οροφής. Συγκεκριμένα, η απόδοση

Σχήμα 2: Πειραματική προσέγγιση της γραμμής-οροφής σε επ.γραφικών GTX-480

του επεξεργαστή γραφικών GTX-480 προσέγγισε σε μεγάλο βαθμό την θεωρητική μέγιστη υπολογιστική απόδοση (οριζόντιο τμήμα γραφήματος γραμμής-οροφής). Στο τμήμα που η απόδοση εξαρτάται από το εύρος ζώνης μνήμης (κεκλιμένο τμήμα γραφήματος γραμμής-οροφής), η απόδοση είναι ελαφρώς μειωμένη και το φαινόμενο αυτό εκφράζει την αδυναμία επίτευξης της μέγιστης θεωρητικής απόδοσης του εύρους ζώνης μνήμης σε πραγματικούς επεξεργαστές γραφικών. Παρόλο που η μέγιστη θεωρητική απόδοση του GTX-480 που χρησιμοποιήθηκε για τα πειράματα είναι 182GB/sec, το εύρος ζώνης μνήμης που μετρήθηκε δεν ξεπέρασε τα 163GB/sec. Γενικά, τα αποτελέσματα έδειξαν ικανοποιητική ταύτιση της θεωρητικής γραμμής-οροφής με την πειραματική. Παρατηρήθηκαν κάποιες αποκλίσεις, κυρίως στην επίτευξη του μεγίστου εύρους ζώνης μνήμης και προκύψαν παρατηρήσεις.

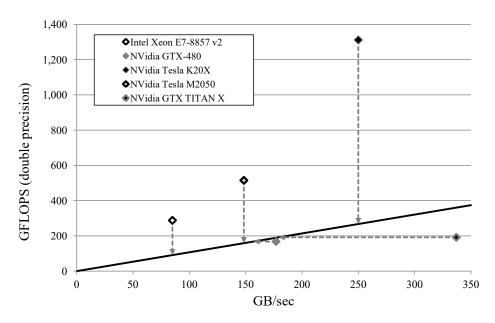

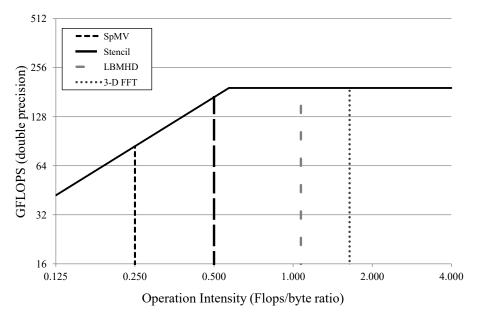

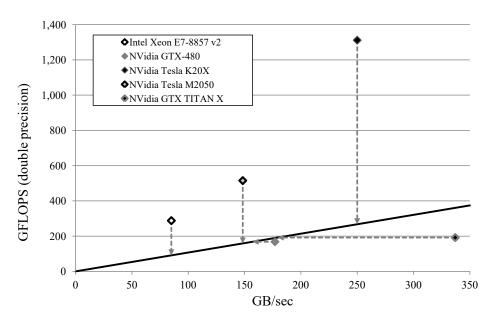

Μια εναλλακτική μέθοδος απεικόνισης που προτείνεται σε αυτή τη διατριβή είναι η απεικόνιση «διαμοιρασμού-τεταρτημορίου» (quadrant-split). Συγκριτικά με την απεικόνιση γραμμής-οροφής, ο οριζόντιος άξονας περιγράφει το εύρος ζώνης μνήμης αντί της εντάσεως πράξεων. Με αυτή τη διαφοροποίηση ο κάθε επεξεργαστής περιγράφεται σαν σημείο και η εφαρμογή ως μια ημι-ευθεία που διαπερνά το σημείο τομής των αξόνων και η κλίση της προσδιορίζεται από την τιμή της εντάσεως πράξεων της εφαρμογής. Για παράδειγμα, στο σχήμα 3 αναπαρίσταται το πρόβλημα LBMHD (Lattice-Boltzmann Magnetohydrodynamic) σε σχέση με 4 επεξεργαστές γραφικών και ένα επεξεργαστή γενικού σκοπού. Τα σημεία του επεξεργαστή Intel Xeon και των NVidia Tesla επεξεργαστών γραφικών εντοπίζονται πάνω από την ημι-ευθεία, το οποίο σημαίνει ότι στους συγκεκριμένους επεξεργαστές η απόδοση αναμένεται να καθορίζεται από το μέγιστο εύρος ζώνης μνήμης (memory bound). Σε αντίθεση, τα σημεία των επεξεργαστών γραφικών GTX-480 και GTX-Titan X εντοπίζονται κάτω από την ημι-ευθεία και συνεπώς η απόδοση τους αναμένεται να καθορίζεται από την μέγιστη ρυθμαπόδοση των επεξεργαστών (compute bound). Οι διακεκομμένες γραμμές υποδεικνύουν τα σημεία πάνω στην ημι-ευθεία του προβλήματος που αναπαριστούν την εκτιμώμενη απόδοση για κάθε επεξεργαστή στο συγκεκριμένο πρόβλημα. Για την εκτίμηση της απόδοσης των άνω σημείων πραγματοποιείται διάσχιση από το σημείο με κάθετη φορά προς τα κάτω, μέχρι την συνάντηση της ημι-ευθείας. Α- ντίστοιχα, για την εκτίμηση της απόδοσης των κάτω σημείων πραγματοποιείται διάσχιση από το σημείο με οριζόντια φορά προς τα αριστερά, μέχρι την συνάντηση της ημι-ευθείας. Η τομή των διακεκομμένων τμημάτων με την ημι-ευθεία της εφαρμογής υποδεικνύουν την αναμενόμενη απόδοση σε κάθε επεξεργαστή.

Σχήμα 3: Η αναπαράσταση διαμοιρασμού-τεταρτημορίου του προβλήματος LBMHD με εφαρμογή σε 5 επεξεργαστές (γραφικών και γενικού σκοπού).

Με την απεικόνιση διαμοιρασμού-τεταρτημορίου περισσότεροι του ενός επεξεργαστές μπορούν να αναπαρασταθούν με φυσικό τρόπο σε ένα μοναδικό γράφημα. Η γραφική εκτίμηση της θεωρητικής απόδοσης πραγματοποιείται με απλό και ευθύ τρόπο. Η αναπαράσταση γραμμής-οροφής είναι προσανατολισμένη στην απεικόνιση ενός επεξεργαστή σε σχέση με πολλά προβλήματα, ενώ η προτεινόμενη απεικόνιση προσφέρεται για την περίπτωση μίας εφαρμογής σε σχέση με πολλούς επεξεργαστές με διαφορετικά χαρακτηριστικά.

#### 3. Ένα ποσοτικό μοντέλο απόδοσης για επεξεργαστές γραφικών

Βασική συνεισφορά της διατριβής αποτελεί ένα μοντέλο απόδοσης για επεξεργαστή γραφικών, που εστιάζει στην ποσοτική προσέγγιση. Αφού προηγήθηκε η παρατήρηση της ικανοποιητικής προσέγγισης του μοντέλου γραμμής-οροφής μέσω της εφαρμογής μικρομετροπρογράμματος, στη συνέχεια προέκυψε το ερώτημα σχετικά με το ποια χαρακτηριστικά πραγματικών εφαρμογών για επεξεργαστές γραφικών αποτρέπουν την επίτευξη μέγιστης απόδοσης, παραπλήσιας με αυτήν που αποδίδεται από το μοντέλο γραμμήςοροφής. Με αυτό το σκεπτικό, μελετήθηκαν τα χαρακτηριστικά βελτιστοποιημένων εφαρμογών τα οποία μπορούν να επηρεάσουν αρνητικά την απόδοση σε σημαντικό βαθμό.

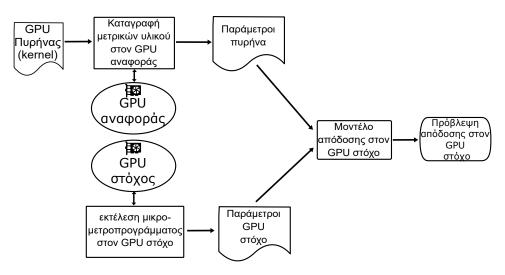

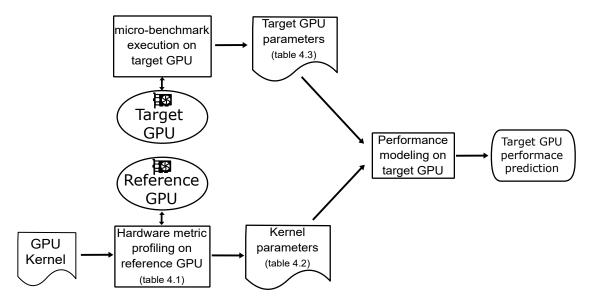

Αυτή η μελέτη οδήγησε στον ορισμό ενός βελτιωμένου μοντέλου απόδοσης βασισμένο

Σχήμα 4: Η ροή των βημάτων εκτέλεσης της μεθόδου πρόβλεψης απόδοσης.

στο μοντέλο γραμμής-οροφής, το οποίο παράλληλα εμβαθύνει ακολουθώντας ποσοτική προσέγγιση με ρεαλιστικές εκτιμήσεις πραγματικών εφαρμογών. Το διάγραμμα ροής των βημάτων όπως περιγράφονται από την προτεινόμενη μέθοδο απεικονίζεται στο σχήμα 4. Βασικά χαρακτηριστικά που ενσωματώθηκαν στο μοντέλο αποτελούν η αποδοτικότητα των ωφελίμων πράξεων, καθώς επίσης και η αποδοτικότητα του συνόλου εκτελούμενων εντολών ως προς το ποσοστό κατά το οποίο εκμεταλλεύονται τους εκτελεστικούς πόρους του επεξεργαστή γραφικών. Ωφέλιμες πράξεις θεωρούνται οι πράξεις που συνεισφέρουν άμεσα στην επίλυση του προβλήματος, δηλαδή τυπικά οι πράξεις κινητής υποδιαστολής. Ως αποδοτικότητα ωφελίμων πράξεων ορίζεται το στατιστικό μέγεθος που εκφράζει την αναμενόμενη τιμή του πλήθους πράξεων που πραγματοποιεί κάθε υπολογιστική εντολή του πυρήνα διαιρεμένο με το μέγιστο πλήθος πράξεων που μπορεί να πραγματοποιήσει μια υπολογιστική εντολή, τυπικά ο αριθμός 2, όπως προκύπτει από το πλήθος πράξεων που πραγματοποιεί μια εντολή τύπου πολλαπλασιασμού-πρόσθεσης (multiply-addition). Ως αποδοτικότητα του συνόλου εκτελούμενων εντολών ορίζεται το ποσοστό κατά το οποίο οι εκτελεστικοί πόροι του επεξεργαστή πραγματοποιούν εκτέλεση ωφελίμων εντολών αντί δευτερευόντων. Τέλος, η μέθοδος λαμβάνει υπόψη πραγματικές μετρήσεις των ρυθμαποδόσεων για ένα σύνολο προκαθορισμένων πράξεων και του εύρους ζώνης μνήμης με την χρήση μικρο-μετροπρογραμμάτων αντί των προδιαγραφών που δίνει ο κατασκευαστής.

Συγκεκριμένα, οι απαιτούμενες μετρικές υλικού που καταγράφονται κατά την εκτέλεση του πυρήνα παρέχονται στον πίνακα 1. Αυτές οι μετρικές απαιτούνται για την εκτίμηση των παραμέτρων του πυρήνα, οι οποίες παρουσιάζονται στον πίνακα 2. Ως κανόνας υπολογισμού για την εκτίμηση του  $K_{type}$  εφαρμόσθηκε η επιλογή του  $\emph{fp64}$  εφόσον η μετρική  $M_{fp64}$  είναι μη μηδενική, του  $\emph{fp32}$  αν η μετρική  $M_{fp32}$  είναι μη μηδενική ή διαφορετικά του  $\emph{int}$ . Για

Πίνακας 1: Οι απαιτούμενες μετρικές υλικού του NVidia GPU για την εκτίμηση των παραμέτρων του πυρήνα.

| Μετρική                 | Συμβολισμός        |

|-------------------------|--------------------|

| flop_count_sp_fma       | $M_{fma32}$        |

| flop_count_dp_fma       | $M_{fma64}$        |

| inst_compute_ld_st      | $M_{ldst}$         |

| inst_executed           | $M_{inst}$         |

| inst_fp_32              | $M_{fp32}$         |

| inst_fp_64              | $M_{fp64}$         |

| inst_integer            | $M_{int}$          |

| dram_read_transactions  | $M_{tran	ext{-}r}$ |

| dram_write_transactions | $M_{tran	ext{-}w}$ |

Πίνακας 2: Το σύνολο των απαιτούμενων παραμέτρων του πυρήνα.

| Παράμετρος  | Περιγραφή                                          | Ανάκτηση  |

|-------------|----------------------------------------------------|-----------|

| $K_{type}$  | $K_{type}$ Τύπος κύριων πράξεων (fp64, fp32 ή int) |           |

| $W_{comp}$  | Πράξεις υπολογισμών                                | τύπος (2) |

| $W_{traf}$  | Πλήθος προσπελαθέντων DRAM bytes                   | τύπος (3) |

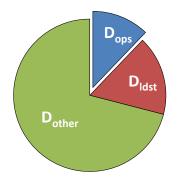

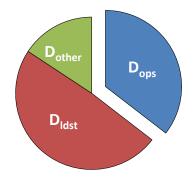

| $E_{mix}$   | Αποδοτικότητα μίξης πράξεων (%)                    | τύπος (4) |

| $D_{ops}$   | Πυκνότητα εντολών πράξεων (%)                      | τύπος (7) |

| $D_{ldst}$  | Πυκνότητα εντολών ανάκτησης/αποθήκευσης (%)        | τύπος (8) |

| $D_{other}$ | Πυκνότητα άλλων εντολών (%)                        | τύπος (9) |

την εκτίμηση των παραμέτρων απαιτείται η εφαρμογή των παρακάτω τύπων:

$$W_{comp} = \begin{cases} M_{fp32} + M_{fma32}, & \text{av } K_{type} = \text{fp32} \\ M_{fp64} + M_{fma64}, & \text{av } K_{type} = \text{fp64} \\ M_{int}, & \text{av } K_{type} = \text{int} \end{cases}$$

(2)

$$W_{traf} = 32 \times (M_{tran-r} + M_{tran-w}) \tag{3}$$

$$E_{mix} = \begin{cases} \frac{M_{fp32} + M_{fma32}}{2 \times M_{fp32}} \times 100\%, & \text{av } K_{type} = \text{fp32} \\ \frac{M_{fp64} + M_{fma64}}{2 \times M_{fp64}} \times 100\%, & \text{av } K_{type} = \text{fp64} \\ 50\%, & \text{av } K_{type} = \text{int} \end{cases}$$

(4)

$$I_{ops} = egin{cases} M_{fp32}, & \operatorname{av} K_{type} = \operatorname{fp32} \\ M_{fp64}, & \operatorname{av} K_{type} = \operatorname{fp64} \\ M_{int}, & \operatorname{av} K_{type} = \operatorname{int} \end{cases}$$

(5)

$$I_{total} = 32 \times M_{inst} \tag{6}$$

$$D_{ops} = \frac{I_{ops}}{I_{total}} \times 100\% \tag{7}$$

$$D_{ldst} = \frac{M_{ldst}}{I_{total}} \times 100\% \tag{8}$$

$$D_{other} = 100\% - D_{ops} - D_{ldst}$$

(9)

Οι απαιτούμενοι παράμετροι του επεξεργαστή γραφικών με τις οποίες θα πραγματοποιηθεί η πρόβλεψη δίνονται στον πίνακα 3. Όλες οι παράμετροι εκτιμώνται με την εκτέλεση ειδικών μικρο-μετροπρογραμμάτων.

Πίνακας 3: Το σύνολο των παραμέτρων του επεξεργαστή γραφικών.

| Παράμετρος          | Περιγραφή                                              | Μονάδα        |

|---------------------|--------------------------------------------------------|---------------|

| $\overline{T_{SP}}$ | Ρυθμαπόδοση πρ.κινητής υποδιαστολής (μονής ακρίβειας)  | GFLOPS        |

| $T_{DP}$            | Ρυθμαπόδοση πρ.κινητής υποδιαστολής (διπλής ακρίβειας) | <b>GFLOPS</b> |

| $T_{int}$           | Ρυθμαπόδοση πρ.ακεραίων (πολλαπλασπροσθέσεων)          | GIOPS         |

| $T_{add}$           | Ρυθμαπόδοση πράξεων ακεραίων (προσθέσεων)              | GIOPS         |

| $T_{ldst}$          | Ρυθμαπόδοση εντ.ανάκτησης/αποθήκευσης διαμοιραζ.μν.    | GOPS          |

| $B_{mem}$           | Εύρος ζώνης μνήμης                                     | GB/sec        |

Η πρόβλεψη απόδοσης προϋποθέτει την εκτίμηση της αποδοτικότητας εντολών ( $E_{instr}$ ) και στην συνέχεια την εκτιμώμενη μέγιστη ρυθμαπόδοση σε ωφέλιμες πράξεις ( $T'_{op}$ ). Ο υπολογισμός πραγματοποιείται ως ακολούθως:

$$T_{op} = egin{cases} T_{SP}, & \operatorname{av} K_{type} = \operatorname{fp32} \ T_{DP}, & \operatorname{av} K_{type} = \operatorname{fp64} \ T_{int}, & \operatorname{av} K_{type} = \operatorname{int} \end{cases}$$

(10)

$$W_{op} = \frac{T_{SP}}{T_{op}} \tag{11}$$

$$W_{ldst} = \frac{1/2T_{SP}}{T_{ldst}} \tag{12}$$

$$W_{other} = \frac{1/2T_{SP}}{T_{add}} \tag{13}$$

$$C_{op} = D_{ops} \times W_{op} \tag{14}$$

$$C_{ldst} = D_{ldst} \times W_{ldst} \tag{15}$$

$$C_{other} = D_{other} \times W_{other} \tag{16}$$

$$E_{instr} = \frac{C_{op}}{C_{op} + C_{ldst} + C_{other}} \times 100\%$$

(17)

$$T'_{op} = E_{mix} \times E_{instr} \times T_{op} \tag{18}$$

Στην τελική εκτιμώμενη απόδοση λαμβάνεται υπόψη και η χρήση του εύρους ζώνης μνήμης όπως φαίνεται στον παρακάτω τύπο:

$$T_{predicted} = \begin{cases} T'_{op}, & \text{av } O_{krn} > O_{dev} \\ O_{krn} \times B_{mem}, & \text{av } O_{krn} \leq O_{dev} \end{cases}$$

(19)

Η μέθοδος αναλύθηκε με την επίδειξη μελέτης περιπτώσεων στα προβλήματα υπολογισμού μορίων (κόκκινο/μαύρο SOR) και πολλαπλασιασμού πινάκων, με επεξεργαστή γραφικών αναφοράς τον GTX-480 και πρόβλεψη στον πάνω στον επεξεργαστή γραφικών GTX-660. Η πρόβλεψη με οπτική αναπαράσταση απεικονίζεται στο σχήμα 5. Τα αποτελέσματα επαληθεύτηκαν τόσο με την αντιπαραβολή τους με πραγματικές μετρήσεις όσο και με την ανάλυση τιμών μετρικών χρησιμοποίησης (utilization metrics) για τους διάφορους πόρους του επεξεργαστή γραφικών. Τέλος, μελετήθηκαν οι προϋποθέσεις κάτω από τις οποίες αναμένεται η μέθοδος να αποφέρει αξιόπιστα αποτελέσματα.

Σχήμα 5: Οπτικοποίηση της πρόβλεψης απόδοσης της μεθόδου κόκκινο/μαύρο SOR στον επεξεργαστή γραφικών GTX-660 με την εφαρμογή των προσαρμογών αποδοτικότητας.

#### 4. Πειραματική αξιολόγηση

Στη συνέχεια ακολουθεί η πειραματική αξιολόγηση της μεθόδου. Επιλέχθηκε ένα ευρύ σύνολο εφαρμογών, αποτελούμενο από υπολογισμούς μορίων (stencils), πολλαπλασιασμό πινάκων (SGEMM) και 28 πυρήνες από 16 μετροπρογράμματα της σουίτας Rodinia. Οι εφαρμογές υπολογισμών μορίων περιελάμβαναν τις μεθόδους κόκκινο/μαύρο (red/black) SOR και LMSOR, οι υλοποιήσεις των οποίων αναπτύχθηκαν και μελετήθηκαν εκτενώς προγενέστερα κατά τη διάρκεια της εκπόνησης της διατριβής και όπως αποδείχθηκε πειραματικά, η αναδιάταξη των στοιχείων με βάση το χρώμα καθώς επίσης και η τακτική του επανυπολογισμού μπορούν να οδηγήσουν σε σημαντική επιτάχυνση της εκτέλεσης προβλημάτων με έντονη χρήση της μνήμης. Τα αποτελέσματα των προβλέψεων αναλύθηκαν και σε περιπτώσεις σημαντικής απόκλισης με τις πραγματικές μετρήσεις πραγματοποιήθηκε πρόσθετη ανάλυση για την αιτιολόγηση των αποτελεσμάτων. Στην πλειονότητα των περιπτώσεων (>50%) το απόλυτο σφάλμα πρόβλεψης εκτιμήθηκε κάτω του 25%, το οποίο και θεωρήθηκε αρκετά ικανοποιητικό. Επιπλέον, μελετήθηκε η ακρίβεια των αποτελεσμάτων του μοντέλου καθώς εφαρμόστηκε στο μικρο-μετροπρόγραμμα που αναφέρθηκε στο πρώτο μέρος. Τα αποτελέσματα ήταν εξαιρετικά ακριβή. Στην αρχική μορφή το μοντέλο περιορίστηκε στο περιβάλλον λογισμικού και υλικού της NVidia το οποίο αποτελεί προϋπόθεση για το περιβάλλον CUDA.

#### 5. Αξιολόγηση μεταξύ διαφορετικών κατασκευαστών και περιορισμοί του μοντέλου

Σε μια δεύτερη μελέτη διερευνήθηκε η εφαρμοσιμότητα της μεθόδου σε επεξεργαστή γραφικών διαφορετικού κατασκευαστή. Το προγραμματιστικό περιβάλλον που επιλέχθηκε είναι το HIP, κάτω από την πλατφόρμα ROCm της AMD, το οποίο προσφέρει ένα γρήγορο και σχεδόν αυτοματοποιημένο τρόπο μετάβασης από το CUDA, διατηρώντας κατ ουσίαν τον κώδικα των πυρήνων αναλλοίωτο. Η ανάκτηση των τιμών των παραμέτρων των πυρήνων πραγματοποιήθηκε σε επεξεργαστή γραφικών της NVidia λόγω έλλειψης των αντιστοίχων μετρικών στους επεξεργαστές γραφικών της ΑΜD. Η πρόβλεψη απόδοσης πραγματοποιήθηκε για τον επεξεργαστή γραφικών της ΑΜD. Παρ όλες τις διαφορές των μεταξύ αρχιτεκτονικών τα αποτελέσματα πρόβλεψης στα 3 προγράμματα στα οποία εφαρμόστηκε η ανάλυση (μέθοδος κόκκινο/μαύρο SOR, πολλαπλασιασμός πινάκων και το lavaMD από την σουίτα Rodinia) έδειξαν ιδιαίτερα θετικά αποτελέσματα καθώς το απόλυτο σφάλμα εκτιμήθηκε στα ίδια πλαίσια στα οποία εκτιμήθηκε και στο περιβάλλον CUDA. Τέλος, πραγματοποιήθηκε εκτενής ανάλυση των εγγενών περιορισμών του μοντέλου και των ορίων του. Ακόμα περισσότερο, μελετήθηκε η εφαρμογή του μοντέλου σε δύο ακόμα μικρο-μετροπρογράμματα, τα οποία επίσης αναπτύχθηκαν στα πλαίσια της διατριβής. Το πρώτο προκαλεί έντονη χρήση των βοηθητικών μνημών (cache) του 1ου και 2ου επιπέδου και το δεύτερο προκαλεί έντονη χρήση της διαμοιραζόμενης μνήμης (shared memory) του επεξεργαστή γραφικών. Τα αποτελέσματα αναδεικνύουν δύο από τους περιορισμούς του μοντέλου που αναφέρθηκαν προηγουμένως με πειραματικό τρόπο. Σε γενικές γραμμές, το προτεινόμενο μοντέλο ενσωματώνει τα χαρακτηριστικά της αφαιρετικότητας και της ικανότητας ρεαλιστικής πρόβλεψης σε μια ιδανική ισορροπία.

#### 6. Συμπεράσματα και μελλοντικές κατευθύνσεις

Σε αυτή τη διατριβή παρουσιάζεται ένα αναλυτικό μοντέλο απόδοσης, το οποίο βασίζεται στο μοντέλο γραμμής-οροφής. Η βασική αρχή του τελευταίου επαληθεύτηκε πειραματικά στους επεξεργαστές γραφικών με την ανάπτυξη εξειδικευμένου μικρο-μετροπρογράμματος, μέσω του οποίου η απόδοση διερευνήθηκε σε ένα ευρύ φάσμα τιμών εντάσεως πράξεων. Μέσω ποσοτικής προσέγγισης, το προτεινόμενο μοντέλο απόδοσης είναι ικανό να παρέχει προβλέψεις που προσεγγίζουν πραγματικούς χρόνους εκτέλεσης στο υλικό. Πρόσθετα, παρουσιάστηκε μια εναλλακτική οπτική αναπαράσταση, ονομαζόμενη «διαμοιρασμού-τεταρτημορίου», η οποίο παρέχει βελτιωμένη ενόραση σε περιπτώσεις όπου πολλοί επεξεργαστές αναπαριστώνται σε σχέση με μία εφαρμογή. Η αξία της απλότητας του μοντέλου και το υψηλό επίπεδο αφαιρετικότητας επιτρέπουν την παροχή αποτελεσμάτων, τα οποία μπορούν εύκολα να ερμηνευθούν και να αξιοποιηθούν από τον προγραμματιστή για την εξαγωγή πολύτιμων συμπερασμάτων.

Ένα από τα σημαντικά σημεία της προτεινόμενης μεθόδου είναι η ικανότητά της να εξαγάγει τις τιμές των παραμέτρων με την εκμετάλλευση ενός απλού συνόλου τιμών μετρικών υλικού. Η σύλληψη των τιμών του πραγματοποιείται με προσέγγιση «μαύρο-κουτί» καθώς δεν απαιτεί κάποια εσωτερική γνώση των εσωτερικών δομών του πυρήνα. Επιπλέον, η προτεινόμενη μέθοδος μπορεί να αναπτυχθεί ως ένα πλήρως αυτοματοποιημένο εργαλείο, το οποίο να λειτουργεί χωρίς την παρέμβαση του προγραμματιστή ή προηγούμενη διερεύνηση του κώδικα του πυρήνα.

Η μέθοδος επιτρέπει καλύτερη κατανόηση του φόρτου υπολογισμού και μνήμης σε αντίθεση με μια αμιγώς θεωρητική προσέγγιση κυρίως για δύο λόγους. Πρώτον, τόσο η εκτέλεση των μη ουσιαστικών εντολών όσο και των εντολών ανάκτησης/αποθήκευσης λαμβάνονται υπόψη μέσω της μοντελοποίησης των επιπτώσεων τους στον κορεσμό της διοχέτευσης εντολών. Πρόσθετα, ο τύπος της μίξης υπολογιστικών πράξεων λαμβάνεται επίσης υπόψη, δηλαδή η αποδοτικότητά της σε σχέση με το πλήθος πράξεων ανά εντολή. Δεύτερον, οι απαιτήσεις σε φόρτο προσβάσεων μνήμης εκτιμώνται μέσω της μέτρησης της πραγματικής κίνησης στη μνήμη, το οποίο σημαίνει ότι οι τοπικότητες καθώς επίσης και οι συγχωνεύσεις των προσβάσεων λαμβάνονται υπόψη εμμέσως στο μοντέλο.

Σαν μελλοντική κατεύθυνση προτείνεται η βελτίωση του μοντέλου με στόχο την καλύτερη ακρίβεια πρόβλεψης. Κάποιες βελτιώσεις θα μπορούσαν να περιλαμβάνουν την καλύτερη εκτίμηση του κόστους εκτέλεσης των εντολών, την ποσοτικοποίηση της απόκλισης εκτέλεσης των νημάτων, του μειωμένου παραλληλισμού λόγω άλλων φαινομένων όπως συγκρούσεων πρόσβασης σε διαμοιραζόμενη ή σταθερή μνήμη. Η μεταβλητότητα των φαινομένων λόγω βοηθητικής μνήμης είναι επίσης ένα ακόμα ζήτημα που θα ήταν σκόπιμο να ενσωματωθεί στο μοντέλο καθώς επηρεάζει το πλήθος των πραγματικών προσβάσεων που παρατηρούνται στην κύρια μνήμη. Ωστόσο, σε κάθε βελτίωση θα πρέπει να λαμβάνεται υπόψη η πιθανή διατάραξη της αφαιρετικότητας και του χαρακτήριστικού «μαύρο-κουτί» της μεθόδου.

## **CONTENTS**

| 1 | INTE | RODUC         | TION                                                                   | 37 |

|---|------|---------------|------------------------------------------------------------------------|----|

|   | 1.1  | Genera        | al purpose computation on GPUs                                         | 37 |

|   | 1.2  | The pe        | erformance analysis challenge                                          | 40 |

|   | 1.3  | Structu       | ure of thesis                                                          | 41 |

| 2 | BAC  | KGRO          | UND AND RELATED WORK                                                   | 43 |

|   | 2.1  | The gr        | aphics accelerator as a Graphics Processing Unit (GPU)                 | 43 |

|   | 2.2  | The G         | PU as a general purpose processor                                      | 44 |

|   |      | 2.2.1         | Unified shaders through the introduction of the Tesla GPU architecture | 45 |

|   |      | 2.2.2         | A comparison of the GPU and the CPU                                    | 47 |

|   | 2.3  | GPU c         | ompute programming paradigms                                           | 49 |

|   | 2.4  | GPU p         | erformance modeling                                                    | 51 |

|   |      | 2.4.1         | Simulation based models                                                | 52 |

|   |      | 2.4.2         | Analytical approaches                                                  | 54 |

|   |      | 2.4.3         | Specialized application models                                         | 59 |

|   |      | 2.4.4         | Power consumption oriented models                                      | 59 |

|   |      | 2.4.5         | Micro-benchmarking of the GPU                                          | 60 |

|   |      | 2.4.6         | This thesis primary contributions                                      | 61 |

| 3 | GPU  | ROOF          | LINE MODEL AND THE QUADRANT SPLIT REPRESENTATION                       | 63 |

|   | 3.1  | Rooflin       | ne GPU considerations                                                  | 63 |

|   |      | 3.1.1         | The latency hiding opportunity on GPUs                                 | 64 |

|   | 3.2  | An exp        | perimental roofline approximation                                      | 65 |

|   |      | 3.2.1         | Experimental results                                                   | 66 |

|   | 3.3  | The <i>qเ</i> | uadrant-split visual representation                                    | 68 |

| 4 | TOV  | VARDS         | A QUANTITATIVE PERFORMANCE MODEL FOR GPUS                              | 71 |

|   | 4.1  | Motiva        | tion and performance considerations                                    | 71 |

|   | 4.2  | A guar        | ntitative roofline GPU performance model                               | 72 |

|   |     | 4.2.1                                                 | An overview of the proposed model               |     | 73  |  |

|---|-----|-------------------------------------------------------|-------------------------------------------------|-----|-----|--|

|   |     | 4.2.2                                                 | Kernel parameter extraction                     | •   | 75  |  |

|   |     | 4.2.3                                                 | Target GPU parameter extraction                 |     | 77  |  |

|   |     | 4.2.4                                                 | Kernel performance estimation                   |     | 78  |  |

|   | 4.3 | Case                                                  | study 1: Red/black SOR stencil computation      | •   | 80  |  |

|   | 4.4 | Case                                                  | study 2: SGEMM computation                      | •   | 84  |  |

|   | 4.5 | Perfor                                                | mance model assumptions                         |     | 88  |  |

| 5 | EXP | ERIME                                                 | ENTAL EVALUATION                                |     | 91  |  |

|   | 5.1 | Applie                                                | ed kernel experiments                           | •   | 92  |  |

|   |     | 5.1.1                                                 | Red/black SOR stencil computation               |     | 93  |  |

|   |     | 5.1.2                                                 | LMSOR stencil computation                       | •   | 96  |  |

|   |     | 5.1.3                                                 | Matrix multiplication (SGEMM)                   |     | 99  |  |

|   |     | 5.1.4                                                 | Rodinia benchmark suite                         | •   | 99  |  |

|   | 5.2 | Perfor                                                | mance prediction experiments                    | . 1 | 101 |  |

|   |     | 5.2.1                                                 | Red/black SOR stencil computation               | . 1 | 102 |  |

|   |     | 5.2.2                                                 | LMSOR stencil computation                       | . 1 | 105 |  |

|   |     | 5.2.3                                                 | Matrix multiplication (SGEMM)                   | . 1 | 107 |  |

|   |     | 5.2.4                                                 | Mixbench performance prediction                 | . 1 | 109 |  |

|   |     | 5.2.5                                                 | Rodinia benchmark suite                         | . 1 | 110 |  |

|   |     | 5.2.6                                                 | Summary and conclusions                         | . 1 | 118 |  |

| 6 | CRO | OSS-VE                                                | ENDOR EVALUATION AND PERFORMANCE LIMITATIONS    | 1   | 23  |  |

|   | 6.1 | Portab                                                | oility on a different vendor's architecture     | . 1 | 123 |  |

|   |     | 6.1.1                                                 | The HIP/ROCm programming environment            | . 1 | 123 |  |

|   |     | 6.1.2                                                 | Kernel parameter portability                    | . 1 | 124 |  |

|   |     | 6.1.3                                                 | Experimental results                            | . 1 | 124 |  |

|   | 6.2 | Perfor                                                | mance model limitations                         | . 1 | 126 |  |

|   |     | 6.2.1                                                 | Exposing limitations through micro-benchmarking | . 1 | 129 |  |

| 7 | CON | NCLUS                                                 | IONS AND FUTURE WORK                            | 1   | 31  |  |

|   | 7.1 | Concl                                                 | usions                                          | . 1 | 131 |  |

|   | 7.2 | Future work discussion and proposed model refinements |                                                 |     |     |  |

|    |      | 7.2.1  | Additional input parameters                    | . 133 |

|----|------|--------|------------------------------------------------|-------|

|    |      | 7.2.2  | Simulated parameter extraction                 | . 134 |

| ΑE | BBRE | VIATIO | ONS - ACRONYMS                                 | 137   |

| ΑF | PPEN | DICES  |                                                | 137   |

| Α  | MIC  | RO-BE  | NCHMARK KERNEL SOURCE CODES                    | 139   |

|    | A.1  | Roofli | ne approximation (mixbench)                    | . 139 |

|    | A.2  | Comp   | ute throughput evaluation                      | . 139 |

|    | A.3  | Memo   | ry bandwidth evaluation                        | . 140 |

|    | A.4  | Load/s | store operation throughput evaluation          | . 141 |

| В  | BEN  | ICHMA  | RKING OF FAST ON-CHIP GPU MEMORIES             | 143   |

|    | B.1  | cache  | bench (L1, L2 & texture cache micro-benchmark) | . 144 |

|    | B.2  | shmer  | mbench (shared memory micro-benchmark)         | . 144 |

|    | B.3  | constb | ench (constant cache micro-benchmark)          | . 145 |

| RE | FER  | ENCES  | 5                                              | 152   |

## **LIST OF FIGURES**

| 1.1 | A comparison of CPU and GPU floating point performance evolution [73]                                                                    | 38   |

|-----|------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.1 | The graphics pipeline                                                                                                                    | 43   |

| 2.2 | The NVidia Tesla GPU architecture[55] block diagram                                                                                      | 46   |

| 2.3 | The roofline visual model for Intel Xeon E7-8857 v2                                                                                      | 57   |

| 3.1 | The roofline visual model on NVidia Titan X GPU against 4 applications                                                                   | 64   |

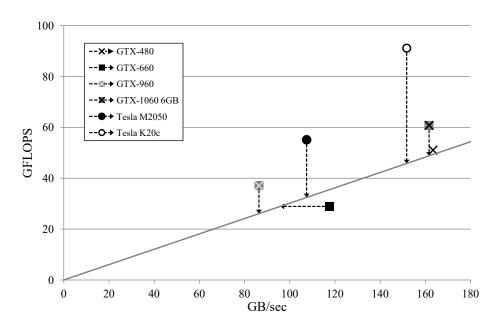

| 3.2 | Experimental roofline estimation on GTX-480 GPU                                                                                          | 66   |

| 3.3 | Experimental roofline estimation on Tesla K20c GPU                                                                                       | 67   |

| 3.4 | Experimental roofline estimation on GTX-960 GPU                                                                                          | 67   |

| 3.5 | The quadrant-split representation of the LBMHD problem using 5 CPU/GPUs.                                                                 | 69   |

| 4.1 | The performance prediction methodology flow diagram                                                                                      | 74   |

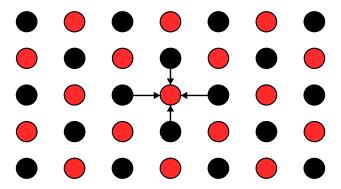

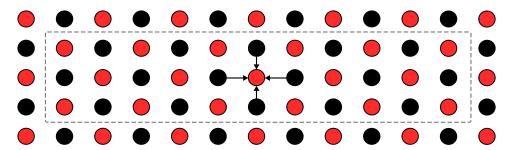

| 4.2 | Red points depend only on the neighboring black points and vice versa                                                                    | 81   |

| 4.3 | Instruction densities per instruction type for the red/black SOR kernel                                                                  | 82   |

| 4.4 | Visualization of red/black SOR performance estimation on GTX-660 with efficiency adjustments                                             | 83   |

| 4.5 | Instruction densities per instruction type for the SGEMM kernel                                                                          | 86   |

| 4.6 | Visualization of SGEMM computation performance estimation on GTX-660 with efficiency adjustments versus using theoretical specifications | 87   |

| 5.1 | Same colored points depend only on the adjacent opposite colored points.                                                                 | 93   |

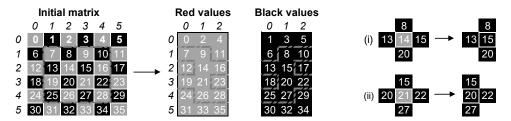

| 5.2 | Matrix element reordering                                                                                                                | 95   |

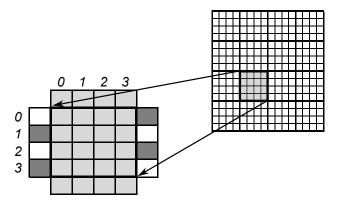

| 5.3 | Read accesses by a hypothetical 4x4 thread block                                                                                         | 96   |

| 5.4 | The proposed model applied on all GPUs for the red/black SOR computation.                                                                | .104 |

| 5.5 | Performance prediction on mixbench (SP) for GTX-480 and GTX-660                                                                          | 109  |

| 5.6 | Performance prediction on mixbench (SP) for GTX-960 and GTX-1060                                                                         | 110  |

| 5.7 | Performance prediction on mixbench (SP) for the two Tesla GPUs                                                                           | 110  |

| 5.8 | Performance prediction on mixbench (SP) for GTX-960 by using same GPU as reference.                                                      | 111  |

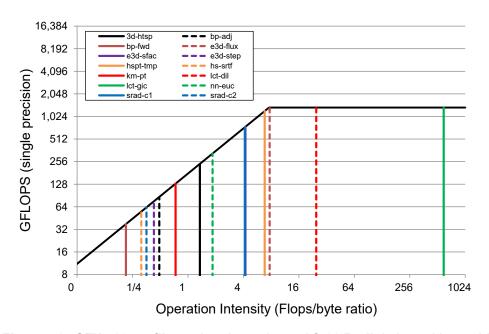

| 5.9 | GTX-480 roofline using the estimated fp32 Rodinia kernel intensities                                                                     | 111  |

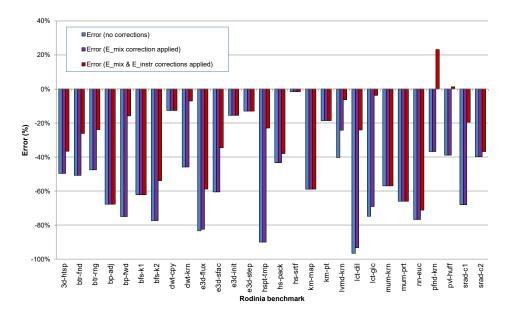

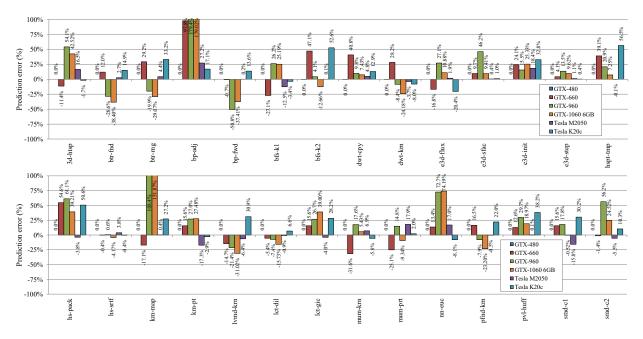

| 5.10 | Prediction errors in the Rodinia suite kernels on GTX-480, in relation to the exploitation of the efficiency factors | 13 |

|------|----------------------------------------------------------------------------------------------------------------------|----|

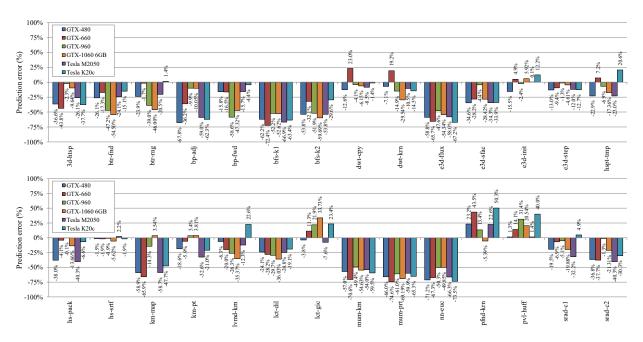

| 5.11 | Prediction error of the selected Rodinia kernels per GPU                                                             | 14 |

| 5.12 | Rodinia prediction errors after applying <i>utilization factor</i> correction 1                                      | 18 |

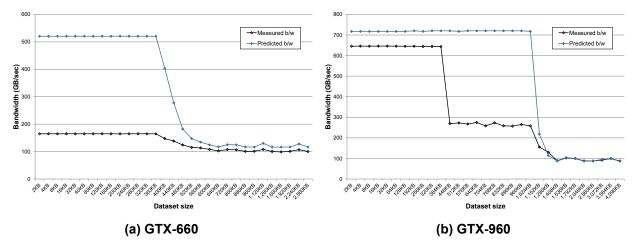

| 6.1  | Cachebench bandwidth predictions and measurements on various data-sets.1                                             | 29 |

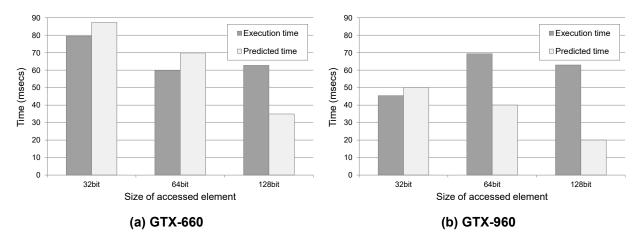

| 6.2  | Shmembench predictions and measurements for various data type sizes 1                                                | 30 |

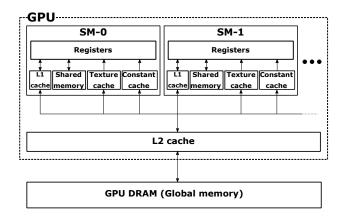

| B.1  | GPU memory hierarchy includes caches and scratchpads                                                                 | 43 |

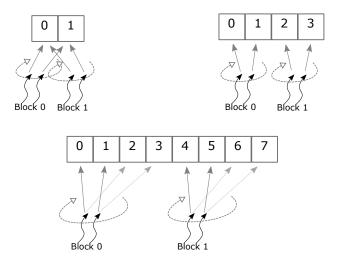

| B.2  | Thread accesses in cachebench under a simplified scenario with 3 different configurations                            | 44 |

### **LIST OF TABLES**

| 1.1  | resia P100 (GP100) GPU compared to prior GPU generations[76]                                                      | 39  |

|------|-------------------------------------------------------------------------------------------------------------------|-----|

| 2.1  | A comparison of Xeon E7-8890 v4 CPU and NVidia GP100 GPU features[76].                                            | 49  |

| 2.2  | Most common intermediate languages leveraged by GPU computing platforms.                                          | 51  |

| 3.1  | Theoretical GPU specifications and the respective flops/byte ratios                                               | 66  |

| 4.1  | The NVidia GPU profiler metrics required for the derivation of kernel parameters.                                 | 75  |

| 4.2  | The set of required <i>kernel parameters</i> in the proposed performance model.                                   | 76  |

| 4.3  | The set of GPU parameters used in the performance model                                                           | 78  |

| 4.4  | The profiling metrics gathered for the red/black computation on a GTX-480 GPU                                     | 81  |

| 4.5  | The extracted kernel parameters of the red/black SOR kernel                                                       | 82  |

| 4.6  | Measured GPU parameters for the NVidia GTX-660                                                                    | 82  |

| 4.7  | The GPU cost weights as measured in the model for the NVidia GTX-660 .                                            | 83  |

| 4.8  | Utilization metric values of the red/black SOR kernel, on the GTX-660                                             | 84  |

| 4.9  | The profiling metrics gathered for the SGEMM computation on a GTX-480 GPU                                         | 85  |

| 4.10 | The extracted kernel parameters of the SGEMM kernel                                                               | 86  |

| 4.11 | Utilization metric values of the SGEMM kernel, on the GTX-660                                                     | 88  |

| 5.1  | List of the CUDA GPUs used in the experiments                                                                     | 91  |

| 5.2  | GPU parameters as measured with micro-benchmarks                                                                  | 91  |

| 5.3  | The GPU cost weights as measured and used in the model                                                            | 92  |

| 5.4  | CUDA benchmark list of the Rodinia benchmark suite                                                                | 100 |

| 5.5  | List of selected kernels of the Rodinia suite used on the experiments                                             | 102 |

| 5.6  | The relative instruction execution costs and the instruction efficiency on all GPUs for the red/black SOR kernel. | 103 |

| 5.7  | The derivation of performance estimation on all GPUs for the red/black SOR kernel ( $O_{krn}$ =0.3)               | 103 |

33 E. Konstantinidis

| 5.8  | The highest rated utilization metric values of the red/black SOR kernel, on all GPUs                                                                                    | 104 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.9  | Prediction results on all GPUs for the red/black SOR stencil computation .                                                                                              | 105 |

| 5.10 | The profiling metrics gathered for the LMSOR kernel on a GTX-480 GPU. All metrics are the accumulated values collected in 4 iterations for the red element calculation. | 106 |

| 5.11 | The $\it kernel\ parameters$ and the operational intensity of the LMSOR $\it kernel$                                                                                    | 106 |

| 5.12 | Prediction results on all GPUs for the LMSOR kernel stencil computation .                                                                                               | 107 |

| 5.13 | The highest rated utilization metric values of the LMSOR SOR kernel                                                                                                     | 107 |

| 5.14 | Prediction results for the matrix multiplication kernel                                                                                                                 | 108 |

| 5.15 | Top GPU utilization metrics on matrix multiplication kernel profiling                                                                                                   | 108 |

| 5.16 | Collected <i>kernel parameters</i> and the operational intensity of the selected Rodinia kernels                                                                        | 112 |

| 5.17 | The highest utilization metrics for the Rodinia kernels and the corresponding utilization rating.                                                                       | 115 |

| 5.18 | Throughput of native integer arithmetic instructions[73] (operations per clock cycle per multiprocessor)                                                                | 120 |

| 6.1  | Theoretical specifications of the R9-Nano GPU                                                                                                                           | 125 |

| 6.2  | Measured <i>GPU parameters</i> for R9-Nano                                                                                                                              | 125 |

| 6.3  | The GPU cost weights as measured for the R9-Nano                                                                                                                        | 126 |

| 6.4  | SGEMM kernel parameters using a 16x16 thread block size                                                                                                                 | 126 |

| 6.5  | Prediction results on the R9-Nano GPU for the red/black SOR, SGEMM and lvmd-krn kernels                                                                                 | 127 |

| B.1  | The GPU on-chip memory types as provided by modern CUDA GPUs                                                                                                            | 143 |

#### **PREFACE**

I'm in the delightful position to author the finishing lines in this manuscript known as *PhD thesis*. The feelings are mixed. It's a great relief that after all the enormous and long effort spent, this work is finally reaching to its completion. On the other hand, there is a sense of emotion as this journey is approaching to the end. I would think of finishing of this thesis to be as one of the most important milestones in my whole life. I thank everyone cordially who helped me reaching this goal.

# 1. INTRODUCTION

Traditionally, the GPU (Graphics Processor Unit) has been used to accelerate the generation of stunning 3D image representations for 3D games and 3D professional graphics applications. Complex 3D image rendering requires a huge number of compute operations to be performed in order to create realistic images. In addition, the 3D rendering process is an embarrassingly parallel problem and this fact led to the adoption of parallel computation paradigm on GPUs in a much quicker pace and to a vastly larger extent than the traditional CPUs did. As GPUs steadily evolved to be more and more powerful rendering engines in recent years they surpassed the compute capabilities of CPUs. Thus, researchers began experimenting on general purpose computation on GPUs. Nowadays, they are considered to be alternative compute accelerators and have found their place in the HPC (High Performance Computing) sector which provides the necessary parallel compute workloads for GPU consumption. However, GPU programming tends to be more cumbersome and tedious compared to the CPU programming posing performance bottlenecks. Moreover, experience has shown that performance is much more sensitive to the proper use of GPU resources and thus it is more difficult to predict.

# 1.1 General purpose computation on GPUs

Historically, a graphics accelerator which afterwards evolved to a GPU was designed and applied for graphics rendering purposes only. The processing units, traditionally called shaders, were initially fixed-functioned. The first programmable shaders were introduced in 2001[56]. This functionality triggered the development of shading programming languages. We note the Cg programming language[58], the OpenGL shading language (also known as GLSL)[38] and Microsoft's DirectX High-Level Shader Language (i.e. HLSL). The emergence of these languages enabled the programmability of the processing units within the GPU not only for graphics rendering but for solving general purpose problems which could naturally map to the graphics pipeline. In this way the GPGPU (General Purpose on Graphics Processing Unit) term was coined[50].

Research regarding the possibilities of GPGPU pushed the development of special programming languages for GPUs with a focus on GPGPU, e.g. Brook[16]. However, the actual breakthrough was set when the NVidia's Tesla architecture[55] as well as pure GPU compute programming languages were introduced. Tesla architecture employed unified shaders which no longer were designed for a particular purpose but they could either be used for vertex, fragment processing or computation. The first GPU adopting Tesla architecture was the GeForce 8800 GPU in 2006, which featured 128 streaming processors with a theoretical peak of 518 single precision GFLOPS performance. Pure GPU computation languages emerged, e.g. CUDA[73] and OpenCL[39]. These languages enabled the programmability of GPU for general purpose computation without involving the graphics pipeline. In this regard, a great interest from the research community was spawned in the adoption of GPUs for general algorithm acceleration.

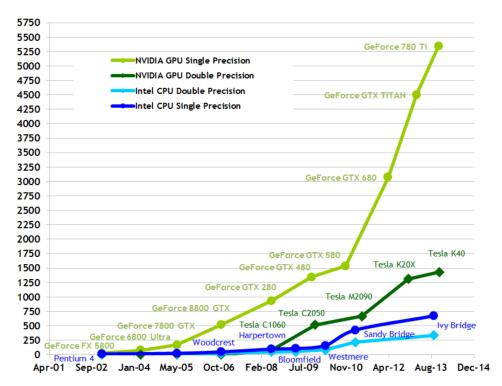

Figure 1.1: A comparison of CPU and GPU floating point performance evolution [73].

The GPU performance has vastly improved over the last years (figure 1.1). In 2010 the highest performing NVidia GPU (GTX-580) featured a theoretical peak of 1,581 GFLOPS single precision, whereas in 2015 the highest performing GPU of the same vendor (Titan-X) was rated at 6,144 GFLOPS, which is a 3.9x improvement. At the time of writing of this paper the highest performing GPU to date was the NVidia GP100. According to [76] the features of this GPU compared to the professional GPUs of the 2 previous generations in table 1.1. Half precision has been pushed mostly with the artificial intelligence applications in mind, e.g. deep learning methods. This performance plus the accompanying energy efficiency of the GPU are the greatest incentives for the adoption of the GPU for general purpose computation.

CUDA programming environment[73] has been developed by NVidia and it works exclusively on NVidia hardware. It is supported on all three major operating systems and it is the most established GPU computing programming environment to date. It is well supported by the vendor and most research on GPUs has been conducted by leveraging this particular API (Application Programming Interface). The most significant drawback of CUDA is the restricted hardware support, which limits users to the particular vendor's hardware.

The OpenCL is an open standard that targets multiple vendors and it is supported by the Khronos group consortium. Programming style is similar to CUDA though more verbose. However, it's not established to the same extent as CUDA though it receives steadily more attention. One of the primary advantages of OpenCL is the wide type of hardware support as it is not limited to GPUs but it can be applied on CPUs, DSPs, or FPGAs, as well.

Table 1.1: Tesla P100 (GP100) GPU compared to prior GPU generations[76].

| Tesla Products           | Tesla K40            | Tesla M40           | Tesla P100            |

|--------------------------|----------------------|---------------------|-----------------------|

| GPU                      | GK110 (Kepler)       | GM200 (Maxwell)     | GP100 (Pascal)        |

| SMs                      | 15                   | 24                  | 56                    |

| TPCs                     | 15                   | 24                  | 28                    |

| FP32 CUDA cores / SM     | 192                  | 128                 | 64                    |

| FP32 CUDA cores / GPU    | 2,880                | 3,072               | 3,584                 |

| FP64 CUDA cores / SM     | 64                   | 4                   | 32                    |

| FP64 CUDA cores / GPU    | 960                  | 96                  | 1,792                 |

| Base clock               | 745 MHz              | 948 MHz             | 1,328 MHz             |

| GPU boost clock          | 810/875 MHz          | 1,114 MHz           | 1,480 MHz             |

| Peak FP32 GFLOP          | 5,040                | 6,840               | 10,600                |

| Peak FP64 GFLOP          | 1,680                | 210                 | 5,300                 |

| Texture units            | 240                  | 192                 | 224                   |

| Memory interface         | 384-bit GDDR5        | 384-bit GDDR5       | 4,096-bit HBM2        |

| Memory size              | Up to 12 GB          | Up to 24 GB         | 16 GB                 |

| L2 cache size            | 1,536 KB             | 3,072 KB            | 4,096 KB              |

| Register file size / SM  | 256 KB               | 256 KB              | 256 KB                |

| Register file size / GPU | 3,840 KB             | 6,144 KB            | 14,336 KB             |

| TDP                      | 235 Watts            | 250 Watts           | 300 Watts             |

| Transistors              | 7.1 ·10 <sup>9</sup> | 8 ·10 <sup>9</sup>  | 15.3 ⋅10 <sup>9</sup> |

| GPU die size             | 551 mm <sup>2</sup>  | 601 mm <sup>2</sup> | 610 mm <sup>2</sup>   |

| Manufacturing process    | 28-nm                | 28-nm               | 16-nm FinFET          |

|                          |                      |                     |                       |

Currently, GPUs have mostly found a place on the HPC sector as the interest of the scientific community is significant. This interest stems from the vast compute requirements of scientific applications which tend to require enormous amounts of computations with inherent parallelism, which pose the GPUs suitable for such kind of algorithms. Mainstream use of GPU compute is still limited mostly to video and image processing, or brute force workloads (e.g. cryptocurrency mining, cryptography). Due to the architectural differences of CPUs and GPUs, performance optimization decisions have to be applied in a different manner in order to attain high performance. Since, the goal of GPU computing paradigm is reaching higher performance levels the proper use of optimization techniques is mandatory.

# 1.2 The performance analysis challenge

As already noted, the real focus of GPU computing is about performance so it would be of great significance to be able to predict performance of GPU applications on a wide range of hardware. Performance modeling information is particularly important that can be exploited for either the consideration of a hardware upgrade or even on choosing important optimization decisions. Additionally, the maximum performance that could be achieved is very important as this could aid in searching for any worthwhile optimizations. However, performance impact of migrating to a GPU accelerator or moving from one type of GPU to another can be a puzzling process to predict. Performance bottlenecks can be different due to architectural changes or variations on the balance of processor resources between different types of processors.

CPUs do not require a vast amount of parallelism in order to yield decent performance. They utilize large hierarchies of cache memories that are able to alleviate the large access latencies of main memory. In addition, they employ advanced techniques in order to maximize the single threaded performance, e.g. aggressive speculative execution, register renaming, result value forwarding, etc. All these features eliminate pipeline and memory bottlenecks, leading to more predictable execution results.

On the other hand, GPUs are significantly more performance sensitive to supplied parallelism, resource usage and memory access patterns. They are considered as massively parallel compute devices as they practically need many thousands of active threads in order to keep them occupied. This fact poses large problems with abundant parallelism as a requirement. The GPUs feature much smaller cache memories which in conjunction with the large amount of active threads allows only limited use, mostly for exploiting the spatial locality between sibling threads. The missing of large cache hierarchies forces programmers to effectively use memory. However, GPUs require regular memory accesses with specific requirements in order to apply coalescing, which is a mandatory requirement for efficient memory accessing. All reasons above induce potential bottlenecks for GPU performance. Practical experience has proven that GPU performance is sensitive to design decisions and fine tuning. In general, GPUs tend to be less tolerant to naive programming practices in regard to performance. Moreover, though GPUs provide great compute performance, this can only be achieved on problems that match their characteristics.

It should be added that GPU ISAs (Instruction Set Architectures) are not fixed, which can also affect the performance estimation process between different ISA GPUs. Modern CPUs tend to be compatible on a specific ISA mostly due to the necessity of software compatibility. The large existing software install base locks the CPU vendors on particular ISAs, though they implement completely different micro-architectures within their products. On GPUs such restriction does not exist as the software install base typically does not directly embed machine code but regularly binary code in other intermediate language forms. That said, typically GPUs execute different machine codes for the same kernels as they are just-in-time compiled for the respective ISA. Such differentiations can potentially change the used instruction mix significantly and subsequently cause performance variations.

For all the reasons above this thesis is focused on proposing a performance model that provides the necessary abstraction in order to be applicable on a wide range hardware, yet it provides decent prediction accuracy, is quick and straightforward to apply and can be fully automated based on *black-box* kernel inspection. In addition, this model was developed as roofline based and as such it is able to indicate an upper bound on performance, which can be fairly useful to the programmer as a guidance, providing performance feedback for further optimizations. The ultimate goal was to provide a tool that runs automatically the whole performance prediction process by utilizing an existing GPU program and producing the final results without the user's intervention.

#### 1.3 Structure of thesis

This thesis is structured as follows. In the next chapter background information and a summary of related work is provided along with their connection to this thesis. The background information includes a short historical overview of the GPU as it evolved from fixed function graphics acceleration hardware to the point being considered as a special general purpose computation coprocessor. The various programming environments developed to date are also described. Related work includes relevant research work conducted in the field of performance prediction models for GPUs, both analytical and simulations.

The third chapter develops a discussion on the foundation of the proposed model, i.e. the roofline model, as well as, an introduction to the *quadrant-split* visual model. The roofline model is a widely accepted tool for performance analysis and the proposed model is based on the same concept. An alternative visual representation proposed is the *quadrant-split* model giving additional insight on multi-processor performance analysis. Furthermore, the roofline model was experimentally approximated by using an artificial micro-benchmark dubbed *mixbench*.

The fourth chapter is essentially the main contribution of this work. It provides a detailed description of all steps required by the proposed method along with an analysis of the proposed performance model. The description is additionally complemented with two applied case studies and validation with real performance measurement.

The fifth chapter is an extended experimental evaluation of the proposed performance method. Experimentation on a wide range of real world kernels is provided and a further analysis on special cases where the prediction was not considered adequately accurate. Additionally, the kernel performance of *mixbench* micro-benchmark was also validated by the exact same methodology.

The sixth chapter exhibits the potential of the proposed methodology in cross-vendor GPU environments (AMD GPUs) and a summary of the assumptions made in the performance model along with known limitations that have been identified.

The last chapter concludes by summarizing on the proposed performance model and initiating a discussion on possible future improvements. The latter includes potential improvements on the model itself, on the hardware support or on software assisted approaches.

A GPU performance estimation model based on micro-benchmarks and black-box kernel profiling

# 2. BACKGROUND AND RELATED WORK

# 2.1 The graphics accelerator as a Graphics Processing Unit (GPU)

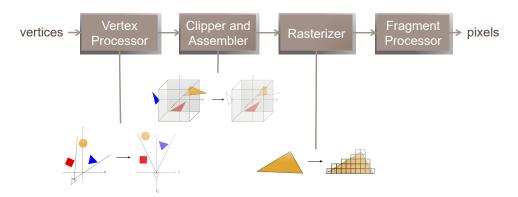

Initially, the graphics accelerator had emerged as an ASIC (Application-Specific Integrated Circuit) that performed fixed functions involved in 3D graphics rendering. In fact, well before 3D hardware acceleration was established there had been graphics acceleration hardware that focused on plain GUI 2D raster operations. The purpose of 3D hardware acceleration was the offloading of these tasks from the CPU to another device with the additional speed-up benefit. A simplified view of the graphics pipeline is illustrated in figure 2.1. Graphics accelerators gradually evolved by taking on the whole graphics pipeline.

Figure 2.1: The graphics pipeline.

The term GPU (Graphics Processing Unit) was first coined by NVidia for the purpose of marketing of the newly launched GeForce 256 accelerator in 1999. According to the original definition a GPU was presented as a "single-chip processor with integrated transform, lighting, triangle setup/clipping, and rendering engines that is capable of processing a minimum of 10 million polygons per second". This term has been established for all modern graphics accelerators ever since.

Initially, no programming could be applied on the graphics pipeline as all functions of the GPU were fixed. However, as the accelerators evolved they allowed programmers do write small custom programs that could be applied to the data processed within the pipeline. These programs are called *programmable shaders*. The first GPU that offered this capability was the GeForce 3 (NV20). It was introduced in 2001 and added programmable pixel and vertex shaders. Thus, programmers could write programmable shaders involved in either the vertex processor stage or the fragment processor stage. This capability allowed the implementation of custom visual effects in graphics applications. Furthermore, it was the feature that enabled the capability of using GPUs for a broader set of problems beyond graphics.

<sup>1</sup>http://www.nvidia.com/object/gpu.html

# 2.2 The GPU as a general purpose processor

CPUs have traditionally been the heart of the computer as it is the primary component that manages and executes the program's instructions. All programs consist of a series of machine code instructions and each instruction describes a tiny step in the progress of computation. The solution of computational problems typically require a vast amount of instructions to be executed in order to reach the final output of a program. Therefore one of the primary factors in the speed of execution of a program is the speed of execution of instructions as permitted by the central processor, i.e. the CPU. Especially the HPC sector employs algorithms that require enormous amounts of computations to be performed. Therefore, the effectiveness of CPUs in the execution of computation is of primary focus in the particular industry.

During last decades the evolution of CPU has been mostly driven by the stable and fastpaced evolution of process technologies employed by the semi-conductor industry. This allowed the longevity of the so called Moore's law[62] which had been first observed by Gordon Moore, one of the founders of Intel corporation. This law was an observation which described a doubling every year in the number of components per integrated circuit and latter it was revised to doubling every two years. The increasing trend in the number of transistors on the CPU combined with increasing clock frequencies allowed the exponential scaling in the performance of CPUs which lasted for many decades. This improvement had been enjoyed by the software industry without applying any changes to the existing software. However, that era has reached to end due to the power wall[79] that seized the long term increasing of CPU frequency clock speeds and the diminishing improvements in exploiting the instruction level parallelism in existing software. Then, CPU vendors turned to multi-core designs that allowed the inclusion of multiple processors within the same chip silicon. IBM Power 4 was the first CPU to employ a multi-core design on year 2001. However, this move forced software designers to change their sequential approach in program development to parallel in order to take advantage of this new trend. An expressive quote used to present this new reality was 'The free lunch is over'[87, 88].

On the other hand, the graphics accelerator employed a parallel design since the early beginnings. The parallel nature of graphics processing allows a huge number of operations to be performed in parallel and thus, GPU vendors adopted widely parallel processing designs on GPUs. For instance, even the GeForce 256, introduced in 1999, employed quad pixel pipelines. Thereafter, the additional transistors per fabrication node generation led the GPU performance to rapidly increase.

Initially however, the GPU didn't offer the programmability required to exploit this compute capacity for anything more than graphics rendering. Later on the programmable shader capability was introduced in 2001, as already reported, but the hardware units (shader units) that were designed to execute shader code were still specialized to the particular unit type. This meant that there were different physical units on the GPU at the time for each pipeline stage, i.e. vertex shader units and pixel/fragment shader units, each built for the execution of particular shader type codes. This led to imbalances in execution loads inducing negative performance impact.

# 2.2.1 Unified shaders through the introduction of the Tesla GPU architecture

The real breakthrough in the GPU computing field was set when the first desktop GPU with unified shaders was released. That was the NVidia GeForce 8800, which was introduced in 2006 and employed the Tesla GPU architecture[55]. It enabled flexible programmability through CUDA[73], a native GPU compute programming environment.

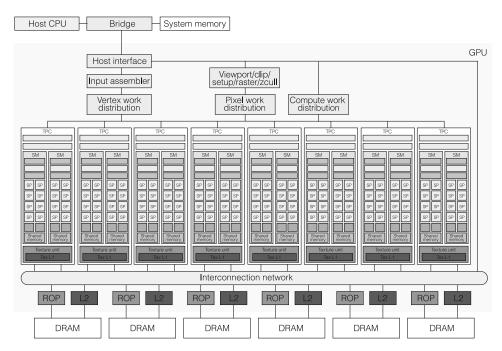

Some key information of the Tesla architecture[55] (figure 2.2):

- 128 streaming-processor (SP) cores organized as 16 streaming multiprocessors (SMs) in eight independent processing units called texture/processor clusters (TPCs)

- The SM manages and executes up to 768 concurrent threads in hardware with zero scheduling overhead.

- The SM is a unified graphics and computing multiprocessor that executes vertex, geometry, and pixel-fragment shader programs and parallel computing programs.

- The SM consists of eight streaming processor (SP) cores, two special function units (SFUs), a multithreaded instruction fetch and issue unit (MT Issue), an instruction cache, a read-only constant cache, and a 16-Kbyte read/write shared memory.

- The GeForce 8800 Ultra clocks the SPs and SFU units at 1.5 GHz, for a peak of 36 GFLOPS per SM. To optimize power and area efficiency, some SM non-data-path units operate at half the SP clock rate.

- To efficiently execute hundreds of threads in parallel while running several different programs, the SM is hardware multithreaded. It manages and executes up to 768 concurrent threads in hardware with zero scheduling overhead.

In order to support a large number of concurrent hardware threads, the SM sustains a large set or registers (8,192 total 32bit registers per SM) in order to be able to perform zero-cost switching whenever required. This allows supporting very fine-grained parallelism in an efficient manner. The SM features a flexible type of SIMD (Single-Instruction, Multiple-Data) architecture which designers call single-instruction, multiple-thread (SIMT). The SM's instruction unit creates, manages, schedules, and executes threads in groups of 32 parallel threads called warps. In essence, each warp maps to 32-lane SIMD operations and is able to follow an independent code path. During the execution, individual threads can be inactive due to independent branching. The SM maps the warp threads to the SP cores, and each thread executes independently with its own register state. The SM executes instructions at full efficiency and performance when all 32 threads of a warp take the same execution path. In case the threads within a warp diverge due to a data dependent conditional branch, the warp serially executes each branch path taken, disabling threads that are not on that path. After the execution of all taken paths complete, the threads re-converge on a common execution path. Different warps can freely follow independent execution paths without incurring negative performance impact.

Figure 2.2: The NVidia Tesla GPU architecture[55] block diagram.

SIMT execution fashion is similar to SIMD. The difference is that SIMT applies instructions to multiple threads instead of multiple data lanes. In essence, the SIMD architecture and its vector width is not directly exposed the GPU ISA architecture. The GPU architecture instructions are scalar but they are executed by multiple threads in lockstep. It is a duty of the hardware to manage the SIMD execution. For that reason, this architecture allows programmers to ignore the SIMT execution implications and write parallel code in a MIMD fashion, by letting the hardware execute coordinated threads in a SIMD fashion. However, they can optimize performance by minimizing the circumstances where thread warp execution diverges. In contrast, typical SIMD vector execution requires from the programmer to explicitly handle vector operations and manage divergence, including vector loads and stores from memory.

The SM warp scheduler operates at half of the SP's clock rate. At each cycle, it selects one warp which is ready for execution to issue an instruction. The selected warp executes the issued instruction over four SP cycles. The warp scheduler issues instructions to the SPs and SFU units on alternate cycles, potentially keeping both fully occupied. These specifications enable the GeForce 8800 Ultra GPU a theoretical peak performance of  $36 \times 16 = 576$  GFLOPS.

The supported ISA includes floating point, integer, flow control, memory load/store and texture operations. The integer and floating point operations include add, multiply, multiply-add, minimum, maximum, compare, transcendental, bitwise and conversions operations. Memory access supports read/write accesses on the three distinct address spaces, i.e. local memory, shared memory and global memory. In addition there is a constant memory address space offering read only access capability and a texture unit which allows cached read-only accesses in addition to sample bilinear filtering. Multiple global memory

accesses can be coalesced, as long as they are aligned and reside on the same memory segments, one fact that can optimize use of memory bandwidth.