# ΕΘΝΙΚΟ ΚΑΙ ΚΑΠΟΔΙΣΤΡΙΑΚΟ ΠΑΝΕΠΙΣΤΗΜΙΟ ΑΘΗΝΩΝ

## ΣΧΟΛΗ ΘΕΤΙΚΩΝ ΕΠΙΣΤΗΜΩΝ ΤΜΗΜΑ ΠΛΗΡΟΦΟΡΙΚΗΣ ΚΑΙ ΤΗΛΕΠΙΚΟΙΝΩΝΙΩΝ

ΠΡΟΓΡΑΜΜΑ ΜΕΤΑΠΤΥΧΙΑΚΩΝ ΣΠΟΥΔΩΝ

ΔΙΠΛΩΜΑΤΙΚΗ ΕΡΓΑΣΙΑ

# FPGA Implementation of encoders for CCSDS Low-Density Parity-Check (LDPC) codes.

Δημήτριος Κ. Θεοδωρόπουλος

Επιβλέπων:

Αντώνιος Πασχάλης, Καθηγητής

AOHNA

ΣΕΠΤΕΜΒΡΙΟΣ 2015

## ΔΙΠΛΩΜΑΤΙΚΗ ΕΡΓΑΣΙΑ

FPGA Implementation of encoders for CCSDS Low-Density Parity-Check (LDPC) codes

# Δημήτριος Κ. Θεοδωρόπουλος Α.Μ.: Μ1321

ΕΠΙΒΛΕΠΩΝ: Αντώνιος Πασχάλης, Καθηγητής

ΕΞΕΤΑΣΤΙΚΗ ΕΠΙΤΡΟΠΗ Α. Αραπογιάννη, Δ. Γκιζόπουλος, Καθηγητές

Σεπτέμβριος 2015

## ΠΕΡΙΛΗΨΗ

Η παρούσα διπλωματική εργασία παρουσιάζει την υλοποίηση με τεχνολογία FPGA αλγορίθμων κωδικοποίησης καναλιού που έχουν προτυποποιηθεί από τον οργανισμό CCSDS για χρήση σε διαστημικές επικοινωνίες.

Ο CCSDS προτείνει δύο κατηγορίες κωδίκων για εφαρμογές τηλεμετρίας: μία για επικοινωνίες στο εγγύς (near-earth) διάστημα (π.χ. δορυφορικές επικοινωνίες) και άλλη μια για επικοινωνίες βαθέος διαστήματος (deep-space), με χαρακτηριστικά η κάθε μία βελτιστοποιημένα ως προς το πεδίο εφαρμογής τους. Και στις δύο περιπτώσεις, οι κώδικες είναι γραμμικοί μπλοκ κώδικες με μεγάλο μέγεθος μπλοκ και πίνακα ισοτιμίας με χαμηλή πυκνότητα (LDPC).

Στην περίπτωση των κωδίκων near-erth, η προδιαγραφή αφορά σε ένα κώδικα LDPC (8160,7136) με ρυθμό 7/8, βασισμένο σε ευκλείδεια γεωμετρία, ενώ για τους κώδικες deep-space προδιαγράφονται 9 κώδικες που προκύπτουν από 3 συνδυασμούς μεγέθους μπλοκ (1024,4096, 16384 bits) με 3 ρυθμούς (½, 2/3, 4/5). Οι κώδικες αυτοί μοιράζονται κοινή μαθηματική περιγραφή, γεγονός που καθιστά εφικτή την περιγραφή με τη γλώσσα VHDL ενός κοινού κωδικοποιητή για όλους.

Στην παρούσα εργασία, γίνεται εκμετάλλευση της δομής των πινάκων-γεννητόρων των κωδίκων deep-space προκειμένου να μεγιστοποιηθεί η απόδοση. Προκύπτουν δύο ειδών παραλληλίες στη δομή των εν λόγω πινάκων, η ταυτόχρονη αξιοποίηση των οποίων οδηγεί σε βελτίωση των επιδόσεων με ελαχιστοποίηση των καταναλισκόμενων πόρων. Το τίμημα βέβαια της βελτιστοποίησης αυτής είναι κάποια αύξηση στην απόκριση (latency) ανάλογα με τις επιλογές παραλληλίας,που ωστόσο αντιμετωπίζεται με την λειτουργία του διαύλου της διεπαφής εξόδου με διοχέτευση (pipelining) Η περιγραφή στη γλώσσα VHDL είναι γενική και επιτρέπει την εύκολη παραμετροποίηση των βασικών χαρακτηριστικών του κώδικα (μέγεθος μπλοκ, ρυθμός), των βαθμών παραλληλίας για κάθε μια από τις δύο κατηγορίες και του εύρους των διαύλων εισόδου-εξόδου.

Αντίστοιχα στην περίπτωση του κώδικα near-earth, περιγράφεται μια αποδοτική μέθοδος στη σχεδίαση των επί μέρους οντοτήτων του κυκλώματος που βελτιστοποιεί την αξιοποίηση των πόρων, σε σχέση με γνωστές λύσεις. Ο κωδικοποιητής σε αυτή την περίπτωση είναι σχεδιασμένος για διαύλους εισόδου-εξόδου μεγέθους 16 bit.

Και στις δύο περιπτώσεις η είσοδος και έξοδος δεδομένων γίνεται από δύο αντίστοιχες διεπαφές συμβατές με το πρωτόκολλο AMBA AXI4-Stream, γεγονός που επιτρέπει την εύκολη διασύνδεσή τους σε μια σχεδίαση SoC ή μια διεπαφή FIFO. Η λειτουργία των κωδικοποιητών είναι βέλτιστη από την άποψη ότι παράγουν μια (σχεδόν) αδιάκοπη ροή δεδομένων στη διεπαφή εξόδου-χωρίς να είναι απαραίτητοι αδρανείς κύκλοι.

Η περιγραφή των κωδικοποιητών σε VHDL επαληθεύεται ως προς την ορθή της σχεδίαση με προσομοιώσεις για όλες τις υποστηριζόμενες περιπτώσεις, όπου απαιτείται η μέγιστη κάλυψη κώδικα (code coverage). Τέλος, το σχέδιο επαλήθευσης περιλαμβάνει την επίδειξη λειτουργίας σε ένα ενσωματωμένο σύστημα υλοποιημένο στην κάρτα XUPV505-LX110T, όπου καταγράφονται και οι πραγματικές επιδόσεις του συστήματος, όπου βρίσκονται στην περιοχή των μερικών Gbps. Η παρούσα υλοποίηση προκύπτει ότι είναι η ταχύτερη για την συγκεκριμένη οικογένεια LDPC κωδικών.

ΘΕΜΑΤΙΚΗ ΠΕΡΙΟΧΗ: Ψηφιακή Σχεδίαση

**ΛΕΞΕΙΣ ΚΛΕΙΔΙΑ**: LDPC, CCSDS, FPGA, near-earth, deep-space

## ABSTRACT

The FPGA implementation of LDPC encoders for channel codes standardized by CCSDS for space communication applications is described in this work.

CCSDS suggests two classes of channel codes for telemetry applications: one for nearearth and another for deep-space communications, each one optimized for the demands of the specific field. In both cases, the specification concerns linear block codes with large block size and sparse generator matrices.

Regarding near-earth codes, the specification describes a Euclidean geometry based (8160,7136) LDPC code at rate 7/8, while in the deep-space case, 9 codes are defined which are the combination of thee block lengths (1024,4096,16384 bits) with three rates ( $\frac{1}{2}$ , 2/3, 4/5), sharing a common mathematical description. This fact enables the VHDL description of a common encoder for all of them.

The generator matrices of these codes possess considerable structure which facilitates implementation. Concerning deep-space codes generator matrices, parallelism extends over two dimensions, which can be exploited concurrently to optimize timing performance and at the same time minimize resource utilization. The price to be paid however is increased latency, which can be mitigated by the pipelined operation of the output interface. VHDL description of the encoder is generic, allowing the easy modification of the code parameters (block size, rate), the amount of parallelism in each dimension and the input-output bus width, leading to different performance-latency balances.

Also in the case of the near-earth code, an efficient design of the encoder's sub-entities is described, leading to resources utilization optimizations, compared to existing implementations. The encoder in this case is designed for 16-bit input-output bus.

All described encoders input-output is performed on AMBA AXI-4 Stream compliant interfaces, facilitating their integration in an embedded system's design and communication with standard FIFO interfaces. The encoders' operation is optimal in that an uninterrupted flow of data is provided on the output interface, without idle cycles. The only exception is the near-earth encoder for which just one idle cycle every 513 is inserted.

The correctness of the VHDL description's is validated by functional simulation for all supported cases, where 100% code coverage is demanded. The verification plan includes also the demonstration of real-time operation of the encoders in an integrated system implemented on a XUPV505-LX110T development board, where the actual performance of the encoders is recorded and lies in the multi-Gbps range. Finally, the proposed encoders are shown to be the fastest stream-oriented implementations for the specified family of LDPC codes, with minimal resource utilization.

SUBJECT AREA: Digital Design

**KEYWORDS**: LDPC, CCSDS, FPGA, near-earth, deep-space

# ACKNOWLEDGEMENTS

I would like to express my gratitude to my supervising professor, Dr. A. Paschalis for the advice and patience exerted and also to his associates, A. Tsigkanos, N. Kranitis and G. Theodorou for their invaluable advice and assistance.

# ΠΕΡΙΕΧΟΜΕΝΑ

| 1. INTRODUCTION TO LDPC CODES                    |    |

|--------------------------------------------------|----|

| 1.1 Noisy Channel Coding Introduction            | 12 |

| 1.2 Low Density Parity Check codes               |    |

| 1.2.1 Linear Block Codes                         | 14 |

| 1.2.2 LDPC description                           | 14 |

| 1.2.3 LDPC features                              |    |

| 1.2.4 LDPC performance                           |    |

| 1.3 Encoder architectures for Quasi-Cyclic codes |    |

| 1.3.1 Straightforward implementation             |    |

| 1.3.2 RCE implementation                         |    |

| 1.3.3 RU encoder                                 |    |

| 1.3.4 Iterative encoder                          |    |

| 2. CCSDS STANDARDS                               | 24 |

| 2.1 AR4JA LDPC code family                       | 25 |

| 2.2 C2 code for near-earth applications          |    |

| 2.3 Frame Synchronization and CADU structure     | 28 |

| 2.4 Randomization                                | 29 |

| 3. ENCODER DESIGN                                |    |

| 3.1 Encoder Architecture selection               | 31 |

| 3.1.1 RCE encoder resources                      |    |

| 3.1.2 Iterative encoder resources                |    |

| 3.1.3 Parallel RCE implementation                |    |

| 3.2 Components Description                       | 35 |

| 3.2.1 RANDOMIZER unit                            |    |

| 3.2.2 Control and Buffer Unit: the general case  |    |

| 3.2.3 Control and Buffer Unit: $L_a=1$           | 40 |

| 3.2.4 Control and Buffer Unit: High latency case | 41 |

| 3.2.5 Control and Buffer Unit: Very small Latency            | 43 |

|--------------------------------------------------------------|----|

| 3.2.6 Control and Buffer Unit: no HALT state                 | 43 |

| 3.2.7 Control and Buffer Unit: C2 code                       | 44 |

| 3.2.8 Function generators                                    | 46 |

| 4. IMPLEMENTATION                                            |    |

| 4.1 Code design and parametrization                          | 47 |

| 4.2 Core synthesis                                           |    |

| 4.3 Performance                                              |    |

| 5. VERIFICATION AND VALIDATION                               | 50 |

| 5.1 General                                                  |    |

| 5.2 Functional simulation                                    |    |

| 5.2.1 Testbench description                                  | 51 |

| 5.2.2 Simulation results                                     | 52 |

| 5.3 Implementation validation                                |    |

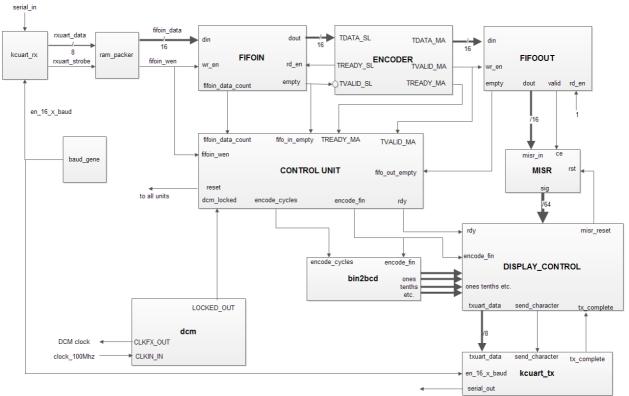

| 5.3.1 Embedded system description: UART input                |    |

| 5.3.2 Results with UART input                                |    |

| 5.3.3 Embedded system description: LFSR input                | 55 |

| 5.3.4 Results with LFSR input                                | 56 |

| 6. RESULTS                                                   |    |

| 6.1 Comparison to other implementations: commercial products | 57 |

| 6.2 Comparison to other implementations: literature          | 58 |

| 7. CONCLUSIONS                                               |    |

| ACRONYMS-ABBREVIATED TERMS                                   |    |

| REFERENCES                                                   |    |

# **FIGURES INDEX**

| Figure 1: A simplified binary noisy communication system                                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2: Capacity limits for the AWGN channel over a selection of data rates13                                                                                                    |

| Figure 3: Tanner graph for the (7,4) Hamming code. Bold lines mark a cycle1                                                                                                        |

| Figure 4: BER performance for the rate 4/5 k=1024 CCSDS LDPC code16                                                                                                                |

| Figure 5: General form of the BER curve for most LDPC code                                                                                                                         |

| Figure 6: Generator matrix of AR4JA LDPC code with k=1024, rate 4/517                                                                                                              |

| Figure 7: A straightforward encoder implementation for a QC LDPC code                                                                                                              |

| Figure 8: RCE encoder19                                                                                                                                                            |

| Figure 9: The parity check matrix transformed into lower triangular form                                                                                                           |

| Figure 10: From top to bottom: The parity check matrix of rate $\frac{1}{2}$ k=1024 CCSDS LDPC code, the same matrix transformed in lower triangular form and the inverse matrix20 |

| Figure 11: Multiplication of a sparse matrix with a vector and the corresponding hardware2 <sup>2</sup>                                                                            |

| Figure 12: H2-1 matrices for various LDPC codes22                                                                                                                                  |

| Figure 13: Submatrices W of generator matrices for codes of k=102427                                                                                                               |

| Figure 14: Scatter chart of the parity-check matrix of C2 LDPC code                                                                                                                |

| Figure 15: A possible implementation of a CCSDS pseudo-random sequence                                                                                                             |

| Figure 16: Encoder's top level diagram30                                                                                                                                           |

| Figure 17: Timing of data on encoder's interfaces                                                                                                                                  |

| Figure 18: Iterative calculation of parity bits                                                                                                                                    |

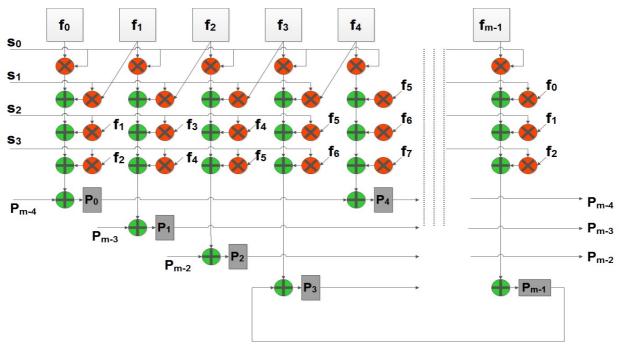

| Figure 19: A RCE module for parallel processing of Lm=4 bits of mxm circulants34                                                                                                   |

| Figure 20: Simplified view of a parallel RCE with both sources of parallelism: La and Lm                                                                                           |

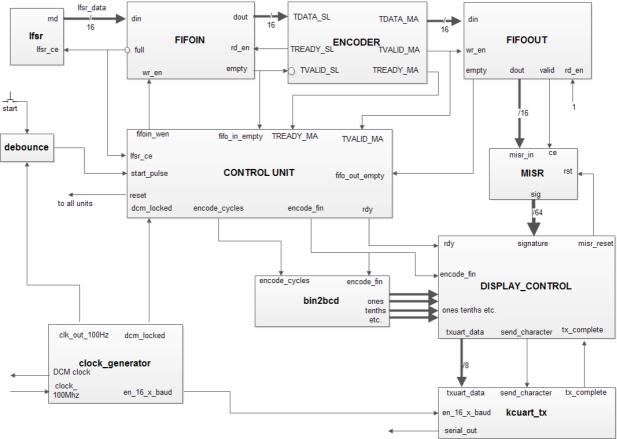

| Figure 21: Encoder Block Diagram                                                                                                                                                   |

|                                                                                                                                                                                    |

| Figure 23: Timing example of the proposed solution                                                             |

|----------------------------------------------------------------------------------------------------------------|

| Figure 24: Implementation of a parallel CCSDS pseudo-random sequence generator38                               |

| Figure 25: Timing of data on encoder's interfaces for the general and high latency cases                       |

| Figure 26: Control and Buffer Unit                                                                             |

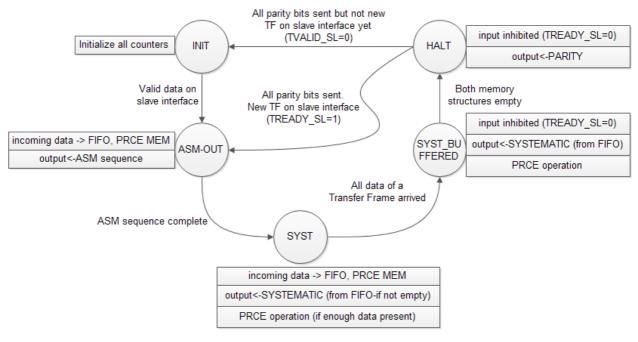

| Figure 27: Simplified state transition diagram of the FSM of the Control and Buffer Unit40                     |

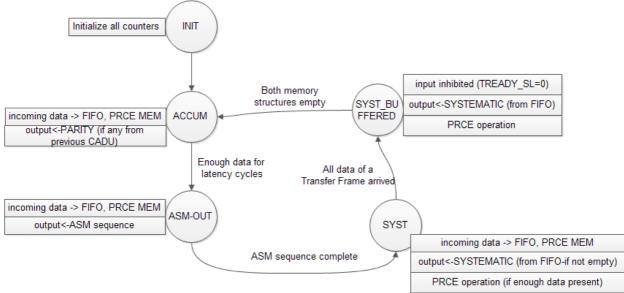

| Figure 28: Simplified state transition diagram of the FSM of the Control and Buffer Unit for La=141            |

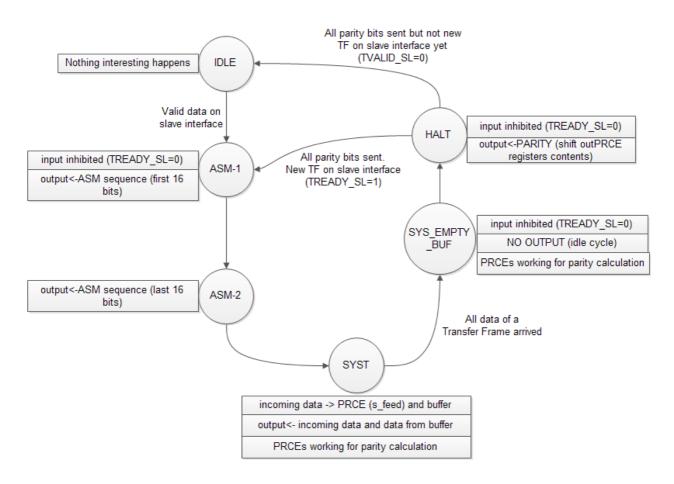

| Figure 29: Simplified state transition diagram of the FSM of the Control and Buffer Unit for high latency case |

| Figure 30: Timing diagram of the FSM states for high latency case42                                            |

| Figure 31: Timing diagram of the FSM states for very low latency case43                                        |

| Figure 32: Timing diagram of the FSM states for the case of no HALT state44                                    |

| Figure 33: Timing diagram of the FSM states for C2 code45                                                      |

| Figure 34: Block diagram of the embedded system for the test with UART input53                                 |

| Figure 35: Sample terminal output54                                                                            |

| Figure 36: Block diagram of the embedded system for the test with LFSR generated data                          |

## TABLES INDEX

| Table 1: Codeword lengths for supported AR4JA codes                                 | 25 |

|-------------------------------------------------------------------------------------|----|

| Table 2: Submatrix size and K parameter for supported codes                         | 26 |

| Table 3: Summary of the most important parameters for AR4JA family                  | 26 |

| Table 4: Bill of materials for RCE-based encoding                                   | 31 |

| Table 5: Bill of materials for iterative encoding                                   | 33 |

| Table 6: Resouces and speed                                                         | 49 |

| Table 7: Implementation test results with UART input data                           | 55 |

| Table 8: Implementation test results with LFSR generated input data                 | 56 |

| Table 9: Summary of demonstrated performance characteristics of the implementations |    |

| Table 10: Comparison of Implementations for C2 code                                 | 58 |

| Table 11: Comparison of various LDPC Encoder Implementations                        | 60 |

## PREFACE

The work presented in this thesis was done in partial fulfillment of the requirements for the post-graduate program of Department of Informatics and Telecommunications of the National and Kapodistrian University of Athens and was supported by the Digital Systems & Computer Architecture Laboratory (DSCAL). Apart form its other areas of activity and research, DSCAL exhibits interest in the development of applications for space systems, including its active involvement is ESA's PROBA-3 space mission.

This work attempts to provide an efficient implementation of communication channel codes already standardized for use in space communications by CCSDS, a multinational forum for the development of communications and data systems standards for spaceflight, based on the expertise of communication experts from its participant nations. Implementations are already parts of launched space missions (Cibola Flight Experiment, MSL-MRO proximity link etc) and are expected to culminate in space communications in future missions, while at the same time gathering attention from disparate application fields, like mobile terrestrial communications (U.S.A.F. LCOT program).

For the development of the encoders for this work, a Xilinx XUPV505-LX110T development board was used, granted by DSCAL. Implementation was performed on Xilinx ISE design suite using VHDL, although considerable effort was made so that the code can be ported to other FPGA vendors without any modifications: it has been verified to be synthesizable also in Altera Quartus software and Microsemi's Libero suite. Simulations were executed in Mentor Graphics Modelsim .

# **1. INTRODUCTION TO LDPC CODES**

The purpose of this chapter is to provide briefly the theoretical background necessary for understanding the encoder implementation. Relevant information theory topics are described to the minimum extent required for the adequate description of the application and by no means intended to explain theoretical topics from a mathematically or information theory concrete point of view.

## 1.1 Noisy Channel Coding Introduction

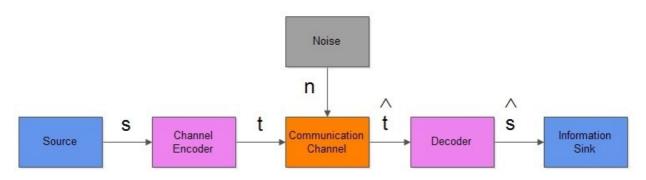

Noise is an inherent element of every communication system. A simplified version of one such system is displayed in figure 1. Noise in space communications channels (not accounting for weather effects at least), is modeled in almost perfect approximation by the Additive White Gaussian Noise (AWGN) model and the channel most commonly considered is the Binary Symmetric Channel (BSC) for a digital communications system. In this model, noise can be represented as a binary vector n, added to the binary sequence t transmitted on the channel, resulting in the received vector t. The purpose of the encoding process is to receive a binary sequence *s* and transform it into another binary sequence t of greater length, which should depict the necessary features to mitigate the result of the addition of the noise vector n. Considering AGWN over a BSC, this noise vector n contains a '1' in each bit position corresponding to a flipped bit of the finally received sequence, and this occurs with a constant probability value "f". The result of this encoding process is that a corresponding decoder at the other end of the communication channel is able to provide an estimate s of the initially transmitted vector s, which is as close to it as possible. This maximum probability of correct inference will be refined later in this chapter.

Figure 1: A simplified binary noisy communication system

Always considering AWGN over BSC, the probability of a bit flipping as a result of the noise vector contribution to the received codeword (i.e.  $P(n_i=1)=f$ ) is expressed by a single metric for an individual bit, namely the bit error rate (BER), or equivalently the error rate for a whole frame (Frame Error Rate, FER). For a sequence of N independent bits, generally  $FER=1-(1-BER)^N$ , although for more interesting codes as our case the frame contains an error if  $s_i \neq s_i^{\circ}$  instead of  $t_i \neq t_i^{\circ}$ . The value of this probability for a single bit ( $P(n_i=1)=f$ ) is a channel parameter, which for the communication model described herein is related to the received signal energy per information bit to the (one sided) spectral density of the white Gaussian noise, commonly referred as  $E_b/N_0$  or Signal to Noise Ratio (SNR).

The encoded sequence t contains redundant information, decreasing thus the rate at which actual communication occurs. In a trivial encoding example, replication codes transmit multiple sequences of the same source bits and decoding is performed on a

majority basis of the value of the received sequence, at the same time though by dividing proportionally the actual information data rate. More interesting codes exploit redundancy more efficiently but generally there seems to be a trade-off between the (decoded) bit error probability and the communication rate.

Before 1948, it was believed that a vanishingly small BER for given channel characteristics (i.e. constant  $E_b/N_0$  value) requires proportionally decreasing rate. All this changed by Claude E. Shannon in his Phd thesis [1], in which the fundamental limits on the performance of all codes (for a given rate) were set.

In particular, Shannon associated with each channel a quantity called capacity C, up to which reliable communication can occur with arbitrarily small BER. This quantity is a channel feature and an equivalent interpretation in the AWGN channel is that for a specific rate, there is a minimum  $E_b/N_0$  for which communication can occur error-free. Figure 2 depicts this relationship for the binary input AWGN channel for a number of communication rates.

Shannon's calculations assume an asymptotically infinite code-block length. In practical applications though this is obviously not feasible and the theoretical capacity limit is lower than that of fig. 2. The effect of block size on code performance is studied further in [3].

Figure 2: Capacity limits for the AWGN channel over a selection of data rates (image from [2])

The above results only prove the feasibility of such codes. The design of the actual codes themselves is nevertheless a different issue, out of Shannon's work scope but a very interesting field of considerable research towards capacity approaching codes. The channel codes implemented in this thesis belong to one such class.

## 1.2 Low Density Parity Check codes

Channel codes can be divided into two major types depending on the grouping of input information in constant size packets (block codes) and the encoding of a continuous stream of data (convolution codes). The codes examined herein belong to the first class. Block codes are further divided into linear and non-linear ones, the latter having never been used in practice. Consequently, we are interested in linear block codes.

## 1.2.1 Linear Block Codes

For a block code, information source bits are grouped into blocks of k bits. The encoding process transforms these into a n -bit codeword, where n > k, adding thus n - k bits of redundant information. For the code to be considered linear, the ensemble of  $2^k$  possible codewords should form a k-dimensional subspace in the vector space  $F_2^n$ . According to this definition, if  $s \in F_2^k$  and  $t \in F_2^n$  are row vectors corresponding to the information block and encoded codeword respectively, there exists a k \* n binary matrix, the rows of which are k linearly independent codewords and  $t \in F_2^n$  is a linear combination of them. Consequently, the encoding process can be described as the operation  $t \in F_2^n$  (performed in  $GF_2$ ). The matrix G is known as the generator matrix and the code itself as a (n, k) linear block code.

The code can be alternatively described by the null space of a different binary matrix H, such that for every valid codeword  $t \in F_2^n$ :  $t H^T = 0$  (zero vector). The H matrix dimensions are (n-k)\*n, assuming full rank (rank deficient matrices are also possible as it will be the case for one of the CCSDS codes of interest) and  $GH^T = 0$ . The H matrix is called the parity check matrix and because it is the null space of the code, it can be perceived as the expression of the constraints an arbitrary binary sequence should satisfied in order to be considered as a valid codeword.

Codes in which the first k bits of the codewords are the uncoded source information bits are called systematic. The codes implemented in this thesis are all systematic. This feature facilitates decoding and other optimizations in the receiver.

## **1.2.2 LDPC description**

LDPC codes where introduced in 1960 by Gallager [4], but generally ignored in the following years due to the current era's technology limitations, which could not allow their implementation at a reasonable cost.

These codes are generally characterized by a sparse parity check matrix H, i.e. a matrix with a very low density of "1s". An absolute definition of sparsity in not defined in literature, but densities up to 1% qualify for the characterization [5]. This sparsity of H matrix coefficients is a key feature for reduced complexity implementation.

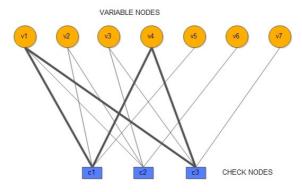

One exception to the oblivion in which LDPC codes succumbed after their invention was the work of Tanner in 1981 [6]. Among other things, he introduced a graphical representation of these codes in what are currently widely known as Tanner graphs. The Tanner graph is a bipartite graph in which node fall into two categories: check nodes and variable nodes, the former expressing the constraints on codewords and the latter the received encoded bits. A connection between a variable node  $v_i$  and a check node  $c_i$  is drawn if the corresponding element  $h_{ii}$  in the parity check matrix is

1. The representation is valid for all linear block codes and a Tanner graph for the well known (7,4) Hamming code is displayed in fig. 3. For LDPC codes this representation facilitates the description of the decoder based on a message passing algorithm between the nodes of the Tanner graph [7].

Figure 3: Tanner graph for the (7,4) Hamming code. Bold lines mark a cycle.

### 1.2.3 LDPC features

An LDPC code is described as **regular** when its parity check matrix has a constant column weight, say  $\gamma$  and constant row weight  $\rho$ . Such a code is said to be ( $\gamma$ , $\rho$ ) regular. In contrast, **irregular** codes have multiple weights. The CCDS codes are all regular.

The parity check matrices of initial Gallager codes possessed no other structure except being linear block codes. The problem is that implementation complexity makes their application prohibitive. A desirable structure to facilitate implementation is that of **cyclic** codes: each row of the parity matrix H is a cyclic shift of the previous one. Since each check equation is related to the previous in a very specific way, encoder complexity is substantial: it is built by simple elements around a shift register. More interesting codes though are built using a viable compromise between complexity and performance, using a **quasi-cyclic (QC) structure**. The parity check matrix of these codes consists of an array of juxtaposed cyclic submatrices called **circulants**. The general form of such a matrix is the following:

| H= | $A_{11} \\ A_{21}$ |                 |   |   | $.A_{1N} \\ .A_{2N}$ |

|----|--------------------|-----------------|---|---|----------------------|

|    | $A_{_{M1}}$        | A <sub>M2</sub> | • | • | . A <sub>MN</sub>    |

Each sub-matrix  $A_{ij}$  is a cyclic matrix with a very low density of ones. The implemented codes in this thesis belong to this class of LDPC codes.

The design of the code for this class of LDPC codes is consequently reduced to the task of defining the optimum position of 1s in the parity check matrix. Several techniques and mathematical tools are employed and considerable research is always hot on these topics. Generally, design techniques are classified in two big categories: a) **random** or **pseudo-random** codes, which use computer-based algorithms or methods and b) **algebraic** codes which use mathematical or combinatorial tools such as finite geometries and combinatorial designs. The codes implemented here belong to both categories. In particular, AR4JA codes were generated by a pseudo-random algorithm based on a design entity known as a **protograph**. This is simply a Tanner graph with a low number of nodes, which is repeated (consider placing a number of such graphs side-by side). Connection lines between variable and check nodes of the expanded super-graph are permuted in a pseudo-random manner. The number of repetitions and

the permutations pattern is a result of advanced techniques (density evolution, progressive edge growth). An introduction to this topic is included in [8].

A common feature shared among the most interesting LDPC codes is the Row-Column **(RC) constraint**: no two rows or two columns are allowed to have a '1' in more than one position at the same time: for example codewords "01001101..." and "11101010.." belong to a non-conformant code because there is a '1' at positions 2 and 5 (at least). The presence of this constraint ensures that the minimum distance of a ( $\gamma$ , $\rho$ ) irregular code is at least  $\gamma$ +1. Moreover, it precludes cycles of length 4 in the Tanner graph of the code. Cycles in a graph are structures in the form of a path in a graph from one node back to itself. One such path in displayed with bold lines in fig. 4 for the Hamming code. These structures jeopardize the code performance, as it will be mentioned in next paragraph.

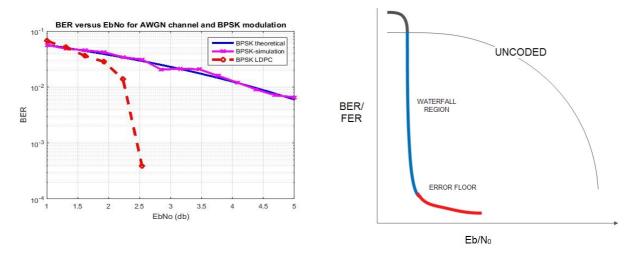

## 1.2.4 LDPC performance

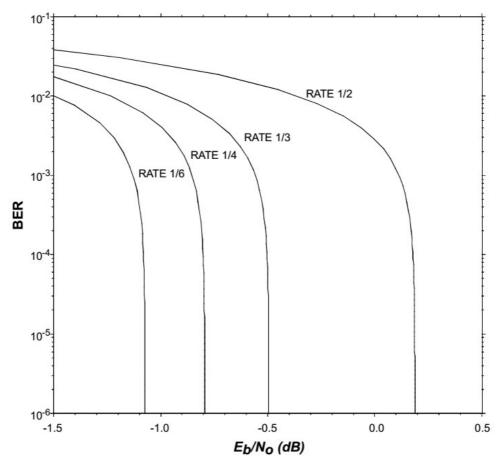

LDPC codes are the most promising solution towards capacity approaching performance. The most obvious performance metric is the BER or FER performance, or in other words, how close to the Shannon capacity limit these codes can approach. In fig. 4, simulation results for the AR4JA rate 3/4, block length 1024 bits LDPC code are presented. Decoding is performed in a software (MATLAB) implementation of the iterative Sum of Products Algorithm (SPA). For the number of simulation iterations specified in this test, BER was zero for  $E_b/N_0$  grater than roughly 2,5 dB.

Figure 4: BER performance for the rate 4/5 k=1024 CCSDS LDPC code

Figure 5: General form of the BER curve for most LDPC code

The BER curve of a code is generally partitioned into three regions displayed on fig. 5: the non-performing region (black), the waterfall region (blue) and the floor region (red). For extremely low SNR values, there is no point to introduce a channel code since the errors are so many that the decoder will try to converge most probably towards another completely different codeword (with smaller distance to the erroneously received). The code is non-operational in this region. Above a certain limit of  $E_b/N_0$  value called the **threshold**, the **waterfall region** begins: this is recognized as an abrupt slope int the plot and it is the area where the code performs optimally. There is however a point where this abrupt transition halts or even the curve remains constant. This is known as

the **error floor** and it is the point where the code becomes inefficient. This weakness is a common feature of all LDPC codes and it is caused mainly by undesirable structures in the Tanner graph of the code such as **trapping sets** or **stopping sets**. For reasons that remain unknown, there seems to be a trade-off between low threshold and low error floor [9].

Decoder complexity is another performance parameter for LDPC codes. Generally, decoding is performed by an iterative belief propagation algorithm in which variable nodes and check nodes exchange messages conveying likelihood information. The number of steps required for decoding may limit the actual data rate of the communication and this is especially important for high data rates.

Generally, the code performance is a still unknown function of a number of code parameters and structures in the Tanner graph and the LDPC codes exhibit a wide diversity of characteristics. The area is open for research. An introduction to performance considerations can be found in [9].

### **1.3 Encoder architectures for Quasi-Cyclic codes.**

Encoding process of a linear block code is in essence nothing more than a matrix multiplication over  $GF_2$ . The encoded vector is  $t = s \cdot G$ , where G is the generator matrix and s the input vector.

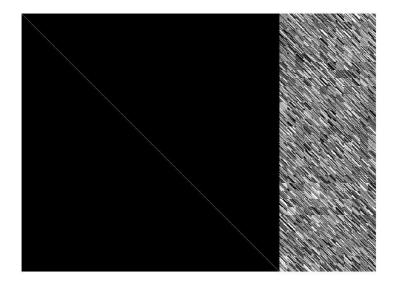

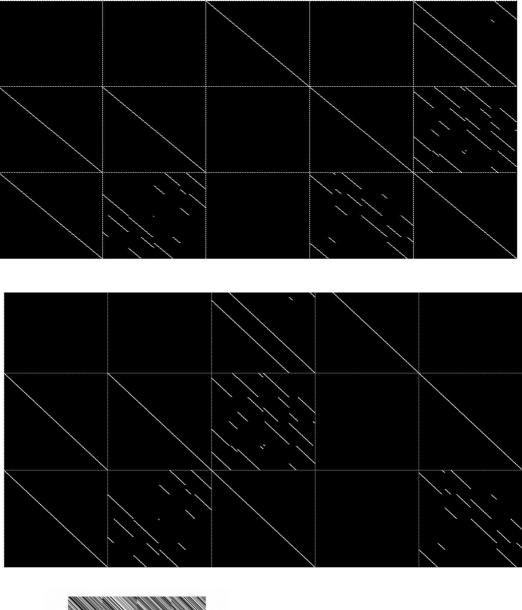

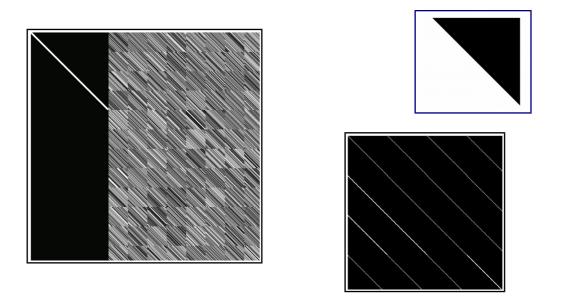

The circulant structure of the parity check matrix can be exploited to facilitate the encoding process. With suitable transformations, it is possible to calculate the Generator matrix in systematic circulant form and limit the encoder's complexity to being just linear with the block length [10]. The circulants though of the resulting generator matrix from this process are dense circulant matrices. Figure 6 displays the shape of such a systematic circulant matrix for one of the codes of interest. A '1' in this image is represented by a white pixel, whereas a '0' is black.

#### Figure 6: Generator matrix of AR4JA LDPC code with k=1024, rate 4/5 (punctured bits included)

The systematic output of the encoder with a generator matrix in this form is the direct output of the input bits. The non-systematic part of the output can be implemented by simple shift registers, as shown below.

## 1.3.1 Straightforward implementation

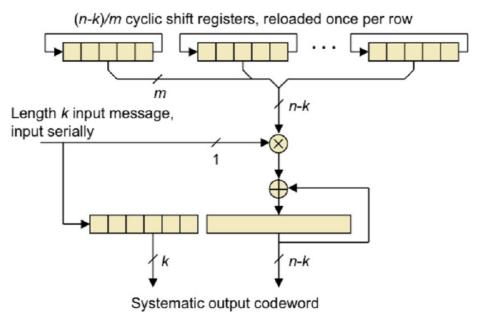

A straightforward solution for the multiplication of a row vector with a systematic circulant matrix is displayed on fig. 7. Codeword length is n, input block size is k and circulant size is m

Initially the last n-k bits of the Generator matrix are stored in the cyclic shift registers at the top of the image. These bits correspond to the first rows of the first row of circulants in the generator matrix. The first information bit to arrive is ANDed with this vector, and the resulting vector is XORed with the current value of the accumulator at the lower end of the image. The accumulator stores the result of this XOR operation. Then the shift registers containing the circulants of the generator matrix; the result is multiplied by the next message bit and added to the accumulator. This process is repeated *m* times to complete the first row of circulants in the generator matrix.

After the AND-XOR operation corresponding to the last row of circulants is completed, the shift registers do not perform a shift operation but a load instead: the next row is loaded and the above steps are repeated until all information bits have arrived at the encoder. During all these steps, arriving input bits form the systematic part of the output.

This straightforward implementation requires 2(n-k) storage elements (flip-flops) and k(n-k) AND-XOR operations.

Figure 7: A straightforward encoder implementation for a QC LDPC code

## 1.3.2 RCE implementation

A more efficient approach is given in [11], henceforth mentioned as RCE encoder. The encoder's architecture is displayed in Figure 8 and it makes use of the ideas applied to the design of convolutional codes, namely the encoder structure of a Recursive Convolutional Encoder (RCE).

The idea behind this implementation is to keep the circulants values stationary and cyclically shift the accumulator bits instead. The generator matrix values become combinational functions of an input message bits counter.

During the information bits input, the (systematic output of the encoder is these input bits: the selectors in the RCEs are set to perform the cyclic shift and the output selector is set to the upper position to select the input. Upon completion of the calculation the selectors positions are switched and the calculated parity bits are simply shifted out of the RCEs.

Figure 8: RCE encoder

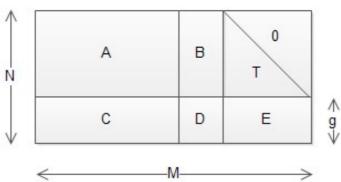

### 1.3.3 RU encoder

In 2001 Thomas Richardson and Rüdiger Urbanke demonstrated a reduced complexity encoder for LDPC codes [12]. As a first step, the parity check matrix is rearranged into in an approximately lower triangular form through reordering of rows and columns. The resulting matrix has the general shape of fig. 9.

Figure 9: The parity check matrix transformed into lower triangular form

Since the original matrix is sparse, the sub-matrices A, B C, D are also sparse. The elements of matrix T are all zero above a certain diagonal. Without describing the mathematical details of the work in [12], we use only their result, keeping the notation though consistent. For a systematic code, the k=M-N input vector s is encoded as a systematic codeword  $t = [sp_1p_2]$ , where parity bits are partitioned in two sub-vectors  $p_1 = p_2$ . The steps are outlined below.

Firstly, calculate  $\varphi = ET^{-1}B + D$ , which is a dense g x g matrix. The first parity bit vector is  $p_1^T = \varphi^{-1}(ET^{-1}A + C)s^T$  and the second is  $p_2^T = T^{-1}(As^T + Bp_1^T)$ . This calculation involves several sparse matrices and for several interesting codes (including the CCSDS AR4JA examined here), T is the identity matrix. As a result, the above

equations are further simplified into the following:  $\varphi = EB + D$ ,  $p_1^T = \varphi^{-1}(EA + C)s^T$  and  $p_2^T = As^T + Bp_1^T$ . The dense matrix  $\varphi$  can be precomputed in advance, while other operations on sparse matrices can be calculated using simplified hardware.

As an example, the corresponding matrices for one of the codes implemented in this thesis are displayed in fig. 10.

Figure 10: From top to bottom: The parity check matrix of rate  $\frac{1}{2}$  k=1024 CCSDS LDPC code, the same matrix transformed in lower triangular form and the inverse matrix  $\varphi^{-1}$ . Each rectangular is 512x512 bits. The  $\varphi^{-1}$  matrix is also 512x512, consisting of 64x64 submatrices.

The dense matrix operations are calculated using a usual encoder such as those described in previous chapters. For sparse matrix operations, a simplified architecture is displayed in fig. 11.

#### Figure 11: Multiplication of a sparse matrix with a vector and the corresponding hardware[13]

The sparse matrix is constructed from circulant submatrices of size N. The circuit on the figure performs a multiplication of a vector of size 4N with a sparse matrix 4Nx8N. As incoming information bits arrive, the multiplexors below the shift registers select which bit of the shift register is going to be subject to modification by the XOR gate. This is easy to understand since from the N bits of the circulant, only one is going to take part in the parity calculation at each step. A (hopefully) small memory controls the MUX operations. More XOR gates are needed in case the sparse matrix is not a rotated identity matrix like those in the given example.

The iterative encoder calculates parity bits directly from the parity-check matrix instead of the generator. This can lead to high performance parallel encoders, provided that the corresponding LDPC codes are amenable to the modifications described in Richardson-Urbanke work (very low value of g). This is the case with LDPC codes employed in DVB-T and 802.16ac standards for which encoders have been proposed in the multi-gigabits per second range speed [14] [15].

## 1.3.4 Iterative encoder

In the special case where g=0 (fig. 9), the parity check matrix is simplified into a lowertriangular form, the structure of which can be exploited in order to create especially optimized high-throughput encoders. Like in RU method, parity bits can be directly calculated from the parity-check matrix using back-substitution: Let  $c = [m \ p]$  be a codeword block, where m and p indicate the information bit sequence and the parity bit sequence, respectively and H=[H<sub>1</sub> H<sub>2</sub>] the parity-check matrix partitioned into two submatrices H<sub>1</sub> and H<sub>2</sub> of suitable size to correspond to the multiplication operations detailed below. From the property that the correct codeword satisfies the parity check equation, the parity bit sequence p can be derived as follows:

$$H \cdot c^{T} = H_{1} m^{T} + H_{2} p^{T} \implies p^{T} = H_{2}^{-1} H_{1} \cdot m^{T}$$

Matrix  $H_1$  is sparse in all LDPC codes but this is not always the case for  $H_2^{-1}$  matrix, which is generally sparse. LDPC codes designed with encoding efficiency as a primary goal contain significant structure in these codes. Efficient encoders for the applicable codes can take advantage of these structures to maximize throughput while keeping resource utilization at a minimum.

Examples of such codes are LDPC codes for IEEE 802.11ac and DVB standards. In the former case,  $H_2^{-1}$  matrix consists of rotated identity submatrices, while in DVB-S2 it is an upper triangular matrix (fig. 12). In all cases, the sparse matrix operation  $H_1 \cdot p^T$  between the sparse matrix  $H_1$  and the vector *m* can be performed in a highly parallel way, which can even be performed in just one clock cycle. For 802.11ac, the last multiplication with  $H_2^{-1}$  can be performed in parallel with shift registers and back-forward accumulation [16] in just a few clock cycles (depending on the rotated identity matrix size in  $H_2^{-1}$ ). In a similar way, the structure of  $H_2^{-1}$  in DVB-S2 corresponds to a trivial forward substitution operation [17]. Encoders have been proposed for such codes in [16], [17], [18], [19] with performance in the multi-Gbps range.

Figure 12: H<sub>2</sub><sup>-1</sup> matrices for various LDPC codes: AR4JA code (left),DVB-S2 (right-top), IEEE802.11ac (right bottom). Left image identity matrix stressed for emphasis.

These highly parallel architectures however are not suitable for the codes considered in the current work. Considering fig. 12, this is obvious. Indeed, the matrix for AR4JA codes (rate ½, k=1024 in the case depicted) consists of a 512×512 identity matrix on the left and a 12×8 array of 128x128 dense circulants. This matrix is apparently more complicated than the generator matrix of the code and there is absolutely no benefit if this algorithm is followed. Instead, hardware requirements are expected to be even larger because of the calculation of the (unnecessary) omitted punctured parity bits. Similar assumptions hold also for other examples of LDPC codes whose parity-check matrix exhibits similar structure.

# 2. CCSDS STANDARDS

The Consultative Committee for Space Data Systems was found in 1982 by the major space agencies of the world and it is a multinational forum for the development of communication and data systems standards for spaceflights.

CCSDS protocols, collectively known as Space Communication Protocol Specifications (SCPS) are generally based on well-known Internet protocols, with the necessary modifications and extensions to cope with the specific space demands. For an introduction to CCSDS space communication protocols, reference [20] is a starting point.

CCSDS standards follow a color code according to which, "yellow" publications start as experimental and are finally standardized as "blue" books, which is the color of the recommended publications. Books colored "green" are information reports, generally providing the rationale behind the adoption of each standard or other information of general interest.

In this work, the focus is on the data link layer, in which four Space Data Link Protocols (SDLPs) have been developed:

- Telemetry SDLP (TM-SDLP) is used mainly by spacecraft systems for the emission of sensor data and systems readings.

- Telecommand SDLP (TC-SDLP) for commands from a ground station (or another spacecraft) to a spacecraft.

- Advanced Orbiting Systems SDLP (AOS-SDLP) is an extension to TM-SDLP for bidirectional exchange of on-line information like audio and video.

- Proximity-1 Space Link Protocol for short-range bidirectional links between fixed probes, landers, rovers, orbiting constellations and orbiting relays. Proximity-1 is an altogether different protocol stack from the previous one (SCPS) but obviously has a data link layer.

The data link layer's lowest functions are synchronization of upper layer Protocol Data Units (PDUs), called **Transfer Frames (TF)**, randomization and channel coding. These functions belong to a sublayer of data link layer called synchronization and channel coding sublayer. TM and AOS SDLPs share the same synchronization and channel coding sublayer specification.

The excellent performance characteristics of LDPC codes led CCSDS to adopt them in synchronization and channel coding sublayer of TM-SDLP and recently in Proximity-1 data link layer.

Two classes of LDPC codes were adopted for use in TM-SDLP: one class of codes optimized for deep-space applications (AR4JA) and another for near-earth (C2). Interestingly though, one particular code of the AR4JA family (k=1024 rate  $\frac{1}{2}$ ) was selected for Proximity-1 coding and synchronization sublayer.

In the first case, for deep space communications, good  $Eb/N_0$  performance is more important than high data rates. Communication data rates are lower and the bandwidth expansion caused by lower channel code rates can be tolerated. Low error floors are an important parameter defining the SNR performance of the code and for the codes of this family, they achieve a fair combination of low threshold and low error-floor. The CCSDS standards define nine LDPC codes for this family, sharing a common mathematical description. The total number of nine codes is the result of the combination of three block length sizes of 1024, 4096 and 16384 bits over three code rates: 1/2, 2/3 and 4/5. In the second case, for Near Earth communications, data is transmitted at hundredths of Mbps in 375Mhz restricted band. Higher data rates are important in this case, together with fast convergence of the (iterative) decoder. Error floor should be very low (<10<sup>-10</sup> BER) also. For these reasons, CCSDS adopted a (8176,7156) LDPC code for these communications, henceforth described as C2 after [21].

The selected code rates are 1/2, 2/3, 4/5, and approximately 7/8, which are about uniformly spaced by 1 dB on the rate-dependent capacity curve for the binary-input AWGN channel [2]. Near rate 1/2, a one-percent improvement in bandwidth efficiency costs about 0.02 dB in power efficiency; near rate 7/8, a one-percent improvement in bandwidth efficiency costs 0.1 dB in power efficiency.

Within the AR4JA family, the selected block lengths (k=1024, 4096 and 16384) are about uniformly spaced by 0.6 dB on the sphere-packing bound at WER=10 -8. By choosing to keep k constant among family members, rather than n (codeword length), the spacecraft's command and data handling system can generate data frames without knowledge of the code rate. To simplify implementation, the code rates are exact ratios of small integers, and the choices of k are powers of two.

Since the LDPC codes implemented in this thesis are already a standard publicly available in [22], the description that follows is limited to the necessary features for the better understanding of the implementation section that follows. Further insight on the performance characteristics of the adopted codes is provided in [2].

Real-life implementations of the proposed standards exist and they are continuously growing. NASA adopted the AR4JA for the MSL(Curiosity) to MRO link. Proximity-1 LDPC code was also the choice for all links of the Constellation program. Code C2 (rate 7/8) was the choice for LDCM (Landsat 8) and NOAA's geostationary satellite GOES.

## 2.1 AR4JA LDPC code family

TF (information block) length for each of the 9 codes is given on Table 1.

An important feature of this family is that the codes are **punctured**, meaning that not all of the encoded bits are transmitted. Parity check matrices include additional linearly dependent rows.

| Transfer Frame | Codeword length (n) |       |       |

|----------------|---------------------|-------|-------|

| length (k)     | 1/2                 | 2/3   | 4/5   |

| 1024           | 2048                | 1536  | 1280  |

| 4096           | 8192                | 6144  | 5120  |

| 16384          | 32768               | 24576 | 20480 |

Table 1: Codeword lengths for supported AR4JA codes (in bits

The parity check matrix of this code is a juxtaposition of circulant sparse M×M submatrices. The value of the parameter M is given on Table 2.

| Rate                         |       | 1/2  | 2/3      | 4/5   |

|------------------------------|-------|------|----------|-------|

|                              |       | Subn | natrix s | ize M |

|                              | 1024  | 512  | 256      | 128   |

| Transfer Frame<br>length (k) | 4096  | 2048 | 1024     | 512   |

|                              | 16384 | 8192 | 4096     | 2048  |

| K parame                     | 2     | 4    | 8        |       |

The positions of 1 in the parity check matrix are provided by the standard as a formula and they can be easily implemented in MATLAB. One pictorial example of a parity check matrix was displayed on fig. 10 for the k=1024 rate  $\frac{1}{2}$  member.

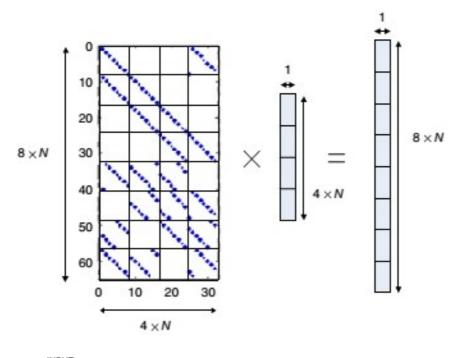

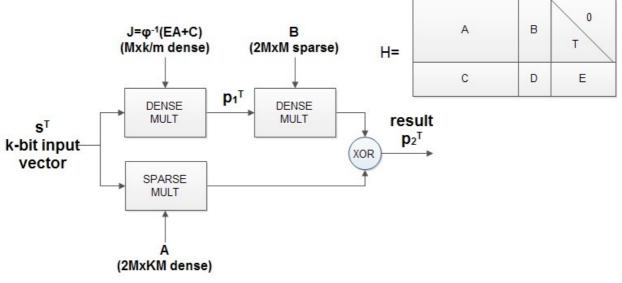

The generator matrix for each member of the family has the form  $G = [I_{MK}W]$ , where  $I_{MK}$  is the MKxMK identity matrix and W is a dense matrix of size MKx3M. Matrix W is calculated in systematic-circulant form, according to a methodology provided in [23]. The punctured bits can be omitted from the generator matrix during the encoding process and the matrix W can be simplified to MKx2.

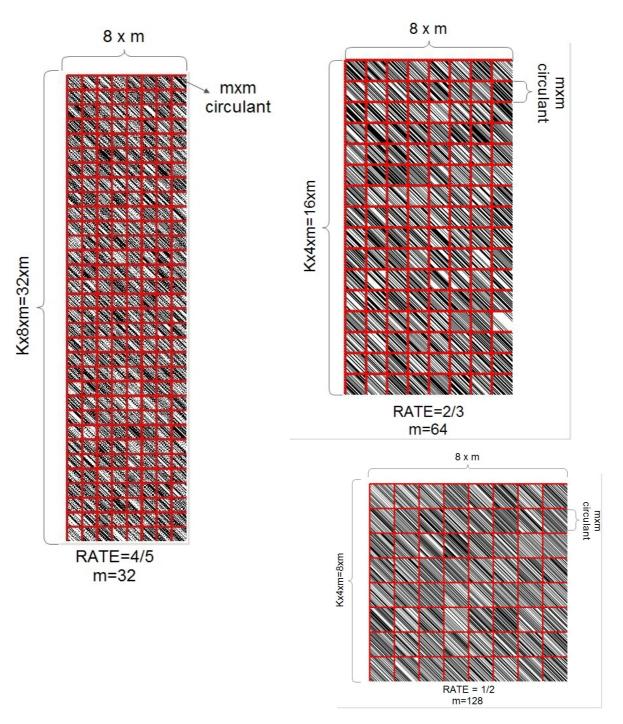

The submatrix W is also an array of juxtaposed circulants. The parameter m describes the circulant size of the generator submatrix W and its value is for all members m=M/4. It follows that the submatrix W is consequently a 4Kx8 array of m×m circulants. Note that parameter K is related only to the code rate and is independent of block length! For better intuition into the structure of the generator matrix, fig. 13 displays the W submatrices for all k=1024 codes. Also, the code parameters defined so far are of high importance for the encoder's design. Table 3 summarizes them briefly. These parameters and images are important for the description of encoder operation.

| Parameter | Description                                                          |

|-----------|----------------------------------------------------------------------|

| k         | Transfer Frame block length                                          |

| n         | Codeword length                                                      |

| М         | H matrix circulant size, depends on rate and k                       |

| m         | G matrix circulant size, equals M/4                                  |

| K         | Describes G matrix vertical dimension as a function of m, equals k/M |

Table 3: Summary of the most important parameters for AR4JA family

Figure 13: Submatrices W of generator matrices for codes of k=1024.

It is very important to note that for all members of the family, there are always 8 circulant columns. Also note that the number of circulant rows depends only on the code rate and not the block length (k). These notes will enable the development of a single parametric VHDL model for the encoder to cover all the members of the family.

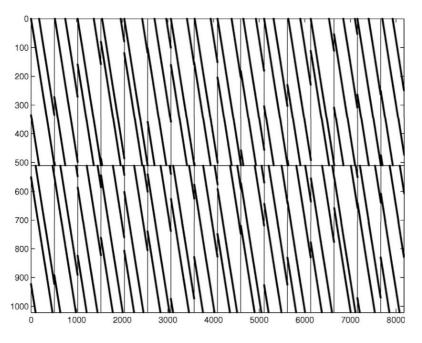

## 2.2 C2 code for near-earth applications

According to the standard, (8160,7136) C2 LDPC code is an expurgated, shortened, and extended version of a basic (8176,7156) LDPC code, based on Euclidean geometry. The important features of the code needed for the design of a suitable encoder are the following:

- A TF of 7136 bits is provided for encoding, to which 18 zero bits are prepended. The reason for this is to ensure that incoming information block is divided by 8 and 16, which is the word length of many microprocessor buses.

- The 18 prepended zeros take part in the encoding process, but they are not transmitted as a part of the systematic output of the encoder. To ensure though that the output is also divided by 8 and 16, two filling zero bits are appended to the final codeword to produce an 8160 bit output.

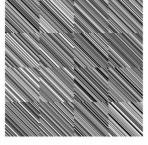

- Parity check matrix is quasi-cyclic: is consists of a 2×14 array of 511×511 sparse circulants (image 13). Generator matrix in systematic circulant form is provided in the standard. The non-systematic part of it is a 14×2 array of 511×511 dense circulants.

Figure 14: Scatter chart of the parity-check matrix of C2 LDPC code

### 2.3 Frame Synchronization and CADU structure

At the receiving end, a method is required for discerning the boundaries of codewords in the received stream of code symbols, or else decoding process would fail: the decoding algorithm would be applied to the wrong sequence of received bits.

CCSDS standards require that LDPC codewords shall be synchronized with a specially designed bit sequence, called Attached Sync Marker (ASM). For AR4JA codes, this sequence is 64 bit, while for C2, a 32-bit sequence has been adopted. Note that the 64-bit ASM is the same for TM SDLP and Proximity-1.

The ASM patterns in hexadecimal notation are the following:

AR4JA: 034776C7272895B0

## C2: 1ACFFC1D

ASM sequence is prepended to the encoded codeword to form a data unit called Channel Access Data Unit (CADU).

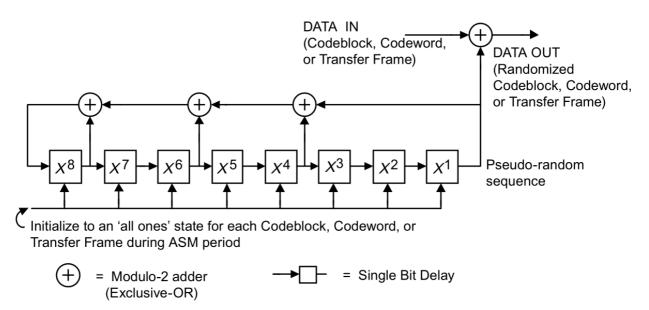

## 2.4 Randomization

The correct operation of the receiver requires that incoming data should contain adequate transition density of received symbols. Transitions help receiver maintain symbol synchronization with the coded symbol boundaries in the received signal. In addition, short periodic data patterns generate spurious frequencies which impair receiver's performance. The absence of randomization in the encoded data has been the source of several unexpected problems with the telemetry links of a number of projects [20]. Consequently, randomization is highly recommended by CCSDS standards, although not mandatory.

Randomization is assured through the bit-wise addition of the codeword data with a pseudo-random sequence generated by the polynomial  $h(x) = x^8 + x^7 + x^5 + x^3 + 1$ . This polynomial can be implemented an 8-bit Linear Feedback Shift Register (LFSR). A possible implementation of the LFSR provided in the standard is displayed on fig. 15 with a Fibonacci LFSR. At the beginning of each codeword, the LFSR is initialized to all 1s. The pseudo-random sequence is repeated every 255 bits until the end of the codeword.

It is important to note that the ASM sequence defined in previous paragraph is already optimized for transition density and should not be subject to randomization. Also, the specified randomization sequence remains the same for all protocols.

## 3. ENCODER DESIGN

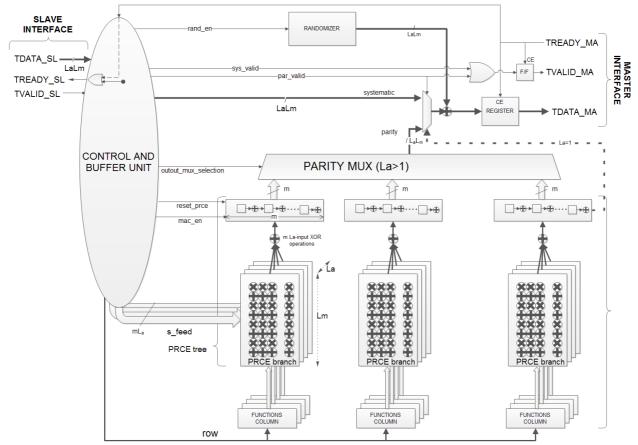

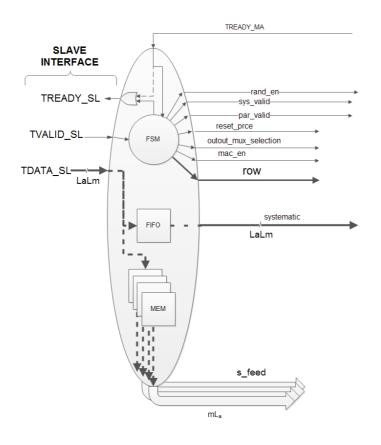

Having provided the necessary background for the description of the implementation, this chapter moves on to the implementation itself. A single encoder top entity is designed for all members of CCSDS LDPC codes and the corresponding diagram is displayed on fig. 16.

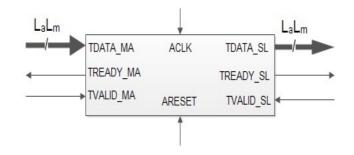

The encoder receives a continuous stream of data and produces a stream of CADUs. The receiving (slave) and transmitting (master) interfaces conform to AMBA 4 AXI4-Stream protocol [24] and are built according to the simplest possible configuration allowed by the protocol specification.

Figure 16: Encoder's top level diagram

The data buses are  $L_m \times L_a$  bits wide. The meaning of the parameters  $L_m$  and  $L_a$  is to be clarified in this chapter. Valid data are framed by TVALID signal and a TREADY signal signifies the availability of the interface. According to the specification, for a transfer to occur both the TVALID and TREADY signals must be asserted at a rising clock edge.

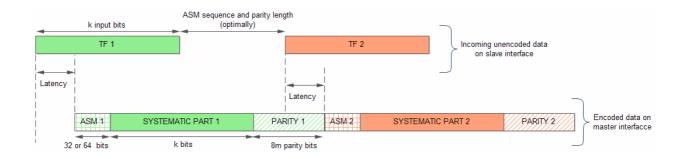

No other signaling triggers the encoder to initiate the synthesis of a CADU other than the presence of valid data on the slave bus and the boundaries between successive TFs are not marked by any handshake signals but are kept by the encoder's counters instead. For maximum performance, the master (output) interface should be busy 100% of the time and this means that idle cycles should be imposed on the receiving (slave) interface through the AXI-4 Stream handshake signals. The timing of input and output data is displayed on fig. 17.

## 3.1 Encoder Architecture selection

In §1.3 the general encoder architectures were briefly presented. Among the proposed architectures, the one that is most suitable for the characteristics of CCSDS codes needs to be selected for implementation.

The advantages of RCE encoder over the straightforward implementation are selfevident and have already been amply described in [11] and [13]. Consequently, the straightforward implementation is not subject to further investigation. Following the analysis for iterative encoders in §1.3.4, they are also excluded from investigation. The choice is to be made among the two remaining options, namely the RCE and RU encoder, based on the combination of resources and the performance each method can achieve. This analysis is similar to the work in [13], with the difference that a real AR4JA code is taken as an example here instead of the (small) example code considered in that paper. In addition, this work focuses on FPGA implementation possibilities.

### 3.1.1 RCE encoder resources

For all members of the AR4JA family, the generator matrix is composed of eight circulant columns for which eight RCEs similar to those displayed on fig. 8 can be used. Each RCE is implemented with m flip-flops (F/F), m 2-input AND operations and m 2-input XOR operations. The circulants are implemented by m function generators of *ceil(log<sub>2</sub>(k/m))* inputs. For the interconnection of the RCEs, a negligible amount of resources are needed. In particular, 8 2-input multiplexors to select the desired input for the RCE (switches in fig. 8) and a small amount of control logic to activate them, not taken into consideration. The necessary resources are listed on Table 4.

| Resource                                        | # needed | Example for k=1024 rate 1/2 |

|-------------------------------------------------|----------|-----------------------------|

| AND                                             | 8xm      | 1024                        |

| XOR                                             | 8xm      | 1024                        |

| F/F                                             | 8xm      | 1024                        |

| ceil(log₂(k/m))<br>input function<br>generators | 8xm      | 1024 (3-input)              |

| 2-input<br>multiplexors                         | 8        | 8                           |

Table 4: Bill of materials for RCE-based encoding

### 3.1.2 Iterative encoder resources

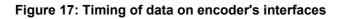

The calculations based on Richardson-Urbanke work [12] can be executed according to the flow diagram of fig. 18 for maximum parallelism. The partition of parity-check matrix into submatrices is repeated from figure 9 for easier understanding.

The encoding process entails one dense matrix multiplication and two sparse. The partial products are added in the end. For the dense matrix multiplication in the first stage, RCE encoders shall be employed. The dense matrix J is quasi-cyclic: it is a

4×(k/m) array of m×m circulants. Following an analysis similar to the previous paragraph, the resources for the RCEs corresponding to the column J stage of Table 5 are calculated.

Figure 18: Iterative calculation of parity bits

Sparse matrices multiplications can be efficiently executed by the circuit of figure 11. For each circulant of size m this configuration needs 1 XOR operation, m F/Fs for implementation of the shift register, 1 m-input encoder and m OR operations between the elements of the shift registers to multiplex the input to the F/Fs between the value of the previous register and the input from the decoder. The last requirement for the shift registers was not taken into account in [13]. The control logic for x circulant rows can be implemented by a function generator of ceil( $log_2(x)$ ).

Matrix A is an  $8 \times 4K$  array of m×m circulants. The first 4 rows are always zero, so the function generator required for the control logic can be simplified to 2 inputs. Column.

Similarly, matrix B is an 8×4 array of m×m circulants. Resource reuse between stages A and B cannot be established for pipeline operation, so independent hardware should be allocated to these two stages. Table 5 summarizes the results.

A comparison between the two matrices justifies the assumption that the iterative encoder –at least at this form- is not an appealing proposal. The simplification of the functions generators and the reduced number of AND and XOR functions of the iterative encoder implementation are balanced by the increased number of flip-flops, the addition of the OR functions amidst the elements of the shift registers and the large multiplexors and decoders Another important drawback of the iterative encoder is the higher latency introduced. B stage operations cannot start before all bits of the TF have been processed by stages A and J.

As stated in [13], modifications could be made to the standard's code design without significant impact on the BER performance of the code. This however is an area of considerable interest and research of information theory and future developments are heavily anticipated.

In this thesis, the design based on the RCE is selected for the implementation of the CCSDS LDPC codes. Optimizations of the basic design are presented in next paragraph

| Resource                          | # J stage | #A stage | #B stage | TOTAL (example for k=1024 rate 1/2) |

|-----------------------------------|-----------|----------|----------|-------------------------------------|

| AND                               | 4xm       | -        | -        | 512                                 |

| XOR                               | 4xm       | 4xK      | 32       | 512+8+32=552                        |

| F/F                               | 4xm       | 4xKxm    | 4xm      | 512+1024+512=2048                   |

| 1 input<br>function<br>generators | 4xmxK     | -        | -        | 1024                                |

| 3 input<br>function<br>generator  | -         | -        | 4        | 4                                   |

| 2 input<br>function<br>generators |           | 4xK      | -        | 8                                   |

| 2-input<br>multiplexors           | k/m       | -        | -        | 8                                   |

| m-input<br>multiplexor            | -         | 4xK      | 4        | 12 (128-input)                      |

| m-input<br>decoder                | -         | 4xK      | 4        | 12 (128-input)                      |

| OR                                | -         | 4xKxm    | 4xm      | 1024+512=1536                       |

Table 5: Bill of materials for iterative encoding

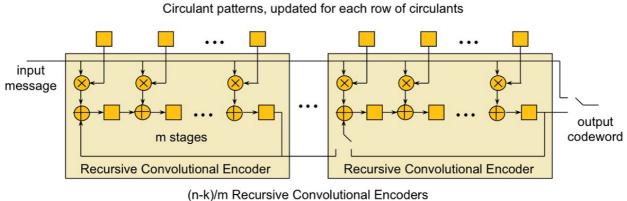

### 3.1.3 Parallel RCE implementation

The RCE described so far (fig. 8) is capable of serial (one bit at a time) output of the calculated parity bits. A parallel output of a number of  $L_m$  bits can be produced with a modification of the basic RCE according to fig. 19. In the image,  $L_m$ =4 for easier understanding. Note that shift operations have a step of  $L_m$  bits to the right, instead of one in the shift register of figure 8.

Alternatively, the input at each register can be conceived as a function generator of the  $L_m$  information bits and the  $log_2(k/m)$  bits of each function generator  $f_i$ . It follows that increasing the  $L_m$  parallelism leads to larger combinational paths in the design but at the same time it increases throughput.

Another source of parallelism can arise from the structure of the generator matrix. For all members of the family, it consists of k/m circulants of size  $m \times m$  each. Two or more circulants (generally L<sub>a</sub>) can be processed at the same time, provided that the corresponding input information bits are available. The partial products of the multiple circulants are XORed. Figure 20 is a simplified diagram showing this possibility. Different colors are employed to show the parts of the generator matrix for which each branch of AND-XOR operations is responsible.

The two sources of parallelism are are thus described by two corresponding degrees:  $L_m$  describes the successive bits parallelism and  $L_a$  multiple circulants parallelism.

Figure 19: A RCE module for parallel processing of L<sub>m</sub>=4 bits of mxm circulants.

Figure 20: Simplified view of a parallel RCE with both sources of parallelism: La and Lm.

Increasing  $L_a$  parallelism comes with the advantage of simplification of the function generators ( $f_i$ ,  $g_i$ ,  $h_i$ ,  $i_i$  in fig. 20) for the values of the generator matrix. In the example given in this figure, the 3-input functions generators necessary for 8 rows of circulants of the generator matrix are simplified to just 1-input. Since this simplification affects all the 8xm functions generator for all the parity bits of the code, considerable amounts of resources can be saved, leading to more efficient encoders.

On the other hand, the information bits corresponding to a number of L<sub>a</sub> circulants need to be available for the RCE operation to begin. In cases where the information bits arrive at the encoder as a stream of data, buffer structures are necessary to save them until the required amount for processing has arrived. These buffer structures and the control logic required for their operation place demands on the resources budget of the design. In fact, the amount of memory required is not just mL<sub>a</sub> bits, but double this  $(2 \times m \times L_a)$  for uninterrupted operation. In addition, the commencement of parity calculations for a given TF has to be delayed for at least  $(L_a-1) \times (m/L_m)/L_a$  clock cycles, introducing an equal amount of latency.

The product of these two sources of parallelism ( $L_m \times L_a$ ) can give the total combined degree of parallelism of the encoder which describes the total number of input bits to the encoder. Generally, this number should be a power of two, so as to match the width of computer buses. For optimal performance, calculated parity bits should also be output in the same number. For  $L_a > 1$  and optimal performance (i.e.  $L_a \times L_m$  bits output), it is not possible to just shift out the calculated parity bits, like the encoder of fig. 8 or fig.19. The  $L_a \times L_m$  output parity bits are selected each time from a multiplexor shown in fig. 20. The multiplexor and associated control logic are another source of complexity as a result of an encoder selection with  $L_a > 1$ .

For AR4JA codes, the encoders described in this thesis implement every reasonable combination of  $L_a$  and  $L_m$  parallelism for a given amount of total parallelism ( $L_a \times L_m$ ), leading to different compromises between latency, speed and resource utilization. These results are provided in a subsequent chapter. The degrees of parallelism are design parameters statically defined for each individual implementation. An obvious limitation in the value of  $L_a$  is that it cannot exceed the number of the circulant rows of the generator matrix. For example, for all rate  $\frac{1}{2}$  AR4JA codes it cannot exceed the value of 8.

For C2 code, the circulant size is 511 bits. Any value of  $L_a$  parameter other than one would impose very high latency and at the same time require a large number of memory for FIFO and PRCE structures, so it avoided and only the case of  $L_a$ =1 is considered for this code.  $L_m$  parallelism is constant at 16 bits for this encoder.

## 3.2 Components Description

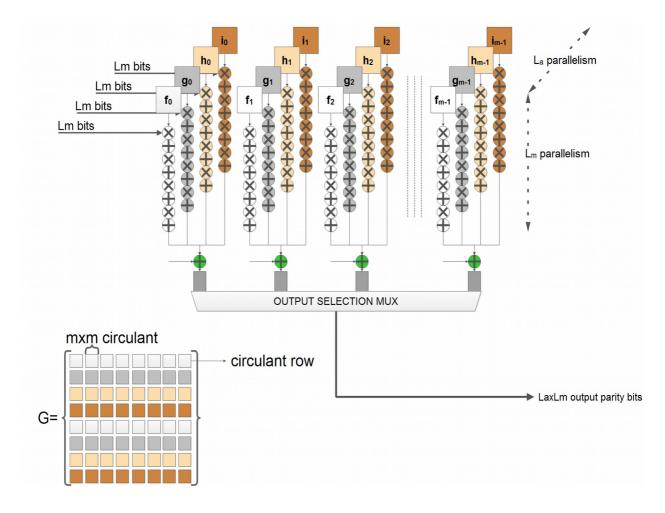

This paragraph describes the implemented encoder a block diagram of which is displayed on fig. 21. The parallel RCE of fig 20 has been incorporated and can be recognized in the figure.

The Control and Buffer unit implements the receiving interface and accumulates incoming data until the necessary amount has arrived for RCE operation to start. For a given value of the L<sub>a</sub> parameter, the parallel RCE of fig. 20 is not able to operate (efficiently) until all the L<sub>a</sub> branches of the PRCE tree have data to process. In particular,  $(L_a-1)m+L_aL_m$  bits need to have arrived to the Control and Buffer unit for the calculation of parity bits to begin. The L<sub>m</sub> bits of the L<sub>a</sub> circulants concurrently being processed by the parallel RCE are applied to it through *s\_feed* signal. The shift registers of the encoder are controlled by two signals issued from the Control Unit: *mac\_en* signal,

which is the clock enable of the corresponding registers and *reset\_prce*, which reinitializes the contents of the registers to all zeros after parity calculation and export of each CADU.

Figure 21: Encoder Block Diagram.

At the same time, incoming information bits form the receiving interface form the systematic part of the CADU. The systematic output, in which the ASM sequence is included, is multiplexed with the parity bits by the MUX at the upper part of the image, to select the output vector.

If randomization has been selected, the bits of the CCSDS pseudo-random sequence generator are XORed with the output of the MUX. The operation of the randomization circuit is controlled by the *rand\_en* signal.

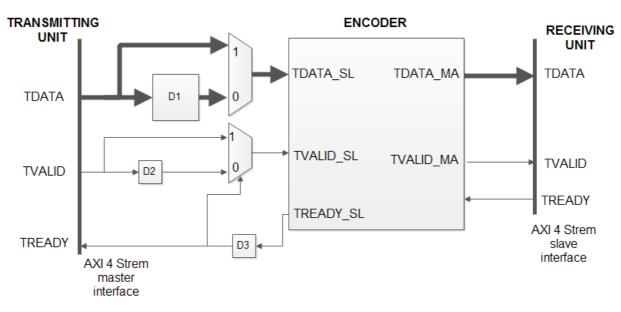

Output data are valid during either the systematic or during parity output where *sys\_valid* and *par\_valid* signals are correspondingly asserted. The master interface validity signal is consequently the result of the OR operation on these signals. Incoming TREADY\_MA signal on the master interface is the clock enable of the output registers of the encoder and is also routed to the Control Unit to halt the operation of the encoder. In fact TREADY\_MA becomes directly (through a gated combinatorial path) the TREADY\_SL signal of the receiving interface, as indicated by the OR gate in the control unit in the above diagram. In cases where the encoder is to be used in an embedded system where this arrangement could significantly jeopardize performance, the circuit of fig. 22 could be used. In applications considered in this work however, no critical paths were presented along this path and the this solution was not necessary.

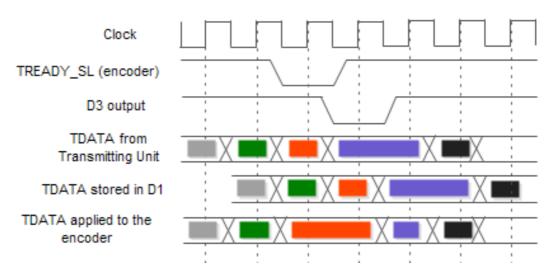

When the encoder is ready, TDATA and TVALID signals from the transmitting unit are selected from the multiplexors. Registers D1, D2 keep the last value of these signals when the output from D3 is asserted. When TREADY\_SL is de-asserted, the values saved by the delay elements D1, D2 are maintained in the registers. During the first cycle after TREADY\_SL assertion, they are provided to the corresponding encoder's inputs. The timing diagram of fig. 23 is an effort to clarify this. Only TDATA is displayed but the timing of TVALID is identical.

Figure 22: A solution to the non-registered output TREADY\_SL

Figure 23: Timing example of the proposed solution

Figure 21 also describes the simplifications allowed in the case where  $L_a$  parameter is 1. In particular, the PARITY MUX can be omitted in that case and  $L_m$  parity bits can be simply shifted out of the shift registers, as described in previous paragraph, to form *parity* signal.

Each FUNCTION COLUMN block in the figure describes m function generators for one branch of the parallel RCE each. For example, regarding Figure 20, all  $f_i$  functions are described by one such block.

The description of the building blocks of the encoder continues with the randomizer and control and buffer units.

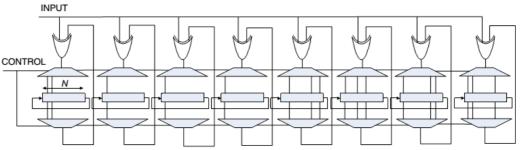

## 3.2.1 RANDOMIZER unit

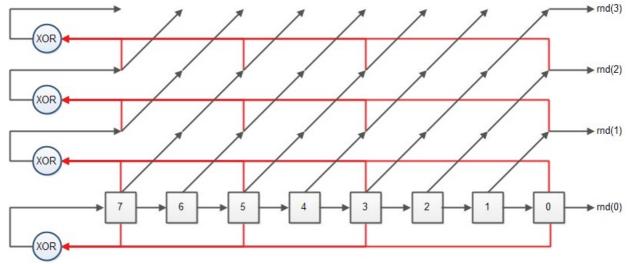

Randomizer unit implements the polynomial mentioned in § 2.4. Since the output of the encoder is not one bit at a time but  $L_a \times L_m$ , a parallel implementation is needed. The solution adopted for this design is displayed on fig. 24.

Figure 24: Implementation of a parallel CCSDS pseudo-random sequence generator.

In the figure, the LFSR at the bottom implements the polynomial, with the output coming from the rightmost register (numbered 0). A number of N bits of the pseudo-random sequence can be obtained if the bit sequence in the LSFR is expanded to an array of N vectors of 8 bit each according to the following algorithm:

- Considering an array of vectors, *lfsr\_array*, the first element of the array (*lfsr\_array(0*)) is the LFSR itself.

- Foreach vector from 1 to N, the bit position i takes the value of the bit position i+1 of the previous vector, except from bit position 0.

- Bit position 0 takes the value of the XOR operation corresponding to the polynomial over the bits of the previous vector.

It is evident that the for the first eight bits of the produced result no additional XOR gates are needed.

### 3.2.2 Control and Buffer Unit: the general case

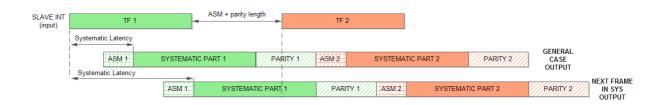

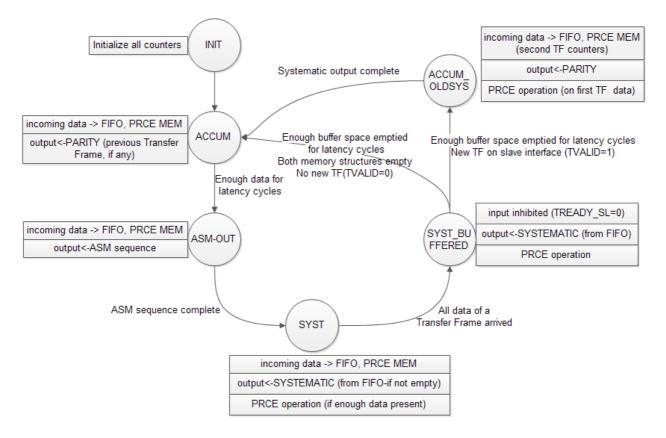

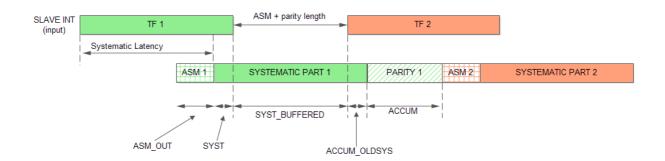

The general case for considered first is the control unit for an encoder with a "reasonable" value of  $L_a>1$ . For such an encoder, the latency introduced by the  $L_a$  parameter is adequately small so that the next TF arrives to the encoder when it (the encoder) outputs the parity bits of the current TF. This is the case depicted on fig. 17 and the corresponding part of fig. 25. Note the difference between the term Latency in fig. 17 and Systematic Latency in fig. 25. The former was introduced during a high level description of the encoder and refers to the latency from receiving unit's perspective, while the latter is the number of cycles it takes to begin the output of the systematic part of the CADU. Systematic Latency is caused by the  $L_a$  parameter and it is the time it takes to accumulate enough data for the operation of all branches of the parallel RCE.

Obviously this latency does not exist for  $L_a=1$ . Also shown in the figure is the case of very high latency, such that the next TF arrives to the encoder while the systematic output of the current TF has not finished. This situation calls for a different FSM of the control unit examined later.

Figure 25: Timing of data on encoder's interfaces for the general and high latency cases

Figure 26: Control and Buffer Unit

Apart from the generation of all control signals for the encoder's operation, the control and buffer unit includes also the necessary memory structures to buffer incoming data on slave interface. The first such structure is a FIFO for the systematic part of the output. Until enough data have gathered for RCE operations for all branches of the parallel RCE, incoming data arriving at the encoder at a rate of  $L_aL_m$  bits in every cycle, are queued in a FIFO for subsequent output. The size of this FIFO is therefore such that all bits arriving during the latent cycles can be stored. Since the Systematic Latency period is  $(L_a-1)(m/L_m)/L_a$  clock cycles, the FIFO should accommodate for this number of words of  $L_aL_m$  bits.

The second memory structure necessary for the Parallel RCE operation rearranges incoming "packets" of  $L_aL_m$  bits into pages of m bits each, where each page contains

input bits referring to the same circulant of the Generator matrix. Due to  $L_a$  parallelism,  $L_m$  inputs bits of  $L_a$  circulants are concurrently processed by the PRCE. Considering uninterrupted operation of the sender, one clock cycle after the  $L_a$ -1 of these pages have been filled with data,  $L_aL_m$  bits for the last page are received by the encoder. This condition fulfills the prerequisites for commencement of RCE operations. For fully pipelined operation however, the double amount of memory is required for the structure to work as a double buffer. In the actual implementation, resource sharing between these two memory structures exploits the same resources for both memories.

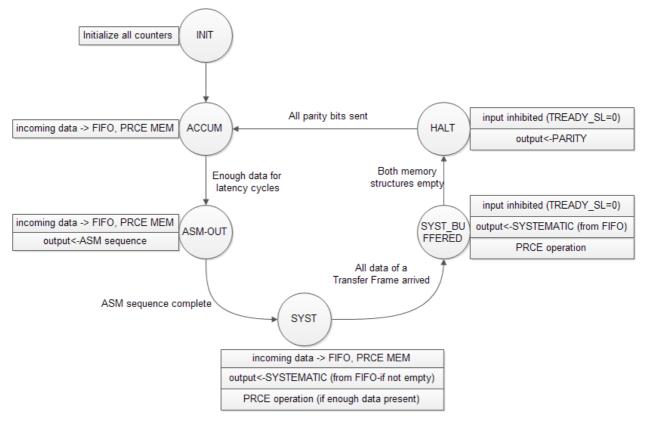

Control signals generation and routing of data to the described memory structures are orchestrated by a FSM. The top-level diagram of the unit with a simplified pictorial representation of its constituent structures is provided on fig. 26, while fig. 27 displays the transition diagram of the FSM. The diagram of fig. 27 does not intend to provide a detailed description of the FSM, but to assist in the better understanding of the functionality of the control unit. All the hardware for the Control and Buffer Unit is described by a FSMD model at a high level of abstraction and amply documented in-line with the code.

Figure 27: Simplified state transition diagram of the FSM of the Control and Buffer Unit

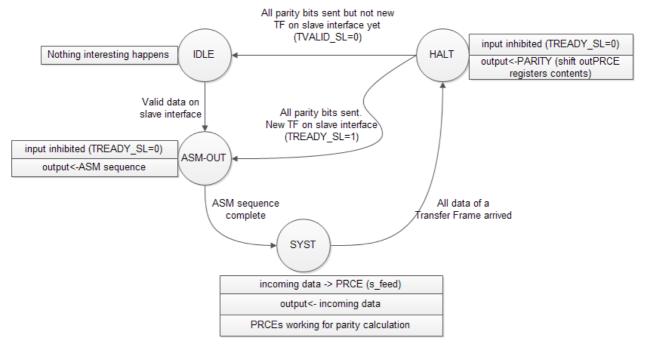

### 3.2.3 Control and Buffer Unit: L<sub>a</sub>=1.