## NATIONAL AND KAPODISTRIAN UNIVERSITY OF ATHENS

#### SCHOOL OF SCIENCES DEPARTMENT OF INFORMATICS AND TELECOMMUNICATIONS

### **PROGRAM OF POSTGRADUATE STUDIES**

PhD THESIS

# Methodologies for Accelerated Analysis of the Reliability and the Energy Efficiency Levels of Modern Microprocessor Architectures

Emmanouil E. Kaliorakis

ATHENS

**MARCH 2018**

## ΕΘΝΙΚΟ ΚΑΙ ΚΑΠΟΔΙΣΤΡΙΑΚΟ ΠΑΝΕΠΙΣΤΗΜΙΟ ΑΘΗΝΩΝ

#### ΣΧΟΛΗ ΘΕΤΙΚΩΝ ΕΠΙΣΤΗΜΩΝ ΤΜΗΜΑ ΠΛΗΡΟΦΟΡΙΚΗΣ ΚΑΙ ΤΗΛΕΠΙΚΟΙΝΩΝΙΩΝ

### ΠΡΟΓΡΑΜΜΑ ΜΕΤΑΠΤΥΧΙΑΚΩΝ ΣΠΟΥΔΩΝ

ΔΙΔΑΚΤΟΡΙΚΗ ΔΙΑΤΡΙΒΗ

# Μεθοδολογίες για την Επιτάχυνση της Ανάλυσης της Αξιοπιστίας και της Ενέργειας Σύγχρονων Αρχιτεκτονικών Μικροεπεξεργαστών

Εμμανουήλ Ε. Καληωράκης

AOHNA

**ΜΑΡΤΙΟΣ 2018**

#### **PhD THESIS**

Methodologies for Accelerated Analysis of the Reliability and the Energy Efficiency Levels of Modern Microprocessor Architectures

#### Emmanouil E. Kaliorakis

ADVISOR: Dimitris Gizopoulos, Professor UoA

#### THREE-MEMBER ADVISORY COMMITTEE:

Dimitris Gizopoulos, Professor UoA Antonis Paschalis, Professor UoA Angeliki Arapoyanni, Professor UoA

#### SEVEN-MEMBER EXAMINATION COMMITTEE

(Signature)

Dimitris Gizopoulos, Professor UoA

(Signature)

Antonis Paschalis,

**Professor UoA**

(Signature)

Ioannis Smaragdakis, Professor UoA

Dionisios Pnevmatikatos, Professor TUC

(Signature)

(Signature)

arakis, essor UniPi

(Signature)

Dimitrios Soudris, Associate Professor NTUA Nectarios Koziris, Professor NTUA

(Signature)

Mihalis Psarakis, Assistant Professor UniPi

Examination Date 02/03/2018

#### ΔΙΔΑΚΤΟΡΙΚΗ ΔΙΑΤΡΙΒΗ

Μεθοδολογίες για την Επιτάχυνση της Ανάλυσης της Αξιοπιστίας και της Ενέργειας Σύγχρονων Αρχιτεκτονικών Μικροεπεξεργαστών

Εμμανουήλ Ε. Καληωράκης

ΕΠΙΒΛΕΠΩΝ ΚΑΘΗΓΗΤΗΣ: Δημήτρης Γκιζόπουλος, Καθηγητής ΕΚΠΑ

#### ΤΡΙΜΕΛΗΣ ΕΠΙΤΡΟΠΗ ΠΑΡΑΚΟΛΟΥΘΗΣΗΣ:

**Δημήτρης Γκιζόπουλος,** Καθηγητής ΕΚΠΑ Αντώνης Πασχάλης, Καθηγητής ΕΚΠΑ Αγγελική Αραπογιάννη, Καθηγήτρια ΕΚΠΑ

### ΕΠΤΑΜΕΛΗΣ ΕΞΕΤΑΣΤΙΚΗ ΕΠΙΤΡΟΠΗ

(Υπογραφή)

#### Δημήτρης Γκιζόπουλος, Καθηγητής ΕΚΠΑ

#### Αντώνης Πασχάλης, Καθηγητής ΕΚΠΑ

(Υπογραφή)

Διονύσιος Πνευματικάτος,

Καθηγητής Πολυτεχνείο Κρήτης

(Υπογραφή)

#### Ιωάννης Σμαραγδάκης, Καθηγητής ΕΚΠΑ

(Υπογραφή)

(Υπογραφή)

#### Μιχάλης Ψαράκης, Επίκουρος Καθηγητής Πα.Πει

(Υπογραφή)

Δημήτριος Σούντρης, Αναπληρωτής Καθηγητής ΕΜΠ

Ημερομηνία εξέτασης 02/03/2018

Νεκτάριος Κοζύρης, Καθηγητής ΕΜΠ

(Υπογραφή)

## ABSTRACT

The evolution in semiconductor manufacturing technology, computer architecture and design leads to increase in performance of modern microprocessors, which is also accompanied by increase in products' vulnerability to errors. Designers apply different techniques throughout microprocessors life-time in order to ensure the high reliability requirements of the delivered products that are defined as their ability to avoid service failures that are more frequent and more severe than is acceptable.

This thesis proposes novel methods to guarantee the high reliability and energy efficiency requirements of modern microprocessors that can be applied during the early design phase, the manufacturing phase or after the chips release to the market. The contributions of this thesis can be grouped in the two following categories according to the phase of the CPUs lifecycle that are applied at:

• Early design phase: Statistical fault injection using microarchitectural structures modeled in performance simulators is a state-of-the-art method to accurately measure the reliability, but suffers from low simulation throughput. In this thesis, we firstly present a novel fully-automated versatile microarchitecture-level fault injection framework (called MaFIN) for accurate characterization of a wide range of hardware components of an x86-64 microarchitecture with respect to various fault models (transient, intermittent, permanent faults). Next, using the same tool and focusing on transient faults, we present several reliability and performance related studies that can assist design decision in the early design phases.

Moreover, we propose two methodologies to accelerate the statistical fault injection campaigns. In the first one, we accelerate the fault injection campaigns after the actual injection of the faults in the simulated hardware structures. In the second, we further accelerate the microarchitecture level fault injection campaigns by proposing MeRLiN a fault pre-processing methodology that is based on the pruning of the initial fault list by grouping the faults in equivalent classes according to the instruction access patterns to hardware entries.

• Manufacturing phase and release to the market: The contributions of this thesis in these phases of microprocessors life-cycle cover two important aspects. Firstly, using the 48-core Intel's SCC architecture, we propose a technique to accelerate online error detection of permanent faults for many-core architectures by exploiting their high-speed message passing on-chip network. Secondly, we propose a comprehensive statistical analysis methodology to accurately predict at the system level the safe voltage operation margins of the ARMv8 cores of the X-Gene 2 chip when it operates in scaled voltage conditions.

**SUBJECT AREA**: Computer Architecture

**KEYWORDS**: Dependability, Reliability, Transient Faults, Permanent Faults, Energy Efficiency, Statistical Analysis

### ΠΕΡΙΛΗΨΗ

Η εξέλιξη της τεχνολογίας ημιαγωγών, της αρχιτεκτονικής υπολογιστών και της σχεδίασης οδηγεί σε αύξηση της απόδοσης των σύγχρονων μικροεπεξεργαστών, η οποία επίσης συνοδεύεται από αύξηση της ευπάθειας των προϊόντων. Οι σχεδιαστές εφαρμόζουν διάφορες τεχνικές κατά τη διάρκεια της ζωής των ολοκληρωμένων κυκλωμάτων με σκοπό να διασφαλίσουν τα υψηλά επίπεδα αξιοπιστίας των παραγόμενων προϊόντων και να τα προστατέψουν από διάφορες κατηγορίες σφαλμάτων διασφαλίζοντας την ορθή λειτουργία τους.

Αυτή η διδακτορική διατριβή προτείνει καινούριες μεθόδους για να διασφαλίσει τα υψηλά επίπεδα αξιοπιστίας και ενεργειακής απόδοσης των σύγχρονων μικροεπεξεργαστών οι οποίες μπορούν να εφαρμοστούν κατά τη διάρκεια του πρώιμου σχεδιαστικού σταδίου, του σταδίου παραγωγής ή του σταδίου της κυκλοφορίας των ολοκληρωμένων κυκλωμάτων στην αγορά. Οι συνεισφορές αυτής της διατριβής μπορούν να ομαδοποιηθούν στις ακόλουθες δύο κατηγορίες σύμφωνα με το στάδιο της ζωής των μικροεπεξεργαστών στο οποίο εφαρμόζονται:

Πρώιμο σχεδιαστικό στάδιο: Η στατιστική εισαγωγή σφαλμάτων σε δομές που είναι μοντελοποιημένες σε προσομοιωτές οι οποίοι στοχεύουν στην μελέτη της απόδοσης είναι μια επιστημονικά καθιερωμένη μέθοδος για την ακριβή μέτρηση της αξιοπιστίας, αλλά υστερεί στον αργό χρόνο εκτέλεσης. Σε αυτή τη διατριβή, αρχικά παρουσιάζουμε ένα νέο πλήρως αυτοματοποιημένο εργαλείο εισαγωγής σφαλμάτων σε μικροαρχιτεκτονικό επίπεδο που στοχεύει στην ακριβή αξιολόγηση της αξιοπιστίας ενός μεγάλου πλήθους μονάδων υλικού σε σχέση με διάφορα μοντέλα σφαλμάτων (παροδικά, διακοπτόμενα, μόνιμα σφάλματα). Στη συνέχεια, χρησιμοποιώντας το ίδιο εργαλείο και στοχεύοντας τα παροδικά σφάλματα, παρουσιάζουμε διάφορες μελέτες σχετιζόμενες με την αξιοπιστία και την απόδοση, οι οποίες μπορούν να βοηθήσουν τις σχεδιαστικές αποφάσεις στα πρώιμα στάδια της ζωής των επεξεργαστών.

Τελικά, προτείνουμε δύο μεθοδολογίες για να επιταχύνουμε τα μαζικά πειράματα στατιστικής εισαγωγής σφαλμάτων. Στην πρώτη, επιταχύνουμε τα πειράματα έπειτα από την πραγματική εισαγωγή των σφαλμάτων στις δομές του υλικού. Στη δεύτερη, επιταχύνουμε ακόμη περισσότερο τα πειράματα προτείνοντας τη μεθοδολογία με όνομα MeRLiN, η οποία βασίζεται στη μείωση της αρχικής λίστας σφαλμάτων μέσω της ομαδοποίησής τους σε ισοδύναμες ομάδες έπειτα από κατηγοριοποίηση σύμφωνα με την εντολή που τελικά προσπελαύνει τη δομή που φέρει το σφάλμα.

Παραγωγικό στάδιο και στάδιο κυκλοφορίας στην αγορά: Οι συνεισφορές αυτής της διδακτορικής διατριβής σε αυτά τα στάδια της ζωής των μικροεπεξεργαστών καλύπτουν δύο σημαντικά επιστημονικά πεδία. Αρχικά, χρησιμοποιώντας το ολοκληρωμένο κύκλωμα των 48 πυρήνων με ονομασία Intel SCC, προτείνουμε μια τεχνική επιτάχυνσης του εντοπισμού μονίμων σφαλμάτων που εφαρμόζεται κατά τη διάρκεια λειτουργίας αρχιτεκτονικών με πολλούς πυρήνες, η οποία εκμεταλλεύεται το δίκτυο υψηλής ταχύτητας μεταφοράς μηνυμάτων που διατίθεται στα ολοκληρωμένα κυκλώματα αυτού του είδους. Δεύτερον, προτείνουμε μια λεπτομερή στατιστική μεθοδολογία με σκοπό την ακριβή πρόβλεψη σε επίπεδο συστήματος των ασφαλών ορίων λειτουργίας της τάσης των πυρήνων τύπου ARMv8 που βρίσκονται πάνω στη CPU X-Gene 2.

#### ΘΕΜΑΤΙΚΗ ΠΕΡΙΟΧΗ: Αρχιτεκτονική Υπολογιστών

**ΛΕΞΕΙΣ ΚΛΕΙΔΙΑ**: Αξιοπιστία, Φερεγγυότητα, Παροδικά Σφάλματα, Μόνιμα Σφάλματα, Ενεργειακή Απόδοση, Στατιστική Ανάλυση

Στην Άννα.

### ACKNOWLEDGEMENTS

I would like to thank my advisor, Professor Dimitris Gizopoulos, who gave me the opportunity to work in very interesting research topics and projects of computer architecture, while he advised me throughout these years. His guidance and encouragement especially in times of failure have been invaluable to the conduction of my dissertation. The interaction with Professor Dimitris Gizopoulos provided me with several knowledge and skills that would be very helpful in my future career and life.

I also like to thank all my collaborators throughout these years and especially all the members of Computer Architecture Lab of University of Athens with whom I shared the good and the bad moments in the lab. I learned a lot from them, hoping the same for them. I also want to thank Dr. Shidhartha Das from ARM Ltd. in Cambridge for his hospitality and his guidance during my three-month PhD internship in UK.

Especially, I would also like to thank my family and my friends who always stand by me. Finally, I would like to thank Anna who encouraged me in the times of failure and celebrated my successes, while she always shows me the way to become a better man. I am grateful for her support and I would like to dedicate my dissertation to her.

# LIST OF PUBLICATIONS

#### Peer reviewed conferences:

- G.Papadimitriou, A.Chatzidimitriou, M.Kaliorakis, Y.Vastakis, D.Gizopoulos, "Micro-Viruses for fast system-level voltage margins characterization in multicore CPUs", IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS), 2018.

- G.Karakonstantis, K.Tovletoglou, L.Mukhanov, H.Vandierendonck, D.S.Nikolopoulos, P.Lawthers, P.Koutsovasilis, M.Maroudas, C.D.Antonopoulos, C.Kalogirou, N.Bellas, S.Lalis, S.Venugopal, A.Prat-Perez, A.Lampropulos, M.Kleanthous, A.Diavastos, Z.Hadjilambrou, P.Nikolaou, Y.Sazeides, P.Trancoso, G.Papadimitriou, M.Kaliorakis, A.Chatzidimitriou, D.Gizopoulos, S.Das, "An energy-efficient and error-resilient server ecosystem exceeding conservative scaling limits", IEEE/ACM Design, Automation & Test in Europe Conference (DATE), 2018.

- G.Papadimitriou, M.Kaliorakis, A.Chatzidimitriou, D.Gizopoulos, P.Lawthers, S.Das, "Harnessing voltage margins for energy efficiency in multicore CPUs", IEEE/ACM International Symposium on Microarchitecture (**MICRO**), 2017.

- G.Papadimitriou, M.Kaliorakis, A.Chatzidimitriou, C.Magdalinos, D.Gizopoulos, "Voltage margins identification on commercial x86-64 multicore microprocessors", IEEE International On-Line Testing Symposium (IOLTS), 2017.

- A.Chatzidimitriou, M.Kaliorakis, D.Gizopoulos, M.Pipponzi, R.Mariani, S.Di Carlo, "RT Level vs. microarchitecture level reliability assessment: case study on ARM Cortex-A9 CPU", IEEE/IFIP International Conference on Dependable Systems and Networks (**DSN**), 2017.

- M.Kaliorakis, D.Gizopoulos, R.Canal, A.Gonzalez, "MeRLiN: Exploiting dynamic instruction behavior for fast and accurate microarchitecture level reliability assessment", ACM/IEEE International Symposium on Computer Architecture (ISCA), 2017.

- A.Chatzidimitriou, M.Kaliorakis, S.Tselonis, D.Gizopoulos, "Performance-aware reliability assessment of heterogeneous chips", IEEE VLSI Test Symposium (VTS), 2017.

- A.Vallero, A.Savino, G.Politano, S.Di Carlo, A.Chatzidimitriou, S.Tselonis, M.Kaliorakis, D.Gizopoulos, M.R.Villanueva, R.Canal, A.Gonzalez, M.Kooli, A.Bosio, G.Di Natale, "Cross-Layer system reliability assessment framework for hardware faults", IEEE International Test Conference (ITC), 2016.

- S.Tselonis, M.Kaliorakis, N.Foutris, G.Papadimitriou, D.Gizopoulos, "Microprocessor reliability-performance tradeoffs assessment at the microarchitecture level", IEEE VLSI Test Symposium (**VTS**), 2016.

- M.Kaliorakis, S.Tselonis, A.Chatzidimitriou, D.Gizopoulos, "Accelerated microarchitectural fault injection-based reliability assessment", IEEE International Symposium on Defect and Fault Tolerance in VLSI Systems (**DFTS**), 2015.

- M.Kaliorakis, S.Tselonis, A.Chatzidimitriou, N.Foutris, D.Gizopoulos, "Differential fault injection on microarchitectural simulators", IEEE International Symposium on Workload Characterization (**IISWC**), 2015.

- A.Vallero, A.Savino, S.Tselonis, N.Fourtis, M.Kaliorakis, G.Politano, D.Gizopoulos, S.Di Carlo, "Bayesian network early reliability evaluation analysis for both permanent and transient faults", IEEE International On-Line Testing Symposium (IOLTS), 2015.

- A.Vallero, A.Savino, S.Tselonis, N.Fourtis, M.Kaliorakis, G.Politano, D.Gizopoulos, S.Di Carlo, "A bayesian model for system level reliability estimation", IEEE European Test Symposium (ETS), 2015.

- N.Foutris, M.Kaliorakis, S.Tselonis, D.Gizopoulos, "Versatile architecture-level fault injection framework for reliability evaluation: a first report", IEEE International On-Line Testing Symposium (**IOLTS**), 2014.

- M.Kaliorakis, M.Psarakis, N.Foutris, D.Gizopoulos, "Accelerated online error detection in many-core microprocessor architectures", IEEE VLSI Test Symposium (VTS), 2014.

- M.Kaliorakis, N.Foutris, D.Gizopoulos, M.Psarakis, "Online error detection in multiprocessor chips: A test scheduling study", IEEE International On-Line Testing Symposium (IOLTS), 2013.

#### Peer reviewed journals:

- M.Kaliorakis, A.Chatzidimitriou, G.Papadimitriou, D.Gizopoulos, "Statistical analysis of multicore CPUs operation in scaled voltage conditions", IEEE Computer Architecture Letters (CAL), Jan. 2018.

- A.Vallero, S.Tselonis, N.Foutris, M.Kaliorakis, M.Kooli, A.Savino, G.Politano, A.Bosio, G.Di Natale, D.Gizopoulos, S.Di Carlo, "Cross-layer reliability evaluation, moving from the hardware architecture to the system level: a CLERECO EU Project overview", Journal of Microprocessors and Microsystems, June 2015.

#### Peer reviewed conferences/workshops with informal proceedings:

- G.Papadimitriou, M.Kaliorakis, A.Chatzidimitriou, D.Gizopoulos, G.Favor, K.Sankaran, S.Das, "A system-level voltage/frequency scaling characterization framework for multicore CPUs", IEEE Workshop on Silicon Errors in Logic - System Effects (SELSE), 2017.

- K.Tovletoglou, C.Chalios, G.Karakonstantis, L.Mukhanov, H.Vandierendonck, • D.S.Nikolopoulos, P.Koutsovasilis, M.Maroudas, C.Antonopoulos, C.Kalogirou, N.Bellas. S.Lalis. M.M.Rafique, S.Venugopal, A.Prat-Perez, A.Diavastos. Y.Sazeides. Z.Hadjilambrou, P.Nikolaou, P.Trancoso, G.Papadimitriou, M.Kaliorakis, A.Chatzidimitriou D.Gizopoulos, "An energy-efficient and error-resilient server ecosystem exceeding conservative scaling limits", Workshop on Energyefficient Servers for Cloud and Edge Computing (EnESCE), in conjunction with HiPEAC 2017.

- A.Vallero, A.Savino, G.Politano, S.Di Carlo, A.Chatzidimitriou, S.Tselonis, M.Kaliorakis, D.Gizopoulos, M.Riera, R.Canal, A.Gonzalez, M.Kooli, A.Bosio, G.Di Natale, "Early component-based system reliability analysis for approximate computing systems", 2nd Workshop On Approximate Computing (WAPCO) in conjunction with HiPEAC, 2016.

- M.Kaliorakis, D.Gizopoulos, "Ensuring dependability of modern computing systems", 11th International Summer School on Advanced Computer Architecture and Compilation for High-Performance and Embedded Systems (HiPEAC ACACES), 2015.

- M.Kaliorakis, M.Psarakis, N.Foutris, D.Gizopoulos, "Parallelizing online error detection in many-core microprocessor architectures", Joint Euro-TM/Median Workshop on Dependable Multicore and Transactional Memory Systems (DMTM) in conjunction with HiPEAC, 2014.

## ΣΥΝΟΠΤΙΚΗ ΠΑΡΟΥΣΙΑΣΗ ΔΙΔΑΚΤΟΡΙΚΗΣ ΔΙΑΤΡΙΒΗΣ

Η εξέλιξη της τεχνολογίας κατασκευής ημιαγωγικών κυκλωμάτων και της αρχιτεκτονικής και σχεδίασης υπολογιστών δίνει στους σχεδιαστές ολοκληρωμένων κυκλωμάτων την ευκαιρία να ενισχύσουν την απόδοση (performance) των σύγχρονων υπολογιστικών συστημάτων τα οποία χρησιμοποιούνται σε διάφορους τομείς της πληροφορικής και των τηλεπικοινωνιών. Οι σχεδιαστές υπολογιστών μπορούν να βελτιώσουν την υπολογιστική απόδοση χρησιμοποιούντας πιο πολύπλοκες πολιτικές λειτουργίας των επεξεργαστών, καθώς η τεχνολογία ημιαγωγών μειώνει το μέγεθος των τρανζίστορ δίνοντας έτσι τη δυνατότητα ολοκλήρωσης όλο και περισσότερων τρανζίστορ πάνω στο ίδιο κύκλωμα. Έτσι από την μια πλευρά, η εξέλιξη της τεχνολογίας ημιαγωγών και της αρχιτεκτονικής υπολογιστών κάνει τους υπολογιστές όλο και πιο αποδοτικούς ως προς τις επιδόσεις, αλλά από την άλλη πλευρά τους κάνει όλο και πιο σύνθετους.

Όμως, αυτή η αύξηση σε απόδοση συνοδεύεται και από αύξηση στην ευπάθεια (ή αντίστοιχα μείωση στην αξιοπιστία) των επεξεργαστών καθώς η ποιότητα των προϊόντων περιορίζεται εξαιτίας: (α) των αυστηρών χρονοδιαγραμμάτων τα οποία ορίζονται για να μειωθεί ο χρόνος που απαιτείται μέχρι το προϊόν να κυκλοφορήσει στην αγορά (άρα και ο χρόνος για τον έλεγχο της αξιοπιστίας του), (β) των σύγχρονων τεχνικών κατασκευής ολοκληρωμένων κυκλωμάτων όλο και μικρότερης κλίμακας (κάνοντάς τα όλο και πιο ευάλωτα στην ακτινοβολία και πιο επιρρεπή σε κατασκευαστικές ατέλειες), και (γ) της αυξημένης πολυπλοκότητας του σχεδίου των κυκλωμάτων (κάνοντας σε πολλές περιπτώσεις τον έλεγχο ορθής λειτουργίας τους σε εύλογο χρονικό διάστημα πολύ δύσκολο). Ειδικότερα, οι σύγχρονοι μικροεπεξεργαστές αντιμετωπίζουν σοβαρά προβλήματα αξιοπιστίας κατά τη διάρκεια της ζωής τους εξαιτίας: (i) των σφαλμάτων που προέρχονται από την κοσμική ακτινοβολία και από τα φορτισμένα ηλεκτρικά σωματίδια που βάλλουν τα κυκλώματα ακόμα και στο επίπεδο της θάλασσας, (ii) της γήρανσης και φθοράς των κυκλωμάτων με την πάροδο του χρόνου, και (iii) των κατασκευαστικών ατελειών που δημιουργούνται κατά την παραγωγή των ολοκληρωμένων κυκλωμάτων. Κάποιες από αυτές τις κατασκευαστικές αστοχίες που κάνουν ακόμα και κυκλώματα που θεωρητικά είναι κατασκευασμένα να λειτουργούν υπό τις ίδιες συνθήκες τάσης τελικά να λειτουργούν ορθά κάτω από διαφορετικές συνθήκες, συνήθως ωθούν τους κατασκευαστές ολοκληρωμένων κυκλωμάτων στην υιοθέτηση απαισιόδοξων ορίων τάσης λειτουργίας, τα οποία κατ' επέκταση θυσιάζουν την ενεργειακή απόδοση των προϊόντων.

Για τους παραπάνω λόγους οι σχεδιαστές χρειάζεται να διασφαλίσουν υψηλά επίπεδα αξιοπιστίας και ενεργειακής απόδοσης των ολοκληρωμένων κυκλωμάτων πριν αυτά διοχετευθούν στην αγορά. Ο σκοπός αυτής της διδακτορικής διατριβής είναι να προτείνει νέες τεχνικές που εφαρμόζονται σε διαφορετικές φάσεις της διάρκειας ζωής των ολοκληρωμένων κυκλωμάτων με σκοπό την επίλυση σημαντικών προβλημάτων ως προς την αξιοπιστία και την ενεργειακή απόδοση των προϊόντων μικροεπεξεργαστών. Γενικά, η ζωή των ολοκληρωμένων κυκλωμάτων διακρίνεται στα ακόλουθα στάδια: (α) το πρώιμο σχεδιαστικό στο οποίο καθορίζονται οι απαιτήσεις του κυκλώματος στους τομείς της απόδοσης, της αξιοπιστίας και της κατανάλωσης ενέργειας, (β) το στάδιο του σχεδιασμού στο οποίο οι σχεδιαστές υλοποιούν με γλώσσες περιγραφής υλικού το κύκλωμα σύμφωνα με τις απαιτήσεις του προηγούμενου σταδίου, (γ) το στάδιο της παραγωγής στο οποίο αρχικά φτιάχνεται ένας μικρός αριθμός από κυκλώματα και μετά την επιτυχημένη αξιολόγησή τους συνεχίζεται η μαζική παραγωγή κυκλωμάτων, και (δ) το στάδιο κατά το οποίο τα κυκλώματα διοχετεύονται στην αγορά. Να σημειώσουμε ότι στο τελευταίο στάδιο της ζωής των ολοκληρωμένων κυκλωμάτων οι σχεδιαστές δεν έχουν πλέον φυσική επαφή με τα κυκλώματα και κατ' επέκταση πρέπει από τα προηγούμενα στάδια να διασφαλίσουν την υψηλή ποιότητα των προϊόντων ως προς την απόδοση, την αξιοπιστία και την ενεργειακή κατανάλωση.

Οι τεχνικές που προτείνονται σε αυτή τη διδακτορική διατριβή μπορούν να εφαρμοστούν κατά τη διάρκεια του πρώιμου σχεδιαστικού σταδίου (α), του σταδίου παραγωγής (γ) ή του σταδίου της κυκλοφορίας των ολοκληρωμένων κυκλωμάτων στην αγορά (δ). Στη συνέχεια παρουσιάζουμε συνοπτικά τις συνεισφορές της διατριβής αυτής ανάλογα με το στάδιο της ζωής των ολοκληρωμένων κυκλωμάτων στο οποίο εφαρμόζονται.

Πρώιμο σχεδιαστικό στάδιο: Ένα πολύ σημαντικό βήμα κατά τη διάρκεια των • πρώτων σταδίων της σχεδίασης των ολοκληρωμένων κυκλωμάτων είναι η εκτίμηση της αξιοπιστίας του κυκλώματος ως προς τα παροδικά σφάλματα (transient faults) που είναι πιθανόν να επηρεάσουν την ορθή λειτουργία των κυκλωμάτων. Οι απαιτήσεις ως προς της αξιοπιστία και την απόδοση καθορίζουν σχεδιαστικές αποφάσεις που εφαρμόζονται στα επόμενα στάδια της της ζωής των ολοκληρωμένων κυκλωμάτων, όπως είναι για παράδειγμα η ενσωμάτωση μηχανισμών στο κύκλωμα για την προστασία από τέτοιου είδους σφάλματα ή ακόμα και ο καθορισμός συγκεκριμένων μικροαρχιτεκτονικών παραμέτρων (π.χ. μέγεθος μικροαρχιτεκτονικών δομών και πολιτικών κλπ.) που μπορούν να επηρεάσουν τόσο την αξιοπιστία όσο και την απόδοση. Η ακριβής εκτίμηση της ανθεκτικότητας (ή αντίστροφα της ευπάθειας) των κυκλωμάτων ως προς αυτά τα σφάλματα είναι ζωτικής σημασίας για να αποφευχθεί κάποια οικονομική καταστροφή για την εταιρία κατασκευής τους σε περίπτωση που το πρόβλημα παρουσιαστεί αφού κυκλοφορήσει το προϊόν στην αγορά ή για να εξοικονομηθούν χρήματα, κόπος και τμήμα από τη διαθέσιμη συνολική επιφάνεια του ολοκληρωμένου κυκλώματος που μπορεί να σπαταληθεί στην υλοποίηση κάποιου μηχανισμού προστασίας που στην πραγματικότητα δεν είναι Για αυτούς τους λόγους, απαραίτητος. OI εταιρίες κατασκευής μικροεπεξεργαστών δίνουν ιδιαίτερη βαρύτητα σε αυτό το πρώιμο σχεδιαστικό στάδιο αξιολόγησης της αξιοπιστίας των κυκλωμάτων.

Η στατιστική εισαγωγή παροδικών σφαλμάτων (statistical fault injection) σε δομές που είναι μοντελοποιημένες σε προσομοιωτές οι οποίοι στοχεύουν στην μελέτη της απόδοσης (performance simulators) είναι μια επιστημονικά καθιερωμένη μέθοδος για την ακριβή μέτρηση της αξιοπιστίας, αλλά υστερεί στον αργό χρόνο εκτέλεσης. Η στατιστική εισαγωγή παροδικών σφαλμάτων μοντελοποιείται στους προσομοιωτές αυτούς με την τροποποίηση της πραγματικής τιμής ενός bit μιας δομής υλικού όπως για παράδειγμα η στιγμιαία αλλαγή της τιμής ενός bit σε ένα αρχείο καταχωρητών ή σε κάποια κρυφή μνήμη.

Η διδακτορική διατριβή παρουσιάζει διάφορες συνεισφορές στο επιστημονικό πεδίο που σχετίζεται με την αξιολόγηση της αξιοπιστίας των μονάδων υλικού στο πρώιμο σχεδιαστικό στάδιο των ολοκληρωμένων κυκλωμάτων. Αρχικά, με την εργασία [27] παρουσιάζουμε ένα νέο πλήρως αυτοματοποιημένο εργαλείο εισαγωγής σφαλμάτων σε μικροαρχιτεκτονικό επίπεδο (με την ονομασία MaFIN) που στοχεύει στην ακριβή αξιολόγηση της αξιοπιστίας ενός μεγάλου πλήθους μονάδων υλικού της μικροαρχιτεκτονικής x86-64, σε σχέση με διάφορα μοντέλα σφαλμάτων (παροδικά, διακοπτόμενα, μόνιμα σφάλματα). Για την ρεαλιστικότερη μοντελοποίηση της λειτουργίας των κυκλωμάτων και την ακριβή μέτρηση της αξιοπιστίας χρειάστηκε να ενσωματωθούν στον μικροαρχιτεκτονικό προσομοιωτή που χρησιμοποιήθηκε τα πεδία των δεδομένων σε όλες τις κρυφές μνήμες. Να σημειώσουμε ότι οι προσομοιωτές απόδοσης (performance simulators) είναι κατασκευασμένοι αποκλειστικά για το σκοπό αυτό με χρήση γλωσσών προγραμματισμού υψηλού επιπέδου όπως η C/C++ και κάποιες λειτουργίες που δεν επηρεάζουν τις μετρήσεις ως προς την απόδοση παραλείπονται ή μοντελοποιούνται με τέτοιο τρόπο ώστε να επιταχύνεται ο χρόνος της

προσομοίωσης. Η ανάπτυξη του εργαλείου που χρησιμοποιείται για την ακριβή αξιολόγηση τόσο της αξιοπιστίας όσο και της απόδοσης στα πρώτα στάδια μελέτης αυτής της επιστημονικής περιοχής ήταν απαραίτητη καθώς τέτοιου είδους εργαλεία δεν υπάρχουν δημοσίως διαθέσιμα. Στη συνέχεια, χρησιμοποιώντας το ίδιο εργαλείο και στοχεύοντας τα παροδικά σφάλματα, παρουσιάζουμε δύο διαφορετικές μελέτες σχετιζόμενες με την αξιοπιστία και την απόδοση, οι οποίες μπορούν να βοηθήσουν τις αποφάσεις των σχεδιαστών ολοκληρωμένων κυκλωμάτων στα πρώιμα σχεδιαστικά στάδια.

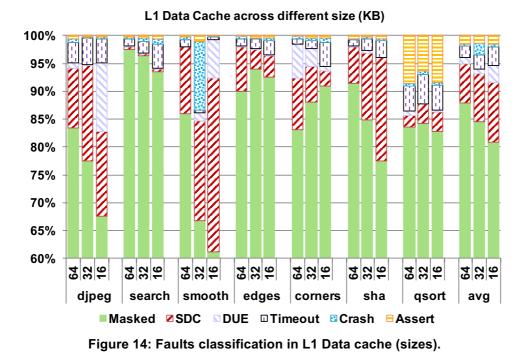

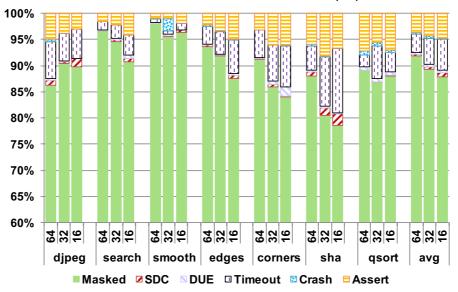

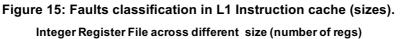

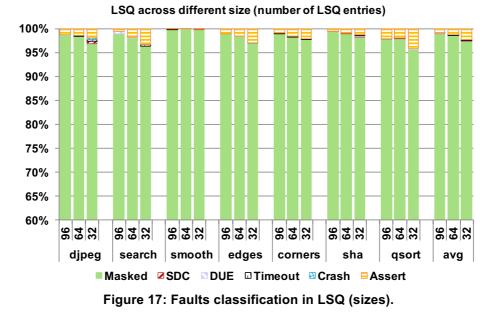

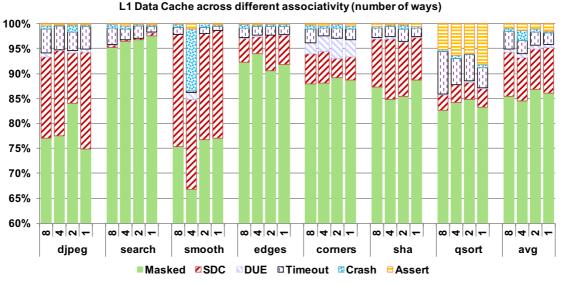

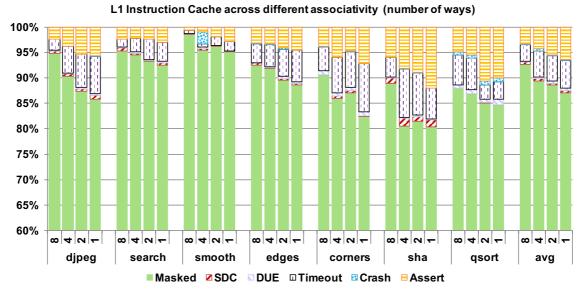

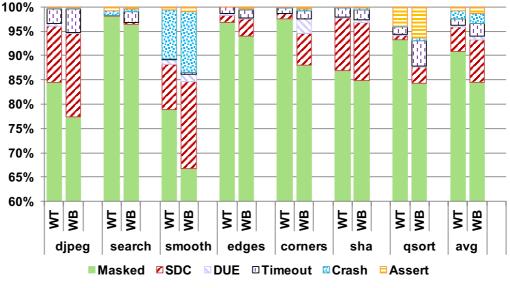

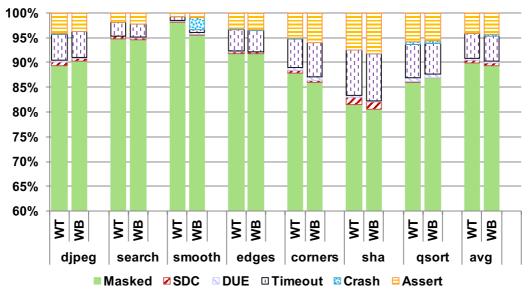

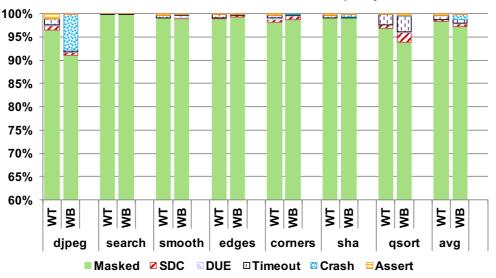

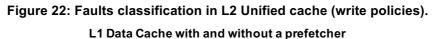

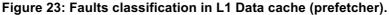

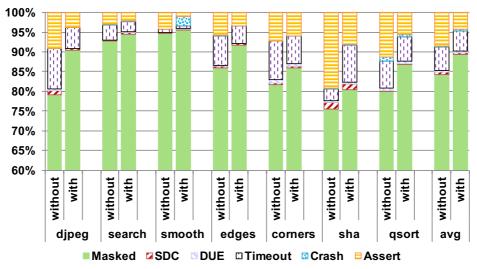

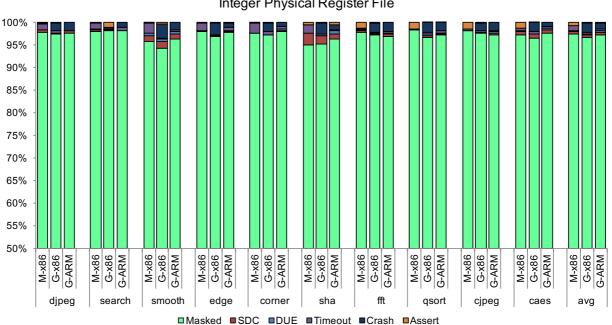

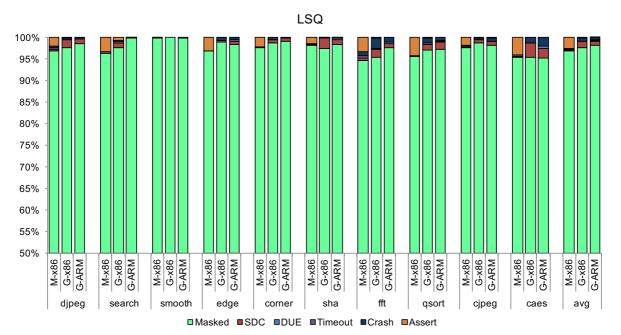

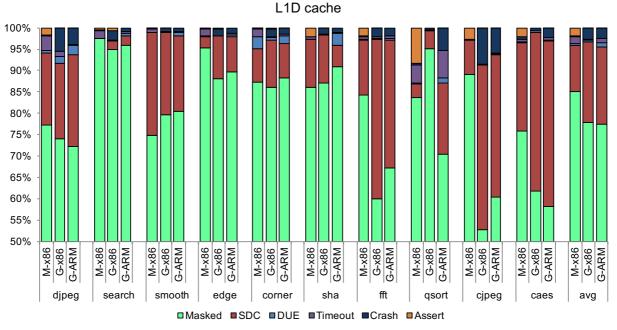

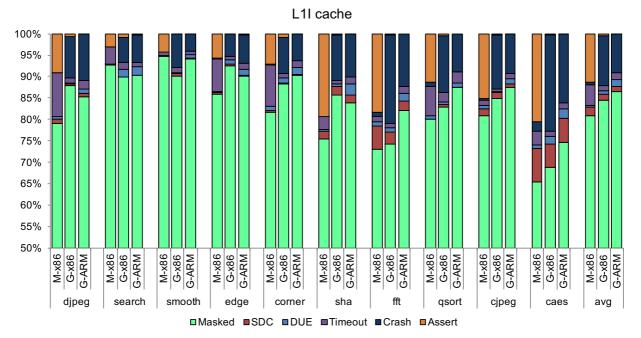

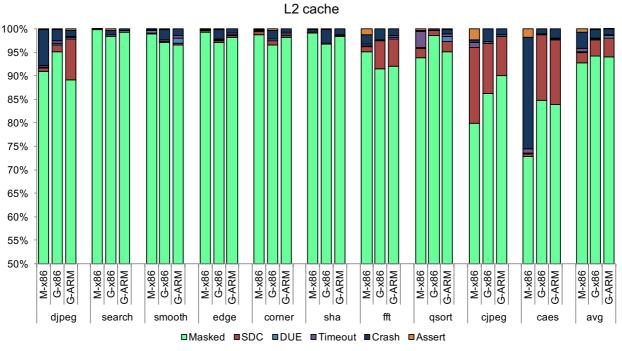

Στην πρώτη μελέτη [28], αξιολογούμε την στενή σύνδεση αξιοπιστίας και απόδοσης σε μια μικροαρχιτεκτονική x86-64 μεταβάλλοντας τις σχεδιαστικές παραμέτρους σημαντικών μονάδων του υλικού του μικροεπεξεργαστή. Συγκεκριμένα, πειραματιζόμαστε με το μέγεθος του αρχείου φυσικών ακεραίων καταχωρητών (physical integer register file), με τις κρυφές μνήμες πρώτου και δεύτερου επιπέδου (L1 Instruction cache, L1 Data cache, L2 cache) και με την φόρτωσης/αποθήκευσης (load/store queue) και **3**μύοιοποποστ ουρά παραμέτρους όπως το μέγεθος όλων των δομών, την πολιτική εγγραφής (write policy) των κρυφών μνημών, το είδος συσχετιστικότητας των κρυφών μνημών (cache associativity) και την ύπαρξη ή όχι κυκλωμάτων εκ των προτέρων προσκόμισης (prefetchers) στις κρυφές μνήμες πρώτου επιπέδου. Στη συγκεκριμένη μελέτη, για το συγκερασμό των μετρήσεων απόδοσης και αξιοπιστίας προτείνουμε μια νέα συνάρτηση (με την ονομασία fitness function). Τα αποτελέσματα αυτής της μελέτης μπορούν να καθοδηγήσουν σχεδιαστικές αποφάσεις σχετικά με την αξιοπιστία και την απόδοση των πραγματικών μονάδων υλικού των μικροεπεξεργαστών.

Στη δεύτερη μελέτη [29], χρησιμοποιούμε τον MaFIN μαζί με ένα άλλο εργαλείο μέτρησης της αξιοπιστίας των μονάδων υλικού σε μικροαρχιτεκτονικό επίπεδο (με την ονομασία GeFIN [30]) με σκοπό να αξιολογήσουμε: (α) την ευαισθησία ως προς την αξιοπιστία διάφορων μικροαρχιτεκτονικών δομών του ίδιου αρχιτεκτονικού συνόλου εντολών (ISA x86-64) που είναι υλοποιημένα σε διαφορετικούς μικροαρχιτεκτονικούς προσομοιωτές, και (β) την ευαισθησία ως προς την αξιοπιστία μεταξύ δύο διαφορετικών αρχιτεκτονικών συνόλου εντολών (ARM και x86-64). Η μελέτη αυτή αποκάλυψε πολύ ενδιαφέροντα συμπεράσματα για τα χαρακτηριστικά των εργαλείων που χρησιμοποιούνται στις μελέτες αξιολόγησης της αξιοπιστίας και μπορούν να επηρεάσουν τις μετρήσεις, καθώς και τις μικροαρχιτεκτονικές διαφορές και τις παραμέτρους των αρχιτεκτονικών συνόλου εντολών (ISA) που επηρεάζουν την αξιοπιστία. Είναι η πρώτη φορά που καταγράφεται μια μελέτη αυτού του είδους και τα συμπεράσματά της μπορούν να βοηθήσουν τους αρχιτέκτονες υπολογιστών στην επιλογή των εργαλείων για την αξιολόγηση της αξιοπιστίας, στην επιλογή της καταλληλότερης αρχιτεκτονικής συνόλου εντολών, στην επιλογή της καταλληλότερης υλοποίησης μια δομής υλικού σε μικροαρχιτεκτονικό επίπεδο και στην επιλογή των κατάλληλων μηχανισμών προστασίας που χρειάζεται να προστεθούν με τελικό σκοπό να επιτευχθούν οι υψηλοί στόχοι αξιοπιστίας των προϊόντων που τίθενται στα πρώιμα σχεδιαστικά στάδια.

Μια μεγάλη πρόκληση για την αξιολόγηση της αξιοπιστίας των μονάδων υλικού ενάντια σε παροδικά σφάλματα σε μικροαρχιτεκτονικό επίπεδο χρησιμοποιώντας στατιστική εισαγωγή σφαλμάτων είναι ότι τα μαζικά πειράματα που τελικά εξασφαλίζουν εκτιμήσεις αξιοπιστίας υψηλής στατιστικής ακρίβειας είναι εξαιρετικά χρονοβόρα. Στη διδακτορική διατριβή παρουσιάζουμε δύο μελέτες για να επιταχύνουμε τα μαζικά πειράματα εισαγωγής σφαλμάτων υψηλής ακρίβειας.

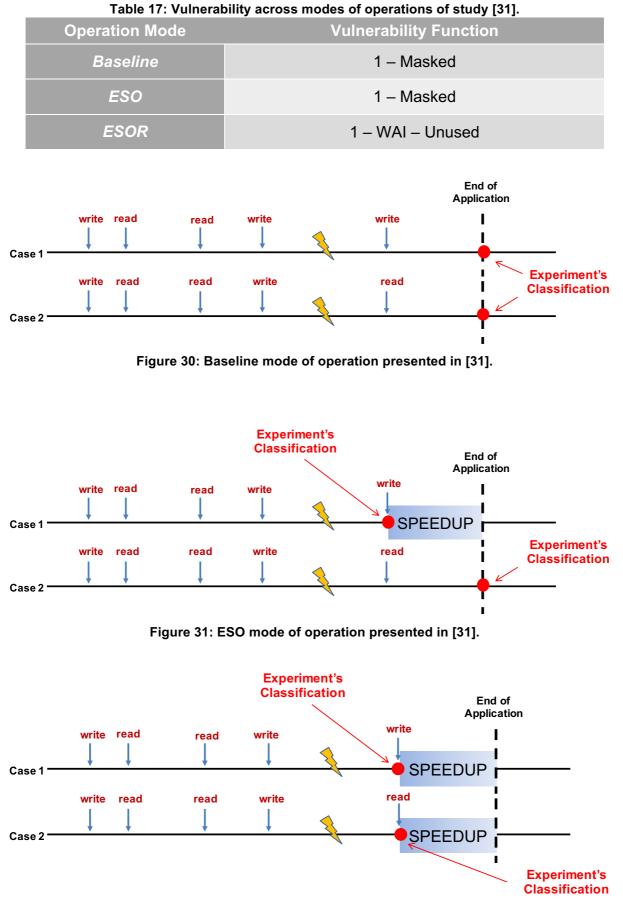

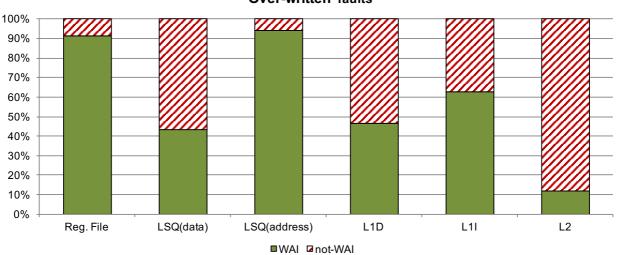

Στην πρώτη μελέτη που παρουσιάζουμε [31] χρησιμοποιώντας τον MaFIN, προτείνουμε δύο διαφορετικές τεχνικές για να επιταχύνουμε τα πειράματα. Οι τεχνικές αυτές λαμβάνουν χώρα μετά από την πραγματική εισαγωγή των σφαλμάτων στις δομές του υλικού κατά τη διάρκεια ζωής του σφάλματος μέσα μέσα στη δομή. Συγκεκριμένα, στην πρώτη τεχνική που προτείνεται σταματάμε τα πειράματα της εισαγωγής σφαλμάτων μόλις το παροδικό σφάλμα επικαλυφθεί από κάποια άλλη εγγραφή στην ίδια θέση της μικροαρχιτεκτονικής δομής. Τα σφάλματα αυτά είμαστε σίγουροι ότι δεν μπορούν να επηρεάσουν τη σωστή λειτουργία του προγράμματος και κατ' επέκταση μπορούν να τερματίσουν πρόωρα χωρίς καθόλου απώλειες ακρίβειας στην τελική εκτίμηση. Στη δεύτερη τεχνική που προτείνεται στην ίδια μελέτη, σταματάμε τα πειράματα είτε όταν το σφάλμα έχει επικαλυφθεί (όμοια με την προηγούμενη τεχνική) είτε όταν το σφάλμα διαβάζεται από μια αρχιτεκτονική εντολή και αυτή η εντολή τελικά διεκπεραιώνεται (commit) χωρίς να περιμένουμε την ολοκλήρωση του προγράμματος. Η ανάγνωση αυτή του σφάλματος και η διεκπεραίωσή της από την εντολή σηματοδοτεί τη μετάβασή του από το μικροαρχιτεκτονικό στο αρχιτεκτονικό επίπεδο (επίπεδο του λογισμικού). Η δεύτερη προτεινόμενη τεχνική επιφέρει ακόμα μεγαλύτερη επιτάχυνση από την πρώτη, η οποία όμως συνοδεύεται από μερική απώλεια ακρίβειας. Η αξιολόγηση των προτεινόμενων τεχνικών έγινε σε 6 διαφορετικές δομές υλικού: στο αρχείο φυσικών καταχωρητών, στις κρυφές μνήμες πρώτου και δεύτερου επιπέδου (L1 Data cache, L1 Instruction cache, L2 cache) και σε δύο πεδία της ουράς φόρτωσης/αποθήκευσης (load/store queue data and address fields). Από την πειραματική διαδικασία παρατηρήσαμε ότι η πρώτη τεχνική που δεν επιφέρει απώλεια ακρίβειας δίνει επιτάχυνση που μπορεί να φτάσει μέχρι τις 2,92 φορές, ενώ η δεύτερη τεχνική που επιφέρει απώλεια ακρίβειας μπορεί να οδηγήσει σε επιτάχυνση μέχρι 4,06 φορές. Επιπλέον, παρατηρήσαμε ότι η απώλεια ακρίβειας που επέρχεται από τη δεύτερη προτεινόμενη τεχνική είναι μικρή (έως 6,58 ποσοστιαίες μονάδες) για τις περιπτώσεις των δομών που βρίσκονται μέσα στον επεξεργαστή (αρχείο φυσικών καταχωρητών και ουρά φόρτωσης/αποθήκευσης), ενώ δεν είναι αμελητέα (έως 20,13 ποσοστιαίες μονάδες) στην περίπτωση των κρυφών μνημών. Κατ' επέκταση, η δεύτερη τεχνική μπορεί να χρησιμοποιηθεί χωρίς κίνδυνο απώλειας ακρίβειας για τις δομές που βρίσκονται μέσα στον επεξεργαστή.

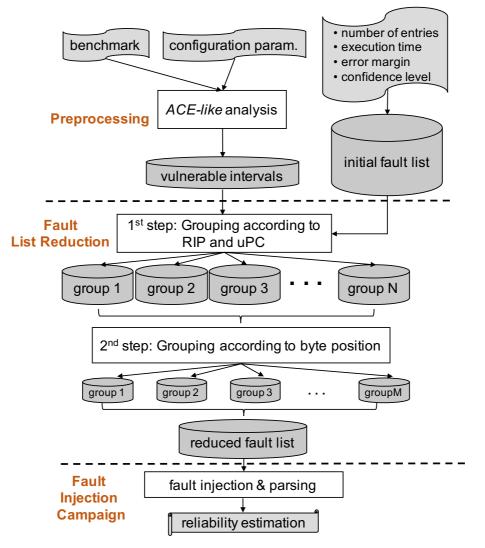

Στη συνέχεια, για να επιταχύνουμε ακόμα περισσότερο τα πειράματα στατιστικής εισαγωγής σφαλμάτων υψηλής στατιστικής ακρίβειας προτείνουμε μια νέα τεχνική που εφαρμόζεται σε μικροαρχιτεκτονικό επίπεδο με την ονομασία MeRLiN [32]. Η μέθοδος αυτή είναι διαφορετική από τις τεχνικές που περιγράφονται στο [31], γιατί εφαρμόζεται πριν από την πραγματική εισαγωγή των σφαλμάτων στις μονάδες του υλικού και την εκτέλεση των προσομοιώσεων. Πιο συγκεκριμένα, η μέθοδος MeRLiN μειώνει το πλήθος της αρχικής λίστας σφαλμάτων και διασφαλίζουν εκτίμηση αξιοπιστίας υψηλής στατιστικής ακρίβειας. Αυτή η αρχική λίστα σφαλμάτων χαρακτηρίζεται από το πολύ μεγάλο πλήθος σφαλμάτων που την αποτελούν, τα οποία επιβάλλεται να εισαγωγή όλων αυτών των σφαλμάτων είναι από τους σημαντικότερους λόγους για την μεγάλη καθυστέρηση των μαζικών πειραμάτων.

Η μεθοδολογία MeRLiN βασίζεται σε δύο βασικά βήματα. Στο πρώτο βήμα γίνεται μια αρχική ανάλυση της εφαρμογής (χωρίς καμία εισαγωγή σφάλματος) με σκοπό τον εντοπισμό των χρονικών διαστημάτων για κάθε οντότητα υλικού

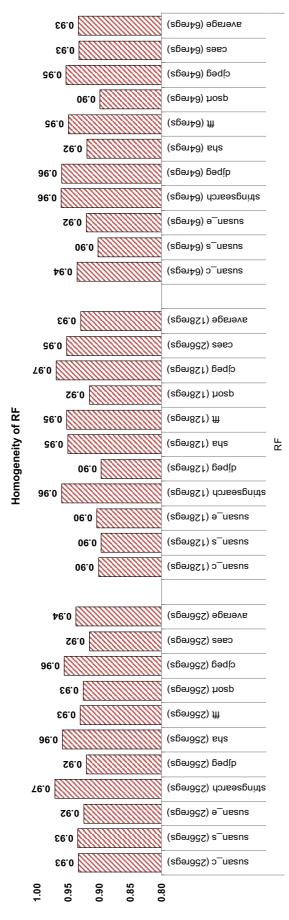

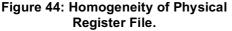

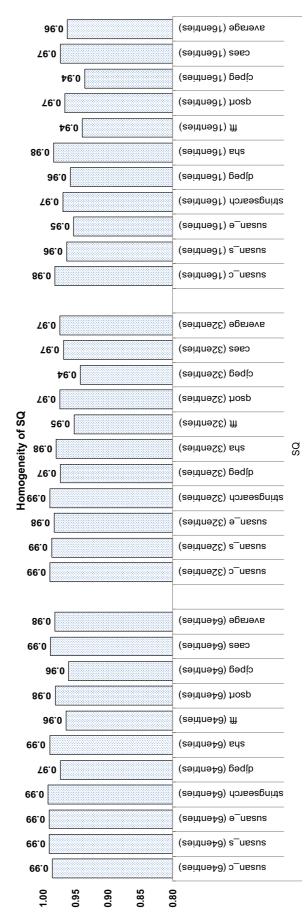

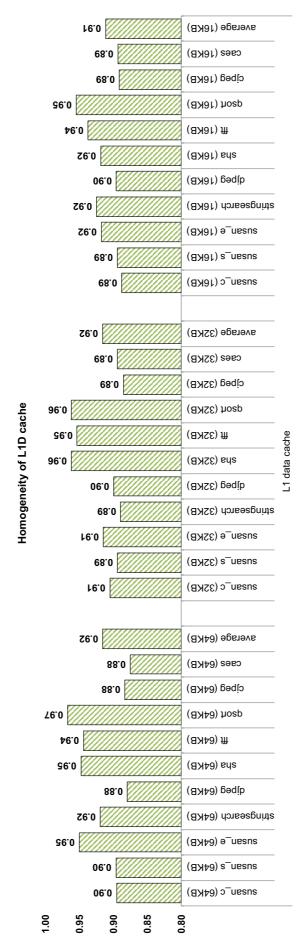

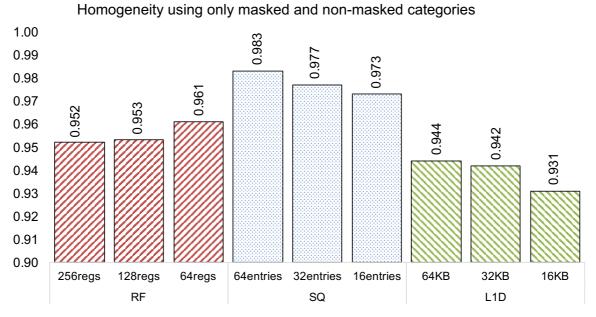

κατά τη διάρκεια των οποίων ένα σφάλμα είναι σίγουρο ότι δεν πρόκειται να επηρεάσει την ορθή λειτουργία της εφαρμογής. Αυτά τα σφάλματα έπειτα από μία και μόνο εκτέλεση της εφαρμογής μπορούν να αφαιρεθούν από την αρχική λίστα σφαλμάτων χωρίς να χρειάζεται να τρέξουν πειράματα εισαγωγής και χωρίς να επηρεαστεί η ακρίβεια. Επιπλέον, κατά τη διάρκεια αυτού του βήματος της μεθοδολογίας καταγράφεται και αποθηκεύεται η πληροφορία της εντολής η οποία τελικά προσπελαύνει την μονάδα υλικού που φέρει το σφάλμα: δείκτης εντολής (RIP) και μετρητής μικροπρογράμματος (uPC) της εντολής. Αυτή η πληροφορία είναι απαραίτητη για το δεύτερο βήμα της μεθόδου. Στο δεύτερο βήμα της μεθόδου MeRLiN, χρησιμοποιούνται μόνο τα σφάλματα που απομένουν από το πρώτο βήμα της μεθόδου. Αυτά τα σφάλματα ομαδοποιούνται ανάλογα με την εντολή που τελικά προσπελαύνει τη μονάδα υλικού που φέρει το σφάλμα (αυτή η πληροφορία είναι καταχωρημένη από το πρώτο βήμα της μεθόδου). Μετά την ομαδοποίηση αυτή, μόνο κάποιοι αντιπρόσωποι από κάθε ομάδα επιλέγονται για εισαγωγή σύμφωνα με τη θέση του byte της δομής στο οποίο βρίσκεται το σφάλμα. Οι αντιπρόσωποι που έχουν επιλεγεί από κάθε ομάδα σφαλμάτων αναμένεται ότι επιφέρουν το ίδιο αποτέλεσμα στην εκτέλεση που προγράμματος με τα άλλα σφάλματα που περιέχονται στην ίδια ομάδα. Αυτή η υπόθεση έχει αξιολογηθεί στην πειραματική μας διαδικασία με τη χρήση της μεταβλητής της ομοιογένειας (homogeneity) των ομάδων που έχουμε ορίσει για το σκοπό αυτό. Η μέθοδος MeRLiN οδηγεί σε ακριβής εκτιμήσεις της αξιοπιστίας των μονάδων του υλικού, ενώ η εισαγωγή τελικά μόνο των αντιπροσώπων από κάθε ομάδα οδηγεί σε μεγάλη επιτάχυνση της διαδικασίας.

Για την αξιολόγηση της μεθοδολογίας του MeRLiN ως προς την επιτάχυνση και την ακρίβεια στοχεύσαμε τέσσερις αντιπροσωπευτικές μονάδες. Οι τρεις από αυτές είναι μονάδες που σχετίζονται με δεδομένα: (1) κρυφή μνήμη δεδομένων πρώτου επιπέδου - L1D cache, (2) αρχείο φυσικών ακέραιων καταχωρητών physical integer register file, και (3) ουρά αποθήκευσης - store queue. Η τέταρτη μονάδα σχετίζεται με εντολές (ουρά εντολών - issue queue). Στα πειράματά μας αξιολογήσαμε τον MeRLiN για διαφορετικά μεγέθη των τεσσάρων μονάδων υλικού, ενώ το πλήθος σφαλμάτων της αρχικής λίστας σφαλμάτων είναι 60.000 σφάλματα, πλήθος που διασφαλίζει τελικές εκτιμήσεις αξιοπιστίας υψηλής στατιστικής ακρίβειας (~0,63% error margin, 99.8% confidence level).

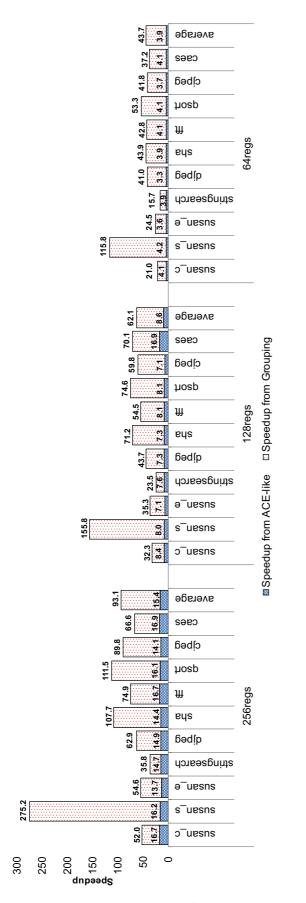

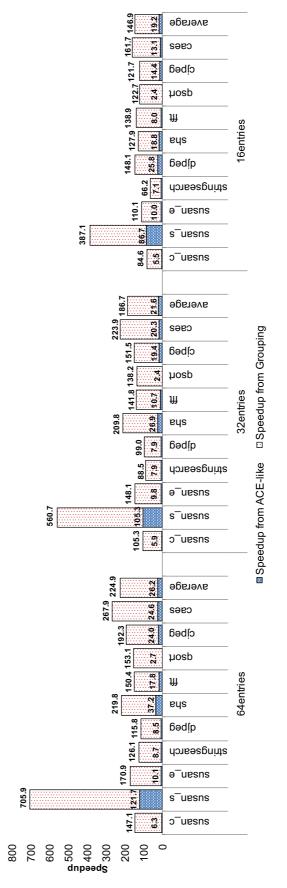

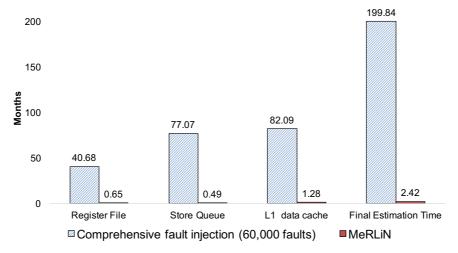

Η πειραματική διαδικασία επιβεβαίωσε ότι ο MeRLiN εκτιμά την αξιοπιστία των δομών υλικού με πολύ μεγάλη ακρίβεια, αλλά ταυτόχρονα προσφέρει επιτάχυνση 93Χ, 225Χ, 68Χ και 28Χ κατά μέσο όρο για το αρχείο φυσικών καταχωρητών, την ουρά αποθήκευσης, την κρυφή μνήμη δεδομένων πρώτου επιπέδου και την ουρά εντολών όταν εκτελούνται 10 μετροπρογράμματα από τη σουίτα MiBench. Όταν εκτελούμε τη μεθοδολογία MeRLiN με 10 μετροπρογράμματα από τη σουίτα SPEC CPU2006, τότε κατά μέσο όρο η επιτάχυνση είναι 1644X, 2018X και 171Χ για το αρχείο φυσικών καταχωρητών, την ουρά αποθήκευσης και την κρυφή μνήμη δεδομένων πρώτου επιπέδου, αντίστοιχα. Η επιτάχυνση που προσφέρει ο MeRLiN σε συνδυασμό με τη διατήρηση της ακρίβειας των αξιοπιστίας, βοηθούν την ανάλυση της εκτιμήσεων αξιοπιστίας σε μικροαρχιτεκτονικό επίπεδο με χρήση της μεθοδολογίας στατιστικής εισαγωγής σφαλμάτων κατά τα πρώιμα σχεδιαστικά στάδια ενός επεξεργαστή μειώνοντας με αυτό τον τρόπο τον χρόνο που απαιτείται ώστε το προϊόν να κυκλοφορήσει στην αγορά.

Τέλος, άλλες μελέτες που βασίζονται στα παραπάνω εργαλεία και μεθόδους είναι οι εξής: [90] [91] [92] [93] [94] [95].  Παραγωγικό στάδιο και στάδιο κυκλοφορίας στην αγορά: Οι συνεισφορές της διδακτορικής διατριβής σε αυτά τα στάδια της ζωής των ολοκληρωμένων κυκλωμάτων καλύπτουν δύο σημαντικά ερευνητικά πεδία: (α) τον εντοπισμό μονίμων σφαλμάτων σε αρχιτεκτονικές πολλών πυρήνων με σκοπό τη διασφάλιση της ορθής λειτουργίας τους, και (β) τη διασφάλιση της βέλτιστης ενεργειακής απόδοσης των πολυπύρηνων ολοκληρωμένων κυκλωμάτων σε συνδυασμό με τη διατήρηση της αξιοπιστίας τους σε υψηλά επίπεδα.

Η πρώτη συνεισφορά που παρουσιάζουμε συνοπτικά σε αυτό το σημείο της διατριβής σχετίζεται με την επιτάχυνση της διαδικασίας εντοπισμού των μονίμων σφαλμάτων σε αρχιτεκτονικές πολλών πυρήνων [33]. Τα σφάλματα αυτού του είδους μπορούν να προκύψουν από κατασκευαστικές ατέλειες ή μπορούν να προκύψουν λόγω της γήρανσης του ολοκληρωμένου κυκλώματος αφού αυτό έχει κυκλοφορήσει και χρησιμοποιηθεί στην αγορά. Οι αρχιτεκτονικές με πολλούς πυρήνες εμφανίζουν ραγδαία ανάπτυξη τα τελευταία χρόνια, ενώ και η επιστημονική κοινότητα δίνει ιδιαίτερη βαρύτητα στον εντοπισμό τεχνικών για τη διασφάλιση της ορθής λειτουργίας τους.

Σε αυτό το πλαίσιο και χρησιμοποιώντας το ολοκληρωμένο κύκλωμα των 48 πυρήνων με ονομασία Intel Single-chip Cloud Computer (SCC), προτείνουμε μια τεχνική επιτάχυνσης του εντοπισμού μονίμων σφαλμάτων σε αρχιτεκτονικές με πολλούς πυρήνες κατά τη διάρκεια λειτουργίας τους. Η προτεινομένη μέθοδος εκμεταλλεύεται το δίκτυο υψηλής ταχύτητας μεταφοράς μηνυμάτων που διατίθεται στα ολοκληρωμένα κυκλώματα αυτού του είδους με σκοπό την παραλληλοποίηση του προγράμματος ελέγχου ορθής λειτουργίας. Η επιτάχυνση εμφανίζεται στις περιπτώσεις που τα προγράμματα ελέγχου ορθής λειτουργίας δημιουργούν συμφόρηση περισσότερο στη μνήμη του κυκλώματος, παρά στην ίδια την κεντρική μονάδα επεξεργασίας. Η πειραματική διαδικασία απέδειξε ότι η προτεινόμενη μεθοδολογία επιτάχυνσης των προγραμμάτων ελέγχου που δημιουργούν συμφόρηση στη μνήμη μπορεί να επιφέρει επιτάχυνση μέχρι και 38,2Χ για όλους τους πυρήνες του επεξεργαστή. Επιπλέον, χρησιμοποιώντας την προτεινόμενη μεθοδολογία για προγράμματα ελέγχου λειτουργίας που δημιουργούν συμφόρηση στη μνήμη και συνδυάζοντάς την παράλληλα με προγράμματα ελέγχου λειτουργίας που δημιουργούν συμφόρηση στην κεντρική μονάδα επεξεργασίας μετρήσαμε επιτάχυνση 47,6X. Н προτεινόμενη μεθοδολογία επιταχύνει αισθητά τη διαδικασία εντοπισμού μονίμων σφαλμάτων σε αρχιτεκτονικές πολλών πυρήνων και μπορεί να χρησιμοποιηθεί είτε κατά την παραγωγική διαδικασία είτε μετά την κυκλοφορία του επεξεργαστή στην αγορά.

Η δεύτερη συνεισφορά που εφαρμόζεται τόσο στο στάδιο της παραγωγής όσο και μετά την κυκλοφορία στην αγορά σχετίζεται με την εξασφάλιση της βέλτιστης ενεργειακής απόδοσης και αξιοπιστίας σε ένα πολυπύρηνο ολοκληρωμένο κύκλωμα με ονομασία X-Gene 2, το οποίο διαθέτει 8 πυρήνες μικροεπεξεργαστή τύπου ARMv8. Οι διάφορες κατασκευαστικές ατέλειες των ολοκληρωμένων κυκλωμάτων προκαλούν τη διαφοροποίηση των ορίων ασφαλούς λειτουργίας (ως προς την τάση) ακόμα και ανάμεσα σε όμοιους πυρήνες που υποτίθεται ότι έχουν σχεδιαστεί ώστε να λειτουργούν ορθά υπό τις ίδιες ακριβώς συνθήκες. Επιπλέον, οι ίδιες ατέλειες και το φαινόμενο της γήρανσης του κυκλώματος μπορεί να οδηγήσει σε λάθη χρονισμού (timing errors) που μπορούν να επηρεάσουν την ορθή λειτουργία του κυκλώματος όταν αυτό έχει ήδη κυκλοφορήσει στην αγορά. Για την αντιμετώπιση αυτών των φαινομένων, οι σχεδιαστές συχνά υιοθετούν απαισιόδοξα όρια τάσης λειτουργίας των επεξεργαστών, κατασπαταλώντας με αυτό τον τρόπο την ενεργειακή απόδοση του κυκλώματος στο βωμό της αξιοπιστίας. Ο εντοπισμός των βέλτιστων τιμών

τάσης λειτουργίας ώστε να υπάρχει μια ισορροπία ανάμεσα στην αξιοπιστία και την ενεργειακή κατανάλωση είναι ζωτικής σημασίας για τα σύγχρονα υπολογιστικά συστήματα.

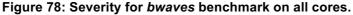

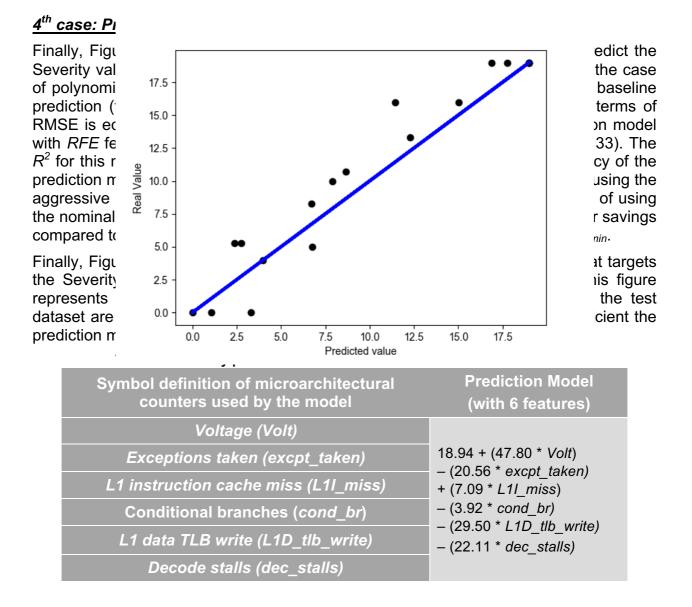

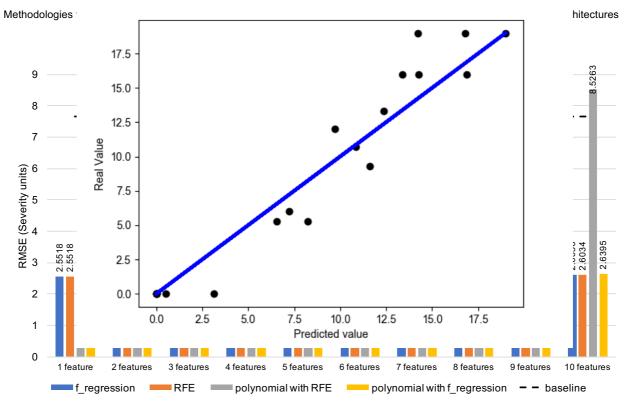

Προς αυτή την επιστημονική κατεύθυνση, στη διατριβή αυτή παρουσιάζουμε τις μελέτες [35] [167], στις οποίες προτείνουμε μια στατιστική μεθοδολογία που βασίζεται στη μέθοδο linear regression (γραμμικής παλινδρόμησης) με σκοπό την ακριβή πρόβλεψη σε επίπεδο συστήματος των ασφαλών ορίων λειτουργίας της τάσης των πυρήνων τύπου ARMv8 που βρίσκονται πάνω στο ολοκληρωμένο κύκλωμα X-Gene 2. Η πειραματική διαδικασία απέδειξε ότι μπορούμε να προβλέψουμε το ασφαλές όριο τάσης λειτουργίας των πυρήνων με πολλή μεγάλη ακρίβεια κερδίζοντας σε ενέργεια έως 20,28%.

Ελπίζουμε ότι οι τεχνικές που παρουσιάζονται στη διατριβή αυτή, θα ενισχύσουν την αξιοπιστία και την ενεργειακή απόδοση των σύγχρονων επεξεργαστών. Τέλος, ελπίζουμε ότι οι προσεγγίσεις μας θα αποτελέσουν εφαλτήριο πολλών μελλοντικών ερευνητικών μελετών βελτιώνοντας την ποιότητα των σύγχρονων υπολογιστικών συστημάτων.

# TABLE OF CONTENTS

| 1.                | INTRODUCTION                                                                                        | 37         |

|-------------------|-----------------------------------------------------------------------------------------------------|------------|

| 1.1               | The evolution of microprocessor design                                                              | 37         |

| 1.2               | Design life-cycle of microprocessors                                                                | 40         |

| 1.3               | Reliability life-cycle of microprocessors                                                           | 41         |

| 1.4               | Distribution of failures in different phases of the processor life-cycle                            | 43         |

| 1.5               | Contribution of this thesis                                                                         | 44         |

| 1.6               | Thesis outline                                                                                      | 47         |

| 2.                | PRE-SILICON RELIABILITY ANALYSIS                                                                    | 49         |

|                   |                                                                                                     |            |

| 2.1               | Background of early reliability estimation at the microarchitecture level                           |            |

| 2.1               |                                                                                                     |            |

| 2.1               |                                                                                                     |            |

| 2.1               |                                                                                                     |            |

| 2.1               |                                                                                                     |            |

| 2.1               | I.5 Statistical fault injection at the microarchitecture level                                      | 54         |

|                   |                                                                                                     |            |

| 2.2               | MaFIN tool for early microarchitecture level reliability assessments                                | 57         |

| 2.2               |                                                                                                     |            |

| 2.2               | •                                                                                                   |            |

| 2.2               |                                                                                                     |            |

| 2.2               |                                                                                                     |            |

| <b>3.</b><br>3.1  | ACCELERATION OF RELIABILITY ASSESSMENTS USING MERLIN<br>MeRLiN's results on data-related structures |            |

|                   |                                                                                                     |            |

| 3.2               | MeRLiN's results on instruction-related structures                                                  | 109        |

| 3.3               | Comparison of MeRLiN with architecture level fault injection approaches                             | 112        |

| 3.4               | Theoretical analysis of MeRLiN                                                                      | 114        |

| 3.5               | Related work                                                                                        | 116        |

| 3.6               | Findings Summary                                                                                    | 118        |

| 4.                | POST-SILICON RELIABILITY ANALYSIS                                                                   | 121        |

|                   | Online normanant fault data dian in many and and its stores                                         | 104        |

| <b>4.1</b><br>4.1 | 123                                                                                                 | nitectures |

| 4.1               |                                                                                                     | 129        |

| 4.1               | I.3 Related work                                                                                    | 130        |

|                   |                                                                                                     |            |

| 4.2               | Statistical analysis to predict the safe voltage margins in multicore CPUs for er                   | nerav      |

|                   | ency                                                                                                |            |

| 4.2               | •                                                                                                   |            |

| 4.2               |                                                                                                     |            |

| 4.2               |                                                                                                     |            |

| 4.2               |                                                                                                     |            |

| 4.4               | 2.4 INCIALEU WUIN                                                                                   |            |

| 4.3 | Findings Summary           | 149 |

|-----|----------------------------|-----|

| 5.  | CONCLUSION AND FUTURE WORK | 151 |

| AC  | RONYMS                     | 153 |

| AN  |                            | 155 |

| RE  | FERENCES                   | 159 |

# LIST OF FIGURES

| Figure 1: The evolution forecast of global connected electronic devices until 2025<br>Billions of electronic devices (source: IHS, www.ihs.com) |          |

|-------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Figure 2: Transistor density per Million Transistor per mm <sup>2</sup> (MTr / mm <sup>2</sup> ) until 2018 [5].                                | 38       |

| Figure 3: Increase in processor performance relative to the VAX 11/780 as measured the SPECint benchmarks.                                      |          |

| Figure 4: Processor design life-cycle.                                                                                                          | 41       |

| Figure 5: Processor reliability life-cycle                                                                                                      | 43       |

| Figure 6: Distribution of failures during processor life-cycle                                                                                  | 43       |

| Figure 7: Relative cost of finding bugs throughout processor life-cycle [26]                                                                    | 44       |

| Figure 8: Contributions of this thesis in the processor life-cycle.                                                                             | 45       |

| Figure 9: Generalized concept of transient fault effect classification that is used reliability studies.                                        | in<br>52 |

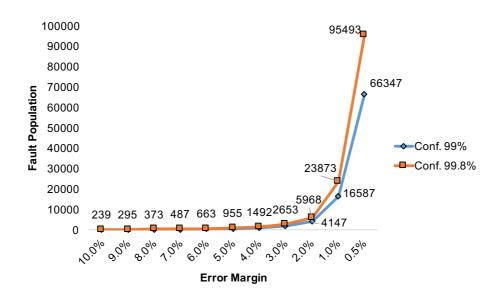

| Figure 10: Fault Population vs. Error Margin for Confidence Level 99% and 99.8%                                                                 | 56       |

| Figure 11: Fault Population vs. Confidence Level for Error Margin 3% and 1%                                                                     | 57       |

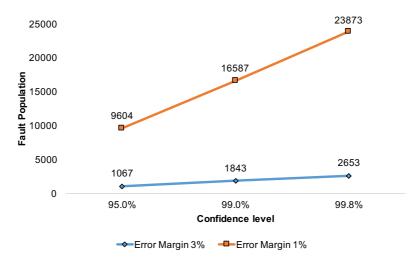

| Figure 12: Flowchart of fault effect classification used in our reliability estimation studies.                                                 |          |

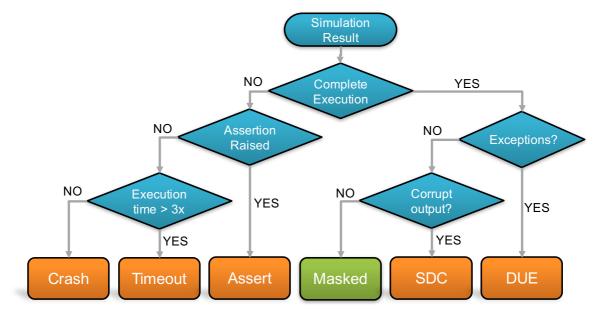

| Figure 13: MaFIN injection framework                                                                                                            | 61       |

| Figure 14: Faults classification in L1 Data cache (sizes).                                                                                      | 66       |

| Figure 15: Faults classification in L1 Instruction cache (sizes).                                                                               | 67       |

| Figure 16: Faults classification in Physical Register File (sizes).                                                                             | 67       |

| Figure 17: Faults classification in LSQ (sizes).                                                                                                | 67       |

| Figure 18: Faults classification in L1 Data cache (associativity).                                                                              | 68       |

| Figure 19: Faults classification in L1 Instruction cache (associativity)                                                                        | 68       |

| Figure 20: Faults classification in L1 Data cache (write policies).                                                                             | 69       |

| Figure 21: Faults classification in L1 Instruction cache (write policies).                                                                      | 69       |

| Figure 22: Faults classification in L2 Unified cache (write policies).                                                                          | 70       |

| Figure 23: Faults classification in L1 Data cache (prefetcher).                                                                                 | 70       |

| Figure 24: Faults classification in L1 Instruction cache (prefetcher).                                                                          | 70       |

| Figure 25: Faulty behavior classification for the integer physical register file                                                                | 77       |

| Figure 26: Faulty behavior classification for Load/Store Queue (data field)                                                                     | 78       |

| Figure 27: Faulty behavior classification for L1D cache (data arrays)                                                                           | 79       |

| Figure 28: Faulty behavior classification for L1I cache (instruction arrays)                                                                    | 80       |

| Figure 29: Faulty behavior classification for L2 cache (data arrays).                                                                           | 81       |

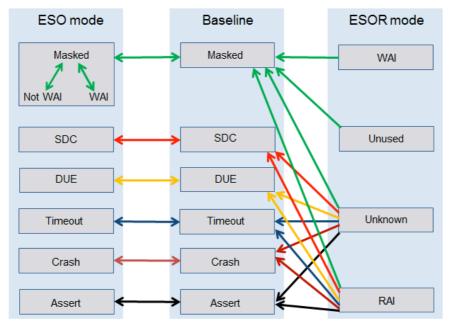

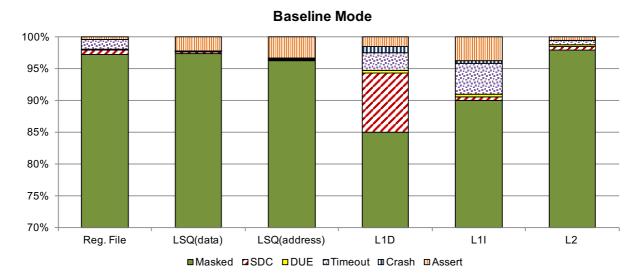

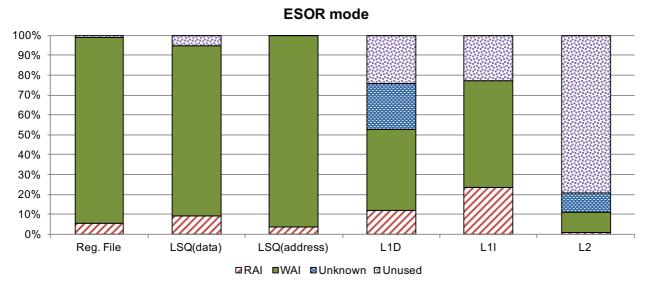

| Figure 30: Baseline mode of operation presented in [31]                                                                                         | 84       |

| Figure 31: ESO mode of operation presented in [31]                                                                                              | 84       |

| Figure 32: ESOR mode of operation presented in [31].                                                                                            | 84       |

| Figure 33: Correlation of classes among the three modes of presented in [31]85                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 34: Faulty Behaviors classification of Baseline and ESO mode                                                                                                                                                                                      |

| Figure 35: Percentage of over-written or injected on invalid entry faults                                                                                                                                                                                |

| Figure 36: Faulty Behaviors classification of ESOR mode                                                                                                                                                                                                  |

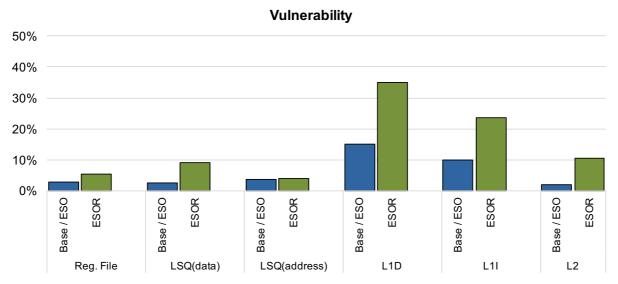

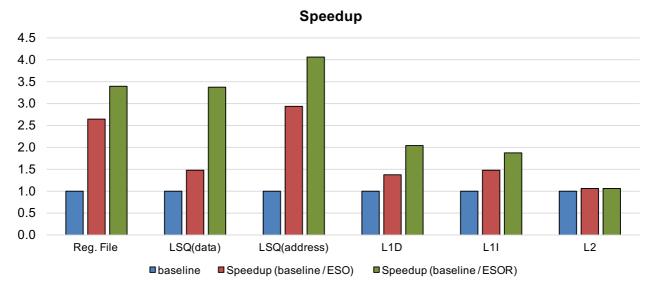

| Figure 37: Structures vulnerability reported by the three operation modes. There is no loss of accuracy in the vulnerability reports between the baseline mode and the <i>ESO</i> mode, while <i>ESOR</i> mode reports higher vulnerability in all cases |

| Figure 38: Speedup of the three operation modes of study [31]                                                                                                                                                                                            |

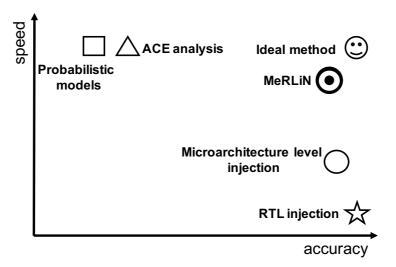

| Figure 39: Motivation of MeRLiN methodology compared to the four state-of-the-art methods used for reliability assessments (as described in Section 2.1.4)                                                                                               |

| Figure 40: Flowchart of MeRLiN92                                                                                                                                                                                                                         |

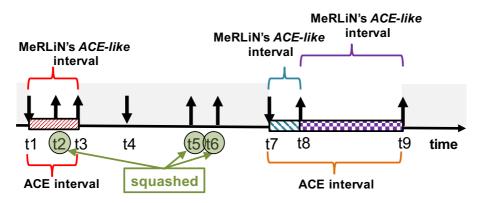

| Figure 41: ACE and ACE-like intervals definition example                                                                                                                                                                                                 |

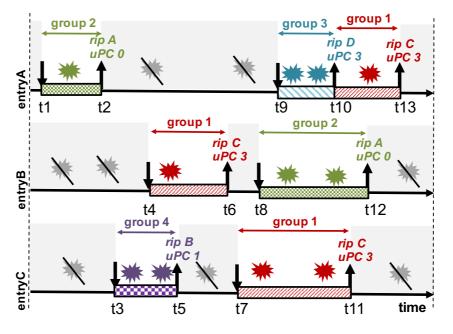

| Figure 42: 1 <sup>st</sup> step example of the grouping algorithm95                                                                                                                                                                                      |

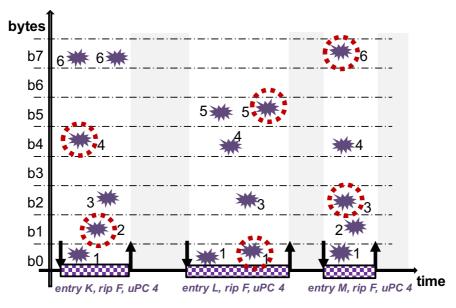

| Figure 43: 2 <sup>nd</sup> step example of the grouping algorithm                                                                                                                                                                                        |

| Figure 44: Homogeneity of Physical Register File                                                                                                                                                                                                         |

| Figure 45: Homogeneity of Store Queue                                                                                                                                                                                                                    |

| Figure 46: Homogeneity of L1 Data cache100                                                                                                                                                                                                               |

| Figure 47: Coarse-grained homogeneity (number on top of the bars) and percentage of groups with perfect homogeneity that is equal to 1.0 (number on the bottom of the bars); average for 10 MiBench                                                      |

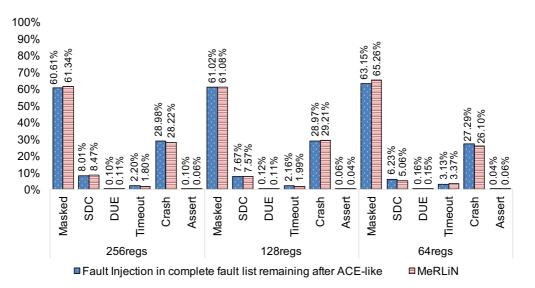

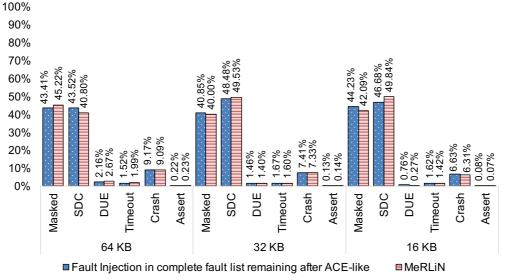

| Figure 48: Fault effect classification of MeRLiN against injection with the remaining faults after <i>ACE-like</i> step for the Physical Integer Register File; average for 10 MiBench benchmarks                                                        |

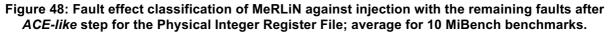

| Figure 49: Fault effect classification of MeRLiN against injection with the remaining faults after <i>ACE-like</i> step for the Store Queue; average for 10 MiBench benchmarks.102                                                                       |

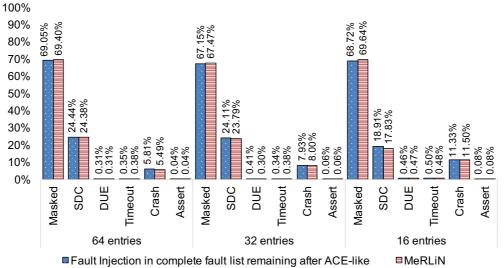

| Figure 50: Fault effect classification of MeRLiN against injection with the remaining faults after <i>ACE-like</i> step for the L1 Data cache; average for 10 MiBench benchmarks.                                                                        |

| Figure 51: Final fault effect classification of MeRLiN against comprehensive baseline fault injection with 60,000 faults for the Physical Register File; average for 10 MiBench benchmarks                                                               |

| Figure 52: Final fault effect classification of MeRLiN against comprehensive baseline fault injection with 60,000 faults for the Store Queue; average for 10 MiBench benchmarks                                                                          |

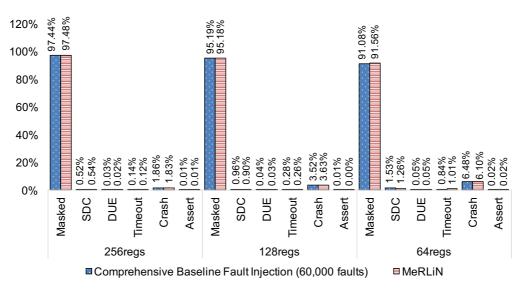

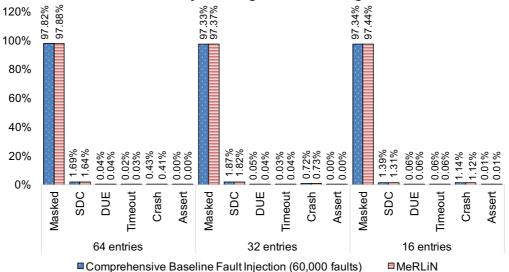

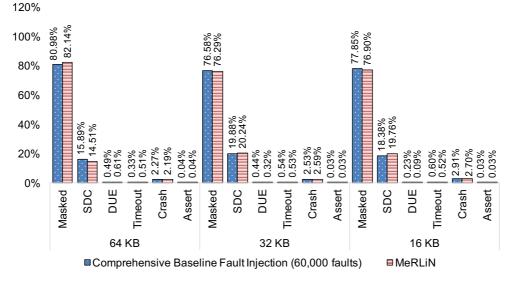

| Figure 53: Final fault effect classification of MeRLiN against comprehensive baseline fault injection with 60,000 faults for the L1 Data cache; average for 10 MiBench benchmarks                                                                        |

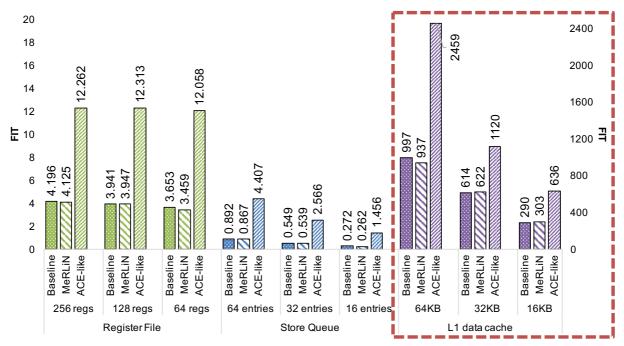

| Figure 54: Final reliability assessment (FIT) for Integer Physical Register File, Store Queue, and L1 Data cache (average for 10 MiBench benchmarks)                                                                                                     |

| Figure 55: MeRLiN speedup for the three sizes of the Physical Integer Register File running 10 MiBench benchmarks                                                                                                                                        |

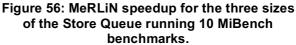

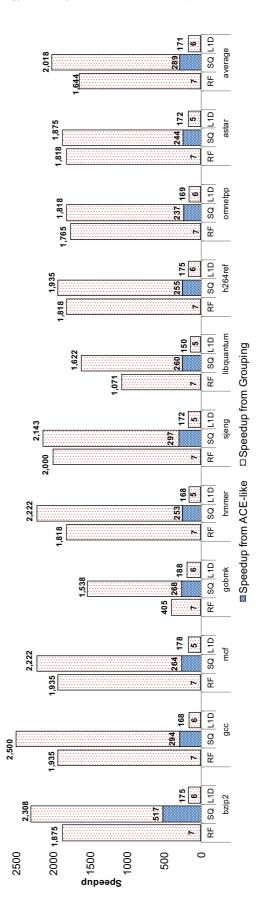

| Figure 56: MeRLiN speedup for the three sizes of the Store Queue running 10 MiBench benchmarks                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

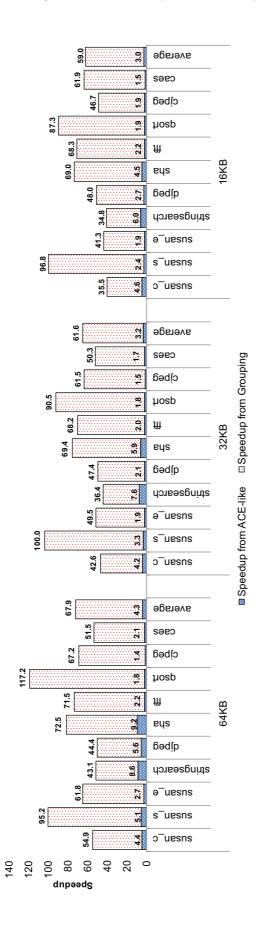

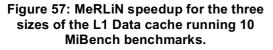

| Figure 57: MeRLiN speedup for the three sizes of the L1 Data cache running 10 MiBench benchmarks                                                                                                                                             |

| Figure 58: MeRLiN speedup for the RF, SQ, and L1D running 10 Simpoints of 100M committed instructions from SPEC CPU2006107                                                                                                                   |

| Figure 59: Actual reliability estimation times of the comprehensive baseline injection vs. MeRLiN for all structures configurations of this study running 10 MiBench benchmarks. 108                                                         |

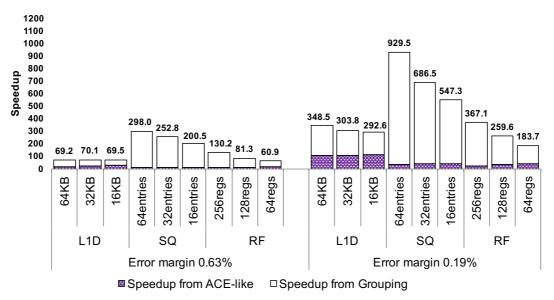

| Figure 60: MeRLiN speedup scaling for 0.63% (60K faults) and 0.19% error margin (600K faults); average for 10 MiBench benchmarks                                                                                                             |

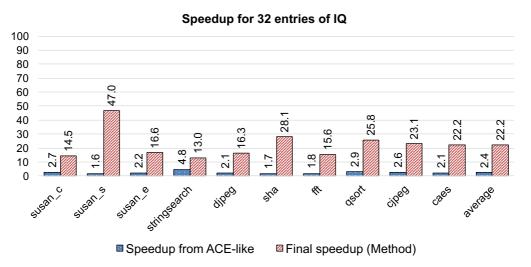

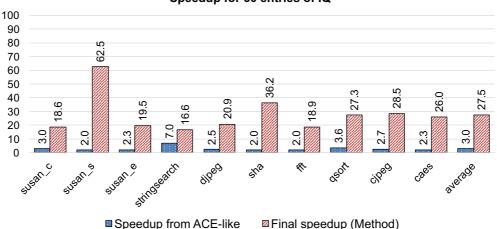

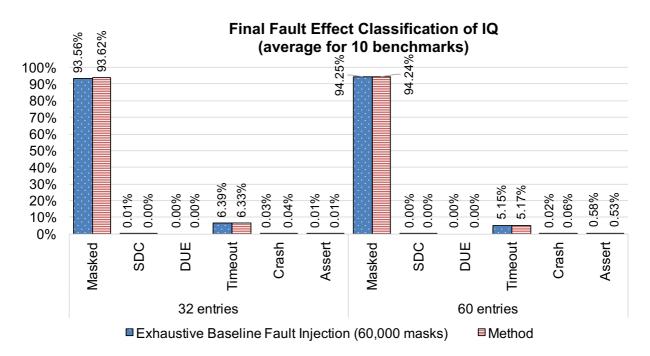

| Figure 61: MeRLiN speedup for the Issue Queue with 32 entries running 10 MiBench benchmarks                                                                                                                                                  |

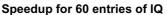

| Figure 62: MeRLiN speedup for the Issue Queue with 60 entries running 10 MiBench benchmarks                                                                                                                                                  |

| Figure 63: Homogeneity of Issue Queue110                                                                                                                                                                                                     |

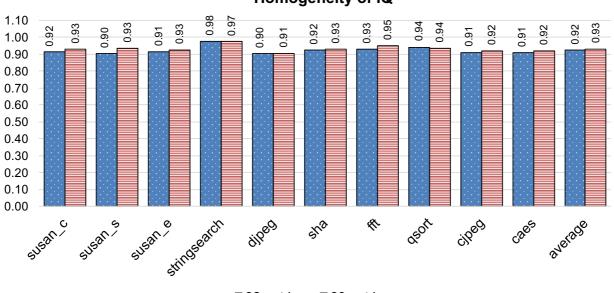

| Figure 64: Fault effect classification of MeRLiN against injection with the remaining faults after ACE-like step for the Issue Queue; average for 10 MiBench benchmarks.111                                                                  |

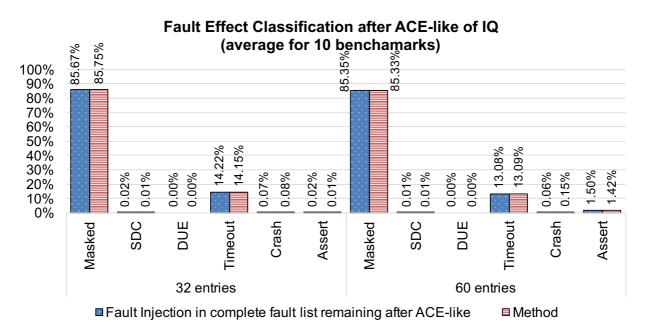

| Figure 65: Final fault effect classification of MeRLiN against comprehensive baseline fault injection with 60,000 faults for the Issue Queue; average for 10 MiBench benchmarks                                                              |

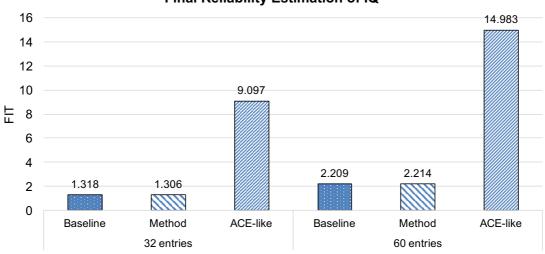

| Figure 66: Final reliability assessment (FIT) for the Issue Queue (average for 10 MiBench)                                                                                                                                                   |

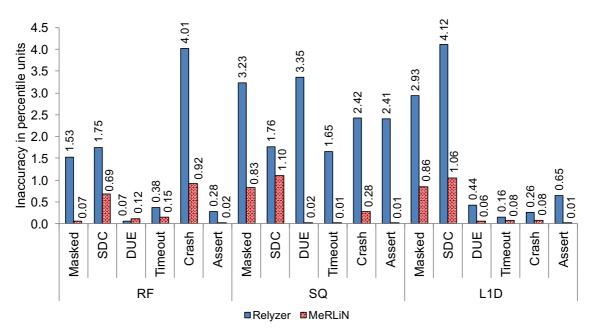

| Figure 67: Inaccuracy of MeRLiN and Relyzer vs. injection with the remaining faults after <i>ACE-like</i> ; average for 10 MiBench114                                                                                                        |

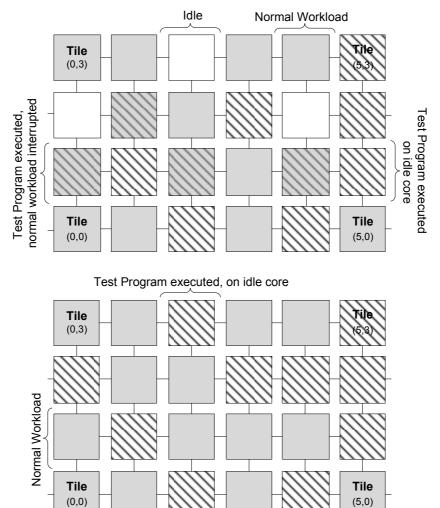

| Figure 68: Intrusive (upper) and non-intrusive (lower) online functional detection approach                                                                                                                                                  |

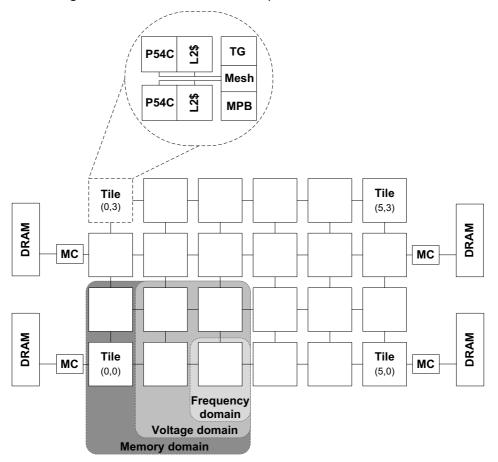

| Figure 69: Intel's many-core SCC Architecture124                                                                                                                                                                                             |

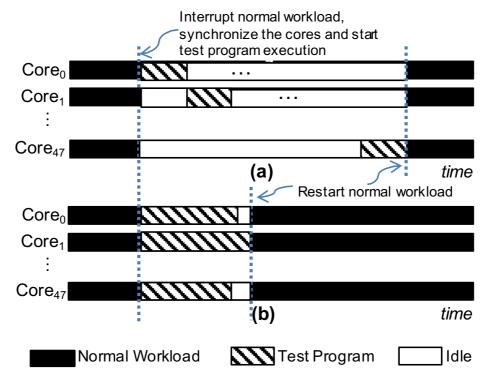

| Figure 70: (a) Serial test program, (b) Naïve parallel test program                                                                                                                                                                          |

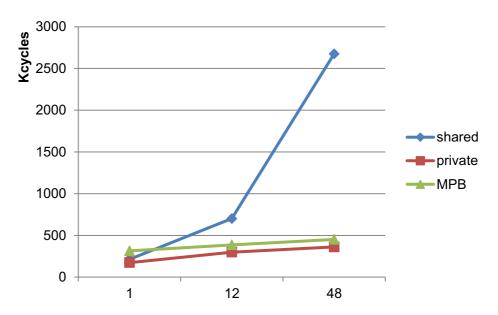

| Figure 71: Execution times (in core clock cycles) of loading 8KB test data. Clock frequency settings: tile/mesh/DDR-533MHz/800MHz/800MHz127                                                                                                  |

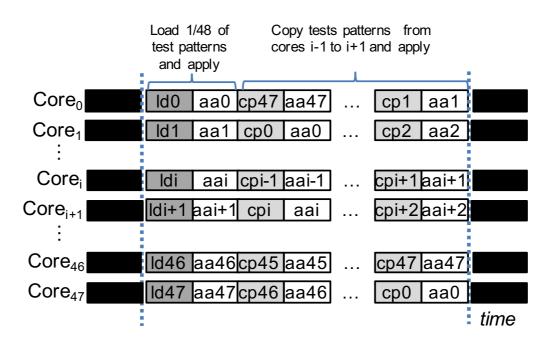

| Figure 72: The proposed parallelization method of LAA test program (ldi: core i loads test patterns from its private memory, aai: core applies and accumulates the test pattern segment i, cpi: core copies patterns from the MPB of core i) |

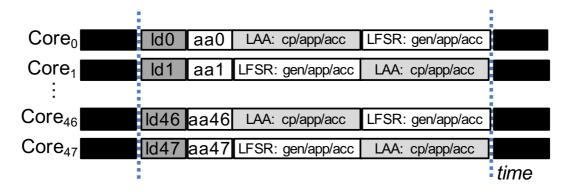

| Figure 73: The proposed parallelization method of LAA-LFSR test program (ldi: core i loads test patterns from its private memory, cp/app/acc: core copies, applies & accumulates test patterns)                                              |

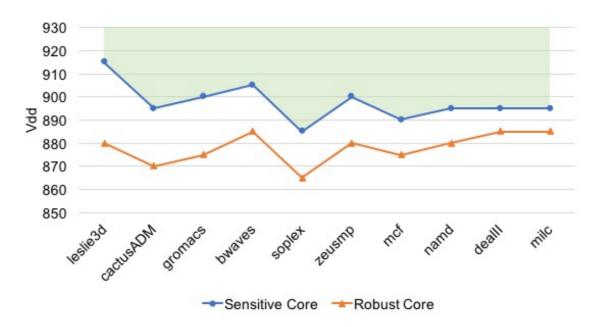

| Figure 74: Variation of <i>V<sub>min</sub></i> between the most sensitive and most robust cores running 10 SPEC CPU2006 benchmarks on X-Gene 2                                                                                               |

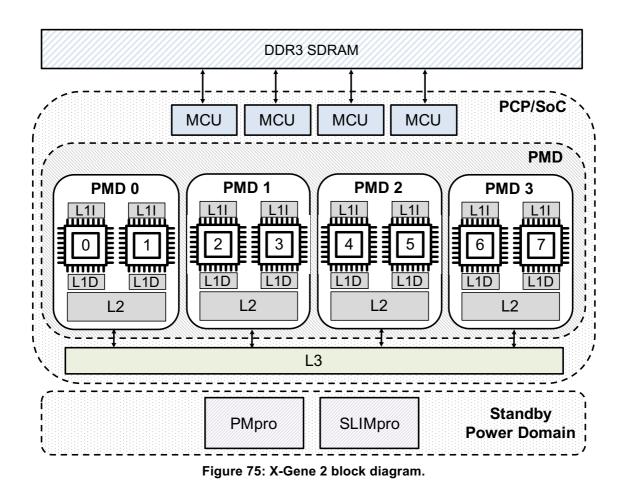

| Figure 75: X-Gene 2 block diagram134                                                                                                                                                                                                         |

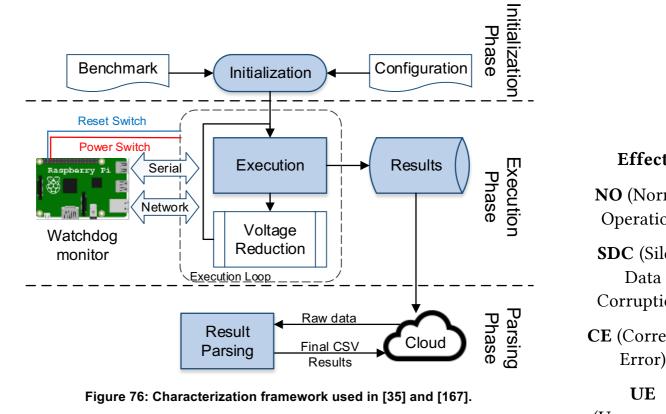

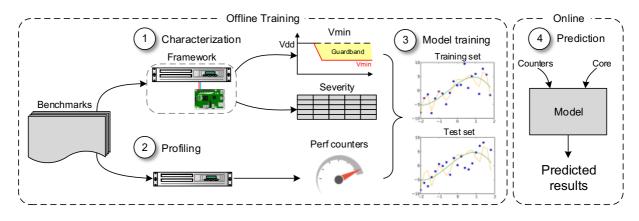

| Figure 76: Characterization framework used in [35] and [167]135                                                                                                                                                                              |

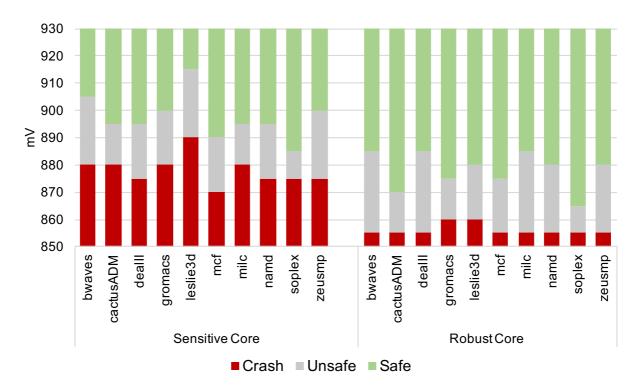

| Figure 77: Regions of operation for 10 benchmarks from SPEC CPU2006 suite running on the most robust and most sensitive core of the X-Gene 2                                                                                                 |

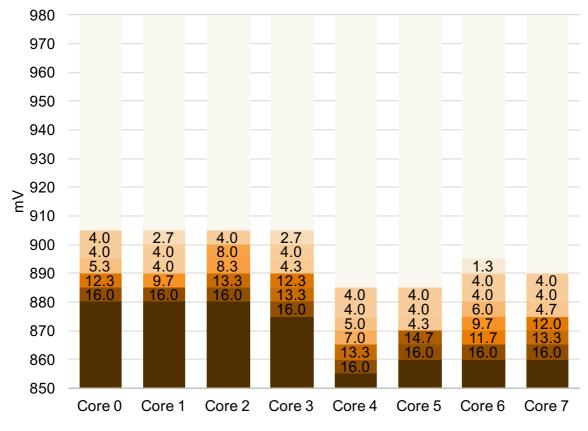

| Figure 78: Severity for <i>bwaves</i> benchmark on all cores13                                                                                    | 38 |

|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 79: Power savings targeting the $V_{min}$ or using Severity function                                                                       | 39 |

| Figure 80: Overview of the prediction flow used in studies [35] and [167]14                                                                       | 41 |

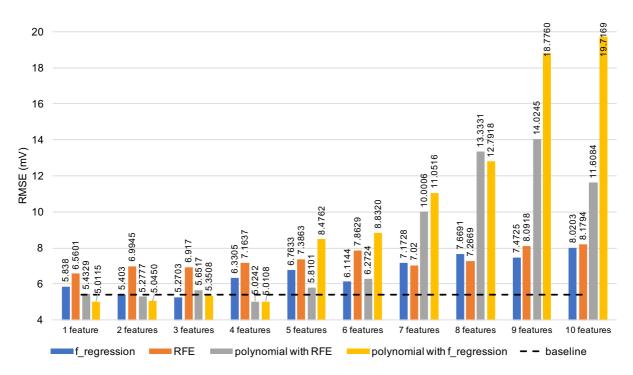

| Figure 81: Accuracy of predicting the $V_{min}$ of the most sensitive core14                                                                      | 44 |

| Figure 82: Accuracy of predicting the $V_{min}$ of the most robust core14                                                                         | 45 |

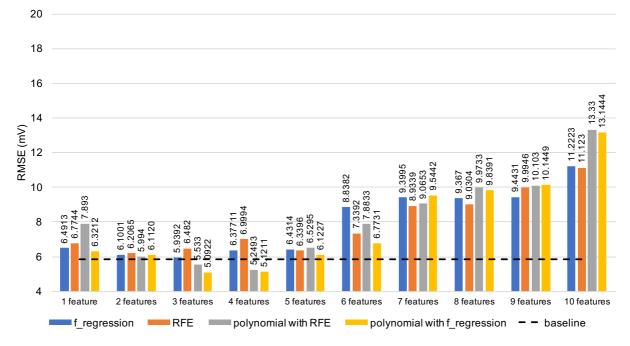

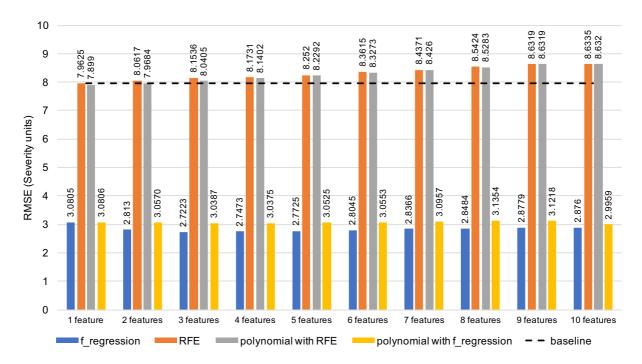

| Figure 83: Accuracy of predicting the <i>Severity</i> of the most sensitive core14                                                                | 46 |

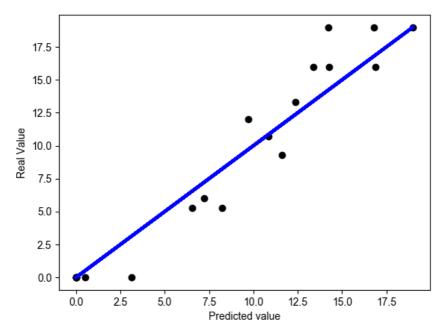

| Figure 84: Intuitively representation of the efficiency of the proposed model that targe<br>the Severity of the most sensitive core of X-Gene 214 |    |

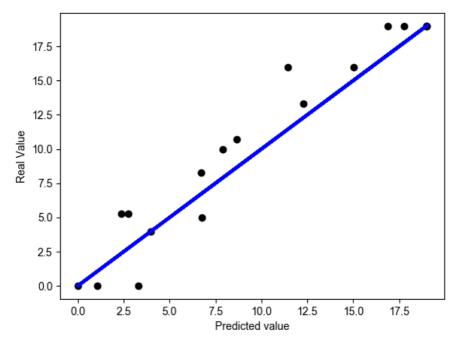

| Figure 85: Accuracy of predicting the <i>Severity</i> of the most robust core                                                                     | 48 |

| Figure 86: Intuitively representation of the efficiency of the proposed model that targe<br>the Severity of the most robust core of X-Gene 214    |    |

# LIST OF TABLES

| Table 1: Example of estimating reliability of an entire CPU in FIT                                                                               | 51  |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2: Qualitative comparison among the methods used for reliability evaluation                                                                | 54  |

| Table 3: Fault models supported by MaFIN.                                                                                                        | 58  |

| Table 4: Fault effect classification.                                                                                                            | 60  |

| Table 5: MaFIN enhancements and supported components.                                                                                            | 63  |

| Table 6: Baseline configuration of study [28].                                                                                                   | 64  |

| Table 7: Experimental setup used in study [28]                                                                                                   | 65  |

| Table 8: FIT, IPC and Fitness values for the L1 Data cache                                                                                       | 72  |

| Table 9: FIT, IPC and Fitness values for the L1 Instruction cache                                                                                | 72  |

| Table 10: FIT, IPC and Fitness values for the Integer Physical Register File                                                                     | 72  |

| Table 11: FIT, IPC and Fitness values for the LSQ                                                                                                | 72  |

| Table 12: FIT, IPC and Fitness values for the L2 cache                                                                                           | 72  |

| Table 13: State-of-the-art and contributions of [29] in fault injection techniques microarchitectural simulators                                 |     |

| Table 14: Simulators configurations for [29] study                                                                                               | 76  |

| Table 15: Fault effect classification of Masked category for ESO mode in [31]                                                                    | 82  |

| Table 16: Fault effect classification of ESOR mode of study [31].                                                                                | 83  |

| Table 17: Vulnerability across modes of operations of study [31].                                                                                | 84  |

| Table 18: Baseline configuration of study [31].                                                                                                  | 85  |

| Table 19: Baseline configuration used to evaluate MeRLiN on RF, SQ, L1D and IQ         32 entries                                                |     |

| Table 20: Haswell-like configuration used to evaluate MeRLiN on IQ with 60 entries.                                                              | 97  |

| Table 21: MeRLiN's accuracy for gcc and bzip2 benchmarks.                                                                                        | 105 |

| Table 22: MeRLiN vs. Relyzer using exhaustive fault list                                                                                         | 112 |

| Table 23: Naïve parallel method vs. serial method (Times in 10 <sup>6</sup> cycles. Number parentheses denote speedup against serial execution). |     |

| Table 24: Memory latencies in SCC                                                                                                                | 127 |

| Table 25: Execution time of the proposed parallel method of LAA.                                                                                 | 130 |

| Table 26: Execution time of the parallel execution of LAA and LFSR test programs                                                                 | 130 |

| Table 27: Microarchitectural parameters of APM X-Gene 2                                                                                          | 134 |

| Table 28: Effects classification used in [35] and [167].                                                                                         | 136 |

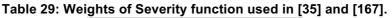

| Table 29: Weights of Severity function used in [35] and [167].                                                                                   | 138 |

| Table 30: <i>V<sub>min</sub></i> prediction model of the most sensitive core of X-Gene 2                                                         | 144 |

| Table 31: <i>V<sub>min</sub></i> prediction model of the most robust core of X-Gene 2                                                            | 145 |

| Table 32: Severity prediction model of the most sensitive core of X-Gene 2                                                                       | 146 |

| Table 33: Severity prediction model of the most robust core of X-Gene 2                                                                          | 147 |

| Table 34: Future work.         152 |

|------------------------------------|

|------------------------------------|

# PREFACE

This thesis was conducted in the Department of Informatics and Telecommunications of the National and Kapodistrian University of Athens during the period 2014-2018.

# 1. INTRODUCTION

The evolution in semiconductor technology and computer architecture gave designers the opportunity to boost the performance of modern computing systems that are used in several domains of information and communication technology systems. Despite the changes in Moore's Law [1] and Dennard Scaling [2], computer architects and designers are still able to improve processor performance by using more aggressive and sophisticated techniques. The combined effect of the progress in semiconductor technology and the evolution in computer architecture makes microprocessors more efficient, but on the other hand much more complex.

However, the scaling in performance is also accompanied by increase in the vulnerability (or decrease in reliability) of microprocessors due to: (a) the strict deadlines that are required to minimize Time-to-Market (TTM) (minimizing also the time needed to test the circuits), (b) the modern device integration techniques that make processors more vulnerable to the radiation and also increase the occurrence of manufacturing defects, and (c) the increased design complexity that makes the testing process of the microprocessor products very difficult and unaffordable for the available TTM. Specifically, the modern microprocessors face serious reliability issues during their entire life-cycle due to: (i) the errors that come from transient faults caused by cosmic rays, alpha particles and electromagnetic interference and are manifested as instantaneous flips of the values of real hardware bits, (ii) aging that leads to errors that appear at regular time intervals (intermittent errors) or exist indefinitely (permanent errors), and (iii) manufacturing defects that can either be manifested as permanent errors or lead to timing errors when the chips operate beyond their nominal voltage and frequency conditions. These manufacturing imperfections usually force computer architects to adopt pessimistic operation margins in terms of voltage in order to protect the chips, while sacrificing the energy efficiency of the delivered product.

Designers need to ensure sufficient reliability levels (according to the needs of the application domain) and energy efficiency levels of the chips after they are released to the market. The goal of this thesis is to propose different techniques that are applied in different phases of the entire life-cycle of a microprocessor in order to solve important reliability challenges of current and future microprocessor products.

# **1.1** The evolution of microprocessor design

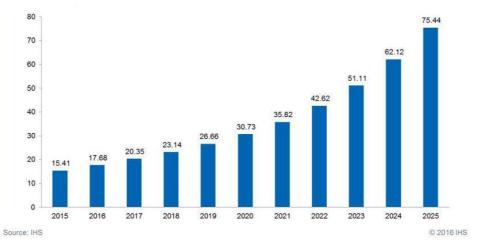

The use of electronic devices is increased every year far beyond all the pessimistic expectations from the 1971's, when the first commercial processor (Intel 4004 [3]) was released to the market. Indicatively, Figure 1 presents the increase of population of global connected electronic devices in the past years (starting from 2015) until nowadays (in 2018). Also, the same figure presents a forecast for the population of the devices that are going to be connected each year until 2025. All these devices are used in all the major fields of the electronics ecosystem such as Desktop PCs, Portable PCs, Smartphones and Tablets. From 2015 until this year (2018), we observe a 1.50X increase in the population of consumer electronic devices that corresponds to 23.14 billions of devices, while for the next years there will be an explosion (increase of 3.26X from 2018 to 2025 that is translated into 75.44 billions of devices). Note that the field of Internet of Things (IoT) that rapidly evolves the last years is a major contributor to this explosion of the total population of the electronic devices that are used in the entire ecosystem of electronics.

Figure 1: The evolution forecast of global connected electronic devices until 2025 in Billions of electronic devices (source: IHS, www.ihs.com).

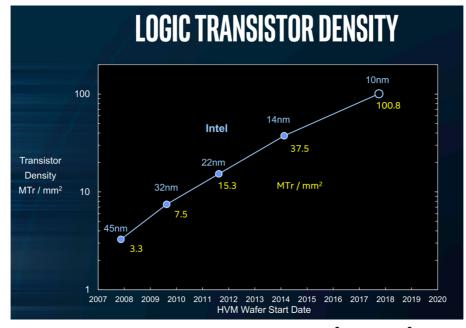

Moreover, as the size of transistors shrinks, much more transistors are inserted on the same silicon die. Figure 2 illustrates the transistor density of a chip die per  $mm^2$  in conjunction with the evolution of technology nodes starting from the 45nm lithography process that was widely used in 2008, until the 10nm that is currently used. From this figure, it is observed that there is a large increase equal to 30.55X in the transistors density that are used in the same die during the last 10 years, starting from 3.3 Millions per  $mm^2$  in 2008 to 100.8 Millions of transistors per  $mm^2$  in 2018. Today, the feature size that is used for the new massively produced chips is in the range of 10nm and is already announced that some chips will start to use 7nm technology (e.g. AMD is going to reveal AMD Starship with up to 48 Zen 2 Cores in Q2 of 2018 based on 7nm FinFET technology process [4]).

**Figure 2:** Transistor density per Million Transistor per mm<sup>2</sup> (MTr / mm<sup>2</sup>) until 2018 [5]. The increase of transistors density and the evolution in lithography process gives computer architects the opportunity to implement more aggressive and sophisticated mechanisms in their chips that deliver superior levels of scalability by building and using multi-dimensional transistors. These mechanisms that enhance performance of microprocessors include aggressive speculative mechanisms (e.g. branch prediction units, data and instruction prefetchers, and value predictors), larger capacity structures (caches, memories, queues) and mechanisms that exploit parallelism of different levels (Instruction-Level, Thread-Level and Data-Level parallelism). Figure 3 illustrates the

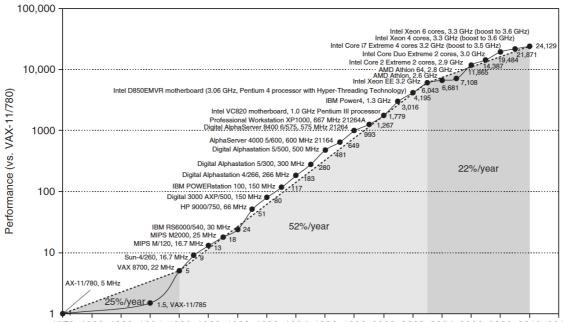

increase in microprocessor performance since 1978 compared to the performance relative of the VAX 11/780. From this figure, we observe a 25% increase in processor performance per year before 1986 that was largely technology driven. From 1987 to 2004, the increase in performance was about 52% per year that mainly came from more advanced architectural and organizational ideas. Finally, from 2003 to 2010, processor performance improvement has dropped to about 22% per year mainly due to the following obstacles: (a) heat dissemination, (b) little Instruction-Level Parallelism (ILP) left to exploit, and (c) limitations due to memory delays. These obstacles signal historic switch from relying solely on ILP to Thread-Level Parallelism (TLP) and Data-Level Parallelism (DLP) [6].

1978 1980 1982 1984 1986 1988 1990 1992 1994 1996 1998 2000 2002 2004 2006 2008 2010 2012

# Figure 3: Increase in processor performance relative to the VAX 11/780 as measured by the SPECint benchmarks.

However, the implementation of aggressive and sophisticated mechanisms to boost performance in conjunction with the decrease of the size of transistors make the chips more and more complex, while they also suffer from many reliability issues that are manifested before or after they are released to the market. There are many reports of microprocessors operational failures of real hardware chips that can come from: (i) transient faults [7] [8] [9], (ii) aging [10], and (iii) manufacturing defects that can be manifested as permanent errors [11] or can lead to operation divergences among the chips of the same design; this forces the designers to adopt pessimistic voltage and frequency operation margins sacrificing a part of the energy efficiency or the performance of the product in order to ensure the correct operation of microprocessors [12].

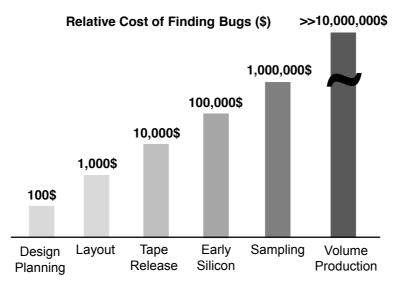

To handle all these reliability issues the major microprocessor manufacturers such as Intel, AMD, ARM and IBM spend a huge amount of human resources, time, chip area and money to protect the chips by developing techniques that are implemented either before or during the fabrication process of the chips or after they are released to the market. On top of all these challenges that the companies have to handle, they also have to face the strict deadlines of minimizing Time-to-Market (TTM) and satisfying the high requirements of the consumed electronic devices. Towards this direction, this thesis provides solutions that can be implemented in different phases of the life-cycle of microprocessors in order to boost their reliability.

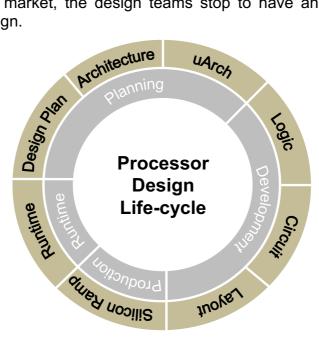

#### **1.2** Design life-cycle of microprocessors

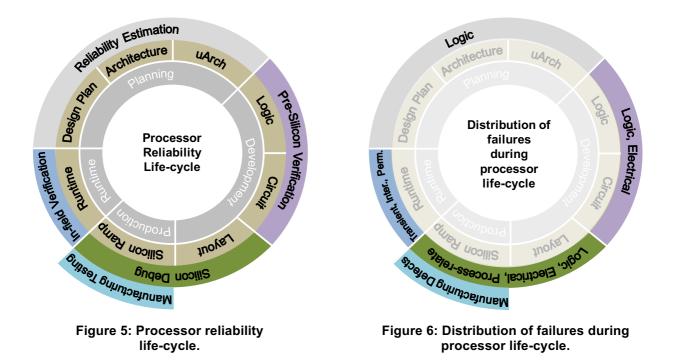

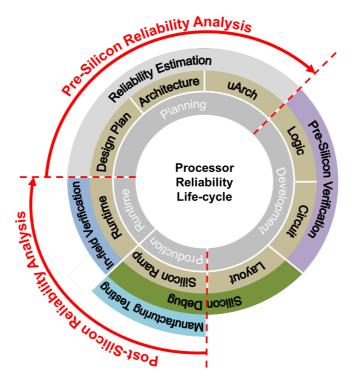

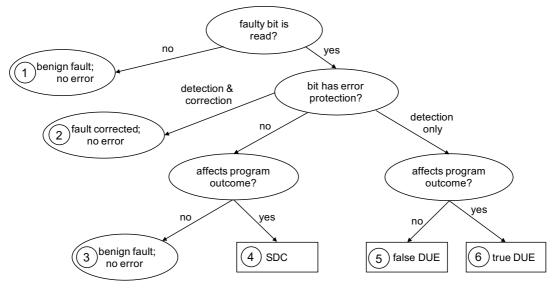

Each microprocessor product has a long life-cycle that consists of many design, analysis and manufacturing phases before it is integrated in a computing system and released to the market. Figure 4 presents all the design phases of a microprocessor that are summarized below:

• **Planning**: In this phase, computer architects and designers define the microprocessor product design and manufacturing strategy. In particular, they define: (i) the product requirements in terms of functionality, performance, power and reliability, (ii) the technology node that is going to be used, (iii) the design methodology, and (iv) the tools that are going to be used during the entire manufacturing procedure. All these decisions are guided according to the nature of the market segment that the product targets, the budget and finally the TTM. For instance, a microprocessor that targets the market of aerospace or automotive should satisfy different reliability and power consumption requirements compared to a product that is going to be used in the desktop market segment or in low-end consumer electronics.