W&M ScholarWorks

Dissertations, Theses, and Masters Projects

Theses, Dissertations, & Master Projects

2022

### Techniques For Accelerating Large-Scale Automata Processing

Hongyuan Liu William & Mary - Arts & Sciences, lliuhy@gmail.com

Follow this and additional works at: https://scholarworks.wm.edu/etd

Part of the Computer Sciences Commons

#### **Recommended Citation**

Liu, Hongyuan, "Techniques For Accelerating Large-Scale Automata Processing" (2022). *Dissertations, Theses, and Masters Projects*. William & Mary. Paper 1673275513. https://dx.doi.org/10.21220/s2-dbkj-z447

This Dissertation is brought to you for free and open access by the Theses, Dissertations, & Master Projects at W&M ScholarWorks. It has been accepted for inclusion in Dissertations, Theses, and Masters Projects by an authorized administrator of W&M ScholarWorks. For more information, please contact scholarworks@wm.edu.

Techniques for Accelerating Large-scale Automata Processing

Hongyuan Liu

Jinan, Shandong, China

Bachelor of Engineering, Shandong University, 2013 Master of Science, University of Hong Kong, 2016

A Dissertation presented to the Graduate Faculty of The College of William & Mary in Candidacy for the Degree of Doctor of Philosophy

Department of Computer Science

College of William & Mary January 2022

$\bigodot$  Copyright by Hongyuan Liu 2022

### APPROVAL PAGE

This Dissertation is submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

2 4.50

Hongyuan Liu

Approved by the Committee, January 2022

Adwait fog

Committee Chair Adwait Jog, Associate Professor, Computer Science College of William & Mary

Pradeep Kuman

Pradeep Kumar, Assistant Professor, Computer Science College of William & Mary

Zhenming Live

Zhenming Liu, Assistant Professor, Computer Science College of William & Mary

Weighen Mao

Weizhen Mao, Professor, Computer Science College of William & Mary

Zhiji Zhiji Zhao, Associate Professor University of California, Riverside

### ABSTRACT

The big-data era has brought new challenges to computer architectures due to the large-scale computation and data. Moreover, this problem becomes critical in several domains where the computation is also irregular, among which we focus on automata processing in this dissertation. Automata are widely used in applications from different domains such as network intrusion detection, machine learning, and parsing. Large-scale automata processing is challenging for traditional von Neumann architectures. To this end, many accelerator prototypes have been proposed. Micron's Automata Processor (AP) is an example. However, as a spatial architecture, it is unable to handle large automata programs without repeated reconfiguration and re-execution. We found a large number of automata states are never enabled in the execution but still configured on the AP chips, leading to its underutilization. To address this issue, we proposed a lightweight offline profiling technique to predict the never-enabled states and keep them out of the AP. Furthermore, we develop SparseAP, a new execution mode for AP to handle the misprediction efficiently. Our software and hardware co-optimization obtains  $2.1 \times$  speedup over the baseline AP execution across 26 applications.

Since the AP is not publicly available, we aim to reduce the performance gap between a general-purpose accelerator—Graphics Processing Unit (GPU) and AP. We identify excessive data movement in the GPU memory hierarchy and propose optimization techniques to reduce the data movement. Although our optimization techniques significantly alleviate these memory-related bottlenecks, a side effect of them is the static assignment of work to cores. This leads to poor compute utilization as GPU cores are wasted on idle automata states. Therefore, we propose a new dynamic scheme that effectively balances compute utilization with reduced memory usage. Our combined optimizations provide a significant improvement over the previous state-of-the-art GPU implementations of automata. Moreover, they enable current GPUs to outperform the AP across several applications while performing within an order of magnitude for the rest of them.

To make automata processing on GPU more generic to tasks with different amounts of parallelism, we propose ASYNCAP, a lightweight approach that scales with the input length. Threads run asynchronously in ASYNCAP, alleviating the bottleneck of thread block synchronization. The evaluation and detailed analysis demonstrate that ASYNCAP achieves significant speedup or at least comparable performance under various scenarios for most of the applications.

The future work aims to design automatic ways to generate optimizations and mappings between automata and computation resources for different GPUs. We will broaden the scope of this dissertation to domains such as graph computing.

### TABLE OF CONTENTS

| A  | Acknowledgments v |                                                                  |     |  |

|----|-------------------|------------------------------------------------------------------|-----|--|

| De | edicat            | tion                                                             | vi  |  |

| Li | st of             | Tables                                                           | vii |  |

| Li | st of             | Figures                                                          | ix  |  |

| 1  | Intr              | oduction                                                         | 2   |  |

|    | 1.1               | Towards Efficient Large-scale Automata Accelerator               | 3   |  |

|    | 1.2               | Reducing the Gap between GPGPU and Automata Accelerator          | 4   |  |

|    | 1.3               | Designing and Analyzing a Generic Automata Processing Scheme on  |     |  |

|    |                   | GPU                                                              | 5   |  |

|    | 1.4               | Dissertation Organization                                        | 5   |  |

| 2  | Bac               | kground                                                          | 7   |  |

|    | 2.1               | Automata                                                         | 7   |  |

|    | 2.2               | Automata Processor                                               | 8   |  |

|    | 2.3               | Graphics Processing Units (GPUs)                                 | 9   |  |

| 3  | Arcl              | hitectural Support for Efficient Large-Scale Automata Processing | 11  |  |

|    | 3.1               | Introduction                                                     | 12  |  |

|    | 3.2               | Background and Terminology                                       | 15  |  |

|    |                   | 3.2.1 NFA-based Pattern Matching                                 | 15  |  |

|    |                   | 3.2.2 Baseline Automata Processor (AP)                           | 16  |  |

|   | 3.3 | Motiv  | vation and Analysis                                               | 18 |

|---|-----|--------|-------------------------------------------------------------------|----|

|   |     | 3.3.1  | Topological Order and Normalized Depth                            | 18 |

|   |     | 3.3.2  | Analysis of Normalized Depth and Enabled NFA States $\ . \ . \ .$ | 20 |

|   |     | 3.3.3  | Analysis of Performance Benefits                                  | 21 |

|   | 3.4 | Desig  | n and Implementation of NFA Partitioning                          | 23 |

|   |     | 3.4.1  | Profiling-based Hot/Cold State Prediction                         | 24 |

|   |     | 3.4.2  | Where to Partition?                                               | 25 |

|   |     | 3.4.3  | How to Partition?                                                 | 26 |

|   |     | 3.4.4  | Discussion                                                        | 27 |

|   | 3.5 | Hardy  | ware Support for Intermediate Report Handling and Partitioned     |    |

|   |     | NFA    | Processing                                                        | 28 |

|   |     | 3.5.1  | Analysis of New Execution Modes for AP                            | 28 |

|   |     | 3.5.2  | Implementation Details                                            | 31 |

|   | 3.6 | Evalu  | ation Methodology                                                 | 33 |

|   |     | 3.6.1  | Applications                                                      | 33 |

|   |     | 3.6.2  | Experimental Setup                                                | 34 |

|   | 3.7 | Exper  | rimental Results                                                  | 36 |

|   | 3.8 | Relate | ed work                                                           | 41 |

|   | 3.9 | Concl  | usions                                                            | 42 |

| 4 | Wh  | v GPU  | s are Slow at Executing NFAs and How to Make them Faster          | 43 |

|   | 4.1 |        | $\mathbb{I}$ uction                                               | 44 |

|   | 4.2 |        | ground                                                            |    |

|   |     | 4.2.1  | Pattern Matching via NFAs                                         |    |

|   |     | 4.2.2  | NFA Processing on GPUs                                            |    |

|   | 4.3 |        | em and Previous Efforts                                           |    |

|   |     | 4.3.1  | Data Movement                                                     |    |

|   |     |        |                                                                   |    |

|   |                                                                     | 4.3.2    | Compute Utilization                                             | 50 |  |  |

|---|---------------------------------------------------------------------|----------|-----------------------------------------------------------------|----|--|--|

|   |                                                                     | 4.3.3    | Limitations of Prior Efforts                                    | 51 |  |  |

|   | 4.4                                                                 | Addre    | essing the Data Movement Problem via Matchset Analysis          | 52 |  |  |

|   |                                                                     | 4.4.1    | Inefficiencies in the Transition Table                          | 52 |  |  |

|   |                                                                     | 4.4.2    | Optimization I: A New Way to Store and Access Matchset and      |    |  |  |

|   |                                                                     |          | Topology Information (NewTran/NT) $\ldots \ldots \ldots \ldots$ | 54 |  |  |

|   |                                                                     | 4.4.3    | Optimization II: Matchset Compression (MaC)                     | 56 |  |  |

|   | 4.5                                                                 | Addre    | essing the Utilization Problem via Activity Analysis            | 57 |  |  |

|   |                                                                     | 4.5.1    | Analysis of Activation Frequency                                | 57 |  |  |

|   |                                                                     | 4.5.2    | Optimization III: Activity-based Processing                     | 58 |  |  |

|   |                                                                     | 4.5.3    | How do we choose the hot states?                                | 61 |  |  |

|   | 4.6                                                                 | Evalu    | ation Methodology                                               | 63 |  |  |

|   | 4.7                                                                 | Exper    | rimental Results                                                | 66 |  |  |

|   | 4.8                                                                 | Relate   | ed Work                                                         | 71 |  |  |

|   | 4.9                                                                 | Concl    | usions                                                          | 72 |  |  |

| 5 | Generalizing Automata Processing on GPUs by Leveraging Symbol-level |          |                                                                 |    |  |  |

|   | Para                                                                | allelism | 1                                                               | 74 |  |  |

|   | 5.1                                                                 | Intro    | luction                                                         | 75 |  |  |

|   | 5.2                                                                 | Backg    | ground                                                          | 79 |  |  |

|   | 5.3                                                                 | Async    | chronous Parallel Automata Processing on GPUs                   | 80 |  |  |

|   |                                                                     | 5.3.1    | Why do we need a new way to process Automata on GPUs?           | 80 |  |  |

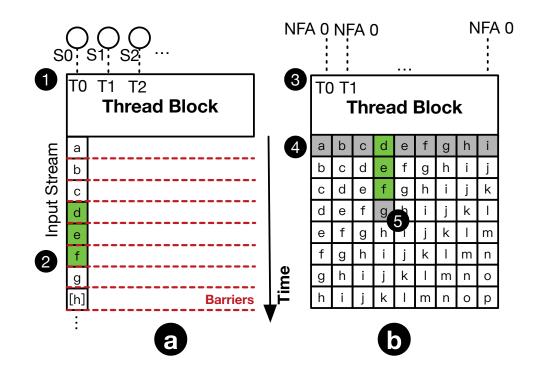

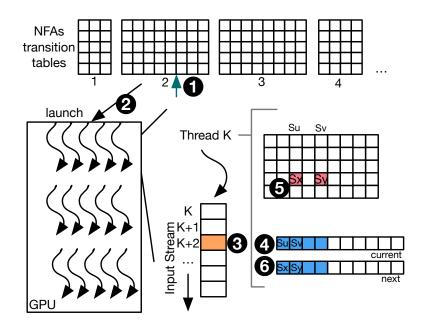

|   |                                                                     | 5.3.2    | Overview of Asynchronous Parallel Automata Processing           | 82 |  |  |

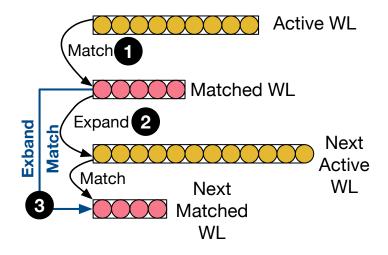

|   |                                                                     | 5.3.3    | Design and Implementation                                       | 84 |  |  |

|   |                                                                     | 5.3.4    | Analysis                                                        | 87 |  |  |

|   | 5.4                                                                 | Chara    | acterization of Synchronous Automata Processing and ASYNCAP     | 89 |  |  |

|   |                                                                     | 5.4.1    | Applications Configurations                                     | 89 |  |  |

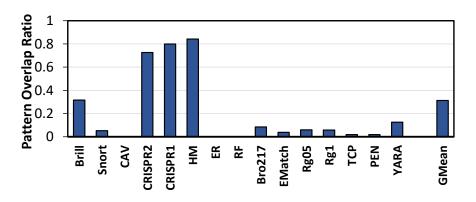

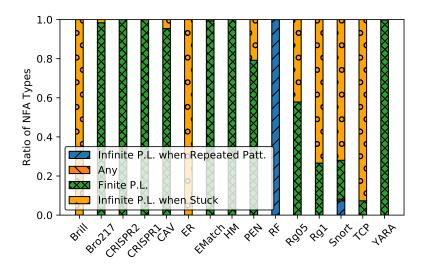

|    |       | 5.4.2   | Comparison of Identified Patterns         |     | 89  |

|----|-------|---------|-------------------------------------------|-----|-----|

|    |       | 5.4.3   | Characterization of Work by Emulation     | •   | 92  |

|    |       | 5.4.4   | Comparison of Useful Work                 | •   | 95  |

|    |       | 5.4.5   | Comparison of Total Work                  |     | 95  |

|    |       | 5.4.6   | How balance the work is in ASYNCAP?       | •   | 96  |

|    | 5.5   | Evalu   | ation                                     | •   | 97  |

|    |       | 5.5.1   | Evaluation Configurations                 | •   | 97  |

|    |       | 5.5.2   | Experimental Results                      | •   | 98  |

|    |       | 5.5.3   | Analysis of Pattern Lengths               | •   | 102 |

|    | 5.6   | Relate  | ed Work                                   | •   | 105 |

|    |       | 5.6.1   | Mapping Automata to Computation Resources | •   | 106 |

|    |       | 5.6.2   | Increasing Parallelism of Automata        | •   | 106 |

|    | 5.7   | Concl   | lusions                                   | •   | 107 |

| 6  | Con   | clusion | ns and Future Work                        |     | 109 |

| Ŭ  | 6.1   |         | nary of Dissertation Contributions        |     |     |

|    | 6.2   |         | e Research Directions                     |     |     |

|    | 0.2   | rutur   | e Research Directions                     | • • | 110 |

| Bi | bliog | raphy   |                                           |     | 112 |

| Vi | ita   |         |                                           |     | 133 |

### ACKNOWLEDGMENTS

This dissertation would not have been possible without the help and support of many people.

I would like to express my deepest appreciation to my advisor, Adwait Jog for his helpful and valuable guidance throughout my Ph.D. journey. I have been extremely lucky to work with Adwait and I enjoyed my Ph.D. life. Adwait has been a role model for me. I also thank his family for their support.

I would like to thank our collaborators. I am so grateful to Sreepathi Pai for his valuable ideas and insights, which have greatly helped my automata projects in this dissertation. I also wish to thank Onur Kayıran for his knowledge and insights in the automata accelerator project. I very much appreciate Bogdan Nicolae, Sheng Di, and Franck Cappello for the valuable mentorship on the DNN project when I was a visiting student at ANL.

I would like to thank my dissertation committee members, Pradeep Kumar, Zhenming Liu, Weizhen Mao, and Zhijia Zhao, for their valuable feedback, suggestions, and time.

I would like to thank Meena Arunachalam for the mentorship when I interned at Intel.

I thank the entire technical staff for managing computing facilities at William & Mary. Special thanks to Eric Walter, who helped me with my requests efficiently. I also thank the Administrative Director of the computer science department, Vanessa Godwin, for being efficient, professional, and caring.

I am especially thankful to our lab members Mohamed Assem Ibrahim, Gurunath Kadam, Ying Li, and Haonan Wang for the support, companionship, and discussions. It's a bit sad to say goodbye to our previous office McG-101B.

I would like to extend my gratitude to all my friends. Especially, I am also very fortunate to have a group of dear friends in William & Mary!

I am deeply indebted to my family. My wife and our cat Lume always support me.

I also thank my parents and other family members for their care and encouragement without which I would not be what I am today.

To my family

### LIST OF TABLES

| 3.1 | The effectiveness of profile-based prediction. $©$ 2018 IEEE          | 25 |

|-----|-----------------------------------------------------------------------|----|

| 3.2 | List of evaluated applications: "RStates" stands for reporting states |    |

|     | and "MaxTopo" stands for maximum topological order across NFAs.       |    |

|     | "Grp" stands for resource requirement groups: High (H), Medium        |    |

|     | (M), Low (L). © 2018 IEEE                                             | 34 |

| 3.3 | Summary of Execution Scenarios. © 2018 IEEE                           | 35 |

| 3.4 | Runtime statistics for AP and BaseAP/SpAP (under $1\%$ profiling      |    |

|     | input): The first three columns show the number of executions on the  |    |

|     | AP, BaseAP mode and SpAP mode, respectively. "EStalls" stands         |    |

|     | for the stalls caused by enable operations for handling simultaneous  |    |

|     | intermediate reports. "JumpRatio" is defined as the proportion of     |    |

|     | cycles skipped in the SpAP mode. © 2018 IEEE. $\ldots$                | 39 |

| 4.1 | Overview of the evaluated schemes on GPU                              | 63 |

| 4.2 | Characteristics of evaluated NFA applications.                        | 65 |

| 4.3 | Absolute throughput with our schemes (MB/s). The best performance     |    |

|     | among GPU schemes is highlighted.                                     | 66 |

| 5.1 | Three levels of parallelism in NFA processing                         | 76 |

| 5.2 | Categorization of Prior Works                                         | 81 |

| 5.3 | Comparison of Time Complexity. $n$ : number of symbols; $m$ number    |    |

|     | of states.                                                            | 88 |

| 5.4 | Overview of Evaluated Applications                                    | 90 |

| 5.5 | Characteristics of applications based on our execution models: Our                                           |

|-----|--------------------------------------------------------------------------------------------------------------|

|     | key observations: (1) The GPU utilization depends on applications.                                           |

|     | (2) Although ASYNCAP has higher time complexity, in reality only                                             |

|     | 5% more useful work is needed on average. (3) Most applications                                              |

|     | balance the work across threads well, but rarely the work is severely                                        |

|     | imbalanced. $\ldots \ldots $ 92 |

| 5.6 | Absolute throughput (in MB/s) of evaluated applications under the                                            |

|     | scenarios with different amounts of parallelism                                                              |

| 5.7 | Pattern Lengths of Applications                                                                              |

### LIST OF FIGURES

| 2.1 | Illustrating an Automata Processor and the NFA configured to it 8               |

|-----|---------------------------------------------------------------------------------|

| 2.2 | Overview of GPU Memory Hierarchy                                                |

| 3.1 | A large portion of NFA states are cold (never-enabled) but are still            |

|     | configured on the AP leading to its under<br>utilization.<br>C 2018 IEEE 14     |

| 3.2 | A homogeneous NFA that accepts regular expression                               |

|     | a((bc) (cd)+)f: the doubled circle represents starting state                    |

|     | and the hexagon represents reporting state. $\bigcirc$ 2018 IEEE. $\ldots$ . 16 |

| 3.3 | The figure illustrates the first execution cycle of an AP configured            |

|     | with the NFA shown in Figure 3.2. S1 is enabled when input symbol               |

|     | <b>a</b> arrives, which activates S1, and enables S2 and S4 in the next cycle.  |

|     | Downward arrows represent the enable signal being fed to routing                |

|     | matrix in the current cycle. Upward arrows enable successor states for          |

|     | the next cycle. The physical connections between STEs and routing               |

|     | matrix are bi-directional, which are represented by the dashed arrows.          |

|     | © 2018 IEEE                                                                     |

| 3.4 | Illustration of topological ordering and normalized depth. $\bigodot$ 2018      |

|     | IEEE                                                                            |

| 3.5 | Distribution of normalized depth for NFA states. For presentation               |

|     | purposes only, normalized depth is classified as: i) shallow $([0-0.3))$ ,      |

|     | ii) medium ([0.3–0.6)), and iii) deep ([0.6–1]). © 2018 IEEE 21                 |

| 3.6  | An illustrative figure showing that by not configuring cold states on           |    |

|------|---------------------------------------------------------------------------------|----|

|      | AP, all the hot states can fit onto an AP at the same time, reducing            |    |

|      | the number of re-executions over the input and hence saving time. ©             |    |

|      | 2018 IEEE                                                                       | 22 |

| 3.7  | Partitioning an NFA by the partition layer. © 2018 IEEE                         | 27 |

| 3.8  | Constrained states are cold states but configured on the AP due to the          |    |

|      | constraints in our topological-order-based partitioning scheme. Conse-          |    |

|      | quently, some AP resources are underutilized with a few applications.           |    |

|      | © 2018 IEEE                                                                     | 28 |

| 3.9  | Illustration of performance benefits under realistic partitioning: be-          |    |

|      | cause of the $jump$ operation, only a portion of input symbols are              |    |

|      | executed in the SpAP mode execution. © 2018 IEEE.                               | 29 |

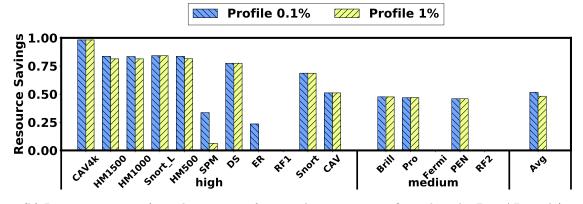

| 3.10 | Speedup and Resource Savings on AP. © 2018 IEEE                                 | 36 |

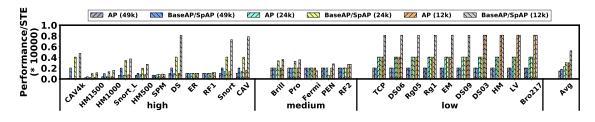

| 3.11 | Performance per STE of various AP sizes with BaseAP/SpAP execu-                 |    |

|      | tion considering 1% profiling input. © 2018 IEEE. $\ldots$                      | 37 |

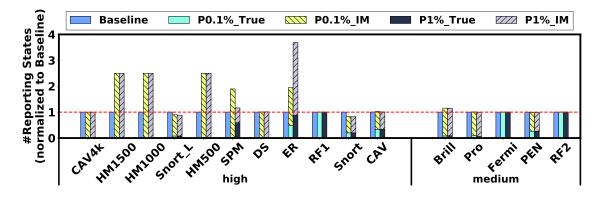

| 3.12 | Comparison of number of reporting states: "IM" stands for interme-              |    |

|      | diate reporting states. "True" stands for original reporting states on          |    |

|      | BaseAP mode. "P" stands for profiling. © 2018 IEEE                              | 38 |

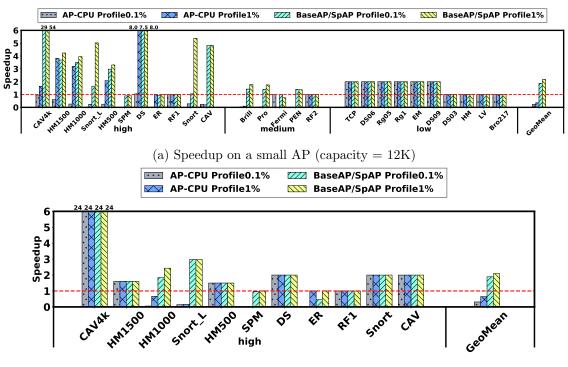

| 3.13 | Sensitivity on the different capacities of AP chip. $\bigodot$ 2018 IEEE        | 40 |

| 4.1  | Working example of an NFA                                                       | 47 |

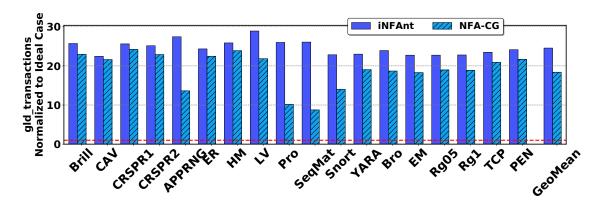

| 4.2  | The data movement normalized to the ideal cases: two prior schemes              |    |

|      | use $25 \times$ and $18 \times$ compared to the ideal case where only the input |    |

|      | stream is loaded. The evaluation methodology is discussed in Section 4.6.       | 52 |

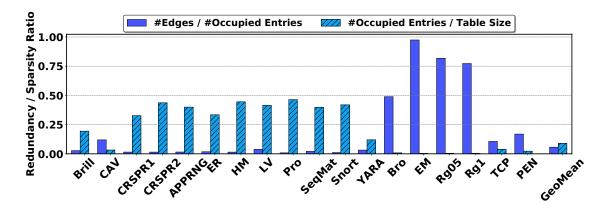

| 4.3  | Two metrics showing the redundancy (#edges/#occupied-entries)                   |    |

|      | and sparsity (#occupied-entries/table-size) in the transition table.            |    |

|      | Lower is worse.                                                                 | 53 |

|      |                                                                                 |    |

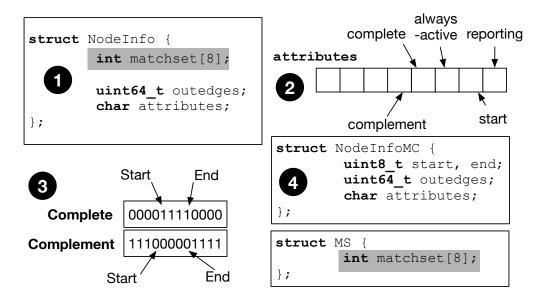

| 4.4  | Illustrating the per-node data structure of NewTran (NT). Shaded                           |    |

|------|--------------------------------------------------------------------------------------------|----|

|      | variables are in the local memory and others are in the registers                          | 55 |

| 4.5  | Percentage of states whose matchesets are complete, complement, or                         |    |

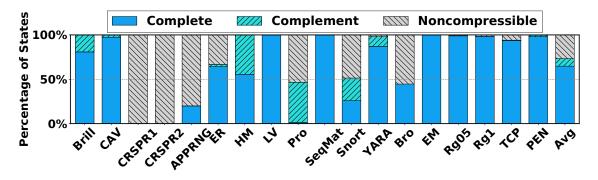

|      | not compressible.                                                                          | 56 |

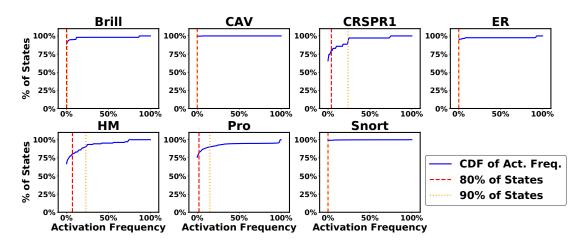

| 4.6  | The activity profile of the states. For the majority of applications,                      |    |

|      | 80% of non-starting states are activated for only less than $1%$ of the                    |    |

|      | processed symbols.                                                                         | 58 |

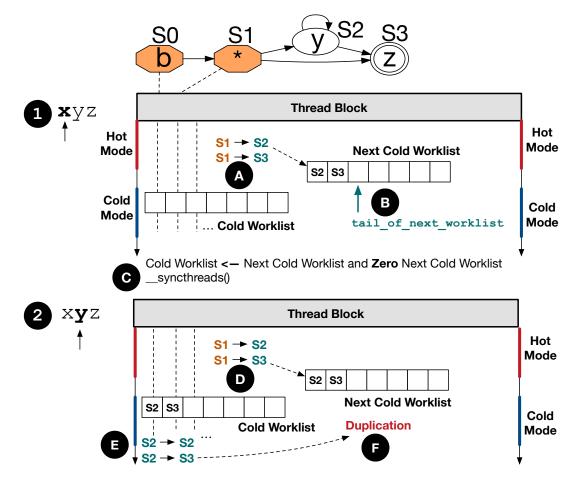

| 4.7  | Illustrating the activity-based processing                                                 | 60 |

| 4.8  | Throughput sensitivity to the selection of hot states. Detailed evalua-                    |    |

|      | tion methodology is in Section 4.6. HotStart (or HotStart_Opt,                             |    |

|      | an optimized version) has the best performance among these selection                       |    |

|      | schemes. Hence, we choose the always-active start states as hot states.                    | 61 |

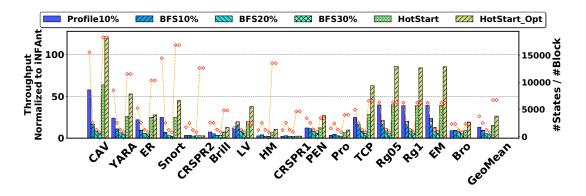

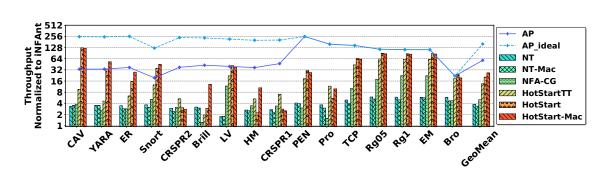

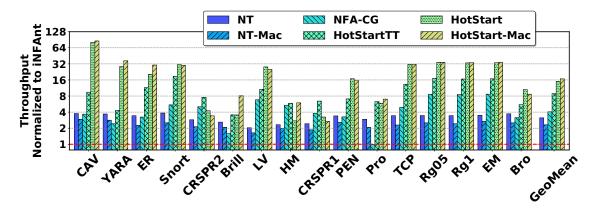

| 4.9  | Throughput enhancement results normalized to INFANT. On average                            |    |

|      | HotStart-MaC achieves $26.5\times$ speedup across 16 applications. The                     |    |

|      | best GPU results outperform an AP chip in 5 applications (CAV,                             |    |

|      | YARA, Snort, LV, and Bro).                                                                 | 66 |

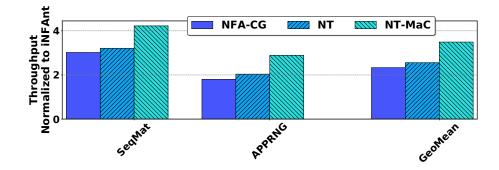

| 4.10 | Throughput enhancement for the applications without $always$ -active                       |    |

|      | start states in the single input stream scenario. Our schemes outper-                      |    |

|      | form NFA-CG and INFANT by at least 9% and 2.6×, respectively. $% \mathcal{A} = 10^{-10}$ . | 68 |

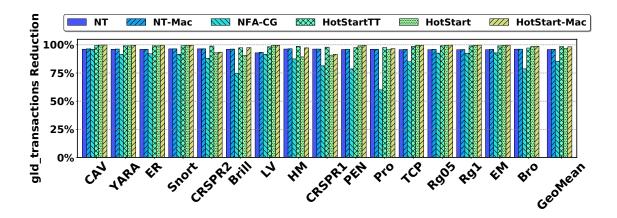

| 4.11 | Effect on data movement reduction: our schemes use significantly                           |    |

|      | fewer gld_transactions than prior work. For example, HotStart-                             |    |

|      | MAC reduces gld_transactions by 99.3% over infant                                          | 69 |

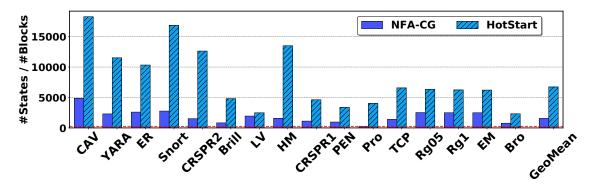

| 4.12 | Effect on the number of NFA states per thread block (a proxy for                           |    |

|      | compute utilization). More states are handled per thread block in                          |    |

|      | HotStart.                                                                                  | 69 |

| 4.13 | Performance sensitivity to Volta GPU Architecture. Both                                                                                                   |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | HOTSTART-MAC and HOTSTART show more than $15 \times$ speedup over                                                                                         |

|      | INFANT, indicating their effectiveness on newer GPU architectures 70                                                                                      |

| 5.1  | Illustrating an NFA that accepts $a*.x*y$ . $S_0$ and $S_1$ are all-input                                                                                 |

|      | starting states, which are always active in the execution 80                                                                                              |

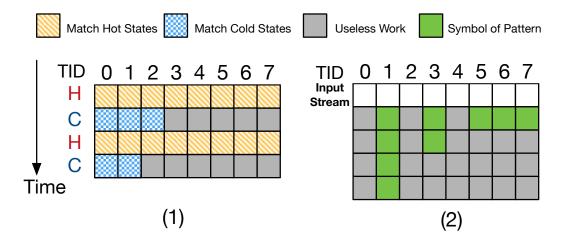

| 5.2  | Revisiting traditional synchronous automata processing on GPU (a)                                                                                         |

|      | and the basic idea of ASYNCAP (b). The executions try to find                                                                                             |

|      | pattern def in an input stream abcdefg 83                                                                                                                 |

| 5.3  | Worklist holds active states or matched states. WL stands for worklist. 85                                                                                |

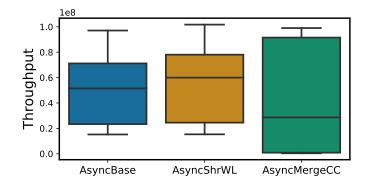

| 5.4  | Performance of Selected Implementations of ASYNCAP. Evaluation                                                                                            |

|      | methodology is described in Section 5.5                                                                                                                   |

| 5.5  | Illustrating our implementation of ASYNCAP                                                                                                                |

| 5.6  | Synchronous execution identifies disjoint patterns; Patterns identified                                                                                   |

|      | by different threads in a<br>synchronous execution may overlap. $\ldots$ . 91                                                                             |

| 5.7  | Ratio of Overlapped Patterns $(R)$ in Evaluated Applications $\ldots \ldots 91$                                                                           |

| 5.8  | Illustrating the Execution Models of Synchronous (GPU-NFA) and                                                                                            |

|      | Asynchronous (ASYNCAP) Automata Processing on GPU 93                                                                                                      |

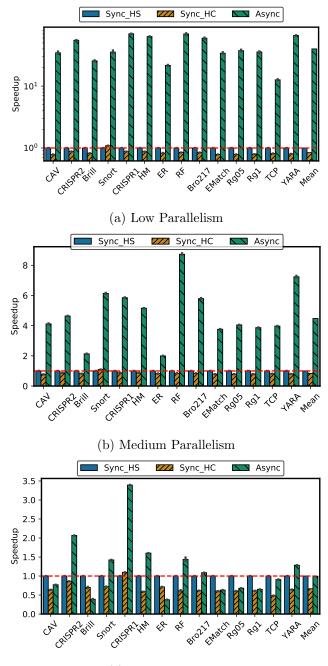

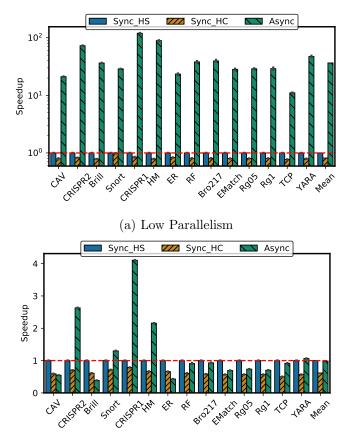

| 5.9  | Performance of synchronous and asynchronous automata executions                                                                                           |

|      | on GPU under different amounts of parallelism                                                                                                             |

| 5.10 | Performance sensitivity to Ampere GPU Architecture                                                                                                        |

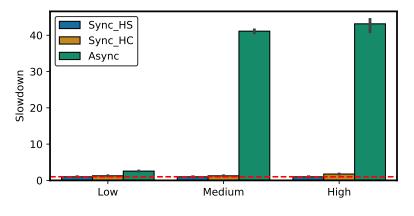

| 5.11 | Slowdown of PEN                                                                                                                                           |

| 5.12 | 2 Large portion of NFAs can never have infinite long patterns 104                                                                                         |

| 5.13 | 3 When limiting the pattern length to 1K, PEN does not exhibit slow-                                                                                      |

|      | down (i.e., slowdown is less than 1). $\dots \dots \dots$ |

Techniques for Accelerating Large-scale Automata Processing

### Chapter 1

# Introduction

For decades, computing has relied on Moore's law to provide abundant computing resources. However, achieving continued growth in terms of performance and energy efficiency has become extremely challenging due to near-end of Moore's law and Dennard scaling. Being compute-centric [25], the current general-purpose von Neumann architectures (CPUs and GPUs) need to fetch instructions/data from memory involving costly operations in terms of energy and speed. Further, achieving fine-grain parallelism and synchronization on these general-purpose processors is difficult from both software and hardware perspectives [7]. Therefore, it is very challenging for these conventional processors to efficiently execute all types of computations.

To address such inefficiencies, domain-specific accelerators (DSAs) are being developed to achieve ASIC-like performance and at very high energy efficiency. A plethora of DSAs have emerged in recent years from both industry and academia—Google's Tensor Processing Unit (TPU) [58] and Pixel Visual Core [4] for machine learning and image processing workloads respectively; NVIDIA's Deep Learning Accelerator (DLA) [3]; ARM's Trillium Project [2]; Microsoft's Brainwave [1]; the DianNao ML accelerator family [39, 40, 45]; GenAx and Darwin for bioinformatics [49], and many more.

This dissertation considers an important domain—automata processing. Similar to the aforementioned examples, many accelerators are proposed to accelerate automata processing [44, 98, 47, 21]. Automata work as computation kernels of a large set of applications used in different areas such as machine learning [93, 112], bioinformatics [34, 90], and network intrusion detection [10, 131]. However, in the big-data era, automata applications are also growing fast. The applications require many automata and input streams running at the same time. For example, ClamAV [6] is an application containing a lot of virus patterns, which are accumulated very fast with the increased number of internet viruses.

This dissertation focuses on tackling the large-scale automata processing problem on both domain-specific accelerators and general-purpose accelerators.

We study three aspects for efficient large-scale automata processing: 1) How to make current automata DSAs (i.e., Automata Processor) efficient for large-scale automata processing [66]? 2) How can we reduce the gap between the general-purpose accelerator (i.e., General-purpose Graphics Processing Units, GPGPUs) and the DSA (i.e., Automata Processor) for large-scale automata processing [69]? 3) How do we generalize the automata processing on GPU to adapt to various automata task sizes?

#### 1.1 Towards Efficient Large-scale Automata Accelerator

We focus on Automata Processor [44] (AP), which is one of the recently proposed Automata DSAs. We found a fundamental problem of AP—it is unable to handle large-scale automata programs without repeated reconfiguration and re-execution.

To achieve higher throughput in those large-scale automata applications, we propose efficient architectural support for large-scale automata processing. Our mechanisms are based on our key observation that not all states of the automata are enabled during execution, and hence need not be configured to the AP. Specifically, a large fraction of states unnecessarily take space in the AP chip but are not part of any state transitions, leading to its underutilization. To address this problem, we propose a profiling scheme to predict which states are not needed to be configured to AP. We propose a lightweight misprediction handling approach working as an execution mode of AP with marginal hardware overhead. The detailed experiments demonstrate that our software/hardware co-optimization significantly improves the performance of AP as well as performance per area.

### 1.2 Reducing the Gap between GPGPU and Automata Accelerator

GPUs are massively parallel accelerators that are widely used and available on the market. Besides its ability in graphics, GPUs also accelerate many general-purpose workloads such as machine learning and scientific computing. Execution of automata on highly parallel architectures like GPUs, therefore, appears very attractive. However, automata applications are very hard to accelerate on traditional von Neumann architectures. In this direction, we analyze the bottlenecks of the large-scale automata processing on GPU. Specifically, we observe two major bottlenecks: 1) excessive data movement through the GPU memory hierarchy is needed for *every* input byte; 2) many threads are idle in the execution due to the characteristics of automata execution.

To tackle the two bottlenecks, we propose new data structures and parallel execution mechanisms tailored for GPU. The new data structures fit the topology of NFA into GPU registers, which avoids the data movement for transition table look-ups. Our parallel execution mechanisms map the active states to threads while mapping the infrequently active states to worklists. These optimizations not only outperform the state-of-the-art GPU automata processing approaches but also reduce the gap between GPU and AP into an order of magnitude. Moreover, for several applications we evaluated, our approach outperforms AP.

### 1.3 Designing and Analyzing a Generic Automata Processing Scheme on GPU

To make automata processing on GPU more generic for tasks with different parallelism, we propose ASYNCAP, an approach that processes automata asynchronously on GPU. Our approach exploits an additional source of parallelism that scales with the length of an input stream. As the input stream is often long enough, ASYNCAP enables all tasks to have enough parallelism that can utilize all GPU cores. Each thread of ASYNCAP works asynchronously, reducing the overhead incurred by thread block synchronization.

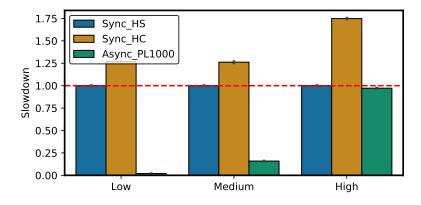

Theoretically, ASYNCAP has more time complexity than the traditional synchronous automata processing approaches on GPUs. However, no prior work has studied the amount of work in practice. To understand the amount of work needed in reality, our detailed characterization of synchronous automata execution and ASYNCAP demonstrates that ASYNCAP only incurs marginal more work on average across the evaluated applications.

For most of the applications, the evaluation demonstrates that a significant speedup is obtained when the original parallelism of a task is not enough. Further, even when the task is equipped with enough parallelism originally, the new approach achieves comparable performance to the state-of-the-art GPU automata processing engine.

#### 1.4 Dissertation Organization

The rest of this dissertation is organized as follows. Chapter 2 introduces the background for automata, Automata Processor (AP), and General-purpose Graphics Processing Units (GPGPUs). Chapter 3 introduces our observation that the current automata processor cannot efficiently execute large-scale automata processing. Based on our key observations that a large fraction of states are never enabled, we propose software-hardware co-design optimizations for AP to accelerate large-scale automata processing. Chapter 4 answers why GPUs are not efficient at executing automata and propose software approaches to accelerate it. Our optimizations reduce the gap between a general-purpose accelerator (GPU) and a domain-specific accelerator (AP) and even outperform AP for a few applications. Chapter 5 focuses on the problem that automata processing tasks may not always have enough parallelism to utilize GPU cores. To address this problem, we propose a more generic scheme that exploits symbol-level parallelism, achieving at least comparable performance as the state-of-the-art scheme on GPU for most of the evaluated applications. Chapter 6 summarizes the dissertation and discusses the future work.

### Chapter 2

## Background

### 2.1 Automata

Automata are also known as finite state machines (FSMs). Deterministic Finite Automaton (DFA) and Non-deterministic Finite Automaton (NFA) are two commonly used representations. DFA allows only one *active* state for each symbol. On the contrary, NFA allows multiple active states, which is ideal for parallel processing. The NFA used in Automata Processor is Glushkov NFA (aka homogeneous NFA) [51]. In this dissertation, we focus on Glushkov NFA and use *automata* or NFA to term it.<sup>1</sup> We refer the readers to the classical textbooks for the basic knowledge of automata theory [102].

NFA and matching process. An NFA is a directed graph where each node represents a state and each edge represents a state transition. Every state in the NFA has a *matchset* that contains the alphabets (symbols) it matches. Every NFA has at least one *start* state and at least one *reporting* state. The matching process begins by activating the start states. An NFA consumes one symbol at a time from the input stream. For each symbol, all currently active states attempt to match the incoming symbol with their matchset. If any of them match, they activate their successors. Unlike DFA, where only one state is active, NFAs can have multiple states active simultaneously—making them ideal for

<sup>&</sup>lt;sup>1</sup>Those representations can be transformed with each other, with the same expressiveness.

parallel architectures. If a reporting state matches an input symbol, it generates a report showing that a relevant pattern has been observed in the input stream. Usually, all starting states are always-active, unless a user wants to search patterns that only start at a certain position of the input stream.

### 2.2 Automata Processor

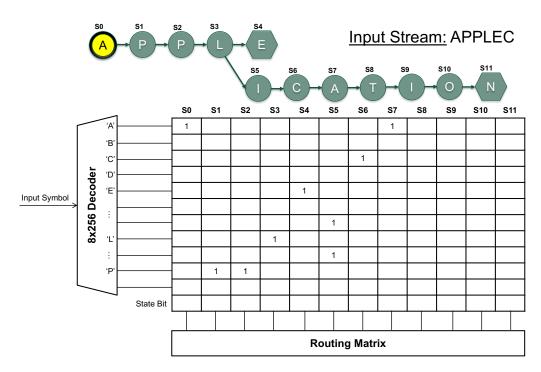

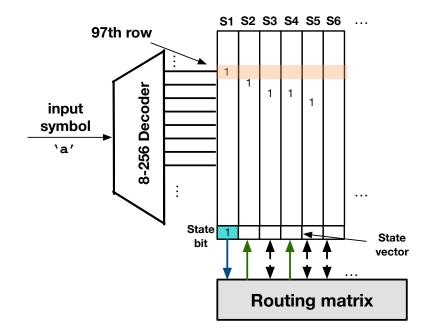

Figure 2.1: Illustrating an Automata Processor and the NFA configured to it

Automata Processor (AP) is a memory-centric accelerator for finite state automata processing by implementing NFA states and state transitions in memory. AP exploits the high parallelism in DRAM. Figure 2.1 illustrates an AP and the NFA configured to it. The matcheset of each state is stored in the DRAM columns. For example, S0 accepts symbol A, then the bitset of A is mapped to the first column. The transitions are configured to the *routing matrix*. Each cycle, the  $8 \times 256$  decoder selects the row of the incoming symbol. If a state accepts the incoming symbol (i.e., its state bit is 1), then the routing matrix sets the state bit of its successors. The entire input stream is processed sequentially at the

rate of one symbol per cycle.

We refer the readers to prior work [44, 126] and Chapter 3.2 for more details of AP.

### 2.3 Graphics Processing Units (GPUs)

GPU was an accelerator designed for computer graphics originally. Now, GPUs are found in a wide range of computer systems such as data centers, embedded systems, mobile phones, personal computers, workstations, and game consoles [67, 68, 136, 54]. Compared to the CPU, GPU provides much higher instruction throughput and memory bandwidth than the CPU within a similar price and power envelope. Many applications leverage these higher capabilities to run faster on the GPU than on the CPU [129, 137, 134, 133, 132, 135], making GPU a general-purpose accelerator. We refer the readers to this document [7] for more background about GPU.

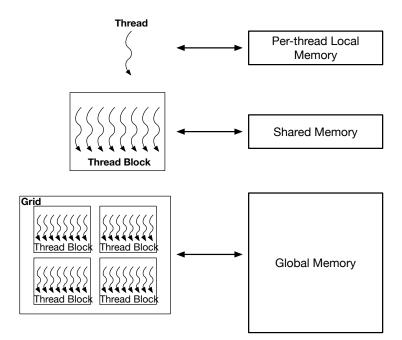

Figure 2.2: Overview of GPU Memory Hierarchy

**Programming model and memory hierarchy.** GPU uses SIMT programming model [7, 64]. The code running on the device (i.e., *kernel*) is launched in a *grid*. The grid

consists of multiple *thread blocks* (aka Cooperative Thread Arrays, CTA, or workgroups). A thread block contains one or more *warps* where 32 *threads* are grouped. The thread block scheduler assigns thread blocks to stream multiprocessors (SMs) in a many-to-one manner depending on the SM resources and the requirements of thread blocks. In each cycle, the warp schedulers issue an instruction from an active warp to the SIMD executions units. The independent scheduled multiple warps lead to high throughput because of better latency hiding [57, 56].

Figure 2.2 shows the memory hierarchy corresponding to the programming model. Local memory is private to each thread. While the local memory can use cache hierarchy in recent GPU architectures, it is located in the off-chip DRAM. Shared memory is allocated to each thread block. The threads within a thread block can communicate through the low-latency on-chip shared memory. Global memory is located in the off-chip DRAM which is accessible to all threads within the same CUDA context.

### Chapter 3

# Architectural Support for Efficient Large-Scale Automata Processing

The Automata Processor (AP) accelerates applications from domains ranging from machine learning to genomics. However, as a spatial architecture, it is unable to handle larger automata programs without repeated reconfiguration and re-execution. To achieve high throughput, this paper proposes for the first time architectural support for AP to efficiently execute large-scale applications. We find that a large number of existing and new Non-deterministic Finite Automata (NFA) based applications have states that are never enabled but are still configured on the AP chips leading to their underutilization. With the help of careful characterization and profiling-based mechanisms, we predict which states are never enabled and hence need not be configured on AP. Furthermore, we develop SparseAP, a new execution mode for AP to efficiently handle the mis-predicted NFA states. Our detailed simulations across 26 applications from various domains show that our newly proposed execution model for AP can obtain  $2.1 \times$  geometric mean speedup (up to  $47 \times$ ) over the baseline AP execution.

#### 3.1 Introduction

Many applications from domains such as genomics, malware detection, machine learning, and data analytics exhibit high levels of parallelism and are being accelerated through the use of *spatial architectures* that can exploit higher levels of parallelism than CPUs and also can significantly reduce data movement [39, 71, 45, 49, 110, 47, 100, 73, 19]. Spatial architectures usually consist of many interconnected processing elements that expose a very high degree of parallelism. Field-programmable gate arrays (FPGAs) are a classic example; the systolic-array-based Matrix Multiply Unit in Google's Tensor Processing Unit [58] is also a spatial architecture. One of the fundamental challenges with spatial architectures is that program size is a first order concern – there are a fixed number of states available and a spatial program must fit *completely* to begin execution. Otherwise, execution may be impossible, or in the best case multiple rounds of reconfiguration and re-execution may be required that can incur significant performance penalties [144]. On traditional von Neumann architectures, these issues can typically be handled by traditional mechanisms such as context switching and virtualization. However, the large size of the spatial program state means that these techniques do not transfer directly. Some of these issues affect also traditional architectures like the Graphics Processing Units (GPUs), whose massive parallelism also means that the amount of state is often prohibitively large to support efficient multitasking [109, 80, 65, 38].

In this paper, we focus on providing architectural support for executing largescale tasks on a special class of spatial architectures, known as automata processors (APs) [44]. These architectures accelerate the processing of Non-deterministic Finite Automata (NFA), a widely used representation of Finite State Machines (FSMs). FSMs are foundational in a wide range of application domains such as DNA sequence matching, network intrusion detection and machine learning [152, 113, 91, 33, 81, 121]. Although many existing approaches [36, 146, 154, 88] accelerate NFA processing on CPUs or GPUs, none of them completely solve the problem of data movement caused by irregular accesses due to NFA transition table lookups. In comparison, the AP executes NFAs natively and achieves significant performance speedup [123, 76] primarily because of: a) AP's massive parallelism where NFA states are mapped to columns in DRAM and can be activated independently and simultaneously in a given cycle; and b) AP's in-memory processing capability that handles NFA transitions without data movement between processor and memory.

An AP half-core (the basic processing unit of AP) can hold up to 24K states. However, in future, we expect that the NFA-based applications are going to scale both in terms of the number of NFAs per application and the number of states in an NFA. We expect this scaling from at least two aspects. First, in the era of big-data, the new applications will likely be mining even larger databases. For example, ClamAV [6], an anti-virus application, uses a variant of regular expression to specify each virus signature in an everenlarging database. The number of NFA states constructed from these signature regular expressions is consequently larger and state-of-the-art AP chips can no longer hold all the states at once. Second, a number of existing and newly proposed techniques enhance the throughput of FSM processing, but only by increasing the number of states. For example, existing AP supports duplicating NFAs to run multiple input symbol streams in parallel [5]; newly proposed Parallel Automata Processor [106] duplicates NFAs for parallel enumeration; and the Multi-stride NFAs [35, 29] transformation increases the number of transitions for processing multiple symbols at one step. Current AP chips execute these applications with a large number of NFAs/states by making independent batches of NFAs and executing each batch on the entire input while reconfiguring the AP between each batch.

To address the performance inefficiencies from repeated re-executions, we propose hardware and software support for large-scale NFA-based applications that currently do not fit in the AP chips. Our mechanisms are based on our key observation that not all states of an NFA are enabled during execution, and hence need not be configured to the AP. Specifically, a large fraction of states unnecessarily take space in the AP chip but are

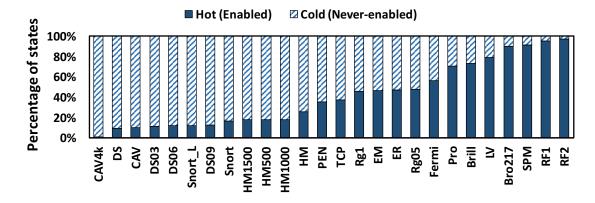

**Figure 3.1**: A large portion of NFA states are cold (never-enabled) but are still configured on the AP leading to its underutilization. (c) 2018 IEEE.

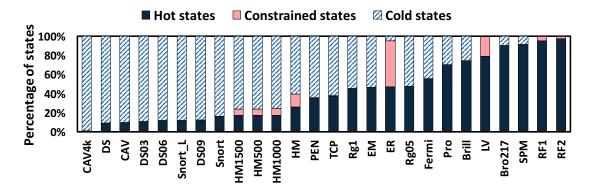

not part of any state transitions. We refer to such never enabled states as *cold* states and the remaining (enabled) states as *hot* states. Figure 3.1 quantitatively shows our observation across 26 diverse applications [123, 30] sorted in the increasing order of their percentage of hot states (across all NFAs in an application). We find that on average 59% of states are cold and it can be up to 99% in applications such as CAV4k.

These observations can be explained by revisiting the way NFAs process inputs. NFA behavior is highly input dependent. A state can attempt to match a symbol of input only if it is enabled. In the most general case, a state is enabled only if at least one of its predecessor states matched a symbol of input (the exceptions being starting states, which are always enabled). A match indicates that the current input string is plausibly still a valid prefix of the regular language recognized by the NFA. States stop matching as soon as the input string is definitely not in the language. However, the AP must still process all input symbols as long as there is one state enabled (which is always true for an NFA with at least one starting state that is always enabled), thus leaving many states never enabled. Section 3.3 shows that this is indeed the case for the NFAs running on the AP.

Based on the above key insight, we first develop software-based mechanism to predict which states are cold and hence need not be configured on the AP. Next, we propose changes in the AP hardware to efficiently execute the mis-predicted cold states. To the best of our knowledge, this is the first work that proposes architectural support for efficiently executing large-scale NFA-based applications on the AP. In summary, this paper makes the following contributions:

• We demonstrate that a large number of NFA states are cold during execution but are still configured on the AP. This leads to its severe underutilization.

• We develop a prediction mechanism to classify the NFA states into *predicted hot* and *predicted cold* sets. We use properties of NFA execution to develop a simple and effective partitioning scheme based on a state's topological order and profiling information.

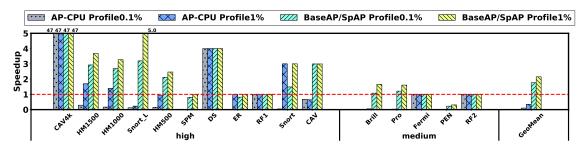

• We develop efficient hardware mechanisms to execute *predicted cold* states using a new *sparse execution mode* for the AP (called as SparseAP). Our detailed evaluation shows that we can achieve  $2.1 \times$  geometric mean speedup (up to  $47 \times$ ) over the baseline AP execution across a wide range of 26 applications.

#### **3.2** Background and Terminology

In this section, we provide a brief background on NFAs and their processing on the AP.

#### 3.2.1 NFA-based Pattern Matching

An NFA is represented by a 5-tuple,  $(Q, \Sigma, \Delta, q_0, F)$ , where Q is a set of states,  $\Sigma$  is the alphabet (set of input symbols),  $\Delta$  is a transition function which maps  $\Sigma \times \Delta$  pairs to a new set of states,  $q_0$  is the set of *starting* states, and F is a set of *accepting* or *reporting* states. Because there can be more than one possible state on a transition, such FSM is called *non-deterministic*. The NFAs used by APs are *homogeneous*<sup>1</sup>.

These NFAs can be visualized as a directed graph where each node represents a state and each edge represents a state transition. Each state in the NFA has a *symbol-set* that represents what symbols can be accepted by this state. Each state has one or multiple

<sup>&</sup>lt;sup>1</sup>In homogeneous NFAs [44, 20], all incoming transitions to any given state must accept the same set of input symbols (symbol-set). In the rest of this paper, we treat *homogeneous* NFA synonymous with NFA, because they have the same computational ability and time complexity.

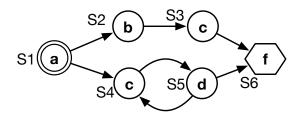

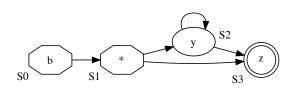

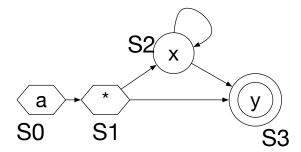

**Figure 3.2**: A homogeneous NFA that accepts regular expression a((bc)|(cd)+)f: the doubled circle represents starting state and the hexagon represents reporting state. © 2018 IEEE.

successors connected by directed edges. In each step, the NFA has a number of *enabled* states. The starting states are *enabled* prior to the execution. The matching process is driven by a stream of input symbols. Each cycle, an enabled state compares the input symbol with its symbol-set for matching; when the symbol matches, the state is *activated*, and all its successor states are enabled in the next cycle. When a *reporting state* is activated, it generates a report showing that a relevant pattern has been observed in the input symbol stream.

Figure 3.2 shows the NFA of the regular expression a((bc)|(cd)+)f. At first, the starting state  $S_1$  is enabled. abcf is the input symbol stream. a activates state  $S_1$ , resulting in the successors of  $S_1$  (i.e.,  $S_2$  and  $S_4$ ) to be enabled in the next cycle. bactivates state  $S_2$  ( $S_4$  is not activated since it does not accept symbol b), then the successor of  $S_2$  (i.e.,  $S_3$ ) is enabled. The process repeats until all input symbols are consumed. In this case, since reporting state  $S_6$  is activated by input symbol f, a report is generated indicating a successful match.

#### 3.2.2 Baseline Automata Processor (AP)

Figure 3.3 shows a schematic of the considered baseline AP chip. The AP is a DRAMbased spatial architecture in which each state of NFA is stored in a memory column of the DRAM, namely a state transition element (STE). A bit in the column represents whether the STE can accept the corresponding input symbol represented by each row.

**Figure 3.3**: The figure illustrates the first execution cycle of an AP configured with the NFA shown in Figure 3.2. S1 is enabled when input symbol **a** arrives, which activates S1, and enables S2 and S4 in the next cycle. Downward arrows represent the enable signal being fed to routing matrix in the current cycle. Upward arrows enable successor states for the next cycle. The physical connections between STEs and routing matrix are bi-directional, which are represented by the dashed arrows. (c) 2018 IEEE.

The maximum size of the alphabet is 256 as this is the width of the address decoder in the current AP architecture. Therefore, there are 256 rows in total. An AP chip consists of two *half-cores*. The state transition cannot go across half-cores due to the limitation of the interconnect. The state transitions are compiled to the reconfigurable interconnecting network namely *routing matrix*.

The entire input stream is processed sequentially with the rate of one symbol per cycle. Each cycle, one input symbol is fed into the address decoder, which selects a whole row (out of 256) of the DRAM (orange shaded part in Figure 3.3). Each STE column has a bit that represents whether the STE is enabled or not, namely *state bit*. The state bits for all STEs are combined as a *state vector*. This information is available from the previous cycle. An *AND* operation is performed between the selected row (e.g., shaded part) and the state vector resulting in a vector that determines the activated states. This activation information is sent to the routing matrix, which updates the state vector with the enabled states for processing next symbol. Such a process is repeated until the entire input symbol stream is processed.

To understand the working of AP, we illustrate the execution of previously considered NFA (Figure 3.2) via Figure 3.3. We previously observed in Figure 3.2 that  $S_1$  accepts symbol **a**. Accordingly, the bit stored in the 97th row (corresponding to the ASCII of **a**) and the column of STE that stores  $S_1$  is set to 1 and the others remain 0. The state bit of  $S_1$  is 1 and  $\{a\}$  is in the symbol-set of  $S_1$ , therefore,  $S_1$  is activated and it broadcasts the enable signals to the successor states  $(S_2, S_4)$  via the routing matrix (upward arrows in Figure 3.3).

#### **3.3** Motivation and Analysis

In this section, we analyze why a high percentage of states are cold, which states are more likely to be cold, and how avoiding these states from being configured to AP can improve the performance.

#### 3.3.1 Topological Order and Normalized Depth

In general, it is hard to predict which states will be enabled in NFAs [149]. Clearly, all starting states will be enabled at least once and this does not depend on the input. The states that are further away from the starting state, however, depend on the input. Each subsequent state transition in a homogeneous NFA must match a symbol of input (homogeneous NFAs do not have  $\epsilon$ -transitions [101]). Intuitively, a state that is further away from the starting state is less likely to be enabled since each additional state on the path to it increases the chances of a mismatch.

To verify if this intuition holds on NFAs from real-world applications executing on the AP, we study whether states are hot or cold with respect to their depths in the NFAs.

For simplicity of exposition, we first consider only NFAs that are also directed-acyclic graphs (DAGs). In this case, the depth of a state is simply its topological order (i.e., the maximum steps from the starting state to itself in the matching process). Thus, the matching process goes from states with a lower topological order to states with a higher topological order but cannot go back as DAGs do not have cycles. Such an NFA can be viewed as a graph with layers, where all starting states are in the first layer (i.e., their topological order is one), states in the second layer (i.e., states with topological order of two) are reachable from the first layer, states in the third layer are reachable from the first and second layers, and so on.

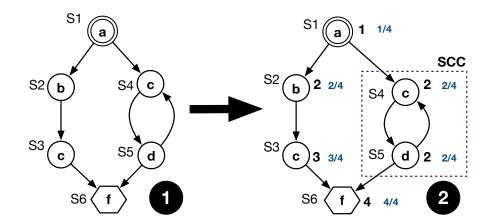

However, NFAs are not always DAGs, because they can contain back edges (i.e., from a later layer to an earlier layer) and cycles. For example, the NFA in Figure 3.4 ( $\bigcirc$ ) contains a cycle between states  $S_4$  and  $S_5$ . Topological sort cannot be performed on such graphs. Therefore, we pre-process an NFA by identifying all its strongly connected components (SCC) [42]. Each state *s* is marked with a connected component number SCC(*s*), such that the states belonging to the same SCC are marked with the same number. We construct graph *G'* from directed graph *G* (i.e., the NFA) by treating each SCC in *G* as a single node in *G'* (e.g., in Figure 3.4, the SCC that includes states  $S_4$  and  $S_5$  is considered as a single node in *G'*). For each edge (u, v) in *G*, an edge (SCC(u), SCC(v)) is added in *G'* if nodes *u* and *v* are in different SCCs. The resulting *G'* is a DAG on which we can run a topological sort. Figure 3.4 ( $\bigcirc$ ) shows the results of identifying SCCs and topological sort. The topological order of each state is indicated as a number right to the state. Since  $S_4$  and  $S_5$  belong to the same SCC, they are assigned with the same topological order.

The absolute topological order or depth of a state is uninformative as different NFAs can have a different number of layers, even within the same application. Therefore, we normalize the depth of a state to the maximum depth in the NFA it belongs to, resulting in *normalized depth*. For example, in Figure 3.4 (2), because the maximum topological order is 4 ( $S_6$ ), the normalized depth of each state s is topoorder(s)/4 (e.g., for  $S_4$  and  $S_5$ , it is 2/4 or 0.5) where topoorder is a function that returns the topological order of

Figure 3.4: Illustration of topological ordering and normalized depth. © 2018 IEEE.

a state. A normalized depth closer to 1 indicates the state is at the bottom of the NFA (or relatively deep), while a value closer to 0 indicates the state is closer to the top (or relatively shallow).

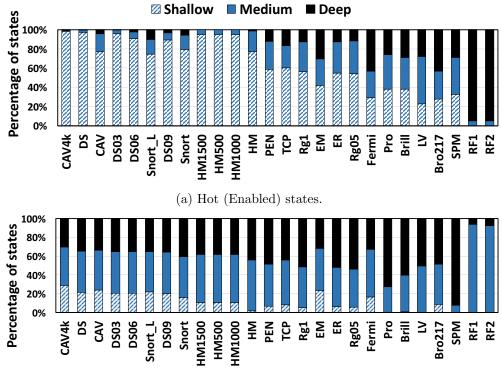

## 3.3.2 Analysis of Normalized Depth and Enabled NFA States

Figure 3.5(a) shows the normalized depth distribution of enabled (hot) states for our evaluated applications. Each application is comprised of many NFAs, each representing a different pattern. We find that for the majority of applications, the hot states have low normalized depth (i.e., they are closer to the starting state of the NFAs). Furthermore, for the same set of applications, Figure 3.5(b) shows the normalized depth distribution of cold (never enabled) states. We observe that the cold states in the majority of the applications have high normalized depth (i.e., they are in deeper regions of the NFAs). To confirm this conclusion further, we also find that there is a significant negative correlation (average correlation coefficient is -0.82) between normalized depth and percentage of hot states for all applications, except ER.

We conclude that whether a state is hot or cold is highly correlated with its normalized depth. Overall, "shallow" states are more likely to be hot while "deep" states are more likely to be cold.

(b) Cold (Never-enabled) states.

**Figure 3.5**: Distribution of normalized depth for NFA states. For presentation purposes only, normalized depth is classified as: i) shallow ([0-0.3)), ii) medium ([0.3-0.6)), and iii) deep ([0.6-1]). © 2018 IEEE.

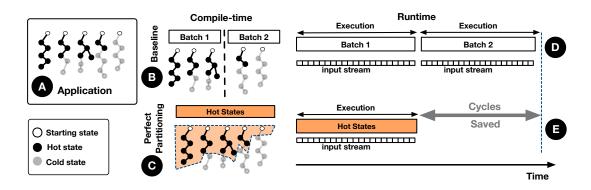

## 3.3.3 Analysis of Performance Benefits

We analyze the ideal performance benefits when we completely eliminate the cold states from being configured on the AP. We show the potential benefits using a performance model assuming oracular knowledge of which states are cold and not configured on the AP.

**Performance Model.** Consider the case of the baseline AP execution, where the application has S states (across all NFAs) and the number of states the AP half-core can hold (capacity) is  $C_{AP}$ . Without loss of generality, we only discuss the case of one AP half-core. If the number of states (S) is larger than the size of AP  $(C_{AP})$ , it is not possible to configure the entire application at once to the AP and will require configuring the AP

Figure 3.6: An illustrative figure showing that by not configuring cold states on AP, all the hot states can fit onto an AP at the same time, reducing the number of re-executions over the input and hence saving time. © 2018 IEEE.

multiple times. Each configuration places a set of NFAs that can collectively fit in the AP. Suppose the size of each NFA in the application is less than the size of AP, therefore, the number of configurations to the AP would be  $N_{config} = \lceil \frac{S}{C_{AP}} \rceil$ , under the assumption that individual NFAs can be split at state granularity. In the current AP architecture, batches (partitions) usually contain whole NFAs, so the number of configurations may be even higher.

To maintain semantics, each configuration batch must see the same input stream. The matching process finishes after all batches of NFAs are executed on the same input stream. Thus, the total number of cycles spent on the same input stream is  $N_{config} \times n$ , where n is the length of the input stream and  $N_{config}$  is the number of batches. Under a perfect scenario where we can identify cold states  $(S_{cold})$  with 100% accuracy, we can reduce  $N_{config}$  by not configuring the cold states to the AP. We define the resource saving  $p = \frac{S_{cold}}{S}$ . Therefore, the speedup over the baseline case is  $\lceil \frac{S}{C_{AP}} \rceil / \lceil \frac{(1-p) \cdot S}{C_{AP}} \rceil$ . If the number of states is sufficiently large, the speedup we can get is proportional to  $\frac{1}{1-p}$ ,  $p \neq 1$ . Thus, the larger the proportion of cold states that can be correctly identified and eliminated, the more speedup we can have over the baseline execution scenario.

**Illustrative Example.** To illustrate the benefits of configuring the AP with only hot states, Figure 3.6 shows two scenarios: a) the baseline AP execution, and b) the AP that

only executes hot states. The execution in both cases considers the same application (a). In the baseline scenario, if the number of total states is more than the AP capacity, the execution will need to be done in batches as discussed before. In this example, the compiler partitions the application into two batches, where each batch can individually fit in the AP (b). Hence, the same input stream is executed twice in a sequential manner (b). However, with the oracular knowledge of cold states, the compiler can generate a *perfect partition* of the application with only the hot states (c). If this perfect partition fits in the AP, it can execute on it by consuming the same input stream only once (b), resulting in significant savings in the execution cycles.

In summary, significant speedup can be achieved if cold states are not configured to AP. In the next section, we propose a simple and effective profiling-based mechanism to identify such states in realistic scenarios and then leverage the profiling information to efficiently partition them from the NFAs.

## 3.4 Design and Implementation of NFA Partitioning

Any realistic implementation that eliminates cold states from NFAs (i.e., partitions NFAs into cold and hot states, and only configures AP with hot states) has to deal with at least three challenges. First, although it is not possible to predict cold states with 100% accuracy in general, we need to develop low-overhead techniques to improve the accuracy of prediction as much as possible. Second, in the case of a mis-prediction, some transitions may require states that are not configured on the AP. To this end, we need a mechanism working as a safety net to handle a transition from a state on the AP to a state that is not on the AP. Third, to minimize the cost of such mis-predictions, transitions should be unidirectional to avoid re-executions of inputs on the AP.

Our proposed partitioning scheme systematically addresses these challenges. First, we use a profiling-based scheme to identify the topological layer that acts as a *partition layer* for each NFA in the application. Second, our proposed scheme handles transitions out of the AP by adding *intermediate reporting states* that piggyback on existing AP reporting hardware. Finally, to ensure unidirectional transitions, we partition the NFA at a specific topological order. Since the matching always proceeds from a lower to a higher topological order, edges that cross partitions go only in one direction.

#### 3.4.1 Profiling-based Hot/Cold State Prediction

We use a small portion of input for each application as profiling input. Basically, at compile time, we run the profiling input on the NFAs of the application and determine whether a state is hot or cold. We assume that this profiling information holds true during the actual execution and hence are able to predict which states will be hot or cold. In the following parts of this sub-section, we evaluate the effectiveness of our profiling-based prediction.

**Profiling and Testing Inputs.** Each application that we evaluate has a 1MB input. We divide this 1MB input into two equal parts of 512KB. The first 512KB of input is used for creating different sizes of profiling inputs and the last 512KB is used for testing input. We create different sizes of profiling inputs by using the first 0.2%, 2%, 20%, 100% symbols of the 512KB portion, which is essentially 0.1%, 1%, 10%, 50% of the entire input. **Methodology for Evaluating the Effectiveness of Profiling.** In our evaluation, we treat hot as *positive* (P) and cold as *negative* (N). Therefore, *true positives* (TP) are states that are hot both under profiling input and testing input. Similarly, *false positives* (FP) are states that are hot under profiling input but actually cold under testing input. True negatives (TN) and false negatives (FN) are defined similarly. We define: a) *accuracy* =  $\frac{TP+TN}{P+N}$ , which measures overall how well is the profiling-based prediction; b) *recall* =  $\frac{TP}{TP+FN}$ , which measures how complete our prediction is terms of predicting hot states; and c) *precision* =  $\frac{TP}{TP+FP}$ , which measures how well the prediction could realize the resource saving scope (p).

Effectiveness of Profiling. Table 3.1 shows the average numbers for accuracy, recall, and precision when we use different sizes of profiling inputs. We evaluate all applications

| Percentage of the entire input $\Rightarrow$ | 0.1% | 1%  | 10% | 50% |

|----------------------------------------------|------|-----|-----|-----|

| Accuracy                                     | 87%  | 90% | 93% | 97% |

| Recall                                       | 64%  | 76% | 87% | 97% |

| Precision                                    | 94%  | 92% | 90% | 92% |

Table 3.1: The effectiveness of profile-based prediction. © 2018 IEEE.

except Fermi and SPM. Specifically, using only 2% prefix of the first 512KB (i.e., 1% of the entire input) can achieve 76% recall, which means 76% of hot states under testing input are also hot with the small profiling input. The results are consistent across 24 applications (recall varies from 49% to 100%). In addition, the prediction also has good results in terms of accuracy and precision. To conclude, only a small profiling input can identify most of the hot states during the actual execution. Therefore, we use 0.1% and 1% of the entire input for profiling and the remaining for the actual evaluation<sup>2</sup> (Section 3.7).

#### 3.4.2 Where to Partition?

In current AP architecture, the application is split at NFA granularity into batches. In contrast, we partition the NFAs at topological-order granularity. There are two reasons that we use topological-order as our partition granularity. First, our previous analysis (Section 3.3.2) shows there is a correlation between normalized depth and percentage of hot states. Second, partition at topological-order granularity can guarantee the unidirectional transition between predicted cold and hot states. In this sub-section, we show how do we obtain partition layer  $k_U$  for each NFA U of the application. We will show how to partition each NFA at the topological-order granularity in Section 3.4.3.

**Choosing Partition Layer.** At compile time, we functionally simulate all NFAs of the application using the profiling input and predict whether a state is hot or cold. After simulation, for each NFA U, we set  $k_U = \max\{topoorder(s)\}, \forall s$  is a hot state in NFA U under the profiling input. We define the predicted hot  $set = \{s \mid s \in U \land topoorder(s) \le k_U, \forall U\}$ . Accordingly, the predicted cold  $set = \{s \mid s \in U \land topoorder(s) > k_U, \forall U\}$ . We

<sup>&</sup>lt;sup>2</sup>For Fermi and SPM, we use the entire input for the actual execution because their starting states are only enabled at position 0 (*start-of-data* in ANML configuration).

divide the predicted hot set at NFA level into batches that can fit in AP and configure each batch sequentially.

**Optimization.** As an optimization, to make each batch fill the AP completely, we assign additional states to the predicted hot set from predicted cold set. This is achieved by incrementing  $k_U$ , which adds the states of the subsequent partition layers for each NFA U. This process terminates when the capacity of AP is met for each batch.

## 3.4.3 How to Partition?

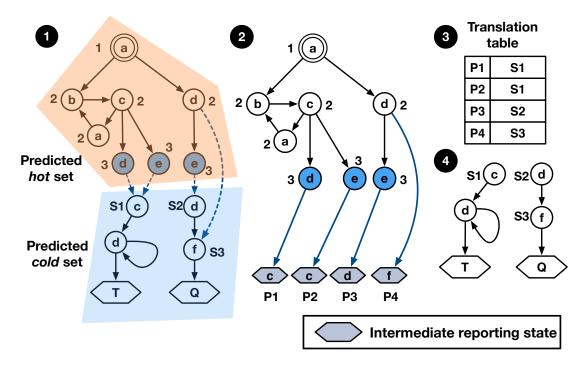

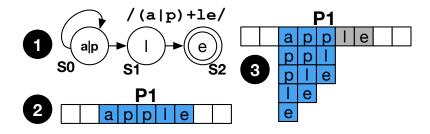

In this sub-section, we demonstrate how to partition an NFA into two parts at a given partition layer k calculated based on the description presented in Section 3.4.2 and how to handle state transitions when the partitioning is imperfect. For brevity, we describe our partitioning scheme for a single NFA, which then can be separately applied to each NFA in the application. Figure 3.7 illustrates NFA partitioning using the partition layer k = 3 and cut the edges that connect states with  $k \leq 3$  to states with k > 3 (indicated as dashed lines in Figure 3.7 (**①**)). However, the prediction may not be perfect – a state in the predicted cold set could end up being enabled during matching. Since only states in the predicted hot set are present on the AP, the matching process must transition out of the AP.

To handle such cases, for each edge (u, v) we cut in the original NFA, we introduce an *intermediate reporting state* v' and an edge (u, v'). The state v' matches exactly the same input symbols (symbol-set) as v but is also a *reporting state*. During execution, the AP contains these *intermediate reporting states* along with the predicted hot set. Therefore, when the matching process tries to enable a state that is not on the AP (i.e., in the predicted cold set), it activates the corresponding intermediate reporting state instead. Consequently, an *intermediate report* is generated that notifies a handler (Section 3.5). The handler will enable corresponding states in predicted cold set to continue the matching process. Since we use topological order to partition, after the matching process continues, it will never go back to the predicted hot set. In Figure 3.7 (2), the intermediate reporting

Figure 3.7: Partitioning an NFA by the partition layer. © 2018 IEEE.

states are  $P_1$  through  $P_4$ . When activated, these states enable their corresponding states S1, S2 and S3 as indicated in the translation table (Figure 3.7 (3)), which lie in the predicted cold set shown in Figure 3.7(4).

#### 3.4.4 Discussion

The use of SCC and topological-order-based partitioning imposes constraints that lead to more states than necessary being added to the predicted hot set. Specifically, (1) even if only one state in an SCC is hot, the whole SCC must be included in predicted hot set, and (2) a cold state with topological order less than the partition layer k is still included in the predicted hot set. This might reduce the AP resource savings.

To study the extent of this underutilization, Figure 3.8 shows that for all the 26 evaluated applications, our topological-order based perfect partitioning constrains only 4% on average more states to the predicted hot set (which in reality are not going to be enabled), compared with perfect partitioning that can cut NFAs at arbitrary edges. Two

**Figure 3.8**: Constrained states are cold states but configured on the AP due to the constraints in our topological-order-based partitioning scheme. Consequently, some AP resources are underutilized with a few applications. © 2018 IEEE.

exceptions are LV and ER whose large SCCs prevent effective partitions. In summary, we still have a significant opportunity for resource savings if we can accurately identify the partition layer for each NFA.

# 3.5 Hardware Support for Intermediate Report Handling and Partitioned NFA Processing

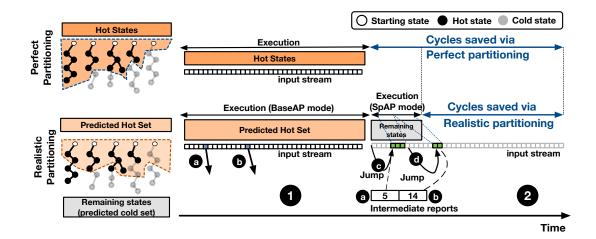

In this section, we discuss how to efficiently handle the intermediate reports generated from the execution of the predicted hot set. To this end, we propose to: a) enable the states that intermediate reporting state directs to, and b) continue the matching process from the cycle (i.e., the input position) where the intermediate report was generated at. Although both steps can be performed on CPU, it incurs significant performance slowdown (Section 3.7), therefore we propose a new execution mode for the AP.

## 3.5.1 Analysis of New Execution Modes for AP