W&M ScholarWorks

Dissertations, Theses, and Masters Projects

Theses, Dissertations, & Master Projects

2021

# Revisiting Isolation For System Security And Efficiency In The Era Of Internet Of Things

Lele Ma William & Mary - Arts & Sciences, lelema.cn@gmail.com

Follow this and additional works at: https://scholarworks.wm.edu/etd

Part of the Computer Sciences Commons

### **Recommended Citation**

Ma, Lele, "Revisiting Isolation For System Security And Efficiency In The Era Of Internet Of Things" (2021). *Dissertations, Theses, and Masters Projects.* William & Mary. Paper 1673273635. https://dx.doi.org/10.21220/s2-sqd8-hs55

This Dissertation is brought to you for free and open access by the Theses, Dissertations, & Master Projects at W&M ScholarWorks. It has been accepted for inclusion in Dissertations, Theses, and Masters Projects by an authorized administrator of W&M ScholarWorks. For more information, please contact scholarworks@wm.edu.

Revisiting Isolation for System Security and Efficiency in the Era of Internet of Things

Lele Ma

Jinan, Shandong, China

Bachelor of Engineering, Shandong University, 2012 Master of Engineering, University of Chinese Academy of Sciences, 2015

A Dissertation presented to the Graduate Faculty of The College of William & Mary in Candidacy for the Degree of Doctor of Philosophy

Department of Computer Science

College of William & Mary August 2021

$\bigodot$  Copyright by Lele Ma 2021

### APPROVAL PAGE

This Dissertation is submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Lele Ma

Lele Ma

Approved by the Committee, August 2021

Junli

Committee Chair Qun Li, Professor, Computer Science College of William & Mary

Weighen Mao

Weizhen Mao, Professor, Computer Science College of William & Mary

Adwait fog

Adwait Jog, Associate Professor, Computer Science College of William & Mary

In tor

Dmitry Evtyushkin, Assistant Professor, Computer Science College of William & Mary

LNZ

Ang Li, Computer Scientist, HPC group Pacific Northwest National Laboratory

### ABSTRACT

Isolation is a fundamental paradigm for secure and efficient resource sharing on a computer system. However, isolation mechanisms in traditional cloud computing platforms are heavy-weight or just not feasible to be applied onto the computing environment for Internet of Things(IoT). Most IoT devices have limited resources and their servers are less powerful than cloud servers but are widely distributed over the edge of the Internet. Revisions to the traditional isolation mechanisms are needed in order to improve the system security and efficiency in these computing environments.

The first project explores container-based isolation for the emerging edge computing platforms. We show a performance issue of live migration between edge servers where the file system transmission becomes a bottleneck. Then we propose a solution that leverages a layered file system for synchronization before the migration starts, avoiding the usage of impractical networking shared file system as in the traditional solution. The evaluation shows that the migration time is reduced by 56% - 80%.

In the second project, we propose a lightweight security monitoring service for edge computing platforms, base on the virtual machine isolation technique. Our framework is designed to monitor program activities from underneath of an operating system, which improves its transparency and avoids the cost of embedding different monitor modules into each layer inside the operating system. Furthermore, the monitor runs in a single process virtual machine which requires only  $\leq 32$ MB of memory, reduces the scheduling overhead, and saves a significant amount of physical memory, while the performance overhead is an average of 2.7%.

In the third project, we co-design the hardware and software system stack to achieve efficient fine-grained intra-address space isolation. We propose a systematic solution to partition a legacy program into multiple security compartments, which we call *capsules*, with isolation at byte granularity. Vulnerabilities in one *capsule* will not likely affect another *capsule*. The isolation is guaranteed by our hardware-based ownership types tagged to every byte in the memory. The ownership types are initialized, propagated, and checked by combining both static and dynamic analysis techniques. Finally, our co-design approach could remove most human refactoring efforts while avoiding the untrustworthiness as well as the cost of the pure software approaches.

In brief, this proposal explores a spectrum of isolation techniques and their improvements for the IoT computing environment. With our explorations, we have shown the necessity to revise the traditional isolation mechanisms in order to improve the system efficiency and security for the edge and IoT platforms. We expect that many more opportunities will be discovered and various kinds of revised or new isolation mechanisms for the edge and IoT platforms will emerge soon.

## TABLE OF CONTENTS

| Ac  | Acknowledgments |                                                 |   |  |  |  |  |  |  |  |  |  |

|-----|-----------------|-------------------------------------------------|---|--|--|--|--|--|--|--|--|--|

| De  | Dedication xii  |                                                 |   |  |  |  |  |  |  |  |  |  |

| Lis | st of '         | Tables xii                                      | i |  |  |  |  |  |  |  |  |  |

| Lis | st of 1         | Figures                                         | V |  |  |  |  |  |  |  |  |  |

| 1   | Intro           | oduction                                        | 2 |  |  |  |  |  |  |  |  |  |

|     | 1.1             | Motivation                                      | 2 |  |  |  |  |  |  |  |  |  |

|     | 1.2             | Efficient Live Migration across Edge Servers    | 4 |  |  |  |  |  |  |  |  |  |

|     | 1.3             | Lightweight Security Monitor for Edge Servers   | 5 |  |  |  |  |  |  |  |  |  |

|     | 1.4             | Secure IoT Systems with Hardware Ownership Tags | 5 |  |  |  |  |  |  |  |  |  |

|     | 1.5             | Dissertation Organization                       | 3 |  |  |  |  |  |  |  |  |  |

| 2   | Back            | rground                                         | 7 |  |  |  |  |  |  |  |  |  |

|     | 2.1             | Docker Containers                               | 7 |  |  |  |  |  |  |  |  |  |

|     | 2.2             | Xen and Unikernels                              | 7 |  |  |  |  |  |  |  |  |  |

|     | 2.3             | QEMU                                            | 3 |  |  |  |  |  |  |  |  |  |

|     | 2.4             | gem5 Simulator                                  | 3 |  |  |  |  |  |  |  |  |  |

|     | 2.5             | Bluespec and <i>bluesim</i>                     | ) |  |  |  |  |  |  |  |  |  |

|     | 2.6             | LLVM toolchain                                  | ) |  |  |  |  |  |  |  |  |  |

|     | 2.7             | Privilege Separation and Isolation              | ) |  |  |  |  |  |  |  |  |  |

|     | 2.8             | Intra-address Space Isolation                   | L |  |  |  |  |  |  |  |  |  |

| 3 | Effic | cient Li | ive Migration across Edge Servers                             | 12 |

|---|-------|----------|---------------------------------------------------------------|----|

|   | 3.1   | Overv    | riew                                                          | 12 |

|   | 3.2   | Introd   | luction                                                       | 13 |

|   | 3.3   | Motiv    | ration                                                        | 16 |

|   |       | 3.3.1    | Offloading Service is Essential for Edge Computing            | 16 |

|   |       | 3.3.2    | Effective Edge Offloading Needs Migration for Service Handoff | 16 |

|   |       | 3.3.3    | Service Handoff via VM Migration is Not Practical             | 17 |

|   |       | 3.3.4    | More Efficient Migration is Achievable with Docker Containers | 19 |

|   | 3.4   | Conta    | ainer Storage and Migration                                   | 20 |

|   |       | 3.4.1    | Container Engines and Storage Drivers                         | 20 |

|   |       | 3.4.2    | Layered Storage in Docker                                     | 21 |

|   |       |          | 3.4.2.1 <i>Container Layer</i> and Base Image Layers          | 21 |

|   |       |          | 3.4.2.2 Image Layer ID Mapping                                | 22 |

|   |       |          | 3.4.2.3 Docker's Graph Driver and Storage Driver              | 23 |

|   |       | 3.4.3    | AUFS Storage: A Case Study                                    | 23 |

|   |       |          | 3.4.3.1 Container's Image Layer Stack List                    | 25 |

|   |       |          | 3.4.3.2 Image Layer Content Directory                         | 26 |

|   |       |          | 3.4.3.3 Unified Mount Point                                   | 27 |

|   |       |          | 3.4.3.4 Layer ID Mapping                                      | 27 |

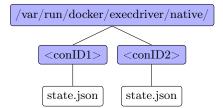

|   |       |          | 3.4.3.5 Container Configuration and Runtime State             | 28 |

|   |       | 3.4.4    | Docker Container Migration in Practice                        | 28 |

|   | 3.5   | Offloa   | ding Service Migration on the Edge                            | 30 |

|   |       | 3.5.1    | System Overview                                               | 31 |

|   |       |          | 3.5.1.1 Edge Controller                                       | 32 |

|   |       |          | 3.5.1.2 Edge Nodes                                            | 33 |

|   |       |          | 3.5.1.3 End Users                                             | 33 |

|   |       | 3.5.2    | Workflow of Service Handoff                                   | 34 |

|   |      | 3.5.3   | Strategy to Synchronize Storage Layers                    |

|---|------|---------|-----------------------------------------------------------|

|   |      | 3.5.4   | Layer ID Remapping                                        |

|   |      | 3.5.5   | Pre-Dump & Dirty Memory Synchronization                   |

|   |      | 3.5.6   | Data Transfer                                             |

|   |      | 3.5.7   | Parallel & Pipelined Processing                           |

|   |      | 3.5.8   | Multi-Mode Migration with Flexible Trade-offs             |

|   |      | 3.5.9   | Two-layer System-wide Isolation for Better Security 42    |

|   |      | 3.5.10  | Discussion                                                |

|   |      |         | 3.5.10.1 Benefits and Applications                        |

|   |      |         | 3.5.10.2 Limitations of Scope                             |

|   | 3.6  | Evalua  | ation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $44$            |

|   |      | 3.6.1   | Set Up and Benchmark Workloads                            |

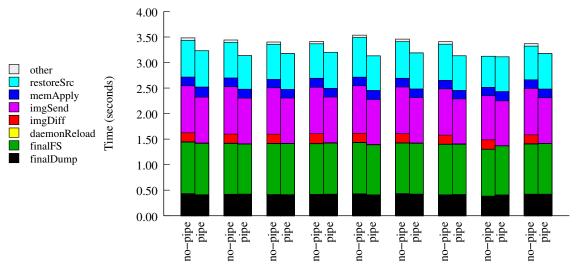

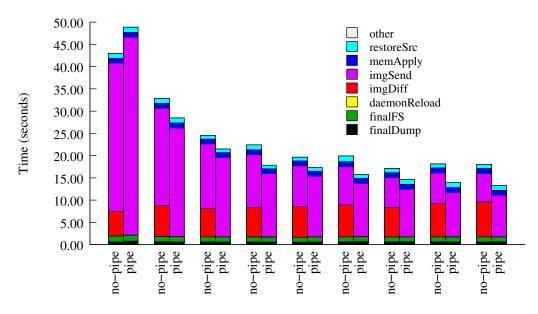

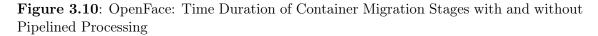

|   |      | 3.6.2   | Evaluation of Pipeline Performance                        |

|   |      | 3.6.3   | Evaluation on Different Metrics                           |

|   |      |         | 3.6.3.1 Evaluation of Changing Network Bandwidth 46       |

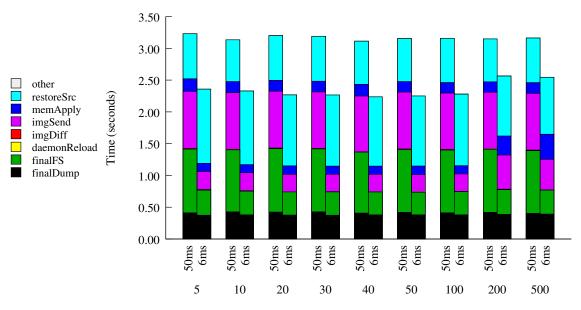

|   |      |         | 3.6.3.2 Evaluation of Changing Latency                    |

|   |      |         | 3.6.3.3 Evaluation of Changing Compression Algorithms and |

|   |      |         | Options                                                   |

|   |      |         | 3.6.3.4 Evaluation of Changing Total Iterations           |

|   |      | 3.6.4   | Overall Performance                                       |

|   | 3.7  | Relate  | ed Work                                                   |

|   |      | 3.7.1   | Edge Computing and Service Mobility                       |

|   |      | 3.7.2   | VM Migration on the Edge                                  |

|   |      | 3.7.3   | Container Migration on the Edge                           |

|   | 3.8  | Conclu  | usion $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $55$   |

| 4 | Ligh | ntweigh | t Security Monitor for Edge Servers 56                    |

| 4.1 | Overv  | riew      |                                                                                                                           | 56         |

|-----|--------|-----------|---------------------------------------------------------------------------------------------------------------------------|------------|

| 4.2 | Introd | luction . |                                                                                                                           | 57         |

| 4.3 | Motiv  | ation     |                                                                                                                           | 59         |

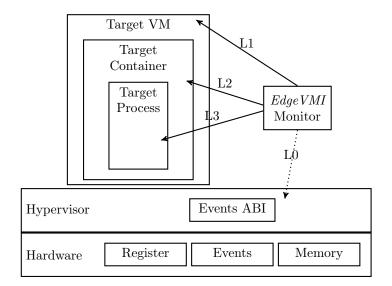

|     | 4.3.1  | Why VN    | $MI?  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                    | 60         |

|     | 4.3.2  | Why We    | e Need Improved VMI? 6                                                                                                    | 60         |

|     |        | 4.3.2.1   | The Trusted Computing Base is Large 6                                                                                     | 31         |

|     |        | 4.3.2.2   | The Overhead is High for Runtime Monitoring 6                                                                             | 61         |

| 4.4 | Design | n Overvie | ew                                                                                                                        | 32         |

|     | 4.4.1  | Threat I  | $Model \dots \dots$ | 52         |

|     |        | 4.4.1.1   | Trusted Components                                                                                                        | 52         |

|     |        | 4.4.1.2   | Threat Source                                                                                                             | 53         |

|     |        | 4.4.1.3   | Applications that Need Small Scale Monitoring 6                                                                           | 33         |

|     | 4.4.2  | Design (  | Goals                                                                                                                     | 64         |

|     |        | 4.4.2.1   | Small Code Base                                                                                                           | 64         |

|     |        | 4.4.2.2   | Transparency                                                                                                              | 64         |

|     |        | 4.4.2.3   | Least Privileges                                                                                                          | 35         |

|     |        | 4.4.2.4   | Isolated Components                                                                                                       | 65         |

|     |        | 4.4.2.5   | Easy to Deploy                                                                                                            | 66         |

|     |        | 4.4.2.6   | Flexible with Rich Primary Mechanisms 6                                                                                   | 66         |

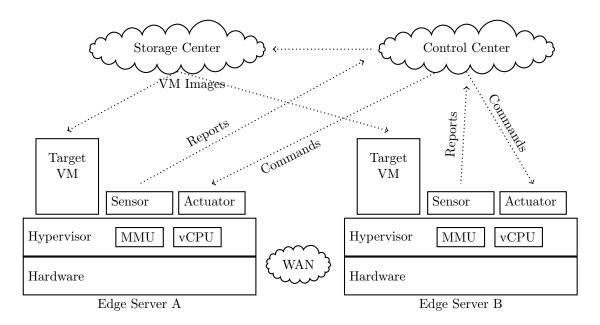

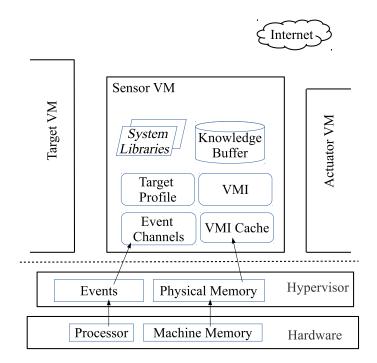

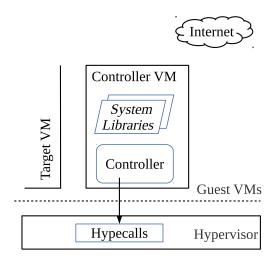

|     | 4.4.3  | EdgeVM    | II Overview                                                                                                               | 36         |

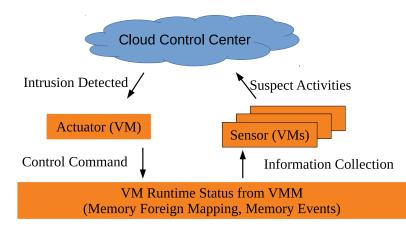

|     |        | 4.4.3.1   | Sensor                                                                                                                    | 67         |

|     |        | 4.4.3.2   | Actuator                                                                                                                  | 58         |

|     |        | 4.4.3.3   | Cloud Storage and Control Center                                                                                          | 58         |

|     | 4.4.4  | Harden    | the Security of Monitors                                                                                                  | <u>5</u> 9 |

|     |        | 4.4.4.1   | Privilege Separation of Monitor and Control 6                                                                             | <u>5</u> 9 |

|     |        | 4.4.4.2   | Control and Information Flow Restrictions 6                                                                               | <u>5</u> 9 |

|     | 4.4.5  | Example   | e of Intrusion Detection                                                                                                  | 70         |

| 4.5 | Edge  | $VMI$ in Deployment $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 71 |

|-----|-------|---------------------------------------------------------------------------------------------|----|

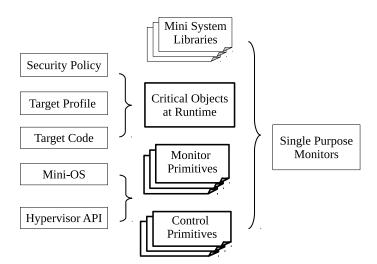

|     | 4.5.1 | Build Single-Purpose, Deeply Customized Monitor VMs $\ . \ . \ .$                           | 71 |

|     |       | 4.5.1.1 Security Policy                                                                     | 72 |

|     |       | 4.5.1.2 Target Profile                                                                      | 72 |

|     |       | 4.5.1.3 Mini-OS and Hypervisor API                                                          | 72 |

|     |       | 4.5.1.4 Mini System Libraries                                                               | 72 |

|     |       | 4.5.1.5 Critical Objects                                                                    | 73 |

|     |       | 4.5.1.6 Monitor and Control Primitives                                                      | 73 |

|     |       | 4.5.1.7 Build Monitor VMs                                                                   | 73 |

|     | 4.5.2 | Raw Physical Memory Access                                                                  | 74 |

|     | 4.5.3 | Monitor Processor Registers                                                                 | 74 |

|     | 4.5.4 | Hardware Event Monitoring                                                                   | 75 |

|     | 4.5.5 | VM Life Cycle Management                                                                    | 75 |

|     | 4.5.6 | Deployment                                                                                  | 75 |

| 4.6 | Imple | ementation of a Prototype                                                                   | 76 |

|     | 4.6.1 | Challenge 1: Stripping Down Libraries                                                       | 76 |

|     | 4.6.2 | Challenge 2: Input & Output without a File System $\ . \ . \ .$ .                           | 78 |

|     | 4.6.3 | Challenge 3: Mandatory Access Control                                                       | 79 |

|     | 4.6.4 | Components of the Sensor                                                                    | 80 |

|     |       | 4.6.4.1 System Libraries                                                                    | 80 |

|     |       | 4.6.4.2 Target Profile                                                                      | 81 |

|     |       | 4.6.4.3 Knowledge Buffer                                                                    | 82 |

|     |       | 4.6.4.4 VMI                                                                                 | 82 |

|     |       | 4.6.4.5 VMI Cache                                                                           | 83 |

|     |       | 4.6.4.6 Event Channels                                                                      | 83 |

|     | 4.6.5 | Implementation of the Actuator                                                              | 83 |

| 4.7 | Secu  | rity Evaluation                                                                             | 84 |

|   |          | 4.7.1    | Reduced Attack Surface                                        | 84  |

|---|----------|----------|---------------------------------------------------------------|-----|

|   |          | 4.7.2    | MAC Isolation Based on FLASK                                  | 85  |

|   |          | 4.7.3    | Least Privilege and Privilege Separation                      | 86  |

|   |          | 4.7.4    | Constrained Information and Control Flow                      | 86  |

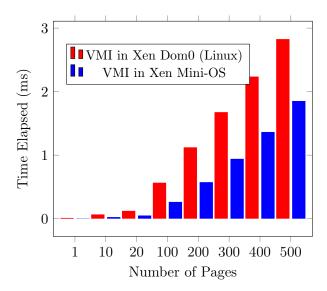

|   | 4.8      | Perfo    | rmance Evaluation                                             | 86  |

|   |          | 4.8.1    | Runtime Memory Overhead                                       | 87  |

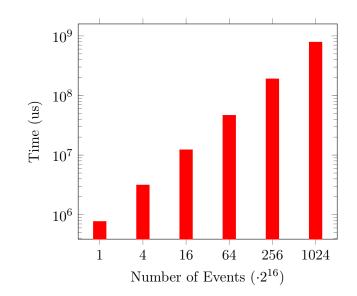

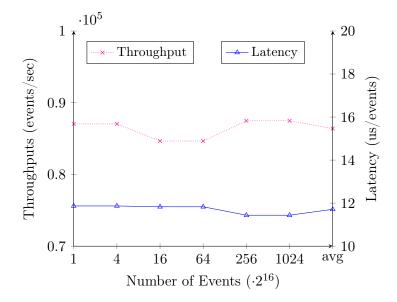

|   |          | 4.8.2    | Monitoring Events                                             | 87  |

|   |          | 4.8.3    | Monitoring a Process                                          | 89  |

|   |          | 4.8.4    | Performance Benefits from Single-Process Mini-OS              | 89  |

|   | 4.9      | Discus   | ssion                                                         | 91  |

|   |          | 4.9.1    | Hypervisor in TCB                                             | 92  |

|   |          | 4.9.2    | Semantic Gap Challenge for VMI                                | 92  |

|   |          | 4.9.3    | Orthogonality with Other Security Solutions                   | 93  |

|   |          | 4.9.4    | Weakness in Large Scale Monitoring                            | 94  |

|   | 4.10     | Relate   | ed Work                                                       | 94  |

|   |          | 4.10.1   | Security on Edge Servers                                      | 94  |

|   |          | 4.10.2   | Virtual Machine Introspection                                 | 94  |

|   |          | 4.10.3   | Privilege Separation on Monolithic Systems                    | 95  |

|   |          | 4.10.4   | Hardware Based Security Approaches                            | 95  |

|   | 4.11     | Conclu   | usion and Future Work                                         | 96  |

| 5 | $Ca_{i}$ | psule: I | Fine-grained Isolation and Pointer Safety with Ownership Tags | 97  |

|   | 5.1      | Overv    | iew                                                           | 97  |

|   | 5.2      | Introd   | luction                                                       | 98  |

|   | 5.3      | Motiva   | ation                                                         | 103 |

|   |          | 5.3.1    | Why a New Isolation Mechanism?                                | 103 |

|   |          |          | 5.3.1.1 Inter- and Intra-address Space Isolation              |     |

|   |          |          |                                                               |     |

|   |    |        | 5.3.1.2          | Drawbacks in Existing Intra-address Space Isolation . 104                                                                                  |

|---|----|--------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

|   |    |        | 5.3.1.3          | Potentials in Pointer Safety Solutions                                                                                                     |

|   |    |        | 5.3.1.4          | Towards Inter- and Intra-Domain Memory Safety 106                                                                                          |

|   |    | 5.3.2  | Why Fi           | ne-grained Isolation?                                                                                                                      |

|   |    | 5.3.3  | Why Cl           | hoose Tagged Memory                                                                                                                        |

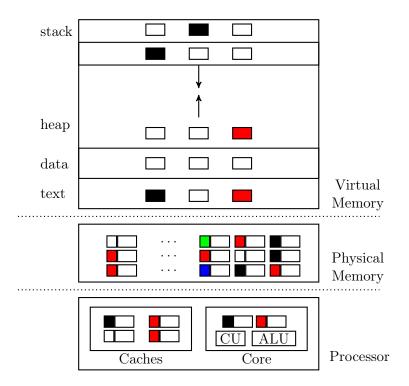

| 5 | .4 | Capsu  | <i>le</i> Syster | m Overview                                                                                                                                 |

|   |    | 5.4.1  | Key Ob           | servations $\ldots \ldots 109$           |

|   |    |        | 5.4.1.1          | Efficient Domain Transition with Ubiquitous Owner-                                                                                         |

|   |    |        |                  | ship Tags                                                                                                                                  |

|   |    |        | 5.4.1.2          | Partition Process Memory into Closure Sets 110                                                                                             |

|   |    |        | 5.4.1.3          | Partition Closure Set with Transition Gates 110                                                                                            |

|   |    |        | 5.4.1.4          | Closure Sets as Domains                                                                                                                    |

|   |    |        | 5.4.1.5          | Achieve Intra-domain Security with Ownership Tags                                                                                          |

|   |    |        |                  | for Pointers                                                                                                                               |

|   |    |        | 5.4.1.6          | Lock and Key with Ownership Tags                                                                                                           |

|   |    | 5.4.2  | Threat           | Model                                                                                                                                      |

|   |    | 5.4.3  | Capsule          | e Overview                                                                                                                                 |

|   |    | 5.4.4  | Owners           | hip Tag Representations and Interpretations $\ldots$ 115                                                                                   |

|   |    |        | 5.4.4.1          | Interpretation of Non-Pointer Tags                                                                                                         |

|   |    |        | 5.4.4.2          | Interpretation of Data Pointer Tags                                                                                                        |

|   |    |        | 5.4.4.3          | Interpretation for Code Pointer Tags                                                                                                       |

|   |    | 5.4.5  | Owners           | hip Space                                                                                                                                  |

|   |    | 5.4.6  | Owners           | hip Allocation and Relocation                                                                                                              |

|   |    | 5.4.7  | Owners           | hip Identity Concealment                                                                                                                   |

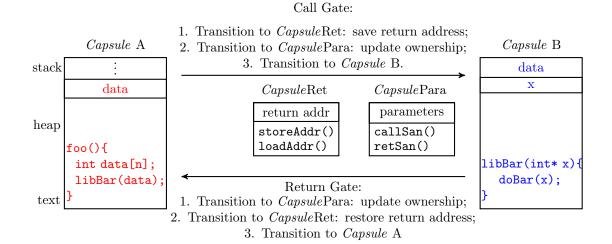

| 5 | .5 | Secure | e Domair         | $Transition \dots \dots$             |

|   |    | 5.5.1  | Transie          | nt Transition                                                                                                                              |

|   |    | 5.5.2  | Sanitize         | ed Transition $\ldots \ldots 121$ |

|     | 5.5.3  | Memory Sharing Mechanisms                                                                                                              |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------|

|     | 5.5.4  | Ownership Transfer                                                                                                                     |

|     | 5.5.5  | Memory Sharing via Object Capsules                                                                                                     |

|     | 5.5.6  | Avoid Supervised Trusted Stack                                                                                                         |

|     | 5.5.7  | Decentralized Call Gates                                                                                                               |

| 5.6 | Deter  | mine the Closure Set for a <i>Capsule</i>                                                                                              |

|     | 5.6.1  | Static Ownership Inference                                                                                                             |

|     | 5.6.2  | Memory Colonization                                                                                                                    |

|     | 5.6.3  | Manual Ownership Assignment                                                                                                            |

|     | 5.6.4  | Manual Conflict Resolving                                                                                                              |

| 5.7 | Syster | m Stack Extension for Ownership Tags                                                                                                   |

|     | 5.7.1  | Architectural Support                                                                                                                  |

|     | 5.7.2  | Toolchain Support                                                                                                                      |

| 5.8 | Imple  | mentation $\ldots \ldots 132$ |

|     | 5.8.1  | Implementations for Functionality, Performance, and Feasibility 133                                                                    |

|     | 5.8.2  | Processor Extension                                                                                                                    |

|     | 5.8.3  | Toolchain Extension                                                                                                                    |

|     | 5.8.4  | Ownership Space Management                                                                                                             |

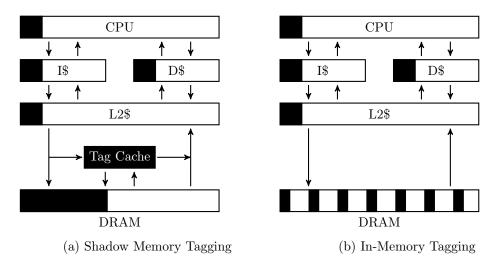

|     | 5.8.5  | Two Forms of Tagged Physical Memory                                                                                                    |

| 5.9 | Securi | ity Evaluation                                                                                                                         |

|     | 5.9.1  | Capsule Security Features                                                                                                              |

|     | 5.9.2  | Spatial Pointer Safety with Bound and Ownership Check $\ . \ . \ . \ 143$                                                              |

|     | 5.9.3  | Temporal Pointer Safety with Ownership Separation $\ . \ . \ . \ . \ . \ . \ . \ . \ . \ $                                             |

|     | 5.9.4  | Code Pointer Integrity for Control Flow Protection                                                                                     |

|     | 5.9.5  | Control Flow Defense against Malicious Capsule                                                                                         |

|     | 5.9.6  | Comparison in Supported Policy Examples                                                                                                |

|     | 5.9.7  | Example: Prevent Heartbleed with Two Levels of Defenses 148                                                                            |

|    |       | 5.9.8    | N    | Aor  | e S  | ecui  | rity | 7 P  | oli        | cies | з.  | •   |     |   | <br>• |   | • | • |   | • | • |       | • | • |   | • | . 1 | 49 |

|----|-------|----------|------|------|------|-------|------|------|------------|------|-----|-----|-----|---|-------|---|---|---|---|---|---|-------|---|---|---|---|-----|----|

|    | 5.10  | Hardw    | wa   | re   | Fea  | sibil | lity | ' ai | nd         | Pe   | rfo | rma | anc | e |       |   | • | • |   | • | • |       |   |   |   | • | . 1 | 49 |

|    |       | 5.10.1   | 1 F  | Iar  | dwa  | are l | Fea  | ısil | bili       | ty   |     |     |     |   |       |   | • | • |   | • | • |       |   |   |   | • | . 1 | 49 |

|    |       | 5.10.2   | 2 N  | Aer  | nor  | y Pe  | erfo | orn  | nar        | nce  |     |     |     |   | <br>• | • | • | • | • | • | • |       |   | • |   | • | . 1 | 51 |

|    | 5.11  | Relate   | ed   | W    | ork  |       |      |      |            |      |     | •   |     |   |       |   | • | • |   | • | • |       |   |   |   | • | . 1 | 54 |

|    |       | 5.11.1   | 1 N  | /ler | nor  | y A   | cce  | ess  | Сс         | ontr | rol |     |     |   | <br>• |   | • | • |   | • | • |       |   | • |   | • | . 1 | 54 |

|    |       | 5.11.2   | 2 I  | sola | atio | n N   | lec  | ha   | nis        | ms   |     | •   |     |   | <br>• |   | • | • |   | • | • |       |   | • |   | • | . 1 | 56 |

|    |       | 5.11.3   | 3 A  | Aut  | om   | atic  | Isc  | ola  | tio        | n    |     | •   |     |   |       |   | • | • |   | • | • |       |   |   |   | • | . 1 | 57 |

|    |       | 5.11.4   | 4 A  | Aut  | om   | atic  | Pr   | ivi  | ileg       | ge S | Sep | ara | tio | n |       |   | • | • |   | • | • |       |   |   |   | • | . 1 | 58 |

|    |       | 5.11.5   | 5 (  | )wi  | ners | ship  | in   | М    | lem        | ory  | у.  |     |     |   | <br>• |   | • | • |   | • | • |       |   | • |   | • | . 1 | 60 |

|    |       | 5.11.6   | 5 T  | ſag  | ged  | Me    | emo  | ory  | <i>'</i> . | •    |     |     |     |   | <br>• |   | • | • |   | • | • | <br>• | • | • | • | • | . 1 | 60 |

|    | 5.12  | Conclu   | lus  | ion  |      |       |      | •    |            |      |     | •   |     |   |       |   | • | • |   | • | • |       |   |   | • |   | . 1 | 61 |

| 6  | Cor   | nclusior | n a  | anc  | l Fı | ıtur  | e V  | No   | rk         |      |     |     |     |   |       |   |   |   |   |   |   |       |   |   |   |   | 1   | 62 |

|    | 6.1   | Conclu   | lus  | ion  | l.   |       |      |      |            |      |     |     |     |   |       |   | • | • |   | • |   |       |   |   |   |   | . 1 | 62 |

|    | 6.2   | Future   | re ' | Wo   | rk   |       |      | •    |            |      | • • |     |     |   |       |   | • | • |   | • | • |       |   |   |   |   | . 1 | 63 |

| Bi | bliog | raphy    |      |      |      |       |      |      |            |      |     |     |     |   |       |   |   |   |   |   |   |       |   |   |   |   | 1   | 64 |

| Vi | ta    |          |      |      |      |       |      |      |            |      |     |     |     |   |       |   |   |   |   |   |   |       |   |   |   |   | 1   | 86 |

### ACKNOWLEDGMENTS

Studying in the US is a journey with so many exciting as well as astonishing moments for me. My PhD pursuit here is very much blessed, by the help of so many people.

First, I thank my advisor, Prof. Qun Li, for his generous support on my research interests, as well as his nuanced care for my living. Professionally, he has given me many professional suggestions over the projects in my thesis as well as much free space to pursue my interests. Thanks to the valuable freedom he allowed, I have been able to learn what I dreamed of, especially for the interest of software-hardware co-design project that has brought me a deeper understanding of the computer system from bottom up. Personally, he had helped me to resolve many difficulties to adapt the new environment here in the US.

I thank Prof. John Criswell at the University of Rochester. Working with John opened a new world of system security for me and inspired me many new ideas that I am still wishing to develop in the future.

I thank Dr. Ang Li at Pacific Northwest National Laboratory. Ang taught me a new skill of how to build a complex system from scratch more efficiently and effectively – the art of growing a minimal toy system into a full-fledged complex system with spiral iterations.

I thank Senior Security Researcher Dr. Tamas K Lengyel. Tamas instructed me to learn hardware events in LibVMI and many Xen internals into the deep during my participation of google summer of code with him.

I thank many teachers and students who helped me improve over the years. To the teachers whose classes or mentoring I have learnt a lot from: Prof. Xu Liu, Prof, Adwait Jog, Prof. Gang Zhou, Prof. Weizhen Mao, Dr. Tim Davis, Mr. Chris Shenefiel, Dr. Sarah Glosson, and Dr. Leslie Bohon at William & Mary, and Prof. John Criswell, Prof. Sreepathi Pai, Prof. Chen Ding, Prof. Micheal Scott from University of Rochester, and Prof. Robert J. Walls from Worcester Polytechnic Institute. And many thanks to Zhuojia Shen, Jie Zhou, and Yufei Du for your effective help on my LLVM study and our impressive collaboration during my visit.

I thank the students in our lab, Yutao Tang, Zijiang Hao, Shanhe Yi, Nancy Carter, Cheng Li, Zeyi Tao, Yunlong Mao, and Qi Xia. You are all awesome and thank you for the interesting discussions we have been on during our group meetings.

I thank my thesis committee members, Prof. Weizhen Mao, Prof. Adwait Jog, Prof. Dmitry Evtyushkin, and Dr. Ang Li, for their willingness to serve in my committee, and their helpful comments on my presentation and thesis.

I thank Vanessa Godwin, Jacqulyn Johnson, Dale Hayes, at our Computer Science Department office and Eva Wong, Zabrina Williams, and Emily Bailey at Reves Center for their prompt help with my Ph.D. program. I thank the Graduate Coordinator Michelle Kiso for her prompt help during my visit at University of Rochester.

Last and most importantly, I thank my family for their constant encouragement. Without their unconditional support, I will not be who I am today. Special thanks to Dr. Ruiqin Tian, especially for her strong encouragement during the hard time. To my family

### LIST OF TABLES

| 3.1                                                                                      | Docker Container Migration Time (bandwidth 600Mbps, latency 0.4ms) 19 | 9                          |

|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------|

| 3.2                                                                                      | Docker Container Migration Time (bandwidth 15Mbps, latency 5.4ms) 19  | 9                          |

| 3.3                                                                                      | Overall System Performance                                            | 7                          |

| 4.1                                                                                      | VMI System Code Base in Lines of Code (LoC)                           | 1                          |

|                                                                                          |                                                                       |                            |

| 4.2                                                                                      | Libraries Ported to Mini-OS                                           | 3                          |

| 4.3                                                                                      | Code Base Reduction                                                   | 4                          |

| 4.4                                                                                      | Binary Size Reduction                                                 | 4                          |

| 4.5                                                                                      | Changes to the Xen hypervisor and Mini-OS kernel                      | 5                          |

| 4.6                                                                                      | Runtime Machine Memory Reduction                                      | 7                          |

| 4.7                                                                                      | Overhead when Monitoring Single Process by CR3 Register Events . 9    | O                          |

|                                                                                          |                                                                       |                            |

| 5.1                                                                                      | ISA Extensions to Load Instructions                                   | 4                          |

| 5.1<br>5.2                                                                               | ISA Extensions to Load Instructions                                   |                            |

|                                                                                          |                                                                       | 5                          |

| 5.2                                                                                      | ISA Extensions to Store Instructions                                  | 5<br>6                     |

| 5.2<br>5.3                                                                               | ISA Extensions to Store Instructions                                  | 5<br>6<br>6                |

| 5.2<br>5.3<br>5.4                                                                        | ISA Extensions to Store Instructions                                  | 5<br>6<br>7                |

| <ol> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> </ol>                           | ISA Extensions to Store Instructions                                  | 5<br>6<br>7<br>1           |

| <ol> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>5.6</li> </ol>              | ISA Extensions to Store Instructions                                  | 5<br>6<br>7<br>1<br>2      |

| <ol> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>5.6</li> <li>5.7</li> </ol> | ISA Extensions to Store Instructions                                  | 5<br>6<br>7<br>1<br>2<br>8 |

| 5.11 | CPU an | nd Memory | Traffic with | th In-Memory  | Tag .   | ••• | <br> | <br>• |  | 153 |

|------|--------|-----------|--------------|---------------|---------|-----|------|-------|--|-----|

| 5.12 | CPU an | nd Memory | Traffic wit  | h Double-Size | e Cache | es. | <br> |       |  | 154 |

### LIST OF FIGURES

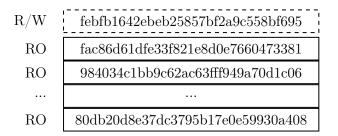

| 3.1        | OpenFace Container's Image Layer Stack                                                                           | 22       |

|------------|------------------------------------------------------------------------------------------------------------------|----------|

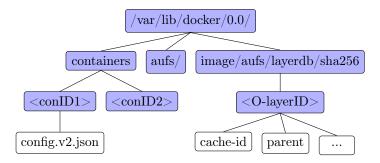

| 3.2        | Docker Layered File System Structure                                                                             | 24       |

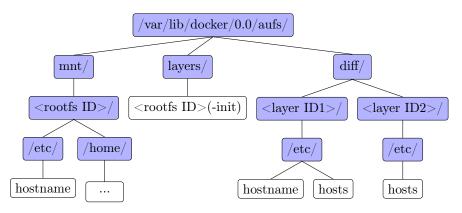

| 3.3        | AUFS Work Directories in Docker's Layered Storage                                                                | 24       |

| 3.4        | Caption for LOF                                                                                                  | 28       |

| 3.5        | Offloading Serivce Handoff: Before and After Migration of Offloading                                             |          |

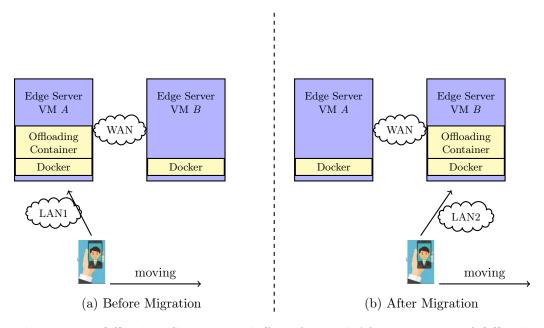

|            | Container.                                                                                                       | 30       |

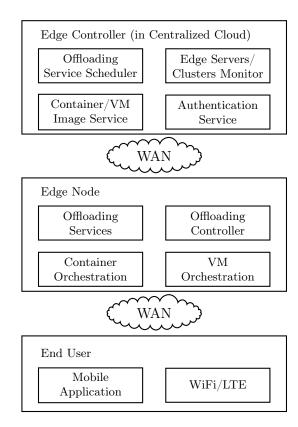

| 3.6        | Overview of Edge Computing Platform                                                                              | 31       |

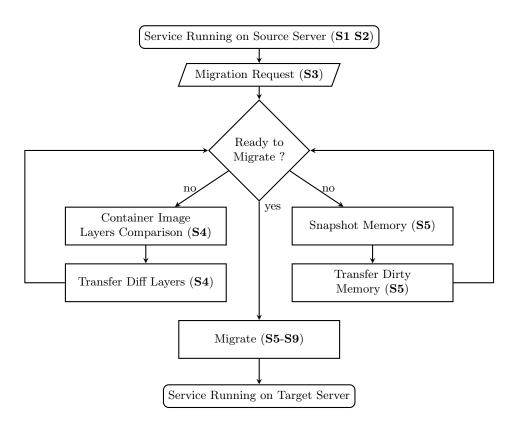

| 3.7        | Full Workflow of Offloading Service Handoff                                                                      | 34       |

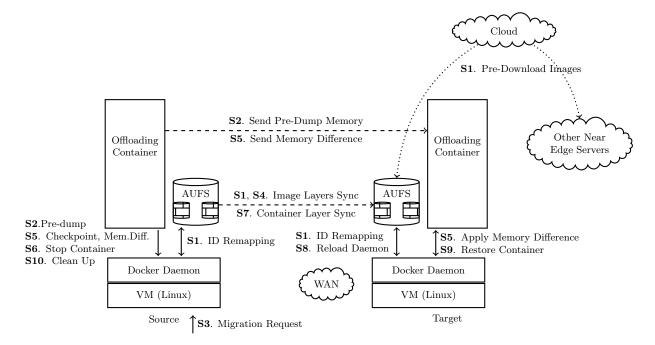

| 3.8        | Major Procedures of Migration                                                                                    | 36       |

| 3.9        | Busybox: Time Duration of Container Migration Stages with and                                                    |          |

|            | without Pipelined Processing                                                                                     | 45       |

| 3.10       | OpenFace: Time Duration of Container Migration Stages with and                                                   |          |

|            | without Pipelined Processing                                                                                     | 45       |

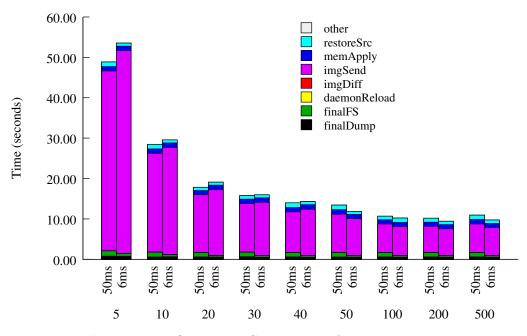

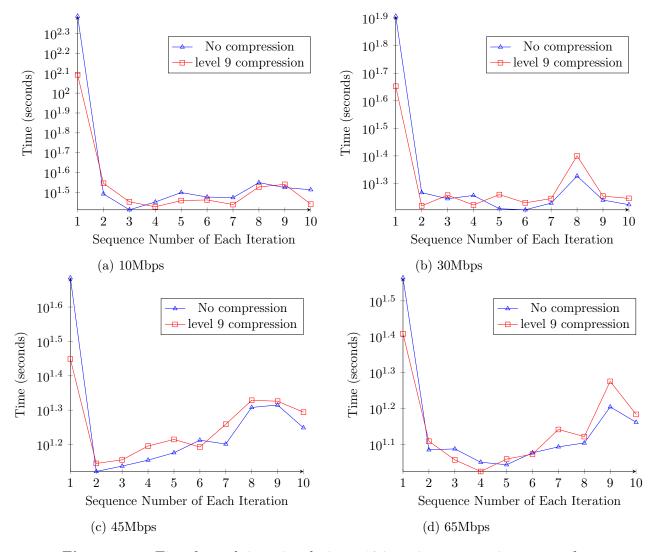

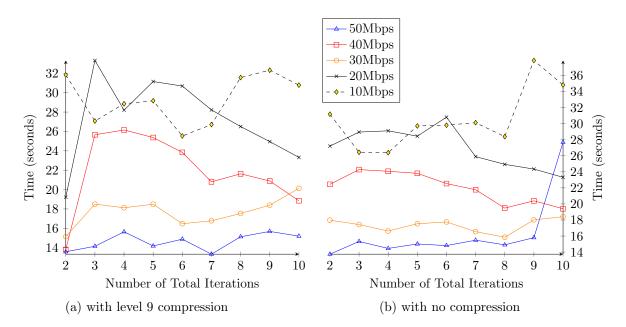

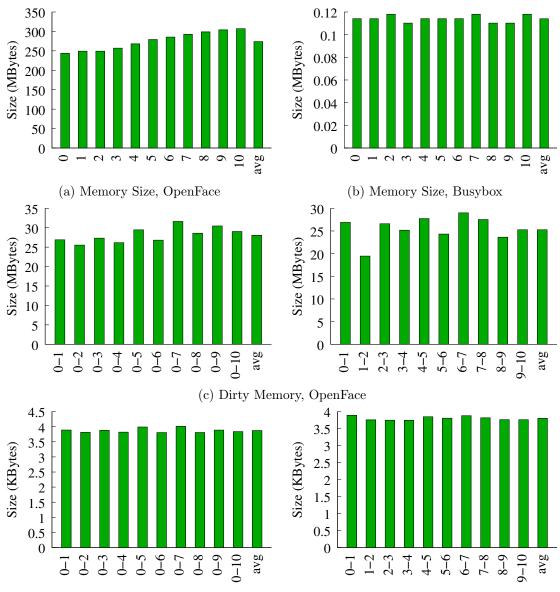

| 3.11       | Busybox: Comparison of Migration Time.                                                                           | 48       |

| 3.12       | OpenFace: Comparison of Migration Time.                                                                          | 48       |

| 3.13       | Time for each iteration during a 10 iteration memory image transfer $% \left( {{{\bf{n}}_{{\rm{m}}}}} \right)$ . | 49       |

| 3.14       | Time of Service Handoff Under Different Total Iterations.                                                        | 50       |

| 3.15       | Dirty Memory Size Analysis for OpenFace and Busybox                                                              | 52       |

| 4.1        | One Layer to Monitor All Layers via <i>EdgeVMI</i>                                                               | 67       |

| 4.2        | <i>EdgeVMI</i> Deploy Example under Centralized Cloud Management                                                 | 68       |

| 4.2<br>4.3 | Run-time Workflow for Intrusion Detection and Emergency Response                                                 | 00<br>70 |

| 4.0        | tun-time worknow for instasion Detection and Emergency Response                                                  | 10       |

| 4.4 | Build Single-Purpose Tiny Monitor VMs in <i>EdgeVMI</i> 71                     |

|-----|--------------------------------------------------------------------------------|

| 4.5 | An Example implementation of <i>Sensor</i> VM 80                               |

| 4.6 | An Example of Actuator VM                                                      |

| 4.7 | Time Cost With Different Number of Events                                      |

| 4.8 | Average Throughput & Latency                                                   |

| 4.9 | Time to Read Raw Memory Pages                                                  |

|     |                                                                                |

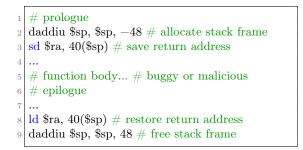

| 5.1 | Return Address Save and Restore                                                |

| 5.2 | Overview of <i>Capsules</i> in the Memory Hierarchy                            |

| 5.3 | Tags for Non-Pointer (32-bit tag per 32-bit memory)                            |

| 5.4 | Tags for a Data Pointer (64-bit tag per 64-bit pointer)                        |

| 5.5 | Tags for a Code Pointer (64-bit tag per 64-bit pointer)                        |

| 5.6 | An example of <i>sanitized transition</i> gate between two <i>capsules</i> 122 |

| 5.7 | Two Memory Models                                                              |

| 5.8 | Spatial Safety for a Global Variable                                           |

| 5.9 | Temporal Safety for Heap Object                                                |

Revisiting Isolation for System Security and Efficiency in the Era of Internet of Things

# Chapter 1

# Introduction

### 1.1 Motivation

Isolation is one of the fundamental paradigms since the birth of computer systems. First, isolation plays an important rule for resource sharing on modern computing systems. For example, resource isolation between different users on a cloud machine enables the efficient sharing of the costly computing resources. Second, isolation is important to secure computing systems. It is one of a few techniques that can defend against unknown vulnerabilities in the program. Program can be separated into different function modules and each module can be isolated in a security domain. In this way, security breaches in one domain will not likely to affect other domains. For example, isolation between the kernel and user space in a computer system effectively reduces the risk of software vulnerabilities that are caused by a diversity of user applications. Until now, we have seen process-based isolation, virtual machines, Linux containers, sandboxes, software fault isolation, Intel SGX, Intel MPK, ARM TrustZone, etc., with a variety of granularities of isolation.

However, when the Internet of Things (IoT), and edge computing platforms <sup>1</sup> bring several new features to the computing environment, many traditional isolation mechanisms become inefficient or just do not work.

<sup>&</sup>lt;sup>1</sup>This thesis will use *edge servers* to refer a cluster of computing nodes (such as *cloudlet* servers [141]) in close proximity to the end users and *IoT devices* as client device that receives services from edge servers.

#### 1.1. MOTIVATION

On the server side, edge servers are usually not in a centralized environment as in data centers for cloud computing, and they are less powerful but more performance sensitive than traditional cloud servers. Edge servers are mostly deployed distributively in large geographical areas. Consequently, the network bandwidth and latency between different edge computing nodes can be rather limited, rendering many traditional cloud services, such as networking shared file system, live migration, etc., unrealistic to be used on the edge. Therefore, the first project (Chapter 3) aims to improve the efficiency of live migration services between edge nodes. Another problem is that the protection of a large amount of small edge servers on the edge becomes challenging. Without the centralized deployment, traditional security solutions can be inefficient to be deployed over large geographical areas. In addition, edge servers are relatively less powerful than high performance computers in the cloud. Therefore, traditional security solutions in the cloud either cannot be directly deployed to the edge, due to either execution overhead or engineering overhead. Therefore, the second project in this thesis (Chapter 4) proposes a lightweight memory monitoring solution to improve the security of edge servers.

On the client side, IoT devices are mostly equipped with low-end processors but require real-time response. Most IoT devices are embedded systems designed for domain specific tasks, where many features for a general purposed design are downgraded or simply removed. With these fundamental changes at hardware level, many traditional isolation solutions on a general purpose machine are no longer suitablefor such small devices. For example, many IoT devices does not have the Memory Management Unit (MMU) in favor of real time response. In practice, this have resulted in almost no protection between the applications and the OS kernel running on the same device. Therefore, IoT devices need either revised or new isolation mechanisms in order to be trustworthy. Following this route, our third project (Chapter 5) proposes a fine-grained isolation technique to improve the memory safety for IoT devices.

In brief, this thesis work explores different isolation techniques on the edge servers and IoT devices. On the server side, this thesis has resolved two problems, including a performance problem for live migration between container-based edge servers, and a security monitoring problem on virtual-machine based edge servers. On the client side, this thesis has described the need for the new fine-grained isolation technique and proposed a software-hardware co-design solution for efficient fine-grained intra-address space isolation on IoT systems.

### **1.2** Efficient Live Migration across Edge Servers

As we mentioned above, many services, such as networking shared file system, live migration, etc., are unrealistic to be used on the edge servers. Live migration has long been used in traditional cloud computing environment. Traditional migration techniques assumes all the file system are shared over high speed network between the source node and target node, which means there is no need for an explicit file system synchronization during migration. However, many edge servers are deployed over the wide area network (WAN). In such a environment, the network bandwidth and latency between different edge servers can be rather limited. Therefore, networking shared file system is not practical for edge servers. A naive solution would be to transfer the entire file system during live migration. However, as expected, the delay of migration will take too long (hours) to be useful.

To resolve the issue, we have investigated the state of the art Docker container's layered file system. We proposed a new live migration solution that does not depends on a networking shared file system. In this solution, file system are managed in different layers where most layers are read only. Therefore, we propose to transfer most of the read only file system layers before migration starts, together with a base image for the runtime memory. During migration, we only need to transfer the latest updated files and dirty memory to reduce the transmission traffic. This reduces the migration time significantly as we will show in Chapter 3.

### 1.3 Lightweight Security Monitor for Edge Servers

As we mentioned, most edge computing servers have limited resources comparing to cloud servers. This makes them more sensitive to heavy weight monitoring solutions such as virtual machine introspection. In addition, edge servers are distributively deployed in large geographical areas, which makes the deployment and maintenance of security monitoring solutions more challenging than in a centralized cloud center.

Therefore, in the second project, we propose a security monitoring solution for edge servers. It is deeply trustworthy without the trust of entire operating system; It is lightweight and applicable to low performance machines; It can be remotely deployed and maintained efficiently without physical intervention on the servers. The key technique is to build a virtual machine introspection monitor in in a minimized library operating system (or a Unikernel as we will introduce in Section 2.2). The evaluations on our prototype system successfully shows the effectiveness and the efficiency of our monitoring solution, as will be described in Chapter 4.

### 1.4 Secure IoT Systems with Hardware Ownership Tags

The client side on edge computing platforms is composed of a various kinds of IoT devices. These include desktop machines, laptops, mobile phones, as well as the much less powerful embedded devices such as smart watches, smart locks, smart bands, etc. Secure and efficient isolation between different modules on such devices are critically important for the security defense on such devices. Intra-address space isolation is much more efficient than virtual memory based isolation mechanisms. Therefore, it is widely used on IoT devices. However, existing intra-address space isolation mechanisms are rather limited. First, they usually support only a limited number of isolation domains. Second, they usually support only coarse-grained isolation in the address space. Third, they usually partially support pointer safety or support isolation in the address space, instead of support both of them. Fourth, most of them require intensive changes in the legacy code in order to enforce the security policies.

Therefore, the third project designs and implements the *Capsule* system. It is an architectural extension along with a full stack toolchain and system support. It supports fine-grained isolation in the same address space. It also supports both temporal and spatial pointer safety to harden the programs writen in unsafe languages such as C programming language. It has fine-grained memory protection at the granularity of instructions and data words. More importantly, it requires minimal porting efforts to protect legacy programs. The prototype system is built by extending an open sourced MIPS core, with the LLVM toolchain, and FreeBSD operating system. Evaluation shows the effectiveness of the system as we will discuss in Chapter 5.

### 1.5 Dissertation Organization

The remainder of this dissertation is organized as follows. Chapter 2 introduces some background conceptions that are necessary to understand this work. Chapter 3 introduces the work to improve the efficiency of container migration by leveraging the Docker layered file system. Chapter 4 introduces the work where a lightweight virtual machine introspection framework is designed to monitor the security of edge servers. Chapter 5 presents the *Capsule* system for fine-grained isolation with hardware-assisted ownership tags in the memory. Chapter 6 concludes this thesis.

# Chapter 2

# Background

### 2.1 Docker Containers

Docker is a set of platform as a service (PaaS) products that deliver software in packages called containers [88]. Docker containers allows the package of the entire developing environment into container images and could be shared among different operating systems including Linux, Windows, MacOS, etc. This allows developers to build, share and run their applications anywhere without the hassle of setting up the new developing environment from time to time. Docker containers are based on OS-level virtualization where different containers on the same host share the same operating system kernel [137].

### 2.2 Xen and Unikernels

Xen Hypevisor [129] is a virtual machine monitor which allows multiple commodity operating systems to share the hardware on the same host in a safe and resource managed fashion, but without sacrificing either performance or functionality [20]. Beside commodity operating system such as Linux and Windows, Xen also supports running Unikernels such as Mini-OS, MirageOS, etc.

A unikernel is a specialized library operating system that has only a single address space and without kernel/user mode separation as in a regular operating system [111]. It is usually built with a minimal set of modules or libraries that are required by the functionality of the application. A unikernel could run directly on a hypervisor such as Xen or run directly on hardware without an intervening OS.

Xen Mini-OS [127] is one of the earliest library operating system on Xen hypervisor. It is used to build stub domains, a set of small virtual machines that disaggregate the Xen Domain 0, and it is used as the basis for the development of Unikernels [8].

### 2.3 QEMU

QEMU [22] is a generic and open source machine emulator and virtualizer. As a machine emulator, QEMU can run operating systems and programs written for one architecture (e.g. a MIPS processor) on a different machine (e.g. an x86 PC). By using dynamic translation, it achieves very good performance. It can be extended for fast evaluating the functionality of a new architecture design. However, QEMU cannot be used to measure the performance of the new architecture design because it lacks the architectural timing measurements (Gem5 can be used instead). In addition, QEMU can also be used as a virtualizer, where it could execute the guest code directly on the host CPU by multiplexing the resources of the host machine (e.g., using the KVM [97] kernel module in Linux).

### 2.4 gem5 Simulator

The gem5 simulator [5] is a modular platform for computer system architecture research. It could simulate system-level architecture as well as processor microarchitecture. It supports multiple processor models such as ARM, x86, RISC-V, SPARC, and Alpha, where each model can be extended with new functionalities for research purposes.

On the gem5 platform, users could composite a full stack computer system by combining the models for the CPU, cache, and the memory, as well as disk images for booting. Users could also play with only partial of the system. For example, gem5 can replay CPU traces or memory traces to evaluate the performance of the memory system without a CPU model or virtual address translation models.

### **2.5** Bluespec and bluesim

Bluespec [119] is a high-level hardware description language (HDL) in develop since 2000. Now it has been used in production designs like RISC-V cores Flute [4], Piccolo [9], and Toooba [10]. It has a powerful type system that can prevent errors prior to synthesis time. In addition to the System Verilog-like syntax, it also comes with syntactic flavor of the Haskell functional programming language and both flavors are interchangeable. The Bluespec compiler emits standard Verilog so it can be compatible with any synthesis toolchain.

In addition to using other simulators for Verilog descriptions, Bluespec also comes with its own cycle simulator *bluesim*. The compiled hardware description could be linked into *bluesim* simulation environment and an executable binary will be generated. When the binary is executed, the hardware module is simulated.

### 2.6 LLVM toolchain

LLVM [7] is a collection of modular and reusable compiler and toolchain technologies. It uses Clang [3] as front-end for C language family (C, C++, Objective C/C++, OpenCL, CUDA, and RenderScript). Clang can be extended to support user annotations in the source code. The front-end compiles the source code into LLVM intermediate code representation (LLVM IR), or LLVM bitcode. Then LLVM core libraries could provide a various of analysis and optimizations on LLVM bitcode so that they do not depend on the source code or the target.

LLVM code generator (codegen) is the backend which translates LLVM IR into target specific machine code. The code generator in LLVM contains multiple stages (or passes in LLVM): instruction selection, register allocation, scheduling, code layout optimization, and assembly emission. LLVM uses its own linker LLD [6] as drop-in replacement for the default system linkers. Linkers are responsible to generate executable file by linking multiple object files generated by the LLVM. LLD supports Link-Time Optimization(LTO) and allows LLVM to do whole program optimization during linking. LLD supports a wide range of binary formats including ELF(Unix), PE/COFF(Windows), Mach-O(macOS) and WebAssembly.

### 2.7 Privilege Separation and Isolation

Privilege separation [138] is an important line of defense against unknown vulnerabilities in a system. In a privilege separated system, a program is partitioned into multiple isolated security domains and each keeps its least privileges that are just enough to do its tasks. In such a system, security breaches in one domain will not likely affect other domains.

Privilege separation has been widely used in modern computer systems to ensure the secure sharing of the computer resources such as CPU, memory, storage, etc. For example, different processes are isolated inside an operating system so that different users and different programs won't interfere with each other erroneously. Another example is that inside the address space of a single process, user memory and kernel memory are separated and isolated by the operating system.

In this thesis, the term of *privilege separation* and *isolation* can be interchangeable when they are used to refer to partitioning a program in general. However, we also differentiate *isolation* from *privilege separation* in terms of the emphasized stage during program partition. We will use *privilege separation* to refer to the process to analyze the program and find out which module should be separated with other modules in a program. This process is usually determined by the security semantic of the program, and is irrelevant to what kind of isolation mechanisms will be used. On the other hand, we will use *isolation* to refer to the process where a list of separated modules and their security requirements are given as input, and these modules will be isolated into different protection domains by leveraging certain kinds of isolation mechanisms. This process is mostly focused on how to leverage specific isolation mechanisms to enforce the domain isolation, and the security requirements and how to separate the program modules are assumed to be known facts.

### 2.8 Intra-address Space Isolation

Intra-address space isolation is used to separate privileges inside the same process, usually used to isolate different modules or libraries inside a single user program or inside an operating system kernel. For example, Software Fault Isolation(SFI) [159] and its derived techniques, such as Native Client [173], BGI [33], etc., are pure software solution can be used to partition the entire address space into different isolated memory regions. In these techniques, every memory accesses are checked either statically or dynamically to ensure the memory address being accessed is valid (does not cross the given boundary).

There are also hardware assisted isolation mechanisms such as CPU Rings [144], Intel SGX [47], MPK [90], and ARM TrustZone [16], ARM MPU [17], etc. Hardware assistance could help to reduce the overhead significantly comparing to the pure software based solutions. In these mechanisms, the memory accesses are checked either by checking the permission bits in the page table entry (CPU Rings, Intel SGX, Intel MPK, and ARM TrustZone) or other hardware supported permission descriptors (ARM MPU). These techniques vary in how they manage the format of permission bits and how to switch the execution between different protection domains.

# Chapter 3

# Efficient Live Migration across Edge Servers

### 3.1 Overview

Mobile users across edge networks require seamless migration of offloading services. Edge computing platforms must smoothly support these service transfers and keep pace with user movements around the network. However, live migration of offloading services in the wide area network poses significant service handoff challenges in the edge computing environment. In this work, we propose an edge computing platform architecture which supports seamless migration of offloading services while also keeping the moving mobile user "in service" with its nearest edge server. We identify a critical problem in the state-of-the-art tool for Docker container migration. Based on our systematic study of the Docker container storage system, we propose to leverage the layered nature of the storage system to reduce file system synchronization overhead, without dependence on the distributed file system. In contrast to the state-of-the-art service handoff method in the edge environment, our system yields a 80%(56%) reduction in handoff time under 5Mbps(20Mbps) network bandwidth conditions.

### 3.2 Introduction

Edge computing has become a prominent concept in many leading studies and technologies in recent years [24, 37, 83, 84, 85, 125, 140, 141, 152, 174, 175, 176]. Since edge servers are in close proximity to the mobile end user, higher quality of services (QoS) could be provided than was possible with the traditional cloud platform [125, 140]. End users benefit from edge services by offloading their heavy duty computations to nearby edge servers [14, 53, 101, 107]. Then the end user experience with cloud services will achieve higher bandwidth, lower latency, as well as greater computational power.

One of the key challenges for edge computing is keeping quality of service guarantees better than traditional cloud services while offloading services to the end user's nearest edge server. However, when the end user moves away from the nearby edge server, the quality of service will significantly decreases due to the deteriorating network connection. Ideally, when the end user moves, the services on the edge server should also be live migrated to a new nearby server. Therefore, efficient live migration is vital to enable the mobility of edge services in the edge computing environment.

Several approaches have been investigated to live migrate offloading services on the edge. Virtual machine (VM) handoff [80, 81] divides VM images into two stacked overlays based on VM synthesis [141]. During migration, only the overlay on the top is transferred from the source to the target server instead of the whole VM image volume. This significantly reduces data transfer size during migration. However, a virtual machine overlay can be tens or hundreds of megabytes in size, thus the total handoff time is still relatively long for latency sensitive applications. For example, OpenFace [14], a face recognition service, will cost 247 seconds to migrate on a 5Mbps wide area network (WAN), which barely meets the requirements of a responsive user experience. Additionally, VM overlays are hard to maintain, and are not widely available in the industrial or academic world.

In contrast, the widely deployed Docker platform raises the possibility of high speed service handoffs on the network edge. Docker [88] has gained popularity in the industrial cloud. It employs layered storage inside containers, enabling fast packaging, sharing, and shipping of any application as a container. Live migration of Docker containers is achievable. For example, *P.Haul* [65] supports live migration containers on Docker 1.9.0 and 1.10.0. They are developed based on a user level process checkpoint and restore tool *CRIU* [52]. But *P.Haul* will transfer the whole container file system in a bundle during the migration, regardless of storage layers, which could induce errors as well as high network overhead.

In exploring an efficient container migration strategy tailored for edge computing, we focus on reducing the file system transfer size by leveraging Docker's layered storage architecture. Docker's storage allows only the top storage layer to be changed during the whole life cycle of the container. All layers underlying the top layer will not be changed. Therefore, we propose to share the underlying storage layers before container migration begins, and only transfer the top layer during the migration itself.

In this work, we build a system which allows efficient live migration of offloading services on the edge. Offloading services are running inside Docker containers. The system will reduce the transferred file volumes by leveraging layered storage in the Docker platform. Our work addressed following challenges during this project:

First, the internals of Docker storage management must be carefully studied. Few studies have been published regarding Docker storage. Reading the raw source code enables better understanding of the inner infrastructure.

Second, an efficient way to take advantage of Docker's layered storage must be carefully designed to avoid file system redundancy. We found that Docker creates a random number as local identification for each image layer downloaded from the cloud. As a result, if two Docker hosts download the same image layer from the same storage repository, these layers will have different reference identification numbers. Therefore, when we migrate a container from one Docker host to another, we must recognize whether there are any image layers with different local identification numbers yet having the same content, thus avoiding transfer of redundant image layers during the container migration.

#### 3.2. INTRODUCTION

Third, besides the file system, we also need to optimize transmission of the raw memory pages, used to restore the live status of the offloading service. Binary data are different in format then the file system, and thus must be treated separately.

Last, in terms of end user experience, we need to reduce the user-experienced connection interruption during service migration. It is possible that user-experienced interruption interval could be shorter than the actual migration time through a well designed migration process strategy. Ideally, our goal is seamless service handoff wherein users will not notice that their offloading service has been migrated to a new edge server.

We propose a framework that enables high speed offloading service migration across edge servers over WAN. During migration, only the top storage layer and the incremental runtime memory is transferred. The total migration time and user perceived service interruption are significantly reduced. The contributions of this work are listed as below (a preliminary version of this work appeared in [109]):

- We have investigated the current status of container migration and identified performance problems.

- We have analyzed Docker storage management based on the AUFS storage driver, and studied the internal image stacking methodology.

- We have designed a framework that enables efficient live migration of offloading services by sharing common storage layers across Docker hosts.

- A prototype of our system has been implemented. Evaluation shows significant performance improvement with our design, up tp 80% on 5Mbps networks.

We will briefly introduce the motivation of this work in Section 3.3. Section 3.4 reports the systematic study of Docker storage management, and the problems of previous Docker migration tools. Section 3.5 discusses the design of our system infrastructure. In Section 3.6, the prototype system is evaluated. Section 3.7 discusses related work, and Section 3.8 concludes this work.

# 3.3 Motivation

In this section, we seek to answer the following questions: Why do edge applications need offloading of computation? Why is service migration needed in edge computing? Why do not use VM-based migration and why do we seek to perform migration via Docker containers?

# 3.3.1 Offloading Service is Essential for Edge Computing

With the rapid development of edge computing, many applications have been created to take advantage of the computation power available from the edge.

For example, edge computing provides powerful support for many emerging augmented reality (AR) applications with local object tracking, and local AR content caching [85, 141]. It can be used to offer consumer or enterprise propositions, such as tourist information, sporting event information, advertisements, etc.. The Gabriel platform [82] is designed within the context of wearable cognitive assistance applications using a Glass-like wearable device, such as Lego Assistant, Drawing Assistant, or Ping-pong Assistant. OpenFace [14] is a real-time mobile face recognition program based on a deep neural network. The OpenFace client sends pictures captured by the camera to a nearby edge server. The server runs a face recognition service that analyzes the picture and sends symbolic feedback to the user in real time. More edge applications can be found in [83, 84, 140, 174, 175]. In brief, applications on the edge not only demand intensive computations, or high bandwidth, but also require real time response.

# 3.3.2 Effective Edge Offloading Needs Migration for Service Handoff

As mentioned previously, highly responsive services rely upon relatively short network distances between the end user and the edge server. However, when the end user moves farther away from its current edge server, offloading performance benefits will be dramatically diminished.

### 3.3. MOTIVATION

In the centralized cloud infrastructure, mobility of end users is well supported since end users are connected to the centralized cloud server through WAN. However, in the edge computing infrastructure, mobile devices connect to nearby edge servers with high bandwidth and low latency connections, usually via a LAN. Therefore, when the mobile device moves farther away from its edge server, the connection will suffer from higher latency, or may even become totally interrupted.

In order to be continuously served by a nearby edge server, the offloading computation service should migrate to a new edge server that is closer to the end user's new location than the current server. We regard this process as a *service handoff* from the current edge server to the new edge server. This is similar to the *handover* mechanism in cellular networks, wherein a moving user connects to the nearest available base station, maintaining connectivity to the cellular network with minimal interruption.

However, there exists one key difference between the cellular network handover and the edge server handoff. In cellular networks, changing a base station for the mobile client is as simple as rebuilding a wireless connection. Most runtime service states are not stored on the base station but are saved either on mobile client, or on the cloud. Therefore, after re-connection, the runtime state can be seamlessly resumed through the new connection.

In the edge infrastructure, mobile devices use edge servers to offload resource-hungry or computation-intensive computations. This means that the edge server needs to hold all the states of the offloading workloads. During the service handoff from one edge server to another, all the runtime states of offloading workloads need to be transferred to the new edge server. Therefore, fast live migration of offloading services across edge servers is a primary requirement for edge computing.

# 3.3.3 Service Handoff via VM Migration is Not Practical