# Performance Comparison of Five-Level Active Neutral Point Converter Based on Phase Disposition-PWM and Alternate Phase Opposition Disposition-PWM

Zainab Ameer Noory 1\*, Raaed. F. Hassan 1

**Abstract.** The work in this paper presents the performance analysis of the reduced component count converter which is the 5-Level Active Neutral Point Converter (5LANPC). This 5-level converter has been configured by stacking the traditional 3-Level Neutral Point Converter with the Flying Capacitor converter. Two types of control algorithms were considered and compared to explore the performance of the 5LANPC. The first algorithm was based on the Phase-Disposition-Pulse Width Modulation (PD-PWM), while the second one was based on the Alternate Phase Opposition Disposition-Pulse Width Modulation (APOD-PWM). These algorithms are used to determine the required voltage level and according to the required level the state of the switches is selected through a simplified voltage balance algorithm. This voltage balance algorithm deals with the redundant switching states to maintain the voltages of the 5LANPC capacitors at a specified level. The comparison between these two modulation strategies was performed by simulation based on MATLAB/Simulink package. Simulation results showed compelling outcomes involving the two techniques concerning the voltage and current characteristics, as well as the equilibrium in the capacitor voltages. By comparing the simulation results, it was found that the performance of the system is relatively better using the PD-PWM strategy.

#### 1 Introduction

In recent decades, converters with the ability to generate multi-level voltages, which are known as multilevel converters (MLC) have become the most attractive in the academic and industrial fields [1-4]. Their attractiveness resulted from the nature of their structure that qualifies there to work in medium and high voltage applications using switches with low voltage rate [5-9]. Moreover, these converters contribute to improving the quality of voltage and current, which leads to reduced total harmonic distortion (THD) and ease of filter design [6]. For more than a decade, three different MLC structures have emerged which have become the main types of the multilevel converters. These three types are the cascaded H-Bridge Converter (CHBC), Diode Clamped Converter (DCC), and Flying Capacitor

© The Authors, published by EDP Sciences. This is an open access article distributed under the terms of the Creative Commons Attribution License 4.0 (http://creativecommons.org/licenses/by/4.0/).

<sup>&</sup>lt;sup>1</sup> Electrical Engineering Technical College, Middle Technical University, Baghdad, Iraq

<sup>\*</sup> Corresponding author: bcc0006@mtu.edu.iq

Converter (FCC) [10-14]. These converters have been used by wide applications such as transformational industries, transmission and improving the quality of electric power, and sustainable energy [15-17].

In any case, the MLC experiences imperative impediments, for example, expanding the quantity of levels prompts increment the exchanging count and control intricacy. Increasing the number of levels for more than three also causes a challenge of maintaining the balance of the capacitor's voltages [6, 13, 18]. To overcomes these limitations and challenges, tremendous reduced switching count topologies of the MLC have been proposed [6, 9, 10, 12, 13, 19-21]. From many others of the reduced switching count MLC topologies, the five-level active neutral point clamped(5LANPC) is the most attractive topology. It merges the 3-level Diode Clamped Converter (DCC) and the 3-level Flying Capacitor Converter (FCC) to obtain merit in operating in each quadrant, simply requires one flying capacitor for each leg and produces high quality waveforms [2, 7, 22-25].

Principally, the Flying Capacitors (FCs) are utilized in the 5LANPC to secure the required voltage across the switching devices. Therefore, the accurate setting of the FCs voltages maintains the reliable operation of the converter and the switching devices adopted [26]. Various control strategies have been appeared in the previous literatures to regulate the voltages of the FCs in the multilevel converter which can be categorized into passive and active control strategies. In the passive category, employing the balance booster structures to control the voltages of the FCs leads to immoderate power losses [27-29]. Moreover, the traditional Proportional Integral (PI) controller was introduced in [30] to regulates the FCs voltages. This approach needs a precise tuning of the PI parameters, it may have undesirable peak overshoot, stability problems, and poor time response. The technique of the space vector modulation (SVM) was significantly utilized for governing different converter structures [31, 32]. Despite its effectiveness, the calculation burden of the SVM increase as the converter number of levels increase. In comparison with the other control strategies, the carrier-based pulse width modulation is the simplest and more compact strategy which is known as multicarrier pulse width modulation. Also, this technique can be ordered into different subprocedures, for example, Phase Disposition Pulse Width Modulation (PD-PWM), Phase Opposition Disposition PWM (POD-PWM), and Alternate Phase Opposition Disposition PWM (APOD-PWM) [33]. In this paper, a comparison of a simplified control algorithm for balancing the capacitor voltages of the three phase 5LANPC based on PD-PWM and APOD-PWM has been carried out. This paper is organized as follows: in section 2, the basic principles of the 5LANPC was introduced, section 3 presents the details of the control algorithm. The system configuration was explained in section 4, the simulation results was showed in section 5, and section 6 contains the conclusions.

#### 2 Five Level-ANPC Inverter

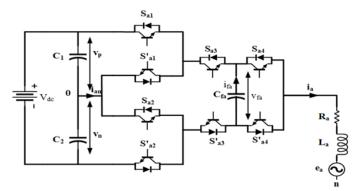

The one leg configuration structure of the 5LANPC is depicted in Fig.1, it contains eight switching devices, two main capacitors C1 and C2 which are maintain (Vdc/2) volt for each, where Vdc is the voltage of the main DC bus. Moreover, it consists of one Flying Capacitor (FC) Cfa, Vfa is the voltage across the Cfa, the current through Cfa is ifa, and ia is the phase current. The backbone of this topology is the four switching devices pairs ((S1a, S'1a) – (S4a, S'4a).

The operation principles of the one-leg 5LANPC comprises eight switching states to achieve five voltage levels based on the sum of the voltage of C1, C2, and Cfa as depicted in Table 1. Table 1 shows the main switching devices, and the remaining switching devices (S'a1, S'a2, S'a3, and S'a4) are work interchangeably with their peers. It can be seen from Table 1 that some inverter output voltage can be realized by different switching states (redundant states). Despite of producing the same output voltage, these redundant states influence the

direction of the FC current which means an indirect effect on the FC voltage. For the typical activity of the 5LANPC, the voltage across Cf for every leg ought to be kept up with at Vdc/4. Therefore, these redundant states will be taken advantage of for the purpose of maintaining the balance of the FC voltage.

Fig. 1. Structure of the one-leg 5LANPC

| <b>TABLE 1.</b> One leg 5LANPC operation principles |                 |                 |                 |                    |             |            |       |  |

|-----------------------------------------------------|-----------------|-----------------|-----------------|--------------------|-------------|------------|-------|--|

| $S_{a1}$                                            | S <sub>a2</sub> | S <sub>a3</sub> | S <sub>a4</sub> | Van                | Sign of ifa | Sign of ia | State |  |

| 0                                                   | 0               | 0               | 0               | $-V_{dc}/2$        | N. E        | N. E       | 0     |  |

| 0                                                   | 0               | 0               | 1               | $-V_{dc}/4$        | +ve         | N. E       | 1     |  |

| 0                                                   | 0               | 1               | 0               | $-V_{dc}/4$        | -ve         | +ve        | 2     |  |

| 0                                                   | 0               | 1               | 1               | 0                  | N. E        | +ve        | 3     |  |

| 1                                                   | 1               | 0               | 0               | 0                  | N. E        | +ve        | 4     |  |

| 1                                                   | 1               | 0               | 1               | $V_{dc}/4$         | +ve         | +ve        | 5     |  |

| 1                                                   | 1               | 1               | 0               | V <sub>dc</sub> /4 | -ve         | N. E       | 6     |  |

| 1                                                   | 1               | 1               | 1               | V /2               | NE          | NE         | 7     |  |

TABLE 1 One leg 5LANPC operation principles

## 3 Control Algorithm of the 5LANPC

#### 3.1 PD-PWM strategy

In this strategy, the (n-1) carrier signals shifted in level are compared with the reference sinusoidal signal to produce the required (n) commanded voltage levels. The carrier signals are divided into two groups, the first (n-1/2) group is located above the zero level (positive values), the other (n-1/2) group is below the zero reference (negative values). The following relationships are governed the operation of the proposed strategy for producing the required level:

$$O_{i} = \begin{cases} 1 & A_{m}(k) \ge A_{ci}(k) \quad i = \pm 1. \pm 2... \frac{n-1}{2} \\ 0 & otherwise \end{cases}$$

(1)

$$L = \sum_{i=0}^{n-1} O_i \tag{2}$$

Where O\_i is the output of the ith comparator, A\_m (k) is the magnitude of the reference sinusoidal signal, A\_ci (k) is the magnitude of the ith carrier signal, n is the required number of levels, and k is the sampling instant. Equations 1 and 2 rearrange the levels sequence in

ascending order, such as level 0 refers to the output voltage of (-Vdc/2), level 1 refers to (-Vdc/4) and so on.

#### 3.2 APOD-PWM strategy

In this strategy, (1) and (2) are valid, it differs from the PD-PWM strategy only in the alternating the phase of the carrier signal by 180° from its adjacent carrier signals.

#### 3.3 Switching selection algorithm

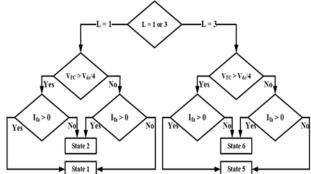

As shown in Table 1, the effect of the redundant states 1 and 2 on the FC current (ifa) is opposite despite they producing the same output voltage, the same case is true for the redundant states 5 and 6. Therefore, the effect of these states on the FC current leads to its indirect effect on the FC voltage balance. As a result, the proposed switching selection algorithm can be realized depending on the three parameters which are, the required level, the FC voltage, and the direction of the FC current. The switching selection algorithm has been configured as shown in Fig.2, its basis operation is the decision to use a switch state depending on the FC voltage and the direction of its current. This algorithm deals with the cases that have redundant states, i.e., it deals with states 1 and 2 (see, Table 1) for level 1, and states 5 and 6 for level 3. The remaining states in Table 1 have no effect on the voltage balancing of the FC so that they will not be considered in switching selection algorithm.

Fig.2. Switching selection algorithm.

### **4 System Configuration**

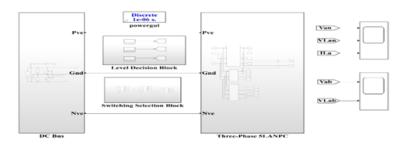

The 5LANPC and its proposed control strategy are designed and configured using MATLAB/Simulink package as shown in Fig.3. In this figure, the DC Bus block contains the Dc voltage supply with the main capacitors C1 and C2 which are hold voltage of (Vdc/2) for each. The level decision block includes the PD-PWM or the APOD-PWM with the level decision circuit that implemented based on the equations 1 and 2 with n = 5. The switching selection block has been configured according to Fig.2. As stated, only states 1 and 3 need a decision that depends on the value of the FC voltage and the direction of its current, the remaining states are supplied to the 5LANPC directly. The configuration of the switching selection block was performed using MATLAB function block. The Three-Phase 5LANPC block consists of 3-phase 5LANPC, 3-phase L-C-L filter, and 3-phase R-L load.

Fig.3. 5LANPC with proposed control strategy using Simulink

### 5 Simulation Results

To verify the effectiveness of 5LANPC based on the proposed control algorithms, simulations were performed using MATLAB/Simulink software package. Table 2 summarizes the system parameters that employed for simulation.

**TABLE 2.** System Parameters

| Parameter                   | Value    |

|-----------------------------|----------|

| DC Supply Vdc               | 600 V    |

| DC Bus Capacitors C1 and C2 | 5000 μF  |

| Flying Capacitor Cf         | 1500 μF  |

| Fundamental Frequency f     | 50 Hz    |

| Carrier Frequency           | 2.5 K Hz |

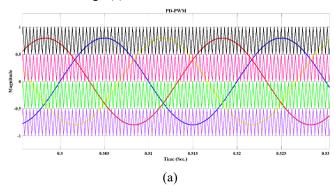

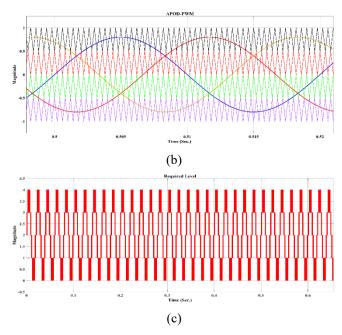

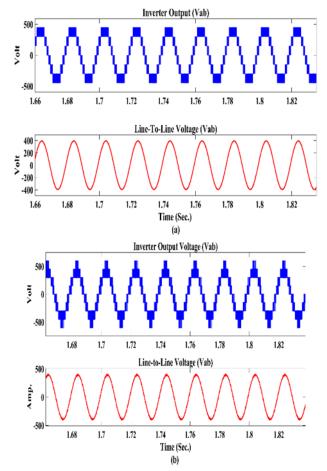

The verification process focused on the performance of the proposed control system and the response of the 5LANPC to command signals. The validity of the level decision block based on PD-PWM and APOD-PWM techniques have been examined and the results are shown in Fig.4. The intersection of the triangle carrier signals with the three-phase sinusoidal reference signals for PD-PWM and APOD-PWM are shown in Fig. 4(a) and Fig. 4(b) respectively. The instantaneous comparison between carrier signals and reference signals result in producing the required level as shown in Fig.4(c).

**Fig. 4.** Simulation Results of the Level Decision Block: (a) PD-PWM, (b)APOD-PWM, (c) Instantaneous Level.

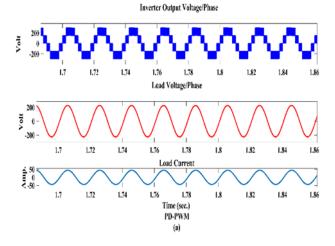

The converter output voltage, filtered load voltage and the load current with PD-PWM and APOD-PWM algorithms are shown in Fig.5. Fig. 5(a) shows the voltages and current with PD-PWM, while the voltages and current with APOD-PWM are shown in Fig. 5(b).

Fig.5. output load voltage and current with: (a) PD-PWM, (b) APOD-PWM

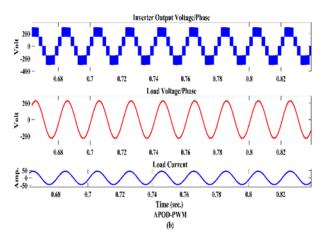

Fig. 6 shows the Line-to-Line output voltage from the 5LANPC, these voltages with PD-PWM is in Fig. 6(a), while Fig. 6(b) shows the Line-to-Line output voltage with the APOD-PWM.

Fig. 6. Line-to-Line output voltage with: (a) PD-PWM, (b) APOD-PWM.

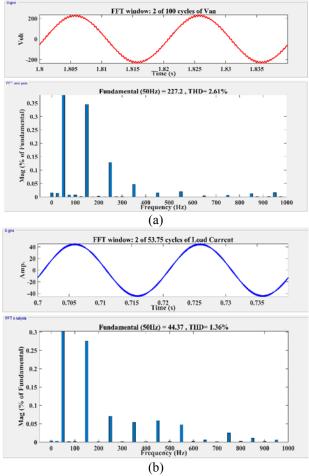

An extremely low (THD) for the stage voltage and the line current have been gotten in light of PD-PWM as portrayed in Fig.7. A 0.48% THD is obtained for the phase voltage as shown in Fig.7 (a), and 0.66% THD for the line current as shown in Fig.7 (b). Fig. 8 show the THD measurements of the load voltage and current when the APOD-PWM is adopted.

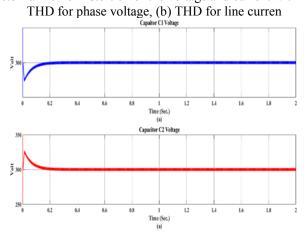

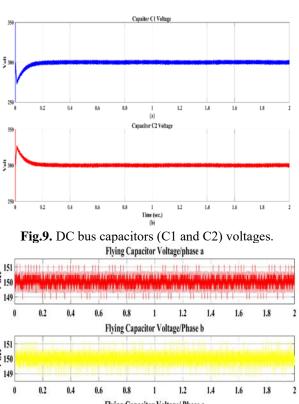

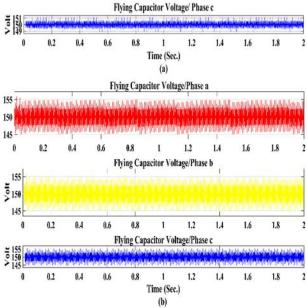

The voltage balance of the DC bus capacitors C1 and C2 is achieved as shown in Fig.9 for both modulation strategies, the voltages of capacitors C1 and C2 according to PD-PWM are shown in Fig.9(a), and these according to APOD-PWM are shown in Fig. 9(b). Finally, the flying capacitor voltages for two modulation strategies are shown in Fig. 10, where Fig. 10(a) refers to the FC voltages when PD-PWM is employed, Fig. 10(b) refers to FC voltages when APOD-PWM is considered. Table 3 summarizes the performance comparison of the 5LANPC under the DP-PWM and APOD-PWM strategies, it can be noticed that the performance is acceptable with these modulation strategies but the converter behaves best with the PD-PWM

**Fig.7.** Total Harmonic Distortion of the voltage and current with PD\_PWM: (a) THD for phase voltage, (b) THD for line current.

Fig.8. Complete Harmonic Distortion of the voltage and current with APOD\_PWM: (a)

Fig.10. Flying Capacitors Voltages.

| parameter                 | Value        |                         |  |  |

|---------------------------|--------------|-------------------------|--|--|

|                           | PD-PWM       | APOD-PWM                |  |  |

| Voltages of C1 and C2     | $300 \pm 2V$ | $300 \pm 2.8 \text{ V}$ |  |  |

| Voltages of FC            | 150 ± 1.5 V  | 150 ± 5.5 V             |  |  |

| THD of the output voltage | 0.48 %       | 2.61 %                  |  |  |

| THD of the load current   | 0.66 %       | 1.36 %                  |  |  |

**TABLE 3.** Performance Comparison

#### 6 Conclusion

In this work two types of pulse width modulation techniques which are PD-PWM and APOD-PWM were employed and compared for driving 5LANPC. The comparison has been performed from the quality of the output voltage, output current, and the capacitor voltages balance points of view. Moreover, a simplified algorithm is built to keep the capacitor voltages in balance by selecting the appropriate switching state according to the capacitor voltages and the required voltage level. Verification and comparison were carried out by simulation using MATLAB/Simulink software package. Through simulation it can be concluded that the installation of the 5LANPC, which is characterized by a small number of switches and capacitors, leads to a significant simplification of the control system. In confirmation of this, the simulation results showed a high performance of the system using the above two modulation methods, with a better result in favor of the PD-PWM method.

#### References

- S. S. Fazel, S. Bernet, D. Krug, and K. Jalili, "Design and comparison of 4-kV neutral-point-clamped, flying-capacitor, and series-connected H-bridge multilevel converters," IEEE Transactions on Industry Applications, vol. 43, no. 4, pp. 1032-1040, 2007.

- E. Burguete, López, J., Zabaleta, M., "New five-level active neutral point clamped converter," presented at the 2013 IEEE Energy Conversion Congress and Exposition, Denver, CO, USA, 2013.

- 3. S. Z. Xu, C. J. Wang, F. L. Lin, and S. X. Li, "Fault-Tolerant Control of ANPC Three-Level Inverter Based on Order-Reduction Optimal Control Strategy under Multi-Device Open-Circuit Fault," Sci Rep, vol. 7, no. 1, p. 14447, Oct 31 2017, doi: 10.1038/s41598-017-15000-9.

- S. S. Shyaa, Hassan, R.F., "Design and Software Implementation of Multilevel Diode Clamped Converter," presented at the 3rd International Conference on Sustainable Engineering Techniques (ICSET 2020) 2020.

- N. D. Dao, Lee, D.-C., "Operation and Control Scheme of a Five-Level Hybrid Inverter for Medium-Voltage Motor Drives," IEEE Transactions on Power Electronics, vol. 33, no. 12, pp. 10178 - 10187, 2018, doi: 10.1109/TPEL.2018.2811182.

- M. Q. Kasim, Hassan, R.F., "Active voltage balancing strategy of asymmetric stacked multilevel inverter," Indonesian Journal of Electrical Engineering and Computer Science, vol. 23, no. 2, pp. 665–674, 2021, doi: 10.11591/ijeecs.v23.i2.

- F. Kieferndorf, M. Basler, L. Serpa, J.-H. Fabian, A. Coccia, and G. Scheuer, "A new medium voltage drive system based on ANPC-5L technology," in 2010 IEEE International Conference on Industrial Technology, 2010: IEEE, pp. 643-649.

- 8. K. Wang, Zheng, Z., Fan, B., Xu, L., Li, Y., "A Modified PSPWM for a Five-Level Hybrid-Clamped Inverter to Reduce Flying Capacitor Size," IEEE Transactions on Industry Applications vol. 55, no. 2, pp. 1658 1666, 2019, doi: 10.1109/TIA.2018.2878833.

- 9. M. Q. Kasim, Hassan, R.F., Humaidi, A.J., Abdulkareem, A.I., Nasser, A.R., Alkhayyat, A., "Control Algorithm of Five-Level Asymmetric Stacked Converter Based on Xilinx System Generator," presented at the 2021 IEEE 9th Conference on Systems, Process and Control (ICSPC 2021), Malacca, Malaysia, 2021.

- 10. J. Chen, C. Wang, and J. Li, "Single-phase step-up five-level inverter with phase-shifted pulse width modulation," Journal of Power Electronics, vol. 19, no. 1, pp. 134-145, 2019.

- A. Dekka and M. Narimani, "Capacitor voltage balancing and current control of a five-level nested neutralpoint-clamped converter," IEEE Transactions on Power Electronics, vol. 33, no. 12, pp. 10169-10177, 2018.

- R. F. Hassan and N. M. Yasin, "Model predictive control based stacked asymmetric multilevel inverter driver," International Journal of Engineering & Technology, vol. 7, no. 4, pp. 3924-3929, 2018.

- M. Q. Kasim, Hassan, R.F., "Reduced Computational Burden Model Predictive Current Control of Asymmetric Stacked Multi-Level Inverter Based STATCOM," presented at the 2021IEEE International Conference on Automatic Control and Intelligent Systems, (I2CACIS), Shah Alam, Malaysia, 2021.

- 14. Y. Wang, A. Aksoz, T. Geury, S. B. Ozturk, O. C. Kivanc, and O. Hegazy, "A review of modular multilevel converters for stationary applications," Applied Sciences, vol. 10, no. 21, p. 7719, 2020.

- J. I. Leon, S. Vazquez, and L. G. Franquelo, "Multilevel converters: Control and modulation techniques for their operation and industrial applications," Proceedings of the IEEE, vol. 105, no. 11, pp. 2066-2081, 2017.

- 16. J. Rodriguez, S. Bernet, P. K. Steimer, and I. E. Lizama, "A survey on neutral-point-clamped inverters," IEEE transactions on Industrial Electronics, vol. 57, no. 7, pp. 2219-2230, 2009.

- 17. S. Kouro, J. Rodriguez, B. Wu, S. Bernet, and M. Perez, "Powering the future of industry: High-power adjustable speed drive topologies," IEEE industry applications magazine, vol. 18, no. 4, pp. 26-39, 2012.

- M. R. J. Oskuee, M. Karimi, Y. Naderi, S. N. Ravadanegh, and S. H. Hosseini, "A new multilevel voltage source inverter configuration with minimum number of circuit elements," Journal of Central South University, vol. 24, no. 4, pp. 912-920, 2017.

- G. Ceglia, V. Guzman, C. Sanchez, F. Ibanez, J. Walter, and M. I. Giménez, "A new simplified multilevel inverter topology for DC-AC conversion," IEEE transactions on power electronics, vol. 21, no. 5, pp. 1311-1319, 2006.

- J. Selvaraj and N. A. Rahim, "Multilevel inverter for grid-connected PV system employing digital PI controller," IEEE transactions on industrial electronics, vol. 56, no. 1, pp. 149-158, 2008.

- N. A. Rahim and J. Selvaraj, "Multistring five-level inverter with novel PWM control scheme for PV application," IEEE transactions on industrial electronics, vol. 57, no. 6, pp. 2111-2123, 2009.

- P. Barbosa, P. Steimer, J. Steinke, M. Winkelnkemper, and N. Celanovic, "Active-neutral-point-clamped (ANPC) multilevel converter technology," in 2005 European Conference on Power Electronics and Applications, 2005: IEEE, pp. 10 pp.-P. 10.

- L. Serpa, P. Barbosa, P. K. Steimer, and J. W. Kolar, "Five-level virtual-flux direct power control for the active neutral-point clamped multilevel inverter," in 2008 IEEE Power Electronics Specialists Conference, 2008: IEEE, pp. 1668-1674.

- K. Wang, Y. Li, and Z. Zheng, "A neutral-point potential balancing algorithm for five-level ANPC converters," in 2011 International Conference on Electrical Machines and Systems, 2011: IEEE, pp. 1-5.

- Z. Liu, Z. Xia, D. Li, Y. Wang, and F. Li, "An optimal model predictive control method for five-level active NPC inverter," IEEE Access, vol. 8, pp. 221414-221423, 2020.

- D. A. Vahid, Khoshkbar, Sadigh; Keith, A., Corzine, "A New Control Technique for Improved Active-Neutral-Point-Clamped (I-ANPC) Multilevel Converters Using Logic-Equations Approach," IEEE Transactions on Industry Applications, vol. 56, no. 1, pp. 488 - 497, 2020, doi: 10.1109/TIA.2019.2952316.

- D. K. Vahid, A., Corzine; Johan, H., Enslin; Arash, Khoshkbar, Sadigh; Jose, Rodriguez; Frede, Blaabjerg, "Logic-Equations-Based Modulation Technique for Natural Balance Control of an Improved Active-Neutral-Point-Clamped (I-ANPC) Multilevel Converter," presented at the 2018 IEEE Energy Conversion Congress and Exposition (ECCE), 2018.

- H. Richardt, Wilkinson; Thierry, A., Meynard; Hendrik, du Toit, Mouton, "Natural Balance of Multicell Converters: The General Case," IEEE Transactions on Power Electronics, vol. 21, no. 6, pp. 1658 - 1666, 2006, doi: 10.1109/TPEL.2006.882951.

- P. Brendan, McGrath; Thierry, Meynard; Guillaume, Gateau; Donald, Grahame, Holmes, "Optimal Modulation of Flying Capacitor and Stacked Multicell Converters Using a State Machine Decoder," IEEE Transactions on Power Electronics, vol. 22, no. 2, pp. 508 - 516, 2007, doi: 10.1109/TPEL.2006.889932.

- L. M. Ricardo, A., Perez; Steffen, Bernet; Jose, R., Espinoza; Jose, Rodriguez, "Control of Arm Capacitor Voltages in Modular Multilevel Converters," IEEE Transactions on Power Electronics, vol. 31, no. 2, pp. 1774 - 1784, 2016, doi: 10.1109/TPEL.2015.2426183.

- L. J. Junjie, Jiang; Shutong, Qiao, "A Space Vector Pulse Width Modulation for Five-Level Nested Neutral Point Piloted Converter," IEEE Transactions on Power Electronics, vol. 32, no. 8, pp. 5991 - 6004, 2016, doi: 10.1109/TPEL.2016.2618931.

- 32. C. M. Sanghun, Saeedifard, "Capacitor Voltage Balancing of Flying Capacitor Multilevel Converters by Space Vector PWM," IEEE Transactions on Power Delivery, vol. 27, no. 3, 2012, doi: 10.1109/TPWRD.2012.2191802.

- 33. İ. Mustafa, "Performance Evaluation of Multi-carrier PWM Techniques: PD, POD and APOD," International Journal of Applied Mathematics, Electronics and Computers, vol. 7, no. 2, pp. 38 43, 2019. Software as Services, pp. 31-56, Springer Berlin Heidelberg, 2011.