## TOWARDS A UNIVERSAL HOT CARRIER DEGRADATION MODEL FOR SIGE HBTS SUBJECTED TO ELECTRICAL STRESS

A Dissertation Presented to The Academic Faculty

by

Uppili S. Raghunathan

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

> Georgia Institute of Technology August 2019

## **COPYRIGHT © 2019 BY UPPILI S. RAGHUNATHAN**

### TOWARDS A UNIVERSAL HOT CARRIER DEGRADATION MODEL FOR SIGE HBTS SUBJECTED TO ELECTRICAL STRESS

Approved by:

Professor John D. Cressler, Advisor School of Electrical and Computer Engineering *Georgia Institute of Technology*

Professor Shyh-Chiang Shen School of Electrical and Computer Engineering *Georgia Institute of Technology*

Professor Asif Islam Khan School of Electrical and Computer Engineering *Georgia Institute of Technology*  Professor Dragomir Davidovic School of Physics Georgia Institute of Technology

Adjunct Professor Nelson E. Lourenco School of Electrical and Computer Engineering *Georgia Institute of Technology*

Date Approved: April 22, 2019

To my grandfather Venkatachalapathy, my uncle Ananth, and parents Anasuya and Raghunathan, who were huge pillars of inspiration for my inclination towards science and engineering. I humbly attempted to follow the examples you all set.

#### ACKNOWLEDGEMENTS

I would like to sincerely thank my advisor Prof. John Cressler for giving me a place in his resourceful team from the start and mentoring me like a kid through both productive and difficult stretches, for almost eight years. His constant guidance, encouragement, and patience enabled me to become an effective researcher despite the limited knowledge and skills I initially possessed. I am really fortunate to have gotten a guide who not only paved my career, but also always accommodated me whenever I've had significant life events. He preached the importance of being resourceful, made me appreciate the broader aspects in life and always emphasized the importance of work-life balance. He has been a role model for me in finding deeper purpose to the work I did, am doing, and will do every day.

I also would like to thank Dr. Shyh-Chiang Shen and Dr. Asif Khan for taking the time to serve on my Ph.D. proposal committee and providing constructive feedback and suggestions for my research. I am also grateful to Dr. Dragomir Davidovich and Dr. Nelson Lourenco for serving on my defense committee and providing the additional technical dialogue and refinement in my research.

My research would not have materialized without significant help, ideas and input from the current and past members of the SiGe team during my years at Georgia Tech. I am deeply grateful to Partha and Kurt for grooming my researching abilities and having given me a wealth of tools and ideas that I greatly benefited from during my initial stages of graduate school. I am fortunate to have had the constant support of Brian Wier, who has been a true comrade in all my research accomplishments in this work, whether it includes lab measurements, simulations, device physics discussions, or writing. I also wish to express my sincere thanks to Tikurete Gebremariam, Hanbin Victor Ying, Rafael Perez Martinez, and Sebastian Martin Fernandez for their timely help with performing difficult measurements. Additionally, I would like to thank Anup Omprakash, Zachary Fleetwood, Nelson Lourenco, Patrick Goley, Ickhyun Song, Saeed Zeinolabedinzadeh, Seungwoo Jung, Peter Song, Adrian Ildefonso, and Harrison Lee for their support, guidance, and collaborations.

I have been privileged to get access to the technology and hardware from Texas Instruments (TI), and GlobalFoundries (GF) that enabled my research. I wish to sincerely thank Hiroshi Yasuda, Jonggook Kim and Philip Meinz at TI, and Vibhor Jain and Alvin Joseph from GF for giving me challenging problems that showed me directions in research. Their guidance through the numerous teleconferences were invaluable for my progress.

I am indebted to the families of Raghavan Rajaji, Dr. Bharath Srivatsa, Sampathkumar Ramalingam, Narayanan Shiyamalann, Damodaran Venkatesan, Vijay Srinivasan, my flute master GS Rajan, and several others, who came for assistance during desperate times of need, and provided love and support. Similarly, my experience in graduate school would not have been complete without the association of Srikrishna Sitaraman, Swarrnnakarthik Parthasarathy, Gokul Kumar, Vijay Sukumaran, Srikanth Dwarakanath, Shreyas Srinivas, Karthik Raghavan, Chandrasekharan Nair, and Kaushiik Baskaran.

I would definitely not be where I am today without the limitless support and constant encouragement from my parents and my extended family in India (grandparents, aunts, uncles, and cousins). Their unconditional belief in my strengths and abilities from

V

childhood empowered me to accomplish a lot in life. Most of all, I cannot find words to express my gratitude to my loving wife Malavika, who has cared for and sustained me through difficult stretches. I have learned many things from her, and have become a more joyful and complete person in her company.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTSiv                                                        |

|---------------------------------------------------------------------------|

| LIST OF TABLES xi                                                         |

| LIST OF FIGURES xii                                                       |

| LIST OF SYMBOLS AND ABBREVIATIONS xx                                      |

| SUMMARY xxii                                                              |

| CHAPTER 1 Introduction1                                                   |

| 1.1 Motivation and Background for Using SiGe HBTs1                        |

| 1.2 Reliability Challenges of SiGe HBT Scaling                            |

| 1.3 Thesis Outline                                                        |

| CHAPTER 2 Silicon-Germanium BICMOS Technology and Reliability             |

| 2.1 Brief History of Silicon-Germanium Technology                         |

| 2.2 Overview of Competing Degradation Effects in SiGe HBTs7               |

| 2.2.1 Avalanche-Generated Hot Carriers                                    |

| 2.2.2 Auger-Generated Hot Carriers                                        |

| 2.2.3 Trap Annealing                                                      |

| 2.3 Extent of SiGe HBT Reliability Modeling in Literature                 |

| CHAPTER 3 Accumulated Stress Modeling of Mixed-mode damage in Sige HBTs17 |

| 3.1 Motivation                                                            |

| 3.2 Damage Physics of Mixed-Mode Stress Degradation                       |

| 3.3 Impact-Ionization Calibration                                         |

| 3.4 Mixed-Mode Damage Temperature Dependence                              |

| 3.5 Damage Calibrations Over Electrical Bias and Temperature              |

| 3.6 Accumulated Stress Damage                                             |

| 3.7 Summary                                                               |

|             | Modeling of High-Current Damage in SiGe HBTs Under Pu                                  |     |

|-------------|----------------------------------------------------------------------------------------|-----|

| 4.1 Motiva  | ation                                                                                  |     |

| 4.2 Physic  | s of High-Current Damage                                                               |     |

| 4.3 High-O  | Current Pulsed Stress Measurements                                                     |     |

| 4.4 Model   | ing High-Current Auger Damage                                                          |     |

| 4.5 Summ    | ary                                                                                    |     |

|             | Physical Differences in Hot Carrier degradation of oxide int<br>ry (NPN+PNP) SiGe HBTs |     |

| 5.1 Motiva  | ation                                                                                  |     |

| 5.2 Mixed   | -Mode Damage Mechanism in NPN and PNP SiGe HBTs                                        |     |

| 5.3 Damag   | ge due to Polarity of Hot Carriers                                                     |     |

| 5.4 Interfa | ce Dependence of Damage                                                                | 57  |

| 5.5 Hot Ca  | arrier Damage Sources and Significance of Model Parameter                              | 63  |

| 5.6 Discus  | sion of Results and Calibrations                                                       | 67  |

| 5.7 Summ    | ary                                                                                    |     |

|             | Hot-Carrier-Damage-Induced Current Gain Enhancement<br>Ge HBTs                         | · / |

| 6.1 Motiva  | ation                                                                                  |     |

| 6.2 Curren  | t Gain Due to Polysilicon                                                              | 76  |

| 6.2.1       | Hot Carrier Damage of Polysilicon                                                      | 77  |

| 6.2.2       | Vulnerabilities for CGE Due to Polysilicon Dopants                                     |     |

| 6.2.3       | Simplified TCAD Simulations showing CGE                                                |     |

| 6.3 Measu   | red Response to Polysilicon Damage                                                     |     |

| 6.3.1       | Evidence for CGE in DC Stress Measurements                                             |     |

| 6.3.2       | Evidence for Polysilicon Degradation                                                   |     |

| 6.4 Summary                                                                                                                       |     |

|-----------------------------------------------------------------------------------------------------------------------------------|-----|

| CHAPTER 7 High Temperature Degradation Effects in SiGe HBTs                                                                       |     |

| 7.1 Motivation                                                                                                                    |     |

| 7.2 Background on Current Gain Enhancement                                                                                        |     |

| 7.3 TCAD Modeling of Polysilicon Degradation                                                                                      |     |

| 7.4 Capturing Electrical Response to Polysilicon Degradation                                                                      |     |

| 7.5 High Temperature Measurements                                                                                                 |     |

| 7.6 Summary                                                                                                                       | 111 |

| CHAPTER 8 Emitter-Base Profile Optimization of SiGe HBTs for Imp<br>Thermal Stability and Frequency Response at Low-Bias Currents |     |

| 8.1 Motivation and Background on Electro-Thermal Feedback                                                                         | 113 |

| 8.2 Temperature-Invariant Current Gain Physics                                                                                    | 116 |

| 8.3 Methods for Improving Large-Signal Performance                                                                                | 119 |

| 8.4 Emitter-Base Optimized Device Profiles                                                                                        | 121 |

| 8.5 Measurements and Discussion                                                                                                   | 123 |

| 8.6 Summary                                                                                                                       |     |

| CHAPTER 9 On the Reliability and Increased Variability of SiGe HBT<br>Cryogenic Temperature Operation                             |     |

| 9.1 Motivation for Cryogenic Studies in SiGe HBTs                                                                                 |     |

| 9.2 Reliability Scaling at Low Temperatures                                                                                       |     |

| 9.3 Variability Challenges for Cryogenic Applications                                                                             |     |

| 9.4 TCAD Verification of Electrical Variability                                                                                   |     |

| 9.5 Summary                                                                                                                       | 144 |

| CHAPTER 10 Conclusion                                                                                                             |     |

| 10.1 Summary of Contributions                                                                                                     |     |

| 10.2 Future Work                                                                                                                  | 147 |

| REFERENCES |  |

|------------|--|

| VITA       |  |

# LIST OF TABLES

| Table 4.1: | Comparison of equations used in the lucky electron model for generation high-field and high-current hot carriers. After [29] |    |

|------------|------------------------------------------------------------------------------------------------------------------------------|----|

| Table 5.1: | Technology specifications of the NPN and PNP devices in this work                                                            | 53 |

| Table 6.1: | Performance Metrics of Measured Devices                                                                                      | 86 |

| Table 8.1: | Profile Differences of Measured Devices                                                                                      | 23 |

| Table 8.2: | Device Performance FoMs                                                                                                      | 29 |

| Table 9.1: | List of Devices Measured                                                                                                     | 39 |

## LIST OF FIGURES

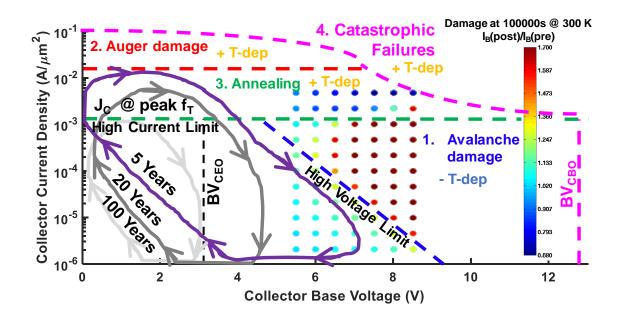

| Figure 1.1: | Simulated SOA of forward-Gummel characteristics degradation in an NPN SiGe HBT after 100,000 s of stress with various T-dependent damage regions outlined. Various dynamic load lines that change the EOL of the device due to hot carrier damage are overlaid (after [3])                                                           |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

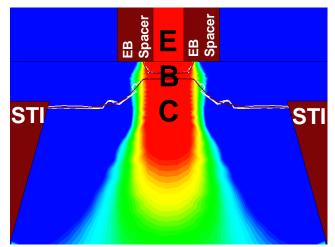

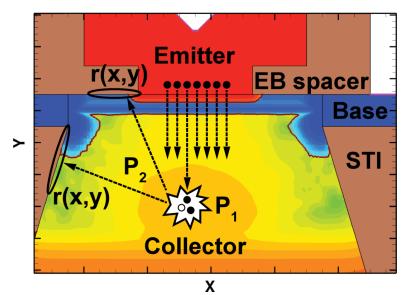

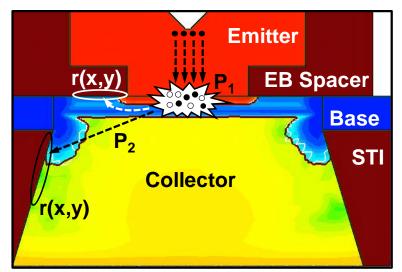

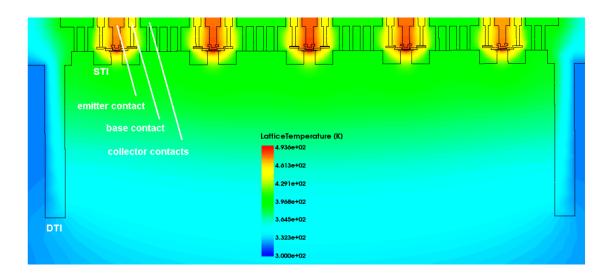

| Figure 2.1: | TCAD cross section showing current density through a fourth generation SiGe HBT under a high power condition of $J_E = 50 \text{ mA}/\mu\text{m}^2$ and $V_{CB} = 4 \text{ V}$ . Current constricts towards the center of the device under high voltage operation, eventually triggering catastrophic thermal runaway of the device. |

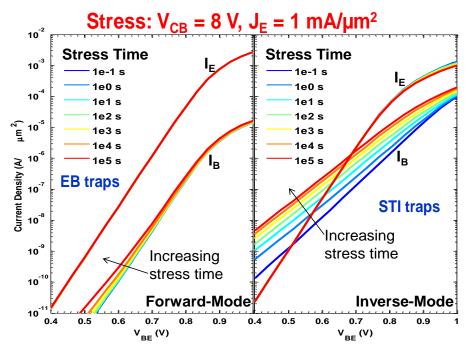

| Figure 2.2: | TCAD simulation of increasing base leakage current due to hot carrier damage following a high voltage stress. Forward and inverse mode operation of the SiGe HBT samples the base leakage due to EB and STI oxide traps (after [29])                                                                                                 |

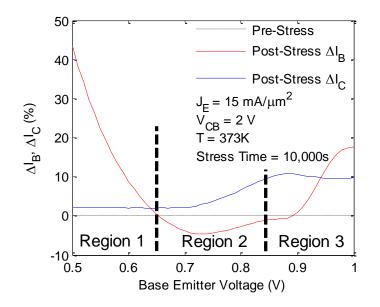

| Figure 2.3: | Measured change in the Gummel characteristics of a NPN SiGe HBT following high-current stress of $V_{CB} = 2 \text{ V}$ , $J_E = 15 \text{ mA}/\mu\text{m}^2$ (after [16]).                                                                                                                                                          |

| Figure 2.4: | Hot carrier generation and transport to oxide interfaces under mixed-mode stress (after [29])                                                                                                                                                                                                                                        |

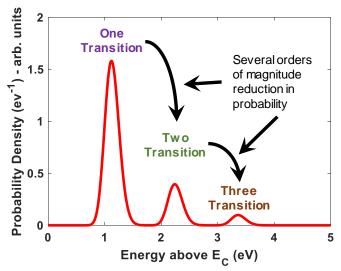

| Figure 2.5: | Probability distribution of hot electrons with multiple simultaneous Auger transition energies in silicon                                                                                                                                                                                                                            |

| Figure 2.6: | Auger hot carrier generation and transport to oxide interfaces under high-<br>current stress                                                                                                                                                                                                                                         |

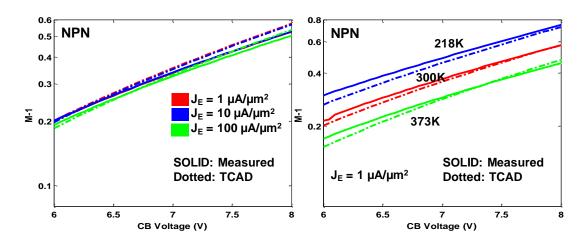

| Figure 3.1: | Calibration of avalanche multiplication across varying current levels and across temperature                                                                                                                                                                                                                                         |

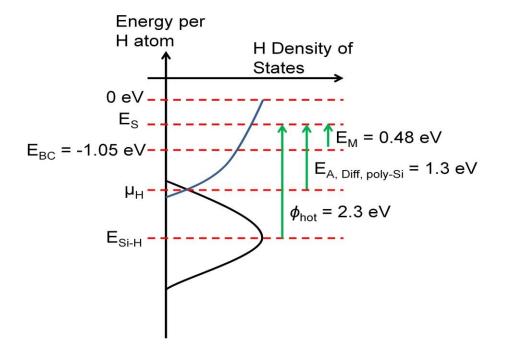

| Figure 3.2: | Distinct trap states in Silicon and the associated activation energies required for diffusion of hydrogen                                                                                                                                                                                                                            |

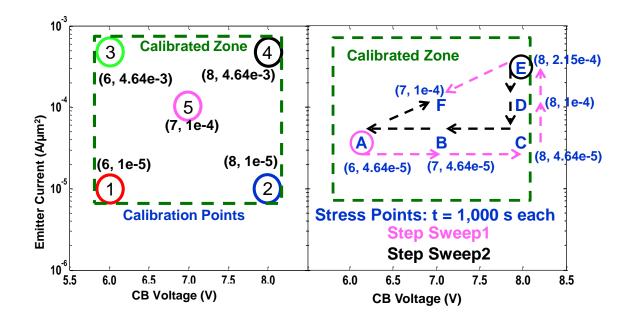

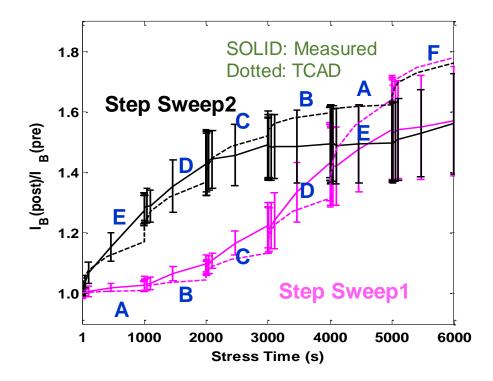

| Figure 3.3: | Five points for damage calibration marked on the left with numbers 1-5. Six points for measuring accumulated damage marked on the right with letters A-F. Two paths for accumulating stress damage are marked with pink and black arrows. 26                                                                                         |

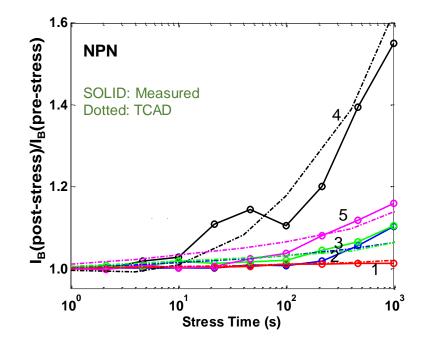

| Figure 3.4: | Degradation (I <sub>B</sub> increase) from forward-Gummel characteristics measured at $I_C = 0.1 \text{ nA}/\mu\text{m}^2$ for the 5 calibration points from Figure 3.3                                                                                                                                                              |

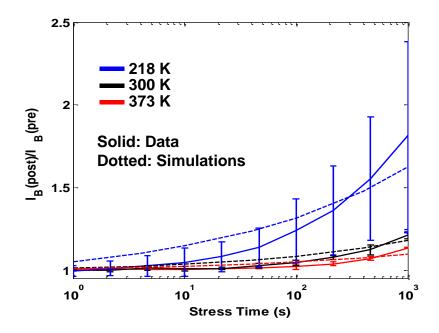

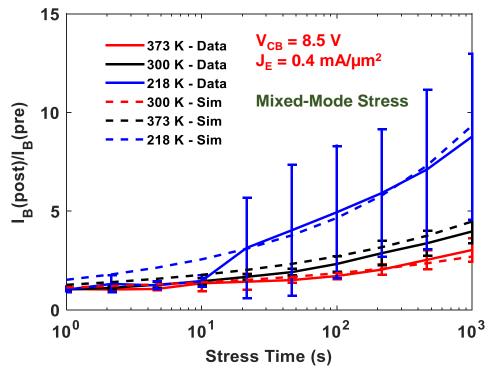

| Figure 3.5:  | Calibration of simulations to measurements for $I_B$ degradation over<br>temperature for a stress condition of $V_{CB} = 8.5$ V and $J_E = 0.464$ mA/ $\mu$ m <sup>2</sup> .<br>The base current degradation is extracted at $J_C = 10$ nA/ $\mu$ m <sup>2</sup> from forward-<br>Gummel Characteristics. Vertical error bars show the spread of data across<br>3 devices                                                                                                                                                                                       |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

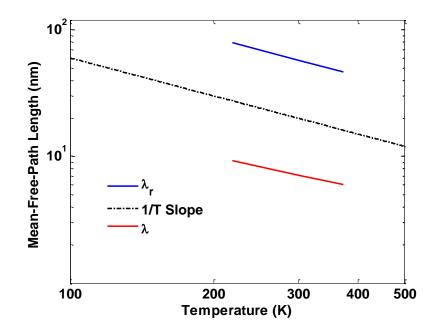

| Figure 3.6:  | Temperature dependence of $\lambda$ and $\lambda_r$ . These are the values used for the calibrations in Figure 3.5. 28                                                                                                                                                                                                                                                                                                                                                                                                                                          |

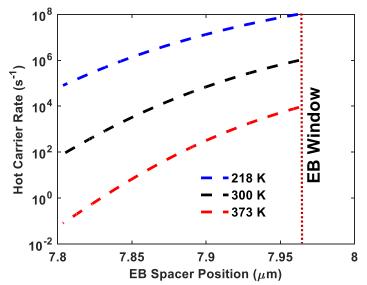

| Figure 3.7:  | Simulated Hot carrier impingement rates at EB spacer over temperature.29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

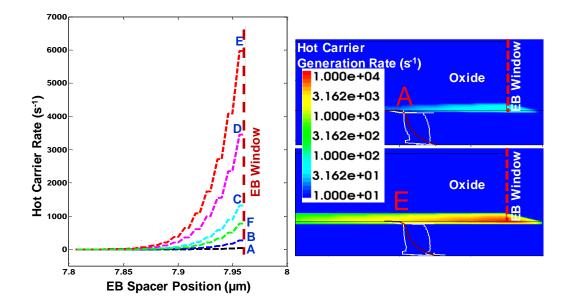

| Figure 3.8:  | Simulated Hot carrier generation rate at EB spacer after 10 s of stress on the left. 2-D cross-section of the rate for stress points A and E shown on the right                                                                                                                                                                                                                                                                                                                                                                                                 |

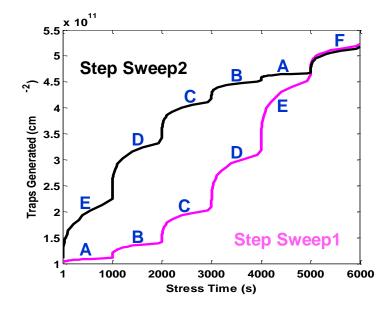

| Figure 3.9:  | Peak Trap concentration at EB spacer over the two different stress sweeps.<br>The stress condition associated with each stress period of 1000 s has been<br>identified with labeling convention from Figure 3.3                                                                                                                                                                                                                                                                                                                                                 |

| Figure 3.10: | Degradation from forward-Gummel characteristics at EB spacer over the two different stress sweeps for $V_{BE} = 0.5$ V. The stress condition associated with each stress period of 1000 s has been identified with labeling convention from Figure 3.3. The solid lines show the mean value of measured data and the vertical cross-lines show the spread of the data over a sample of six devices for each stress sweep                                                                                                                                        |

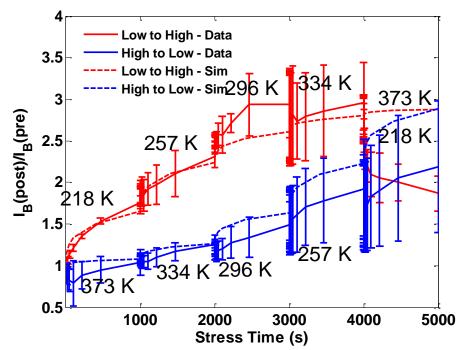

| Figure 3.11: | Degradation from forward-Gummel characteristics at EB spacer over two different temperature stress sweeps for a stress condition of $V_{CB} = 8.5$ V and $J_E = 0.464$ mA/ $\mu$ m <sup>2</sup> . The temperature associated with each stress period of 1000 s is labeled. The base current degradation is extracted at $J_C = 10$ nA/ $\mu$ m <sup>2</sup> from forward-Gummel Characteristics. The solid lines show the mean value of measured data and the vertical cross-lines show the spread of the data over a sample of 3 devices for each stress sweep |

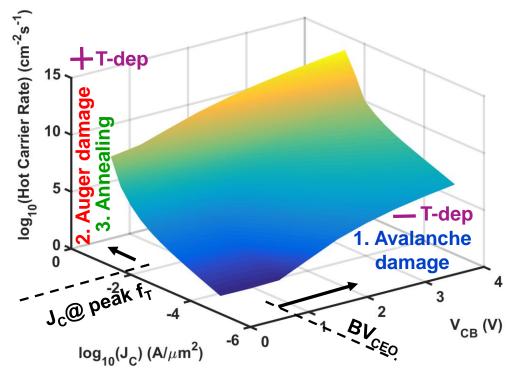

| Figure 4.1:  | Contour map of hot-carrier production due to high-fields (Impact-<br>ionization) and high-currents (Auger generation) at room temperature<br>incorporating self-heating of the device                                                                                                                                                                                                                                                                                                                                                                           |

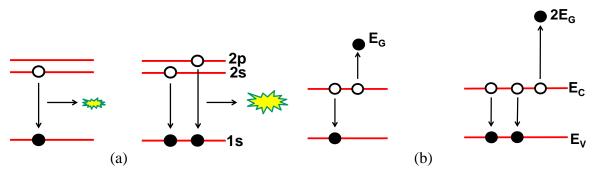

| Figure 4.2:  | (a) One and two electron transitions followed by a photon emission in an atom. (b) One and two electron transitions in bulk semiconductors resulting in energetic excitation of carriers                                                                                                                                                                                                                                                                                                                                                                        |

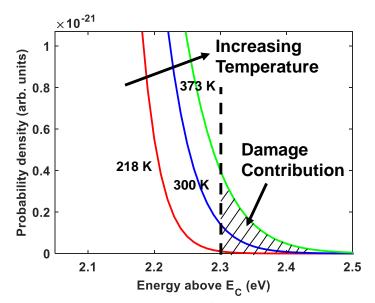

| Figure 4.3:  | Temperature dependence of the hot-carrier energy distribution assuming a phonon-assisted process for the two electron transitions. After the device has enough thermal energy from self-heating, Auger process has enough probability of producing hot carriers that can overcome the 2.3 eV energy required for breaking Si-H bonds                                                                                                                                                                                                                            |

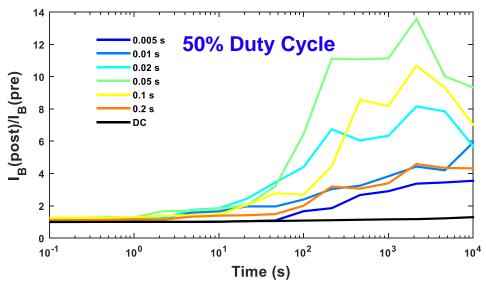

| - | Variations in pulsed stress damage for a DC equivalent stress condition of $J_E = 20 \text{ mA}/\mu m^2$ and $V_{CB} = 1.5 \text{ V}$ . I <sub>B</sub> degradation was extracted from forward-Gummel characteristics at $J_C = 1 \mu A/\mu m^2$ . Damage from pulse width variation compared to DC stress for a fixed 50% duty cycle                                 |

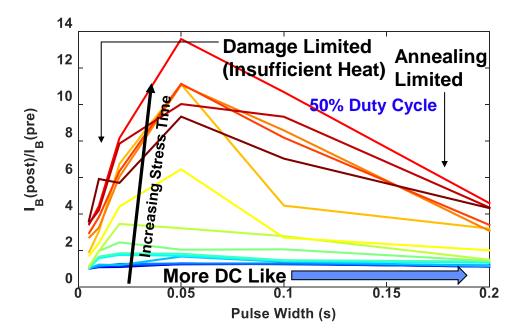

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| - | Stress damage evolution plotted against pulse width for a fixed 50% duty cycle for the conditions in Figure 4.4. The transition from dark blue to dark brown indicates increasing time from 0.1 s to 10000 s                                                                                                                                                         |

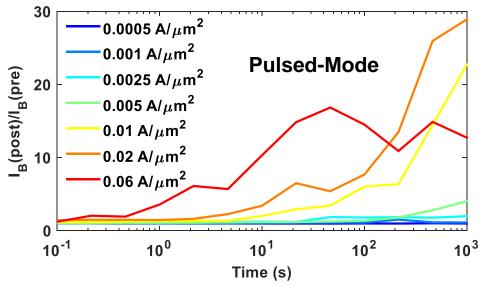

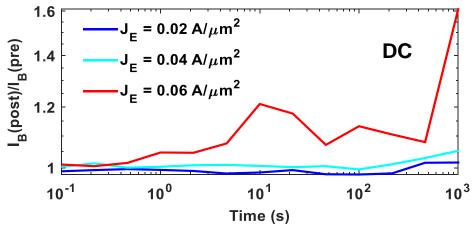

|   | High-current stress degradation under pulsed-mode for $V_{CB} = 0$ V. $I_B$ degradation extracted from forward-Gummel characteristics at $J_C = 0.1 \mu A/\mu m^2$ . Pulsed-mode stress degradation with 50 ms width and 50% duty cycle                                                                                                                              |

|   | High-current stress degradation under DC for $V_{CB} = 0$ V. I <sub>B</sub> degradation extracted from forward-Gummel characteristics at $J_C = 0.1 \ \mu A/\mu m^2$ 45                                                                                                                                                                                              |

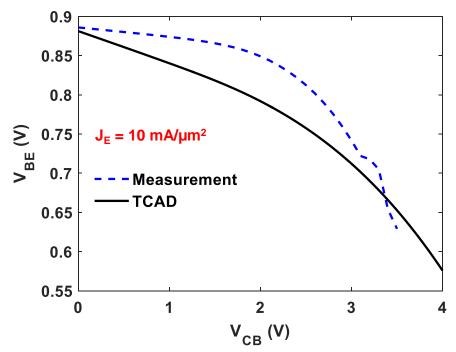

| - | Comparison of the calibration of $V_{BE}$ roll-off in TCAD and measurements to account for self-heating                                                                                                                                                                                                                                                              |

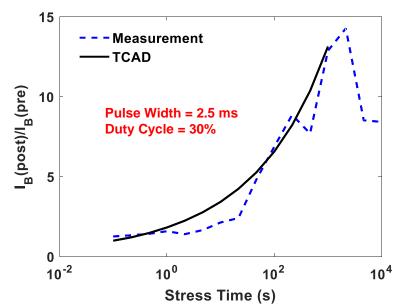

| - | Calibration of TCAD to a measured pulsed condition with a pulse width of 2.5 ms and a duty cycle of 30%. I <sub>B</sub> degradation was extracted from forward-Gummel characteristics at $J_C = 1 \ \mu A/\mu m^2$                                                                                                                                                   |

| U | Calibrated forward-Gummel characteristics of the PNP and NPN devices in this work. All devices used have $A_E = 0.3 \ \mu m \ x \ 6.4 \ \mu m \ x \ 253$                                                                                                                                                                                                             |

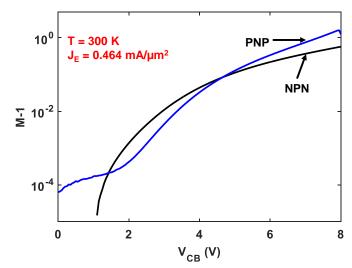

| - | Relative level of impact ionization seen in the PNP and NPN SiGe HBTs for $JE = 464 \mu A/\mu m2$ at 300 K. Level of bias determines which device sees more impact ionization. 55                                                                                                                                                                                    |

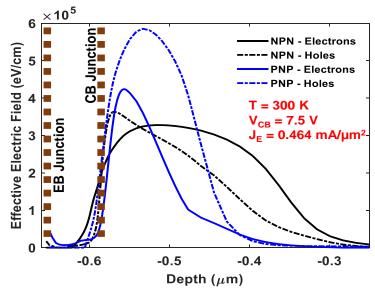

|   | Relative effective field strength in NPN and PNP SiGe HBTs at the CB junction for $J_E = 464 \ \mu A/\mu m^2$ and $V_{CB} = 7.5 \ V$ at 300 K. The peak field is larger in the PNP                                                                                                                                                                                   |

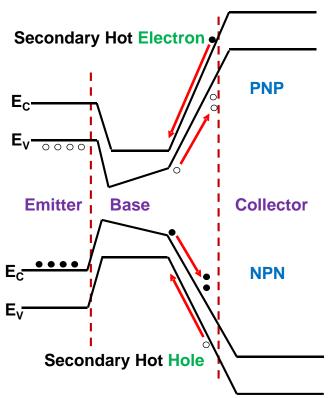

| • | Respective secondary hot carriers responsible for damage at the EB interface for an NPN and PNP SiGe HBT under mixed-mode stress 56                                                                                                                                                                                                                                  |

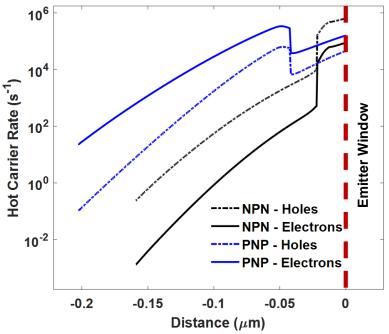

| - | Hot carrier impingement along the EB oxide interface in NPN and PNP SiGe HBTs for a stress condition of $V_{CB} = 8.5$ V and $J_E = 400 \ \mu A/\mu m^2$ at 300 K                                                                                                                                                                                                    |

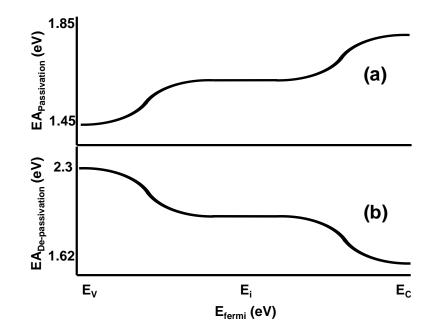

|   | Qualitative functions for the passivation and de-passivation activation energies required as a function of the local $E_{fermi}$ of the trap to alter the Si-H bond. The actual shape of these functions is dependent on interface orientation and quality. (a) Qualitatively derived from [66]. (b) Follows the values reported in [37] and the assumptions in [36] |

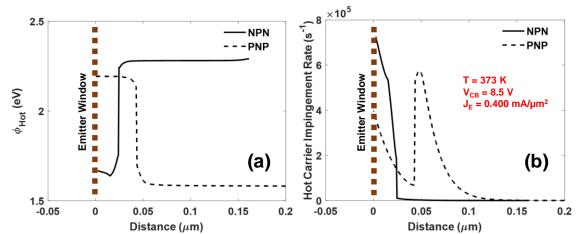

| Figure 5.7:  | Simulated (a) activation energies and (b) hot carrier rates along the EB interface for NPN and PNP devices for a stress condition of $V_{CB} = 8.5$ V and $J_E = 0.400$ mA/ $\mu$ m <sup>2</sup> at 373 K. The sharp transitions of activation energies and hot carrier rates along the interface indicate the carrier population inversion                                                               |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

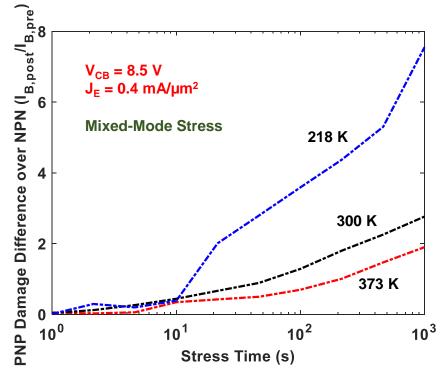

| Figure 5.8:  | Difference in measured mixed-mode damage between NPN and PNP across temperature for a stress condition of $V_{CB} = 8.5$ V and $J_E = 0.400$ mA/ $\mu$ m <sup>2</sup> . Each temperature curve is averaged over 4 devices of NPN and 4 devices of PNP                                                                                                                                                     |

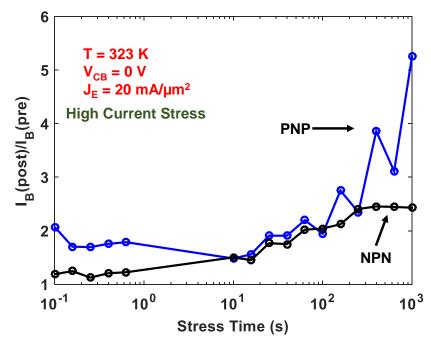

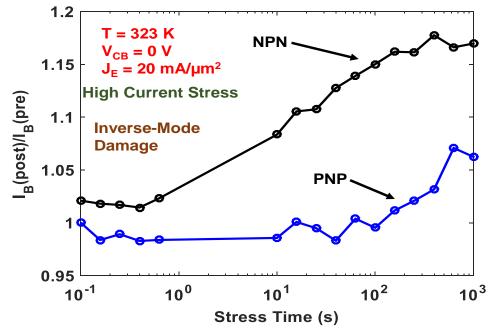

| Figure 5.9:  | Damage due to high-current stress at 323 K for $V_{CB}=0$ V and $J_E=20$ mA/ $\mu m^265$                                                                                                                                                                                                                                                                                                                  |

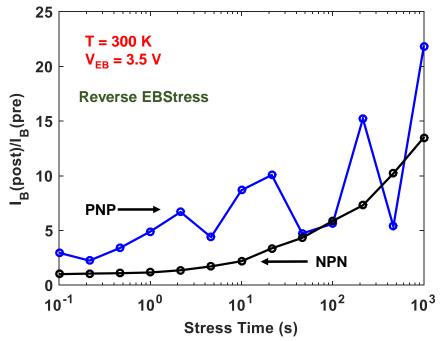

| Figure 5.10: | Damage due to reverse EB stress condition of 3.5V at 300 K. All damages were extracted from forward-Gummel characteristics at $J_C = 10 \text{ nA}/\mu m^2.65$                                                                                                                                                                                                                                            |

| Figure 5.11: | Inverse-mode (STI) degradation due to forward-mode high-current stress at 323 K for $J_E = 20 \text{ mA}/\mu\text{m}^2$ . Extracted at $J_C = 10 \text{ nA}/\mu\text{m}^2$                                                                                                                                                                                                                                |

| Figure 5.12: | Mixed-mode degradation of a PNP device. Calibration of TCAD to measurements for $I_B$ degradation over temperature for a mixed-mode stress condition of $V_{CB} = 8.5$ V and $J_E = 0.400$ mA/ $\mu$ m <sup>2</sup> . The base current degradation is extracted at $J_C = 10$ nA/ $\mu$ m <sup>2</sup> from forward-Gummel characteristics. Vertical error bars show the spread of data across 4 devices. |

| Figure 6.1:  | Measured degradation of Gummel characteristics and $\beta$ in a NPN SiGe HBT following a high-current stress of V <sub>CB</sub> = 0 V, J <sub>E</sub> = 21.5 mA/µm <sup>2</sup> 74                                                                                                                                                                                                                        |

| Figure 6.2:  | Current components contributing to and limiting current gain76                                                                                                                                                                                                                                                                                                                                            |

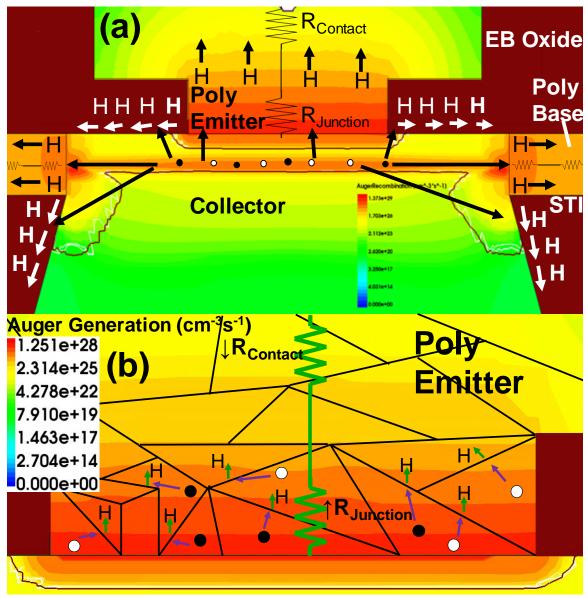

| Figure 6.3:  | (a) High-current stress induced Auger hot carrier damage to oxide interfaces<br>and polysilicon, and hydrogen movement. (b) Grain boundary damage of<br>polysilicon emitter. Overall polysilicon resistance a function of local<br>hydrogen distribution                                                                                                                                                  |

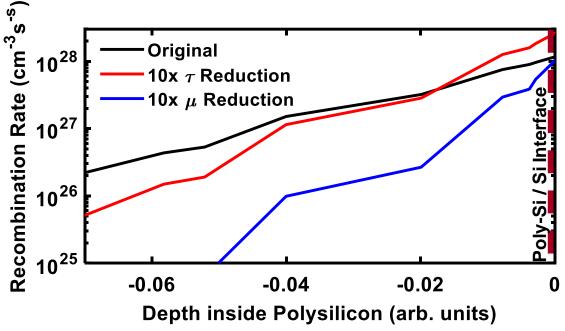

| Figure 6.4:  | TCAD simulation of the total recombination rate (Auger + SRH) when $\mu$ and $\tau$ are independently degraded by 10x                                                                                                                                                                                                                                                                                     |

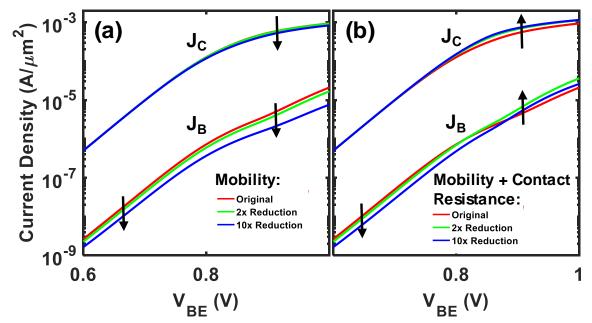

| Figure 6.5:  | TCAD simulation of forward-Gummel characteristics for a 1 <sup>st</sup> generation SiGe HBT. (a) With $\mu$ reduction (b) With $\mu$ and contact resistance reduction. Original series resistance of 100 $\Omega$ at the emitter and 500 $\Omega$ at the base                                                                                                                                             |

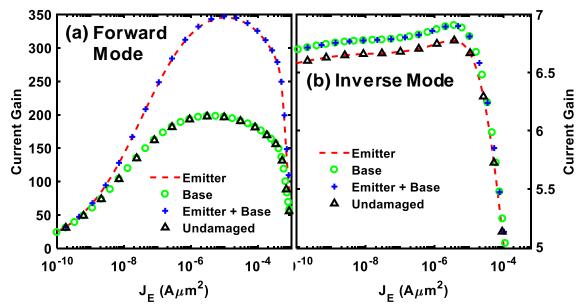

| Figure 6.6:  | TCAD simulation of current gain while independently reducing the mobilities in the emitter and base poly by 10x to qualitatively see damage dependence under (a) forward and (b) inverse modes of operation                                                                                                                                                                                               |

XV

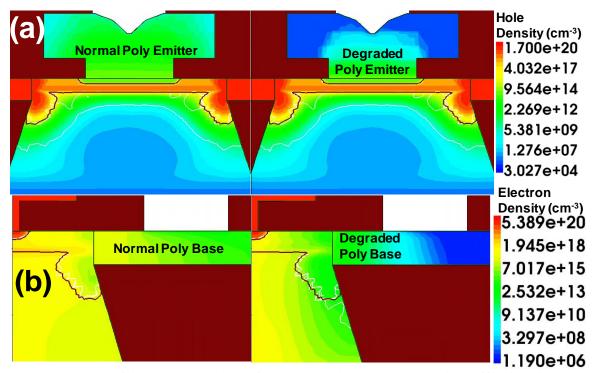

| Figure 6.7:  | TCAD cross-section of 10x polysilicon $\mu$ degradation affecting (a) hole injection from the base into the emitter and (b) electron injection from the emitter into the base. 85                                                                                                                                                                                                   |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

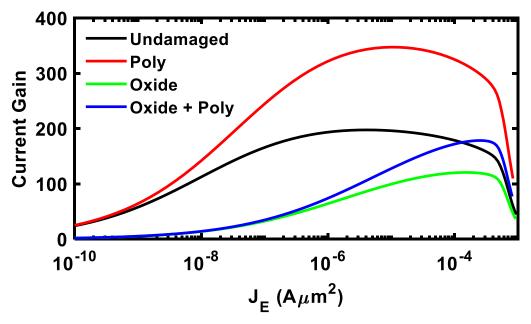

| Figure 6.8:  | TCAD simulation of current gain under forward mode while independently considering the polysilicon and oxide interface damage mechanisms 85                                                                                                                                                                                                                                         |

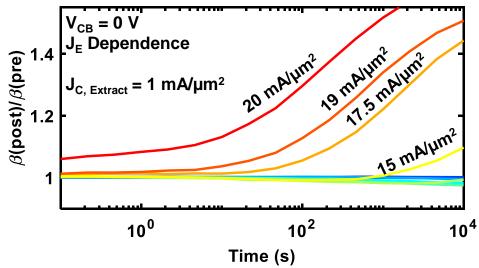

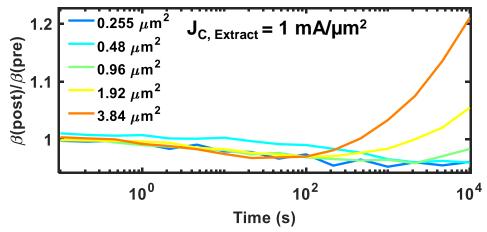

| Figure 6.9:  | Measured forward mode CGE in NPN1 with $A_E = 15.36 \ \mu m^2$ following high-current stress at T = 300 K with $V_{CB} = 0$ V. Colors from blue to red indicate increasing stress current density. $\beta$ extracted from Gummel characteristics at $J_C = 1 \ mA/\mu m^2$                                                                                                          |

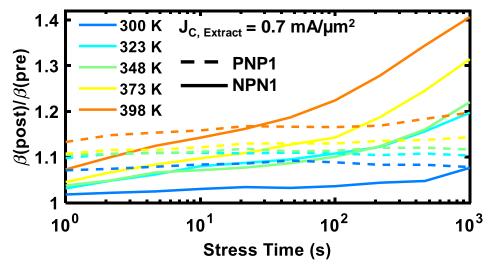

| Figure 6.10: | Measured forward mode CGE in NPN1 and PNP1 with $A_E = 3.84 \ \mu m^2$ following high-current stress of $V_{CB} = 0$ V and $J_E = 21.5 \ mA/\mu m2$ . $\beta$ extracted from Gummel characteristics at $J_C = 7e-4$ A/ $\mu m^2$ . NPN is given by solid lines and PNP by dotted ones                                                                                               |

| Figure 6.11: | Measured current gain degradation and enhancement for a high-current stress condition of $J_E = 21.4 \text{ mA}/\mu\text{m}^2$ and $V_{CB} = 0 \text{ V}$ across various emitter areas at T = 300 K. $\beta$ extracted at $J_C = 1 \text{ mA}/\mu\text{m}^2$                                                                                                                        |

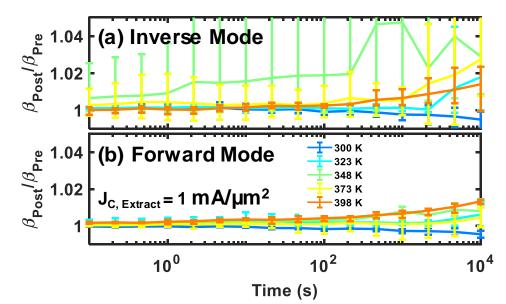

| Figure 6.12: | Measured current gain degradation and enhancement for a mixed-mode condition of $J_E = 21.5 \text{ mA}/\mu\text{m}^2$ and $V_{CB} = 1.5 \text{ V}$ for NPN2 across various temperatures under (a) inverse and (b) forward modes of operation. $\beta$ extracted at $J_C = 1 \text{ mA}/\mu\text{m}^2$ . 4 device samples per temperature                                            |

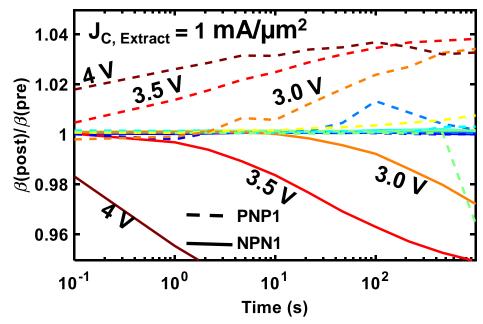

| Figure 6.13: | Measured inverse mode complementary $\beta$ degradation following reverse EB stress at T = 300K. Colors from blue to brown indicate increasing stress condition from VBE = 0 to 4 V in steps of 0.5 V. Extracted from inverse-Gummel characteristics at $J_C = 7e-4 \text{ A}/\mu m^2$ . NPN is given by solid lines and PNP by dotted ones                                         |

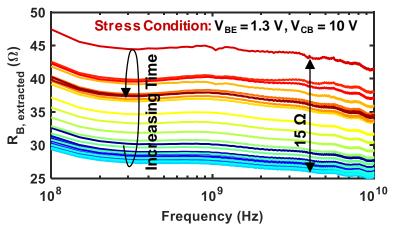

| Figure 6.14: | Evolution of the extracted RB as a function of frequency during a stress of $V_{CB} = 10$ V and $V_{BE} = 1.3$ V on NPN3 at T = 323 K. S-Parameters were measured for $V_{BE} = 1$ V. Colors from blue to red indicate increasing stress period from 0 to 100,000 s. During the stress period, the extracted RB changes by as much as 15 $\Omega$                                   |

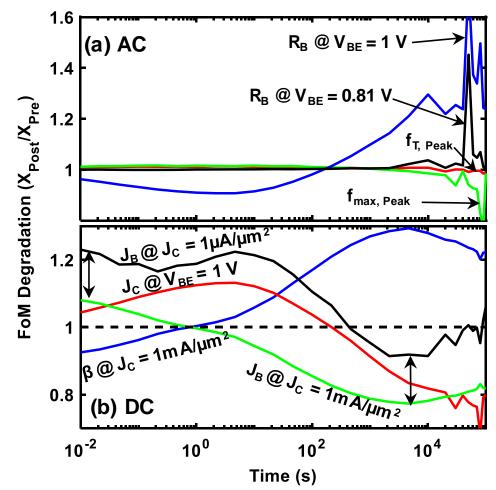

| Figure 6.15: | Correlated degradation of (a) AC and (b) DC FoMs during a stress of $V_{CB}$<br>= 10 V and $V_{BE}$ = 1.3 V on NPN3 at T = 323 K. Peak $f_T/f_{max}$ extracted from<br>S-Parameters. RB extracted from open-circle plots based on S-Parameters<br>at $V_{BE}$ = 1 V. J <sub>B</sub> , J <sub>C</sub> , and $\beta$ degradation are extracted from forward-Gummel<br>characteristics |

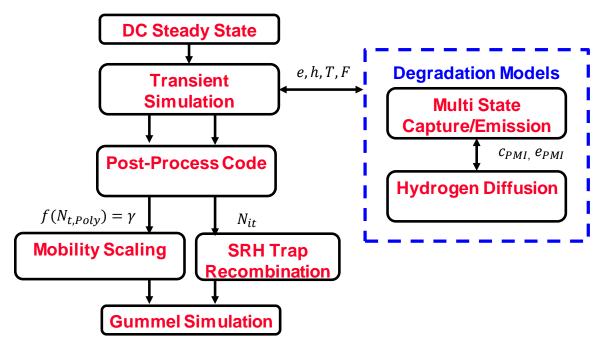

| Figure 7.1:  | Flow diagram of models for simulating polysilicon degradation in Synopsys<br>Sentaurus                                                                                                                                                                                                                                                                                              |

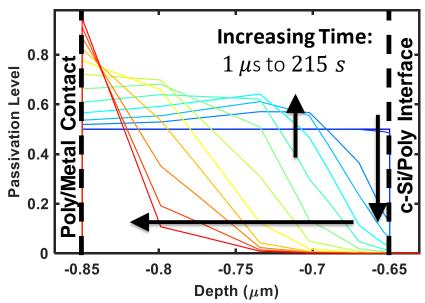

| Figure 7.2:  | Simulated change of passivation level in the polysilicon emitter in response to high-current stress of $J_E = 21.5 \ \mu A/\mu m^2$ and $V_{CB} = 0 \ V$ . Blue to red color indicate increasing stress time from 1 $\mu$ s to 215 s |

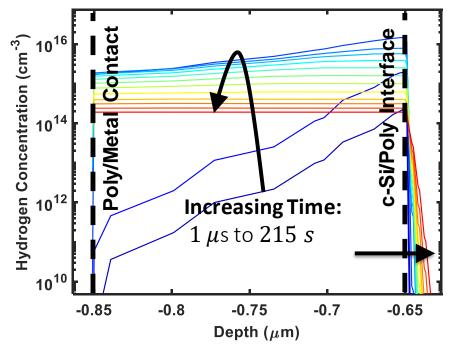

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 7.3:  | Simulated hydrogen concentration within polysilicon emitter in response to high-current stress of $J_E = 21.5 \ \mu A/\mu m^2$ and $V_{CB} = 0 \ V$ . Blue to red color indicate increasing stress time from 1 $\mu$ s to 215 s      |

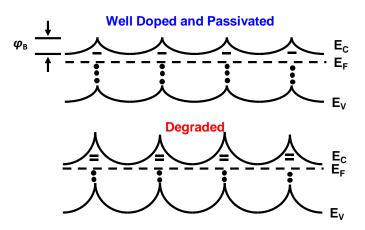

| Figure 7.4:  | Reduction of potential barriers at grain boundaries by passivation and doping                                                                                                                                                        |

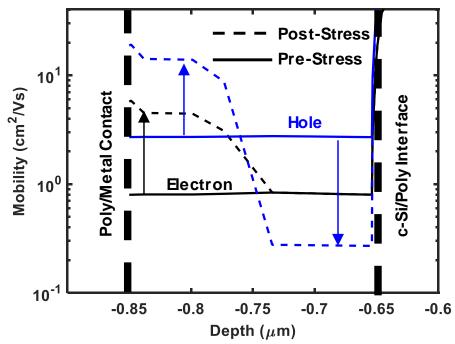

| Figure 7.5:  | Changes in electron and hole mobilities using the spatial mobility degradation model for the condition in Figure 7.2 after a stress period of 100 s                                                                                  |

| Figure 7.6:  | Simulated Gummel characteristics using the spatial mobility degradation model for the condition in Figure 7.2 after a stress period of 100 s 105                                                                                     |

| Figure 7.7:  | Parallel shifts in collector current under forward and inverse mode operation. Indicates boron neutralization                                                                                                                        |

| Figure 7.8:  | Increase in collector current at a fixed $V_{BE}$ corresponding to an initial low injection condition of $J_C = 1 \ \mu A/\mu m^2$ . Indicates parallel collector current shifts due to boron neutralization                         |

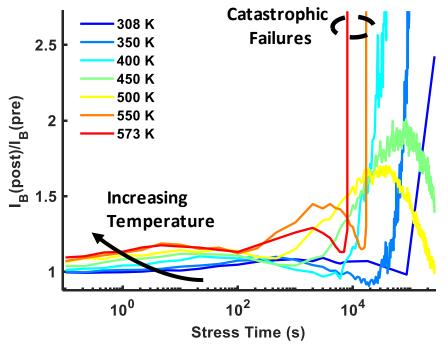

| Figure 7.9:  | Increase in base current degradation at a fixed $V_{BE}$ corresponding to an initial low injection condition of $J_C = 1 \ \mu A/\mu m^2$ . Indicates oxide interface damage. 109                                                    |

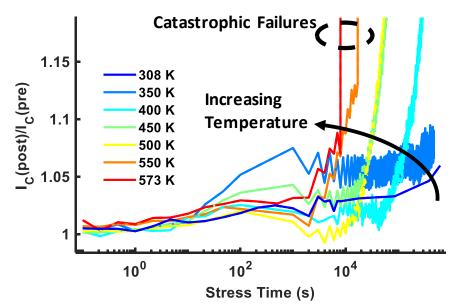

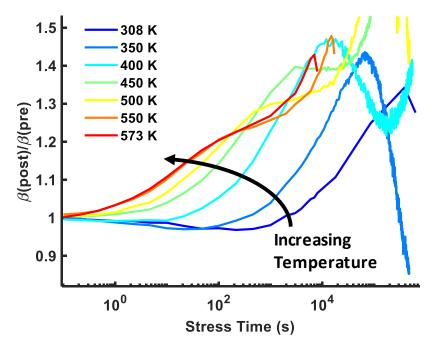

| Figure 7.10  | Increase in CGE at a fixed $V_{BE}$ corresponding to an initial high injection condition of $J_C = 1 \text{ mA}/\mu\text{m}^2$ . Indicates polysilicon minority mobility degradation                                                 |

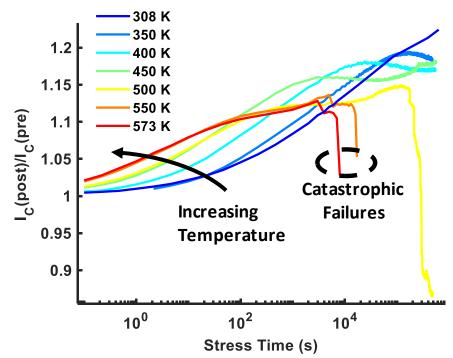

| Figure 7.11: | Collector current enhancement at a fixed $V_{BE}$ corresponding to an initial high injection condition of $J_C = 1 \text{ mA}/\mu\text{m}^2$ . Indicates changes in polysilicon resistance                                           |

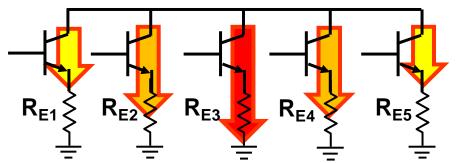

| Figure 8.1:  | Heat distribution in a multi-transistor array. (after [89])115                                                                                                                                                                       |

| Figure 8.2:  | Unequal current distribution in a multi-transistor array following the heat distribution in Figure 8.1. Length and color of arrows indicate the magnitude of the current. (after [])                                                 |

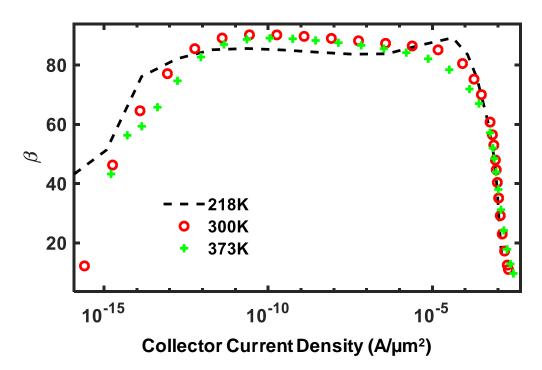

| Figure 8.3:  | TCAD simulations of the temperature dependence of $\boldsymbol{\beta}$ for different collector current densities                                                                                                                     |

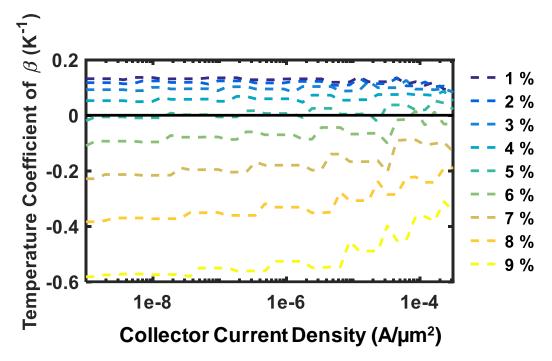

| Figure 8.4:  | TCAD-simulated temperature coefficient of $\beta$ for different collector current densities as EB Ge percentage is varied for a fixed doping profile 119                                                                             |

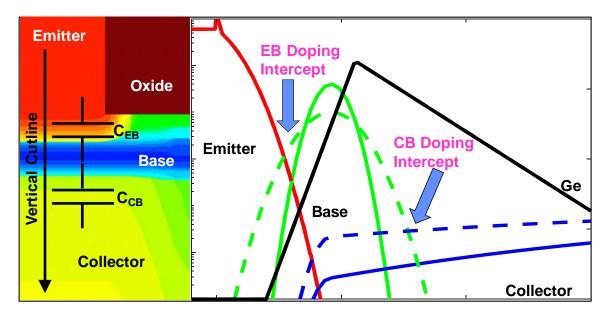

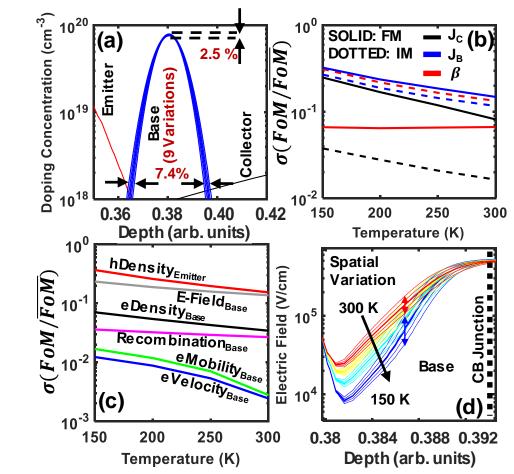

| Figure 8.5:  | (a) Reduction of EB and CB junction doping for reduced capacitance.<br>Reduction of base width and increased base doping peak for improved<br>speed                                                                                                                                                                                                                                                             |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

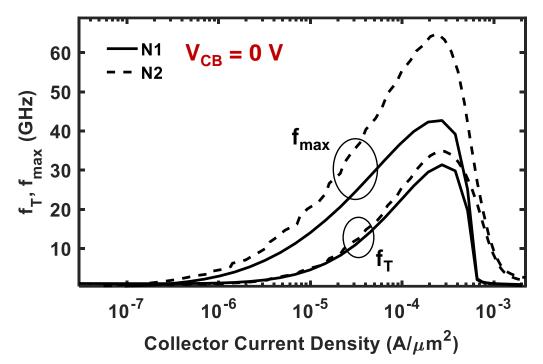

| Figure 8.6:  | Measured $f_T/f_{max}$ improvement from the control profile N1 to the optimized N2 profile with reduced EB and CB capacitance, reduced base width and increased base doping                                                                                                                                                                                                                                     |

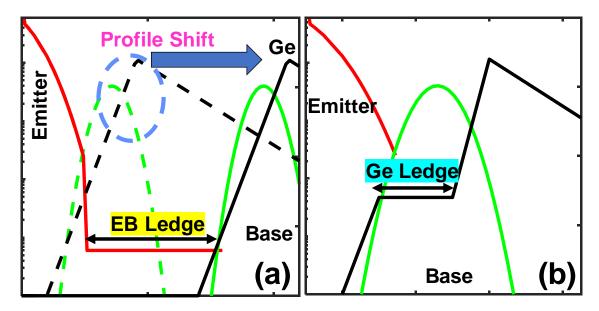

| Figure 8.7:  | (a) Constantly doped EB ledge for increased EB separation, reduced doping intercept and reduced $C_{EB}$ . (b) Ge ledge at the EB junction consisting of a constant Ge percentage                                                                                                                                                                                                                               |

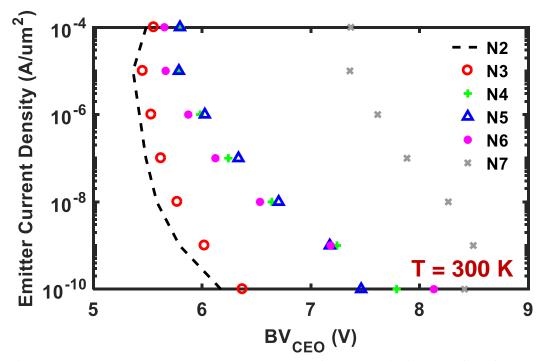

| Figure 8.8:  | Measured and extracted $BV_{CEO}$ for EB optimized profiles from the base current reversal point at different fixed emitter current density inputs 124                                                                                                                                                                                                                                                          |

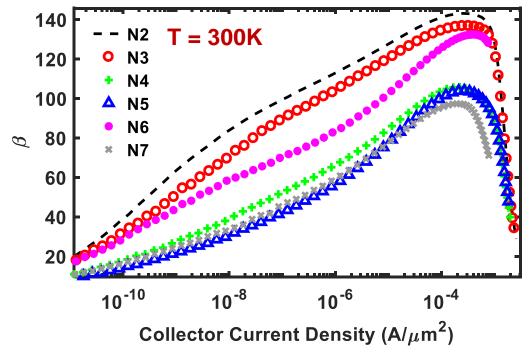

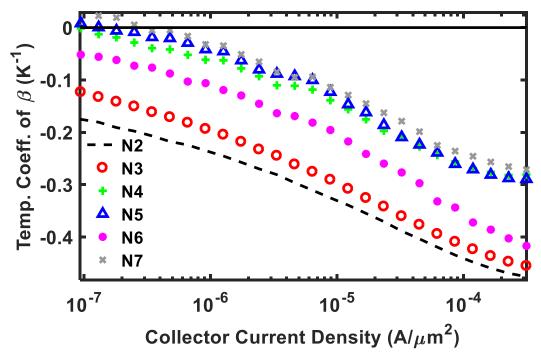

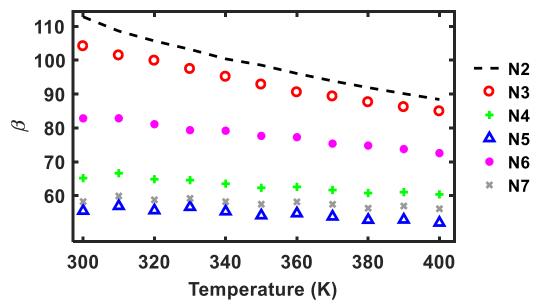

| Figure 8.9:  | Measured $\boldsymbol{\beta}$ at T = 300 K for the different profiles. $\boldsymbol{\beta}$ -optimized profiles consistently show reduced $\boldsymbol{\beta}$                                                                                                                                                                                                                                                  |

| Figure 8.10: | Measured temperature coefficient of $\beta$ ( $\Delta \beta$ w.r.t temperature) for different profiles versus J <sub>C</sub> . Extracted over 300 to 400 K                                                                                                                                                                                                                                                      |

| Figure 8.11: | Measured current gain of different profiles extracted at $J_C = 1 \ \mu A / \mu m^2$ for different temperatures                                                                                                                                                                                                                                                                                                 |

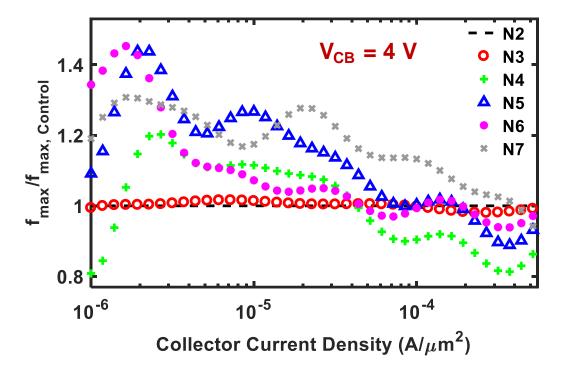

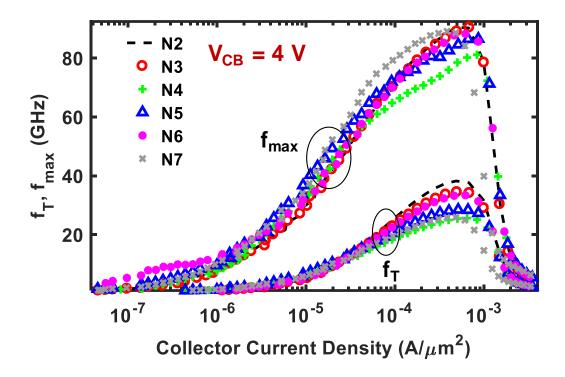

| Figure 8.12: | Measured improvement in $f_{max}$ over the control profile for $V_{CB} = 4 V128$                                                                                                                                                                                                                                                                                                                                |

| Figure 8.13: | Measured $f_T$ and $f_{max}$ curves for the different profiles for $V_{CB} = 4 V 128$                                                                                                                                                                                                                                                                                                                           |

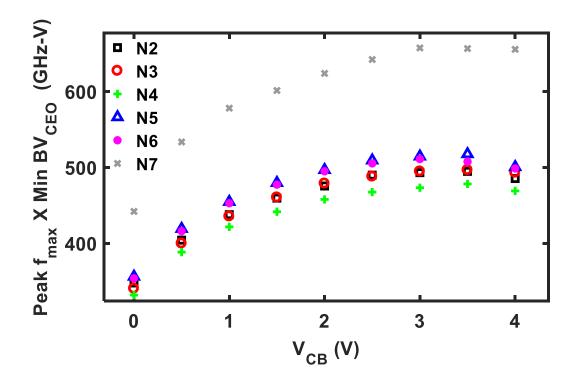

| Figure 8.14: | Measured Peak $f_{max} \times BV_{CEO}$ FoM for the different profiles for $V_{CB} = 4 \text{ V}$ .<br>                                                                                                                                                                                                                                                                                                         |

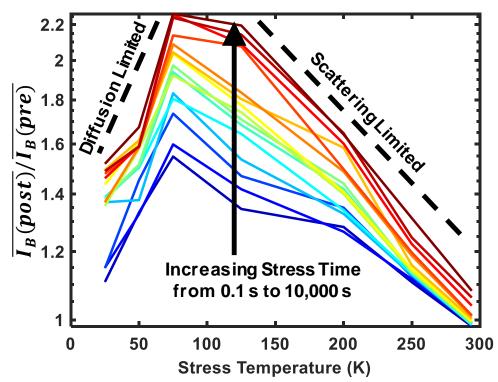

| Figure 9.1:  | Increase in mean base current degradation seen across four device samples for cryogenic temperatures following a mixed-mode stress of $J_E = 100 \ \mu A/\mu m^2$ and $V_{CB} = 2 \ V$ . I <sub>B</sub> extracted at $J_C = 1 \ \mu A/\mu m^2$ . Colors from blue to red indicate increasing stress time from 0.1 s to 10,000s. Regions of damage limited by hydrogen diffusion and phonon scattering indicated |

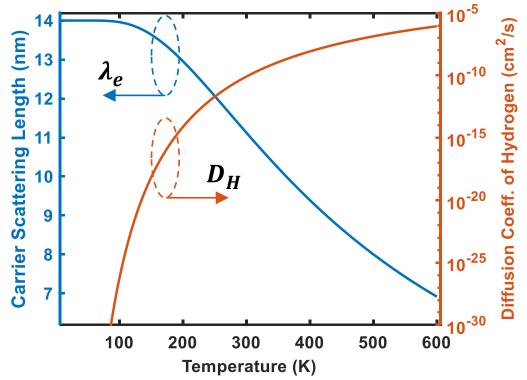

| Figure 9.2:  | Temperature dependence of electron scattering length and diffusion coefficient of hydrogen following the calibration in [3]                                                                                                                                                                                                                                                                                     |

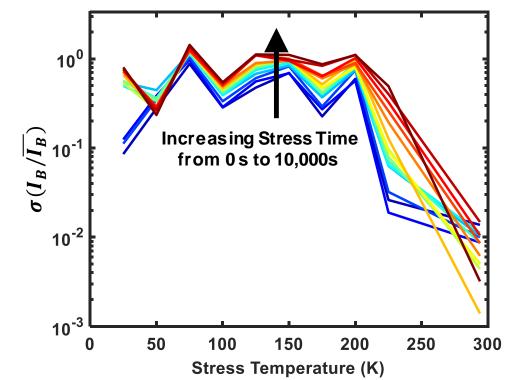

| Figure 9.3:  | Measured variabilities of aged base currents plotted as standard deviations from the normalized mean value for the mixed-mode stress condition in Figure 9.1. Colors from blue to red indicate increasing stress time from 0 s to 10,000s                                                                                                                                                                       |

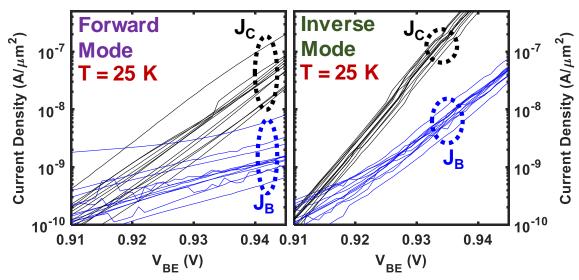

| Figure 9.4:  | Measured variability of Gummel characteristics in a fourth-generation SiGe HBT across 12 sample devices under FM and IM operation at 25 K 137                                                                                                                                                                                                                                                                   |

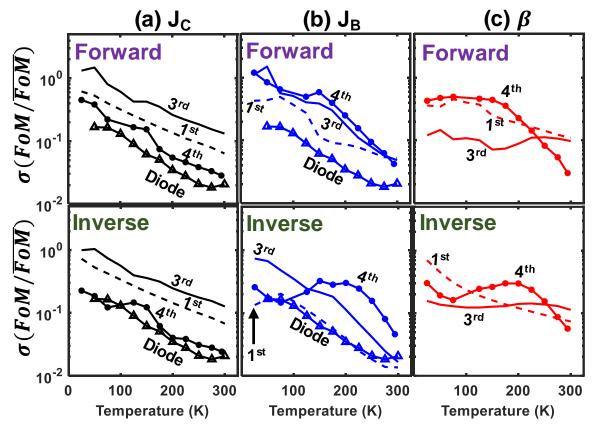

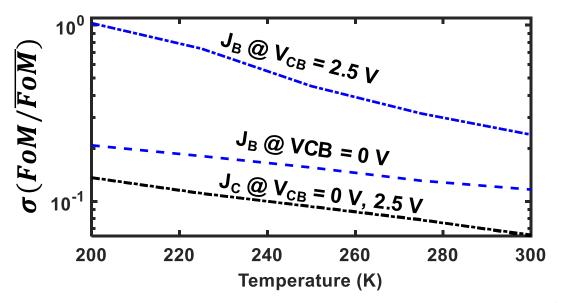

- Figure 9.6: Measured FM electrical variability plotted as standard deviations from the normalized mean value for  $J_c$  and  $J_B$  extracted at fixed  $V_{BE}$  near  $J_c = 1 \,\mu A / \mu m^2$  with and without an applied  $V_{CB} = 2.5 \, V_{CB}$ .

#### LIST OF SYMBOLS AND ABBREVIATIONS

BiCMOS Bipolar Complementary Metal Oxide Semiconductor

- SiGe Silicon-Germanium

- HBT Heterojunction Bipolar Transistor

- CB Collector-Base

- EB Emitter-Base

- BV<sub>CEO</sub> Breakdown voltage at the point of base current reversal

- TCAD Technology Computer-Aided Design

- EOL End of lifetime

- SOA Safe Operating Area

- R-D Reaction-Diffusion

- CGE Current Gain Enhancement

- NBTI Negative bias temperature instability

- QC Quantum Computing

- M-1 The measure of Avalanche multiplication from electric fields

- FoM Figure of Merit

- H Hydrogen

- FM Forward Mode operation of SiGe HBT

- IM Inverse Mode operation of SiGe HBT

- $\lambda$  Scattering length of a carrier

- $\phi_{hot}$  Hot carrier activation energy for depassivating Si-H bond

- $\beta$  Current Gain

- $\mu$  Mobility

- $\tau$  Recombination Lifetime

- $\sigma$  Standard Deviation or variation

#### SUMMARY

The objective of this work is to develop a generalizable understanding of the degradation mechanisms present in Silicon-Germanium (SiGe) heterojunction bipolar transistors (HBTs) that can be used to not only predict the reliable end of lifetime (EOL) of these devices but also overcome some of these aging limitations using clever device engineering. Presently, Bipolar Complementary Metal Oxide Semiconductor (BiCMOS) foundries impose very pessimistic restrictions on how much a SiGe HBT's performance can be pushed before facing adverse aging effects. While these foundries supply compact device models for circuit designs, a universal degradation model (currently unavailable) with push-button reliability prediction for these devices using hot-carrier physics could enable design optimizations that maximize performance while meeting the EOL requirement. This broad motivation for understanding and improving SiGe HBT device reliability is explored through the following specific goals: 1) develop an understanding of the dominant hot carrier degradation sources across temperature (25 K – 573 K); 2) develop a broad understanding of all potentially vulnerable regions of damage within a SiGe HBT using electrically measured data, and how these degradations can be captured in a modeling framework; and 3) design optimized SiGe HBTs that can potentially overcome some of these device-level limitations in reliability across temperature.

The following is a summary of accomplishments towards the above goals:

1. An introduction to the history and making of SiGe HBTs, and their relevance in modern high-speed communication systems. The challenges of SiGe HBT operation under extreme biasing and temperature conditions are summarized.

- 2. A preliminary demonstration of a TCAD-based aging model for simulating SiGe HBT aging under dynamic bias and temperature This work fully explores the physics of impact-ionization-induced (by high electric fields) hot-carriers in SiGe HBTs using a physics-based TCAD model. This was first presented at SRC TECHON © 2013 [1], published in the IEEE Bipolar/BiCMOS Circuits and Technology Meeting (BCTM) © 2013 [2] and later extended in the IEEE Transactions on Electron Devices (TED) © 2015 [3].

- 3. First physics-based high current damage model for SiGe HBTs This work explores the bias and temperature dependence of the Auger hot carrier generation under high current operation, and uses pulsed current stress measurements to see the effect on electrical degradation. This model is the first of its kind in both the CMOS and bipolar communities, and complements the electric field driven degradation model that was previously available. This was published in IEEE BCTM © 2016 [4].

- 4. Differences in the aging of complementary transistors (NPN+PNP) This work explains how the differences in activation energies for the damage of the oxide interfaces of the two devices is the primary cause for accelerated degradation seen in PNP SiGe HBTs, and generalizes an analytical model for simulating complementary aging. This work was published in the IEEE TED © 2017 [5].

- 5. Hot-carrier-damage-induced current gain enhancement effects in SiGe HBTs This work shows how hot carrier generation can damage both oxide interfaces and polysilicon regions of the emitter and base. A new current gain enhancement (CGE) effect is proposed that affects carrier mobilities in

polysilicon. In turn, this affects the series resistances and current gain ( $\beta$ ) at high injection, where circuits are typically biased to extract maximum device performance. This work was published in the IEEE TED © 2018 [6].

- 6. Comprehensive modeling of high-temperature aging effects in SiGe HBTs This work implements a Hydrogen diffusion model within TCAD to simulate the passivation and degradation within polysilicon, and in turn verify the electrical predictions of CGE effects in [6]. While existing aging models in the industry only predict current gain degradation due to oxide interface damage, this work identifies all relevant physical parameters in a device that can degrade at high temperatures due to hot carrier damage. This work is currently waiting for approval to submit to the IEEE TED.

- 7. Emitter-Base profile optimizations in SiGe HBTs for improved thermal stability and improved frequency response at low-bias currents This work explores profile designs that look at improving device reliability by reducing power consumption and engineering temperature-independent current gain, which can be useful for minimizing thermal runaway mechanisms. This work was published in the IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS) © 2018 [7].

- 8. A preliminary study of reliability and electrical variability in SiGe HBTs at cryogenic temperatures – This paper presents the first measurements of variability in currents due to cryogenic temperature operation for a Si diode and three different SiGe HBT platform nodes. The physics behind increased variability at low temperatures is explained with the help of TCAD. The

implications of variability on SiGe HBT reliability is also addressed. This work is currently under peer review for publication in IEEE TED.

#### **Copyright Statement**

In reference to IEEE copyrighted material which is used with permission in this thesis, the IEEE does not endorse any of the Georgia Institute of Technology's products or services. Internal or personal use of this material is permitted. If interested in reprinting/republishing IEEE copyrighted material for advertising or promotional purposes or for creating new collective works for resale or redistribution, please go to http://www.ieee.org/publications standards/publications/rights/rights link.html to learn how to obtain a License from RightsLink.

Portions of the enclosed text and many of the figures will become IEEE copyrighted material in the future.

#### **CHAPTER 1**

#### INTRODUCTION

#### 1.1 Motivation and Background for Using SiGe HBTs

In the last two decades, there have been many emerging applications requiring highfrequency circuits including radar, communication (terrestrial and satellite), and imaging and sensing using mmWave to terahertz (THz) frequency bands [8]. These applications target different audiences, including consumer gadgets, industry (automotive and aviation), military, scientific research, space exploration, and medicine, and require elegant system designs that consider the overall cost, size, and efficiency [9], [10]. For such applications, silicon-germanium (SiGe) heterojunction bipolar transistor (HBT) technology is increasingly becoming an attractive platform because of its ability to deliver III-Vtransistor-like performance using a bipolar CMOS (BiCMOS) process platform that offers high levels of integration with reduced design complexity at a significantly lower cost. A wide variety of example circuits employing SiGe HBTs for mmWave and sub-mmWave applications are already available today [11]. The adoption of SiGe BiCMOS technology for low-cost high-speed mixed-signal systems continues to increase, and to support the technological front, several foundries like IHP, GLOBAL-FOUNDRIES, Tower Jazz, STMicro, NXP, and Texas Instruments are major contributors. Although it is a relatively new technology compared to traditional silicon CMOS processing, the idea of exploiting bandgap engineering to induce a drift field in the base for enhanced speed goes back to the 1950s. These graded-base SiGe HBTs can be designed with significantly better analog and RF properties (gain, transconductance per unit area, output resistance, linearity, speed, and noise) compared to a Si BJT, while offering good compatibility and yield using standard CMOS processing [12]. These device-level advancements along with optimizations for passives [13], [14], allow for improved circuit designs for RF and analog applications.

#### 1.2 Reliability Challenges of SiGe HBT Scaling

Just like CMOS devices, SiGe HBTs also have enjoyed the benefits of scaling, including increased speed and performance. Recent state-of-the-art SiGe HBTs showcase maximum oscillation and maximum unity-gain power frequencies ( $f_T / f_{max}$ ) of 505 GHz / 720 GHz at room temperature and the barrier to THz operation continues to decrease with technology scaling [15], [16]. However, the scaling-induced reduction of operating voltages has proven to be a major reliability concern, since devices need to operate close to the safe operating area (SOA) boundaries that set the functional EOL limits for a given device. A scaled SiGe HBT with reduced breakdown voltage is more susceptible to hot carrier effects (avalanche and Auger generation) and must be carefully evaluated before being utilized in a circuit that needs a device with high-performance and reliably good EOL. Critical devices that operate in typical RF and mixed-signal circuits are subjected to mixed-mode stress (simultaneous application of both high current and high voltage stress) and can operate dynamically in various regions on the output plane consisting of either damaging or annealing regions, as shown in Figure 1.1. These regions are also driven by distinct physical processes with different temperature dependencies as operation deviates from room temperature [17], [18]. At medium to high currents, the traps created by hot carrier damage are annealed due to self-heating of the device, which can be enhanced at high temperatures. At very high currents, on the other hand, hot carrier damage caused by

Auger recombination is more prominent, and similarly has a positive dependence on temperature as shown experimentally in [18]. At even higher current levels below the electromigration limits of metal layers, the high power operation of the device causes catastrophic failures due to thermal runaway mechanisms [19]. For low to medium currents, at voltages much higher than  $BV_{CEO}$  (breakdown voltage defined by the base current reversal point), hot carrier damage is caused by impact-ionization and has a negative dependence on temperature. Being able to simulate the aging of devices following complex load lines shown in Figure 1.1 is an invaluable tool for any circuit designer needing high performance and robust reliability. First, however, a good universal physics-based model capable of predicting the accumulated stress damage seen by a device over time, electrical bias and temperature is mandatory at the device level.

Figure 1.1: Simulated SOA of forward-Gummel characteristics degradation in an NPN SiGe HBT after 100,000 s of stress with various T-dependent damage regions

outlined. Various dynamic load lines that change the EOL of the device due to hot carrier damage are overlaid (after [3]).

#### 1.3 Thesis Outline

The goal of this work is to develop a good understanding of degradation mechanisms in SiGe HBTs across temperature and overcome some limitations in device reliability with device profile engineering. The contents of this work are organized as follows:

**Chapter 1** – an introduction to the SiGe HBT reliability problem.

Chapter 2 – an overview of SiGe HBT history and known degradation mechanisms.

Chapter 3 – describes a TCAD model for high field damage.

**Chapter 4** – provides a TCAD model for high current damage.

Chapter 5 – shows how to adapt NPN models for PNP devices.

**Chapter 6** – shows the physical basis for current gain enhancement and polysilicon resistance degradation effects in SiGe HBTs.

**Chapter 7** – gives a TCAD model for capturing the effects in Chapter 6, along with extensive packaged measurements of high current damage at high temperatures.

**Chapter 8** – discusses emitter-base profile optimizations in SiGe HBTs to overcome thermal and power limitations that can affect reliability.

**Chapter 9** – explores the reliability and electrical variability of SiGe HBTs at cryogenic temperatures.

Chapter 10 – concludes the findings in this work and indicates future research directions.

#### **CHAPTER 2**

# SILICON-GERMANIUM BICMOS TECHNOLOGY AND RELIABILITY

#### 2.1 Brief History of Silicon-Germanium Technology

The structure of a modern SiGe HBT transistor is constructed with various characteristic features today for a reason. Ever since the development of the P-N junction and bipolar transistor theories by William Shockley, and the first demonstration of a point contact transistor in 1947, transistors have undergone extensive research, development, adoption, and evolution. Because of the initially insignificant speed and gain achievable in bipolar transistors, in 1957, Herbert Kroemer proposed using the following: 1) built-in electric fields independent of applied bias, and 2) a narrow bandgap base for improved emitter injection efficiency [20]. The latter is achieved by changing the alloy composition, and the former by grading the doping concentration or the bandgap. Although Kroemer's theory looked promising, due to the deficient technological development for SiGe epitaxy, the first successful demonstration (in 1987) of a SiGe HBT had to wait nearly three decades [21].

After the first proof of concept, several innovations in microfabrication methods from generation-to-generation, combined with CMOS processing methods, were needed to allow the rapid growth of faster SiGe HBT technology platforms over the years as shown by several roadmaps [8]–[10]. Beginning with the advancement of a low thermal budget (< 600 °C) UHVCVD process for SiGe HBTs in 1988, a high throughput, yet commercially reliable production of SiGe HBTs was a possibility since December of 1994 [22], [23]. The first-generation process (> 50 GHz  $f_{max}$ ) integrated the bipolar base after the CMOS gate flow to minimize the thermal cycle. Although the first-generation devices avoided the conventional high thermal Si epitaxy (>1000 °C) of the 1980s, building narrow base widths in the second generation onwards (> 100 GHz  $f_{max}$ ) required the incorporation of carbon during the epitaxy for suppressed boron diffusion [24]–[26]. In many second-generation devices, improvement of  $f_{max}$  came at the expense of a lowered  $f_T$  due to increasing parasitic capacitances and resistances with lateral (aimed at CMOS process flow) and vertical optimizations (steep doping and SiGe alloy grading) [27]-[29]. This problem was addressed in the third- (> 200 GHz  $f_{max}$ ) and fourth- (> 400 GHz  $f_{max}$ ) generation SiGe BiCMOS platforms with the introduction of a raised extrinsic base, which reduced the base resistance while also minimizing the collector-base and emitter-base overlap capacitances with better separation [30]. Lastly, adding lower doped regions to the emitter-base and base-collector transitions (for lowered parasitic capacitance) have allowed the creation of faster transistors (720 GHz  $f_{max}$ ) that continue to bridge the gap to the THz barrier [15].

#### 2.2 Overview of Competing Degradation Effects in SiGe HBTs

The vertical and lateral scaling of SiGe HBTs has led to junctions with large builtin fields and also smaller isolation layers (oxides and nitrides) separating the different terminals. As a result, for the same bias condition, this has led to the generation of more energetic hot carriers in scaled technologies. In addition, since these hot-carriers have less distance to traverse and physically damage vulnerable regions of a device, they can cause significantly more damage. As a result, scaling imposes restrictions on breakdown voltages and SOAs for devices. In order to quantify the reliable EOL and also quickly observe the electrical tolerance and degradation of SiGe HBTs, aggressive bias (high electric field and high current) and temperature conditions (well above and below room temperature) are often used to stress devices at an accelerated pace. The effects of these stresses can be categorized into "hard" and "soft" damage. The former consists of a catastrophic failure triggered by the high power operation of a device [19]. During this failure process, under very high current or very high voltage conditions, a device undergoes electro-thermal feedback and current pinch-in mechanisms as shown by Figure 2.1. Such conditions can physically melt and fuse the collector, base and emitter junctions, effectively turning the transistor into a resistor [19]. In contrast, "soft" damage is described by the degradation of electrical performance (current gain, noise and frequency response) over time due to physical damage by hot carriers. Figure 2.2 shows that the transistor nature in the Gummel characteristics is preserved despite the "soft" damage (trap accumulation) in the device.

Figure 2.1: TCAD cross section showing current density through a fourth generation SiGe HBT under a high power condition of  $J_E = 50 \text{ mA}/\mu\text{m}^2$  and  $V_{CB} = 4$  V. Current constricts towards the center of the device under high voltage operation, eventually triggering catastrophic thermal runaway of the device.

Figure 2.2: TCAD simulation of increasing base leakage current due to hot carrier damage following a high voltage stress. Forward and inverse mode operation of the SiGe HBT samples the base leakage due to EB and STI oxide traps (after [31]).

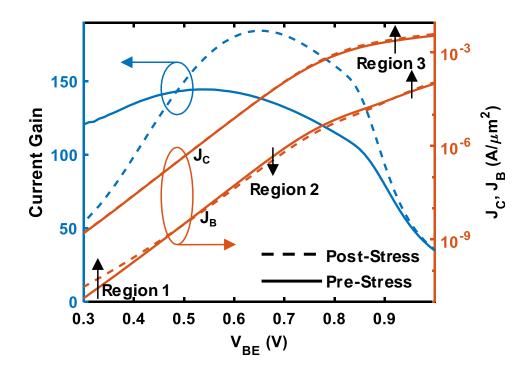

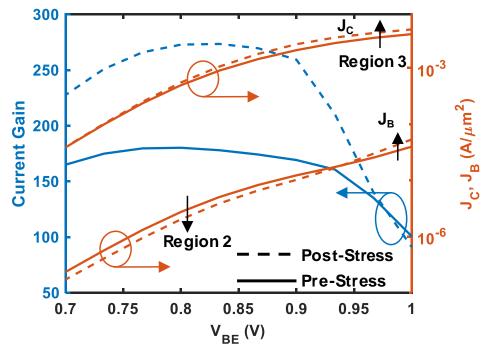

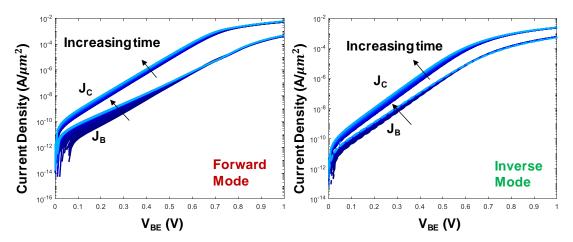

This thesis will primarily focus on providing models for transient performance degradation due to hot carriers in SiGe HBTs. Physical damage translates to electrical changes in a SiGe HBT that can broadly be recognized by three distinguishable regions in the change of Gummel characteristics shown in Figure 2.3. Of the three regions indicated, Region 1 has been the most studied and modeled. It is characterized by a strong increase in the base leakage current that degrades current gain, and can be described by the classical depassivation of the Si-H bonds along the emitter-base (EB) and shallow-trench (STI) oxide-silicon interfaces. The hot carrier sources and mechanisms that are capable of altering electrical behavior in this region will be discussed briefly in Sections 2.2.1 to 2.2.3, and more in detail in Chapters 3, 4 and 5. In contrast to Region 1, Region 2 is characterized by a decrease in the base current, suggesting an enhancement in current gain. In addition, Region 3 shows an increase in base and collector currents, suggesting a change in the

emitter resistance. The cumulative behaviors of Regions 2 and 3 have largely been attributed to the degradation of the polysilicon emitter [18]. Chapters 6 and 7 will demonstrate how the hot carrier sources that affect Region 1 can also cause changes in Regions 2 and 3.

Figure 2.3: Measured change in the Gummel characteristics of a NPN SiGe HBT following high-current stress of  $V_{CB} = 2 \text{ V}$ ,  $J_E = 15 \text{ mA}/\mu\text{m}^2$  (after [18]).

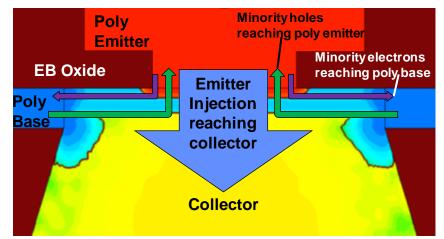

#### 2.2.1 Avalanche-Generated Hot Carriers

High electric field stresses (mixed-mode and reverse-EB) have been the most commonly used and well-studied methods for inducing hot carrier damage in SiGe HBTs [17], [32]–[34]. During mixed-mode stress, hot carriers are generated in the collector-base (CB) space-charge region due to the acceleration of injected minority carriers by the high electric-fields as shown in Figure 2.4. These carriers can once again produce electron-hole pairs via impact ionization, thus leading to a temperature-dependent avalanche generation of energetic carriers. If these carriers have sufficient energy from the field acceleration, they can travel towards the EB and STI oxides and displace hydrogen (H) atoms used to passivate the Si dangling bonds at the oxide-silicon interfaces. This causes H atoms to diffuse away from the interface, producing a net increase in interface traps. This ultimately leads to an increase in base current to compensate for trapping and de-trapping events occurring at the EB and STI interfaces as shown by Figure 2.2. Under reverse-EB bias stress, the large electric field across the EB junction enables band-to-band tunneling and also accelerates the generated carriers, making them capable of damaging oxide interfaces in a process similar to mixed-mode stress.

**Figure 2.4:** Hot carrier generation and transport to oxide interfaces under mixedmode stress (after [31]).

#### 2.2.2 Auger-Generated Hot Carriers

Similar to the high-field stresses, high-current stresses have also been known to cause damage to the Gummel characteristics [18], [35]–[37]. When SiGe HBTs are operated close to or beyond the peak  $f_T$  current density, the emitter-base (EB) field collapses and the neutral base and emitter are filled with carriers recombining via the Auger process. In the Auger process, an electron-hole pair recombines and donates the energy to

a nearby carrier. The recipient hot carrier will roam about the low-field region until it loses kinetic energy through momentum robbing collisions. In order for the hot carrier to cause damage to oxide interfaces, it must have sufficient energy to break Si-H bonds, and is known to be around 2.3 eV [38]. As the Auger hot carrier will have kinetic energy close to the bandgap ( $E_g$ ), an Auger hot carrier generated in silicon ( $E_g = 1.1 \text{ eV}$ ) should not have sufficient energy for producing damage. If current density within the device is high enough, however, simultaneous recombination events can lead to a single carrier receiving the energy of multiple recombination events (with limited probability) as illustrated in Figure 2.5. This generation of energetic hot carriers near the EB junction via the Auger process was first offered as an explanation by [37] to explain the electrical degradation seen under high-current stress in Si BJTs. The Auger-generated hot carriers at the EB junction can travel to the oxide interfaces and cause damage in a manner similar to the avalanchegenerated hot carriers as shown in Figure 2.6.

Figure 2.5: Probability distribution of hot electrons with multiple simultaneous Auger transition energies in silicon.

Figure 2.6: Auger hot carrier generation and transport to oxide interfaces under high-current stress.

# 2.2.3 Trap Annealing

Dangling bonds at oxide interfaces are passivated in SiGe HBTs with atomic hydrogen, which helps move the trap states outside of the semiconductor bandgap [39]. When the Si-H bonds are broken due to impingement by energetic carriers, an equal concentration of hydrogen and traps are created at the oxide interface that can subsequently participate in the annealing reaction of recreating this Si-H bond. Regardless of the mechanism responsible for damage at oxide interfaces, post-damage, this annealing phenomenon is always present and will try to counter any further damage, provided there is sufficient thermal energy. However, this thermal energy can go both ways in that it not only facilitates the creation of the Si-H bond, but also aids in diffusing the atomic hydrogen deeper within the oxide. Even slight changes to the local interface temperature due to different bias conditions can swing the reaction rate either way. The overall effect of selfheating can have a complex effect on the short term and long-term device degradation and recovery on the output plane due to the temperature dependencies of the different dynamic damaging and annealing components.

#### 2.3 Extent of SiGe HBT Reliability Modeling in Literature

Modeling the different hot carrier degradation mechanisms in Section 2.2 consists of two main components: 1) the process by which hot carriers are generated (indicated by P<sub>1</sub> in Figure 2.4 and Figure 2.6) and transported (indicated by P<sub>2</sub> in Figure 2.4 and Figure 2.6) to vulnerable regions (oxide interfaces and polysilicon) of the device and 2) the dynamic degradation and annealing processes at those regions. The lucky-electron (carrier) model was originally proposed for the first component in MOSFETs, and captured the field-induced hot-electron tunneling and gate leakage currents [40]–[42]. This model has been in use for several years and was also adapted for modeling mixed-mode stress degradation in SiGe HBTs under both compact modeling and TCAD environments [31], [43]. For the second modeling component, the reaction-diffusion (R-D) formalism was first proposed for MOSFETs in order to track the interface trap creation along the gate oxide interface that is responsible for bias temperature instability [44]. This model too was assimilated for SiGe HBTs and has helped in monitoring the trap creation at the EB and STI interfaces, which increases low-injection base current leakage [31], [43].

Although the lucky-electron model is advantageous in terms of simulation time, it can be inaccurate as it assumes instantaneous hot carrier generation and transport to oxide interfaces primarily based on the local electric field and current density. In reality, however, the creation of energetic hot carriers responsible for damage involves multiple excitations. An accurate solution for the energy distribution of carriers at an oxide interface would require a full-band solution to the Boltzmann Transport Equation (BTE). Using spherical harmonic expansion (SHE), the BTE can be solved without resorting to Monte Carlo methods, which can be time-consuming and noisy [45]. An approach coupling carrier energies using the SHE method to multistate trap configurations has also been applied for modeling SiGe HBT aging [46].

While accurate hot carrier generation and transport models are important, they also need to be coupled with accurate interface degradation models for simulating device aging. At the hearts of all interface degradation models are some variant of the depassivation of the Si-H bond. According to the R-D model, which has been in use for nearly four decades, the interface degradation is limited by the diffusion of hydrogen inside the oxide. In the last decade, however, the accuracy of this model for predicting the amount of recovery under negative bias temperature instability (NBTI) in MOSFETs has been questioned. For NBTI, the leading alternative explanation for R-D is the trapping and de-trapping of preexisting hole traps at the oxide interface without involving any hydrogen diffusion [47]. This process shows very minimal annealing even at elevated temperatures, suggesting a damage mechanism that is reaction-limited [48]. Instead of a diffusion-limited process, this reaction-limited approach for modeling hot carrier damage has also been applied in SiGe HBTs using SHE for hot carrier energy calculation [46]. Given the differences in the size and shape of the oxides, the electric fields along the oxides can differ by several orders of magnitude in SiGe HBTs and MOSFETs. Moreover, the degradation mechanisms for NBTI and hot carrier damage differ vastly in terms of temperature dependence, the carrier energies in play, and degradation in SiGe HBTs usually cannot be recovered [49]. This is one of the main reasons why the degradation mechanisms in MOSFETs and SiGe HBTs may not necessarily be the same, and that R-D may still be applied for SiGe HBTs.