# STARS

University of Central Florida

STARS

Electronic Theses and Dissertations, 2020-

2022

## Reconfigurable Load-Modulated Power Amplifier For Energy- and Spectrum-Efficient Wireless Communications

Haifeng Lyu University of Central Florida

Find similar works at: https://stars.library.ucf.edu/etd2020 University of Central Florida Libraries http://library.ucf.edu

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations, 2020- by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

## **STARS Citation**

Lyu, Haifeng, "Reconfigurable Load-Modulated Power Amplifier For Energy- and Spectrum-Efficient Wireless Communications" (2022). *Electronic Theses and Dissertations, 2020-.* 1405. https://stars.library.ucf.edu/etd2020/1405

## RECONFIGURABLE LOAD-MODULATED POWER AMPLIFIER FOR ENERGY- AND SPECTRUM-EFFICIENT WIRELESS COMMUNICATIONS

by

## HAIFENG LYU M.S. The University of Rhode Island, 2017

A dissertation submitted in partial fulfilment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical and Computer Engineering in the College of Engineering and Computer Science at the University of Central Florida Orlando, Florida

Fall Term 2022

Major Professor: Kenle Chen

© 2022 Haifeng Lyu

## ABSTRACT

With the increasing demand for faster date rates and extensive user connectivities, the complex modulation schemes and large-scaled arrays have been widely researched and employed in the modern wireless links e.g., 5G and beyond-5G systems. These pose major challenges to design the power amplifiers (PAs) to accommodate the system level evolution. As the critical part, the power amplifiers (PAs) dominate the output power, efficiency, linearity and reliability of the radio frequency (RF) transmitter. Consequently, the PA's capability of maintaining an efficient, linear and reliable signal amplification operation is essential to the communication systems. On the other hand, due to the deployment of massive multiple input/multiple output (MIMO) technique, the highly integrated active antenna systems replaced traditional  $50\Omega$ -based PA with sectorized antenna architectures. This brings the fact that, as the beam is steered in the antenna array, the dynamic load impedance observed from PAs can be up to 2: 1 Voltage Standing Wave Ratio (VSWR) due to the time-varying phasing and output power between the adjacent antenna elements and PAs, thus severely deteriorate PAs' performance.

To resolve aforementioned challenges, a novel design theory of Quasi-balanced Doherty power amplifier (QB-DPA) is first presented in this dissertation, which opens a new vision to counteract the mismatch-induced degradation using reconfigurable PA architectures. In this QB-DPA design, the isolation port of the PA's output coupler is alternatively terminated to 50- $\Omega$  load and ground to enable the balanced and Doherty modes. With the implementation of the silicon-on-insulator (SOI)-based single-pole-double-throw (SPDT) switch to realize the reconfiguration, the physical prototype is demonstrated exhibiting remarkable DPA performance, in terms of the linearity, efficiency and output power.

Subsequently, a series/parallel QB-DPA theory that not only can improve the back-off efficiency

of QB-DPA, but also significantly restore the load-mismatch degradation is proposed. This novel topology includes and unifies QB-DPA modes at balanced, series and parallel Doherty, respectively. Moreover, a novel linearity-enhanced combiner is introduced for nominal 50- $\Omega$  load to improve the linearity at both series and parallel QB-DPA modes. The reconfiguration between series and parallel operations largely restore the performance degradation when the PAs suffer a dynamic antenna mismatch condition.

Finally, a wideband mismatch-resilient QB-DPA is presented. Through parallel/series reconfiguration and reciprocal biasing, it is for the first time shown that the QB-DPA is able to maintain a stable output power as well as enhanced efficiency and linearity across 2 : 1 VSWR circle, and this operation can be seamlessly extended to a wide bandwidth which holds promising potential for application to array-based massive MIMO systems.

To my wife Minyi Zhang and my family

## ACKNOWLEDGMENTS

The PhD journey at University of Central Florida (UCF) have profoundly impacted my life and I will never be able to forget the time, people and everything here.

First and foremost, I would like to give the warmest appreciation to my advisor Professor Kenle Chen. The area of RFIC and mm-Wave PA is totally new for me before I began my PhD. It is Dr. Chen's continuous guidance, encouragement and trust that discover the new potentials on me and make my research projects and publications succeed. Dr. Chen is brilliant, professional and knowledgeable in radio technology and wireless communication systems. It's an enjoyable experience to work with him.

I would like to thank the members of my dissertation committee, Dr. Xun Gong, Dr. Mahdi Assefzadeh, Dr. Kalpathy Sundaram and Dr. Yajie Dong, for taking the time to review this work, providing valuable comments and serve in my committee. It is the most precious time to talk and learn from them.

I am sincerely grateful to my friends Jim Wunder, Carol Wunder, Dr. Michael Getachew Tadesse, Dr. Josiah Wong, Dr. Munan Gao, Dr. Yuanhang Zhang and Dr. Guanzhi Wang for their kindly help and encouragement. And my colleges in the lab, Dr. Wei Ouyang, Dr. Michael Trampler, Dr. Ricardo Lovato, Dr. Junyi Huang, Dr. Yuchen Cao, Ectis Velazquez, Jiachen Guo and Niteesh Bharadwaj Vangipurapu for their valuable advice and generous support during my Ph.D. study. I sincerely appreciate every one of you.

Most importantly, I would like to give gratitude and appreciation to my parents, my amazing wife and my two awesome sons, who endured this long journey with me, always offering a lot of love and motivation that I can be here today.

## TABLE OF CONTENTS

| LIST C | OF FIGURES                                                                                                          | xi  |

|--------|---------------------------------------------------------------------------------------------------------------------|-----|

| LIST C | DF TABLES                                                                                                           | kix |

| СНАР   | TER 1: INTRODUCTION                                                                                                 | 1   |

| 1.1    | Motivation of Mismatch-Resilient PAs                                                                                | 1   |

| 1.2    | Chapter Outline                                                                                                     | 4   |

| СНАР   | TER 2: BALANCED-TO-DOHERTY MODE-RECONFIGURABLE POWER AM-<br>PLIFIER WITH HIGH EFFICIENCY AND LINEARITY AGAINST LOAD |     |

|        | MISMATCH                                                                                                            | 5   |

| 2.1    | Introduction                                                                                                        | 5   |

| 2.2    | Quasi-Balanced Doherty PA Theory                                                                                    | 9   |

|        | 2.2.1 QB-DPA Operation at 6-dB Power Back-off and Below                                                             | 10  |

|        | 2.2.2 QB-DPA Operation at Power Saturation                                                                          | 12  |

| 2.3    | Practical Design Methodology of Linear B2D Mode-Reconfigurable PA                                                   | 14  |

| 2.4    | Prototype Design and Demonstration                                                                                  | 17  |

|        | 2.4.1 Design of the Standalone GaN PA                                                                               | 18  |

|       | 2.4.2  | Design of B2D Reconfigurable PA with Optimized Efficiency and Linearity | 20 |

|-------|--------|-------------------------------------------------------------------------|----|

|       | 2.4.3  | Qudrature Coupler and RF Switch Implementations                         | 23 |

|       | 2.4.4  | Fabrication                                                             | 25 |

| 2.5   | Measu  | rement Results and Analysis                                             | 25 |

|       | 2.5.1  | Continuous-Wave Measurement                                             | 25 |

|       | 2.5.2  | Modulated Measurement for Nominal 50- $\Omega$ Termination              | 26 |

|       | 2.5.3  | Two-Tone Measurement                                                    | 28 |

|       | 2.5.4  | Reconfigurable-Mode Measurement under Load Mismatch                     | 31 |

| 2.6   | Conclu | usion                                                                   | 33 |

| CHAP' | TER 3: | LINEARITY-ENHANCED QUASI-BALANCED DOHERTY POWER AM-                     |    |

|       |        | PLIFIER WITH MISMATCH RESILIENCE THROUGH SERIES/PARALLEI                |    |

|       |        | RECONFIGURATION FOW MASSIVE MIMO                                        | 34 |

| 3.1   | Introd | uction                                                                  | 34 |

| 3.2   | Series | & Parallel Quasi-Balanced Doherty PA Theory and Linearity Enhancement . | 38 |

|       | 3.2.1  | Transistor Modeling                                                     | 39 |

|       | 3.2.2  | QB-DPA Theory: Series and Parallel Topologies                           | 40 |

|       | 3.2.3  | Linearity-Enhanced Series and Parallel QB-DPAs                          | 44 |

|       | 3.2.4  | Verification using Emulated QB-DPA Model                                | 49 |

| 3.3   | Series/ | Parallel Mode Reconfiguration for Mismatch Recovery                     | 51    |

|-------|---------|-------------------------------------------------------------------------|-------|

|       | 3.3.1   | Analysis of Impedance Mismatch Effects                                  | 52    |

|       | 3.3.2   | Performance Enhancement for Mismatch Conditions: Analog Approach        | 56    |

| 3.4   | Prototy | ype Design and Demonstration                                            | 58    |

|       | 3.4.1   | Design of Linearity-Enhanced QB-DPA at Nominal Condition                | 59    |

|       | 3.4.2   | Mode Reconfiguration for VSWR Resilience                                | 62    |

| 3.5   | Fabric  | ation and Measurement Results                                           | 63    |

|       | 3.5.1   | Continuous-Wave Measurement                                             | 64    |

|       | 3.5.2   | Modulated Measurement with Nominal 50- $\Omega$ Termination $\ldots$    | 67    |

|       | 3.5.3   | Reconfigurable-Mode Measurement under Load Mismatch                     | 69    |

| 3.6   | Conclu  | sion                                                                    | 73    |

| 3.7   | Appen   | dix                                                                     | 74    |

| CHAPT | ΓER 4:  | ANALYSIS AND DESIGN OF RECONFIGURABLE MULTI-BAND MISMA                  | ATCH- |

|       | ]       | RESILIENT QUASI-BALANCED DOHERTY POWER AMPLIFIER FOR                    |       |

|       | ]       | MASSIVE MIMO SYSTEMS                                                    | 76    |

| 4.1   | Introdu | action                                                                  | 76    |

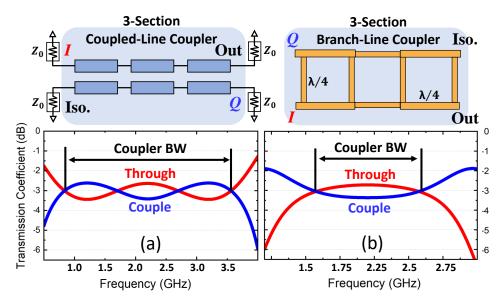

| 4.2   | Misma   | tch-Resilient and Wideband Quasi-Balanced Doherty Theory                | 80    |

|       | 4.2.1   | Ideal Parallel & Series Quasi-Balanced Doherty PA for Mismatch Recovery | 80    |

|        | 4.2.2   | Effects of Transistor Parasitics and Matching Networks                | 84 |

|--------|---------|-----------------------------------------------------------------------|----|

|        | 4.2.3   | Exchangeable Biasing for Bandwidth Extension                          | 88 |

| 4.3    | Prototy | pe Design and Demonstration                                           | 90 |

|        | 4.3.1   | Design of Wideband Matching Network                                   | 90 |

|        | 4.3.2   | Exchangeable Biasing for Multi-Band Operation and Parallel/Series Re- |    |

|        |         | configuration Against Load Mismatch                                   | 94 |

| 4.4    | Fabrica | ation and Measurement Results                                         | 97 |

|        | 4.4.1   | Continuous-Wave Measurement                                           | 98 |

|        | 4.4.2   | Modulated Measurement                                                 | 02 |

| 4.5    | Conclu  | ision                                                                 | 05 |

| CHAP   | TER 5:  | SUMMARY AND OUTLOOK                                                   | 07 |

| LIST C | OF REFI | ERENCES                                                               | 10 |

## **LIST OF FIGURES**

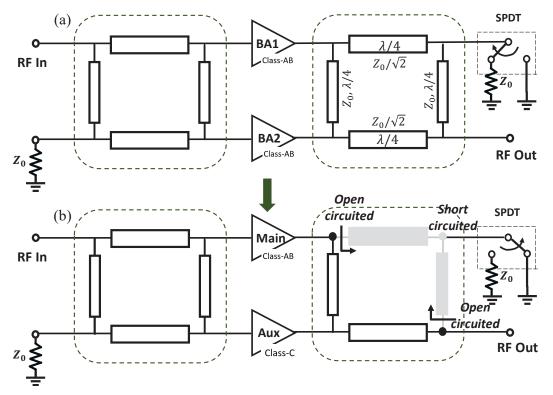

| 2.1 | Conceptual architecture of the proposed B2D mode-reconfigurable power                   |    |

|-----|-----------------------------------------------------------------------------------------|----|

|     | amplifier. A SOI-based SPDT switch terminates the isolation port of the                 |    |

|     | output coupler to $50$ - $\Omega$ load and ground alternatively. (a) Balanced mode. (b) |    |

|     | Doherty mode                                                                            | 6  |

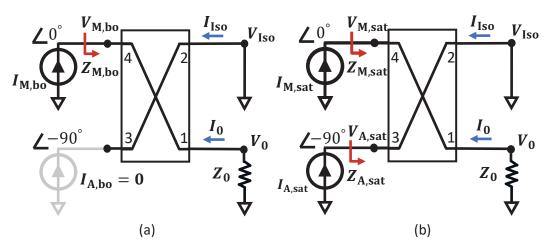

| 2.2 | Generalized schematic of the output combining network for analyzing the                 |    |

|     | proposed QB-DPA architecture at (a) 6-dB power back-off and below and (b)               |    |

|     | power saturation.                                                                       | 12 |

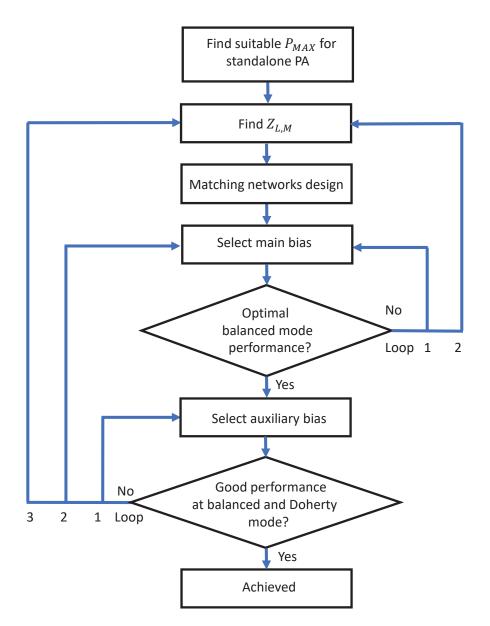

| 2.3 | Systematic design flow of the B2D mode-reconfigurable PA                                | 14 |

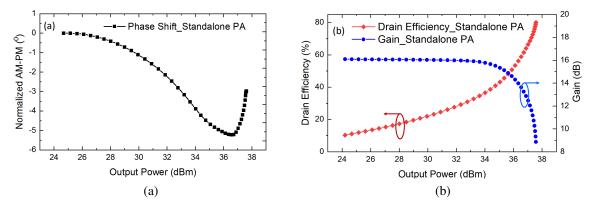

| 2.4 | Simulation results of the standalone PA at 3.5 GHz. (a) Normalized AM-PM.               |    |

|     | (b) DE and gain                                                                         | 17 |

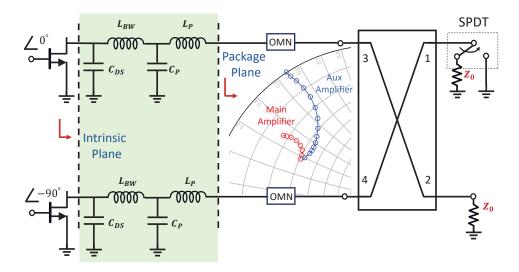

| 2.5 | Designed output combiner network with device parasitics. The inset Smith                |    |

|     | chart illustrates the desired dynamic load trajectories at package plane for the        |    |

|     | main and auxiliary amplifiers                                                           | 18 |

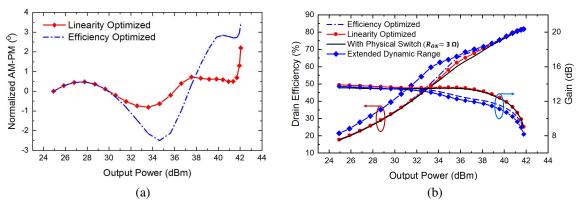

| 2.6 | Linearity- and efficiency-optimized designs of QB-DPA (Doherty mode of                  |    |

|     | B2D PA). (a) Normalized AM-PM. (b) DE and gain.                                         | 18 |

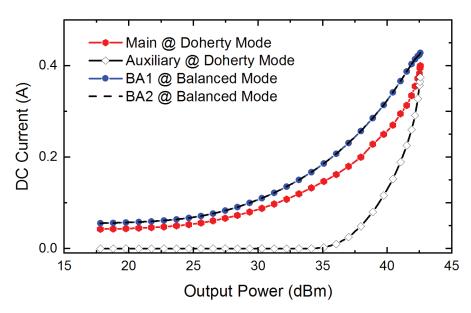

| 2.7 | Comparison of simulated drain dc currents between the balanced mode and                 |    |

|     | Doherty mode                                                                            | 19 |

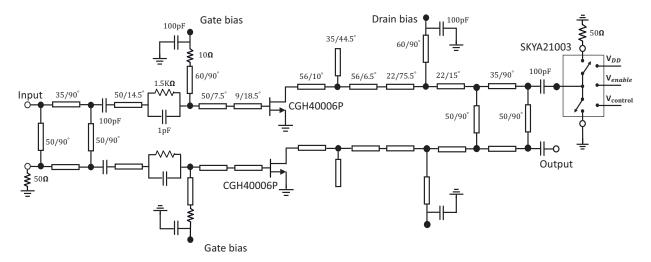

| 2.8 | Overall schematic of the designed B2D mode-reconfigurable PA with an im-                |    |

|     | plemented SOI-based SPDT switch.                                                        | 20 |

| 2.9  | Realization of reconfigurability using RF switch(es). (a) Alternative cir-<br>cuit topology with a single switch. (b) Design using a SPDT switch. (c) |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | Schematic of the SOI-COMS SPDT switch.                                                                                                                | 21 |

| 2.10 | Investigation on output combiner efficiency (insertion loss). (a) Effect of                                                                           |    |

|      | switch $R_{\rm on}$ resistance for shorting the isolation port in Doherty mode. (b)                                                                   |    |

|      | Over 2 : 1 VSWR circle in Doherty mode $R_{on} = 3 \Omega$ . (c) Over 2 : 1 VSWR                                                                      |    |

|      | circle in balanced mode.                                                                                                                              | 22 |

| 2.11 | Top view of the fabricated circuit board                                                                                                              | 23 |

| 2.12 | Measured DE and gain of Doherty mode and balanced mode                                                                                                | 26 |

| 2.13 | Measured frequency response of (a) DE and (b) gain at saturation and 6-dB                                                                             |    |

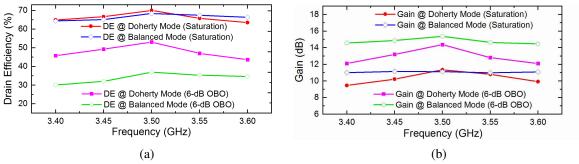

|      | OBO for both Doherty and balanced modes.                                                                                                              | 26 |

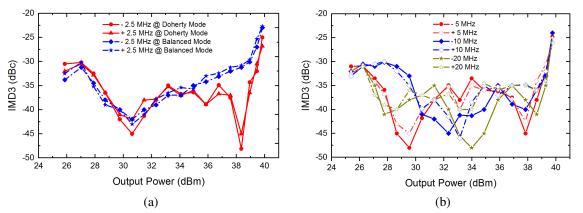

| 2.14 | Two-tone measurement centered at 3.5 GHz. (a) IMD3 of Doherty and bal-                                                                                |    |

|      | anced modes with 5-MHz tone spacing. (b) IMD3 of Doherty mode with                                                                                    |    |

|      | variable tone spacing.                                                                                                                                | 27 |

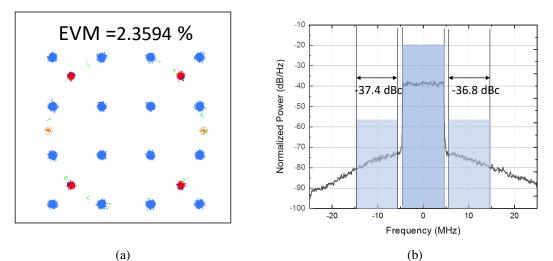

| 2.15 | Measured modulated signal at Pout = $34.5$ dBm without DPD. (a) 16-QAM                                                                                |    |

|      | constellation diagram corresponding to an efficiency of 42.4%. (b) Normal-                                                                            |    |

|      | ized PSD for a 10-MHz LTE signal at 3.5 GHz.                                                                                                          | 27 |

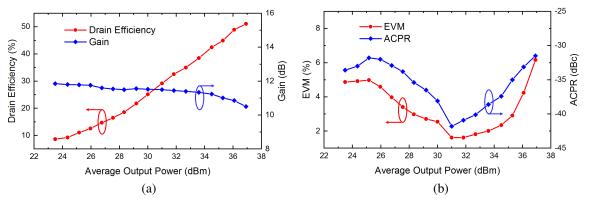

| 2.16 | Measured modulated signal versus average output power. (a) DE and Gain.                                                                               |    |

|      | (b) EVM and ACPR                                                                                                                                      | 28 |

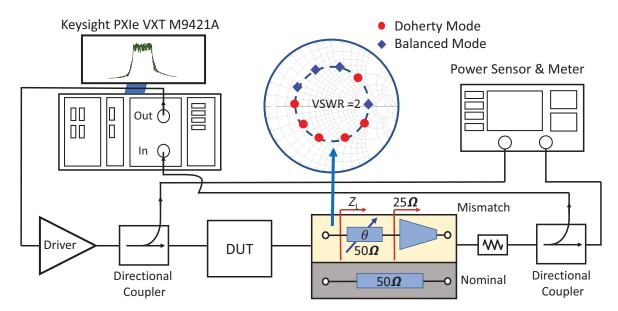

| 2.17 | An illustrative measurement setup for characterization of the B2D mode-      |    |

|------|------------------------------------------------------------------------------|----|

|      | reconfigurable PA under nominal 50- $\Omega$ and mismatch (2 : 1 VSWR) load- |    |

|      | ing conditions. Inset Smith chart presents a system-level operation scenario |    |

|      | when the B2D PA switches between Doherty and balanced modes to maintain      |    |

|      | the optimized performance over load variation.                               | 29 |

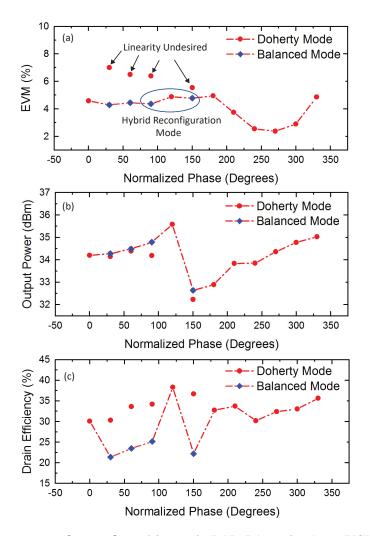

| 2.18 | Measurement of reconfigurable mode B2D PA under 2 : 1 VSWR over entire       |    |

|      | phase range. (a) EVM. (b) Output power. (c) Average DE                       | 30 |

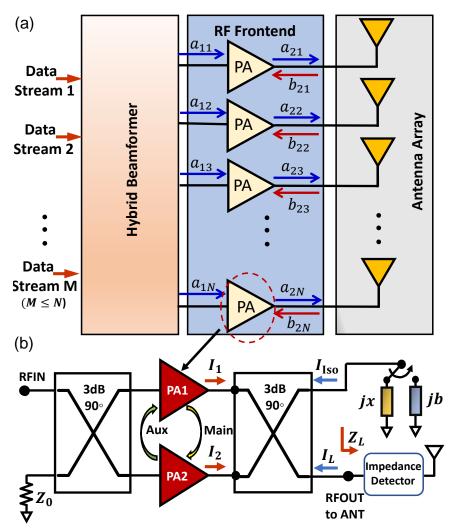

| 3.1  | Conceptual illustration: (a) MIMO antenna array with mutual coupling af-     |    |

|      | fecting the PA loading, (b) proposed reconfigurable series/parallel QB-DPA   |    |

|      | for load mismatch resilience.                                                | 35 |

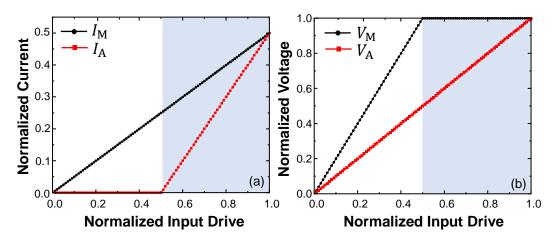

| 3.2  | Fundamental current and voltage profiles for the ideal DPA                   | 38 |

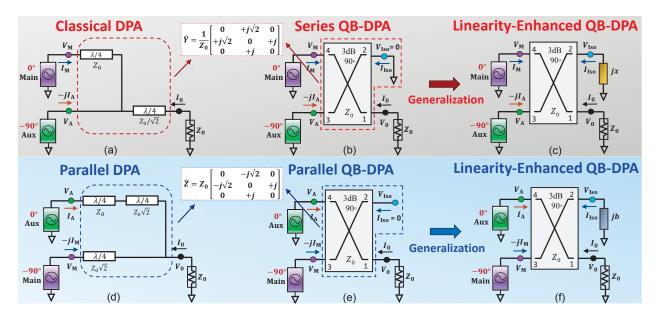

| 3.3  | Derivation of DPA architectures: (a) classical DPA, (b) series QB-DPA, (c)   |    |

|      | linearity-enhanced series QB-DPA, (d) parallel DPA, (e) parallel QB-DPA,     |    |

|      | (f) linearity-enhanced parallel QB-DPA                                       | 41 |

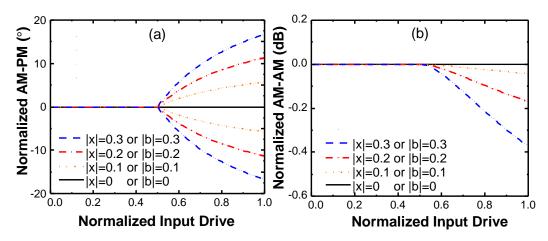

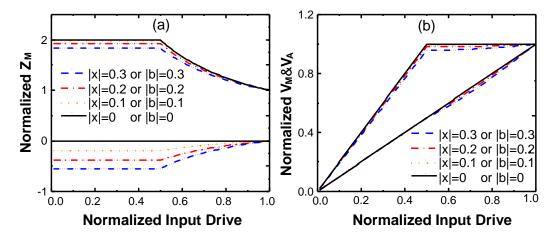

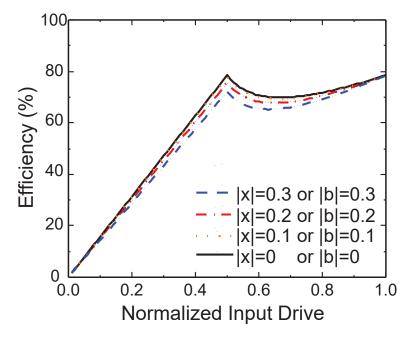

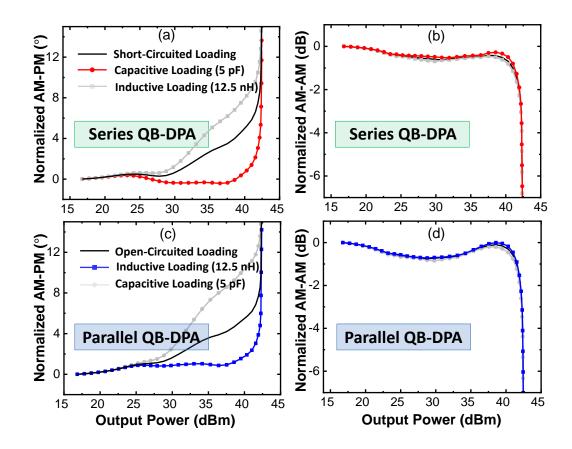

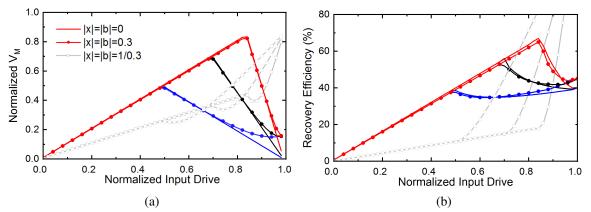

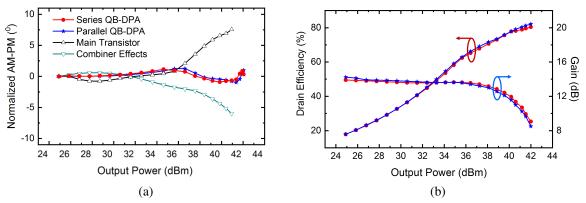

| 3.4  | Calculated dynamic PA behaviors of the linearity-enhanced architecture: (a)  |    |

|      | AM-PM profiles, (b) AM-AM profiles                                           | 47 |

| 3.5  | (a) Load and (b) voltage behaviors of the symmetric series and parallel QB-  |    |

|      | DPA modes                                                                    | 47 |

| 3.6  | Efficiency calculation based on the proposed reconfigurable QB-DPA           | 48 |

| 3.7  | Setup of the emulated QB-DPA model                                           | 49 |

| 3.8  | Simulated AM-PM and AM-AM profiles of the emulated QB-DPA model in                                                                          |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | series and parallel modes.                                                                                                                  | 50 |

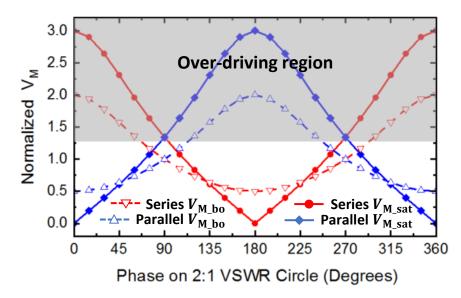

| 3.9  | Sketch of main amplifier voltage at series/parallel modes due to load mismatch.                                                             | 51 |

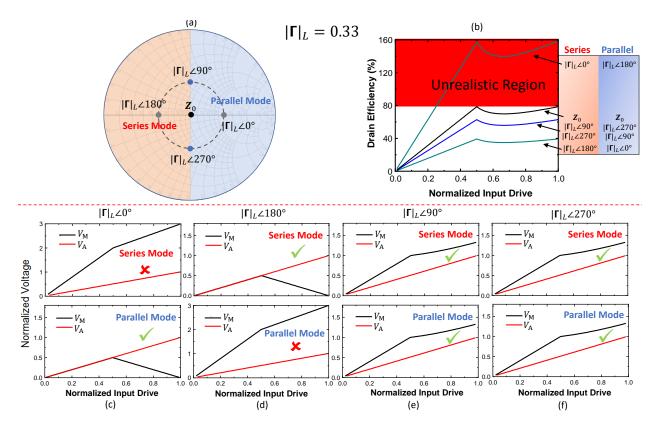

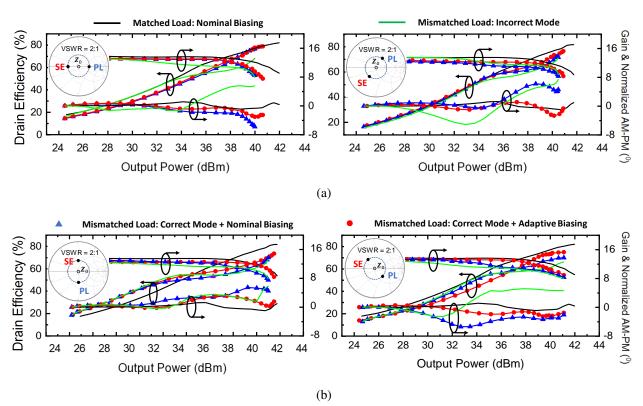

| 3.10 | Load mismatch analysis: (a) representative cases on VSWR 2 : 1 circle, (b)                                                                  |    |

|      | DE profile induced by the mismatched load and voltages at series/parallel                                                                   |    |

|      | modes for the corresponding loads, (c) $ \Gamma_L  \angle 0^\circ$ , (d) $ \Gamma_L  \angle 180^\circ$ , (e) $ \Gamma_L  \angle 90^\circ$ , |    |

|      | and (f) $ \Gamma_L  \angle 270^\circ$                                                                                                       | 52 |

| 3.11 | Illustration of (a) voltage and (b) efficiency recovery for $\Gamma_L=0.33 \angle 0^\circ$ at                                               |    |

|      | parallel mode and $\Gamma_L = 0.33 \angle 180^\circ$ at series mode, respectively                                                           | 55 |

| 3.12 | Illustration of (a) voltage and (b) efficiency recovery for $\Gamma_L = 0.33 \angle 90^\circ$ and                                           |    |

|      | $\Gamma_L = 0.33 \angle 270^\circ$ at both series and parallel modes                                                                        | 55 |

| 3.13 | Symmetrical series and parallel load modulation behaviors at device plane in                                                                |    |

|      | realistic design.                                                                                                                           | 57 |

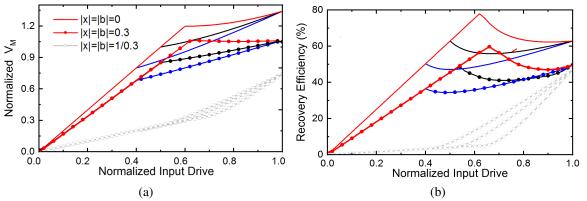

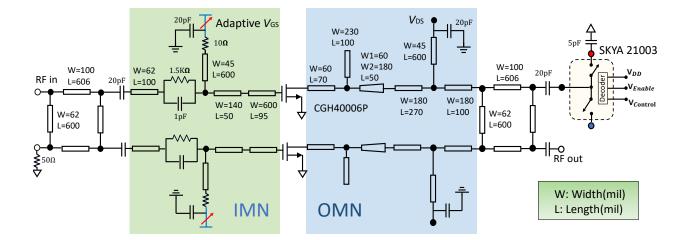

| 3.14 | Schematic of the designed IMN and OMN of standalone PA                                                                                      | 58 |

| 3.15 | Full Schematic of the designed reconfigurable QB-DPA with an SOI-based                                                                      |    |

|      | SPDT switch                                                                                                                                 | 59 |

| 3.16 | Simulation results of the QB-DPA at 3.5 GHz: (a) AM–PM, (b) DE and gain.                                                                    | 59 |

| 3.17 | Simulated gain, DE and AM-PM recovery for the illustrative mismatched-                                                                      |    |

|      | loads. (Minor differences in results between symmetrical conditions, i.e., SE                                                               |    |

|      | mode $@z_L$ and PL mode $@1/z_L$ , are omitted for clarity of plotting.)                                                                    | 60 |

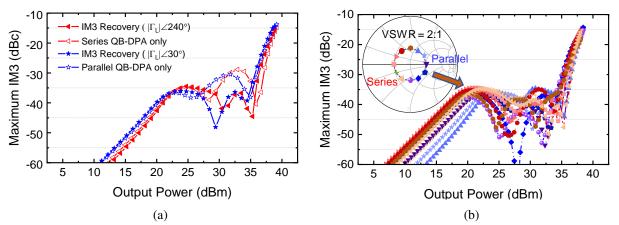

| 3.18 | Two tone simulation to verify IM3 recovery through reconfigruation of se-                                                                                                                                                                                              |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | ries/parallel modes.                                                                                                                                                                                                                                                   | 63 |

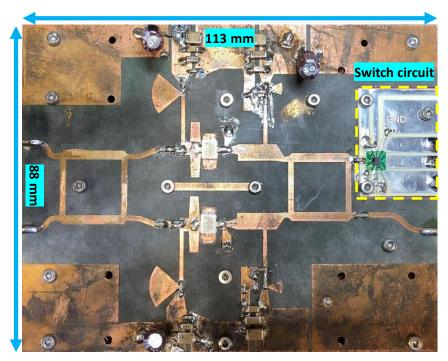

| 3.19 | Top view of the fabricated circuit board.                                                                                                                                                                                                                              | 64 |

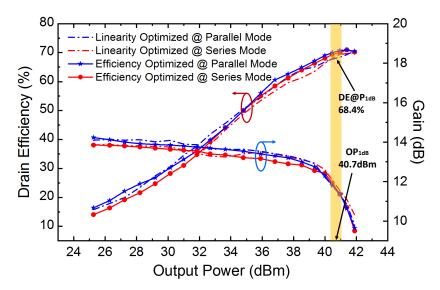

| 3.20 | Measured DE and gain versus output power centered at 3.5 GHz                                                                                                                                                                                                           | 65 |

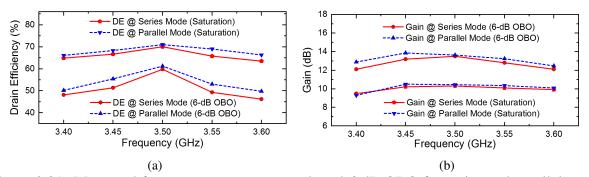

| 3.21 | Measured frequency response at peak and 6-dB OBO for series and parallel modes: (a) DE, (b) gain.                                                                                                                                                                      | 65 |

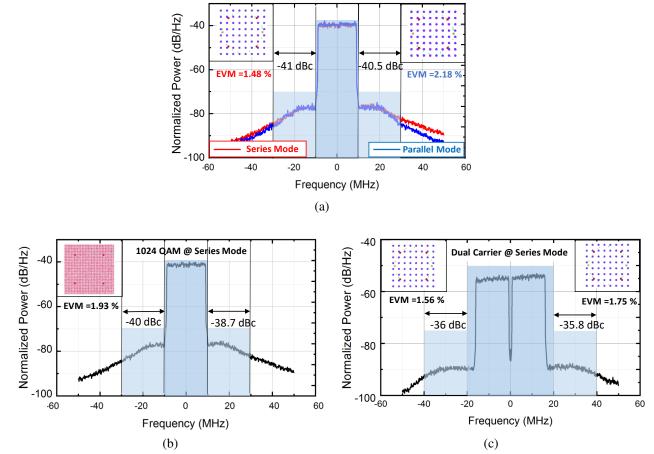

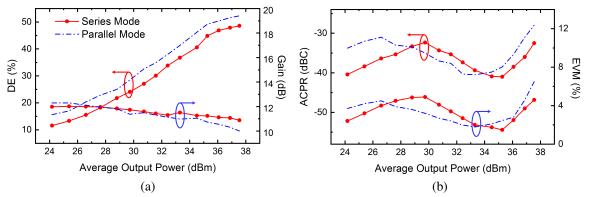

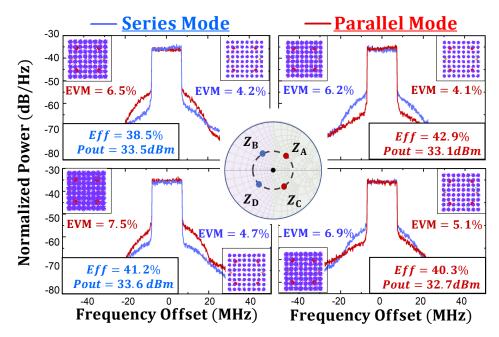

| 3.22 | Measured PSD, ACPR and EVM at 3.5 GHz without DPD: (a) At series/parallel modes under a 20MHz modulated signal with 64-QAM, (b) At series mode under a 20-MHz modulated signal with 1024-QAM, (c) At series mode under dual carrier 40-MHz modulated signal for 64-QAM | 66 |

| 3.23 | (a) DE and gain, (b) EVM and ACPR versus average output power under modulated signal with 20MHz modulation bandwidth and 64 QAM                                                                                                                                        | 67 |

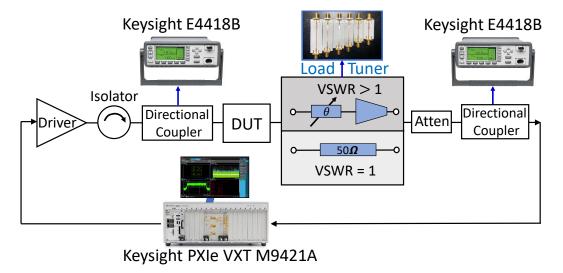

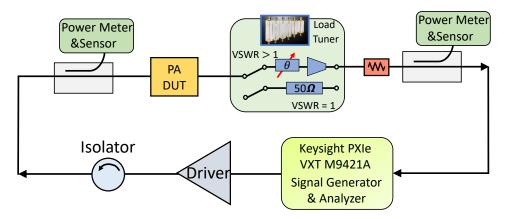

| 3.24 | Measurement setup for characterization of the series/parallel QB-DPA under nominal 50- $\Omega$ and mismatch loading (VSWR > 1) conditions                                                                                                                             | 67 |

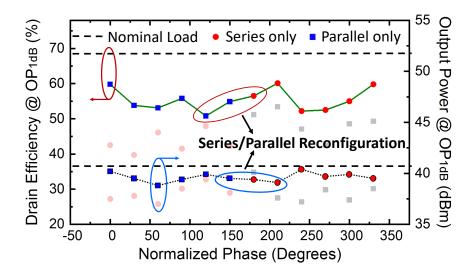

| 3.25 | Measured DE and $\mathrm{OP}_{1\mathrm{dB}}$ over 2:1 VSWR with CW signal                                                                                                                                                                                              | 69 |

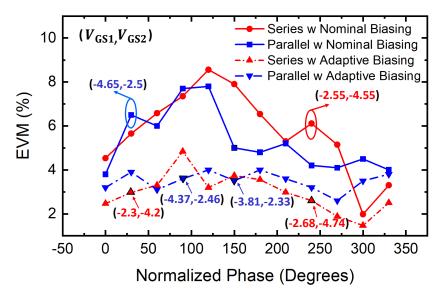

| 3.26 | EVM at 2:1 VSWR with modulated signal under nominal biasing and adap-<br>tive biasing, respectively.                                                                                                                                                                   | 70 |

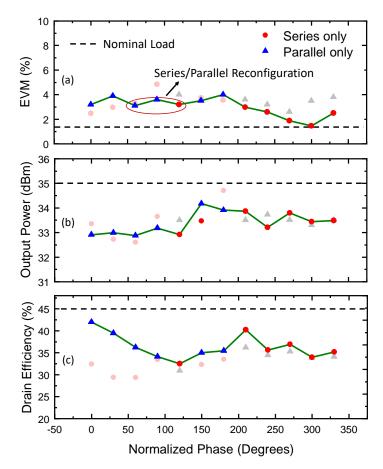

| 3.27 | Modulation signal Measurement of reconfigurable series/parallel PA under<br>2 : 1 VSWR over entire phase range: (a) EVM, (b) output power, and (c)<br>average DE                                                                                                       | 71 |

| 3.28 | Modulation signal Measurement of series/parallel QB-DPA under variable         |    |

|------|--------------------------------------------------------------------------------|----|

|      | VSWR over entire phase range: (a) EVM, (b) output power, and (c) Average       |    |

|      | DE                                                                             | 72 |

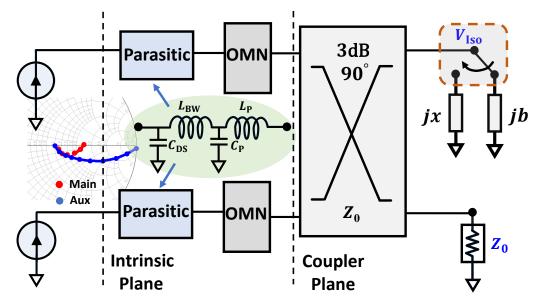

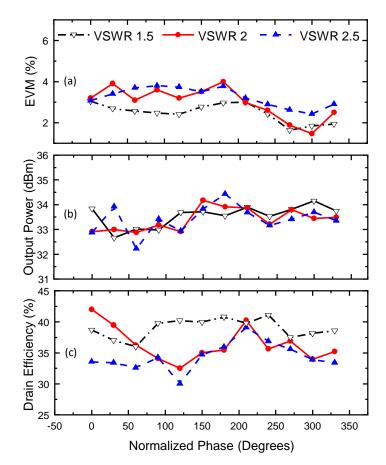

| 4.1  | Proposed wideband QB-DPA: (a) Circuits mechanism for parallel/series switch-   |    |

|      | ing and nominal/exchanged biasing alteration, (b) operation division for par-  |    |

|      | allel/series QB-DPA to recover mismatch and (c) broadband realization with     |    |

|      | nominal/exchanged biasing                                                      | 77 |

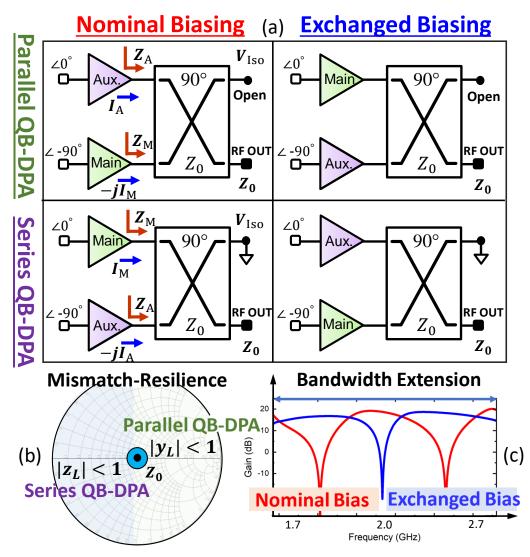

| 4.2  | (a) Proposed wideband QB-DPA OMN, (b) equivalent OMN with ideal trans-         |    |

|      | former and TL                                                                  | 82 |

| 4.3  | Calculated QB-DPA behaviors due to the $\theta$ dispersion for: (a) normalized |    |

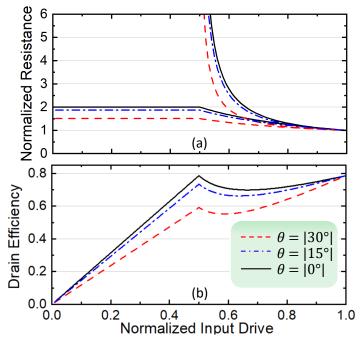

|      | resistance of $Z_{\rm M}$ and $Z_{\rm A}$ , (b) drain efficiency.              | 84 |

| 4.4  | Calculated QB-DPA behaviors due to the $\theta$ dispersion for: (a) AM-PM, (b) |    |

|      | AM-AM                                                                          | 86 |

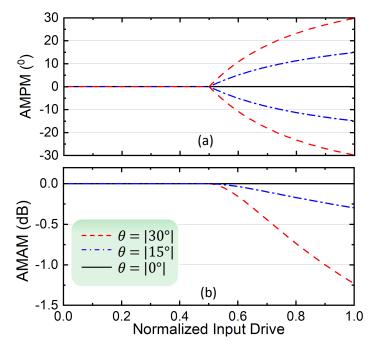

| 4.5  | Simulated AM-PM responses using emulated QB-DPA circuit model [1] for          |    |

|      | different values of phase dispersion.                                          | 87 |

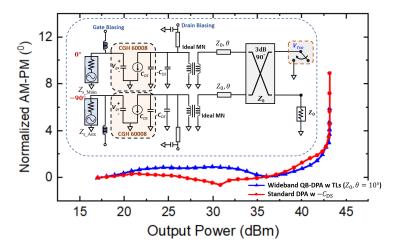

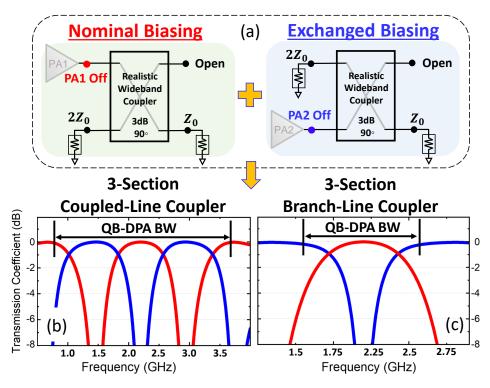

| 4.6  | Wideband coupler with transmission coefficients: (a) coupled-line coupler,     |    |

|      | (b) branch-line coupler                                                        | 88 |

| 4.7  | Wideband QB-DPA at parallel mode: (a) back-off power equivalent circuit        |    |

|      | with nominal/exchanged biasing, and bandwidth extension with combiner of       |    |

|      | (b) coupled-line coupler, (c) branch-line coupler                              | 89 |

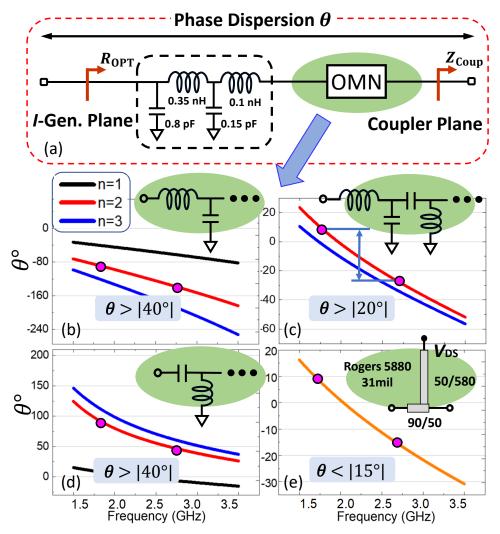

| 4.8  | Analysis of the wideband OMNs and phase dispersion from current source                               |     |

|------|------------------------------------------------------------------------------------------------------|-----|

|      | plane to coupler plane: (a) concept of OMN design, (b) low-pass OMN, (c)                             |     |

|      | low-pass plus high-pass OMN, (d) high-pass OMN and (e) proposed OMN.                                 | 91  |

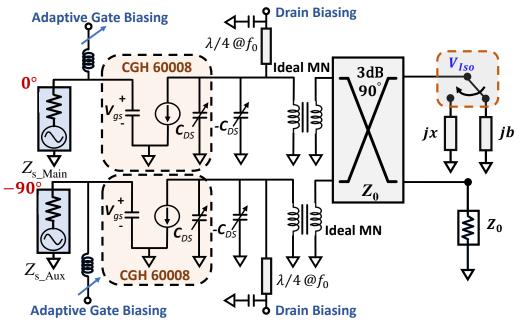

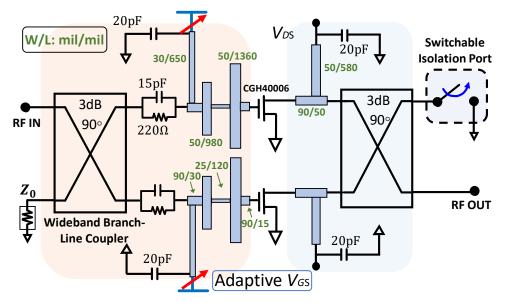

| 4.9  | Full Schematic of the designed wideband mismatch-resilient QB-DPA archi-                             |     |

|      | tecture                                                                                              | 92  |

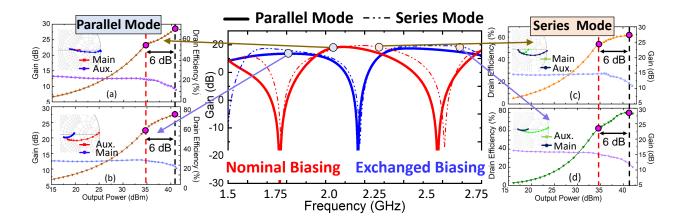

| 4.10 | Small-signal and large-signal simulation results for wideband QB-DPA in                              |     |

|      | parallel and series modes and with nominal/exchanged biasing                                         | 92  |

| 4.11 | Simulation performance of wideband QB-DPA under $2:1$ VSWR for $\mathrm{OP}_{1dB}$                   |     |

|      | and drain efficiency at $\mathrm{OP}_{\mathrm{1dB}}$ and 6-dB back-off region for (a) and (b) at 2.1 |     |

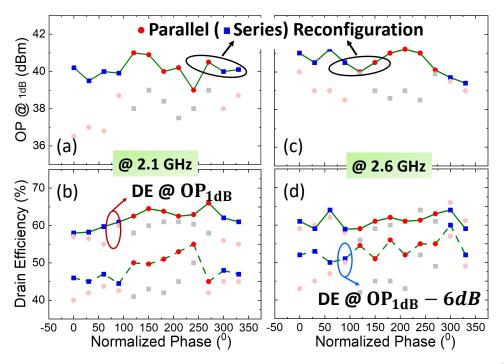

|      | GHz, (c) and (d) at 2.6 GHz                                                                          | 94  |

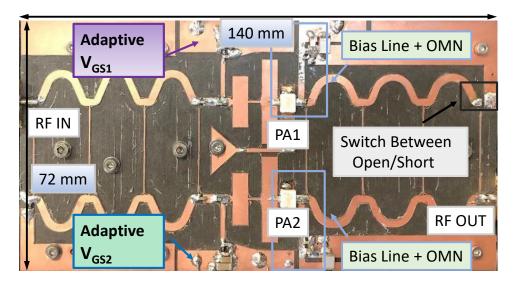

| 4.12 | Top view of the fabricated PCB board.                                                                | 95  |

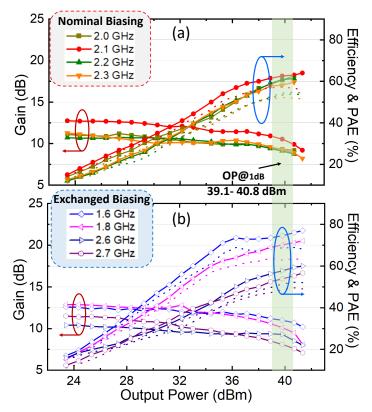

| 4.13 | CW measurement of power-swept DE, PAE and gain over 1.6-2.7 GHz at                                   |     |

|      | matched-load condition for parallel QB-DPA.                                                          | 96  |

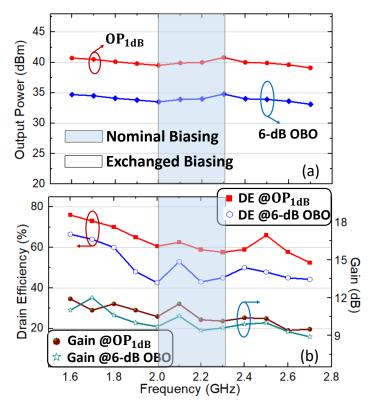

| 4.14 | Frequency response with exchangeable biasing for (a) output power, (b) drain                         |     |

|      | efficiency (DE) and gain.                                                                            | 97  |

| 4.15 | Measurement setup for characterization of the wideband QB-DPA under nom-                             |     |

|      | inal 50- $\Omega$ and mismatched loading (VSWR > 1) conditions                                       | 98  |

| 4.16 | Measured $OP_{1dB}$ over 2:1 VSWR with CW signal at 1.7 GHz: (a) parallel                            |     |

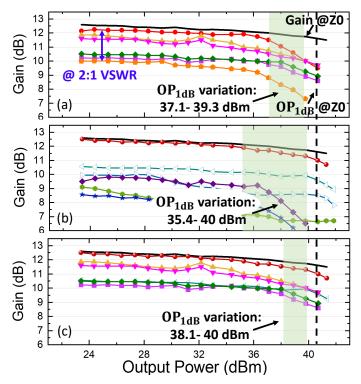

|      | only, (b) series only, (c) reconfiguration combination.                                              | 99  |

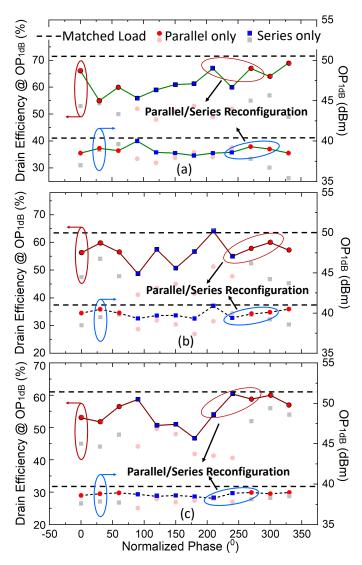

| 4.17 | Measured DE and $\rm OP_{1dB}$ over 2:1 VSWR with CW signal at (a) 1.7 GHz, (a)                      |     |

|      | 2.1 GHz and (c) 2.6 GHz                                                                              | 100 |

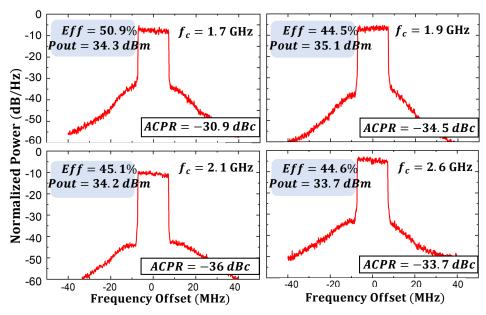

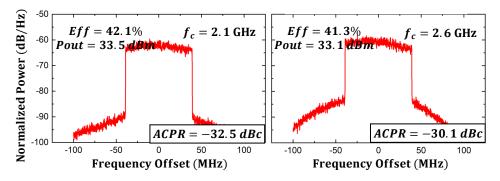

| 4.18 | Modulation measurement under 20-MHz 64-QAM LTE signal over 1.7-2.6                                                |

|------|-------------------------------------------------------------------------------------------------------------------|

|      | GHz with 50- $\Omega$ load                                                                                        |

| 4.19 | Modulation measurement under 80-MHz 5G-NR with 50- $\Omega$ load 101                                              |

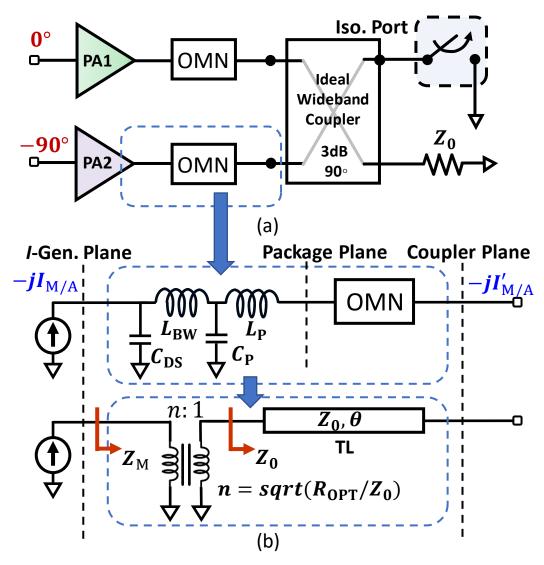

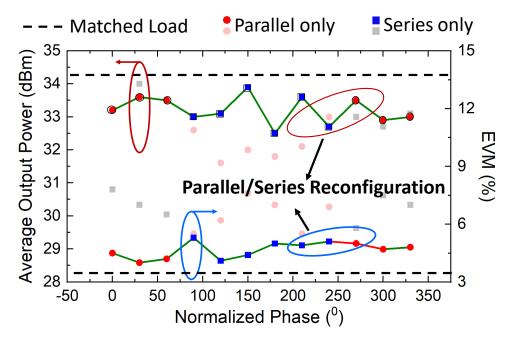

| 4.20 | Measured ACPR, EVM, $P_{OUT}$ and average efficiency over 2:1 VSWR with 64-QAM 20-MHz bandwidth signal at 2.1 GHz |

| 4.21 | Modulated evaluation using 64-QAM 20-MHz bandwidth 4G LTE signal at                                               |

|      | $2:1$ VSWR at 2.1 GHz for average $P_{OUT}$ and EVM                                                               |

## LIST OF TABLES

| 2.1 | Comparison with State-of-the-Art of Recently-Reported Linear GaN PAs         | 32  |

|-----|------------------------------------------------------------------------------|-----|

| 3.1 | State-of-the-Art of Linear and Efficient GaN PAs                             | 68  |

| 4.1 | Comparison with State-of-the-Art of Recently-Reported Mismatch-Resilient PAs | 105 |

## **CHAPTER 1: INTRODUCTION**

#### 1.1 Motivation of Mismatch-Resilient PAs

The modern wireless systems, i.e., 5G and beyond-5G, featured as ultra-fast data rates and everincreasing user connectivity, have stimulated the research and development of new technologies of the radio frequency front-end (RFFE) to cope with the challenges. It is envisioned that the wider instantaneous bandwidth and spectrally efficient modulation schemes will be widely employed for the future communication ecosystem. As the key device in the RF transmitter, power amplifiers (PAs) play a critical role to amplify the RF signals to the antennas, which dominate the many performance aspects of the entire system [2]. Therefore, the PAs are expected to achieve an ultimate balance of energy efficiency and linearity as well as other specs in the wireless links.

To achieve a maximum channel throughput, modern communication standards and applications extensively employ complex modulation schemes, such as Orthogonal frequency division multiplexing (OFDM), high-order quadrature amplitude modulation (QAM) and carrier aggregations, which exhibits large dynamic ranges featured with high peak-to-average-power ratio (PAPR). This, however, causes a dramatic degradation of average efficiency of power amplifier (PA), since it has to routinely operate in significant power back-off regions. Conventional PAs (basic classes of A-C and harmonic tuned classes E,F and J) are designed target for high peak power efficiency at saturation level, which brings in the concern about the thermal management when amplifying such high-PAPR signals. Moreover, due to the complex constellations requirements, the PA linearity are also mandatory to ensure the signal fidelity and the communication link Quality-of-Service (QoS) to transmit high-PAPR signals.

Meanwhile, with the proliferation of communication bands, more and more spectrum fragments

are being incorporated into wireless communications. In order to accommodate the ever-increasing number of allocated frequency bands, the RF bandwidth of power amplifiers and transmitters need to be as wideband as possible to support the multi-band/multi-mode operations without suffering from non-affordable hardware complexity, size, and cost. Therefore, broadband and highly-performance PA technologies are of crucial importance for next-generation wireless systems. Extensive research regarding PA architectures to enhance the PA efficiency over the broad bandwidth have been proposed and developed including supply modulation (envelope tracking) and load modulation. However, due to the bandwidth limitation and time constraints of the current dc-dc converter techniques to track the modulation signal envelope, load modulation PA architectures becomes a hot topic that draws more interests. Various of load-modulation architectures have been proposed and employed in realistic systems, including Doherty PA (DPA), out-phasing PA, and load modulated balanced amplifier (LMBA).

Doherty PAs are amongst the most widely adopted in cellular base station due to its enhanced efficiency at significant power back-offs as well as simple and mature architecture. The original Doherty PA (DPA) topology invented by William H. Doherty in 1936 consists of two different biased amplifiers (Class AB for main and Class C for auxiliary) combined with two quarter-wave transmission lines (TLs). Compared with conventional PAs (mentioned above), the DPA's back-off efficiency can be substantially enhanced, which makes it be a competitive candidate to amplify signals with complex modulation. However, due to the quarter-wave transformer employed ,strong nonlinearity is accompanied during the load modulation process. Consequently, external linearization techniques such as digital predistortion (DPD) are required to maintain the signal's quality and comply with the communications standards. Since DPD is quite energy consuming, especially when accommodating wide modulation bandwidths of signals, intrinsically linear DPAs are more preferred in emerging array-based communication systems, e.g., 5G.

On the other hand, to further enhance the spectral efficiency, array-based spatial multiplexing tech-

nique has been widely exploited in 5G base stations that leverages the spatial differences to enable concurrent transmission of multiple signals at the same frequency, also known as massive multiple-input multiple-output (MIMO). Compared with small-scale MIMO systems, the massive MIMO serve more subscribers with the expansion of the array scale to produce the required effective isotropically radiated power (EIRP) towards receivers through the digital (Sub-6-bands) or hybrid (mm-Wave) beamformer. However, the high-density antenna array inevitably brings about strong mutual couplings between the co-located antennas as the beam is steered in the array. These couplings result in a high-speed antenna impedance variation as well as a large time-varying change of voltage standing wave ratio (VSWR) and therefore, the antenna presents a sub-optimal loadline to the associated PA in the RF chain that engender a significant performance (e.g., efficiency, linearity, and OP1dB) degradation of PA. A more severe issue is the main beam distortion due to the accumulated PA non-linearity among the array in which different AM-AM and AM-PM distortion generated for different element location, and it render (DPD) ineffective to be applied at array level considering the power, cost and complexity.

While meeting all the aforementioned requirements, the future PA architectures are expected to improve the efficient and linear operations when exposed to substantial load mismatch, while maintaining a large achievable bandwidth for sustainable cost and space. To solve these challenges, a generalized coupler-based Quasi-balanced Doherty PA (QB-DPA) theory was first proposed. This novel PA architecture can be reconfigured from balanced mode to Doherty modes (B2D) through a SOI voltage-controlled single-pole double-throw (SPDT) switch to counteract the load mismatch, while high efficiency and linearity can be maintained over the VSWR variations. More importantly, this theory analytically proves that the load modulation behavior of the QB-DPA is mathematical equivalent to the conventional DPA, which provides a new design methodology of linear and efficient DPA.

The discovery of QB-DPA theory enables the PA reconfiguration between Doherty and balanced

modes to mitigate the performance impairment induced by dynamic antenna impedance variation. In order to enhance the back-off efficiency due to the identical drain bias conditions applied for PAs at balanced mode, a series and parallel QB-DPA theory is then proposed. Through reciprocally exchanging the main and auxiliary amplifiers and alternatively terminating the isolation port of the output coupler to a small reactance (close to short circuit) and susceptance (close to open circuit), the QB-DPA can significantly alleviate the load mismatch related degradation. This expanded theory reveals that the series and parallel modes have different sensitivity to load mismatch in a complementary way. In conjunction with a first-ever proposed reactive loadline tuning at the coupler's isolation port, the series/parallel QB-DPA can be utilized to counteract the arbitrary load mismatch up to 2.5 : 1 of VSWR with a state-of-the-art performance. Although the proposed series/parallel QB-DPA in the second part of this dissertation presents a distinctive performance improvement in terms of power efficiency, linearity, and output power, it is presently limited to the relative narrow bandwidth operation. The last part of the dissertation will focus on a bandwidth extension for the PA based on the QB-DPA theory to counteract the load mismatch.

### 1.2 Chapter Outline

This dissertation will focus on the mode-reconfigurable Quasi-balanced Doherty PA against load mismatch for massive MIMO application. Chapter 1 gives a brief introduction of modern wire-less systems architecture and the performance specifications required for future PA's design. The balanced-to-Doherty PA theory will be derived and established in chapter 2 with proposed linear DPA design methodology. The chapter 3 explores the series/parallel QB-DPA theory that can largely mitigate the degradation due to the dynamic impedance variation. The wideband active antenna array friendly QB-DPA is introduced in chapter 4. Summary will then be drawn in chapter 5 with projected future works.

## CHAPTER 2: BALANCED-TO-DOHERTY MODE-RECONFIGURABLE POWER AMPLIFIER WITH HIGH EFFICIENCY AND LINEARITY AGAINST LOAD MISMATCH

<sup>1</sup>A design methodology of load insensitive PA has drawn extensive interests recently due to the massive MIMO deployment. In particular, load modulation PAs with high average efficiency, linearity over VSWR variation are a competitive candidate to be applied in the 5G or beyond 5G systems. This chapter will systematically investigate a first-ever proposed mismatch-resilient load modulation PA architecture.

### 2.1 Introduction

The evolution of wireless communications has triggered ever-increasing demands for higher data rate and enhanced spectral efficiency, which are typically realized through widened modulation bandwidths and advanced modulation techniques, such as orthogonal frequency-division multiplexing (OFDM) and high-order quadrature amplitude modulation (e.g., 1024 QAM). These modulation schemes introduce large peak-to-average power ratio (PAPR) that not only substantially degrade the power-amplifier (PA) efficiency but also impose stringent linearity requirements on PAs. Consequently, the PA's capability of efficiently and linearly transmitting high-PAPR signals is critical to modern communication systems towards ultra-fast speed and high energy efficiency.

In the past two decades, the Doherty PA (DPA) architecture has been widely employed in wireless

<sup>&</sup>lt;sup>1</sup>This chapter was published as

Haifeng Lyu *et al.*, "Doherty-to-balanced Switchable Power Amplifier." 2019 IEEE MTT-S International Microwave Symposium June. 2019: 1339-1342.

Haifeng Lyu *et al.*, "Balanced-to-Doherty Mode-reconfigurable Power Amplifier with High Efficiency and Linearity against Load Mismatch." *IEEE Transactions on Microwave Theory and Techniques* 68(5) March 2020: 1717-1728.

communications infrastructures (e.g., base stations) due to its enhanced efficiency at significant power back-offs. Until now, numerous DPA techniques and demonstrations have been reported, exhibiting significant progress towards realizing highly efficient DPAs in various semiconductor technologies [3–9] together with extended application horizons, e.g., from single-band to multi-band [10–15] and from microwave frequencies to millimeter-wave frequencies [16–22].

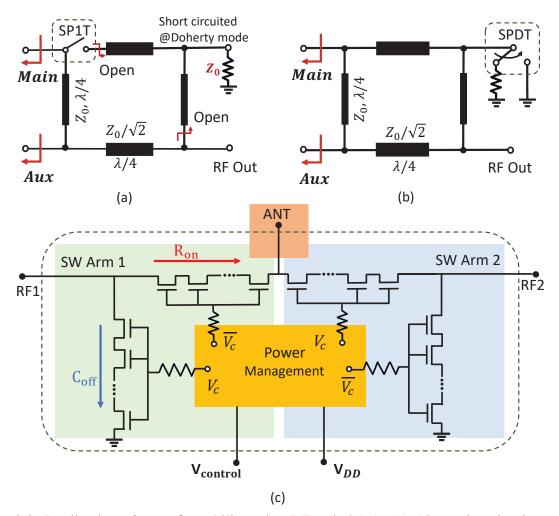

Figure 2.1: Conceptual architecture of the proposed B2D mode-reconfigurable power amplifier. A SOI-based SPDT switch terminates the isolation port of the output coupler to  $50-\Omega$  load and ground alternatively. (a) Balanced mode. (b) Doherty mode.

In realistic communications, due to the non-linear nature of DPAs, external linearization using digital pre-distortion (DPD) is usually applied to DPAs to maintain the transmission signal's fidelity and to comply with specific communications standards. In the future generations of wireless communications, e.g., 5G, the cell size is expected to be reduced significantly (e.g., from Marco cell to Micro/Femto cell) leading to much higher base-station densities and considerably lower power levels. Since DPD is quite energy consuming, especially when accommodating wide modulation bandwidths of signals [23], PAs at lowered power level are strongly desired to be intrinsically linear. Recently, several linear DPAs have been presented in terms of both theoretical analysis and practical design demonstrating enhanced linearity as well as high efficiency [24–27].

On the other hand, the spatial multiplexing/combining techniques, such as multi-input multi-output (MIMO) antennas and active antenna array, have been widely applied in the 5G communications to further increase the data rate, radiation distance, and overall system capacity. However, the mutual coupling between different antennas under concurrent MIMO transmissions and/or beam steering can lead to ongoing variation of antenna impedance at very fast time scales [28–31]. As a result, the current solution of discrete antenna tuners based on phase-detection and feedback control will in-all-likelihood not be able to seamlessly respond to such a rapid impedance variation [32]. Although the circulators/isolators can be placed between PA and antenna element, they introduce extra loss and are too costly and bulky for massive-array applications [29,31]. Therefore, the PAs in future communications systems are expected to maintain efficient and linear operations against substantial load mismatch by themselves. Different from the conventional impedance tuning method, new paradigms of mismatch recovery at PA stage have been investigated, such as specialized control of digital Doherty PAs against load variation [33] and direct impedance measurement using distributed sensors [34]. Until now, there has not been a solid solution that is able to cover a large impedance variation range and is readily compatible with the existing systems as a "drop-in" module.

To solve the aforementioned challenges, a balanced-to-Doherty (B2D) mode-reconfigurable PA is proposed in this paper, as conceptually illustrated in Fig. 2.1. The isolation port of the output coupler is alternatively terminated to  $50-\Omega$  load and ground to enable balanced mode and Doherty mode, as shown in the Fig. 2.1(a), (b) respectively, which can be physically realized by a single-pole double-throw (SPDT) switch. In our related conference paper [35], we have pre-

liminarily presented a proof-of-concept demonstration of the B2D reconfigurable PA. This paper significantly expands our previous works [35, 36] in the following aspects. **First**, a generalized theory of the quasi-balanced Doherty PA (Doherty mode of the B2D reconfigurable PA) is analyzed based on the ideal mathematical model of quadrature coupler, and it is analytically proven that the load modulation behavior of QB-DPA is equivalent to the conventional Doherty PA. This generalization inclusively explains and verifies the designs using branch-line hybrids in [35, 36]. **Second**, a systematical design methodology of the B2D PA is presented targeting for high linearity and efficiency at both the balanced and Doherty modes. Based on the QB-DPA theory and the proposed design methodology, a prototype is developed using GaN technology at 3.5 GHz demonstrating state-of-the-art DPA performance in terms of linearity and efficiency at the nominal  $50-\Omega$  load condition. **Third**, a comprehensive mismatch evaluation using modulated signals is experimentally presented. It is remarkably discovered that the linear and efficient PA performance can be well maintained up to 2 : 1 (predicted in typical MIMO operations [28, 37]) of voltage standing wave ratio (VSWR) by using B2D reconfiguration.

In actual MIMO systems [31, 38], the transmitter system performance (e.g., ALCR and EVM) is monitored in real time, and the PA can be adapted from QB-DPA mode to balanced mode when an abnormal linearity is detected. In phased-array applications, the impedance of each antenna element could be pre-characterized as a function of scan angle [31]. For a particular antenna element, the associated PA can be adapted according to scan angle. Envisioning these scenarios, the B2D adaption can be applied seamlessly without having to detect the phase and amplitude of mismatch.

### 2.2 Quasi-Balanced Doherty PA Theory

In this section, based on the new quasi-balanced Doherty PA (QB-DPA) configuration, the operation of active load-modulation is theoretically analyzed. In this circuit topology, the essential Doherty combining network is implemented using a specially configured quadrature coupler in a balanced amplifier topology, as illustrated in Fig. 2.1. In [39, 40], by leaving the isolation port of the branch-line coupler as open circuit, the possibility of implementation hybrid coupler as a output combining network for the DPAs is introduced. In this section, a new methodology of quadrature hybrid modularization is theoretical analyzed.

Assuming a system impedance of  $Z_0$ , the voltage and current relationship of the four-port coupler network can be expressed using an impedance matrix constructed with Z-parameters, given by

$$\begin{bmatrix} V_1 \\ V_2 \\ V_3 \\ V_4 \end{bmatrix} = Z_0 \begin{bmatrix} 0 & +j & -j\sqrt{2} & 0 \\ +j & 0 & 0 & -j\sqrt{2} \\ -j\sqrt{2} & 0 & 0 & +j \\ 0 & -j\sqrt{2} & +j & 0 \end{bmatrix} \begin{bmatrix} I_1 \\ I_2 \\ I_3 \\ I_4 \end{bmatrix}$$

(2.1)

To theoretically model this new type of DPA, a simplified output combining network is constructed based on an ideal 3-dB quadrature hybrid coupler model, as shown in Fig. 2.2, including the excitation and loading. The isolation port (Port 2) is terminated to ground, and the output port (Port 1) is loaded to a 50- $\Omega$  terminal. Two ideal current sources  $I_{\rm M}$  and  $I_{\rm A}$ , which represent main and auxiliary amplifiers, are connected to the two excitation ports (Port 4 and Port 3) of the coupler, respectively.

As the isolation port is grounded, the associated port voltage is thus zero. By applying this condition ( $V_2 = V_{Iso} = 0$ ) on the first row expansion of the matrix operation in Eq. 2.1, the dependence of the main amplifier current and load current can be determined by:

$$I_{\rm M} = \frac{\sqrt{2}}{2} I_0. \tag{2.2}$$

where  $I_M = I_4$  and  $I_0 = I_1$ . Meanwhile, the load current and voltage of the RF-output port can be expressed by

$$V_0 = -Z_0 I_0. (2.3)$$

In this design, to ensure reconfiguration between Doherty mode and balanced mode, the main PA and auxiliary PA in Doherty mode are identical in terms of the current/voltage scaling, because this symmetry has to be enforced in balanced mode. Nevertheless, the main and auxiliary PAs can be asymmetrical in Doherty-only designs based on this quasi-balanced configuration. The theoretical analysis on the QB-DPA operation is performed at both back-off and saturation.

### 2.2.1 QB-DPA Operation at 6-dB Power Back-off and Below

In the power region at 6-dB back-off and below, the equivalent circuit can be modeled as Fig. 2.2(a). As the auxiliary amplifier is turned off, it presents an ideal open circuit to Port 3 with no current injection from the auxiliary path ( $I_A = I_3 = 0$ ). With this boundary condition, the matrix operation in Eq. (2.1) can be re-written as

$$\begin{bmatrix} V_{0} \\ 0 \\ V_{A,bo} \\ V_{M,bo} \end{bmatrix} = Z_{0} \begin{bmatrix} 0 & +j & -j\sqrt{2} & 0 \\ +j & 0 & 0 & -j\sqrt{2} \\ -j\sqrt{2} & 0 & 0 & +j \\ 0 & -j\sqrt{2} & +j & 0 \end{bmatrix} \begin{bmatrix} I_{0} \\ I_{Iso} \\ 0 \\ I_{M,bo} \end{bmatrix}$$

(2.4)

where  $V_{\rm M,bo}$  and  $I_{\rm M,bo}$  denote the back-off voltage and current of the main amplifier, respectively, and  $V_{\rm A,bo}$  represents the voltage swing at the floating auxiliary amplifier port. By substituting the condition of  $I_{\rm A} = 0$  into the above matrix operation in Eq. (2.4), it leads to the following dependencies:

$$V_{\rm M,bo} = -j\sqrt{2}I_{\rm Iso}Z_0 \& I_{\rm Iso} = jI_0.$$

(2.5)

Together with Eq. (2.2), the impedance seen by the main and auxiliary amplifiers can be expressed as

$$Z_{\rm M,bo} = \frac{V_{\rm M,bo}}{I_{\rm M,bo}}$$

$$= \frac{-j\sqrt{2}I_{\rm Iso}}{I_{\rm M,bo}}Z_0$$

$$= 2Z_0,$$

$$Z_{\rm A,bo} = \infty.$$

(2.6)

From the above Eq. (2.6), it is interesting to note that this quasi-balanced DPA is functionally equivalent to the standard Doherty PA at the power back-off condition.

Figure 2.2: Generalized schematic of the output combining network for analyzing the proposed QB-DPA architecture at (a) 6-dB power back-off and below and (b) power saturation.

## 2.2.2 QB-DPA Operation at Power Saturation

At the saturated power level, both the main and auxiliary amplifiers are fully operating towards saturation of voltage and current so that the impedance matrix can be re-arranged as

$$\begin{bmatrix} V_{0} \\ 0 \\ V_{A,sat} \\ V_{M,sat} \end{bmatrix} = Z_{0} \begin{bmatrix} 0 & +j & -j\sqrt{2} & 0 \\ +j & 0 & 0 & -j\sqrt{2} \\ -j\sqrt{2} & 0 & 0 & +j \\ 0 & -j\sqrt{2} & +j & 0 \end{bmatrix} \begin{bmatrix} I_{0} \\ I_{Iso} \\ I_{A,sat} \\ I_{M,sat} \end{bmatrix}$$

(2.7)

Since the two amplifiers are designed identically, the saturation voltages and currents between the main and auxiliary path have the same magnitude. By conducting the matrix operation using Eq. 2.7, the following dependencies are formed

$$I_{\rm M,sat} = j I_{\rm A,sat} \& I_{\rm Iso} = 0.$$

(2.8)

The 90° phase difference between the  $I_{\rm M}$  and  $I_{\rm A}$  is due to the ideal 3-dB quadrature-coupler divider at the input. It is also interesting to note that the isolation port becomes an electrical "null" in this condition, since it has zero voltage and zero current, simultaneously. Based on Eqs. (2.3) and (2.8), the load impedance seen by the main amplifier, i.e.,  $Z_{\rm M,sat}$ , can thus be calculated using the associated saturation voltage,  $V_{\rm M,sat}$ , and current,  $I_{\rm M,sat}$ , given by

$$Z_{M,sat} = \frac{V_{M,sat}}{I_{M,sat}}$$

$$= \frac{jI_{A,sat} - j\sqrt{2}I_{Iso}}{I_{M,sat}}Z_0$$

$$= Z_0.$$

(2.9)

For the auxiliary path, the exhibited load  $Z_{A,sat}$  can be derived as

$$Z_{A,sat} = \frac{V_{A,sat}}{I_{A,sat}}$$

$$= \frac{jI_{M,sat} - j2I_{M,sat}}{I_{A,sat}}Z_0$$

$$= Z_0.$$

(2.10)

Eqs. (2.9) and (2.10) underline that the quasi-balanced DPA operation at saturation level is again equivalent to a standard DPA.

The load modulation behaviors of the main and auxiliary PAs at both power back-off and power saturation reveal a remarkable discovery: when loading the isolation port of the output quadrature coupler to ground, the balanced PA can be fully converted into an ideal Doherty PA. This finding not only enables PA reconfiguration between Doherty and balanced modes, but it also exhibits promising potential of the quasi-balanced DPA for extension to wideband implementations, since the balanced amplifier configuration is considered bandwidth-friendly by nature [41], [42].

2.3 Practical Design Methodology of Linear B2D Mode-Reconfigurable PA

Figure 2.3: Systematic design flow of the B2D mode-reconfigurable PA.

The derivation described in the previous section shows the possibility of converting a balanced PA to an ideal Doherty PA by terminating the isolation port of the output coupler to ground. Based upon the proposed theory, the design methodology of linear balanced-to-Doherty mode-

reconfigurable PA is presented in this section. It is worth noting that the two standalone PAs in the QB-DPA architecture should be designed identically and, thus, the device periphery ratio is equalized between the main and auxiliary transistors. The flowchart in Fig. 2.3 describes the detailed design procedure, which includes the following key steps:

• Step 1: Determination of  $P_{\text{Max}}$ . The maximum power is usually determined by the target application in which the maximum rated power ( $P_{\text{Rated}}$ ) is specified by the particular communications standard.  $P_{\text{Rated}}$  can be approximately expressed as

$$P_{\text{Rated}} = P_{1\text{dB}} - \text{PAPR.} \tag{2.11}$$

where  $P_{1dB}$  is the 1-dB compression point, and PAPR represents the peak-to-average ratio of the modulated signal. In this linear PA design,  $P_{Max}$  is selected to allow sufficient headroom for linear amplification of modulated signals. In real-world implementations, this  $P_{Max}$  is physically realized by properly selecting semiconductor technology and transistor size.

- Step 2: Loadline Selection. Since the balanced mode requires two amplifier branches to be fully symmetrical, the loadlines of main and auxiliary amplifiers are identically selected  $(Z_M = Z_A)$ . A full power utilization transistor designed in Step 1 is ideally associated with a unique load impedance for a particular class of PA which generates optimized power and efficiency, which can be determined using load-pull at the operation frequency. However, the linearity is usually not optimal following the conventional load-pull evaluation. Given the fact that PA linearity is the key factor in determining whether a system is compliant to a certain communication standard, the possible impedance selection (at both fundamental and harmonic frequencies) in this design is prioritized for linearity with a meanwhile balance for efficiency, gain, and power.

- Step 3: Matching Networks Design. After determining the optimal loadline, the output

matching network is designed to physically realize the target impedance at both fundamental and harmonic frequencies. It is important to note that the output matching network (OMN) also plays an important role in determining the load modulation behaviors of main and auxiliary PAs in Doherty mode [24], which needs to be co-designed with the coupler-based combiner for achieving efficient and linear performance in Doherty mode. The source impedance can also affect the PA gain and linearity. A conjugate match is desired for maximized gain, while a slight mismatch (if properly designed) can lead to optimized linearity [43]. Therefore, the input matching network design should take into account both aspects, and a compromise is necessary. To enforce the symmetry of balanced mode, the IMN and OMN are designed identically for the two amplifiers.

- **Step 4**: *Bias Selection for Balanced Mode.* In the balanced mode, the two PAs are biased identically for both gate and drain. Therefore, the behavior of the entire balanced amplifier can be treated the same as a standalone PA. In addition to the loadline impedance, the PA linearity profile across the entire power range is also strongly influenced by the gate bias level of the main transistor. Empirically, the PA is biased at Class-AB mode to yield a good balance between efficiency and linearity, and a bias sweep can be performed to eventually determine the value.

- Step 5: *Bias Selection for Doherty Mode.* In the Doherty mode, the main and auxiliary amplifiers are biased in Class-AB and Class-C, respectively. The linearity and efficiency are highly dependent on the combination of these two bias voltages, because the turn-on point of auxiliary PA determines the back-off efficiency, while the interaction (i.e., load modulation) between main and auxiliary PAs dominates the AM-AM and AM-PM profiles. Therefore, the bias voltages are carefully selected based on a nearly exhaustive search to identify an optimal combination. If the linearity requirement cannot be met, we need to revisit the loadline selection and conduct the process from **Step2**.

Overall, the design method considers the PA performance of both Doherty and balanced modes in terms of linearity, efficiency, power, gain, etc. It is important to emphasize that if the linearity can be maintained in both modes, the B2D reconfiguration can greatly extend the operation space of the PA into a large variation of load impedance, as the balanced amplifier has been well proven to be insensitive to load mismatch [41, 42].

Figure 2.4: Simulation results of the standalone PA at 3.5 GHz. (a) Normalized AM-PM. (b) DE and gain.

#### 2.4 Prototype Design and Demonstration

The methodology presented in the above Section 2.3 is implemented to design and realize a prototype of the proposed balanced-to-Doherty mode-reconfigurable PA with high efficiency and enhanced linearity at both balanced mode and Doherty mode. In this design, two 6-W GaN packaged transistors CGH40006P from Wolfspeed are utilized as the power device of a PA operating at a center frequency of 3.5 GHz.

Figure 2.5: Designed output combiner network with device parasitics. The inset Smith chart illustrates the desired dynamic load trajectories at package plane for the main and auxiliary amplifiers.

Figure 2.6: Linearity- and efficiency-optimized designs of QB-DPA (Doherty mode of B2D PA). (a) Normalized AM-PM. (b) DE and gain.

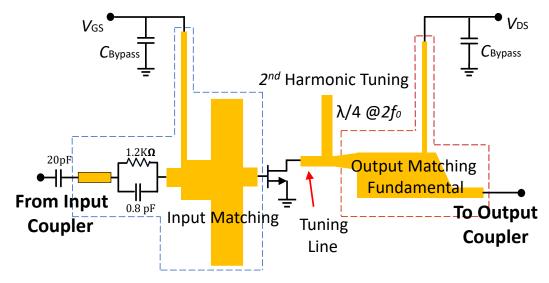

### 2.4.1 Design of the Standalone GaN PA

A load-pull simulation was conducted using the selected transistor model with ADS for the standalone PA, in which the device parasitics have been taken into account. At the device package plane, the optimal load impedances for fundamental and second harmonic for this design were chosen to be  $13 + j9 \Omega$  and  $j65 \Omega$ , respectively, in order to allow for an optimal linearity to meet

Figure 2.7: Comparison of simulated drain dc currents between the balanced mode and Doherty mode.

the communication standard. To physically realize the target fundamental and harmonic terminations, a 2nd harmonic trap is properly designed together with synthesized fundamental matching using a stepped multi-section transmission-line (TL) matching network which also absorbs the drain bias line.

The design of input matching network (IMN) for the standalone PA is targeted for perfecting the linearity performance without considerably compromising the gain capability. Practically, the desired source impedance of the transistor is extracted from the source-pull simulation, while a slight mismatch is carefully conducted in the IMN design in order to achieve an enhanced AM-PM. Meanwhile, a Class-AB mode of gate bias was selected for achieving a balance of linearity and efficiency consideration. The linearity profile of the designed standalone PA is shown in Fig. 2.4, including a linearized AM-PM profile which is normalized with respect to the small-signal value in Fig. 2.4(a) and a flat AM-AM profile (gain versus output power) in Fig. 2.4(b). The complete design of the standalone PA exhibits an efficient performance at 3.5 GHz with a simulated maximal

Figure 2.8: Overall schematic of the designed B2D mode-reconfigurable PA with an implemented SOI-based SPDT switch.

drain efficiency (DE) of 80% towards power saturation, as depicted in Fig. 2.4(b).

#### 2.4.2 Design of B2D Reconfigurable PA with Optimized Efficiency and Linearity

Based upon the initial design of the standalone PA, a linear and high efficiency balanced amplifier is formed by coupling two such PAs with 90° of phase offset through two quadrature couplers as the input power splitter and output combiner, respectively. Due to its highly symmetrical characteristics, a balanced PA presents the same linearity characteristic as a single standalone PA with doubled output power.

As the isolation port is short circuited to ground, the operation of the B2D PA is reconfigured to Doherty mode by enabling of the switch. Due to the parasitics of the transistors resulting from the GaN chip and package as shown in Fig. 2.5, the desired load trajectory can deviate from the optimal path, which could be exacerbated especially when the effect of OMN and output combiner are taken into consideration. This may eventually lead to a degradation of linearity and efficiency. In order to perfect the load modulation behavior, a co-design of the OMN and combiner is essential,

Figure 2.9: Realization of reconfigurability using RF switch(es). (a) Alternative circuit topology with a single switch. (b) Design using a SPDT switch. (c) Schematic of the SOI-COMS SPDT switch.

and a global optimization is performed with the overall circuit schematic following the procedure depicted in Section 2.3. The finalized schematic of B2D reconfigurable PA is shown in Fig. 2.8 including the parameters of all the circuit components.

Moreover, an optimal biasing combination of main and auxiliary PAs is carefully chosen for perfecting linearity as exhibited in Fig. 2.6. In this linearity optimized mode, a linear AM-PM can be achieved with  $< 2^{\circ}$  of variation from low power to  $P_{1dB}$  shown in Fig. 2.6(a). Meanwhile, a flat

Figure 2.10: Investigation on output combiner efficiency (insertion loss). (a) Effect of switch  $R_{on}$  resistance for shorting the isolation port in Doherty mode. (b) Over 2:1 VSWR circle in Doherty mode  $R_{on} = 3 \Omega$ . (c) Over 2:1 VSWR circle in balanced mode.

AM-AM is also realized, as depicted in Fig. 2.6(b), while achieving a saturation efficiency as high as 80% and a 62% efficiency at 6-dB power back-off. The back-off efficiency can be further improved with a different bias setting oriented for optimized efficiency, while slightly compromising the linearity. This mode can be applied when digital pre-distortion (DPD) is available. Meanwhile, an extended 9-dB power back-off dynamic range can be achieved with a properly adjusted drain biases of main and auxiliary amplifiers in QB-DPA mode.

The power-dependent DC currents of main and auxiliary amplifiers are shown in Fig. 2.7. It is observed that the auxiliary current rises sharply after turning on, and it reaches to the same level as the main amplifier current in saturation region. This is mainly due to the strong expansion behavior of GaN device under Class-C bias condition. This is achieved with an equal input power split ratio

Figure 2.11: Top view of the fabricated circuit board.

using the quadrature coupler. In comparison with balanced mode, the saturation currents are the nearly the same due to the saturation of two sub amplifier, while the QB-DPA mode significantly reduces the current consumption at power back-off.

## 2.4.3 Qudrature Coupler and RF Switch Implementations

The reconfigurability of this B2D PA is realized with the implementation of a quadrature coupler and an RF switch. For the single-section branch-line hybrid coupler used in this design, there is an alternative topology to realize the switchable B2D combiner, as shown in Fig. 2.9(a), in which a single switch is placed between the main amplifier node and the top quarter-wave branch line. An open circuit needs to be created by the switch to enable Doherty mode. This open circuit can be converted to short circuit at the isolation node through the top  $\lambda/4$  TL, bypassing the 50- $\Omega$  resistor and eventually presenting an open circuit towards the RF output port. However, among commercially available switch devices including MEMS, SOI, PIN diode, etc., such a "pure" open circuit can only be realized using MEMS switch which is not widely available now, and the power handling of MEMS devices is a general concern for high-power applications especially under high load mismatch.

Therefore, this demonstration design follows the default topology (Fig. 2.9(b)) where a SPDT switch is placed at the isolation port to alternately enable connection to the 50- $\Omega$  loading and ground. A commercial SOI-based RF switch (SKYA21003) is utilized as the SPDT, which consists of three ports: antenna (ANT), RF1, and RF2. As the switch topology shown in Fig. 2.9(c), the ANT port is connected to the isolation port of the output coupler, while the RF1 and RF2 ports are terminated to the 50- $\Omega$  loading and ground, respectively. Between ANT and RF ports, two switch arms are connected and controlled by a management unit. In the "ON" state, the switch introduces certain series resistance, i.e.,  $R_{on}$ . To model this effect, a switch model with 3- $\Omega R_{on}$  is established based on [44], and the switch is co-simulated with the QB-DPA. It is interesting to note that such an  $R_{on}$  does not lead to considerable impact on the QB-DPA performance, as shown in Fig. 2.6(b). The simulation results verifies the feasibility of this default switch design topology. It is interesting to note that, for a typical multi-throw SOI switch, there is typically a shunt arm at each switch port which shorts the node to ground at "OFF" state leading to an improved isolation. Thus, this type of switch cannot offer a complete open circuit at "OFF" state, which cannot be used in the first switchable combiner topology in Fig. 2.9(a).

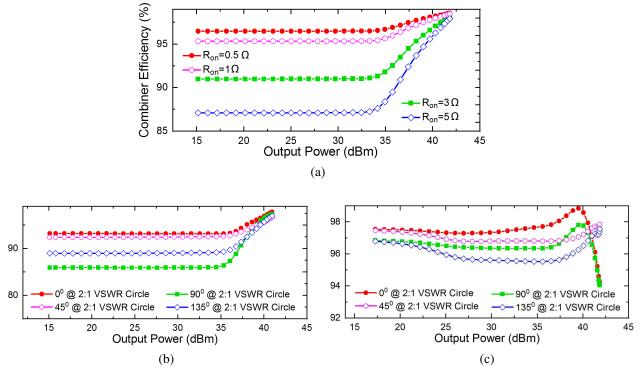

The overall insertion loss of the quadrature coupler under dynamic PA operation is further studied, as shown in Fig. 2.10. To fully evaluate the switch effect on insertion loss, the combiner loss in the form of passive efficiency is extracted from large-signal Harmonic Balanced simulation. The passive combiner efficiency versus output power of Doherty mode is shown in Fig. 2.10(a). At

saturation power, the value of switch  $R_{on}$  has negligible impact to insertion loss, since the isolation port is an electrical "null" as mathematically proven. Meanwhile, the increase of  $R_{on}$  leads to higher loss at power back-off. In the mismatch condition as shown in Figs. 2.10(b) and (c), the balanced mode leads to better combiner efficiency compared to Doherty mode.

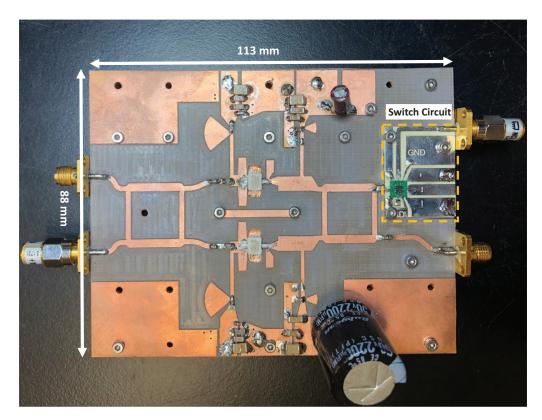

## 2.4.4 Fabrication

The overall layout is generated from circuit schematic, and it is modeled using 3D electromagnetic simulator. The EM model is then co-simulated with active components, and the layout is optimized until the co-simulation results match the schematic-only case. The fabricated B2D PA is shown in Fig. 2.11 which is developed on the Rogers 5880 substrate, and the entire PCB is mounted on a copper substrate and fastened using screws. The RF switch module is placed on another small PCB board, and it is mounted on the same copper substrate with RF connection to the isolation node of the output quadrature coupler. By applying different bias setting of the switch control, the ANT port of the SPDT switch can be routed to RF1 (ground) and RF2 (50- $\Omega$  termination) alternatively.

#### 2.5 Measurement Results and Analysis

#### 2.5.1 Continuous-Wave Measurement

In the Doherty-mode measurement, the gate bias of the main device is primarily set to -2.6 V in Class-AB in order to improve the linearity at low power range. The auxiliary gate bias voltage is set to -4.5 V for linearity-optimized operation. A proper combination of bias setting can generate complimentary non-linear behaviors of main and auxiliary amplifiers that cancel each other leading to enhanced linearity of the overall Doherty PA, as reported in [45]. In the balanced-mode measurement, the two PAs are biased identically in Class AB with  $V_{\rm GS} = -2.5$  V for primarily

optimized linearity.

Figure 2.12: Measured DE and gain of Doherty mode and balanced mode.

Figure 2.13: Measured frequency response of (a) DE and (b) gain at saturation and 6-dB OBO for both Doherty and balanced modes.

#### 2.5.2 Modulated Measurement for Nominal 50- $\Omega$ Termination

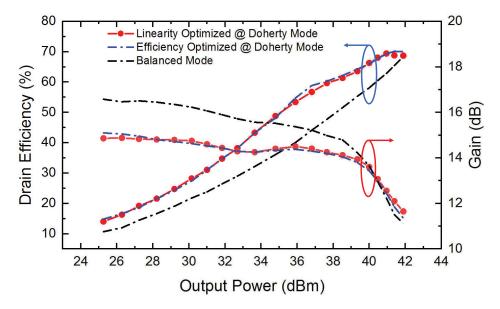

Fig. 2.12 shows the measured drain efficiency, gain versus the output power at different operation frequencies of the B2D reconfigurable PA, driven by a power-swept Continuous-Wave (CW)

Figure 2.14: Two-tone measurement centered at 3.5 GHz. (a) IMD3 of Doherty and balanced modes with 5-MHz tone spacing. (b) IMD3 of Doherty mode with variable tone spacing.

Figure 2.15: Measured modulated signal at Pout = 34.5 dBm without DPD. (a) 16-QAM constellation diagram corresponding to an efficiency of 42.4%. (b) Normalized PSD for a 10-MHz LTE signal at 3.5 GHz.

stimulus at balanced mode and Doherty mode respectively. A desired Doherty profile is experimentally obtained in Doherty mode. The measured gain at center frequency 3.5 GHz is around 14 dB at low-power range, and it remains almost flat up to  $P_{1dB}$ . Such an AM-AM behavior ensures a good linearity of the Doherty mode. The efficiency and gain of balanced mode are also plotted in Fig. 2.12. A higher gain is achieved in balanced mode given the fact that there is no turn-off

Figure 2.16: Measured modulated signal versus average output power. (a) DE and Gain. (b) EVM and ACPR.

of auxiliary PA wasting half of the input power at low-power region, which also leads to a better backoff-efficiency behavior at Doherty mode. The measured efficiency at  $P_{\text{Max}}$  is almost the same for both Doherty and balanced modes at the operating center frequency due to the identical loadline at saturation region. Fig. 2.13 illustrates the frequency response of the B2D across 3.4 - 3.6 GHz. In Doherty mode, at peak output power, the measured drain efficiency is 64%-70% and the gain is 9.5 - 11.35 dB, whereas, at 6-dB OBO, the measured gain and drain efficiency are 12.1 - 14.4dB and 46%-55%, respectively. The balanced mode experiences a decent performance in terms of drain efficiency and gain as well.

#### 2.5.3 Two-Tone Measurement

The third-order intermodulation (IMD3) is measured with two-tone stimulus at a center frequency of 3.5 GHz to evaluate the linearity of the designed B2D PA. Due to the innate characteristic of soft saturation, the balanced mode presents a slight IMD3 degradation as compared to the Doherty mode near the saturation region, where the Doherty PA experiences a clear gain expansion (see Fig. 2.12). Nevertheless, the overall IMD3 of balanced mode remains below -30 dBc with frequency spacing of 5 MHz for output power lower than 39 dBm, as can be seen from Fig. 2.14(a).

Figure 2.17: An illustrative measurement setup for characterization of the B2D modereconfigurable PA under nominal  $50-\Omega$  and mismatch (2 : 1 VSWR) loading conditions. Inset Smith chart presents a system-level operation scenario when the B2D PA switches between Doherty and balanced modes to maintain the optimized performance over load variation.

Meanwhile, the Doherty-mode PA maintains a low IMD3 (i.e., < -35 dBc) across a large power range from saturation to 10-dB back-off, which is crucial to achieve linear amplification of high-PAPR modulated signals. As the frequency spacing increases to 10 MHz, 20 MHz and 40 MHz, according to Fig. 2.14(b), a low IMD3 of Doherty mode is maintained with minimum deviation of lower and upper IMD3 components. This indicates that the memory effect is well suppressed when amplifying high-bandwidth signals.

To evaluate the efficiency and linearity performance of the B2D PA in realistic communication scenarios, a modulated measurement using an LTE signal with 10 MHz bandwidth and 8.4 dB PAPR is performed. A Keysight PXIe vector transceiver (VXT M9421) is used as modulated signal generator and analyzer. The generic LTE signal is then boosted by a pre-amplifier (ZHL-5W-422+) to a sufficient level for driving the PA. The measured power spectral density (PSD) and error vector magnitude (EVM) are presented in Figs. 2.15(a) and (b), respectively. The designed

Figure 2.18: Measurement of reconfigurable mode B2D PA under 2 : 1 VSWR over entire phase range. (a) EVM. (b) Output power. (c) Average DE.

B2D PA presents an average efficiency of 42.4% and ACPR around -37 dBc at a rated average output power of 34.5 dBm without any DPD applied. A low corresponding error vector magnitude (EVM) of 2.36% is measured in this condition, as shown in Fig. 2.15(b).

The PA is further tested using a power-swept LTE signal with the same modulation, and the drain efficiency and gain versus the average output power are plotted in Fig. 2.16(a). The profile of EVM and ACPR are presented as well in Fig. 2.16(b). It can be seen that the EVM versus  $P_{\rm out}$

profile agrees well with the two-tone measurement when tone spacing is at 10 MHz. Based on the measurement in Fig. 2.16, the designed Doherty mode PA maintains a low EVM below 3.5% and a raw ACPR between -33.8 and -41.8 dBc over a large power range from 27.5 to 35.6 dBm, while the corresponding average efficiency is between 20% and 45%.

This design exhibits a state-of-the-art PA performance as compared to other contemporary linear GaN-based PAs published recently, as listed in Table 2.1. The Doherty mode of the proposed B2D PA offers a very competitive efficiency and linearity at the maximum rated output power, which well verifies the effectiveness of the proposed QB-DPA theory.

#### 2.5.4 Reconfigurable-Mode Measurement under Load Mismatch

To experimentally demonstrate the reconfigurable operation, the designed B2D PA is evaluated with the same LTE modulated signal (used in Sec. 2.5.2) under load mismatch at a constant VSWR of 2 : 1. Using the measurement system setup in Fig. 2.17, the PA output is connected to a mismatched load which covers the 2 : 1 VSWR circle on Smith Chart with the phase swept at  $30^{\circ}$  step. This is physically realized using a 2 : 1 transformer in series with a series of transmission lines with different electrical lengths.