### University of Tennessee, Knoxville TRACE: Tennessee Research and Creative Exchange

**Doctoral Dissertations**

**Graduate School**

12-2022

### Hardware for Memristive Neuromorphic Systems with Reliable Programming and Online Learning

Ryan Weiss rweiss2@vols.utk.edu

Follow this and additional works at: https://trace.tennessee.edu/utk\_graddiss

#### **Recommended Citation**

Weiss, Ryan, "Hardware for Memristive Neuromorphic Systems with Reliable Programming and Online Learning." PhD diss., University of Tennessee, 2022. https://trace.tennessee.edu/utk\_graddiss/7703

This Dissertation is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a dissertation written by Ryan Weiss entitled "Hardware for Memristive Neuromorphic Systems with Reliable Programming and Online Learning." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Electrical Engineering.

Garrett Rose, Major Professor

We have read this dissertation and recommend its acceptance:

Nicole McFarlane, Andrew Sarles, Aziz Ahmedullah

Accepted for the Council:

Dixie L. Thompson

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

# Hardware for Memristive Neuromorphic Systems with Reliable Programming and Online Learning

A Dissertation Presented for the

Doctor of Philosophy

Degree

The University of Tennessee, Knoxville

Ryan John Weiss

December 2022

© by Ryan John Weiss, 2022 All Rights Reserved.  $Dedicated\ to\ my\ family\ who\ have\ loved\ and\ supported\ me\ through\ this\ journey.$

## Acknowledgments

I would like to thank my advisor Dr. Garrett S. Rose for his dedication and support in the completion of my Phd at the University of Tennessee. I would also like to thank the members of my doctoral committee Dr. Nicole McFarlane, Dr. Andy Sarles, and Dr. Ahmedullah Aziz for serving on my committee and for their support and time. I could not have achieved this without the support of the TENN-lab research team. Thank you to everyone who has helped make this a possibility.

### Abstract

Alternative computing technologies are highly sought after due to limitations on transistor fabrication improvements. Fabricated memristive technology allows for a non-volatile analog memory for neuromorphic computing. In an integrated CMOS process, the synapse circuits designed for a spiking neuromorphic system can use memristors to regulate accumulation in the neuron circuits. Testing the fabricated memristive devices composed of hafnium oxide and developing a model to represent the key device characteristics lead to specific design choices in implementing the analog memory core of the synapse circuit. The circuits I designed for neuromorphic computing in this process take advantage of the unique capabilities of the memristive device to store a programmable analog memory reliably and efficiently. I designed the peripheral circuitry required including the circuits for programming the memristor and for online learning capabilities.

## Table of Contents

| 1 | Intr | roduction                                        | 1  |

|---|------|--------------------------------------------------|----|

|   | 1.1  | Motivation                                       | 1  |

|   | 1.2  | Research Goal                                    | 4  |

|   | 1.3  | Research Contribution                            | 4  |

|   | 1.4  | Dissertation Overview                            | 6  |

| 2 | Bac  | kground                                          | 8  |

|   | 2.1  | Nano Electronic Devices                          | 8  |

|   | 2.2  | Memristor Theory and History                     | 12 |

|   | 2.3  | Fabricated Hafnium-Oxide Memristors              | 14 |

|   | 2.4  | Alternative Memristors                           | 17 |

|   | 2.5  | Neuromorphic Computing Framework                 | 19 |

|   | 2.6  | Synapse and Neuron Circuits                      | 21 |

| 3 | Mei  | mristor Model                                    | 26 |

|   | 3.1  | Experimental Results for Hafnium-Oxide Memristor | 26 |

|   | 3.2  | Memristor Model                                  | 30 |

|   |      | 3.2.1 Set Operation                              | 32 |

|   |      | 3.2.2 Reset Operation                            | 35 |

| 4 | Mei  | mristive Synapse Circuit                         | 42 |

|   | 4.1  | Analog Synapse with Memristor for Weight Storage | 42 |

|    | 4.2   | Synapse Circuit                         | 43 |

|----|-------|-----------------------------------------|----|

|    |       | 4.2.1 Memristor Cell                    | 43 |

|    |       | 4.2.2 Synapse Output                    | 48 |

|    |       | 4.2.3 Current Control                   | 52 |

|    | 4.3   | Weight Programming                      | 52 |

|    | 4.4   | Reference Feedback Circuit              | 54 |

|    | 4.5   | Online Learning                         | 60 |

|    | 4.6   | Synapse Conclusion                      | 63 |

| 5  | Net   | iron                                    | 66 |

|    | 5.1   | Integrate and Fire Neuron circuit       | 66 |

|    | 5.2   | Axon Hillock Neuron                     | 69 |

|    | 5.3   | Neuron Model                            | 69 |

| 6  | Dev   | vice Testing and Circuit Simulation     | 72 |

|    | 6.1   | Hybrid CMOS memristor wafer             | 72 |

|    |       | 6.1.1 Hafnium Oxide testing and results | 73 |

|    |       | 6.1.2 Forming                           | 73 |

|    |       | 6.1.3 Switching characteristics         | 75 |

|    |       | 6.1.4 Cycle Variability                 | 75 |

|    | 6.2   | Circuit simulation                      | 82 |

|    | 6.3   | Test structures                         | 82 |

|    | 6.4   | Test Cores                              | 89 |

| 7  | Sun   | nmary                                   | 93 |

|    | 7.1   | Future Work                             | 94 |

| Bi | bliog | graphy                                  | 97 |

| Α  | Abł   | previations 1                           | 07 |

| В  | Test | t Struc | ctures                              |       | 108   |

|----|------|---------|-------------------------------------|-------|-------|

|    | B.1  | Test S  | Structure Procedures                | • • • | . 108 |

|    |      | B.1.1   | First Test Structures               | •••   | . 108 |

|    |      | B.1.2   | Second Test Structures              | • • • | . 113 |

|    |      | B.1.3   | Third Test Structures               | •••   | . 116 |

|    |      | B.1.4   | Fourth Test Structures              | •••   | . 119 |

| С  | Ver  | ilog-A  | Code for Memristor and Neuron Model |       | 123   |

|    | C.1  | Memri   | istor Model                         | • •   | . 123 |

|    | C.2  | Neuro   | n Model                             | •••   | . 129 |

| Vi | ta   |         |                                     |       | 133   |

## List of Tables

| 1.1 | VLSI synapse implementations.                                   | 5   |

|-----|-----------------------------------------------------------------|-----|

| 2.1 | Nonvolatile memory devices                                      | 11  |

| 3.1 | Fitting parameters for memristor model.                         | 41  |

| 4.1 | High voltage transistor connected to memristor size and voltage | 46  |

| 4.2 | Area estimates for synapse components.                          | 65  |

| 4.3 | Energy usage for synapse circuits.                              | 65  |

| 4.4 | Energy usage for STDP circuits.                                 | 65  |

| 7.1 | Energy comparison for synapse circuits                          | 95  |

| B.1 | Pad frame for test structure 1 pad names                        | 10  |

| B.2 | Pad frame for test structure 2 pad names                        | 15  |

| B.3 | Pad frame for test structure 3 pad names                        | 18  |

| B.4 | Pad frame for test structure 4 pad names                        | .20 |

## List of Figures

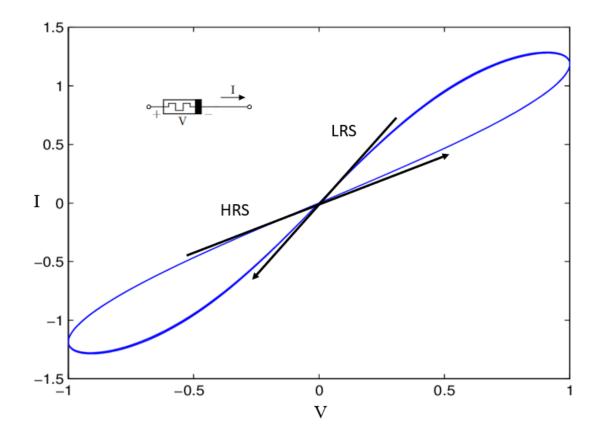

| 2.1 | An ideal I-V sweep of a memristor showing device symbol, LRS and             |    |

|-----|------------------------------------------------------------------------------|----|

|     | HRS.Adapted from [72]                                                        | 13 |

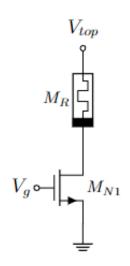

| 2.2 | One transistor one memristor circuit adapted from [53]                       | 16 |

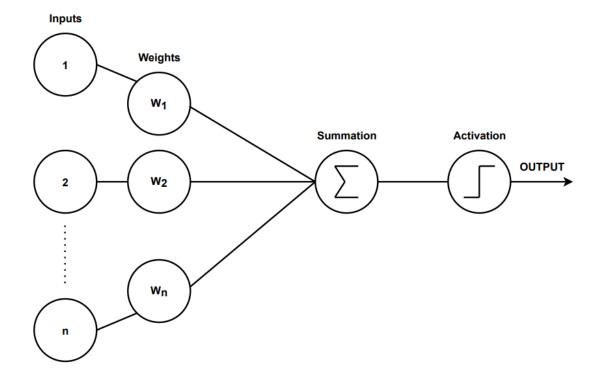

| 2.3 | Single perceptron showing weighted inputs, summation, and output activation. | 20 |

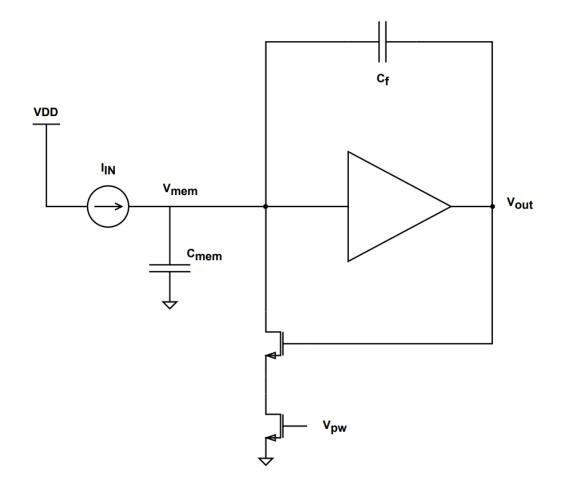

| 2.4 | Original axon hillock neuron circuit [28, 40]                                | 23 |

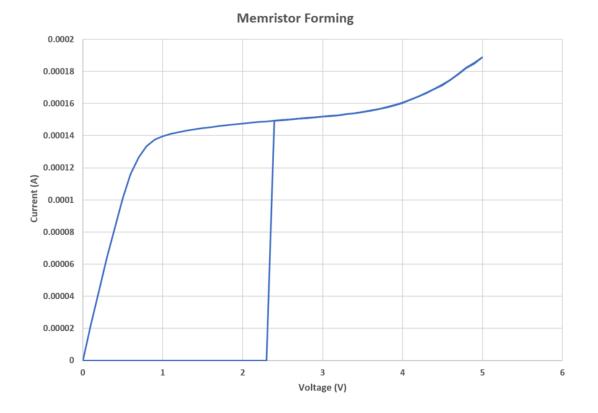

| 3.1 | Voltage sweep of unformed hafnium-oxide memristor with conductive            |    |

|     | filament forming at 2.3 V                                                    | 28 |

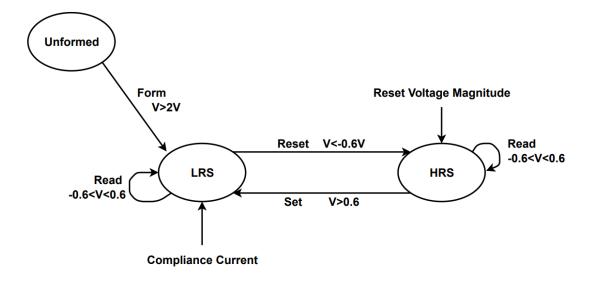

| 3.2 | Flow state diagram of hafnium-oxide memristor                                | 31 |

| 3.3 | Diagram of hafnium-oxide memristor resistance movement                       | 31 |

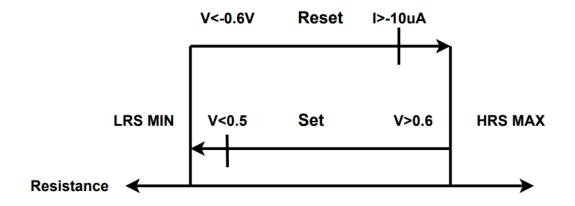

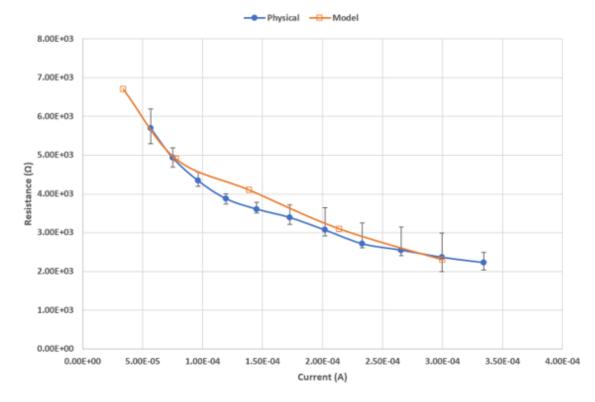

| 3.4 | Model vs. Physical tested device set resistance at different currents        | 34 |

| 3.5 | Model vs. Physical tested device calculated voltage across device during set |    |

|     | at LRS.                                                                      | 36 |

| 3.6 | Model vs. Physical tested device reset resistance at different voltages      | 38 |

| 3.7 | Model vs. Physical tested device calculated current through the device       |    |

|     | during reset at HRS.                                                         | 39 |

| 3.8 | Model vs. Physical tested device I-V sweep results                           | 41 |

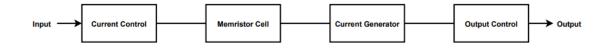

| 4.1 | Block diagram of Synapse circuit.                                            | 44 |

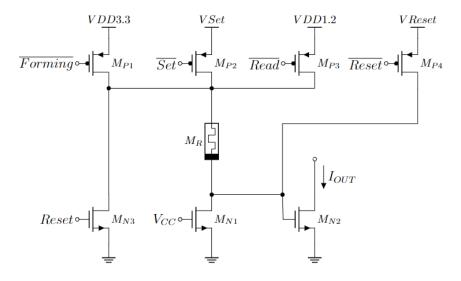

| 4.2 | Circuit depicting the memristor and transistors directly connected to it     | 44 |

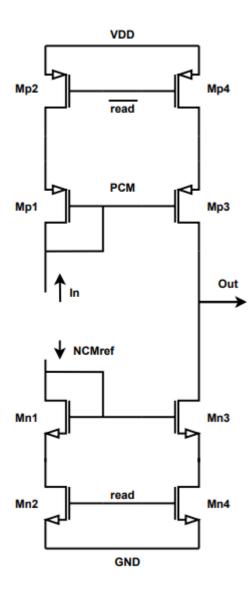

| 4.3 | Synapse output buffer circuit.                                               | 49 |

| 4.4 | Block diagram of the output control circuit.                                 | 51 |

| 4.5  | Current control circuit for read reference generation adjustment             | 53 |

|------|------------------------------------------------------------------------------|----|

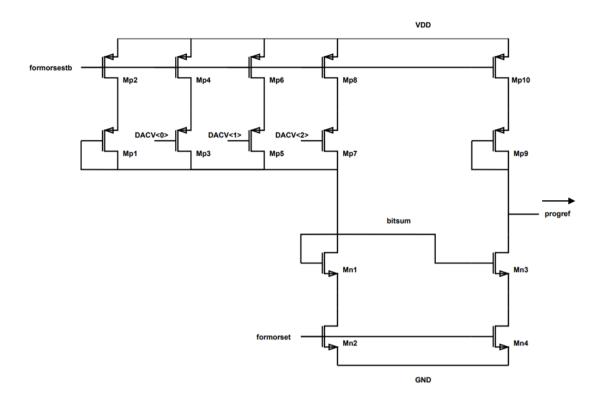

| 4.6  | Current steering DAC for programming.                                        | 55 |

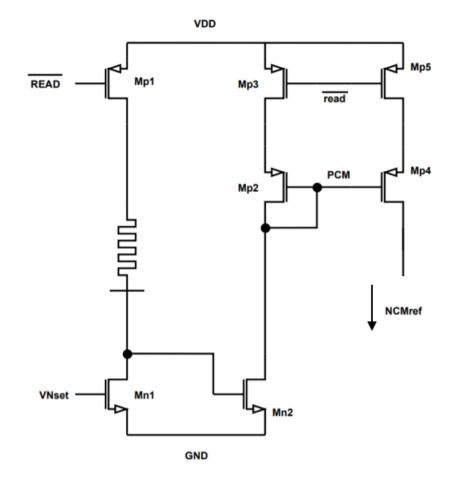

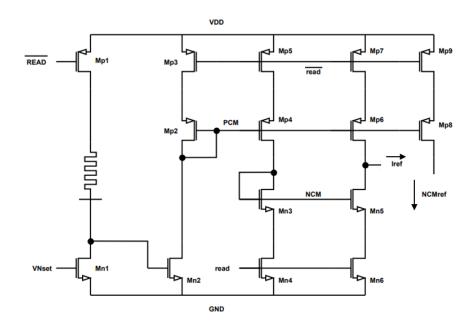

| 4.7  | Memristor reference generator circuit                                        | 56 |

| 4.8  | Memristor reference generator circuit                                        | 58 |

| 4.9  | Current reference feedback control circuit block diagram                     | 58 |

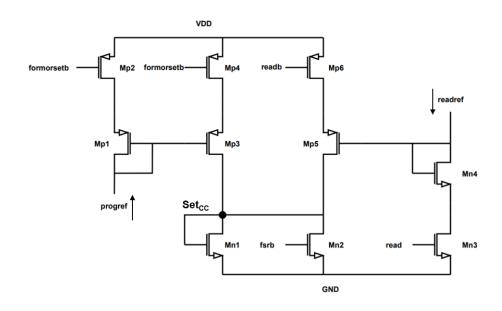

| 4.10 | Current reference feedback control circuit.                                  | 59 |

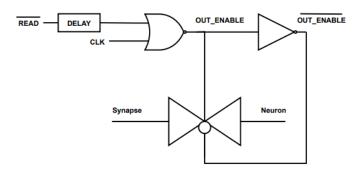

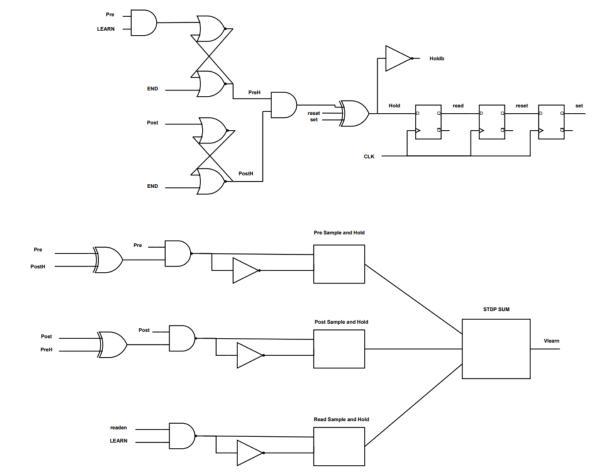

| 4.11 | Block diagram for STDP circuit                                               | 61 |

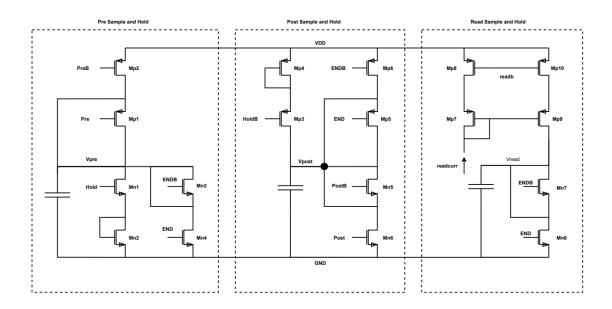

| 4.12 | Sample and hold circuit.                                                     | 62 |

| 4.13 | STDP summation circuit.                                                      | 62 |

| 5.1  | Integrate and Fire neuron [71]                                               | 68 |

| 5.2  | Synchronous axon hillock neuron [70]                                         | 70 |

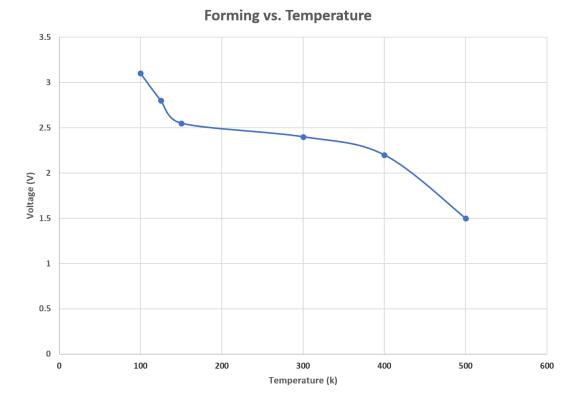

| 6.1  | Averaged forming voltage at different temperatures                           | 74 |

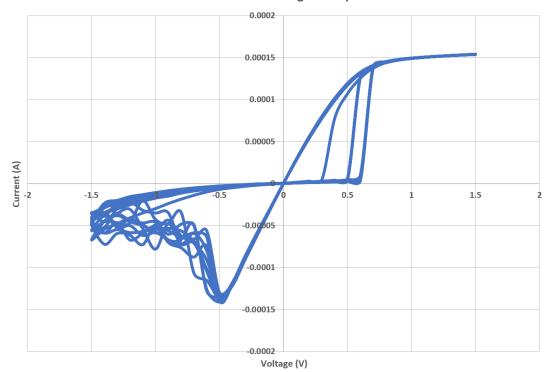

| 6.2  | I-V sweep for set and reset operations.                                      | 76 |

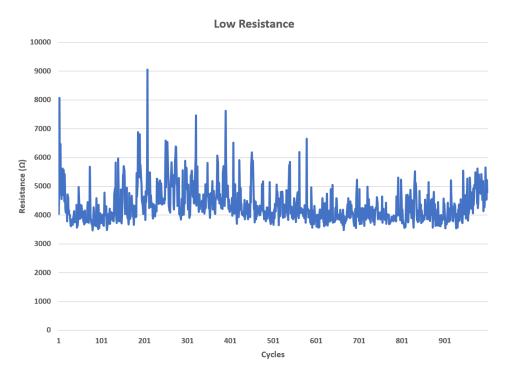

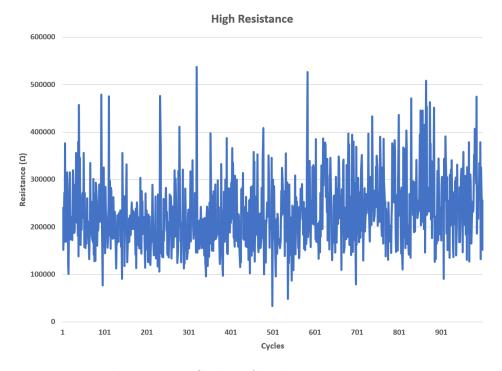

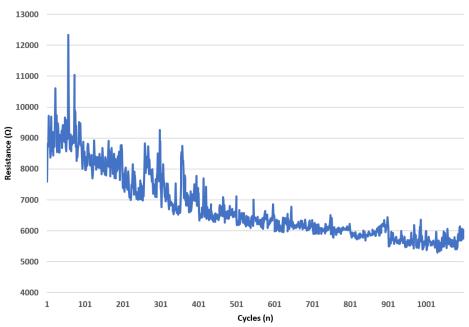

| 6.3  | Cycles of low resistance states                                              | 77 |

| 6.4  | Cycles of high resistance states.                                            | 77 |

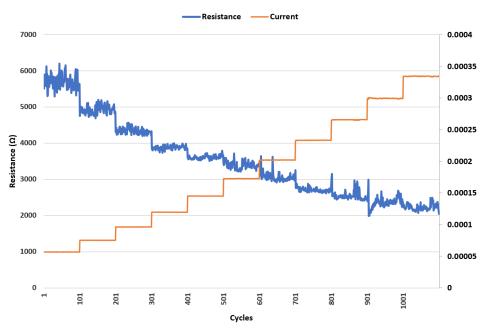

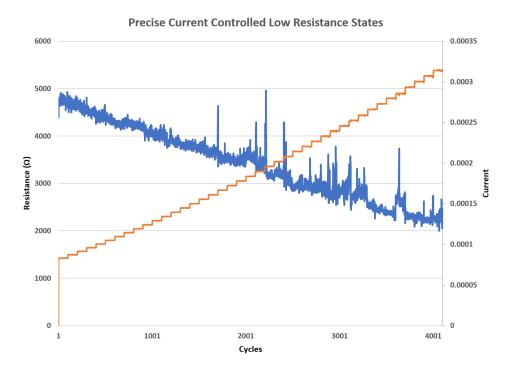

| 6.5  | Increasing current limitation to achieve multiple low resistance states      | 79 |

| 6.6  | Higher precision increasing current limitation to achieve almost continuous  |    |

|      | low resistance states                                                        | 81 |

| 6.7  | Current based read for low resistance states                                 | 81 |

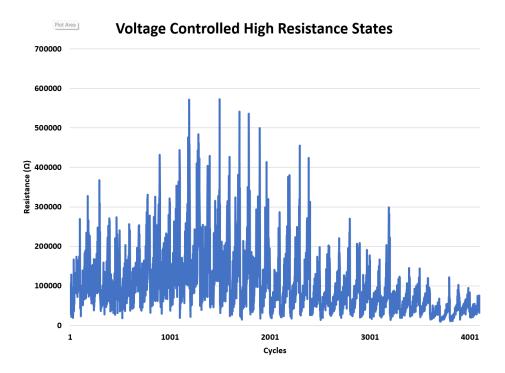

| 6.8  | High resistance states from variable reset voltages                          | 83 |

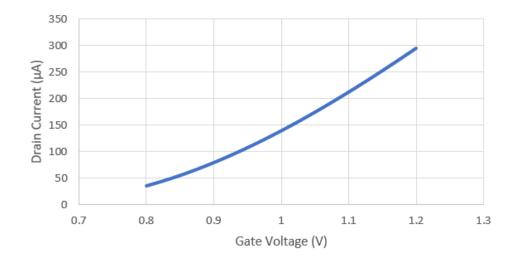

| 6.9  | Expected current from gate voltage in 1T1R in Memristor Cell.                | 85 |

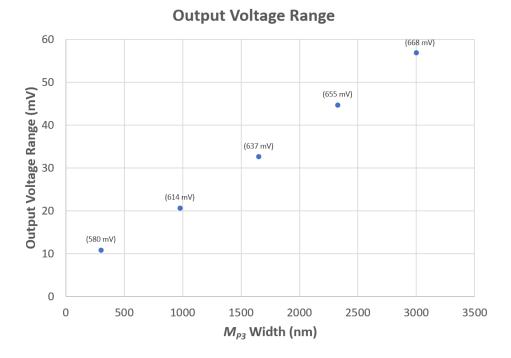

| 6.10 | Maximum output voltage range at best case voltage for different widths.      | 85 |

| 6.11 | Simulation showing the different expected voltages for the current control   |    |

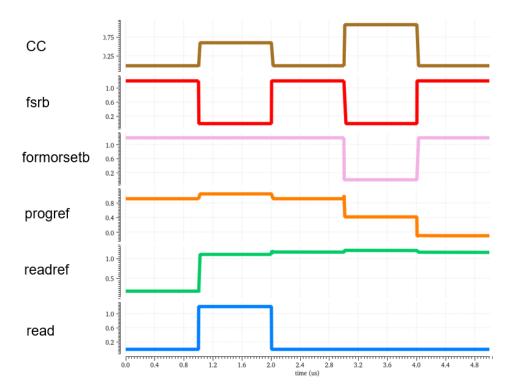

|      | circuit                                                                      | 87 |

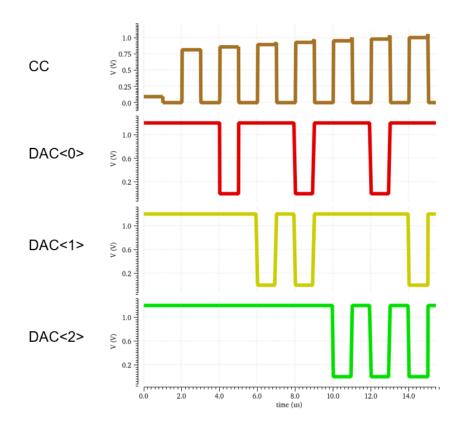

| 6.12 | Simulation showing the different expected voltages for the 3 bit DAC         | 88 |

| 6.13 | Simulation showing the voltage time relationships of the reference generator |    |

|      | working with a synapse and neuron.                                           | 88 |

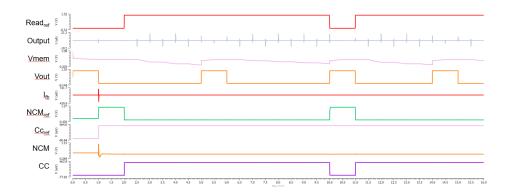

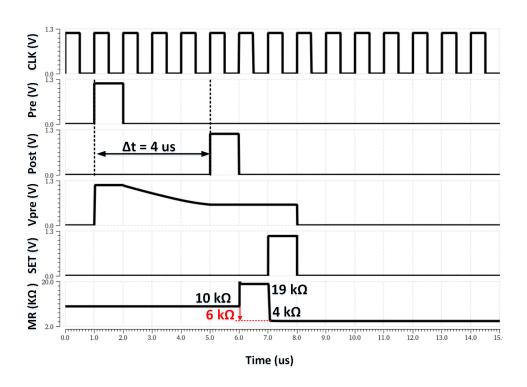

| 6.14 | Simulation showing the voltage time relationships for a potentiation | 90 |

|------|----------------------------------------------------------------------|----|

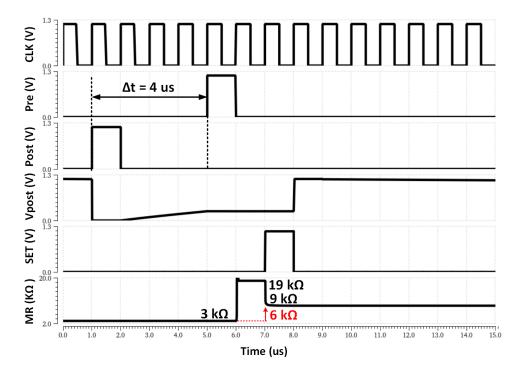

| 6.15 | Simulation showing the voltage time relationships a depresion        | 90 |

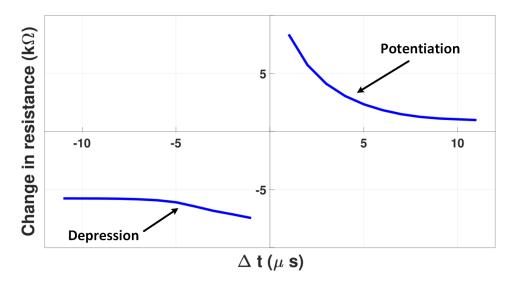

| 6.16 | STDP curve showing decrease in magnitude change for neuron activity  |    |

|      | spacing                                                              | 91 |

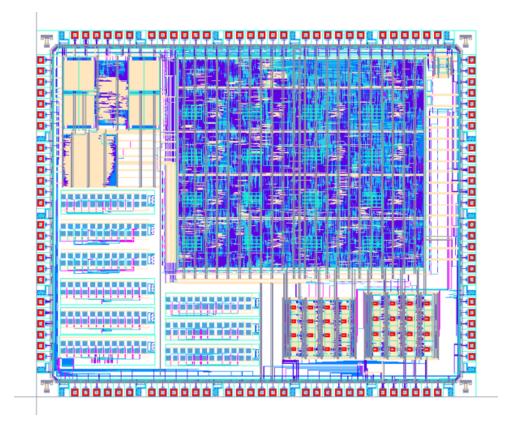

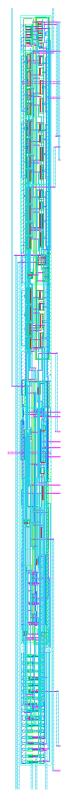

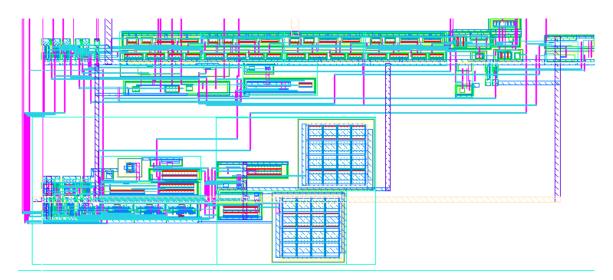

| 6.17 | Layout image of full RAVENS wafer.                                   | 92 |

|      |                                                                      |    |

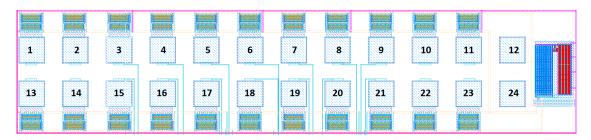

| B.1  | Pad frame for test structure circuits                                | 09 |

| B.2  | Test structure 1 circuit layout image                                | 09 |

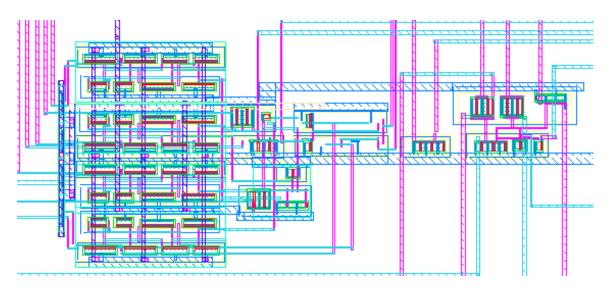

| B.3  | Test structure 2 circuit layout image                                | 14 |

| B.4  | Test structure 3 circuit layout image                                | 17 |

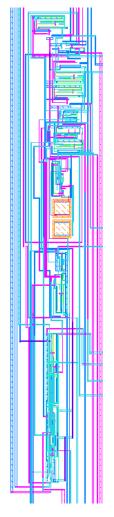

| B.5  | Test structure 4 circuit layout image                                | 21 |

## Chapter 1

## Introduction

#### 1.1 Motivation

The computer is a tool to ease human effort in solving difficult problems. The need for a device that allowed for consistent and quick computation led to the eventual invention of the modern computer. Advancements in computing have continued to improve their capabilities and increased the range of possible problems to solve. While the standard digital computer is capable of solving many problems and continues to improve, varying limitations are slowing the advancement [62]. The continued increase in the number of transistors on chip is going to cease as manufacturing smaller transistor feature sizes becomes increasingly more difficult [74]. The feature sizes of silicon transistors are reaching physical limitations as manufacturing closes in on the atomic size of silicon atoms. Photo-lithography, the technique used to produce transistors on silicon, attempts to continue to reduce feature sizes in silicon, but faces increasing challenges in engineering and cost [63]. Moore's law states the transistor count on chip doubling every two years [37]. The premise of this law implies improvements in computing technology are achieved through increased transistor count. While increasing available transistors can improve computing, the effective use of the available electronic devices can also be improved. Continued effort

in increasing device density will coincide with alternative computing paradigms to enhance future computing technology.

In conjunction with difficulties in increasing computing performance, potential power consumption is relatively increasing. Dennard scaling states the power consumption for smaller technology nodes stays equal to previous technology nodes due to equivalent decrease in necessary voltage and currents for new technology nodes [11]. This no longer holds as feature sizes continue to decrease. For continually decreasing transistor sizes, leakage power is increasing while supply voltage and clock frequency are stagnating. The increase leakage current is due to effects like reverse bias junction currents, bandto-band tunneling current, and tunneling into gate oxide [55]. Many of these sources of leakage become prevalent in deep sub micron processes due to the macro model of silicon transistors breaking down. The quantum effects of electrons allows currents to flow unintentionally. The increase in leakage current compounds negative effects due to thermal runaway into account. One option is slowing down operating frequency. With the increase in embedded battery powered processors, power is a key factor in improving computing systems.

The modern computer uses digital memory and logic to implement processing. The von Neumann architecture that dominates existing computers has a separation of main memory and the processing unit [82]. The separation of processing and memory requires a data bus to transfer the information required by the processor from the memory storage system. Improving computing technology with this architecture requires increased bus performance, otherwise the data sent across the bus will be a bottleneck for processing. To eliminate the potential von Neumann bottleneck, computing architectures can implement processingin-memory computing. Processing-in-memory computing poses significant challenges in topological designs. This process of bringing computing to the memory adds additional difficulty in designing algorithms [64]. Another technique to improve computing capabilities beyond von Neumann architectures is quantum computing. Quantum computing consists of an entirely different paradigm to computing that relies on quantum physics to produce the correct solution to a problem. Quantum computing requires a set of instructions using quantum bits to solve problems. The ability to design quantum computers posses challenges in resilience to environmental noise [16]. These alternatives to the standard computing architecture posses difficulties in both programming and circuit level design.

An architecture for improving computing technology through bio-mimicry is neuromorphic computing. Brain inspiration in computing considers biological processes for naturally accomplished computing and implements equivalent functions in artificial systems [39]. The biological brain efficiently uses high density of cells for computation [13]. Mimicking brain functionality has the potential to solve computing challenges with low power cost. Through the use of neurons and synapses, the brain is a computing system that builds in features to learn and improve functionality. The adaptability inspired by biological functions creates possibilities for this architecture to outperform traditional computing systems [22]. The biological functions performed by the brain are also analog in nature. Analog computing was overtaken by digital computing due to the lack of precision. The neuromorphic computing can take advantage of the brain's nature by build highly efficient analog circuits.

Alongside improvements to transistor technology, other devices have been developed for computing. The memristor is a two terminal element that can store information as a resistance on previous usage [15]. The memristor has potential as a memory storage element to fit into the neuromorphic framework as an adaptable analog memory unit [34]. The ideal device would have an infinite life cycle of a continuous analog range of resistive memory states. Practically, there are challenges with fabricated memristor devices [33]. As manufacturing technology improves the devices, the circuits that utilize them can be further optimized and tailored to the devices. For neuromorphic computing the memristor and similar devices show potential to implement the plasticity of biological functions. Two of the main components of neuromorphic computing, synapses and neurons, when implemented using analog circuits have the need for an adaptive analog memory element. For synapses, the memristor can fit in as a direct representation. The synapse controls the efficiency of communication between neurons, and the memristor can be used as the representation of that connection. Changes in synaptic efficiency are then directly correlated with changes in the resistance of the memristor. To implement memristors as synapses, circuits needed to control and utilize them are needed. The characteristics of the memristor make them suitable for use in an analog neuromorphic system [79].

#### 1.2 Research Goal

Neuromorphic computing can take advantage of the unique properties of the memristor to implement analog memory circuits. In this work, I study the key characteristics of the integration of a hybrid CMOS-memristor VLSI process to develop circuits for neuromorphic computing. The fabrication of on-chip memristors in-line with a CMOS process allows for large scale integration of memristive neuromorphic systems-on-chip (SOC). To implement the memristive neuromorphic SOC, all aspects of the fabrication of the memristors and their utilization are taken into account. The goal of this research is to build the circuits for a reliable and programmable integrated memristor-CMOS fabrication process. The design is grounded in tested results of the devices used.

This work explores the idea of current compliance for programming and implements an online learning technique that is commonly adapted for these circuits. Table 1.1 shows the common usage of memristors and similar devices as memory elements in neuromorphic computing. The methods to program the devices allow for the online learning functionality. This work utilizes circuitry required for the device's basic operations to implement the programming and online learning capabilities seen in this field.

#### **1.3** Research Contribution

The research contributions are enumerated below:

|           | Memory Type | Programming        | Online Learning |

|-----------|-------------|--------------------|-----------------|

| This work | Memristor   | Current Compliance | STDP            |

| [1]       | Memristor   | Pulse Shaping      | STDP            |

| [77]      | Memristor   | Pulse Count        | STDP            |

| [25]      | Memristor   | Pulse Shaping      | STDP            |

| [30]      | PCM         | Pulse Shaping      | STDP            |

Table 1.1: VLSI synapse implementations.

- A simple compact model for the memristor that highlights the relationship of current and voltage on the device. The model takes into account the device response to signals that fully change the updated resistive state.

- A memristor circuit using fabricated on-chip memristors that can perform all necessary functions to use the device as an analog memory. The functions include: forming, set, reset, and read.

- A low-power, low-complexity read out operation based on current limitation for the memristor.

- A current control system for implementing current control for both programming and read out of the memristor.

- A current generating circuit for the memristor to act as a synapse to output current into a neuron.

- A current steering digital to analog conversion circuit to allow for current programming of the memristor.

- A reference generation circuit using a memristor to create a range of output currents for the synapse circuit.

- An online learning circuit to implement spike timing dependent plasticity using the current control programming of the memristor.

#### 1.4 Dissertation Overview

In this dissertation, I will describe the design of analog neuromorphic circuits using memristors. The goal of this work is to show circuits that efficiently use the device technologies available while providing insight into other potential devices and techniques. The core analog circuits used here for neuromorphic computing are designed to utilize the memristive devices. Testing results from the devices led to particular design choices for efficient plastic synapse and neuron circuits. I have implemented a particular flavor of synapse circuit to utilize the devices available. The synapse is designed to take advantage of the characteristics of the memristor device for simple and reliable programming and updating. It is also designed for low area and power cost. The programming technique stems from the physically tested results and is effectively modelled for simulation [36].

## Chapter 2

## Background

#### 2.1 Nano Electronic Devices

The motivation of brain inspired computing leads to different technological needs than standard computing. The potential advantages of neuromorphic computing stems from a highly dense and interconnected memory system. One long term memory is the synapses ability to manage the communication of information between neurons. The activity of the neurons can alter their connected synapses to improve computing performance. The ideal memory for this system is fabricated at high density, representing the value of synaptic strength, and is easily adjustable. In implementing neuromorphic computing, stored values are not required to be digitally precise as neural networks can tolerate a degree of noise. This allows the use of analog circuits, and specifically analog memory elements to implement neural circuits. Analog circuits can implement some mathematical functions efficiently, for example adding to values represented as currents on a wire is accomplished by connecting the wires together. An analog value can be converted from a digital system using a digital to analog converter, but this will require area and power to represent and convert the value. Improving upon this, an analog memory can be created using a multitude of devices, including standard silicon. A standard silicon process is important due to the ease of integrating the memory with the processing circuits. Floating gate

transistors can be used to implement the analog memory in neuromorphic computing using a standard CMOS process [17]. The need for a highly dense analog memory has led to the development of alternative types of non-volatile memory devices. Such analog memory devices for neuromorphic computing include memristors, phase change materials, spintronics, and ferroelectric FETs [68].

Phase change material, or PCM, offers analog memory storage and updating. PCM are made of chalcogenide materials, which are made from one chalcogen and one electropositive element. Chalcogens are in the same family as oxygen in the periodic table of elements. An example PCM device is a stack of Ag, Ag<sub>2</sub>Se, and Ge<sub>2</sub>Se<sub>3</sub> [49]. The chalcogenide material used in these devices changes phase between amorphous and crystalline giving a continuous range of resistance values [48]. These devices can be used to mimic a synaptic learning rule, STDP [66]. The temperature effect on the memory of the device adds additional challenges to efficiently pack in a large amount of synapses on chip [51, 52]. Scaling up the number of devices on chip is a challenge due to high programming current. The resistance in the amorphous state is unstable and varies over time. The device endurance is limited by the number of times the resistance is increased. Systems using this device take in special considerations to reduce the number of resistance increases, control temperature and current levels.

Spintronic devices also called magnetic tunnel junctions, MTJ, use a three layer structure. The layers consist of two magnetic layers with an-oxide layer in between [69]. One magnetic layer is fixed, and the other is free. The free layer can be parallel or antiparallel magnetization relative to the fixed layer, with each orientation yielding a different resistance value. These devices have a programmable resistance range and can achieve synaptic plasticity like STDP. However, the resistance range can be as small as 5  $\Omega$ [32]. A small ratio between the highest and lowest resistance states requires more precise circuitry to detect the different states. These devices require low power to operate, but have high switching times. They have long endurance because the switching mechanism does not require location changes to atoms. However, these devices require improvements in variability and scalability.

A ferroelectric field-effect transistor, FeFET, is a three terminal device similar to a metal-oxide-semiconductor field-effect transistor, MOSFET. Unlike a MOSFET, a FeFET uses a ferromagnetic layer instead of the highly resistive gate-oxide. The properties of FeFET devices are similar to MOSFET, but the ferromagnetic gate layer allows for a programmable channel conductivity [45]. These devices show a wide resistance range and fast programmability. They have symmetric switching for increasing and decreasing channel conductivity. They require large area. Decreasing area and improving scalability generates problems with leakage current, reliability, manufacturing, energy consumption, and sensing capability. They are charge-based memory and suffer from leakage similar to DRAM [44].

The transition metal-oxide memristor, or TMO, is a two terminal device consisting of a switching layer made from a depleted-oxide layer sandwiched between two electrodes. The device stores analog memory states by growing and rupturing a metallic conductive filament through the metal-oxide layer. The composition of the switching layer and the electrodes play a key factor in determining the switching characteristics. A key concern with TMO devices is the variability due to filament growth and rupture [23, 24]. The devices are scalable with a high resistance ratio, but improve the variability to a tolerable level in neuromorphic computing can worsen the switching characteristics. This issue will be addressed in this work by implementing circuits to operate the device by controlling filament growth. The goal is to remove variability due to filament growth by actively controlling the process. The trade off is reducing the resistance range to only filament formed resistances.

These devices are all under active research. The best candidate for neuromorphic computing is yet to be determined. All the device types show the minimum requirements, which are the ability to store an analog memory. Table 2.1 shows the best reported values for key characteristics, not necessarily from the same exact device, adapted from [81].

| Device        | Operating | Power | Size                 | Resistance | Switching         | Endurance |

|---------------|-----------|-------|----------------------|------------|-------------------|-----------|

|               | Voltage   |       |                      | Ratio      | times             | cycles    |

| Memristor     | 0.3V      | 55fj  | $4 nm^2$             | 10^6       | $300 \mathrm{ps}$ | 10^12     |

| PCM           | 0.9V      | 100fj | $100 \mathrm{nm}^2$  | 10^5       | $300 \mathrm{ps}$ | 10^12     |

| Ferroelectric | 0.9V      | 1fj   | 25000nm <sup>2</sup> | 10^6       | 10ns              | 10^5      |

| Spintronic    | 1V        | 1fj   | $800 \text{nm}^2$    | <10^1      | 1ns               | 10^15     |

Table 2.1: Nonvolatile memory devices

From this table, there is no clear winner. The devices suffer from different set backs, including temperature, resistance range, and leakage. To further explore these devices for neuromorphic computing they must be implemented with the rest of the system. This includes all the circuits for controlling the synapses, programming, plasticity, connectivity, and the neurons. The circuits designed for the neuromorphic processor using these devices take into account their specific device properties to best utilize them. This work focuses on the hafnium-oxide memristor. The circuit techniques used to create a neuromorphic component of the device can potentially be applied to other devices if they show similar properties.

#### 2.2 Memristor Theory and History

The memristor has been termed the fourth basic circuit element among electronic devices [15]. Resistors, capacitors, and inductors link current and voltage, charge and voltage, and current and flux, respectively. The theoretical memristor device links flux and charge [15]. The resulting property from this definition creates a controllable state for the resistance of the device that is built on the history of device operation. The ability to hold information representing previous usage of the device is why the device is called a memristor, a term short for "memory resistor". The resulting phenomena of linking flux and charge gives way to variations of resistance from the history of the applied voltage or current. In a current versus voltage graph, this is characterized by a hysteresis loop seen in Figure 2.1. The high and low resistance switches. This idea of a memory in resistance was only theoretical for many years. The theory of a resistance holding memory based on previously applied voltages or currents led to the possibility for other devices to exhibit similar properties. Aside from memristors that can vary in resistance based on previous usage, memcapacitors

**Figure 2.1:** An ideal I-V sweep of a memristor showing device symbol, LRS and HRS.Adapted from [72]

and meminductors are other possible devices that story a state based on previous usage [76]. These memory devices pose challenges in fabrication but show potential for circuit applications.

#### 2.3 Fabricated Hafnium-Oxide Memristors

The memristor was first fabricated in 2008 [65]. Different materials have been used with varying results for potential memory applications. The transition metal-oxide memristor, TMO, is one type of memristor which has shown great results and promise for inline fabrication in CMOS processes. The key characteristics for different applications vary slightly. For this work, an analog resistive memory is allows for analog computation, reducing area and power.

The fabricated device used in this process is a made of hafnium-oxide, a transition metaloxide memristor. It has characteristics suitable for analog memory [10]. The resistance of the device can vary from below  $10 \,\mathrm{k\Omega}$  to over  $100 \,\mathrm{k\Omega}$  [36]. The common operations for using these devices fabricated in silicon includes forming, setting, and resetting. The forming operation is a one time requirement to initialize the device [7]. Before forming the device is in a very high resistive state. Forming generates the conductive filament by applying a high voltage on the device [21]. The set and reset operations are used to change the resistance value of an already formed device. The reset operation occurs when a voltage is applied with the opposite polarity to the forming voltage. The high resistance state, HRS, achieved through the reset operation has high variability, ranging from  $10 \,\mathrm{k}\Omega$  to  $1 \,\mathrm{M\Omega}$  in some devices [21]. The set process generates a low resistance state, LRS, ranging from  $100\,\Omega$  to  $1\,\mathrm{k}\Omega$  in those devices [21]. The devices used in this work have shown HRS ranges from  $10 \,\mathrm{k\Omega}$  to  $300 \,\mathrm{k\Omega}$  and LRS range from  $2 \,\mathrm{k\Omega}$  to  $30 \,\mathrm{k\Omega}$  [53]. A binary application greatly benefits from separating the maximum possible resistance and minimum possible resistance, as it is detecting the correct state is more likely. Analog applications require programming into intermediate states, preferable a continuous range from the highest to

lowest resistances. Achieving specific resistance values and a continuous range between HRS and LRS is theoretically possible, but presents challenges in accurately hitting target resistances. The set and reset operations decrease and increase the resistance, respectively. The reset operation for the fabricated hafnium-oxide memristors can achieve varying resistance by varying the voltage applied to the device or by varying the time the voltage is applied [10]. The low resistance state can vary by controlling the current through the device [36]. The low resistance state is achieved in under 100 ps while the high resistance state is achieved in 100 ns [10]. The magnitude difference in time required to fully set and reset the device implies pulses with opposite polarity will not result in equal resistance changes. The greater time to fully reset allows for incremental pulse based switching, but those pulses will not work with the set operation. Also, the variability in change per pulse increases as the resistance increases. Pulse programming works for these hafnium memristors when in a low resistance state and staying near the low resistance state. The voltage applied to the memristor during reset also controls the maximum high resistance state achieved when fully reset. Due to the difference in the set and reset operations, equal increment and decrement in resistance with opposite polarity voltage pulses is not feasible. Therefore, the circuit is designed to use one repeatable and consistent resistance change method.

The method used for this design takes advantage of the low resistance state of the device and the properties of the set process. During forming and set a transistor is used to limit the current through the device. Figure 2.2 shows the one transistor one memristor, 1T1R, circuit using a n-type transistor. These memristor circuits sometimes refer to the device as a ReRAM, hence the R in 1T1R. The voltage  $V_{top}$  is positive for forming and set and negative for reset operations. The voltage  $V_g$  sets the saturation current, which limits the voltage through the memristor. For forming and setting the device, the current limiting transistor is necessary to achieve switching. Unlimited, the memristor can be permanently stuck in the low resistance state. Since the current limiting transistor is a necessary, the programming method reuses it to control the resistance. Changing the

Figure 2.2: One transistor one memristor circuit adapted from [53].

resistance after forming is achieved by resetting the device into its high resistance state, and once in the high resistance state, the device is then set into the low resistance state. The low resistance state is controlled with  $V_g$  and can achieve a range of resistance values [36]. Using a transistor to limit the current, via the saturation current, shows the low resistance state achieved varies by a few kilo ohms. The current limitation from a transistor in saturation is accomplished by holding the gate at a specific voltage.

#### 2.4 Alternative Memristors

Aside from hafnium-oxide, other types of transition metal-oxides can be used to create a memristor. Other TMO memristors include tantalum-oxide, titanium-oxide, and niobium-oxide [19]. These memristors have different values for properties such as their HRS, LRS, and switching voltages. One of the drawbacks of the hafnium-oxide memristor is the asymmetric switching characteristics. The titanium-oxide memristor does not exhibit the same difference in magnitude between the set and reset switching time [43]. However, these devices require a higher voltage for switching that is incompatible with deep submicron 65 nm CMOS process. These devices also have lower endurance [43]. Finding the best material for creating the memristor layer in a CMOS process is an ongoing area of fabrication research. Ideally the device has high endurance, is CMOS compatible, has a wide continuous, easily achievable resistance range, and is easily fabricated.

There are other devices to consider for different applications due to their different properties. Volatile memristors, or second order memristors, are a class of device that exhibit similar properties to the memristors considered in this work, in that they have definable states due to previously applied voltage and resistance, but these states decay fairly quickly over time. Practically, the volatile device can be programmed into a new state, but will shortly regress to its base condition. This has applications in timing specific circuits or thresholding circuits [6]. The insulator-metal transition memristor, IMT, is a type of memristor similar to the non-volatile TMO, except the resistance change is volatile. The devices work by Joule heating where heating causes a drop in resistance followed by a quick cool down over time, resetting the change in resistance. This can be made from NbO<sub>2</sub> or VO<sub>2</sub> [80]. Research considering IMT devices show promise for theses devices as selectors [50] and potentially as neurons [75]. The devices switch from HRS to LRS when a high voltage is applied due to thermal energy. When the resistance is low, the temperature cools off and the device goes back to a high resistance state. This can work as a threshold for a neuron to activate, or a selector for a synaptic array, but is not equivalent to the nonvolatile TMO for a synaptic device that provides long term memory storage.

The dipole-induced bilayer, DIB, has exhibited properties similar to biological functions [47, 38]. This device is created by a lipid membrane formed when lipid filled water droplets are submerged in oil. The lipids have hydrophobic tails that coat the outside of the water droplet and cause two droplets to not coalesce when brought into contact. Instead the tails of the lipids form a layer that resembles a cell membrane. The droplets can then be doped with voltage controlled peptides. The droplet system without any additives shows a memcapcitive effect due to the change in geometry of the bilayer. The additives create memristive behavior due to the insertion mechanics of the peptides causing a change in resistance. These changes in capacitance and resistance are not permanent, but are also not entirely instantaneous voltage dependant. For both the change in capacitance and change in resistance properties, there is a timing element, were the devices returns to its original state after the voltage is removed. This can be used to store the timing information in synaptic plasticity functions such as spike rate dependent plasticity, SRDP, or spike timing dependent plasticity, STDP [47]. These devices show promise as low power synaptic mimics with dynamic resistance changes to stimuli. They have been connected to an artificial neuron circuit [71]. The circuits have to take into special consideration to not damage the device and fabrication is not inline CMOS compatible.

#### 2.5 Neuromorphic Computing Framework

Neuromorphic computing architecture is one of the most effective alternatives to the existing von-Neumann architecture for certain applications. There are multiple neuromorphic computing frameworks including Intel Loihi and IBM TrueNorth [8, 18]. These computing architectures use biological inspired components to achieve high efficiency in implementing brain-like functions. The advantages of neuromorphic computing are not yet fully understood, but the systems show promising results for reducing power and resources needed to solve problems such as constraint satisfaction problems 3. Neural networks, the key component to implementing neuromorphic computing, has many flavors. Artificial neural networks, ANN, such as multilayer perceptrons are a feed-forward network. An example single layer with a single output is shown in Figure 2.3. The layers consisting of weighted inputs sum together and activate the output. MLPs are trained with gradient descent. This type of neural network strays heavily from biology. Spiking neural networks, SNN, are event based. These neural networks use timing information of activity not present in ANNs. The computing functionality is realized with two brain inspired components, neurons and synapses. The functions of these basic cells as they relate to information processing is a significant unsolved problem. There are a multitude of properties relating to the biological functions of these cells that provide adaptability and efficient computing. Neuromorphic computing uses reduced mathematical models of these cells, limiting the functionality to core components. Biological neurons collect ions to charge their cell body and ultimately release the ions to the subsequent neurons via the synapse. The electrochemical nature of the cells can be interpolated with mathematical models that can then be implemented in digital or analog circuitry. A key factor in the computation is the efficiency with which neurons deliver electrochemical signals. The pathway between neurons is defined as the synapse for neuromorphic computing. The synapse holds a weight value that is a memory of the efficiency of the communication between two neurons. These two components inspired by biology have a plethora of other possible biological functions acting on them to implement the plasticity and learning capable of the brain. Hardware

Figure 2.3: Single perceptron showing weighted inputs, summation, and output activation.

for neuromorphic computing builds these components with all the functionalities desired at a lower cost than running the functions through a general computer. The history of the framework for this project is NIDA, MrDANNA, and the current framework RAVENS[60, 14, 20, 54]. This framework uses an integrate and fire neuron model with connected synapses. The neuron has a threshold for accumulating inputs via synapses. The synapses hold weight information and delay the transmission of the information to the neuron. The setup for defining networks uses a genetic algorithm, evolutionary optimization for neuromorphic systems or EONS, to optimize the network [60, 61]. Optimization generally prioritizes accuracy or functionality, followed by low component count and low power cost. The circuits designed to implement the generated networks need to fulfill the roles given by the framework. The neuron accumulates inputs from the synapse, and the synapses transmit information between neurons with specific delay and strength. Other features, like synaptic plasticity, can be implemented in the framework, and needs to be reflected in the circuits.

#### 2.6 Synapse and Neuron Circuits

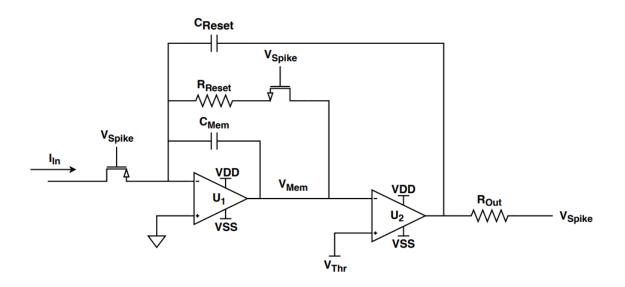

The hardware designed for neuromorphic computing generally follows the biological inspiration. The inputs and outputs are connected to multiple synapses and neurons. While building these components out of purely digital circuits is possible, to truly match the biological nature analog circuits are designed [41]. The use of the term neuromorphic comes from Carver Mead's work on silicon VLSI neurons. The silicon neuron shown in Figure 2.4 is a biologically inspired circuit named after the axon hillock which is the part of the neuron that generates an action potential [40]. The circuit integrates an input on a capacitor,  $C_{mem}$ , creating a voltage,  $V_{mem}$ , and generates a pulse output upon crossing the buffer circuits threshold. Neuromorphic computing continually improved the relationship with circuits to their biological inspiration. The implementation of neuromorphic circuits is limited by the understanding of biology [42]. As the understanding of the principles of

neuromorphic computation improve, the circuits needed to implement the operations will be realized. Improvements to the computational models will elicit the need for the circuits.

In implementing neuromorphic systems, many analog neurons take an input current from the synapse [28]. The axon hillock neuron in Figure 2.4 contains the basis for a silicon neuron. The current into the neuron is integrated and accumulated with the result being a voltage stored on a capacitor. Analog neurons use the stored voltage with a comparator circuit to determine the output of the neuron. Some comparator circuit possibilities include an inverter or op-amp [40, 9]. The output generated when crossing the comparison threshold resets the voltage stored in the neuron and communicates with the next neuron through a synapse. Control circuitry is required to communicate and reset neurons. Synapse circuits respond to the neuron input information and output into the following neuron. The current generated from the synapse into the neuron is a function of the synapse's weight value. For a voltage applied to the synapse an output current can be generated with a resistance.

The memristor could fit into the synapse directly as the weight memory. However, memristors as synapses require additional control circuitry to achieve all the desired synaptic functions. The circuits implementing the neuromorphic functions should be both power and area efficient to outperform the same functions implemented on a traditional system. The benefits can be achieved by improving the circuit efficiency for the simplest models and improving the computing potential of the models used. Including more biological features can potentially improve the computing results and improving the circuitry designed to implement those functions will definitely help the neuromorphic system outperform a traditional counterpart.

Different neurons follow different mathematical models [28]. The integrate and fire neuron uses an integrator and a comparator to accumulate inputs and fire outputs [26]. The axon hillock neuron mimics the axon hillock of a biological neuron [40]. The axon hillock is the location where the output is first generated in the neuron. All neuron circuits have these functions: accumulate and store inputs and output upon crossing an accumulation

Figure 2.4: Original axon hillock neuron circuit [28, 40]

threshold. Some neuron circuits look to implement the intricacies of the ion channels in biological neurons [56]. Other neuron circuits have limited biological representation and are instead optimized for power consumption [31]. Neurons can also benefit from memristor. Neurons have been implemented making use of FeFET, IMT, PCM, and MTJ [35]. Mostly these are integrate and fire neurons.

The synapse can be implemented with transistors and capacitors [28]. These synapse design work by shaping the spike to achieve different accumulations at the input of the neuron. Synapses can consist of only a memristor or similar analog memory element. A common configuration for this is a two dimensional array, where the synapse is a memristor at the intersection of rows and columns. Rows are pre-synaptic neurons and columns are post-synaptic neurons. These configurations are crossbar arrays [9, 27, 33, 29]. The crossbar array has the benefit of a dense connectivity. Synapses connect neurons one to one, but are activated by row and column neurons. This configuration can have current flow through memristors not in use, called sneak paths. These memristor circuits use voltage control to implement both the programming and reading of the memristor. The neurons apply voltages which control what synapses are activated and for plasticity if implemented.

In earlier work, two memristors were used to hold the synaptic weight information [58, 57]. One synapse corresponded to the positive weight value and the other the negative weight value. Weights values came from the model, positive weights allowed for excitation and cause neurons to fire, while negative allowed for inhibition and stopped neurons from firing [59]. This synapse was designed to sink or source current from the neuron. The synapse had STDP functionality using voltage control. Similar to [46, 12] multiple memristors are used to help alleviate potential issues. For the hafnium-oxide memristors, one issue identified was asymmetric switching. Special circuit techniques were used to adjust for the difference in switching speeds.

This work takes into account the variability and asymmetric switching of the memristors fabricated in a hybrid CMOS process. I address the need for a consistent method of programming and updating hafnium-oxide memristors with highly asymmetric switching properties. This required building all necessary components to implement a fully integrated system on a hybrid CMOS memristor wafer. The goal is implementing circuits that are low power and low area to take advantage of the current fabricated memristors. This is accomplished by using the low resistance state to program the device and taking special considerations to reduce power and simplify the required circuitry. The final value of the resistance achieved from the set operation is determined by the current. The current is controlled with one transistor that is reused to control current during a readout operation. This allows for a compact programming and memory storage.

# Chapter 3

# Memristor Model

To simulate circuits that use a memristive device, a model of the device is needed. The memristor's model should include the required characteristics to verify the circuits. The model accurately responds to the operations to update and read the memristor's resistance value. The hafnium-oxide memristor model used here is based on [5, 4]. The device models for hafnium-oxide memristors can be created from intrinsic characteristics of the materials used [78] or from fitting physically tested results of the device [53]. For this model, the characteristics are based on tested results and abstracts possible physiological phenomenon. The switching properties pertaining to the memristor need to be included in the model. Its ability to store a resistance and update that resistance state should match the tested results. The model I implemented for my circuit stems from the tested results of the device with a transistor and leads to my design choices for programming and updating the weight. I found in testing the device, updating the device's resistance is easily achieved with DC signals and created a model that reflects this idea.

## 3.1 Experimental Results for Hafnium-Oxide Memristor

The characteristics of the device are measured to understand and model device behavior. The tests for the memristors are usage-based, including forming voltage and switching voltages, and usability of the device, including cycle to cycle variation and lifetime. The on chip device is part of a one transistor one memristor, 1T1R, test structure seen in Figure 2.2. The connected nodes of the device are the gate  $V_g$  and source of the n-type transistor and the top of the memristor  $V_t op$ . The source of the transistor is held at ground and the gate is held at a DC voltage. At the top of the memristor,  $V_t op$  is a specific voltage applied for different tests. The on chip fabricated devices starts as an unformed device. The unformed resistance is a high resistance and applying a high positive voltage at  $V_{top}$ causes it to form the conductive filament. The device is formed and the resulting voltage at which it formed is measured. Figure 3.1 shows a current response to voltage on the unformed device. The method of collection is further explained in Chapter 6. The forming voltage is temperature dependent, and at room temperature ranges from 1 V to 4 V, but is generally close to  $2.5 \,\mathrm{V}$ . The forming voltage is a high limiting factor for circuit design. The need for a high voltage on the unformed device also implies all circuits attached to those nodes need to be able to handle the high voltage. There are many potential solutions to this including preforming the device before it is connected to the silicon, changing the device to lower its forming voltage, or heating up the wafer to lower its forming voltage. In this work, the forming voltage is a key factor for device consideration at the circuit implementation and design level. The forming process coincides with the set process. In this way, after forming the device is in its low resistance state, which implies a filament is fully formed. A current limitation is needed during this process to reliably reset the device otherwise the device can be stuck in the low resistance state. Aside from the measured forming voltage, different applied current limitations are studied to determine the most reliable forming process.

After forming, the device is in a low resistance state. From here the device is cycled between high and low resistance states. The key characteristics for switching include set and reset switching voltages. For the reset process to occur a switching voltage above -600 mV is applied at  $V_{top}$ . The maximum voltage applied in the reset process affects the high resistance state achieved, and a high negative voltage has the potential to adversely

**Figure 3.1:** Voltage sweep of unformed hafnium-oxide memristor with conductive filament forming at 2.3 V.

affect the device . The reset process is not instantaneous and requires a high negative voltage to be applied for around 100 ns. Different high resistance values can be achieved by either applying varying negative voltages above the switching threshold at  $V_{top}$  or applying the voltage for different lengths of time. The pulses must be shorter than the time needed to fully reset the device to possibly see incremental switching. The pulse programming method for gradually increasing resistance shows good results during the initial resetting of the devices [10]. As the devices resistance gets higher, the possibility of the resistance state is variable, and the relationship of pulse incriminating the resistance is consistent at lower resistances.

The set process is similar to the forming process. However the switching voltage for the set process is constant. It is around 600 mV. The time need for the forming and set process is almost instantaneous at under 100 ps [10]. Due to the fast switching speed, pulse based incremental switching is near impossible. However, this work takes advantage of the low resistance state due to its ability to be consistently programmed. This comes about from another mechanic of the filament forming process. The current limitation needed to reliably recreate the conductive filament has the effect of adjusting the low resistance state varies in a range around 5 k $\Omega$ . All these possible resistance values are achieved with the same voltage applied at  $V_{top}$ . Thus the applied voltage is not the dependent factor, and the current limitation is causing a different final resistance.

After testing the mechanisms for switching, the reliability of the device is tested. The main tests for this are the consistency of the device readout, and the longevity of the device. For the consistency of the readout, the device is programmed to a specific resistance value, and then the device is measured periodically. Ideally, the device will hold this resistance value indefinitely and each measurement will be identical. The device has a constant resistance value and thus is a non-volatile memory device. The readout is consistent over many read operations over a long time. The other reliability factor is the number of cycles of set and reset the device can go through and continue to achieve reliable resistance states.

For these devices, the reliability is a key factor with devices of resistance value changes with equivalent resistance changing processes.

## 3.2 Memristor Model

In my model I capture the ability to reach different high and low resistance states through DC voltage signals. I do not concern myself with the intricacies of the switching and simply linearly increase or decrease at a definable specific rate. Figure 3.2 and 3.3show state diagrams for the hafnium-oxide memristor. The four processes used in the device include forming, set, reset, and read. The device starts in an unformed state, and requires a high positive voltage to form the device. The forming voltage parameterized and is generally above 2 V at room temperature. After forming, the device is at a low resistance and requires a negative voltage with a greater magnitude than the negative switching threshold to increase resistance. The device's resistance decreases with a positive voltage above the positive switching threshold voltage. In any state, the device's current state can be determined with a read voltage that is a between the positive and negative switching threshold voltages. The model encapsulates these different switching capabilities. For a binary implementation, which only includes a singular high resistance state and a singular low resistance state, the model can simply jump from the low resistance to the high resistance state by using a constant positive and negative voltage at  $V_{top}$ . While the resistance during switching is intended to be outside the scope of my model, the final result from a varying voltage at  $V_{top}$  and  $V_g$  should achieve varying resistance levels. To accomplish this goal, I implemented a bounding system in the model that ends the set and reset processes. For the set, and similarly forming, the process begins with a positive voltage above the switching threshold and continues while above another specified voltage. For the reset process, the process starts with a highly negative voltage and continues while the current magnitude is above a specified current. This achieves variable low and high resistance states based on the applied stimuli.

Figure 3.2: Flow state diagram of hafnium-oxide memristor.

Figure 3.3: Diagram of hafnium-oxide memristor resistance movement.

Memristor's are well understood to have a threshold voltage for switching. A high positive voltage,  $600 \,\mathrm{mV}$  is approximately the positive switching voltage threshold Vtpfor the set operation of the hafnium-oxide memristors I tested. I implemented my model with a second voltage threshold for the set operation. This voltage threshold lower bound Vtpl can be approximated as a linear value,  $400 \,\mathrm{mV}$ . However, it is more accurately represented as a function of the device's current resistance value, and it increases as the device decreases. This causes a non-linearity in the relationship between current limitation and resistance achieved. The lower bound voltage allows for different low resistance values as a result of different current limitations due to varying  $V_g$ . As the resistance of the device lowers, the voltage across the current limiting transistor increases and the voltage across the device decreases. For higher transistor saturation currents of the current limiting transistor the voltage across the device will stay above the lower bound positive threshold at lower resistances. This coincides with the physical results of a higher gate voltage, or higher current limitation, resulting in a lower resistance. The memristor model uses the same idea for implementing the forming process, but uses different voltage thresholds Vfand Vfl that match the physically tested results.

#### 3.2.1 Set Operation

The set operation reduces the resistance while above a specific voltage Vtpl. If the voltage applied stays above the lower bound, or has no current limiting device, the device will reach an absolute minimum resistance. While a linear threshold works to achieve the correct relationship between the current limiting transistor and the low resistance state, from device testing, a more accurate relationship can be calculated. The lower bound voltage can be calculated as the relationship between the current limiting transistors current multiplied by the final resistance achieved. From testing, the lower bound is calculated in the model as a function of the resistance. For the low resistance state, as the resistance decreases Vtpl increases. The code snippet below shows the set process in the Verilog-A model. The lower bound voltage Vtpl is calculated with a linear relationship to the current resistance. The set process begins with a voltage across the device Vmr above the threshold Vtp and activates the start flag. The process then continues until the voltage is below the lower bound. In the process of switching, the resistance Rm is lowered linearly at a specified rate td \* dRmp. The rate is calculated by the total range of resistances divided by the positive switching speed, which is 100 ps. If the resistance reaches the absolute minimum resistance the set process will also end.

```

1

//Define the function for the lower bound

2

//Vtpl = .6; //Constant approximation

3

Vtpl = -0.0001 * Rm + 1;

4

5

//Activate flag for set process

6

if (Vmr >= Vtp && Rm > LRS_min) begin

7

Setstart = 1;

8

end

9

10

//Continue set process while flag, voltage, and resistance are high

11

if (Vmr > Vtpl && Setstart == 1) begin

12

Rm = Rm - td * dRmp;

13

if (Rm_tmp <= LRS_min) begin</pre>

14

Rm_tmp = LRS_min;

15

Setstart = 0;

16

end

17

end

18

```

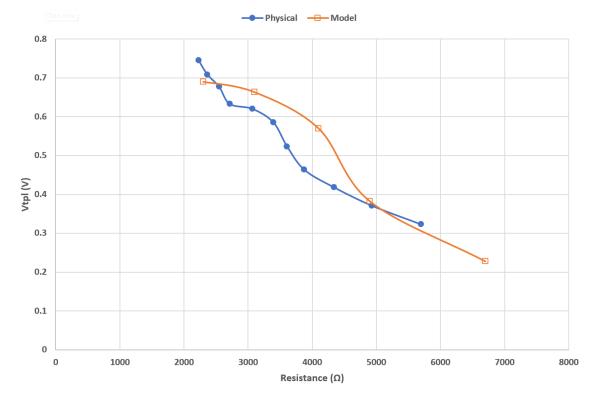

Simulation results for the set process show a close match to a physically tested device for the resulting resistance for different transistor saturation currents. Figure 3.4 shows the resulting resistance after the set process from different applied gate voltages to the current limiting transistor of a 1T1R circuit. The applied voltage was 1.5 V on the memristor and the gate voltage varied. The current through the device during the set process was

### Set Current vs. Resistance

Figure 3.4: Model vs. Physical tested device set resistance at different currents.

directly proportional to the voltage at the gate of the transistor. The gate voltage on the transistor activated the transistor and applied the current limitation at its saturation current. While the resistance of the memristor is decreasing the voltage across the device is decreasing. The voltage across the drain to source of the transistor is increasing. Once the drain to source voltage is high enough, the current through the transistor's drain to source current saturates. The lower bound voltage for the set process is the voltage across the memristor for a given current limitation. This is calculated by multiplying the current limitation used in the set process and the final resulting resistance. Figure 3.5 shows the lower bound voltage Vtpl for different low resistance states. In the simulation Vtpl is fit to that specific device. While a constant voltage works, the lower bound voltage is fit with a function of resistance.

#### 3.2.2 Reset Operation

The reset operation requires a negative voltage below the negative switching threshold. For the hafnium-oxide memristor, the negative voltage at  $V_{top}$  required to increase the resistance is approximately -600 mV. Like the set process, I implemented my model to start the reset process upon crossing this voltage threshold. However, unlike the set process, during the reset process the voltage magnitude across the device is not decreasing due to the change in resistance. To make an equivalent stopping mechanic in the model, I instead used the current through the device. I set a lower bound Itpl of 10 µA as a required current to continue the reset process. This resulted in different high resistance states for the applied voltage. From testing, the lower bound is a function of the resistance. For the high resistance state, as the resistance increases Itpl decreases. The code snippet below shows the reset process in the Verilog-A model. The lower bound voltage Itnl is calculated with a linear relationship to resistance. The reset process begins with a voltage across the device Vmr below the threshold Vtn and activates the start flag. The process then continues until the current is above the lower bound. In the process of switching, the resistance Rm is lowered linearly at a specified rate td \* dRmn. The rate is calculated by

## Set Voltage Bound vs. Resistance

**Figure 3.5:** Model vs. Physical tested device calculated voltage across device during set at LRS.

the total range of resistances divided by the negative switching speed, which is 100 ns. If the resistance reaches the absolute maximum resistance the reset process will also end.

```

1

//Define the function for the lower bound

2

//Itnl = 1e-5; //Constant approximation

3

Itnl = 8e - 11 * Rm - 2.19e - 5;

4

\mathbf{5}

//Activate flag for reset process

6

if (Vmr <= Vtn && Rm < HRS_max ) begin</pre>

7

Resetstart = 1;

8

end

9

10

//Continue set process while flag, voltage, and resistance are high

11

(Imr <= Itnl && Resetstart == 1) begin

if

12

Rm = Rm + td * dRmn;

^{13}

if (Rm_tmp >= HRS_max) begin

14

Rm\_tmp = HRS\_max;

15

Resetstart = 0;

16

end

17

end

18

```

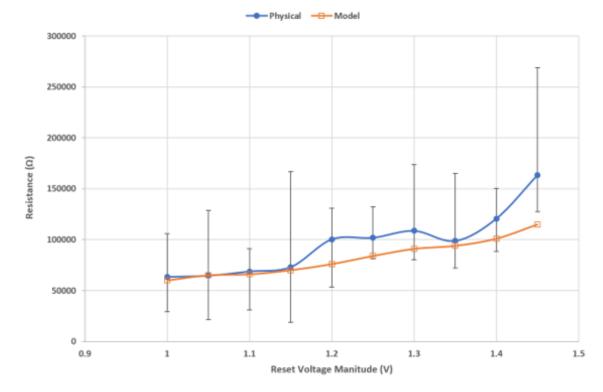

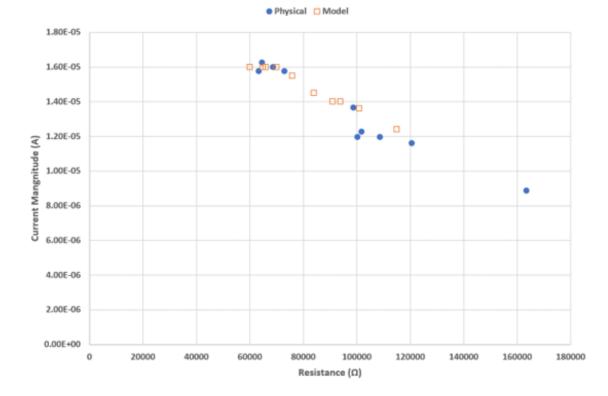

Simulation results for the reset process show a close match to a physically tested device for the resulting resistance for different reset voltages applied. Figure 3.6 shows the resulting resistance after the reset process from different negative voltages on the memristor. The applied voltage was 1 V to 1.45 V on the memristor. The current through the device during the reset process reduces as the resistance increases. The varying applied voltages allow for a higher current at higher resistances. The lower bound current for the set process is the measured current. In the simulation, *Itnl* is fit to the recorded current measurements of that device. Figure 3.7 shows the lower bound current *Itnl* for different

Reset Voltage vs. Resistance

Figure 3.6: Model vs. Physical tested device reset resistance at different voltages.

#### **Reset Current Bound vs. Resistance**

Figure 3.7: Model vs. Physical tested device calculated current through the device during reset at HRS.

low resistance states. While a constant current works, the lower bound voltage is fit with a function of resistance.

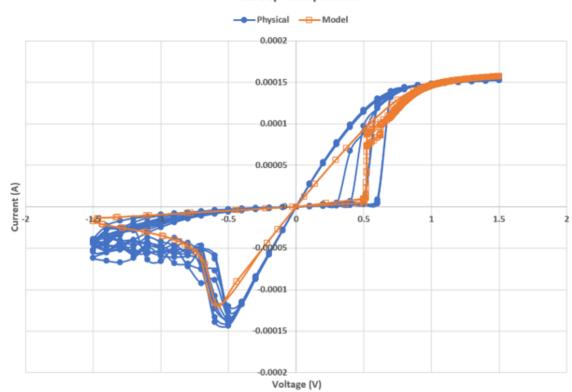

Simulation results for both set and reset for the model show the characteristic hysteresis loop when sweeping voltage. Figure 3.8 shows the transition between HRS and LRS when sweeping voltage from -1.5 V to 1.5 V in both the model and a physically tested device. The model uses a linear relationship between the resistance and the switching bounding variables, *Itnl* and *Vtpl*. Table 3.1 shows the fitting parameters to best approximate the relationship. This model is used in Chapter 6 to show the change in resistance due to change in current compliance for the set operation.

I-V Sweep Comparison

Figure 3.8: Model vs. Physical tested device I-V sweep results.

Table 3.1: Fitting parameters for memristor model.

|      | Slope   | Offset   |

|------|---------|----------|

| Vtnl | -0.0001 | 1        |

| Itpl | 8e-11   | -2.19e-5 |

# Chapter 4

# Memristive Synapse Circuit

## 4.1 Analog Synapse with Memristor for Weight Storage

In a neuromorphic system the synapse is the connection between neurons. The neurons communicate information via the synapse by accumulating charge. The synaptic strength, referred to as the weight of a synapse, is the amount the synapse can charge or discharge its subsequent neuron. The network of neurons and synapses instantiate synaptic weights for all synapses used to solve a given problem. The neuromorphic system can implement weight changes beyond initial values chosen to improve the effectiveness of the neuromorphic system. As an electrical component, the synapse requires two terminals to connect the two neurons, the pre-neuron and post-neuron. Similar to a memristor, the synaptic weight depends on previous usage. The synapse like a memristor is a two terminal device that has memory. The memory functions provided by the synapse require the change and storage of the synaptic weight. Memristors used for the synapse can mimic the plasticity of the synapse by retaining information an past usage. Non-volatile memristors can store long term weight changes and follow learning rules for long term change. Volatile memristors can exhibit short term weight changes. To mimic biological learning rules, the weight change of the synapse needs complex resistance change based on the activity it receives. Building a synaptic circuit using solely memristors requires the memristors

to possess the equivalent resistance change criteria to biological synapses. For fabricated memristors, achieving similar weight change relationships to neuron activity requires circuitry surrounding the synapse. The circuitry provides adequate voltages to integrate the memristor. The synapse control circuitry is required to implement the analog memory. The control circuitry activates the synapse to read out the weight, programs the memristor to store a weight value, and implements the intended synaptic plasticity. The read out of a synapse is a current into the neuron. The synapse is designed as an analog memory cell using the memristor as the value storage. Implementing the synapse ideally uses low power and area while reliably outputting a stored value. The synapse circuit and all additional control circuitry presented here is intended to use the on chip fabricated hafnium oxide memristor efficiently.

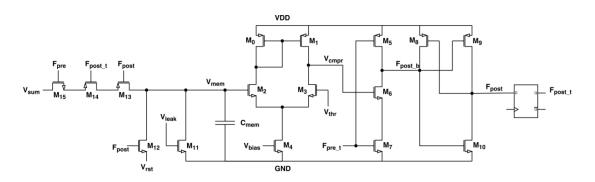

## 4.2 Synapse Circuit

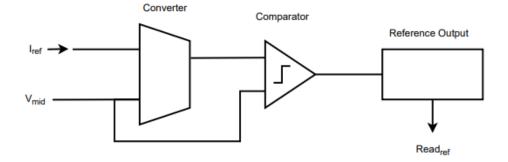

The block diagram in Figure 4.1 shows the components used in this work to implement a synapse. The goal of the synapse is to hold an analog memory that controls the flow of charge in the connected neuron. The current control circuitry used for programming is reused for read out. The memory is stored on the memristor device in the memristor cell circuit. The output current is generated with the synapse output current control circuit. The synapse output is a current intended to charge an integrate-and-fire neuron. The neuron takes the different synaptic currents due to different resistance values of the memristor and charges proportionally. The currents of all synapses connected to a neuron are summed together by directly connecting at the output node.

#### 4.2.1 Memristor Cell

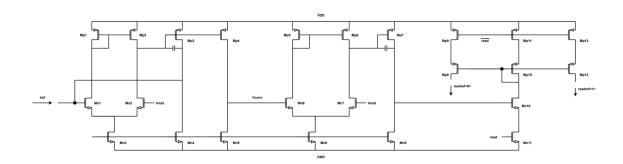

The circuit seen in Fig. 4.2 for the on chip hafnium oxide memristor shows the necessary transistors required for the four different modes of operation, which are *Forming*, *Set*, *Read*, and *Reset*. The size and expected gate voltages of each transistor is seen in

Figure 4.1: Block diagram of Synapse circuit.

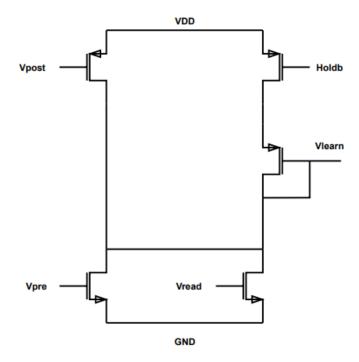

Figure 4.2: Circuit depicting the memristor and transistors directly connected to it.

Table 4.1. The first action is a one time operation to create a metallic filament by applying a high voltage across the unformed device called forming. Due to the need for a high voltage, all transistors that are directly connected to the hafnium oxide memristor will need to be large transistors able to operate in a high voltage region. These large transistors control the memristor through the various operations. For a single stand alone memristor there are seven high voltage transistors. They correspond to four p-type transistors and three n-type transistors. Each operation has a corresponding p-type transistor. The reset and read operations have their own unique n-type transistors. The last n-type transistor is shared for the forming, set, and read operation. For an array of these devices, the transistors for reading and set,  $M_{N1} M_{N2} M_{P1}$  are unique to each memristor, while the other transistors can be shared. The p-type transistors for set, reset and forming are shared across a column in a two by two matrix. The n-type transistor for reset is shared for every row.

The transistor  $M_{N1}$  has three modes of operation. During forming the gate voltage at  $M_{N1}$  is 1 V which corresponds to a 100 µA current in saturation. Due to the unformed device having a high resistance, applying this voltage on the gate of  $M_{N1}$  reduces the voltage below the memristor to near ground. In the forming process the corresponding forming transistor  $M_{P1}$  is digitally turned on by bringing the gate voltage from 3.3 V to 0 V. This causes the upper node of the memristor to be pulled up to 3.3 V. Once the filament forms, the voltage drop across the device reduces, and  $M_{N1}$  goes into saturation. The current of  $M_{N1}$  in saturation limits the current through the forming path.

After forming, the device is in a low resistance state. The synapse is designed to use the low resistance state of the device. In order to program the device to a new low resistance state, the device is first reset to a high resistance. The reset process is digitally controlled by transistors  $M_{P4}$  and  $M_{N3}$ . With all other transistors turned off, activating these two transistors will bring the top node of the memristor to ground and the bottom node of the memristor above 1.6 V. The voltage drop across the device when resetting should be above the switching threshold. This is adjustable with the voltage VReset. The opposite

| Device | Size $(\mu m/\mu m)$ | Gate Voltages (V) |

|--------|----------------------|-------------------|

| Mn1    | 5/0.5                | 0-1.2             |

| Mn2    | 1/0.5                | $\sim 0.675$      |

| Mn3    | 2/0.5                | 0-3.3             |

| Mp1    | 1.5/1                | 0-3.3             |

| Mp2    | 8/4                  | 0-3.3             |

| Mp3    | 0.5/0.5              | 0-3.3             |

| Mp4    | 8/4                  | 0-3.3             |

Table 4.1: High voltage transistor connected to memristor size and voltage.

polarity of high voltage on the device breaks the filament created in the forming process. The time and voltage used for reset in the synapse design is long enough to fully reset the device into a high resistance state. Due to the variability in the high resistance state, it is not used in the read operation of the synapse.