# Hysteresis-Free Nanosecond Pulsed Electrical Characterization of Top-Gated Graphene Transistors

Enrique A. Carrion, Andrey Y. Serov, Sharnali Islam, Ashkan Behnam, Akshay Malik, Feng Xiong, Massimiliano Bianchi, Roman Sordan and Eric Pop

Abstract—We measure top-gated graphene field-effect transistors (GFETs) with nanosecond-range pulsed gate and drain voltages. Due to high- $\kappa$  dielectric or graphene imperfections, the drain current decreases by  $\sim 10\%$  over timescales of  $\sim 10 \mu s$ , consistent with charge trapping mechanisms. The pulsed operation leads to hysteresis-free I-V characteristics that are studied with pulses as short as 75 and 150 ns at the drain and gate, respectively. The pulsed operation enables reliable extraction of GFET intrinsic transconductance and mobility values independent of sweep direction, which are up to a factor of two higher than those obtained from simple dc characterization. We also observe drain-bias-induced charge trapping effects at lateral fields greater than 0.1 V/ $\mu$ m. In addition, using modeling and capacitance-voltage measurements, we extract trap densities up to  $10^{12}$  cm<sup>-2</sup> in the top-gate dielectric (here  $Al_2O_3$ ). This study illustrates important time- and field-dependent imperfections of top-gated GFETs with high- $\kappa$  dielectrics, which must be carefully considered for future developments of this technology.

Index Terms—Charge trapping, field-effect transistors (FETs), graphene, high- $\kappa$  dielectric, hysteresis, mobility, nanosecond pulsed measurements.

#### I. INTRODUCTION

RAPHENE devices are promising candidates for nanoelectronics [1], [2] due to good electrical properties, such as high mobility [3] and high saturation velocity [4]. Other than carbon nanotubes (CNTs), graphene is the only material with intrinsic electron and hole mobilities that are

Manuscript received May 30, 2013; revised February 27, 2014; accepted February 27, 2014. Date of publication April 4, 2014; date of current version April 18, 2014. This work was supported in part by Systems on Nanoscale Information Fabrics (SONIC), one of the six SRC STARnet Centers sponsored by MARCO and DARPA, in part by the U.S. Air Force Office of Scientific Research Young Investigator Program (YIP) Grant FA9550-10-1-0082, the National Science Foundation CAREER Grant ECCS-0954423, the Office of Naval Research YIP Grant N00014-10-1-0853, the Italian Fondazione Cariplo Grant 2011-0373 and Directa Plus srl. The review of this paper was arranged by Editor A. C. Seabaugh.

E. A. Carrion, A. Y. Serov, S. Islam, A. Behnam, A. Malik, and F. Xiong are with the Department of Electrical and Computer Engineering, University of Illinois at Urbana-Champaign, Urbana, IL 61801 USA (e-mail: ecarrio2@illinois.edu; serov2@illinois.edu; sislam5@illinois.edu; abehnam@illinois.edu; malik15@illinois.edu; xiong8@illinois.edu).

M. Bianchi and R. Sordan are with L-NESS, Department of Physics, Politecnico di Milano, Como 22100, Italy (e-mail: massimiliano.bianchi@como.polimi.it; roman.sordan@como.polimi.it).

E. Pop was with the Department of Electrical and Computer Engineering, University of Illinois at Urbana-Champaign, Urbana, IL 61801 USA. He is now with the Department of Electrical Engineering, Stanford University, Stanford, CA 94305 USA (e-mail: epop@stanford.edu).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

both high (10000 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> or higher) at room temperature *and equal*, due to symmetric conduction and valence energy bands. In contrast, transistor materials from Si and Ge to III–V compounds have a reasonably good electron mobility (up to 800 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> for Si electron inversion layers and 30000 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> for InAs and InSb quantum wells), but hole mobility two to twenty times lower (200 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> for Si hole inversion layers and up to 1000 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> for strained InSb) [5].

In the past few years, practical circuits have been demonstrated using graphene field-effect transistors (GFETs), including amplifiers [6], [7], inverters [8], ring oscillators [9], radio-frequency mixers [10]–[12], and wafer-scale circuits [13]. However, depending on the high-permittivity (high- $\kappa$ ) top-gate dielectric used, the graphene–dielectric interface, and the testing conditions (e.g., air ambient versus vacuum), GFETs often exhibit characteristics that depend on the voltage sweep direction, i.e., hysteresis. The hysteresis shift can be defined as the difference in Dirac voltage ( $V_0$ ) between forward (FWD) and reverse (REV) gate voltage sweeps ( $\Delta V_0 = V_{0,\text{FWD}} - V_{0,\text{REV}}$ ), where  $V_0$  is the gate voltage of minimum conductivity in the graphene channel, and can be considered analogous to the threshold voltage in traditional MOSFETs.

Hysteresis is primarily caused by charge trapping [14]–[16] at the graphene–dielectric interfaces and by ambient molecules (i.e., water and oxygen) in contact with the graphene surface [17]. The latter effect can be reduced or eliminated by measurements under vacuum conditions ( $\sim 10^{-5}$  torr) [15], [18] after an annealing step [18], [19]. However, trapping at the interfaces or within the bulk of the dielectrics surrounding the graphene channel is an inherent and challenging problem. Ultimately, such trapping causes device reliability and operation issues that translate to changes in carrier concentrations, and thus introduce uncertainties when extracting parameters of interest, including mobility, contact resistance, and transconductance. Similar threshold voltage instabilities had also been observed in the early years of silicon technology [20] and as recently as the last decade with the introduction of high- $\kappa$  dielectrics and metal gate-stacks [21], [22]. Addressing such trapping and voltage instability issues is crucial for the continued development and accurate metrology of GFETs.

In this paper, we investigate the effect of pulsed current-voltage (I-V) measurements on the hysteresis and extracted parameters (such as mobility) of top-gated GFETs.

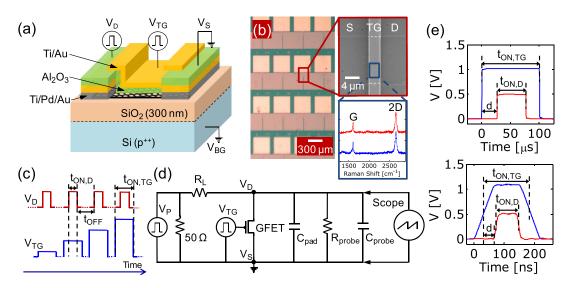

Fig. 1. (a) Schematic diagram of top-gated GFETs fabricated in this paper. (b) Optical and SEM images as well as Raman spectra of typical devices. (c) Schematic diagram of pulses and biases applied at top-gate  $(V_{TG})$  and drain  $(V_D)$  terminals. The amplitude of  $V_{TG}$  is increased when performing a gate sweep of the voltage. (d) Diagram of a circuit used to apply voltage pulses at drain and gate terminals. Current is calculated from the voltage drops across the load resistor  $(R_L = 0.5 - 1.5 \text{ k}\Omega)$ , GFET, probe resistance  $(R_{\text{probe}} = 100 \text{ k}\Omega)$ , and pad  $(C_{\text{pad}} = 8.3 \text{ pF})$  and probe capacitances  $(C_{\text{probe}} = 0.8 \text{ pF})$ . (e) Measured drain and top-gate pulses—top gate scope connection not shown in (d)—with  $t_{\text{ON},TG} = 100 \mu \text{s}$  and  $t_{\text{ON},D} = 50 \mu \text{s}$  (top) and  $t_{\text{ON},TG} = 150 \text{ ns}$  and  $t_{\text{ON},D} = 75 \text{ ns}$  (bottom). In both cases,  $V_D$  has a delay  $d = t_{\text{ON},D}/2$  relative to  $V_{\text{TG}}$ . In addition,  $V_{\text{TG}} = 1 \text{ V}$  and  $V_D = 0.5 \text{ V}$ .

Submicrosecond pulsed output characteristics of top-gated exfoliated graphene FETs [23] and micro- to millisecond pulsed transfer characteristics of back-gated FETs were reported in [14], [15] and [17] (sweep rates used in [17] range from 0.19 to 4.18 V/s), the latter only probing trapping at the graphene-SiO<sub>2</sub> interface. Here, we use graphene grown by large-scale chemical vapor deposition (CVD) and examine the gate and drain effects of reducing drain and gate pulse widths down to 75 and 150 ns, respectively (over  $5 \times$  smaller than the shortest pulses investigated in [23]). We uncover two apparent trapping time constants of approximately 0.3 and 4.2  $\mu$ s, ostensibly due to imperfections in the top-gate high- $\kappa$  dielectric (Al<sub>2</sub>O<sub>3</sub>), its interface (oxidized Al seeding layer), or the graphene itself. Hysteresis is greatly reduced when using nanosecond voltage pulses at the drain and gate terminals, effectively limiting the time over which charge trapping can occur. The extracted mobility is independent of sweep direction and up to a factor of two higher than if dc measurements were simply employed. The approach described here leads to reliable characterization of GFETs, even in the face of imperfect dielectrics and interfaces.

## II. DEVICE FABRICATION AND MEASUREMENT SETUP

Graphene is grown on copper foils similarly to [8], [24], using CVD with a methane/hydrogen mixture as precursor gases. It is then transferred onto  $SiO_2(300 \text{ nm})/Si$  substrates using a dual stack of poly(methyl methacrylate) (PMMA) for support and protection (60 nm of 495 A2 and 250 nm of 950 A4). PMMA is removed using a 1:1 solution of methane dichloride and methanol, followed by a  $H_2/Ar$  anneal (2 h at 400 °C) [25]. Next, Ti/Pd/Au (0.7/20/20 nm) source/drain electrodes are fabricated using UV lithography and e-beam evaporation, followed by  $O_2$ -plasma channel definition and atomic layer deposition (ALD) of  $t_{ox} \approx 20 \text{ nm}$  of  $Al_2O_3$

(seeded by 1.5 nm of evaporated and oxidized Al). Finally, a Ti/Au (0.7/20 nm) top gate with a gate–source/drain overlap of  $\sim$ 150 nm is fabricated using e-beam lithography. Channel dimensions (L and W) range from 2 to 10  $\mu$ m.

Figs. 1(a) and (b) show the schematic, optical, and scanning electron microscope (SEM) images of completed devices. Raman spectra taken after transfer [inset of Fig. 1(b)] indicate that graphene is monolayer (2D-peak to G-peak integrated intensity ratio  $I_{2D}/I_G \approx 2$ ) and with D-peak to G-peak integrated intensity ratio  $I_D/I_G \approx 0.25 \pm 0.15$  [26]. From the  $I_D/I_G$  ratio, we estimate [27] an average distance between Raman-active defects to be  $L_a \approx 250 \pm 150$  nm. Considering micrometer-scale device dimensions used here, we expect the presence of defects and grain boundaries within the channel [28], and thus lower mobilities than those of exfoliated (single crystal) graphene devices [4].

During measurements, we apply voltage pulses  $(V_P)$  at the drain while increasing the amplitude of voltage pulses at the top gate  $(V_{TG})$ , as shown in Fig. 1(c) and (d). The  $V_D$  pulse is applied after the rising  $(t_R)$  edge and removed before the falling  $(t_F)$  edges of  $V_{TG}$ , since gate pulse edges cause a small resonance on  $V_D$ , especially at larger amplitudes (i.e.,  $V_{TG} > 2$  V) and shorter edges  $(t_R = t_F < 500$  ns). Hence, the full-width at half-maximum of  $V_{TG}$  is twice that of  $V_D$  ( $t_{ON,TG} = 2 \cdot t_{ON,D}$ ), and a delay relative to  $V_{TG}$  ( $d = t_{ON,D}/2$ ) is half the width of  $V_D$  [Fig. 1(e)]. We find that these two constraints maximize signal integrity. The rise  $(t_R)$  and fall  $(t_F)$  times of gate or drain pulses vary depending on their width (i.e.,  $t_R = t_F = 10$  ns for  $t_{ON,D} = 75$  ns and  $t_R = t_F = 20 - 50$  ns for  $t_{ON,TG} = 150$  ns).

The OFF-state relaxation time between drain pulses ( $t_{\rm OFF}$ ) ranges between 0.1 and 1 ms, which is 3–4 orders of magnitude larger than the shortest  $t_{\rm ON,\it D}$  applied (75 ns). These OFF-times were found to be sufficiently long to relax all

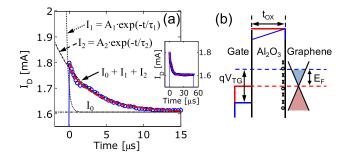

Fig. 2. (a) Measured drain current  $I_D$  (blue circles) during the first 15  $\mu$ s of a typical 50- $\mu$ s pulse ( $V_D=1.9$  V,  $V_{TG}=0.5$  V). Inset shows the same data set, zoomed out for the entire 50  $\mu$ s. Device measured in air ambient ( $L\times W=2\times 10~\mu$ m). Transient behavior is due to the population of interface and bulk oxide charge traps. Current is fitted (red dashed lines) with  $I_D(t)=I_0+A_1 \exp(-t/\tau_1)+A_2 \exp(-t/\tau_2)$ . Exponential terms are shifted by  $I_0$  and shown by black dashed and dotted lines. Fitting parameters are  $I_0=1.6$  mA,  $A_1=0.03$  mA, and  $A_2=0.16$  mA, with two time constants  $\tau_1=0.3$   $\mu$ s and  $\tau_2=4.2$   $\mu$ s. (b) Schematic band diagram of the metal-oxide-graphene device showing population of interface traps as the graphene Fermi level (dashed) changes. Interface states could act as either hole (circles) or electron (x-symbols) traps.

measurable effects of charge trapping from our short pulses. Larger relaxation times (up to the range of seconds) have been used while studying trapping at the graphene/SiO<sub>2</sub> [14]–[17] and CNT/SiO<sub>2</sub> [29] interfaces. In contrast, our analysis attempts to study and control trapping using nanosecond-range top-gate pulses ( $t_{\rm ON,TG}$ ), effectively limiting the amount of carriers than can become trapped instead of increasing detrapping via longer OFF-state relaxation.

To measure pulsed I-V characteristics, we employ a pulse generator, a 1.5-GHz oscilloscope, an active probe, and a simple voltage divider circuit in our setup [Fig. 1(d)]. For each top-gate pulse  $(V_{TG})$ , a corresponding voltage pulse is applied to a load resistor  $(R_L)$ , such that after subtracting its voltage drop  $(V_{RL})$ , a pulse of amplitude  $V_D$  is applied to the GFET  $(V_D = V_P - V_{RL})$ . For  $I_D - V_{TG}$  measurements, the amplitude of  $V_D$  is kept the same throughout the measurement by adjusting the amplitude of the pulse  $V_P$  at each  $V_{TG}$ bias through a feedback loop (since V<sub>RL</sub> changes with the bias-dependent resistance of the device). Every recorded  $V_D$ waveform (at a given  $V_{TG}$ ) is an average over 200 applied pulses. The time dependence of the drain current  $I_D(t)$  is obtained from the voltage drops across the load resistor  $(R_L)$ and a 50- $\Omega$  matching resistor (in parallel with the 50- $\Omega$  output impedance of the pulse generator), the GFET, the active probe resistance ( $R_{\text{probe}}$ ), and pad ( $C_{\text{pad}}$ ) and probe capacitances  $(C_{\text{probe}})$ , such that

$$I_{D}(t) = \frac{V_{P}(t) - V_{D}(t)}{R_{L} + 25 \Omega} - \frac{V_{D}(t)}{R_{\text{probe}}}$$

$$- \left(C_{\text{pad}} + C_{\text{probe}}\right) \times \frac{dV_{D}(t)}{dt}. \tag{1}$$

# III. RESULTS OF PULSED MEASUREMENTS

With this setup, we first look at the typical transient behavior of current [Fig. 2(a)] when  $t_{\rm ON,\it D}=50~\mu \rm s$  pulses are applied at the drain terminal.  $I_D$  reaches the steady state with  $\sim 10\%$

degradation after  $\sim 10 \ \mu s$  due to the effect of charge traps at this particular bias condition. This drop-off is faster than those mentioned in [14] and [17], which studied charge trapping at back gates with much thicker amorphous SiO2 layers. The best fit of  $I_D(t)$  is obtained using two decaying exponentials of the form  $A \cdot \exp(-t/\tau)$  (black dashed lines), yielding time constants  $\tau_1 = 0.3 \ \mu s$  and  $\tau_2 = 4.2 \ \mu s$ . These suggest the presence of at least two trapping mechanisms, such as interface and bulk trapping [23], [30], [31]. Interface trap response times scale exponentially with their energy difference from either the valence or the conduction bands of a typical channel material [30]. Since graphene does not have a band gap and trap states can be located across a wide range of energies [Fig. 2(b)], interface traps can be rapidly filled when the energy of carriers is higher than that of electron (xsymbols) or hole traps (circles). On the other hand, bulk trap response times depend on tunneling through the oxide, and thus they are expected to be slower. In our case, the oxidized Al seeding layer  $(AlO_x)$  and graphene imperfections (i.e., grain boundaries) could be responsible for contributions to interface trapping, while the ALD-grown Al<sub>2</sub>O<sub>3</sub> contributes to bulk trapping. Nevertheless, a simple tunneling front model [29] analysis reveals that such traps are likely less than  $\sim$ 1 nm apart in the Al<sub>2</sub>O<sub>3</sub>, making it challenging to ascertain their exact physical origin, which could be the topic of a future investigation.

We note that the time constants identified here (0.3 and 4.2  $\mu$ s) are not originated from circuit transients, as circuit RC time constants due to  $R_L$ ,  $R_{GFET}$ ,  $R_{probe}$ ,  $C_{pad}$ , and  $C_{probe}$  are  $\sim$ 10 ns. However, thermal time constants of top-gated GFETs with similar geometry are of the order  $\sim$ 100 ns [32]; thus, it is possible that the shorter time constant found here ( $\tau_1 = 0.3 \ \mu$ s) can include a small thermal self-heating transient, which can also influence current degradation (although we note that our pulsed measurements were done at relatively low current density,  $\sim$ 0.1 mA/ $\mu$ m, except those in Section VI).

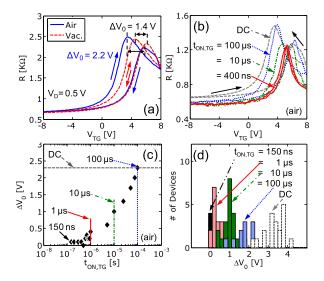

The effect of trap filling on electrical measurements can also be observed in Fig. 3(a), where the dc transfer characteristics of a typical top-gated GFET  $(L \times W = 2 \times 10 \ \mu \text{m})$  show Dirac voltage shift and hysteresis ( $\Delta V_0$ ) in air and vacuum measurements. Charge trapping (or detrapping) is less likely to occur at the bottom graphene/SiO2 interface when we vary  $V_{TG}$ , as the voltage drop between the graphene and back gate is small ( $V_{BG} = 0 \text{ V}$ ). The presence of hysteresis in both air and vacuum suggests that ambient adsorbates (i.e., O<sub>2</sub> and H<sub>2</sub>O) and the top dielectric trapping (interface and bulk) contribute to the change in carrier density in the channel, while the dc top-gate voltage is swept [14], [15]. Thus, to minimize such  $V_0$  instabilities, we perform pulsed measurements as described above. For each  $V_{TG}$  bias,  $I_D$  is calculated as a function of time using (1) and its amplitude is averaged over the duration  $(t_{ON,D})$  of each drain pulse. Fig. 3(b) shows the in-air transfer characteristics for different  $V_{TG}$ ON-times  $(t_{ON,TG})$  and compares them with simple dc I-Vsusing the same bias conditions ( $V_D = 0.5 \text{ V}$  and  $V_{BG} = 0$ V). As  $t_{ON,TG}$  is decreased from 100  $\mu$ s to 400 ns, FWD and REV sweeps collapse onto one another and hysteresis  $\Delta V_0$

Fig. 3. (a) Hysteresis in dc measurement of resistance (R) versus top-gate voltage ( $V_{TG}$ ) of a typical device ( $L \times W = 4 \times 8 \ \mu m$ ) in air (blue-solid) and in vacuum (red-dashed). Arrows indicate sweep directions (from -8 to +8 V and back). Hysteresis is  $\Delta V_0 = 2.2$  and 1.4 V in air and vacuum, respectively ( $V_D = 0.5$  V). (b) Typical  $R - V_{TG}$  characteristics of another device measured in air under dc (dashed lines) and pulsed conditions. Note the suppression of hysteresis between FWD and REV sweeps as  $t_{\rm ON,TG}$  decreases to 400 ns ( $L \times W = 2 \times 10 \ \mu m$ ). (c) Measured shift in Dirac voltage ( $\Delta V_0$ ) from (b) as a function of  $t_{\rm ON,TG}$ .  $\Delta V_0$  is marked (lines and arrows) at five selected testing conditions:  $t_{\rm ON,TG} = 0.15$ , 1, 10, 100  $\mu$ s, and dc. (d) Histogram of  $\Delta V_0$  for 20 devices measured at same five testing conditions:  $t_{\rm ON,TG} = 0.15$ , 1, 10, 100  $\mu$ s, and dc. Note that not all devices were tested for each case.

disappears. In Fig. 3(c), the corresponding  $\Delta V_0$  is shown as a function of  $t_{\rm ON,TG}$  down to 150 ns; we note that for dc I-Vs,  $\Delta V_0=2.3$  V, while for  $t_{\rm ON,TG}<500$  ns hysteresis  $\Delta V_0$  approaches 0 V. This  $\Delta V_0$  reduction was observed across 20 devices ( $L,W=2-10~\mu{\rm m}$ ) [Fig. 3(d)] for five testing conditions:  $t_{\rm ON,TG}=0.15, 1, 10, 100~\mu{\rm s}$ , and dc. We attribute the broadening of each distribution (corresponding to each  $t_{\rm ON,TG}$  case) to device-to-device variations, i.e., graphene or dielectric interface quality and contact resistance.

The transfer characteristics shown in Fig. 3(b) are consistent with the presence of negative charges in the oxide. The fixed negative charges can be present in Al<sub>2</sub>O<sub>3</sub> imperfections [33], and are apparent since  $V_0 > 0$  V for all measurements (dc and pulsed) and sweep directions (FWD and REV). The occupied trapped states, responsible for Dirac voltage shift ( $\Delta V_0$ ) and hysteresis, depend on pulse duration; shorter pulses limit the electrical stress time over which carriers can become trapped. We also observe that the (unified) Dirac voltage of the 400-ns pulsed sweep falls between that of the FWD and REV dc sweeps. These differences in  $V_0$  are consistent with hole traps charging up in the oxide (making it less negative) when  $V_{TG}$ is swept FWD starting in the hole region  $(V_{TG} < V_0)$ , and with electron traps accumulating during the REV sweep in the electron region ( $V_{TG} > V_0$ ) (making the oxide more negative). These additional trapped states in the oxide also contribute to the apparent variation of the channel resistance at  $V_0$  in dc sweeps by increasing the charge puddle density (i.e., increasing impurity or minimum carrier densities in the

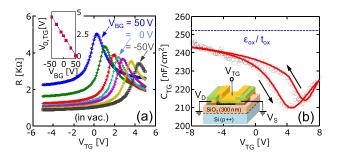

Fig. 4. (a) DC  $R-V_{TG}$  for different  $V_{BG}$  values ( $L\times W=5\times 5~\mu$ m,  $V_D=0.1~V$  for only FWD sweep is shown). Inset:  $V_{0,TG}$  versus  $V_{BG}$ . The slope represents the ratio between top and back-gate oxide capacitances ( $C_{0x}/C_{BG}\approx 22$ ). (b) Measured top-gate capacitance at 100 kHz ( $C_{TG}$ , circles) and calculated (red solid line) using model described in the text. Expected value from simpler extraction in (a) is also shown (dashed line). Inset shows schematic diagram of measurement.  $V_{TG}$  is applied to top gate, source/drain are grounded, and back gate is left disconnected. Side-wall and overlap capacitances that appear in parallel with  $C_{TG}$  were measured in similar FET structures without graphene, and subtracted from the result.

channel) [4]. In contrast, when using short pulses ( $< 1 \mu s$ ), less trapped states are disturbed, and  $V_0$  and  $R(V_{TG} = V_0)$  remain constant independent of sweep direction.

#### IV. GATE CAPACITANCE AND TRAP CHARGING EFFECTS

To estimate quantitatively oxide trapped charge densities responsible for hysteresis, we examine capacitance through measurements and modeling. First, we estimate the top dielectric capacitance, as suggested in [34], by measuring the topgate Dirac voltage  $(V_0, T_G)$  shift as a function of  $V_{BG}$ , in vacuum. As shown in Fig. 4(a), this yields the ratio between the top- and back-gate oxide capacitance,  $C_{\rm ox}/C_{\rm BG} \approx 22$ , which gives  $C_{\rm ox} \approx 250 \, {\rm nF/cm^2}$  and  $\varepsilon_{\rm ox} \approx 5.7 \, {\rm for our}$ top Al<sub>2</sub>O<sub>3</sub> dielectric with oxidized Al seeding layer. Next, we measure C-V characteristics [Fig. 4(b)] by applying dc and ac voltages to the top-gate terminal with an *LCR* meter. Away from the Dirac voltage,  $C_{TG}$  approaches the previously estimated top-layer capacitance ( $C_{ox} = \varepsilon_{ox}/t_{ox}$ ), while near  $V_0$ , it decreases and exhibits hysteresis similar to that observed in the I-V measurements (Fig. 3; C-V and I-V measurements used similar voltage sweep rates,  $\sim 1.6$  V/s.)

To estimate trapped charge densities in the top-gate dielectric quantitatively, we fit a *C-V* model by applying Gauss' law to our structure

$$V_{\text{TG}} - \left[V_0 + \frac{Q_{\text{it}}(E_F = 0)}{C_{\text{TG}}}\right] = -\frac{[Q_n(E_F) + Q_{\text{it}}(E_F)]}{C_{\text{TG}}} + \frac{E_F}{q}$$

(2)

where  $E_F$  is the Fermi level in graphene [Fig. 2(b)],  $Q_n$  is the charge density in graphene, and  $Q_{\rm it}$  is the sum of trapped charge accumulated at the  ${\rm AlO}_x$ /graphene interface and  ${\rm Al}_2{\rm O}_3$  bulk. Quantum capacitance  $(C_q)$  is included in our model explicitly in the carrier density  $[Q_n(E_F)]$  calculation by integrating over the density of states. The total capacitance  $(C_{\rm TG})$  is calculated [Fig. 4(b)] as a derivative of the total charge  $(Q_{\rm TG}=Q_n+Q_{\rm it})$  to the gate voltage by varying

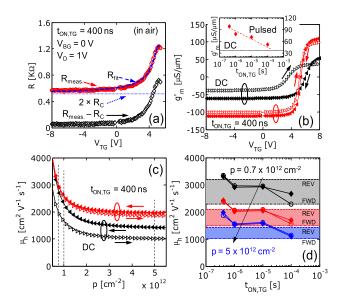

Fig. 5. (a) Hole  $R-V_{TG}$  measured  $(R_{meas})$ , fitted  $(R_{fit})$  as in [35], and with contact resistance  $(R_C)$  subtracted  $(R_{meas}-R_C)$ . (b) Intrinsic transconductance  $(g'_m)$  from Fig. 3(b), as a function of  $V_{TG}$  from pulsed (red)  $(r_{ON,TG}=400 \text{ ns})$  and dc (black) measurements. Arrows indicate direction (FWD or REV) of sweep. Inset shows maximum  $|g_m'|$  (from FWD sweeps) as a function of gate ON-times. (c) Extracted hole mobility as a function of carrier density (p) from Fig. 5(b). (d) Hole mobility versus  $t_{ON,TG}$  for different p=0.7 (black), 1 (red), and  $5\times10^{12}$  cm<sup>-2</sup> (blue). Values extracted from Fig. 5(c) at the marked (vertical dashed lines) concentrations. Open circles and solid diamonds are from FWD and REV pulsed sweeps, respectively. Values extracted from dc FWD and REV sweeps mark limits of shaded regions. Note large mobility uncertainty of dc sweeps (up to  $\sim1000 \text{ cm}^2\text{V}^{-1}\text{s}^{-1}$  or  $\sim30\%$ ) compared with pulsed sweeps ( $\sim50 \text{ cm}^2\text{V}^1\text{s}^1$  or  $\sim2\%$ ).

$E_F$ , such that

$$C_{\text{TG}} = \left(\frac{\partial Q_{\text{TG}}}{\partial E_F}\right) \left(\frac{\partial V_{\text{TG}}}{\partial E_F}\right)^{-1}.$$

(3)

From this model, we estimate (negatively charged) trap densities of  $7.2 \times 10^{11}$  and  $10^{12}$  cm<sup>-2</sup> for the FWD and REV sweeps, respectively, at  $E_F = 0$  eV (Dirac point).

#### V. PULSED MOBILITY EXTRACTION

Next, we extract device transconductance  $(g_m)$  and effective hole mobilities  $(\mu_h)$  from pulsed and dc measurements [Fig. 3(b)]. We do so by first fitting a transport model ( $R_{\rm fit}$ ) [4], [35], which includes contact resistance  $(R_C \approx 2-3 \text{ k}\Omega \cdot \mu\text{m})$ , to the measured  $I_D$ – $V_{TG}$  characteristics ( $R_{\text{meas}}$ ), as shown in Fig. 5(a). Fig. 5(b) then shows the intrinsic transconductance  $g_{m}$  (calculated after  $R_{C}$  is subtracted) derived from 400-ns pulsed measurements (red) and dc measurements (black) for FWD and REV sweep directions. We note that  $g_m$  changes sign as  $V_{TG}$  is swept past the Dirac point (i.e., threshold voltage) and carrier transport changes from holes to electrons. In addition, hysteresis is greatly reduced with 400-ns pulses compared with the dc measurement. Furthermore, the maximum value of  $g_m$ for pulsed measurements ( $\sim 100 \, \mu \text{S/}\mu \text{m}$ ) is approximately twice as high as the one obtained from dc measurements ( $\sim$ 50  $\mu$ S/ $\mu$ m). This trend is evident from the inset of Fig. 5(b),

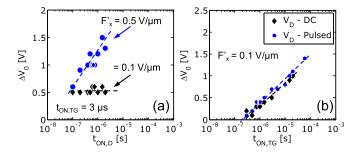

Fig. 6. (a) Dirac voltage shift  $(\Delta V_0)$  as a function of drain on-time  $(t_{\rm ON},D=100~{\rm ns}{-2}~\mu{\rm s}$  and  $t_{\rm ON},T_G=3~\mu{\rm s})$ . The  $V_{\rm TG}$  sweeps (not shown) are from -8 to 8 V and back to -8 V, while  $V_D$  is increased from 1 (black diamonds) to 3 V (blue circles).  $V_D$  values correspond to intrinsic lateral fields  $F_x'\approx0.1$  and 0.5 V/ $\mu{\rm m}$ , respectively, after contact resistance is subtracted ( $L\times W=3\times 9~\mu{\rm m})$ . (b)  $\Delta V_0$  versus  $t_{\rm ON},{\rm TG}$  (300 ns-80  $\mu{\rm s})$ . The drain terminal is biased using a dc (diamonds) and pulsed bias (circles) ( $F_x'=0.1$  V/ $\mu{\rm m}$  and  $t_{\rm ON},D=0.5\cdot t_{\rm ON},{\rm TG})$ .

which shows the maximum  $g_{m}$  (from FWD sweep) as a function of gate ON-time.

In Fig. 5(c), we show the effective mobility calculated as in [4] and [35]. We note that mobility values are approximate since  $R_C$  is fitted and not directly measured, and a constant  $C_{\rm ox}$  was used to simplify the extraction procedure. Nevertheless, this exercise illustrates the consistency and reliability of pulsed characterization versus dc measurements. We show hole mobility  $(\mu_h)$  versus carrier density for 400-ns pulses (red) and dc measurements (black), from FWD and REV sweeps. Pulsed measurements generate higher and consistent mobility values, due to reduced charge trapping. Conversely, mobility appears to be a function of sweep direction (marked with arrows) when obtained from dc I-V measurements. We note that self-heating effects do not play a role because the mobility estimates are all done at low lateral field and low current levels,  $\sim 0.06$  mA/ $\mu$ m, where the maximum temperature rise is at most 5 K for our GFETs [4], [32], even for the dc measurements.

Subsequently, we examine mobility dependence on  $t_{\rm ON,TG}$ . Fig. 5(d) shows  $\mu_h$  at three carrier densities: 0.7, 1, and  $5\times 10^{12}$  cm<sup>-2</sup>; open circles and solid diamonds represent values from FWD and REV sweeps. The mobility range from dc measurements (top and bottom lines of shaded regions) has an uncertainty up to  $1000~{\rm cm^2V^{-1}s^{-1}}$  (or  $\sim 30\%$ ), while for pulsed characterization, this uncertainty is significantly smaller ( $\sim 50~{\rm cm^2V^{-1}s^{-1}}$  or  $\sim 2\%$ ). Once again, we note that mobility is higher at shorter pulses, due to the minimized trapped charge.

# VI. HIGH FIELD EFFECTS

We also briefly examine the effects of high lateral intrinsic fields  $F_{x'}$  (after subtracting  $R_C$ ) on  $\Delta V_0$  using our nanosecond pulsed technique. First, we find that for  $F_x' \sim 0.1 \text{ V}/\mu\text{m}$  and a constant  $t_{\text{ON,TG}}$  (3  $\mu$ s),  $\Delta V_0$  remains constant as we decrease  $t_{\text{ON,D}}$  from 2  $\mu$ s down to 100 ns [Fig. 6(a)]. Conversely, when we raise  $F_{x'}$  to 0.5 V/ $\mu$ m,  $\Delta V_0$  drastically increases as well. This increased  $\Delta V_0$  caused by higher  $F_x'$  occurs when hot carriers in the channel begin to fill interface or bulk trap states of the dielectric [23]. Finally, we examine  $\Delta V_0$  as we decrease

$t_{\rm ON,TG}$  and replace the pulse generator at the drain terminal with a regular dc supply. We find that, at low  $F_x$ ,  $\Delta V_0$  is equally suppressed using a pulsed or a dc voltage at the drain terminal [Fig. 6(b)].

In general, GFET hysteresis is a function of the amount of trapped charge at the interface and bulk of the dielectric  $(Q_{it})$ , which in turn affects the overall charge in the channel, capacitance, and ultimately I-V results. In addition,  $Q_{it}$  is a function of frequency, gate voltage  $(V_{TG} \text{ or } V_{BG})$ , and intrinsic lateral field  $(F'_x)$ . Thus, to eliminate hysteresis and Dirac voltage instabilities during measurements, one should consider these dependencies and bias devices accordingly.

## VII. CONCLUSION

In conclusion, intrinsic properties of GFETs can be probed with pulsed operation and pulses shorter than the trapping time constants of interface and bulk trapping. We also report transfer characteristics, transconductance, and mobility values that do not depend on voltage sweep direction (FWD or REV) or rate. Such results correctly represent the intrinsic properties of the GFET channel, as detrimental effects from oxide and interface traps (hysteresis and  $I_D$  degradation) can be greatly reduced. Finally, we show that high lateral fields can affect hysteresis and charge trapping through hot-carrier injection, a situation that can also be mitigated using short drain ON-times. All of these findings shed light on careful ways to characterize graphene devices and reduce detrimental effects using pulsed measurements, which is important for future advancement of graphene device technology.

# REFERENCES

- [1] F. Schwierz, "Graphene transistors: Status, prospects, and problems," *Proc. IEEE*, vol. 101, no. 7, pp. 1567–1584, Jul. 2013.

- [2] S. K. Banerjee et al., "Graphene for CMOS and beyond CMOS applications," Proc. IEEE, vol. 98, no. 12, pp. 2032–2046, Dec. 2010.

- [3] S. V. Morozov et al., "Giant intrinsic carrier mobilities in graphene and its bilayer," Phys. Rev. Lett., vol. 100, no. 1, p. 016602, 2008.

- [4] V. E. Dorgan, M.-H. Bae, and E. Pop, "Mobility and saturation velocity in graphene on SiO<sub>2</sub>," *Appl. Phys. Lett.*, vol. 97, no. 8, pp. 082112-1–082112-3, 2010.

- [5] J. A. del Alamo, "Nanometre-scale electronics with III-V compound semiconductors," *Nature*, vol. 479, pp. 317–323, Nov. 2011.

- [6] S.-J. Han, K. A. Jenkins, A. V. Garcia, A. D. Franklin, A. A. Bol, and W. Haensch, "High-frequency graphene voltage amplifier," *Nano Lett.*, vol. 11, no. 9, pp. 3690–3693, 2011.

- [7] E. Guerriero, L. Polloni, L. G. Rizzi, M. Bianchi, G. Mondello, and R. Sordan, "Graphene audio voltage amplifier," *Small*, vol. 8, no. 3, pp. 357–361, 2012.

- [8] L. G. Rizzi et al., "Cascading wafer-scale integrated graphene complementary inverters under ambient conditions," Nano Lett., vol. 12, no. 8, pp. 3948–3953, 2012.

- [9] E. Guerriero et al., "Gigahertz integrated graphene ring oscillators," ACS Nano, vol. 7, no. 6, pp. 5588–5594, 2013.

- [10] W. Han, A. Hsu, J. Wu, K. Jing, and T. Palacios, "Graphene-based ambipolar RF mixers," *IEEE Electron Device Lett.*, vol. 31, no. 9, pp. 906–908, Sep. 2010.

- [11] O. Habibpour, S. Cherednichenko, J. Vukusic, K. Yhland, and J. Stake, "A subharmonic graphene FET mixer," *IEEE Electron Device Lett.*, vol. 33, no. 1, pp. 71–73, Jan. 2012.

- [12] L. Liao et al., "Scalable fabrication of self-aligned graphene transistors and circuits on glass," Nano Lett., vol. 12, no. 6, pp. 2653–2657, 2011.

- [13] Y.-M. Lin et al., "Wafer-scale graphene integrated circuit," Science, vol. 332, pp. 1294–1297, Jun. 2011.

- [14] Y. G. Lee et al., "Fast transient charging at the graphene/SiO<sub>2</sub> interface causing hysteretic device characteristics," Appl. Phys. Lett., vol. 98, no. 18, pp. 183508-1–183508-3, 2011.

- [15] H. Wang, Y. Wu, C. Cong, J. Shang, and T. Yu, "Hysteresis of electronic transport in graphene transistors," ACS Nano, vol. 4, no. 12, pp. 7221–7228, 2010.

- [16] Y. G. Lee et al., "Influence of extrinsic factors on accuracy of mobility extraction in graphene metal-oxide-semiconductor field effect transistors," Appl. Phys. Lett., vol. 102, no. 9, pp. 093121-1–093121-4, 2013.

- [17] P. Joshi, H. E. Romero, A. T. Neal, V. K. Toutam, and S. A. Tadigadapa, "Intrinsic doping and gate hysteresis in graphene field effect devices fabricated on SiO<sub>2</sub> substrates," *J. Phys., Condensed Matter*, vol. 22, no. 33, p. 334214, 2010.

- [18] T. Lohmann, K. von Klitzing, and J. H. Smet, "Four-terminal magneto-transport in graphene p-n junctions created by spatially selective doping," *Nano Lett.*, vol. 9, no. 5, pp. 1973–1979, 2009.

- [19] V. E. Dorgan, A. Behnam, H. J. Conley, K. I. Bolotin, and E. Pop, "High-field electrical and thermal transport in suspended graphene," *Nano Lett.*, vol. 13, no. 13, pp. 4581–4586, 2013.

- [20] B. E. Deal, "The current understanding of charges in the thermally oxidized silicon structure," *J. Electrochem. Soc.*, vol. 121, no. 6, pp. 198–205, 1974.

- [21] G. Ribes et al., "Review on high-k dielectrics reliability issues," IEEE Trans. Device Mater. Rel., vol. 5, no. 1, pp. 5–19, Mar. 2005.

- [22] S. Zafar, A. Kumar, E. Gusev, and E. Cartier, "Threshold voltage instabilities in high-k gate dielectric stacks," *IEEE Trans. Device Mater. Rel.*, vol. 5, no. 1, pp. 45–64, Mar. 2005.

- [23] I. Meric et al., "Channel length scaling in graphene field-effect transistors studied with pulsed current-voltage measurements," Nano Lett., vol. 11, no. 3, pp. 1093–1097, 2011.

- [24] A. Behnam et al., "Transport in nanoribbon interconnects obtained from graphene grown by chemical vapor deposition," Nano Lett., vol. 12, no. 9, pp. 4424–4430, 2012.

- [25] Z. Cheng, Q. Zhou, C. Wang, Q. Li, C. Wang, and Y. Fang, "Toward intrinsic graphene surfaces: A systematic study on thermal annealing and wet-chemical treatment of SiO<sub>2</sub>-supported graphene devices," *Nano Lett.*, vol. 11, no. 2, pp. 767–771, 2011.

- [26] Y. K. Koh, M.-H. Bae, D. G. Cahill, and E. Pop, "Reliably counting atomic planes of few-layer graphene (n > 4)," ACS Nano, vol. 5, no. 1, pp. 269–274, 2010.

- [27] L. G. Cancado *et al.*, "General equation for the determination of the crystallite size L<sub>a</sub> of nanographite by Raman spectroscopy," *Appl. Phys. Lett.*, vol. 88, no. 16, pp. 163106-1–163106-3, 2006.

- [28] J. C. Koepke et al., "Atomic-scale evidence for potential barriers and strong carrier scattering at graphene grain boundaries: A scanning tunneling microscopy study," ACS Nano, vol. 7, no. 1, pp. 75–86, 2013.

- [29] D. Estrada, S. Dutta, A. Liao, and E. Pop, "Reduction of hysteresis for carbon nanotube mobility measurements using pulsed characterization," *Nanotechnology*, vol. 21, no. 8, p. 085702, 2010.

- [30] H. Madan, M. J. Hollander, J. A. Robinson, and S. Datta, "Extraction of near interface trap density in top gated graphene transistor using high frequency current voltage characteristics," in *Proc. DRC 70th Annu.*, 2012, pp. 181–182.

- [31] G. I. Zebrev, E. V. Melnik, and A. A. Tselykovskiy, "Influence of interface traps and electron-hole puddles on quantum capacitance and conductivity in graphene field-effect transistors," arXiv cond-mat: 1011.5127, 2011.

- [32] S. Islam, L. Zuanyi, V. E. Dorgan, B. Myung-Ho, and E. Pop, "Role of joule heating on current saturation and transient behavior of graphene transistors," *IEEE Electron Device Lett.*, vol. 34, no. 2, pp. 166–168, Feb. 2013

- [33] J. J. H. Gielis, B. Hoex, M. C. M. van de Sanden, and W. M. M. Kessels, "Negative charge and charging dynamics in Al<sub>2</sub>O<sub>3</sub> films on Si characterized by second-harmonic generation," *J. Appl. Phys.*, vol. 104, no. 7, pp. 073701-1–073701-5, Oct. 2008.

- [34] S. Kim et al., "Realization of a high mobility dual-gated graphene field-effect transistor with Al<sub>2</sub>O<sub>3</sub> dielectric," Appl. Phys. Lett., vol. 94, no. 6, pp. 062107-1–062107-3, 2009.

- [35] M.-H. Bae, S. Islam, V. E. Dorgan, and E. Pop, "Scaling of high-field transport and localized heating in graphene transistors," ACS Nano, vol. 5, no. 10, pp. 7936–7944, 2011.