# A Fast Remotely Operable Digital Twin of a Generic Electric Powertrain for Geographically Distributed Hardware-in-the-Loop Simulation Testbed

Surojit Sen, MSc.

Submitted to the University of Nottingham for the degree of Doctor of Philosophy,

January 2022

## i. Abstract

The automotive industry today is seeing far-reaching and portentous changes that will change the face of it in the foreseeable future. Digitalisation and Electrification are two of the key megatrends that is changing the way vehicles are developed and produced. A recent development in R&D process is the Hardware-in-the-Loop (HIL) method that uses a hybrid approach of testing a physical prototype immersed in a virtual environment, which is nowadays being creatively re-applied towards geographically separated multi-centre testing strategies, that suits the horizontally integrated and supply-chain driven industry very well. Geographical separation entails the deployment of a "Digital Twin" in remote centre(s) participating in multicentre testing. This PhD aims to produce a highly robust, efficient, and rapidly computable Digital Twin of a generic electric powertrain using the multi-frequency averaging (MFA) technique that has been extended for variable frequency operation. This PhD also aims to commission a local HIL simulation testbed for a generic electric power inverter testing. The greater goal is to cosimulate the local HIL centre testing a prototype inverter, and its Digital Twin in a different location "twinning" the prototype inverter as best as possible.

A novel approach for the Digital Twin has been proposed that employs Dynamic Phasors to solve the system in the frequency domain. An original method of multiplication of two signals in the frequency domain has been proposed. The resultant model has been verified against an equivalent time domain switching model and shown to outperform appreciably. A distinctive advantage the MFA Digital Twin offers is the "fidelity customisability"; based on application, the Twin can be set to compute a low (or high)-fi model at different computational cost. Finally, a novel method of communicating high-speed motor shaft position information using a low-speed processing system has been developed and validated. This has been applied to run real-life HIL simulation cycles on a test inverter and effects studied.

The two ends of a multi-HIL testbed, i.e., local HIL environment for an inverter, and its Digital Twin, has been developed and validated. The last piece of the puzzle, i.e., employing a State Convergence algorithm to ensure the Digital Twin is accurate duplicating the performance of its "master", is required to close the loop. Several ideas and process plans have been proposed to do the same.

## ii. Acknowledgements

First and foremost, I wish to express heartfelt gratitude for my parents, Susmita and Abhijit, and my brother, Sanket, for having faith in me and providing unending encouragement and emotional support. My family has been my support system over these years, and I cannot imagine finishing this PhD without them. I must also thank Shreeja for offering much needed support in the last year and cheering me on to the finish line.

I would like to thank my two supervisors, Dr Paul L Evans for his continued academic support and help with day-to-day challenges, and Prof C Mark Johnson for granting me the opportunity to study this topic and giving a strong direction to this PhD. I would also like to thank my moderation supervisor Dr Serhiy Bozhko for keeping my progress in check periodically and offering an outside perspective to various problems during the study. I also appreciate the technical support provided by the department's technician and safety team (Mr Colin Blackburn, Mr Chris Varley, Mr Dan Bathgate, and others). Lastly, I also appreciate the customer support provided by the Triphase (now a part of National Instruments) technical team in ironing out the bugs in the simulator rig.

# iii. Contents

| i.      | Abst     | ract                                                         | 2  |

|---------|----------|--------------------------------------------------------------|----|

| ii.     | Ackn     | owledgements                                                 | 3  |

| iii.    | Cont     | ents                                                         | 4  |

| iv.     | List o   | of Figures                                                   | 9  |

| v.      | List o   | of Tables                                                    | 18 |

| vi.     | List o   | of Abbreviations                                             | 19 |

| CHAPTER | R1 Intro | duction                                                      | 23 |

|         | 1.1      | Automotive industry – Past, Present and Future               | 23 |

|         | 1.2      | Key Technological Enablers of Electrification                | 26 |

|         | 1.3      | Key Challenges in Engineering a Modern Car                   | 29 |

|         | 1.4      | Virtually Connected Hybrid Vehicle                           | 31 |

|         | 1.5      | Intent and Novelty of this PhD Project                       | 33 |

|         | 1.6      | Thesis Structure Guideline                                   | 37 |

| CHAPTER | R2 Geog  | raphically Distributed Power Hardware-In-The-Loop Simulation | 39 |

|         | 2.1      | Introduction                                                 | 39 |

|         | 2.2      | Hardware-in-the-Loop Simulation                              | 40 |

|         | 2.2.1    | Introduction                                                 | 40 |

|         | 2.2.2    | A Brief History of HIL Simulation                            | 43 |

|         | 2.2.3    | Deconstruction and Requirements                              | 46 |

|         | 2.2.4    | Necessity and New Opportunities                              | 49 |

|         | 2.2.5    | Case Studies                                                 | 51 |

|         | 2.3      | Power-HIL Simulation for Electric Powertrain Applications    | 55 |

|        | 2.3.1   | Introduction                                          | 55  |

|--------|---------|-------------------------------------------------------|-----|

|        | 2.3.2   | A Brief History of Power-HIL Simulation               | 57  |

|        | 2.3.3   | Deconstruction and Requirements                       | 58  |

|        | 2.3.4   | Available Equipment and Solutions                     | 63  |

|        | 2.3.5   | Case Studies                                          | 70  |

|        | 2.4     | HIL Simulation Across Geography                       | 77  |

|        | 2.4.1   | Introduction                                          | 77  |

|        | 2.4.2   | Case Studies                                          | 79  |

|        | 2.5     | Summary                                               | 87  |

| СНАРТЕ | R3 Powe | er Electronics and Drives Modelling Techniques        | 90  |

|        | 3.1     | Introduction                                          | 90  |

|        | 3.2     | Different Approaches for Inter-Location Communication | 90  |

|        | 3.2.1   | Introduction                                          | 90  |

|        | 3.2.2   | Direct Exchange of Interface Variables                | 91  |

|        | 3.2.3   | Exchanging Dynamic Phasors                            | 92  |

|        | 3.2.4   | Local Digital Twin                                    | 94  |

|        | 3.3     | Digital Twin Approaches                               | 95  |

|        | 3.3.1   | Introduction to Digital Twin                          | 95  |

|        | 3.3.2   | Modelling strategy                                    | 96  |

|        | 3.3.3   | Hardware Platform (CPU v FPGA v GPU)                  | 98  |

|        | 3.3.4   | Non-Linear Modeling                                   | 100 |

|        | 3.3.5   | Resistive Companion Form (RCF) Model                  | 100 |

|        | 3.3.6   | State-Space Averaging (SSA) Model                     | 103 |

|        | 3.3.7   | Multi-Frequency Averaging (MFA) Model                 | 105 |

|        | 3.4     | Summary                                               | 106 |

|        | Averaging Technique 108                                           |

|--------|-------------------------------------------------------------------|

| 4.1    | Introduction108                                                   |

| 4.2    | Theory of MFA Digital Twin109                                     |

| 4.2.1  | Dynamic Phasors109                                                |

| 4.2.2  | Mathematical Framework for MFA Model112                           |

| 4.2.3  | Variable Frequency Operation114                                   |

| 4.2.4  | "Modified Convolution" for Multiplication-Equivalent in Frequency |

| Domain |                                                                   |

| 4.3    | System of State                                                   |

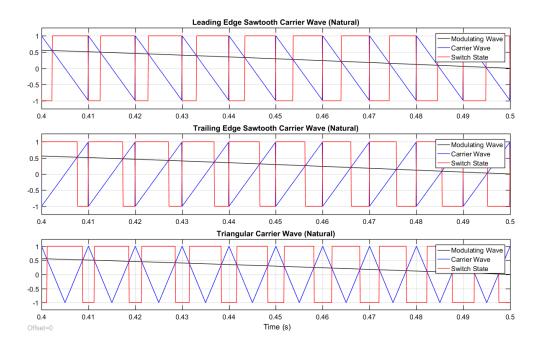

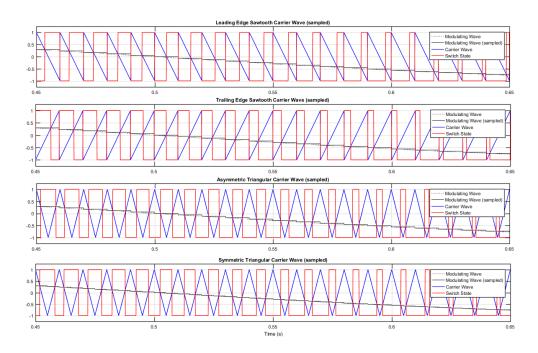

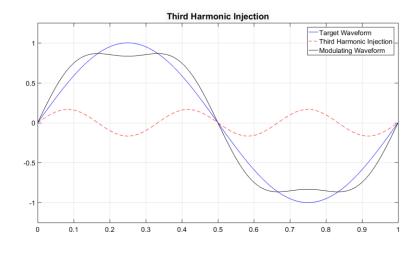

| 4.3.1  | Different PWM schemes for PECs120                                 |

| 4.3.2  | Switching Function (Double Fourier Series Representation). 125    |

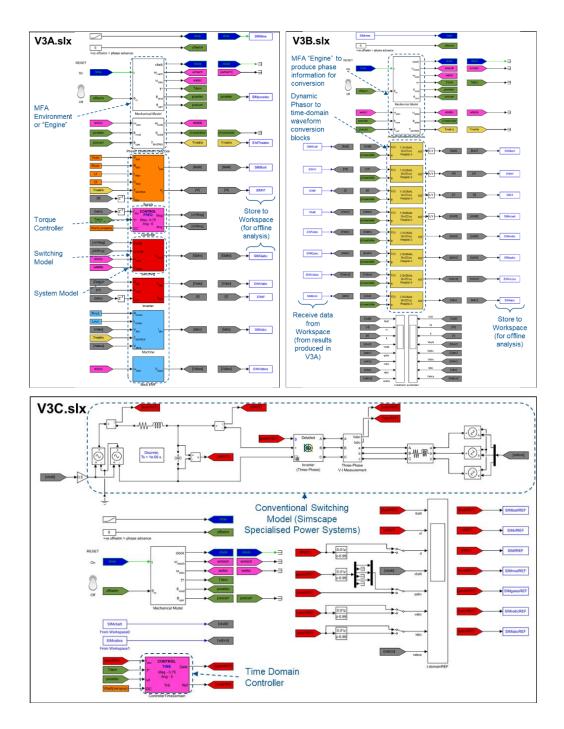

| 4.4    | MATLAB/Simulink™ Implementation of MFA Digital Twin134            |

| 4.4.1  | MFA Environment or "Engine"136                                    |

| 4.4.2  | System Model137                                                   |

| 4.4.3  | "Modified Convolution" 140                                        |

| 4.4.4  | Phase to Time Conversion (V3B.slx)141                             |

| 4.5    | Simulation Results (Steady State)141                              |

| 4.5.1  | Simulation Setup142                                               |

| 4.5.2  | Simulation Run-Time Comparison144                                 |

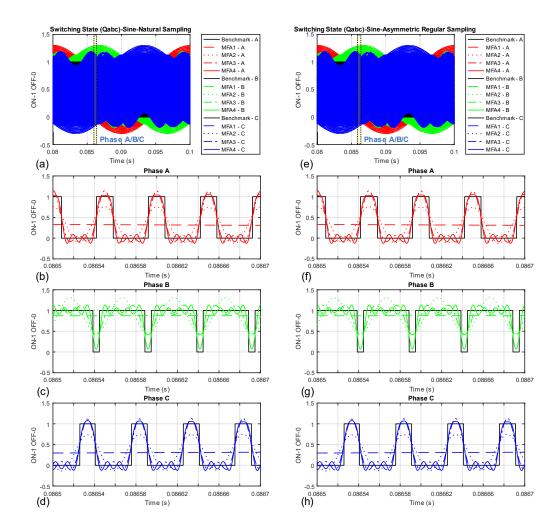

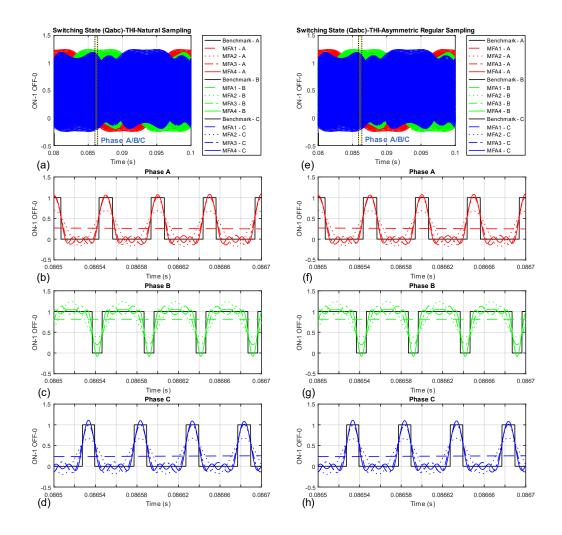

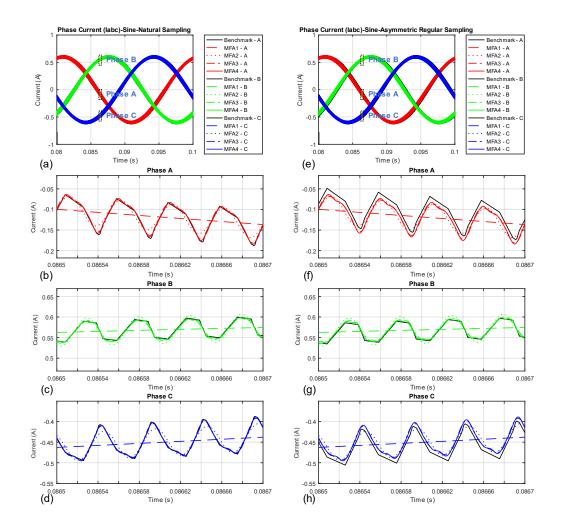

| 4.5.3  | Waveforms Comparison (Time domain)145                             |

| 4.5.4  | Waveforms Comparison (Frequency Domain)                           |

| 4.6    | Simulation Results (Variable Frequency)169                        |

| 4.6.1  | Simulation Setup170                                               |

| 4.6.2  | Waveforms Comparison (Time domain)170                             |

CHAPTER 4 Digital Twin of an Electric Powertrain Emulation using Multi-Frequency

|         | 4.7      | Summary                                                | .172  |

|---------|----------|--------------------------------------------------------|-------|

| CHAPTER | 85 Local | Motor Emulation                                        | 174   |

|         | 5.1      | Introduction                                           | .174  |

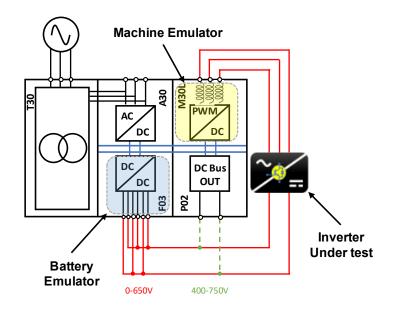

|         | 5.2      | Triphase Real-Time P-HIL Simulator                     | .174  |

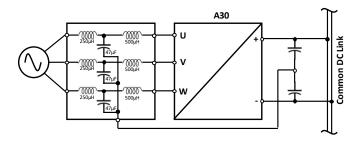

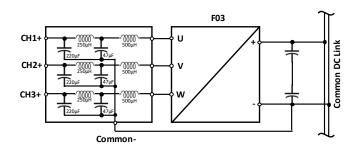

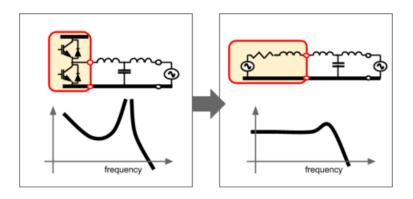

|         | 5.2.1    | Filter Stage                                           | . 176 |

|         | 5.2.2    | Virtual Circuit Emulation                              | . 178 |

|         | 5.2.3    | Real-Time-Target (RTT) PC and Underlying Software      | . 179 |

|         | 5.2.4    | EtherCAT Module                                        | . 179 |

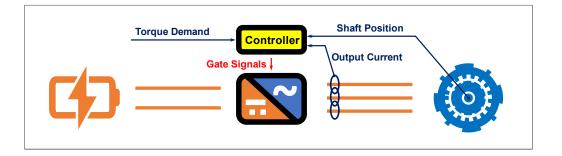

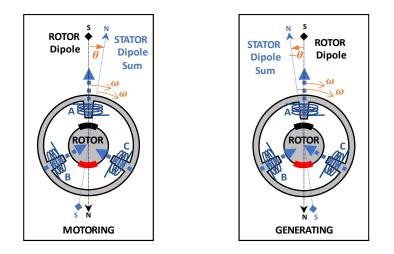

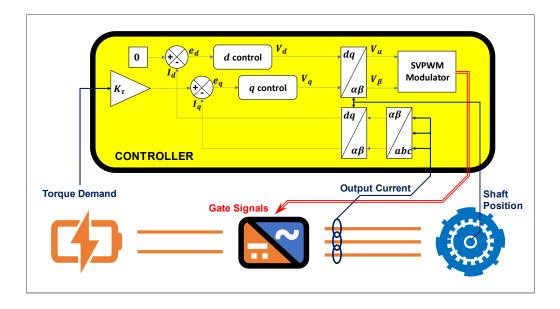

|         | 5.3      | Permanent Magnet Synchronous Machine Control Theory    | .180  |

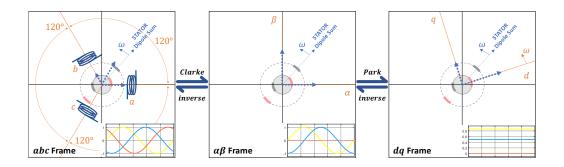

|         | 5.3.1    | Clarke and Park Transforms                             | . 181 |

|         | 5.3.2    | Control System                                         | . 183 |

|         | 5.3.3    | Modulator                                              | . 183 |

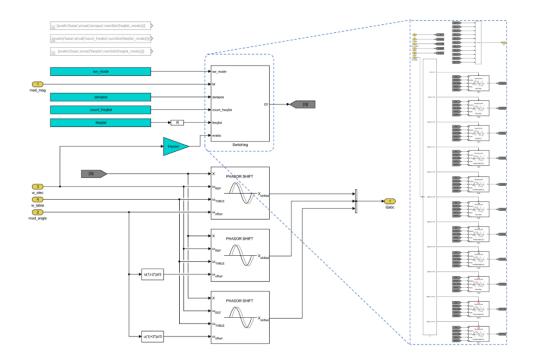

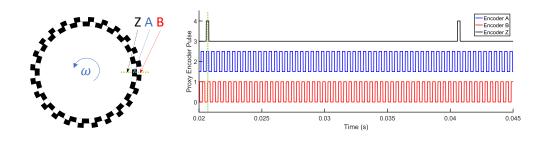

|         | 5.4      | Encoder Emulation – ABZ Type                           | .184  |

|         | 5.4.1    | Theory of Encoder                                      | . 184 |

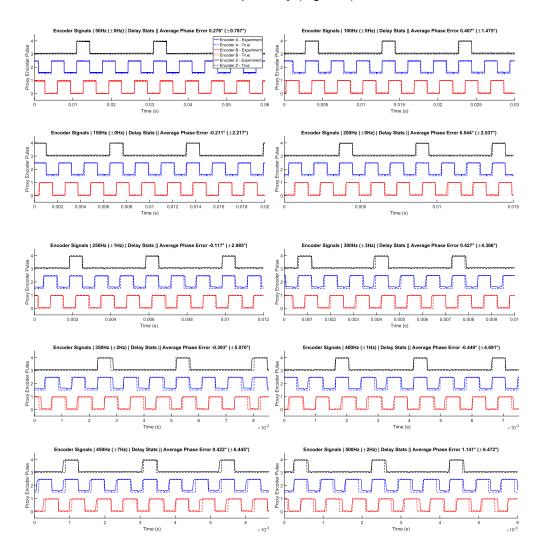

|         | 5.4.2    | Encoder Emulation in Digital HIL Simulator             | . 185 |

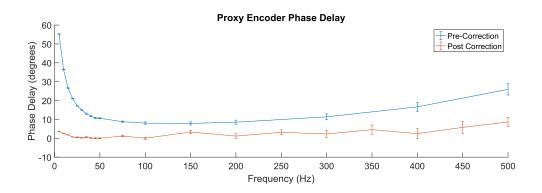

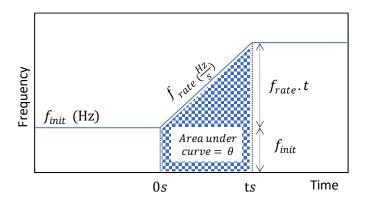

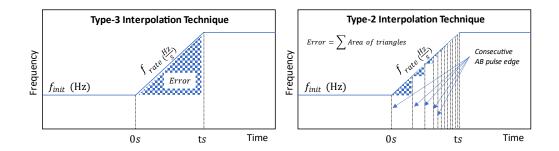

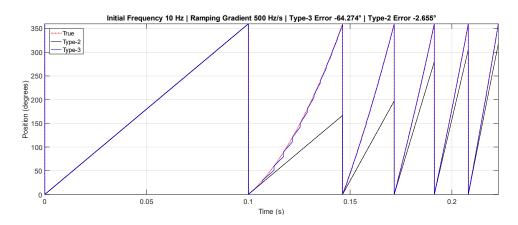

|         | 5.4.3    | Phase Delay Compensation in Proxy Encoder Signal Gener | rator |

|         |          |                                                        | . 193 |

|         | 5.5      | Discussion                                             | .195  |

|         | 5.6      | Summary                                                | .198  |

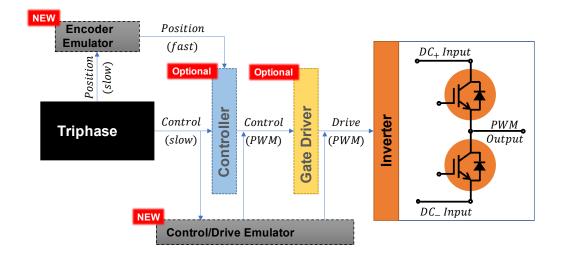

| CHAPTER | 86 Powe  | r-HIL Simulation with Real Inverter-Under-Test         | 200   |

|         | 6.1      | Introduction                                           | .200  |

|         | 6.2      | Experimental Setup                                     | .200  |

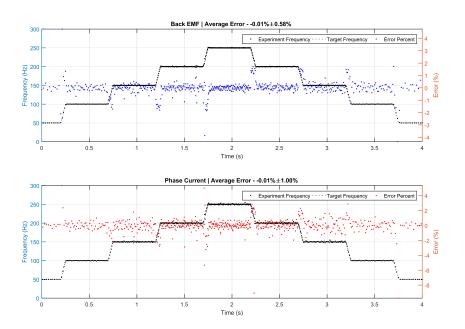

|         | 6.3      | Fixed Frequency Operation                              | .204  |

|         | 6.4      | Variable Frequency Operation                           | .206  |

|         | 6.5      | Discussion                                             | .217  |

| vii.    | Refer   | ences                                        | 233 |

|---------|---------|----------------------------------------------|-----|

|         | 7.4     | Future Work                                  | 230 |

|         | 7.3     | Novel Contributions to Research              | 229 |

|         | 7.2.3   | Digital Twin                                 | 229 |

|         | 7.2.2   | Multifrequency Averaging and Dynamic Phasors | 228 |

|         | 7.2.1   | Hardware-in-the-Loop                         | 227 |

|         | 7.2     | Discussion                                   | 227 |

|         | 7.1     | Introduction                                 | 225 |

| CHAPTER | 7 Concl | usions                                       | 225 |

|         | 6.6     | Summary                                      | 223 |

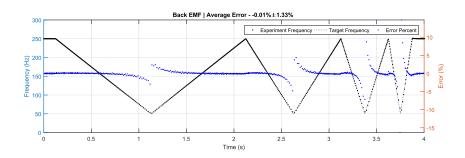

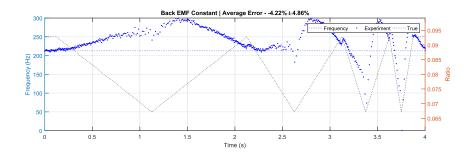

|         | 6.5.2   | Back EMF Voltage Fidelity                    | 221 |

|         | 6.5.1   | Frequency Profile Fidelity                   | 217 |

# iv. List of Figures

| Fig 1-1 Ford Model T Touring Car from 1925 [4]23                                             |

|----------------------------------------------------------------------------------------------|

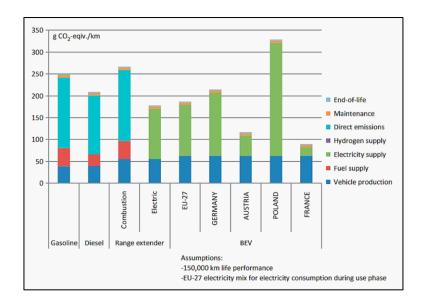

| Fig 1-2 Lifetime greenhouse gas (GHG) emissions of types of vehicles and sub-divided         |

| by countries for Battery Electric Vehicles (BEV) [8]26                                       |

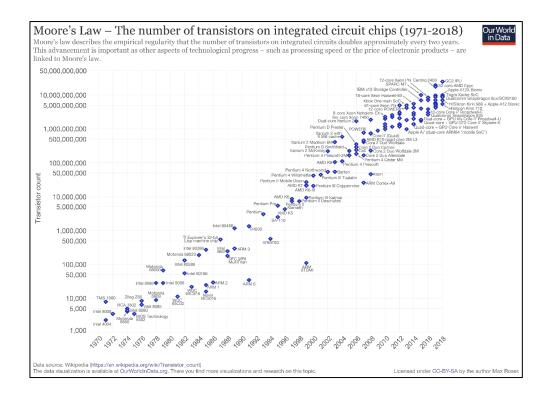

| Fig 1-3 Moore's Law - The number of transistors on integrated circuit chips (1971-2018)      |

| [12]                                                                                         |

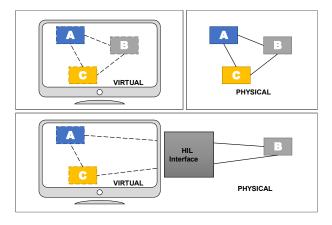

| Fig 1-4 Underlying concept of Hardware-in-the-Loop (HIL) - Hybrid of real and virtual        |

| systems operating in tandem                                                                  |

| Fig 1-5 Suppliers to the Opel/Vauxhall Insignia, demonstrating the hugely scattered          |

| supply chain network in the automotive industry [13]                                         |

| Fig 1-6 Underlying concept of Geographically Distributed Hardware-in-the-Loop (GD-           |

| HIL) - HIL centres in separate locations operating in tandem                                 |

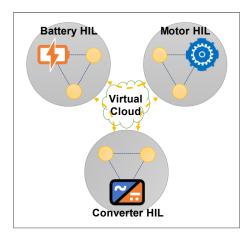

| Fig 1-7 Proposed multi-centre GD-HIL virtual simulation testbed                              |

| Fig 1-8 Concept of local "surrogate" model dealing with instantaneous responses              |

| locally, periodically realigned by actual model over remote communication                    |

| Fig 1-9 Different levels of fidelity of original signal may be required at different centres |

| for their respective application                                                             |

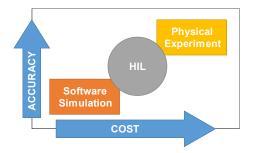

| Fig 2-1 System-V approach to development process from concept to product41                   |

| Fig 2-2 Experimental Cost v Accuracy depiction of prototype validation using software,       |

| HIL, and physical experimentation42                                                          |

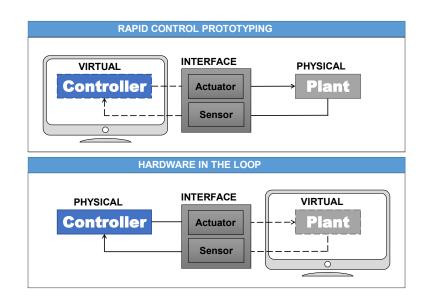

| Fig 2-3 Conceptual distinction between Rapid Prototyping (RP) and Hardware-in-the-           |

| Loop (HIL)                                                                                   |

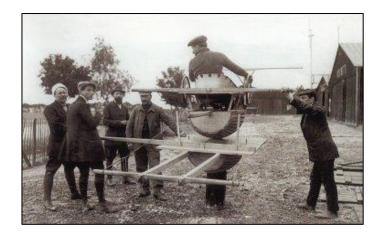

| Fig 2-4 "Antoinette's Barrel", one of the earliest HIL simulator concepts from 1910s [36]    |

|                                                                                              |

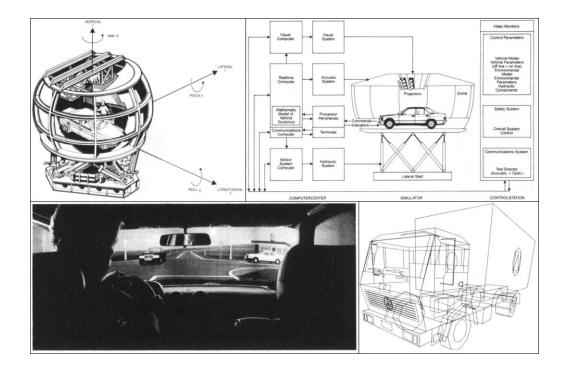

| Fig 2-5 One of the first vehicle cabin simulator from the 80s developed by Daimler Benz      |

| [37]                                                                                         |

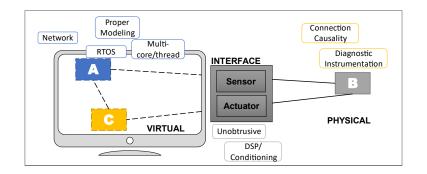

| Fig 2-6 Three key areas of HIL simulation – Virtual Environment, Physical Prototype,         |

| and Interface [47]                                                                           |

| Fig 2-7 PWM-actuated fuel injector solenoid53                                                |

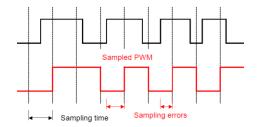

| Fig 2-8 Digital sampling of physical signal at a limited/restricted bandwidth introducing |

|-------------------------------------------------------------------------------------------|

| sampling error [25]54                                                                     |

| Fig 2-9 OPAL-RT™ motor drive simulator types and characteristics [54]55                   |

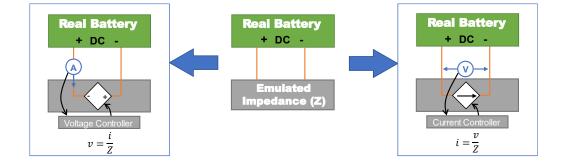

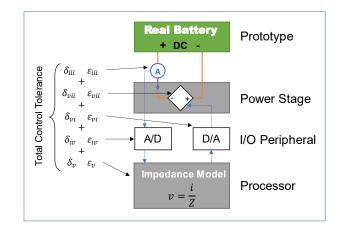

| Fig 2-10 Two ways of DC load emulation – voltage-controlled v current-controlled 59       |

| Fig 2-11 Total round-trip-time in load emualtion control breakdown61                      |

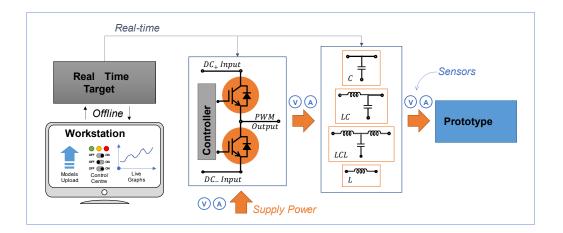

| Fig 2-12 Overall layout of a generic power-HIL simulator rig64                            |

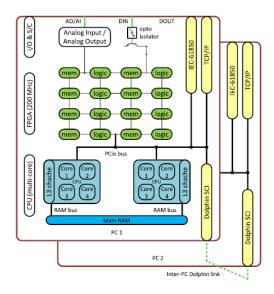

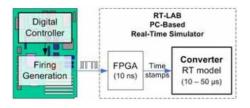

| Fig 2-13 OPAL-RT™ power-HIL simulator rig control overview [62]65                         |

| Fig 2-14 Example use of FPGA "expansion" board in HIL simulator setup to transform        |

| between high-bandwidth and low bandwidth signals [25]65                                   |

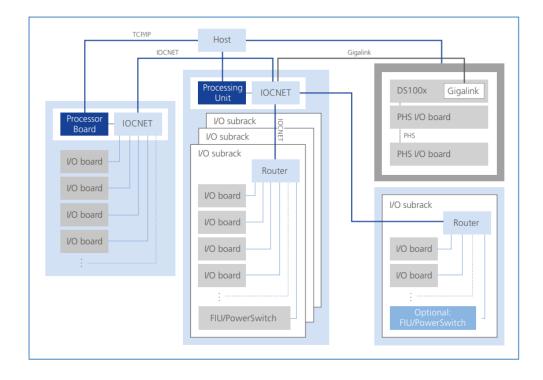

| Fig 2-15 Scalability achievable using the SCALEXIO™ architecture available from           |

| dSPACE™ [67]67                                                                            |

| Fig 2-16 Typical power-HIL simulator layout from dSPACE™ [68]68                           |

| Fig 2-17 Generic block-style "power stages" offered by Triphase to "build-your-own"       |

| power-HIL simulator rig69                                                                 |

| Fig 2-18 Triphase power-HIL simulator rig as configured and procured from Triphase        |

| for this PhD70                                                                            |

| Fig 2-19 Replication of simple linear electric circuit in power-HIL simulator setup using |

| the Ideal Transformer Method (ITM) [58]71                                                 |

| Fig 2-20 Power-HIL simulation approach using the Transmission Line Model (TLM) [58]       |

|                                                                                           |

| Fig 2-21 Power-HIL simulation approach using the Partial Circuit Duplication (PCD) [58]   |

|                                                                                           |

| Fig 2-22 Power-HIL simulation approach using the Damping Impedance Method (DIM)           |

| [58]                                                                                      |

| Fig 2-23 P-HIL interface "transparency" characterisation as observed in [56]73            |

| Fig 2-24 P-HIL interface "transparency" characterisation experimental setup in [56].73    |

| Fig 2-25 P-HIL interface "transparency" characterisation "noise" injection in [56]74      |

| Fig 2-26 Overview layout of motor emulation using two back-to-back converter bridges      |

| (CB) [74][75]75                                                                           |

| Fig 2-27 Novel method to read high-frequency voltage PWM waveforms using low-             |

|-------------------------------------------------------------------------------------------|

| frequency processor [74][75]76                                                            |

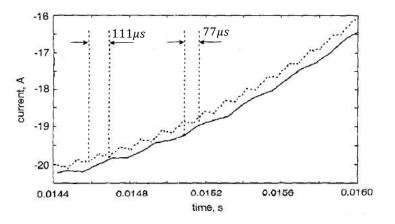

| Fig 2-28 Current waveform Effect of using the "integrate-and-sample" method for           |

| measuring high-frequency waveforms using low-frequency processor [74][75]76               |

| Fig 2-29 Geographically distributed simulation application in the US military with two    |

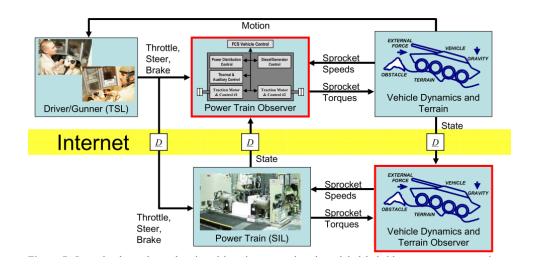

| locations co-simulated [79]-[81]80                                                        |

| Fig 2-30 Geographically distributed simulation application in the US military system      |

| architecture [79]-[81]81                                                                  |

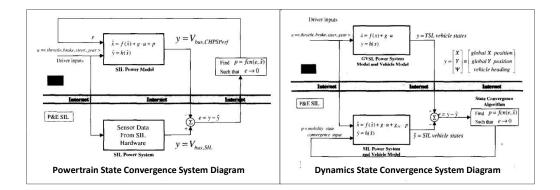

| Fig 2-31 State Convergence Model for the Powertrain and Dynamics control systems          |

| in US Military GD-HIL testbed [79]-[81]82                                                 |

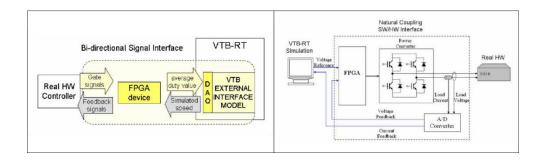

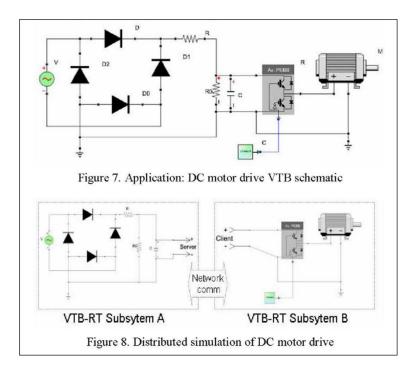

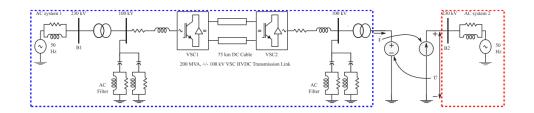

| Fig 2-32 Virtual Test Bed - Real Time (VTB-RT) GD-HIL architecture [87]- [90]84           |

| Fig 2-33 Virtual Test Bed - Real Time (VTB-RT) GD-HIL typical example experiment          |

| [87]- [90]85                                                                              |

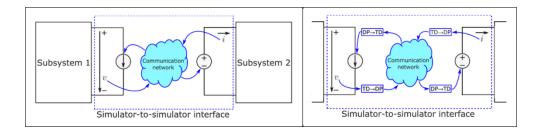

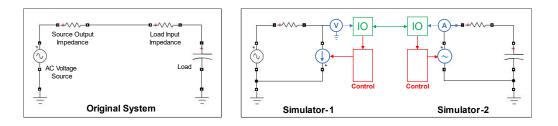

| Fig 2-34 Use of frequency domain representations of interfacing variables in the Global   |

| Real-Time Superlab project [92]- [93]86                                                   |

| Fig 2-35 ITM coupling method used in the Global RT Superlab project [92]- [93]86          |

| Fig 2-36 Globally distributed HIL experimental testbed offered in the Global RT           |

| Superlab project [92]- [93]87                                                             |

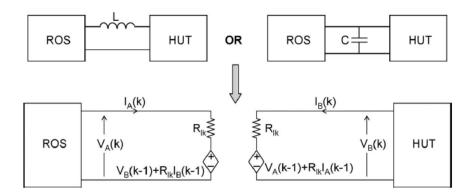

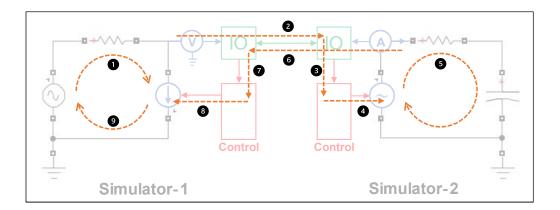

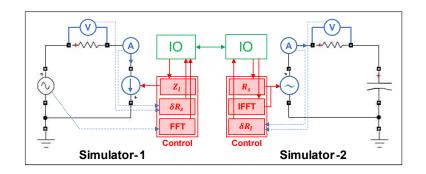

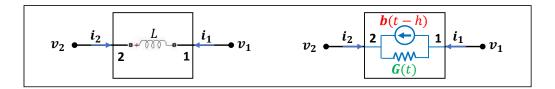

| Fig 3-1 Generic electrical circuit split into two sub-systems using the ITM interface     |

| algorithm91                                                                               |

| Fig 3-2 Operation of split-system model by direct transfer of interface variables (global |

| control loop)92                                                                           |

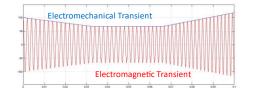

| Fig 3-3 Difference in Electromagnetic (EMaT) and Electromechanical (EMeT) transient       |

| signals92                                                                                 |

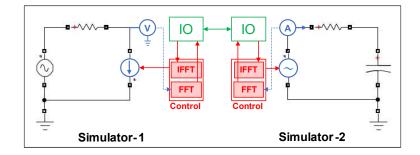

| Fig 3-4 Operation of split-system model by exchanging interface variables in the          |

| frequency domain93                                                                        |

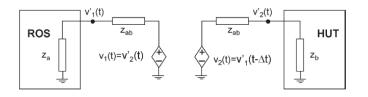

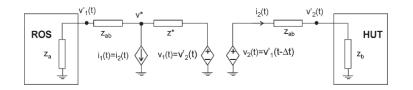

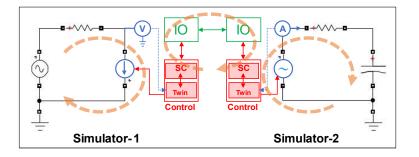

| Fig 3-5 Operation of split-system model by employing a local Digital Twin94               |

| Fig 3-6 Operation of split-system model by employing a local Digital Twin operating on    |

| Dynamic Phasors95                                                                         |

| Fig 3-7 Ideal Model approach for modelling electrical systems97                           |

| Fig 3-8 Switching Function approach for modelling electrical systems                 |

|--------------------------------------------------------------------------------------|

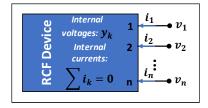

| Fig 3-9 Resistive Companion Form (RCF) model101                                      |

| Fig 3-10 RCF model of an inductor102                                                 |

| Fig 3-11 State Space Averaging (SSA) method for modelling electrical systems103      |

| Fig 4-1 Real automotive hybrid powertrain system split into local P-HIL location (at |

| Nottingham) and remote location108                                                   |

| Fig 4-2 Non-periodic signal being processed as quasi-periodic signal for Dynamic     |

| Phasors                                                                              |

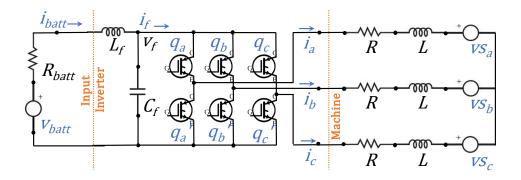

| Fig 4-3 Generic electric powertrain system119                                        |

| Fig 4-4 Pulse Width Modulation using Natural Sampling technique122                   |

| Fig 4-5 Pulse Width Modulation using Regular Sampling technique122                   |

| Fig 4-6 Pulse Width Modulation using Third Harmonic Injection                        |

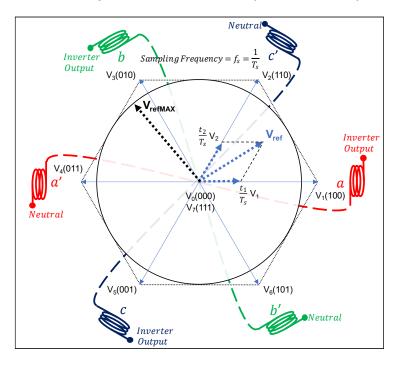

| Fig 4-7 Concept of Space Vector Modulation (SVM)124                                  |

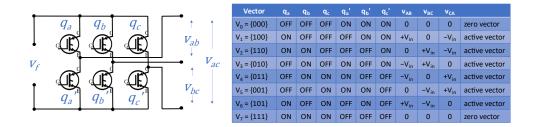

| Fig 4-8 Different switch configurations employable in Space Vector Modulation (SVM)  |

|                                                                                      |

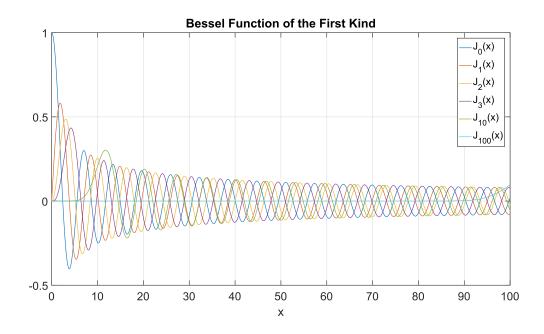

| Fig 4-9 Example of Bessel function output for various index and parameter values 129 |

| Fig 4-10 Top-level view of MFA models developed136                                   |

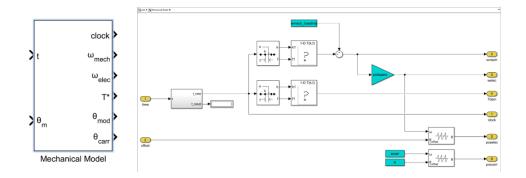

| Fig 4-11 "Mechanical Model" block detailed view137                                   |

| Fig 4-12 "Phasor Environment SinZCos" block detailed view                            |

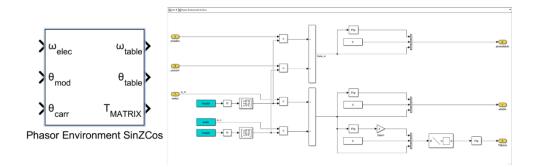

| Fig 4-13 All System Model blocks overview                                            |

| Fig 4-14 "Switching" block detailed view139                                          |

| Fig 4-15 "Controller" block detailed view                                            |

| Fig 4-16 "Modified Convolution" block detailed view                                  |

| Fig 4-17 Warning message flashed for "lost harmonics" in initialisation stage141     |

| Fig 4-18 "Phase-to-Time" block detailed view141                                      |

| Fig 4-19 Simulation run-time comparison experimental plan145                         |

| Fig 4-20 Time-domain waveform comparison (qabc) for Natural and Asymmetric           |

| Regular Sampling (Sine PWM switching strategy)147                                    |

| Fig 4-21 Time-domain waveform comparison (qabc) for Natural and Asymmetric           |

| Regular Sampling (third harmonic injection switching strategy)                       |

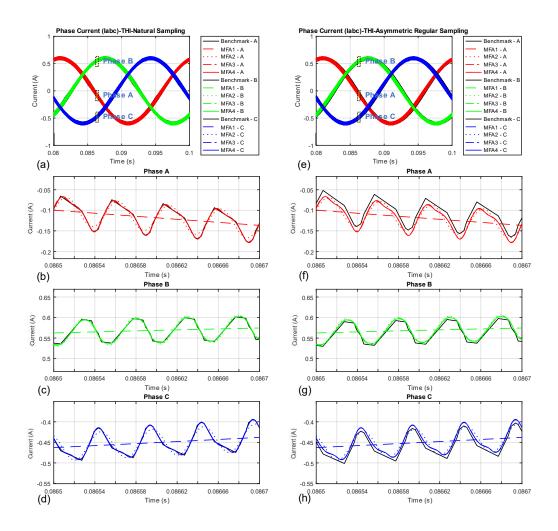

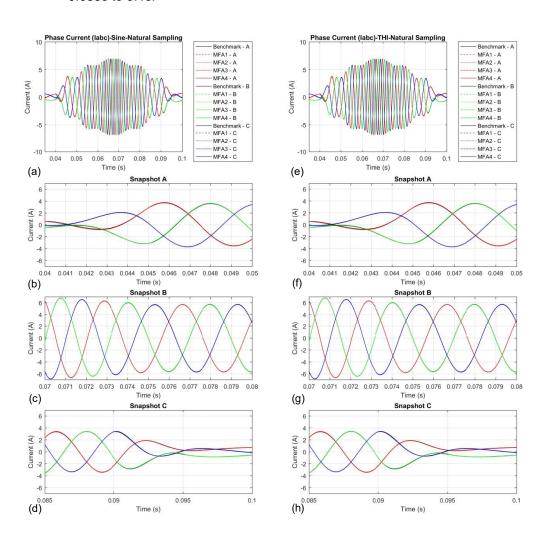

| Fig 4-22 Time-domain waveform comparison ( <i>iabc</i> ) for Natural and Asymmetric                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------|

| Regular Sampling (Sine PWM switching strategy)149                                                                                   |

| Fig 4-23 Time-domain waveform comparison ( <i>iabc</i> ) for Natural and Asymmetric                                                 |

| Regular Sampling (third harmonic injection switching strategy)                                                                      |

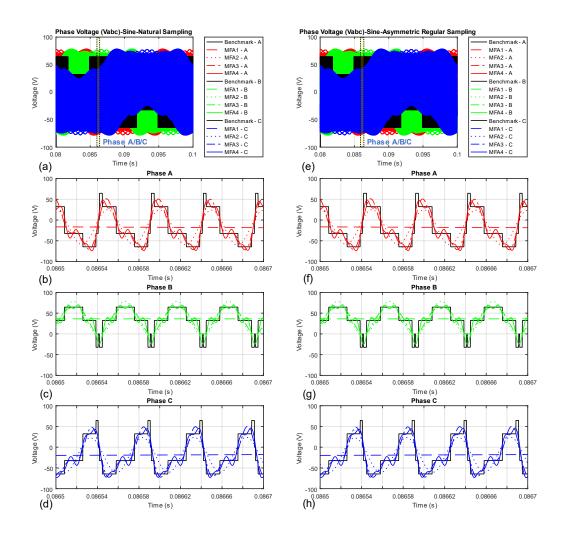

| Fig 4-24 Time-domain waveform comparison (vabc) for Natural and Asymmetric                                                          |

| Regular Sampling (Sine PWM switching strategy)151                                                                                   |

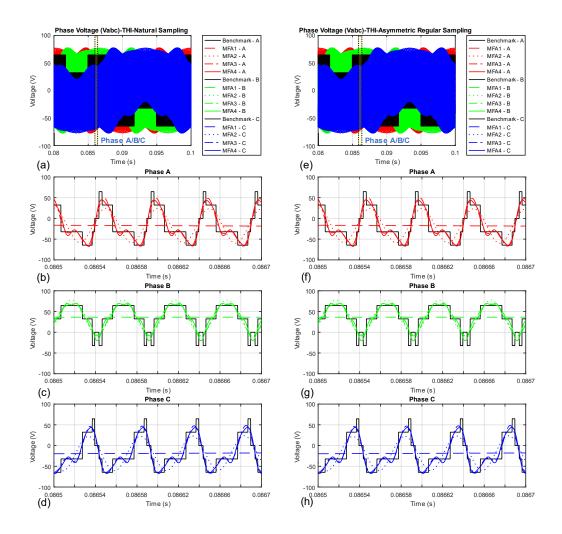

| Fig 4-25 Time-domain waveform comparison (vabc) for Natural and Asymmetric                                                          |

| Regular Sampling (third harmonic injection switching strategy)                                                                      |

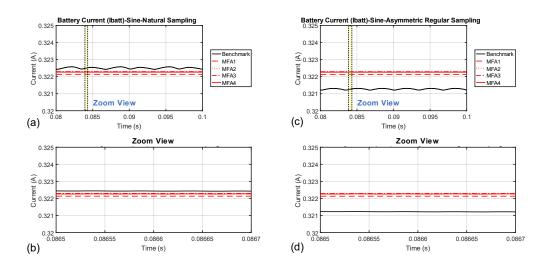

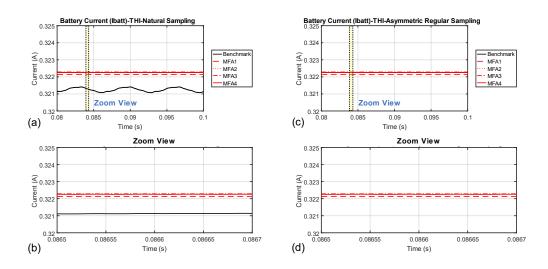

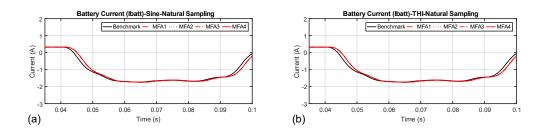

| Fig 4-26 Time-domain waveform comparison ( <i>ibatt</i> ) for Natural and Asymmetric                                                |

| Regular Sampling (Sine PWM switching strategy)153                                                                                   |

| Fig 4-27 Time-domain waveform comparison ( <i>ibatt</i> ) for Natural and Asymmetric                                                |

| Regular Sampling (third harmonic injection switching strategy)                                                                      |

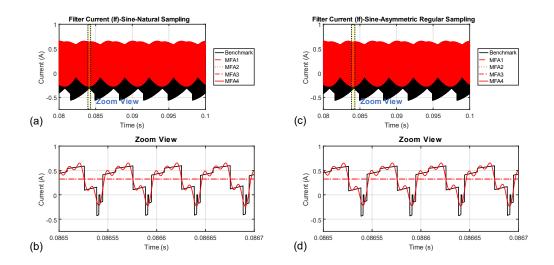

| Fig 4-28 Time-domain waveform comparison $(if)$ for Natural and Asymmetric Regular                                                  |

| Sampling (Sine PWM switching strategy)154                                                                                           |

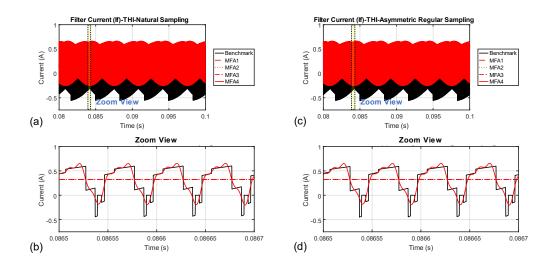

| Fig 4-29 Time-domain waveform comparison $(if)$ for Natural and Asymmetric Regular                                                  |

| Sampling (third harmonic injection switching strategy)155                                                                           |

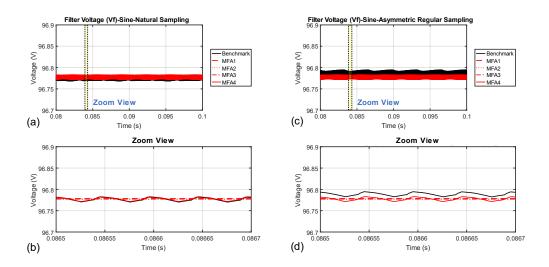

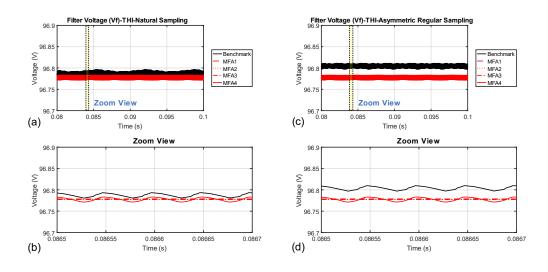

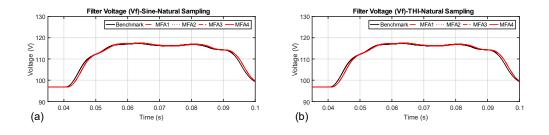

| Fig 4-30 Time-domain waveform comparison $(vf)$ for Natural and Asymmetric Regular                                                  |

| Sampling (Sine PWM switching strategy)156                                                                                           |

| Fig 4-31 Time-domain waveform comparison $(vf)$ for Natural and Asymmetric Regular                                                  |

| Sampling (third harmonic injection switching strategy)156                                                                           |

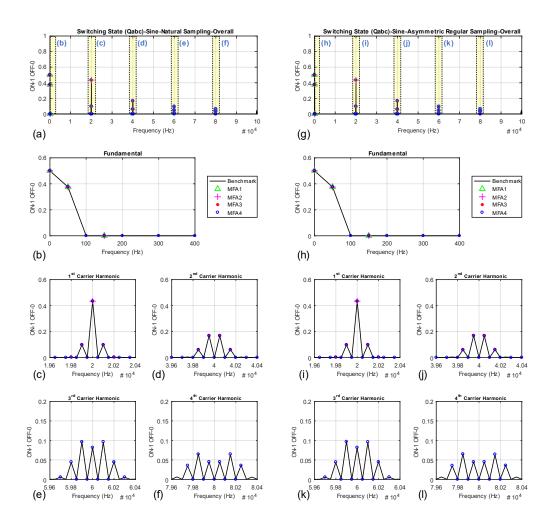

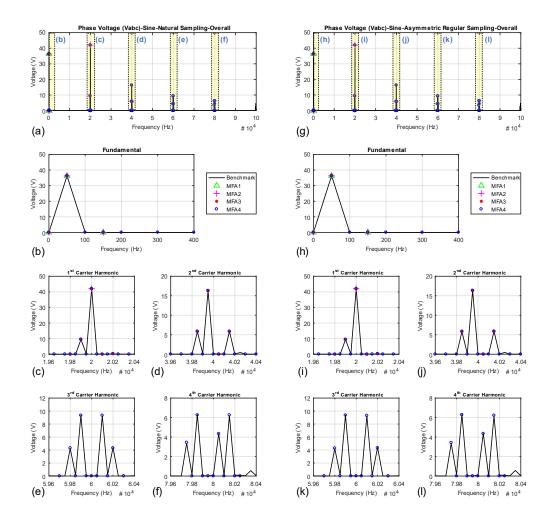

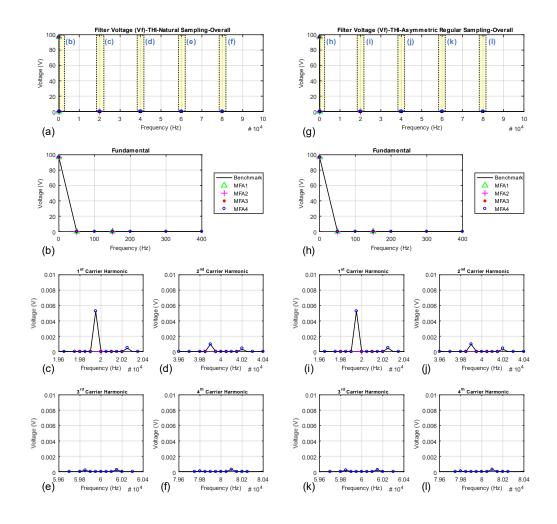

| Fig 4-32 Frequency spectrum comparison ( <i>Qabc</i> ) for Natural and Asymmetric Regular                                           |

| Sampling (sine PWM switching strategy)158                                                                                           |

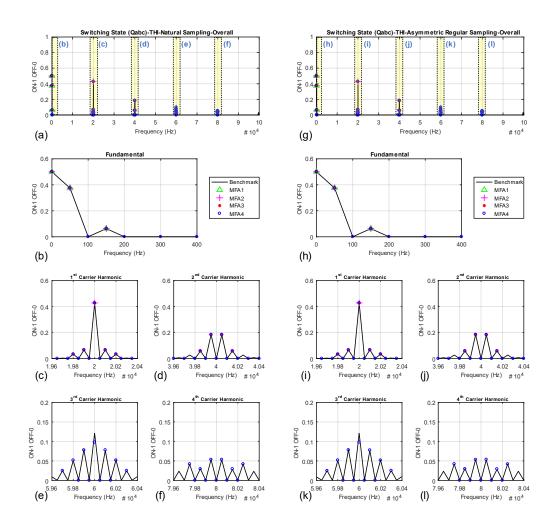

| Fig 4-33 Frequency spectrum comparison ( <i>Qabc</i> ) for Natural and Asymmetric Regular                                           |

| Sampling (third harmonic injection switching strategy)159                                                                           |

|                                                                                                                                     |

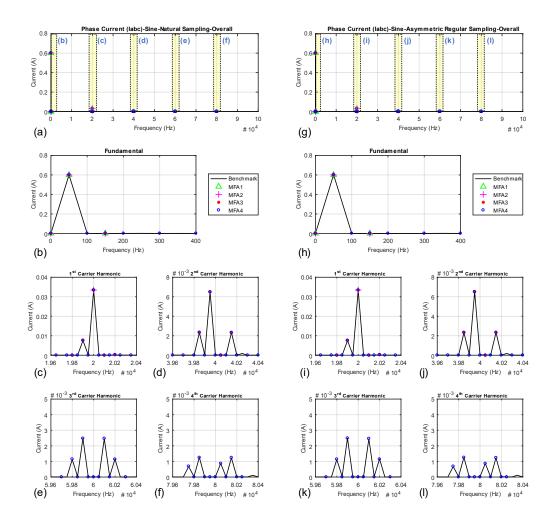

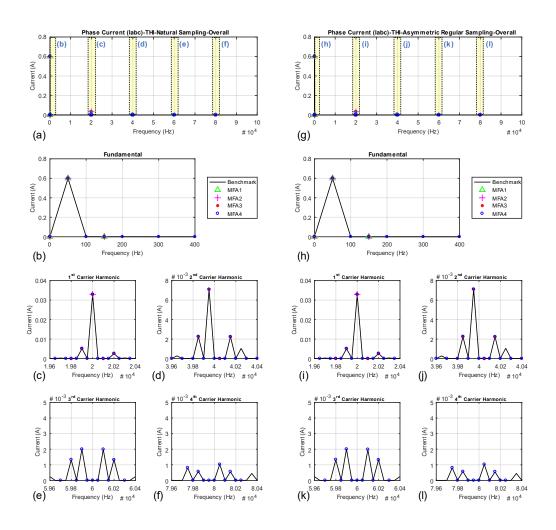

| Fig 4-34 Frequency spectrum comparison ( <i>Iabc</i> ) for Natural and Asymmetric Regular                                           |

|                                                                                                                                     |

| Fig 4-34 Frequency spectrum comparison ( <i>Iabc</i> ) for Natural and Asymmetric Regular                                           |

| Fig 4-34 Frequency spectrum comparison ( <i>Iabc</i> ) for Natural and Asymmetric Regular Sampling (sine PWM switching strategy)    |

| Fig 4-34 Frequency spectrum comparison ( <i>Iabc</i> ) for Natural and Asymmetric Regular<br>Sampling (sine PWM switching strategy) |

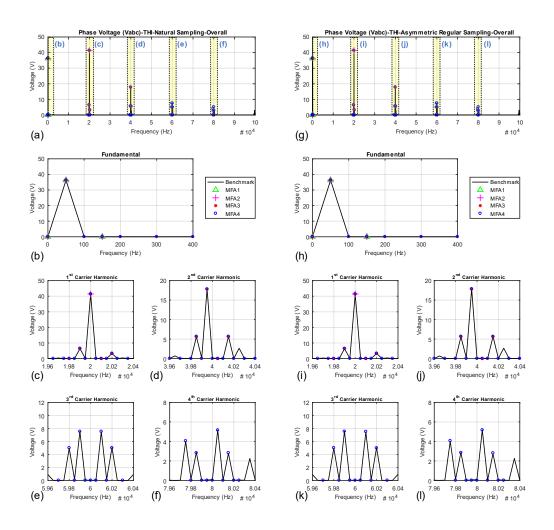

| Fig 4-37 Frequency spectrum comparison (Vabc) for Natural and Asymmetric Regular         |

|------------------------------------------------------------------------------------------|

| Sampling (third harmonic injection switching strategy)163                                |

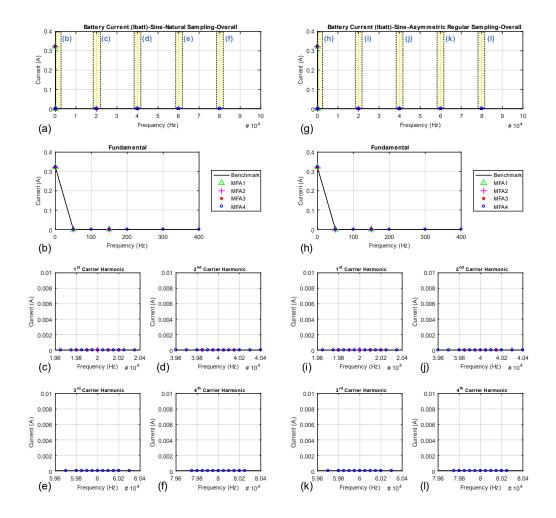

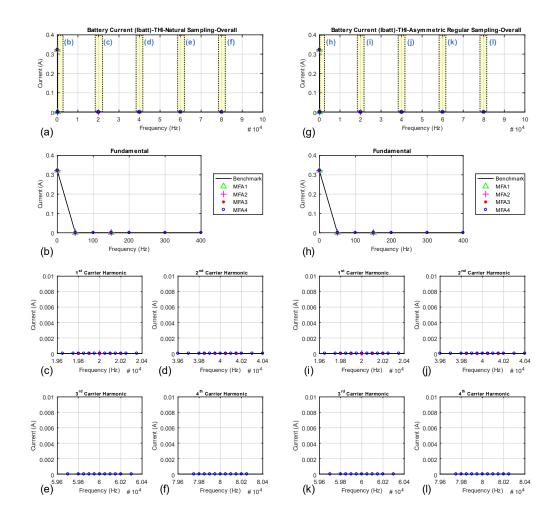

| Fig 4-38 Frequency spectrum comparison (Ibatt) for Natural and Asymmetric Regular        |

| Sampling (sine PWM switching strategy)164                                                |

| Fig 4-39 Frequency spectrum comparison (Ibatt) for Natural and Asymmetric Regular        |

| Sampling (third harmonic injection switching strategy)165                                |

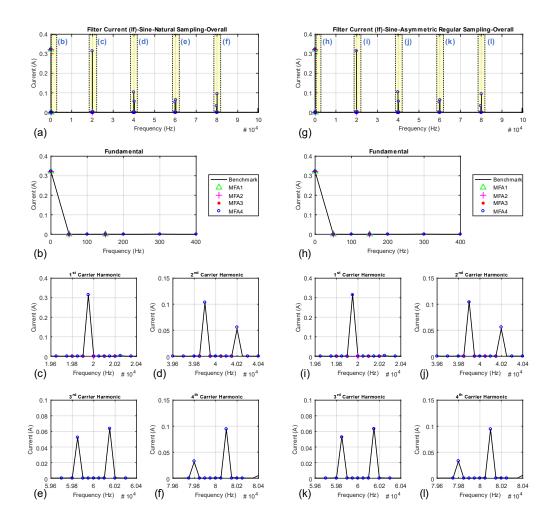

| Fig 4-40 Frequency spectrum comparison (If) for Natural and Asymmetric Regular           |

| Sampling (sine PWM switching strategy)166                                                |

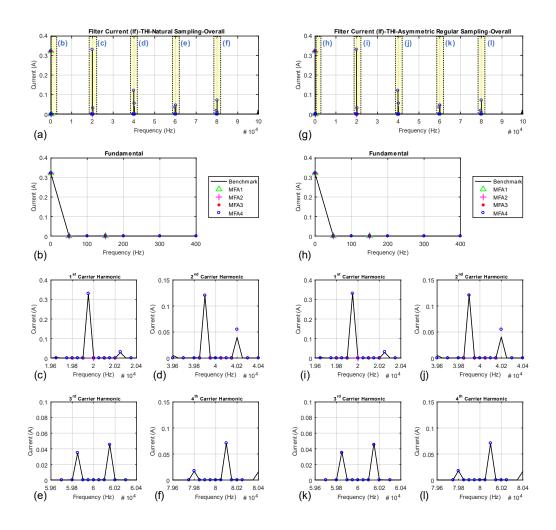

| Fig 4-41 Frequency spectrum comparison (If) for Natural and Asymmetric Regular           |

| Sampling (third harmonic injection switching strategy)167                                |

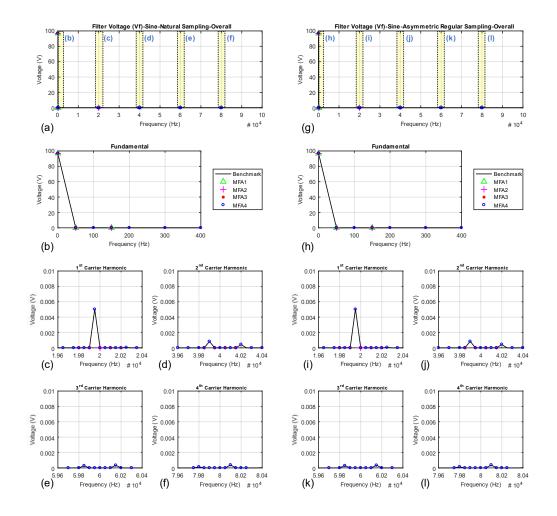

| Fig 4-42 Frequency spectrum comparison $(Vf)$ for Natural and Asymmetric Regular         |

| Sampling (sine PWM switching strategy)168                                                |

| Fig 4-43 Frequency spectrum comparison $(Vf)$ for Natural and Asymmetric Regular         |

| Sampling (third harmonic injection switching strategy)169                                |

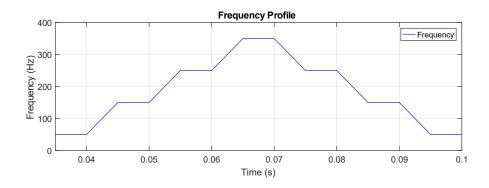

| Fig 4-44 Frequency profile for variable frequency application of MFA model170            |

| Fig 4-45 Time-domain waveform comparison ( <i>iabc</i> ) for naturally sampled Sine PWM  |

| switching strategy171                                                                    |

| Fig 4-46 Time-domain waveform comparison ( <i>ibatt</i> ) for naturally sampled Sine PWM |

| switching strategy172                                                                    |

| Fig 4-47 Time-domain waveform comparison $(vf)$ for naturally sampled Sine PWM           |

| switching strategy172                                                                    |

| Fig 5-1 Triphase power-HIL simulator rig as configured and procured from Triphase for    |

| this PhD175                                                                              |

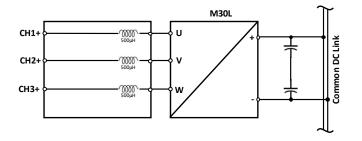

| Fig 5-2 Detailed schematic of Triphase power-HIL simulator rig (A30 unit)176             |

| Fig 5-3 Detailed schematic of Triphase power-HIL simulator rig (F03 unit)177             |

| Fig 5-4 Detailed schematic of Triphase power-HIL simulator rig (M30L unit)177            |

| Fig 5-5 Virtual Circuit Emulation as implemented in Triphase simulator                   |

| Fig 5-6 Triphase power-HIL simulator rig and associated equipment and computers          |

|                                                                                          |

| Fig 5-7 Beckhoff EtherCAT module for digital and analog I/O interfacing180               |

| Fig 5-8 Brief overview diagram of generic permanent magnet synchronous motor drive |

|------------------------------------------------------------------------------------|

|                                                                                    |

| Fig 5-9 Motoring and Generating action conceptualised for a synchronous machine    |

|                                                                                    |

| Fig 5-10 Conceptual difference between frames of reference for three-phase machine |

| control: $abc \vee \alpha\beta \vee dq$                                            |

| Fig 5-11 Detailed overview diagram of generic permanent magnet synchronous motor   |

| control                                                                            |

| Fig 5-12 ABZ type digital encoder operation principle184                           |

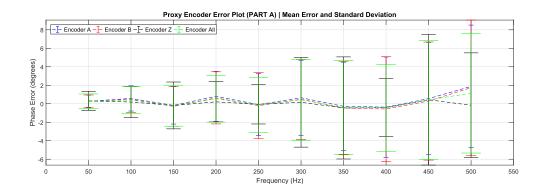

| Fig 5-13 PART A Results – Measured encoder pulse signals compared with requested   |

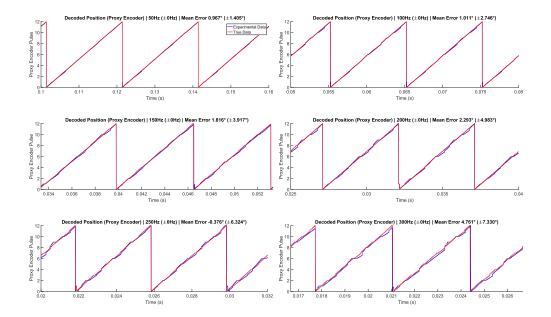

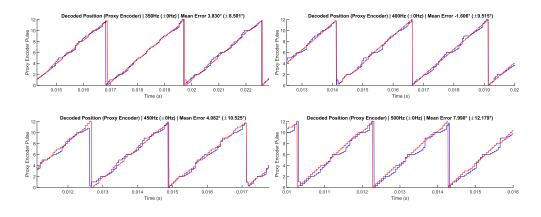

| signals187                                                                         |

| Fig 5-14 PART A Results - Error graph between measured and requested encoder       |

| signals for A, B, and Z pulses189                                                  |

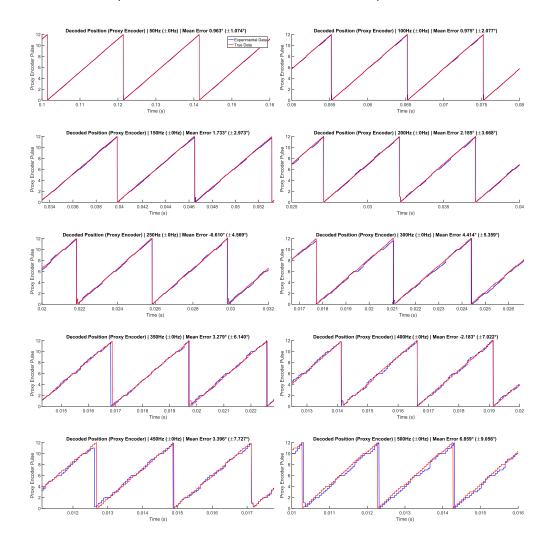

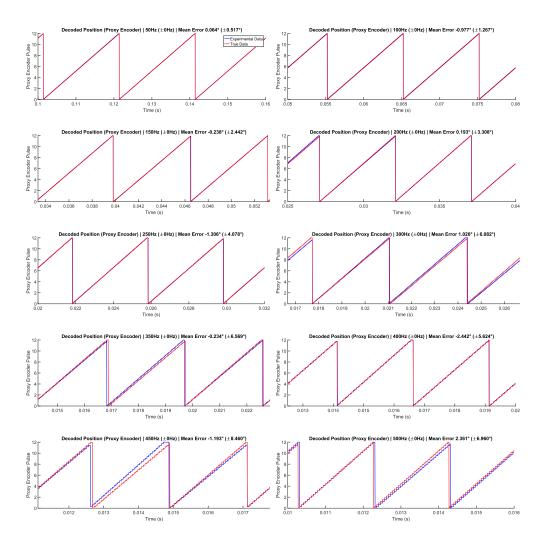

| Fig 5-15 PART B Results – Measured phase angle compared with requested angle       |

| (TYPE 1)                                                                           |

| Fig 5-16 PART B Results – Measured phase angle compared with requested angle       |

| (TYPE 2)                                                                           |

| Fig 5-17 PART B Results – Measured phase angle compared with requested angle       |

| (TYPE 3)                                                                           |

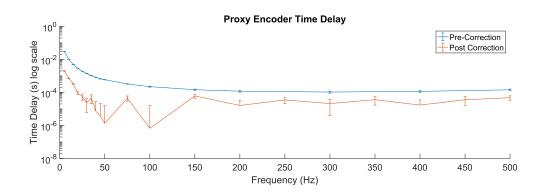

| Fig 5-18 PART B Results – Error graph between measured and requested phase angle   |

|                                                                                    |

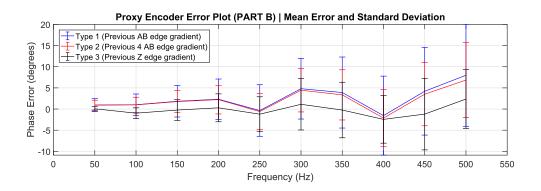

| Fig 5-19 Time and Phase delay between measured and requested phase angle (pre-     |

| correction)                                                                        |

| Fig 5-20 Time and Phase delay between measured and requested phase angle (post-    |

| correction)                                                                        |

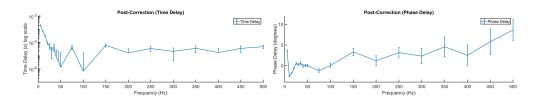

| Fig 5-21 Time delay between measured and requested phase angle (comparison         |

| between pre and post correction)194                                                |

| Fig 5-22 Phase delay between measured and requested phase angle (comparison        |

| between pre and post correction)195                                                |

| Fig 5-23 Mathematical concept underlying interpolation technique for phase angle   |

|------------------------------------------------------------------------------------|

| computation                                                                        |

| Fig 5-24 Mathematical concept underlying interpolation technique for phase angle   |

| computation (comparison of TYPE 2 and TYPE 3 techniques)197                        |

| Fig 5-25 Measured phase angle value compared with requested for TYPE 2 and TYPE    |

| 3 techniques with rising frequency197                                              |

| Fig 5-26 Error graph of TYPE 2 and TYPE 3 phase angle computation techniques at    |

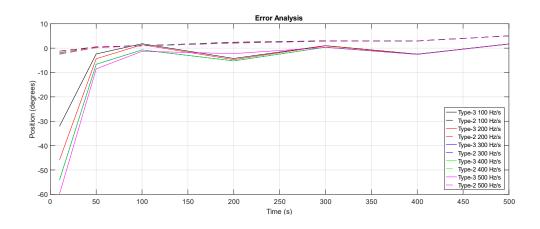

| different frequency rise rates                                                     |

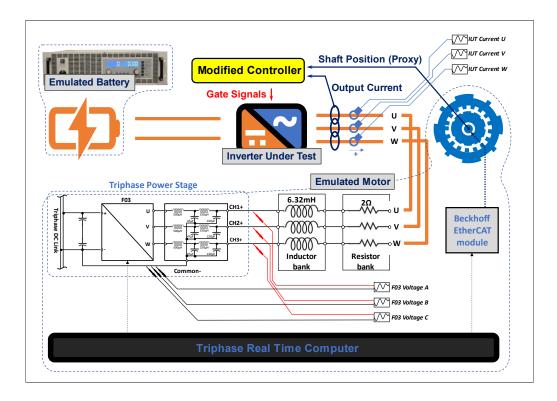

| Fig 6-1 Detailed experimental setup for P-HIL experiments                          |

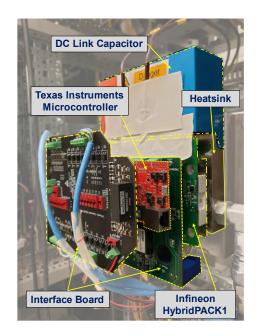

| Fig 6-2 IUT – Infineon inverter setup                                              |

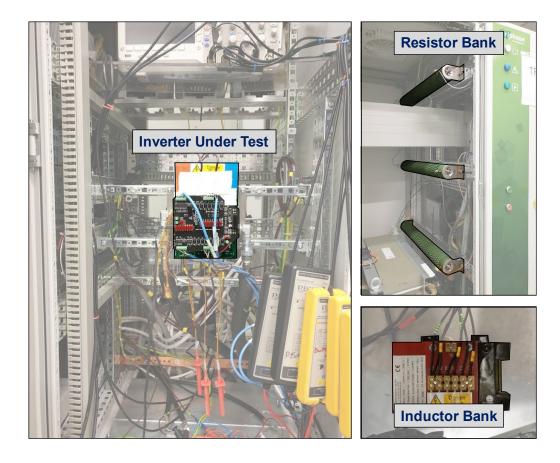

| Fig 6-3 Experimental setup pictures                                                |

| Fig 6-4 External current and voltage measurement instruments for datalogging204    |

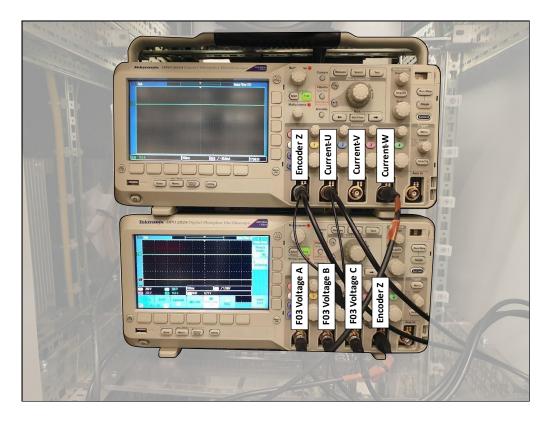

| Fig 6-5 Oscilloscopes for reading and logging measurement voltage and current      |

| waveforms                                                                          |

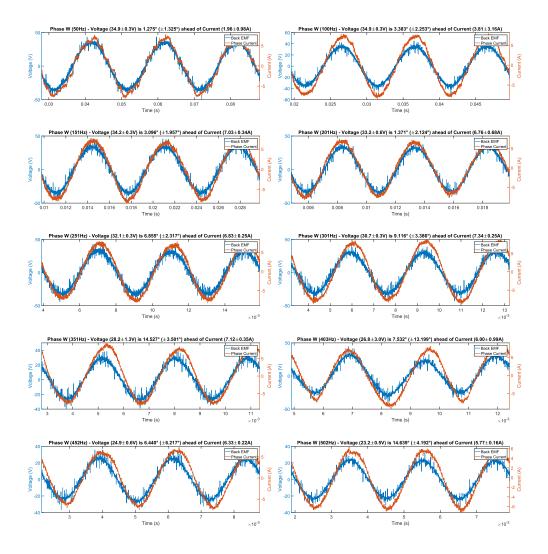

| Fig 6-6 Back EMF voltage (Triphase) and phase current (IUT) waveforms at different |

| frequencies                                                                        |

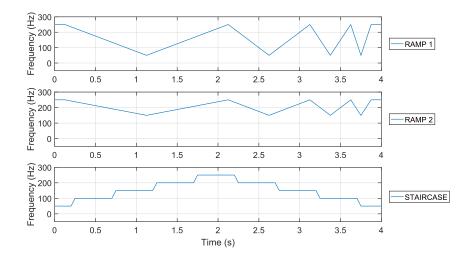

| Fig 6-7 Variable frequency profiles applied (RAMP 1, RAMP2, and STAIRCASE) 207     |

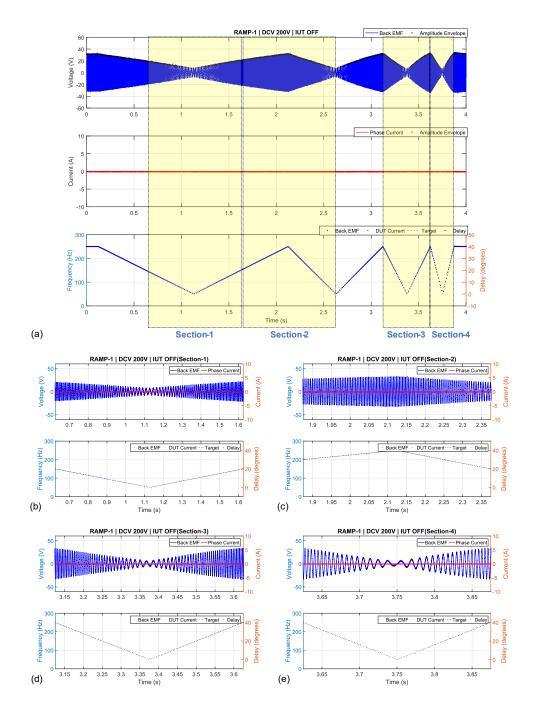

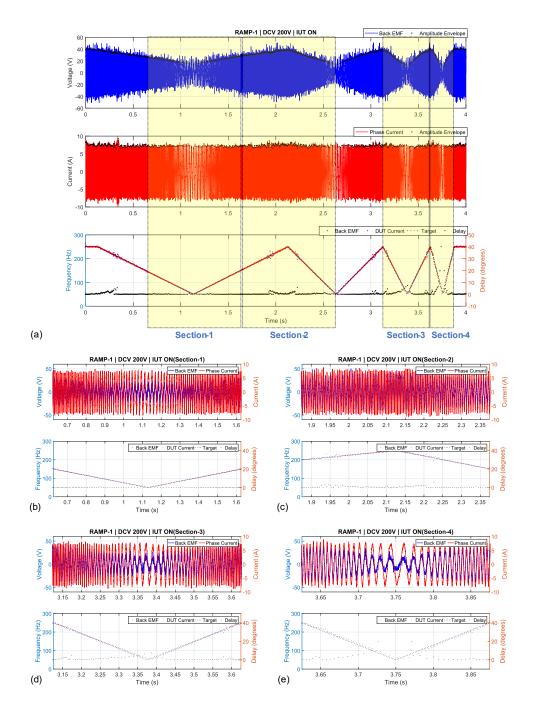

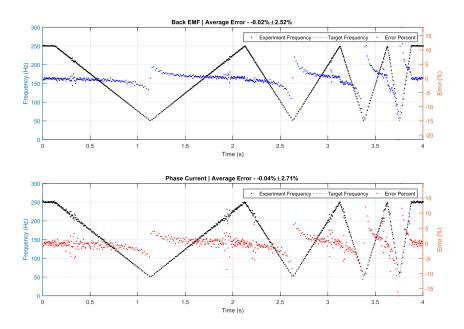

| Fig 6-8 EXPERIMENT 1 Results - Back EMF voltage (Triphase) and phase current       |

| (IUT)210                                                                           |

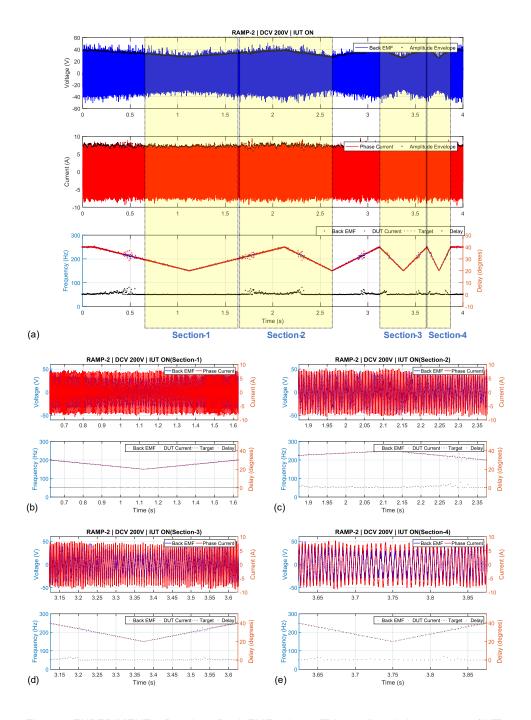

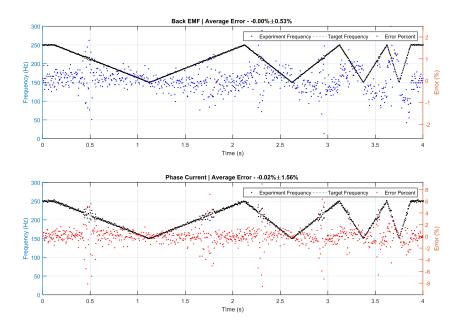

| Fig 6-9 EXPERIMENT 2 Results - Back EMF voltage (Triphase) and phase current       |

| (IUT)212                                                                           |

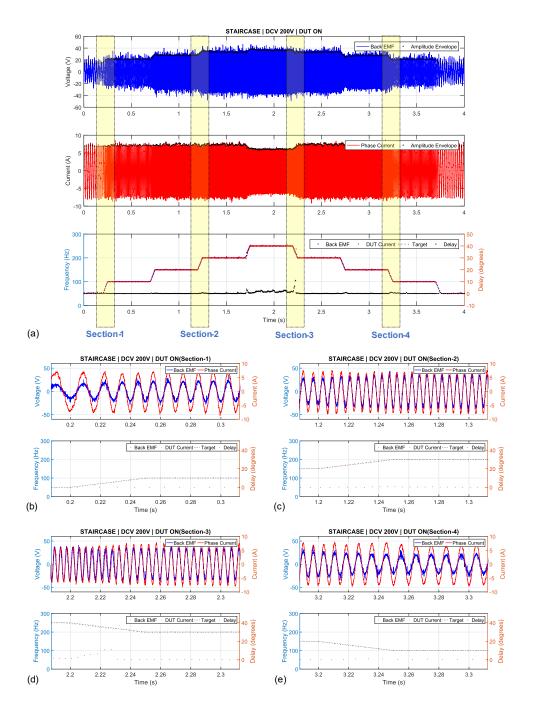

| Fig 6-10 EXPERIMENT 3 Results – Back EMF voltage (Triphase) and phase current      |

| (IUT)214                                                                           |

| Fig 6-11 EXPERIMENT 4 Results – Back EMF voltage (Triphase) and phase current      |

| (IUT)216                                                                           |

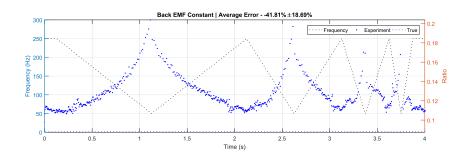

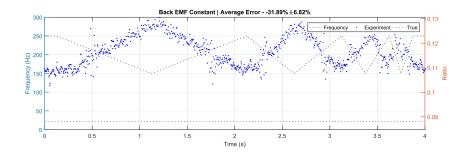

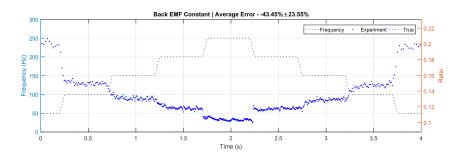

| Fig 6-12 EXPERIMENT 1 - Error in reproduced frequency of back EMF voltage          |

| (Triphase)218                                                                      |

| Fig 6-13 EXPERIMENT 2 - Error in reproduced frequency of back EMF voltage          |

| (Triphase) and phase current (IUT)219                                              |

| Fig 6-14 EXPERIMENT 3 – Error in reproduced frequency of back EMF voltage                 |

|-------------------------------------------------------------------------------------------|

| (Triphase) and phase current (IUT)220                                                     |

| Fig 6-15 EXPERIMENT 4 – Error in reproduced frequency of back EMF voltage                 |

| (Triphase) and phase current (IUT)221                                                     |

| Fig 6-16 EXPERIMENT 1 – Error in back EMF voltage (Triphase) magnitude221                 |

| Fig 6-17 EXPERIMENT 2 – Error in back EMF voltage (Triphase) magnitude221                 |

| Fig 6-18 EXPERIMENT 3 – Error in back EMF voltage (Triphase) magnitude222                 |

| Fig 6-19 EXPERIMENT 4 – Error in back EMF voltage (Triphase) magnitude222                 |

| Fig 7-1 End goal for local Power-HIL testbed for prototype inverter testing at various    |

| stages of development (inverter only, or inverter and gate driver, or controller included |

| too)231                                                                                   |

# v. List of Tables

| Table 4-1 Weighted Total Harmonic Distortion (WTDH0) with reference to modulation  |

|------------------------------------------------------------------------------------|

| wave for Sinusoidal PWM switching technique (various sampling strategies)          |

| [130][131][139]134                                                                 |

| Table 4-2 Weighted Total Harmonic Distortion (WTDH0) with reference to modulation  |

| wave for Third Harmonic Injection and Space Vector Modulation switching technique  |

| (various sampling strategies) [130][131][139]134                                   |

| Table 4-3 List of all harmonics computed in the four MFA models144                 |

| Table 4-4 Simulation execution time of MFA models and equivalent time-domain       |

| switching model145                                                                 |

| Table 4-5 Simulation execution time comparison of MFA models with equivalent time- |

| domain switching model145                                                          |

| Table 5-1 PART A Results - Error statistics between measured and requested encoder |

| signals for A, B, and Z pulses                                                     |

| Table 5-2 PART B Results - Error statistics between measured and requested phase   |

| angle                                                                              |

| Table 5-3 Time and Phase delay statistics for pre and post correction              |

| Table 6-1 Phase offset between back EMF voltage (Triphase) and phase current (IUT) |

| at different frequencies                                                           |

# vi. List of Abbreviations

| ABS   | Anti-lock Braking Systems                      |

|-------|------------------------------------------------|

| AC    | Alternating Current                            |

| AD    | Automatic Differentiation                      |

| AFE   | Active Front-end                               |

| APC   | Advanced Propulsion Centre                     |

| BEV   | Battery Electric Vehicle                       |

| С     | Capacitor-only filter                          |

| CAN   | Controller Area Network                        |

| CASE  | Connected, Autonomous, Shared, and Electrified |

| СВ    | Converter Bridge                               |

| CCS   | Controller Current Source                      |

| C-HIL | Controller Hardware-in-the-Loop                |

| CPU   | Central Processing Unit                        |

| CS    | Current Source                                 |

| CVS   | Controller Voltage Source                      |

| DC    | Direct Current                                 |

| DT    | Digital Twin                                   |

| DIM   | Damping Impedance Method                       |

| DORC  | Degree of Remote Coupling                      |

| DP    | Dynamic Phasor                                 |

| DSP   | Digital Signal Processor                       |

| DSP   | Digital Signal Processor                       |

| DTM   | Direct Torque Modulation                       |

| DUT   | Device Under Test                              |

| EMaT  | Electromagnetic Transient                      |

| EMeT  | Electromechanical Transient                    |

| EMF   | Electromotive Force                            |

| EMTP  | Electromagnetic Transient Program              |

| EV    | Electric Vehicle                               |

| FFT   | Fast Fourier Transform                         |

| FPGA   | Field Programmable Gate Array                     |

|--------|---------------------------------------------------|

| FS     | Fourier Series                                    |

| GAM    | Generalised Average Modelling                     |

| GD-HIL | Geographically Distributed Hardware-in-the-Loop   |

| GHG    | Greenhouse Gases                                  |

| GPU    | Graphics Processing Unit                          |

| GSSA   | Generalised State Space Averaging                 |

| HIL    | Hardware-in-the-Loop                              |

| HVDC   | High Voltage Direct Current                       |

| IA     | Interface Algorithm                               |

| ICE    | Internal Combustion Engine                        |

| ID-HIL | Internet Distributed Hardware-in-the-Loop         |

| IEEE   | Institute of Electrical and Electronics Engineers |

| IET    | Institution of Engineering and Technology         |

| IGBT   | Insulated Gate Bipolar Transistor                 |

| ITM    | Ideal Transformer Method                          |

| IUT    | Inverter Under Test                               |

| L      | Inductor-only filter                              |

| LC     | Inductor-Capacitor filter                         |

| LCC    | Inductor-Capacitor-Capacitor filter               |

| LCL    | Inductor-Capacitor-Inductor filter                |

| LCLC   | Inductor-Capacitor-Inductor-Capacitor filter      |

| LTI    | Linear Time-Invariant                             |

| MAAS   | Mobility-as-a-Service                             |

| MFA    | Multi-Frequency Averaging                         |

| MOSFET | Metal-Oxide-Semiconductor Field Effect Transistor |

| MSc    | Master of Science                                 |

| NASA   | National Aeronautics and Space Administration     |

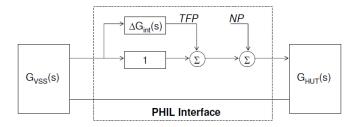

| NP     | Noise Perturbation                                |

| ODE    | Ordinary Differential Equations                   |

| OEM    | Original Equipment Manufacturer                   |

| OS     | Operating System                                  |

| P2T    | Phase-to-Time                                     |

| PC    | Personal Computer                      |

|-------|----------------------------------------|

| PCD   | Partial Circuit Duplication            |

| PCI   | Peripheral Component Interconnect      |

| PCM   | Powertrain Control Module              |

| PEC   | Power Electronic Converter             |

| PhD   | Doctor in Philosophy                   |

| P-HIL | Power Hardware-in-the-Loop             |

| PMSM  | Permanent Magnet Synchronous Machine   |

| PV    | Photovoltaic                           |

| PWM   | Pulse Width Modulation                 |

| RCF   | Resistive Companion Form               |

| RCP   | Rapid Controller Prototyping           |

| RP    | Rapid Prototyping                      |

| RPM   | Revolutions Per Minute                 |

| RS232 | Recommended Standard 232               |

| RT    | Real-Time                              |

| RTDS  | Real-Time Digital Simulator            |

| RTOS  | Real-Time Operating System             |

| RTT   | Real-Time Target                       |

| RTT   | Round-trip-time                        |

| SC    | State Convergence                      |

| SPWM  | Sinusoidal Pulse Width Modulation      |

| SRC   | Signal-extension Resistive Companion   |

| SSA   | State Space Averaging                  |

| SVM   | Space Vector Modulation                |

| SVPWM | Space Vector Pulse Width Modulation    |

| ТСР   | Transmission Control Protocol          |

| TCS   | Traction Control System                |

| TFA   | Time-variant First Order Approximation |

| TFP   | Transfer Function Perturbation         |

| тні   | Third Harmonic Injection               |

| TLM   | Transmission Line Method               |

| TNA   | Transient Network Analyser             |

|       |                                        |

- TSB Time Stamp Bridges

- UDP User Datagram Protocol

- V2G Vehicle-to-Grid

- VCHV Virtually Connected Hybrid Vehicle

- VPPC Vehicular Power and Propulsion Conference

- VS Voltage Source

- VSC Voltage Source Converter

- VSS Virtual System Simulation

- VTB Virtual Testbed

- VTB-RT Real-Time Virtual Testbed

- WTHD Weighted Total Harmonic Distortion

- WTHD0 Weighted Total Harmonic Distortion referenced to modulation wave

- XSG Xilinx System Generator

## **CHAPTER 1** Introduction

#### 1.1 Automotive industry – Past, Present and Future

The automotive industry comprises of all the businesses involved in the production of motor vehicles, that includes the powertrain (engine, transmission, and more recently traction batteries and drives), the body (chassis and panels) and the electronics (display, lights, computing, and software). A little more than a century old, this industry has today grown into a significant economic driving force for most industrial nations around the world and accounts for more than 5 trillion dollars in revenue [1]. Not just economically, the industry has also been on the forefront of technological development and is currently undergoing arguably its grandest and most disruptive changes in its history [1][2][3]; **connected**, **autonomous**, **shared** and **electrified** (CASE) car of the near future. *This thesis is the outcome of the work conducted for the degree of doctorate in philosophy, which facilitates significant reduction of time and effort spent in developing a modern automotive powertrain (hybrid/electric). Therefore, it is prudent to introduce the reader briefly about the origin and evolution, and how is the future getting shaped.*

Fig 1-1 Ford Model T Touring Car from 1925 [4]

The first reciprocating engine-driven "automobile" was developed in late the 19<sup>th</sup> century as a "horseless carriage" in Europe, although steam and electric powered modes of transport were in use for niche applications well before that [5]. By the turn of the twentieth century, numerous other European countries had joined in but the real revolution that cemented the automotive "industry" firmly was Ford Motor Company in America with its assembly line production (Fig 1-1). It is worth noting here that the popular gasoline-powered engine was not the first choice during the inception era of the car as it faced stiff competition between electric and steam power. Electricity mainly because it was minimal maintenance, easy to operate, and noise-free; whereas the steam-powered powertrain was a more serious rival since it was a more mature technology and aided by general adoption by the populace. There are several reasons given in [6][7] as to why electric vehicles never succeeded in garnering market share against the fuel-powered cars during the 1920s and 1930s. Mainly, the problems faced by electric propulsion were extremely limited battery capacity and negligible charging infrastructure. The main problem for steam propulsion was expensive construction of boilers light enough for road cars. Thus, began the era of internal-combustion engine (ICE) automobile as we see today.

Over the decades the technology has evolved gradually to account for passenger and pedestrian safety standards, driving experience and creature comfort, while the business model of private and fleet ownership remained largely the same. Improvement of fuel economy was initially a slow burner among areas of research, but became a mainstay after the global oil crisis in the 1970s. As a result, the latter half of the 20<sup>th</sup> century saw rapid advancement of the internal combustion engine in terms of efficiency and there was a marked shift towards the more efficient diesel engines in Europe. Moreover, there was a marked rise in government interest to fund research in electrified powertrains for road transport as well.

Climate change has been another crucial factor towards the desire for electrification in the automotive industry. Electrified powertrains are advantageous because they have zero tailpipe emissions that helps improve local air quality, which had started to become a major health concern in big cities in the 1990s. Another big reason is reduction in carbon footprint per mile driven for an electrified vehicle. While it may be argued that there is significant carbon impact to generate electricity if the national energy grid is mostly reliant on fossil-fuel based sources, the lifecycle emissions of an electrified vehicle (EV) is still better than ICE vehicles [8]. Most progressive nations in modern

24

times have a sizeable portion of their energy generation from renewable sources which further helps the case. Fig 1-2 below shows that lifetime greenhouse gas emission of an EV varies with the national energy grid quality but is still mostly better than IC vehicles. Moreover, the IC engines after decades of incremental improvements have now reached their peak technological maturity and hence electrification is arguably the best way forward. As a result, **electrification** is one of the key megatrends that is shaping the future of the industry.

The future of the automotive industry and market will see dramatic changes as an exponential rise in digitalisation and Internet of Things (IoT) have continued to shift the cost balance from steel to silicon in vehicle engineering [2]. Big tech giants from the Silicon Valley (Apple, Google, Tesla) have entered the field with vast investment towards **connected** and **autonomous** services for a vehicle. Secondly, the business model of private ownership is gradually giving way to community ownership in the form of "Mobility-as-a-Service" (MAAS) industry as opposed to the traditional automotive industry; research has found a privately owned vehicle spends more than 90% of its lifetime simply parked, increasing the utilisation fraction of a vehicle through vehicle **sharing** holds the potential to drastically reduce the lifecycle cost. These four megatrends of the industry, popularly referred to by the acronym CASE (connected, autonomous, shared, electrified), are complexly interlinked and have forced legacy manufacturers to submit to the post-modern automotive world of a cheap, feature-rich, and highly connected car.

25

Fig 1-2 Lifetime greenhouse gas (GHG) emissions of types of vehicles and sub-divided by countries for Battery Electric Vehicles (BEV) [8]

## **1.2 Key Technological Enablers of Electrification**

Santini [5] notes that the history of EVs can be divided into three phases. The first is the pre-IC era when a small minority of road transportation was done using EVs until the IC engine car completely took over by the 1920s due to reasons discussed earlier. The second era began in the 1970s with the oil crisis when various countries in America and Europe began research in vehicle electrification. The momentum was soon lost within the decade due to drop in oil prices. One of the major reasons that EVs did not take off in the market is that the technology was not mature enough. This changed by the turn of 21<sup>st</sup> century when governmental push was complemented by major strides in technological advancements for widespread uptake in the consumer market. There are three primary technology enablers that have helped make a strong case towards automotive electrification [5]: **energy storage**, **energy conversion** and **energy control**.

First, the development of the Lithium-Ion battery [9][10] that started in late 90s. Having a light compact source of energy has always been the bottleneck for widespread adoption for EV and Li-Ion chemistries today offer the best prospects in this regard. Li-Ion cells have been under research for more than two decades now and started off as energy source for portable appliance like mobile phones and laptops. While they are the best prospects today for automotive applications, there is still a long way to go to compete with the energy and power densities offered by ICE powertrains. They are not very safe to operate and have a sizeable environmental impact during mining and manufacturing.

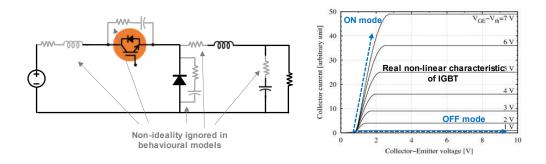

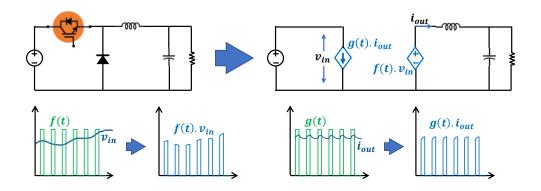

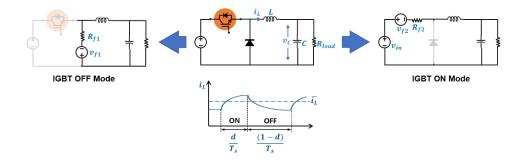

Second, the development of modern power electronics [11] that started in the 80s. Emergence of solid-state switching devices for power applications (thyristors, MOSFETs, IGBTs) significantly accelerated the pace of improvements of drive systems towards smaller, lighter, and more efficient units. This is especially valuable for automotive applications that require low power but high-density units that can sustain a wide range of temperature swing and mechanical vibrations and harshness.

Third, the development of electronics and software that have facilitated lightning-fast computing in small and light package. The Moore's Law states that the density of transistors in an IC package doubles every two years [12], something which has been observed for many decades now (Fig 1-3). The automotive industry has benefited its fair share from this advancement as well and modern cars have exceedingly complex software behind the optimisation of various systems in the powertrain like ignition timing, transmission control and vehicle dynamics related safety features like ABS (**Anti-lock Braking System**, prevents braked wheels from locking up and losing traction) and EBD (**Electric Brake force Distribution**, cleverly manipulating the braking force on the inside and outside wheels to aid the driver in keeping the vehicle pointing in the intended direction). Modern electric drive control schemes are complex and are only possible due to the advent of electronics.

27

Fig 1-3 Moore's Law - The number of transistors on integrated circuit chips (1971-2018) [12]

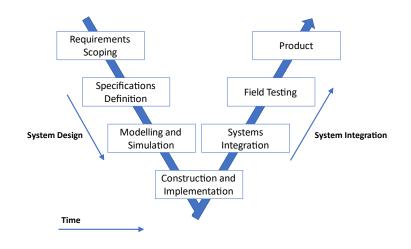

These three enabling technologies, mostly the latter two (fast power electronics and digitalisation) have increasingly trickled into R&D methods and practices in the form of *Virtual Prototyping*. Modern computers are required in every step of development in the form of CAD (**Computer Aided Design**, software packages that are used to draw shapes and assemblies of product) and CAE (**Computer Aided Engineering**, an umbrella term used to indicate all engineering analysis tasks like **Finite Element Analysis**, **Fluid Dynamics**, and **Circuit Simulation** for electrical and electronics). While this evolution has increased the complexity by bringing together new disciplines to solve common goals, it has also opened many avenues to reduce costs by making the development process more automated and simulation intense. While the need for a real prototype is still unavoidable (since digital models can only reach limited levels of accuracy), this step can be pushed further back in the development cycle, dropping the overall cost of designing.

Another significant opportunity that has emerged in the last two decades is *hardware-in-the-loop* (HIL) simulation for testing and validation. A HIL platform allows real prototype units to be connected in a digital closed-loop virtual system for real-time

simulation. This brings the best of both worlds together; highly accurate behaviour of components that cannot be modelled to high fidelity may be incorporated in the testing process. As the rest of the system is in a virtual environment, multiple test iterations are guaranteed to be repeatable.

#### 1.3 Key Challenges in Engineering a Modern Car

Electrification was identified as one of the biggest disruptive changes taking place in the automotive industry due to several reasons but primarily air quality and climate change. Since the associated technologies are still about a decade away from reaching price and weight parity, an EV is still significantly expensive and heavy when compared with an equivalent IC engine car. As a result, engineers are trying to wring out every drop of efficiency that can be achieved in an electrified powertrain through system optimisation and ensuring every component is purpose-built to work hand in hand with the other components. This requires rigorous testing of components at a system level which may get very expensive if real hardware is used.

Virtual Prototyping is a major enabler of repeated testing and validation through reasonably accurate models of various components, as it avoids building a physical prototype. But there are two areas where Virtual Prototyping does not apply and falls short. First, there are numerous components that cannot be modelled to a high degree of fidelity. Consequently, a physical prototype must be built that must be proved in a virtual environment. Second, at system level simulation the overall accuracy is lower than individual components since the error margins of each component tend to compound together.

This expands the remit of Virtual Prototyping into a "hybrid" of both Real and Virtual elements in the simulation (Fig 1-4). HIL simulation is a specialised field of Virtual Prototyping that addresses that by providing for an interface between the real and virtual worlds. A real prototype may be connected in this HIL testbed or rig and operated as if it was fully immersed in the virtual closed-loop system, where the hardware would appear as a black box that reacts exactly as the hardware does. HIL simulation has

emerged as a mainstay since the early 2000s which is especially crucial in developing electrical systems in the car.

Fig 1-4 Underlying concept of Hardware-in-the-Loop (HIL) - Hybrid of real and virtual systems operating in tandem

In automotive powertrains, especially hybrid electric powertrains, there are several components that are very complexly integrated together. While conducting system testing, there may be a case where more than one component would require HIL testing. It is straightforward to combine multiple prototypes together and form a single hardware if they are linked together in the closed-loop system, but any other scenario would require multiple HIL rigs to immerse these physical components in the virtual system. Apart from the obvious cost concern to commission and maintain multiple HIL rigs, a technical issue is not necessarily there with this setup.

The real problem of multiple HIL setup arises when different HIL prototypes are not colocated. This is common in the automotive industry as it is more horizontally integrated as opposed to vertically. The end-product is hugely dependent on an elaborate network of supplier companies. As an example [13], the popular car Opel/Vauxhall Insignia has a multitude of independent suppliers (Fig 1-5). Different companies have their respective intellectual property protection measures in place which adds hindrance to system prototype development with "reserved" technologies. Hence, there is also a logistic barrier to bring all component prototypes together at one place since research centres for these components are usually dispersed geographically. So, having a multi-HIL simulation testbed virtually connected would benefit the R&D process in the industry by allowing system level HIL simulations without having to co-locate various prototypes to enable unparalleled freedom of experiments.

Fig 1-5 Suppliers to the Opel/Vauxhall Insignia, demonstrating the hugely scattered supply chain network in the automotive industry [13]

Delving deeper in imagining this concept, there are several foreseeable challenges in realising such a virtual simulation testbed. An apparent concern is setting up a reliable and fast communication "tunnel" between various locations for stable and real-time co-simulation. This challenge arises due to the requirement for breaking the physical interface between real-components and replacing it with a virtual communication medium (like the internet) that is inherently flawed due to finite delay and *jitter*. Jitter refers to the quality of communication to reorder bits of information upon receipt at the destination.

### 1.4 Virtually Connected Hybrid Vehicle

Considering the increasing pressure from the governments and emerging technological opportunities, the industry has come together with the aid of public funding to reduce developmental expenditure by exploiting digitalisation and virtualisation. Virtually Connected Hybrid Vehicle (VCHV) is one such project. A virtual simulation platform to

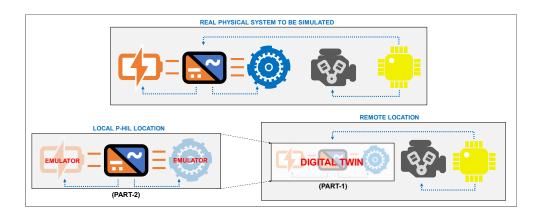

undertake geographically distributed multi-HIL simulation (Fig 1-6) of a generic automotive powertrain was proposed 5 years ago with a vision to reduce development costs and time-to-market of new powertrains. VCHV is one of the many projects funded by the Advanced Propulsion Centre (APC) [14][15], which is the UK government's initiative to propel the country to become the global hub of research, development and production of low carbon propulsion technologies.

Fig 1-6 Underlying concept of Geographically Distributed Hardware-in-the-Loop (GD-HIL) - HIL centres in separate locations operating in tandem

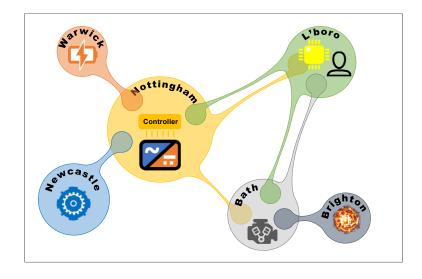

APC operates through its six centres [16] that are technological centres of excellence in their respective fields pertaining to hybrid propulsion system (battery, motor, engine etc.). VCHV project proposes to host a distributed simulation of the entire powertrain with each of these six centres behave as a HIL centre for its respective powertrain component (Fig 1-7). Since something like this has never been done before, the project would start with a feasibility study and arrive at the best opportunity for implementation of a working proof of concept.

Fig 1-7 Proposed multi-centre GD-HIL virtual simulation testbed

University of Nottingham is the **power electronics centre** and strives to deliver the enabling technology to bring a generic automotive power converter "online" in this distributed HIL simulation platform. This PhD aims to explore the state of the art in geographically distributed HIL simulation for automotive hybrid electric powertrains and investigate and identify suitable architecture for the VCHV HIL system. Being the power converter HIL centre, it is aimed to "project" a replica model of a generic electric powertrain to other HIL centres like the **engine centre** and **vehicle controller centre** based on real-time operation of a physical power converter locally and the same for motor and battery remotely.

### 1.5 Intent and Novelty of this PhD Project

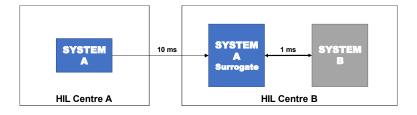

As with any fresh project, a scoping exercise was done to investigate the state of the art in technology and what could be achieved in terms of distributed simulation with the current technology in computing and communications. It may be reasonably inferred that it would be impossible to virtually connect two "halves" of a system and run a simulation cycle to study certain effects of interest that have time constants comparable to the delaying effects of the virtual connection. A tight degree of coupling may warrant the need of a local "surrogate" model that is able to replicate the immediate reactions of the hardware in the short-term and rely on periodic realignment information form the hardware over long-term to keep itself from diverging. Fig 1-8 illustrates this proposition

with a hypothetical scenario. The simulation time constant is 1ms which is analogous to the short term. The virtual connection time constant is 10ms which is the long term. This surrogate model (henceforth referred to as the "Digital Twin") reacts to the simulation in centre B every 1ms. The HIL simulator in centre A sends a realignment packet to its Digital Twin every 10ms hence keeping it in check.

Fig 1-8 Concept of local "surrogate" model dealing with instantaneous responses locally, periodically realigned by actual model over remote communication

Especially true for electrical systems, the waveforms of interest have very short time constants generally in the order of microseconds. This observation made it distinctly clear that a Digital Twin is necessary for electrical systems in this application and much of the PhD was spent towards finding and implementing the best possible Digital Twin. This model of the real hardware shall be deployed at every remote location that would directly interact with the hardware at that remote location (via the HIL simulator) in real-time. Any divergence between the Digital Twin and its "master" hardware shall be periodically realigned through virtual communication between them via the internet.

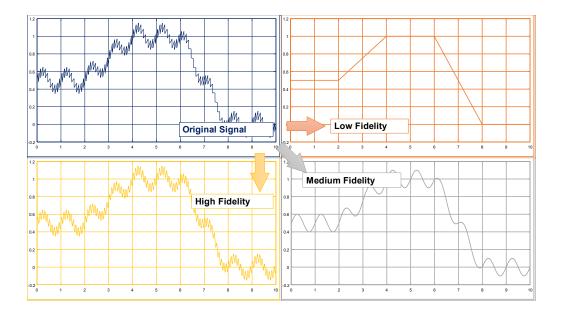

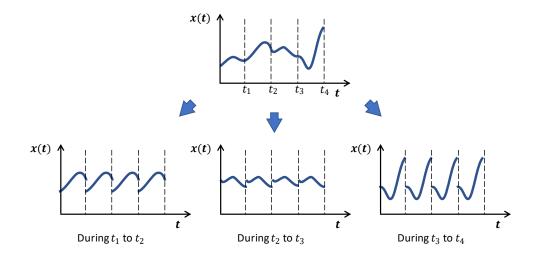

Thinking about its applications, it is also beneficial for a product like this to be as generic as possible. In multi-HIL scenarios (more than two HIL locations), it may be required for a DUT to be replicated in various levels of precision in different locations. For example (Fig 1-9), a power converter of an electric drive needs to be replicated to a high detail at the motor simulator, since performance of a motor vastly depends on the harmonic content of the converter output. Contrarily, the battery management system simulator in a third location does not concern itself with detailed harmonic content of the converter power input and is content with a slow-averaged value.

Fig 1-9 Different levels of fidelity of original signal may be required at different centres for their respective application

So, the Digital Twin is required to do the following:

- A. Computationally efficient for real-time operation with the simulator

- B. Particularly good model accuracy for instantaneous response, i.e., highly accurate model for a narrow operating region

- C. Capability to react to external realignment information to shift its operating region when necessary

- D. Deployable in varying precision configuration basis the coupling requirement with the respective HIL hardware

The best solution for an ideal Digital Twin was sought that conforms with these four key requirements as stated above. Various popular modeling strategies were investigated from the time v frequency domain spectrum and the best methodology was adapted to suit the special requirements for this application.

Following on from the introduction into the project above, outlined below are the outcomes intended for this PhD project:

Develop a robust Digital Twin for a generic electric automotive powertrain that can be deployed in multiple locations and kept converged with the master DUT/hardware over various qualities of the virtual communication like the internet. This Digital Twin must be efficient and quick for real-time operation and consume the minimum computing power as possible by having a customisable "fidelity setting" dependent on the requirement of the local simulator.

- Commission an electric power converter HIL simulator rig to enable HIL testing of an automotive power converter and demonstrate drivecycle runs on the simulator. This would be used as a benchmark to validate the performance of the Digital Twin baseline behaviour, and as the real-time DUT realigning the remotely running Digital Twin, effectively being the second half of the proof of concept for this PhD.

- Undertake a feasibility study of the geographically distributed hardware-in-loop and its viability given the state of the art in power converter modeling and simulation, HIL technology and virtual communications. This is planned to be a collaborative effort with the other partner universities which have similar PhD programs (for distributed HIL virtual testbed) but for other components of a hybrid powertrain, like the engine or battery. Some publications from partner universities are [17][18][19][20][21].

There are **two primary novelty aspects of the Digital Twin** that have been explored and presented in this PhD project – variable frequency operation of a Digital Twin based on the Multi-Frequency Averaging (MFA) technique, and novel approach to multiplication of two waveforms in the frequency domain. As will be shown in the following chapters, MFA is potentially an excellent technique for Digital Twin implementation but all previously published works on MFA-based models explored were found to be only for a fixed frequency operation. Automotive application necessarily requires dynamic speed of operation, and the underlying mathematics was further developed and successfully tested to facilitate variable frequency of operation.

A **third novel contribution** in this PhD is the development and validation of a proxy encoder solution for motor emulation. Control of a physical synchronous motor (primarily used in automotive traction applications) requires highly accurate and precise information of the motor shaft position. Testing an inverter requires this high-speed signal to be generated using low-speed CPU based processor in the simulator. A novel software-based solution was proposed and developed in this work. A virtual HIL simulation testbed for multiple prototypes operating from different locations for an electric automotive powertrain application has never been envisioned or attempted before. This PhD project has endeavoured to do this in the last couple of years by conceptualising this distributed multi-HIL framework for automotive powertrain testing. This also forms the foundation for the subsequent works done on the development and testing of the electric powertrain Digital Twin.

Intermediate results and progress have been presented to the wider community through the following publications:

- Conference paper in VPPC, Chicago, USA [22]

- Journal paper in IET EST [23]

## **1.6 Thesis Structure Guideline**

**CHAPTER 1** provides a broad introduction to the automotive industry and the current disruptive megatrends that will forge the modern electrified car of the future. Key technological challenges are discussed which are needed to be overcome to achieve this. Geographically distributed Hardware-in-the-Loop (GD-HIL) simulation is identified as a key piece of the puzzle and how this PhD project is adding towards the common goal. There is a need for a global system architecture which shall be elaborated in the next two chapters. Key technical elements identified to implement GD-HIL for Power Electronic Converters (PEC) are:

- local emulation of remote hardware (i.e., battery and machine) and

- remote emulation of local hardware (i.e., converter/electric powertrain emulation in the engine location).

**CHAPTER 2** provides an extensive literature review of various HIL types and specific technological challenges and enablers. Every type is supported by multiple ongoing projects in the world as case studies. Specific learning outcomes from each case study are identified that are incorporated in the geographically distributed HIL simulation testbed of a generic electrified propulsion system. An overall global system architecture has been proposed towards a reliable and robust "virtually connected hybrid vehicle".

**CHAPTER 3** provides an extensive literature review of different approaches to virtually connect between different HIL centres. Different methods of information exchange between centres are investigated and the Master-Follower approach is found to be the best option for electrified powertrains. An MFA-based Digital Twin is further identified as the ideal method that satisfies the four pre-requisites stated as A, B, C, D in the previous sub-chapter (1.5). Following on, the thesis has been split into two parts: Part 1 – Remote Digital Twin (CHAPTER 4) and Part 2 – Local HIL implementation (CHAPTER 5 and CHAPTER 6).

Especially for electrified propulsion systems, Multi-Frequency Averaging (MFA) methodology has been identified to be the best for real-time computability, remote realignment of parameters and configurable fidelity of output. Variable frequency operation of MFA and a practical implementation of the above three features have been identified as the novelty in this PhD (preliminary work published earlier in IET and IEEE publications [22][23]). **CHAPTER 4** provides the mathematical foundation of the MFA model and builds on it to produce the variable frequency operation framework. The implementation of the same through a MATLAB/Simulink<sup>™</sup> model has been discussed. A benchmarking study has been done to verify this model against detailed simulation models of an equivalent system.

**CHAPTER 5** provides the methodology for doing a HIL experiment on a generic power electronic converter. Motor emulation is discussed in detail and its implementation on the Triphase simulator rig is explained.

**CHAPTER 6** provides the results and findings after drivecycle experiments using the motor emulation strategy developed in the previous chapter were performed on the Triphase simulator.

**Chapter 7** concludes the thesis by wrapping all technical findings from the previous chapters together. All shortcomings in the project duration are identified and future work has been proposed.

Each chapter has **Introduction** and **Summary** sub-chapters that gives an executive overview without delving into minute details.

38

# **CHAPTER 2 Geographically Distributed**

# **Power Hardware-In-The-Loop Simulation**

## 2.1 Introduction

Geographically distributed power hardware-in-the-loop (GD-PHIL) is a complex term loaded with several important distinguishing features, which requires to be deconstructed to understand properly.

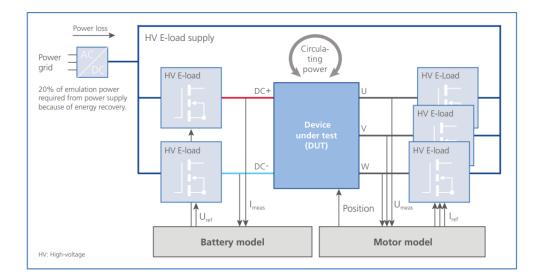

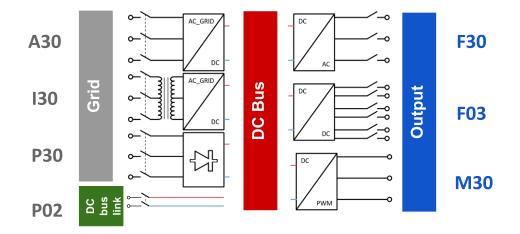

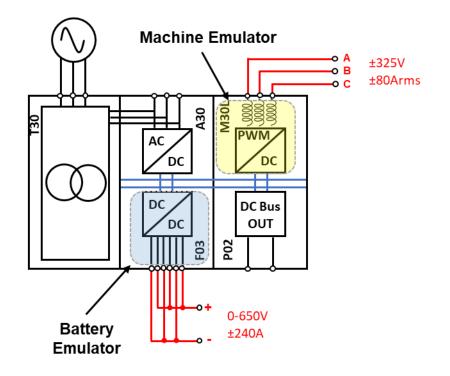

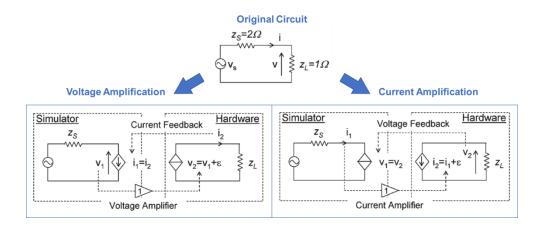

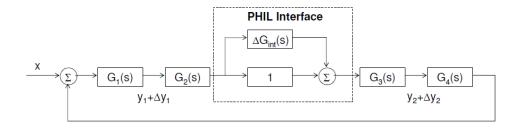

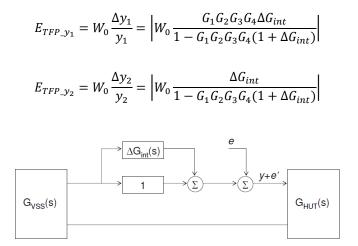

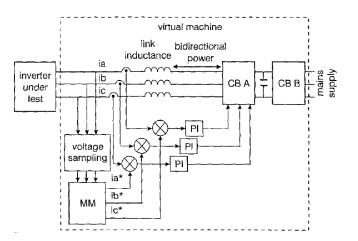

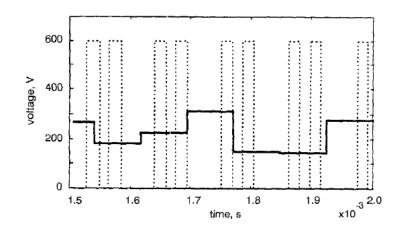

**Simulation** in general, refers to the *imitation* of a real operation or event of a physical system, but without using it. In digital simulation, the imitation occurs in a computer where the physical system in question is replicated in the digital environment using various "digital models" put together in a closed loop. Broadly, there are two categories of models, *analytical* and *empirical*. Analytical models replicate the physics involved in the real system in the form of mathematical equations which are solved at defined periodic intervals or *time-steps*. Empirical or Predictive models use real observations rather than mathematically describable relationships of the system to replicate it. This often requires *training* the model using the real system on a set of operating regions to build a *lookup table*, which is then referred to during simulation. In majority of modern models (thanks to fast computers), some form of hybridisation between the two categories is used.