#### **Department of Electrical and Electronic Engineering**

# On-Board Health Monitoring of Power Modules in Inverters Driving Induction Motors

Attahir Murtala Aliyu MEng

Thesis submitted to the University of Nottingham for the degree of Doctor of Philosophy October 2016

To

My respected parents,

#### **Abstract**

This thesis presents an on-board methodology for monitoring the health of power (converter) modules in drive systems. The ability to keep regular track of the actual degradation level of the modules enables the adoption of preventive maintenance, reducing or even eliminating altogether the appearance of failures during operation, significantly improving the availability of the power devices.

The novelty of this work is twofold: the complete system that is used to achieve degradation monitoring; combining the heating technique (to obtain thermal transient) and the measurement without additional power components such as IGBT, MOSFETS, which affects the reliability, power density and complexity. The only additional component is an analog measurement circuit, which can be integrated into the gate drive board. The test routine is carried out during non-operational periods and idle times. Trains are used as a case study, where checks for degradation are made when the train is not in use, such as at the end of the day, after daily operation or at the start before daily operation and other non-operational periods. It is important to keep the train at standstill while tests are carried out. Hence a methodology to heat the devices with current from the input supply while keeping the motor load at a stand-still is presented. Experimental results obtained from this show that it is possible to implement an on-board health monitoring system in converters which measures the degradation on power modules.

The work uses the concepts of vector control heating and structure function to check for degradation. It puts forward a system that is used on-board to measure the cooling curve and derive the structure function during idle times for maintenance purposes. The structure function is good tool for tracking the magnitude and location of degradation in power modules. Vector control gives the advantage of controlling the motor with field current and torque current (similar concept to DC motors).

#### Acknowledgement

I would really like to thank my supervisor, Associate Prof. Alberto Castellazzi, for his indefatigable support and encouragement coupled with his invaluable advice, motivation and guidance throughout the project.

I would like to express my gratitude towards my internal examiner Associate Professor Christian Klumpner and external examiner Professor Volker Pickert for volunteering their time and effort to examine and provide the very much needed positive feedback. In particular, my special thanks to Associate Professor Christian Klumpner for giving me positive criticism and guidance during my first year and second year PhD reviews.

Also, my sincere thanks to my friends and colleagues at the PEMC group, Emre, Shajjad, Marija, Manju, Savvas, Bilal, Mahmoud, Nourdeen, Shuai, Xiang, Amir, Asad, Adane, Bassem for making these years worthwhile.

I would like to thank Abdulsalam, Ummi, Abubakar, Fatima, Umar, Amira, Nana, aunt Rakiya, aunt Halima, Baba Muhammad and everyone in my family for always being there as helping hands in all matters. I would like to especially thank my uncle Ismail, for his critical support, advice and motivation.

My friends, Awwal, Shubzy, Kamil, White, Timomo and Khalid, thanks for the constant motivation. To Siyam, you have been a big support during my study.

Last but by no means the least, my deepest love and thanks to my parents Murtala Aliyu and Zainab Aliyu for their unconditional love, support, motivation and confidence in me during all these years. This could not have been possible without them.

#### **Thesis Contribution**

The work presented in this thesis has resulted in two conference and one journal publications.

- A.M. Aliyu, S. Chowdhury and A. Castellazzi, "In-situ health monitoring of power converter modules for preventive maintenance and improved availability," *Power Electronics and Applications* (EPE'15 ECCE-Europe), 2015 17th European Conference on, Geneva, 2015, pp. 1-10.

- A.M Aliyu and A. Castellazzi, "Extracting Structure Functions of Power Devices in Induction Motor Drives" *Therminic* 2016, Budapest

- A.M Aliyu and A. Castellazzi," Prognostic System for Power Modules in Converter Systems Using Structure Function" *IEEE Transactions on Power Electronics, (Under review)*.

Learning from this activity has also resulted in a Journal

• J. Ortiz Gonzalez, A.M. Aliyu, O. Alatise, A. Castellazzi, L. Ran, P. Mawby, Development and characterisation of pressed packaging solutions for high-temperature high-reliability SiC power modules, *Microelectronics Reliability*

## **Contents**

| Abstract                                         | iii  |

|--------------------------------------------------|------|

| Acknowledgement                                  | iv   |

| Thesis Contribution                              | v    |

| List of Symbols and Acronyms                     | viii |

| List of Figures                                  | xi   |

| List of Tables                                   | xv   |

| Chapter 1: Introduction                          | 1    |

| 1.1 Motivation                                   | 1    |

| 1.1.1 Power Module                               | 2    |

| 1.2 Aims and Objectives of the Work              | 4    |

| 1.2.1 Background                                 | 5    |

| 1.3 Thesis outline                               | 6    |

| Chapter 2: Power Modules Structure & Reliability | 8    |

| 2.1 Introduction                                 | 8    |

| 2.2 Heat Transfer in Power Devices               | 8    |

| 2.2.1 Analysis (Conduction)                      | 9    |

| 2.3 Structure of Power Modules                   | 13   |

| 2.3.1 Die                                        | 14   |

| 2.3.2 Solder                                     | 15   |

| 2.3.3 Substrate                                  | 16   |

| 2.3.4 Base Plate                                 | 17   |

| 2.3.5 Silicone Gel                               | 17   |

| 2.3.6 Thermal Grease                             | 18   |

| 2.4 Failure mechanisms                           | 19   |

| 2.4.1 Wire-bond Fatigue                          | 19   |

| 2.4.2 Solder Fatigue and Solder Voids            | 22   |

| 2.4.3 Aluminium Reconstruction                   | 24   |

| 2.4.4 Other Failure Mechanisms                   | 25   |

| 2.4.5 Effects of Failure Mechanisms              | 25   |

| 2. 5 Monitoring Degradation                      | 25   |

| 2.5.1 IGBT Structure and Operation               | 26   |

| 2.5.2 Threshold Gate Voltage as TSEP             | 27   |

| 2.5.3 Gate Resistance as TSEP                                                                | 29 |

|----------------------------------------------------------------------------------------------|----|

| 2.5.4 V <sub>ge</sub> Turn-Off Time as TSEP                                                  | 30 |

| 2.5.5 Recovery Rate (di/dt) as TSEP                                                          | 31 |

| 2.5.6 Collector–Emitter Voltage as TSEP                                                      | 32 |

| 2.5.6 Choice of TSEP                                                                         | 34 |

| 2.6 Conclusion                                                                               | 35 |

| Chapter 3: Representation of Module Structural Features: Thermal Impedan Structure Functions |    |

| 3.1 Introduction                                                                             | 37 |

| 3.2 Thermal Networks                                                                         | 39 |

| 3.2.1 Derivation of Thermal Network from Physical Model (Cauer)                              | 41 |

| 3.2.2 Derivation of Thermal Networks from Thermal Transient                                  | 42 |

| 3.3 Foster to Cauer Conversion                                                               | 53 |

| 3.4 Structure Function                                                                       | 55 |

| 3.4.1 Cumulative Structure Function                                                          | 56 |

| 3.4.2 Differential Structure Function                                                        | 57 |

| 3.4.3 Computational Issues of the Structure Function                                         | 58 |

| 3.5 Conclusion                                                                               | 61 |

| Chapter 4: On-Board Temperature Profile Acquisition                                          | 62 |

| 4.1 Introduction                                                                             | 62 |

| 4.2 Measuring Technique                                                                      | 62 |

| 4.2.1 Basic Off-line Measurement Method                                                      | 64 |

| 4.3 On-Board Module Heating-Up Method                                                        | 67 |

| 4.3.1 Vector Control                                                                         | 68 |

| 4.4 Temperature Measurement in the Inverter                                                  | 77 |

| 4.5 Conclusion                                                                               | 81 |

| Chapter 5: Implementation of On-Board Diagnostics Capability                                 | 82 |

| 5.1 Introduction                                                                             | 82 |

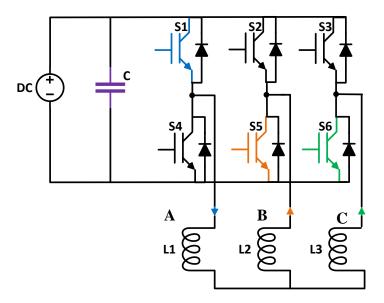

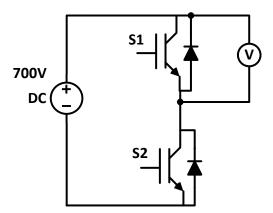

| 5. 2 Power Inverter                                                                          | 84 |

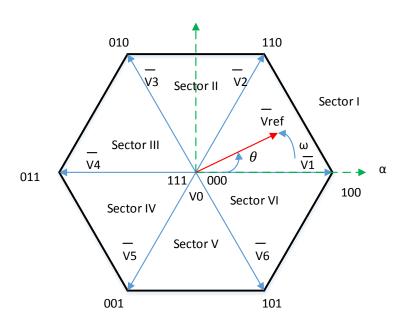

| 5.2.1 Space Vector Modulation Scheme                                                         | 86 |

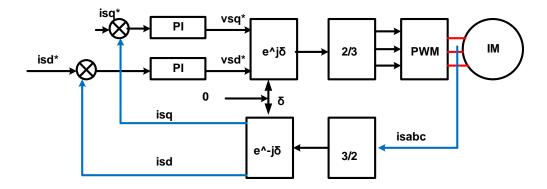

| 5.3 Control                                                                                  | 89 |

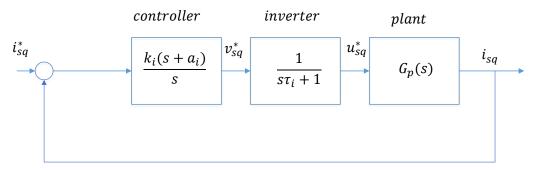

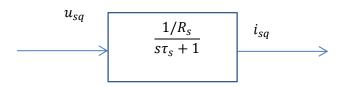

| 5.3.1 Closed Loop Control                                                                    | 90 |

| 5.4 Gate Driver                                                                              | 94 |

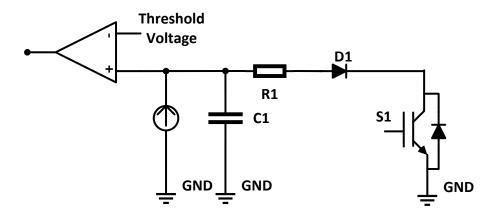

| 5.5 Measurement Circuit Design                                                               | 95 |

| 5.5.1 Protection Board                                              | 99  |

|---------------------------------------------------------------------|-----|

| 5.6 Conclusion                                                      | 102 |

| Chapter 6: Proof of Concept Demonstration                           | 103 |

| 6.1 Introduction                                                    | 103 |

| 6.2 Structure Function Capability                                   | 103 |

| 6.3 Inverter Measurements                                           | 106 |

| 6.4 Conclusion                                                      | 117 |

| Chapter 7: Conclusion                                               | 118 |

| 7.1 Summary                                                         | 118 |

| 7.2 Contribution                                                    | 118 |

| 7.3 Future Work                                                     | 119 |

| 7.4 Application to Other Inverter Topologies                        | 119 |

| Appendix 1                                                          | 123 |

| A1.1 1D Heat Conduction                                             | 123 |

| Appendix 2                                                          | 125 |

| A2.1 Derivation of convolution form equation                        | 125 |

| A2.2 MATLAB code for transforming Foster network to a Cauer network | 126 |

| A2.3 An example of Foster to Cauer Conversion                       | 127 |

| Appendix 3                                                          | 131 |

| A3.1 Clarke's Transformation                                        | 131 |

| A3.2 Principles of an Induction Motor                               | 132 |

| A3.3 Park's Transformation                                          | 134 |

| A3.4 Indirect rotor flux orientation                                | 135 |

| References                                                          | 137 |

# **List of Symbols and Acronyms**

| Symbols             | Definition                                              |  |  |

|---------------------|---------------------------------------------------------|--|--|

| $q_k$               | The rate at which the heat is transferred by conduction |  |  |

| λ                   | Thermal Conductivity                                    |  |  |

| A                   | Surface Area                                            |  |  |

| T                   | Temperature                                             |  |  |

| ρ                   | Material Density                                        |  |  |

| c                   | Specific Heat Capacity                                  |  |  |

| $c_{v}$             | Volumetric Heat Capacitance                             |  |  |

| $R_{th}$            | Thermal Resistance                                      |  |  |

| $C_{th}$            | Thermal Capacitance                                     |  |  |

| τ                   | Time Constant                                           |  |  |

| t                   | time                                                    |  |  |

| $Z_{\text{th}}$     | Thermal Impedance                                       |  |  |

| °C                  | Celsius                                                 |  |  |

| ppm                 | Parts Per Million                                       |  |  |

| μ                   | Micro $(x10^{-6})$                                      |  |  |

| Al                  | Aluminium                                               |  |  |

| Si                  | Silicon                                                 |  |  |

| Cu                  | Copper                                                  |  |  |

| $Al_2O_3$           | Aluminium Oxide                                         |  |  |

| AlN                 | Aluminim Nitride                                        |  |  |

| $Si_3N_4$           | Silicon Nitride                                         |  |  |

| AlSiC               | Aluminium Silicon Carbide                               |  |  |

| SiC                 | Silicon Carbide                                         |  |  |

| AlGaN               | Aluminium Gallium Nitride                               |  |  |

| GaN                 | Gallium Nitride                                         |  |  |

| AsGa                | Arsenic Gallium                                         |  |  |

| BeO                 | Beryllium Oxide                                         |  |  |

| DBC                 | Double Bonded Copper                                    |  |  |

| $V_{ce}$            | Collector Emitter Voltage                               |  |  |

| $V_{\text{ge(th)}}$ | Threshold voltage                                       |  |  |

R<sub>G</sub> Gate Resistance

I<sub>h</sub> Heating Current

I<sub>m</sub> Measurement Current

K Kelvin

m  $Milli(x10^{-3})$

Rgint Internal Gate Resistance

$\Omega$  Ohms

$\begin{array}{ll} \mbox{Vge} & \mbox{Gate-Emitter Voltage} \\ \mbox{T}_{\mbox{\scriptsize i}} & \mbox{Junction Temperature} \end{array}$

f Frequency

n Nano(x10<sup>-9</sup>)

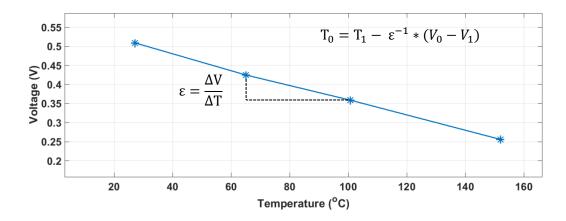

ε Rate of Change of Voltage With Temperature(K factor)

$C\Sigma$  Cumulative Thermal Capacitance

$R\Sigma$  Cumulative Thermal Resistance

R<sub>channel</sub> Channel Resistance

R<sub>drift</sub> Drift Resistance

$\omega$  Angular Speed

V<sub>s</sub> Stator Voltage

V<sub>r</sub> Rotor Voltage

I<sub>s</sub> Stator Current

I<sub>r</sub> Rotor Current

R<sub>s</sub> Stator Resistance

R<sub>r</sub> Rotor Resistance

$\phi_s \qquad \qquad Stator \ Flux$

$\phi_r \qquad \qquad Stator \ Flux$

$\omega_e$  Electrical Speed

$\omega_r$  Rotor Speed

$\omega_{sl}$  Slip Speed

L<sub>o</sub> Magnetizing Inductance

L<sub>r</sub> Rotor Inductance

$L_{lr}$  Rotor Leakage Inductance

L<sub>ls</sub> Stator Leakage Inductance

**Σ** Damping Factor

### Natural Frequency

$\omega_n$

WBG

Wide Band Gap

| Acronym | Definition                                        |  |  |  |

|---------|---------------------------------------------------|--|--|--|

| IGBT    | Insulated-Gate Bipolar Transistor                 |  |  |  |

| CTE     | Coefficient of Thermal Expansion                  |  |  |  |

| TSEP    | Temperature Sensitive Electrical Parameters       |  |  |  |

| TIM     | Thermal Interface Material                        |  |  |  |

| SEM     | Scanning Electron Microscope                      |  |  |  |

| SAM     | Scanning Acoustic Microscope                      |  |  |  |

| NTC     | Negative Temperature Coefficient                  |  |  |  |

| HV      | High Voltage                                      |  |  |  |

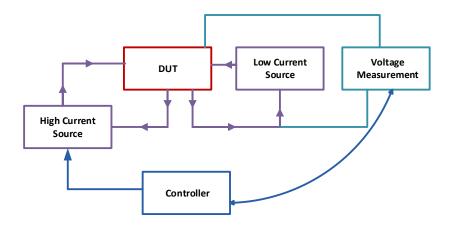

| DUT     | Device Under Test                                 |  |  |  |

| DC      | Direct Current                                    |  |  |  |

| MOSFET  | Metal-Oxide-Semiconductor Field-Effect Transistor |  |  |  |

| NPT     | Non-Punch Trough                                  |  |  |  |

| IEC     | International Electrotechnical Commission         |  |  |  |

| DAQ     | Data Acquisition                                  |  |  |  |

| RMS     | Root Mean Square                                  |  |  |  |

| EMF     | Electromotive Force                               |  |  |  |

| AC      | Alternating Current                               |  |  |  |

| A/D     | Analog to Digital Converter                       |  |  |  |

| IM      | Induction Motor                                   |  |  |  |

| FPGA    | Field Programmable Gate Array                     |  |  |  |

| DSP     | Digital Signal Processor                          |  |  |  |

| VSI     | Voltage Source Inverter                           |  |  |  |

| SVM     | Space Vector Modulation                           |  |  |  |

| HPI     | Host Port Interface                               |  |  |  |

| PWM     | Pulse Width Modulation                            |  |  |  |

| CMMR    | Common Mode Rejection Ratio                       |  |  |  |

| ANPC    | Active Neutral Point Clamped                      |  |  |  |

| MVD     | Medium Voltage Drives                             |  |  |  |

| HEMTs   | High Electron Mobility Transistors                |  |  |  |

# **List of Figures**

| Fig 1.1: Power semiconductor devices and applications [1]                              | 1   |

|----------------------------------------------------------------------------------------|-----|

| Fig 1.2: Illustration of conventional power module cross section                       | 3   |

| Fig 1.3: (Left) Wire-bond lift off (right) solder fatigue and solder voids[11]         | 3   |

| Fig. 2.1. Illustration of any discounting allow flows                                  | 4.4 |

| Fig 2.1: Illustration of one dimensional heat flow                                     |     |

| Fig 2.2: Cross-section representation of a conventional power module                   |     |

| Fig 2.3: Conventional half bridge module with devices connected in parallel            | 15  |

| Fig 2.4: Scanning acoustic microscope image of IGBT and diode solder & cross-          |     |

| section showing solder layer                                                           |     |

| Fig 2.5: Bottom and top side of ceramic substrate                                      |     |

| Fig 2.6 : Baseplate of an IGBT module & plastic housing                                |     |

| Fig 2.7: Illustration of thermal grease used to fill air gaps[33]                      | 18  |

| Fig 2.8: Thermal conductivity of materials used in a module compared to thermal        |     |

| grease[33]                                                                             | 18  |

| Fig 2.9: SEM image wire-bond lift off [7]                                              |     |

| Fig 2.10: Wire-bond subjected to thermo-mechanical stress [37]                         | 21  |

| Fig 2.11: SEM image of wire-bond cracking[7]                                           | 21  |

| Fig 2.12: Relationship between loop height to width ratio and number of cycles to      |     |

| failure[37]                                                                            | 22  |

| Fig 2.13: SAM image of solder between substrate and baseplate indicating solder        |     |

| voids                                                                                  | 23  |

| Fig 2.14: Acoustic scan showing solder fatigue                                         | 23  |

| Fig 2.15: SAM images of cycled solder layer of modules using copper(left) and          |     |

| AlSiC(right) baseplates[38]                                                            | 24  |

| Fig 2.16: Metallization before power cycling (left) and after (rght)[7]                | 24  |

| Fig 2.17: N-channel IGBT (NPT) cross-section                                           | 27  |

| Fig 2.18: Inversion channel IGBT                                                       | 28  |

| Fig 2.19: Basic schematic for threshold voltage measurement                            | 28  |

| Fig 2.20: Principle of using Rgint as a TSEP                                           | 30  |

| Fig 2.21: Vge voltage at different temperatures[46]                                    |     |

| Fig 2.22: di/dt measurement circuit                                                    |     |

| Fig 2.23 IGBT Equivalent Circuit [53]                                                  |     |

| Fig 2.24: Vce measurement showing parasitics                                           |     |

|                                                                                        |     |

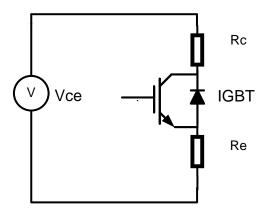

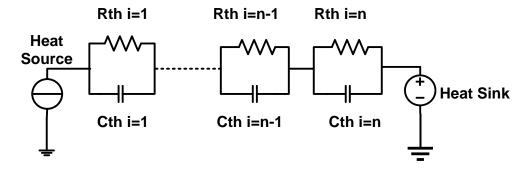

| Fig 3.1: Schematic process of obtaining the structure function.reprinted from [59]     | 38  |

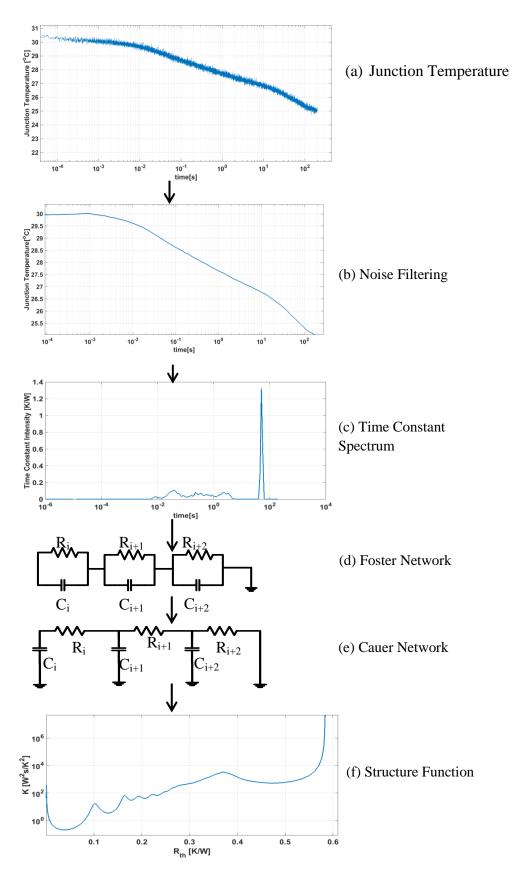

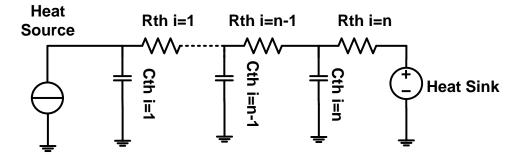

| Fig 3.2: Foster network                                                                | 40  |

| Fig 3.3: Cauer network                                                                 | 40  |

| Fig 3.4: Physical structure indicating heat flow                                       |     |

| Fig 3.5: Junction temperature and heating current                                      |     |

| Fig 3.6: Temperatures at different points in a solid structure in relation to distance |     |

| Fig 3.7: Thermal impedance curve on a semi-logarithmic scale                           |     |

| Fig 3.8: Illustration of data extraction in the graphical method                       |     |

| $\omega$                                                                               | _   |

| Fig 3.9: Thermal impedance represented in the cooling and heating form            | 4/    |

|-----------------------------------------------------------------------------------|-------|

| Fig 3. 10: Thermal impedance with fitted curve                                    | 48    |

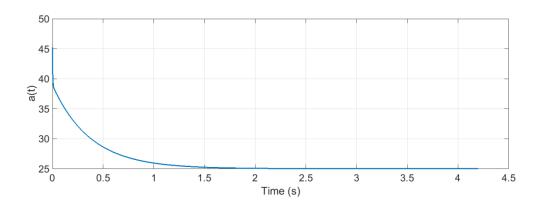

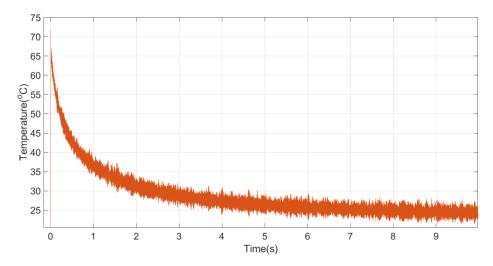

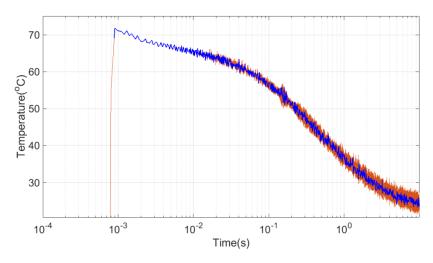

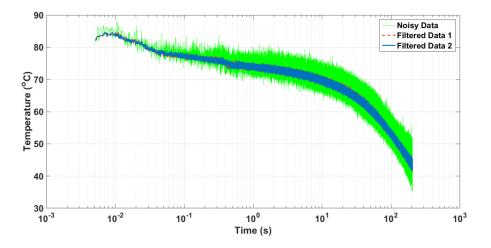

| Fig 3.11: Cooling thermal transient                                               | 50    |

| Fig 3. 12: Cooling thermal transient (log scale)                                  | 51    |

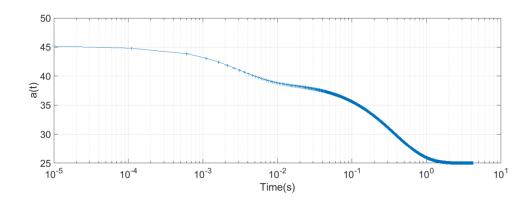

| Fig 3.13: Convolution of thermal transient                                        | 51    |

| Fig 3.14: Weighting function                                                      | 52    |

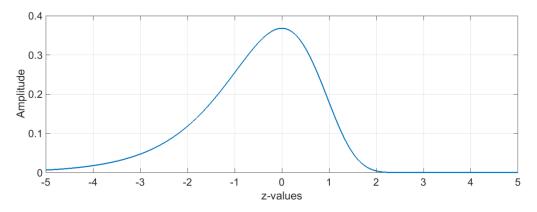

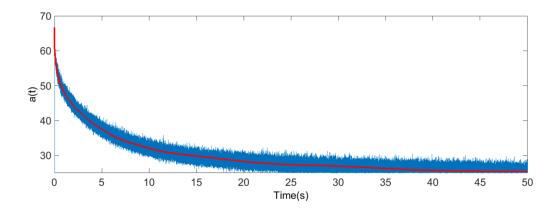

| Fig 3.15: Experimental cooling curve, filtered (red) and unfiltered (blue)        | 53    |

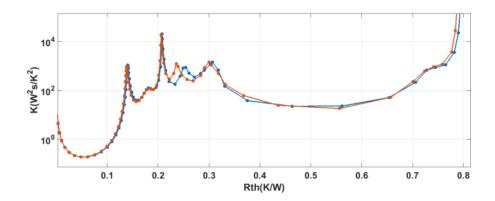

| Fig 3.16: Experimental convolution form                                           | 53    |

| Fig 3.17: Cauer Network Analysis                                                  | 53    |

| Fig 3.18: Cumulative structure function                                           | 56    |

| Fig 3.19: One dimensional heat flow model                                         | 57    |

| Fig 3.20: Differential structure function                                         | 58    |

| Fig 3.21: Reference model. [59]                                                   | 59    |

| Fig 3.22: Differential structure function showing truncating effects. [59]        | 59    |

| Fig 3. 23: Structure functions showing the influence of precision digits.[59]     | 60    |

|                                                                                   |       |

| E' 41 ( ) N. Cl LICOTT (NIDT) C                                                   | 23.50 |

| Fig 4.1: (a) N-Channel IGBT (NPT) Cross Section (b) IGBT Equivalent Circuit[5     | 2]59  |

| Fig 4.2: Relationship between the Collector Emitter Voltage (Vce) and Collector   | Ε0    |

| Current (Ic)                                                                      |       |

| Fig 4.3: Measured temperature dependence of vce for a sense current I=100mA       |       |

| Fig 4.4: Cooling curve measurement chart                                          |       |

| Fig 4.5: Measured Cooling Curve                                                   |       |

| Fig 4.6: Measured cooling curve (log scale)                                       |       |

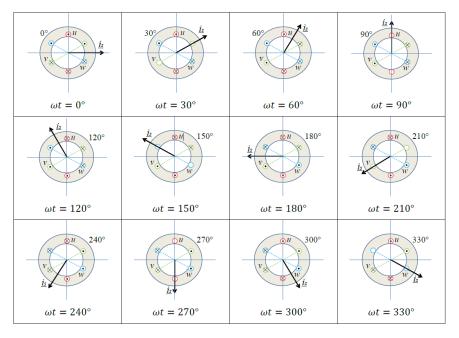

| Fig 4.7: Windings in an induction                                                 |       |

| Fig 4.8: Chart showing the rotation of the current space vector [85]              |       |

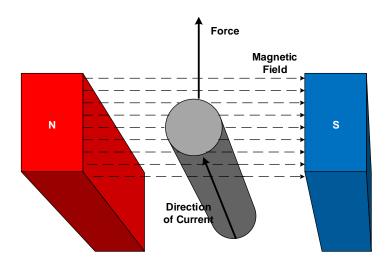

| Fig 4.9: Principle of DC motor                                                    |       |

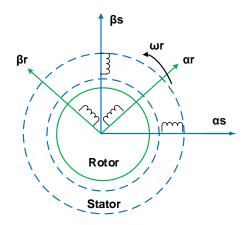

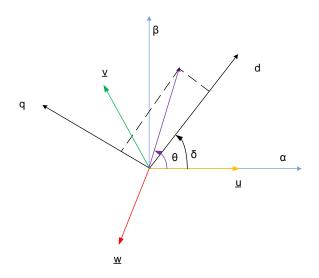

| Fig 4.10: Induction motor represented in $\alpha\beta$                            |       |

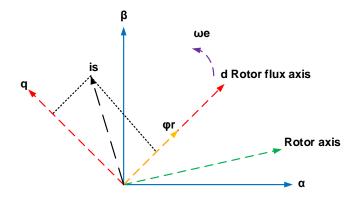

| Fig 4.11: Rotor flux orientation                                                  |       |

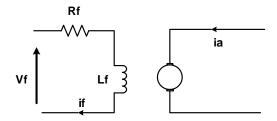

| Fig 4.12: Schematic of a DC motor                                                 |       |

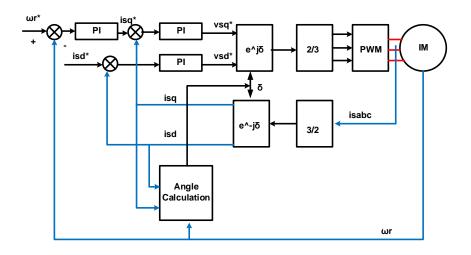

| Fig 4. 13: Fundamental structure of vector control (IRFO)                         |       |

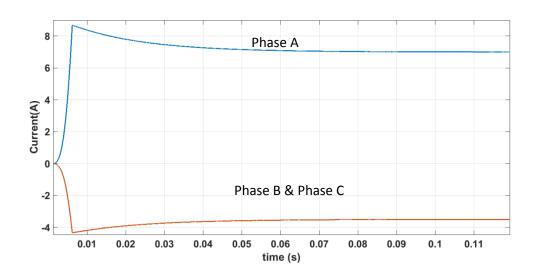

| Fig 4.14: Simulation of three phase currents                                      |       |

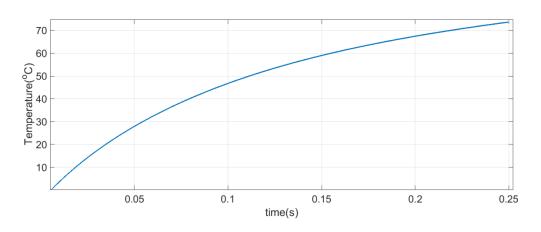

| Fig 4.15: Simulation of junction temperature of top switch (Phase A)              |       |

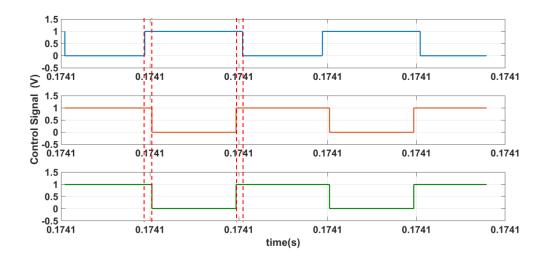

| Fig 4. 16: Simulation of three phase inverter showing currents and heated devices |       |

| Fig 4.17: Simulation switching sequence of heated devices                         |       |

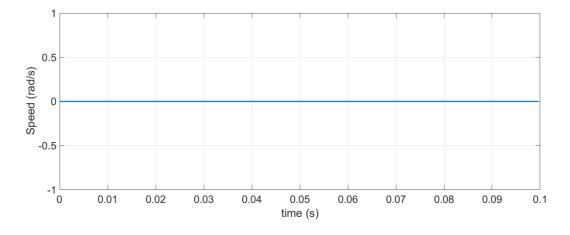

| Fig 4.18: Simulation of rotor speed                                               |       |

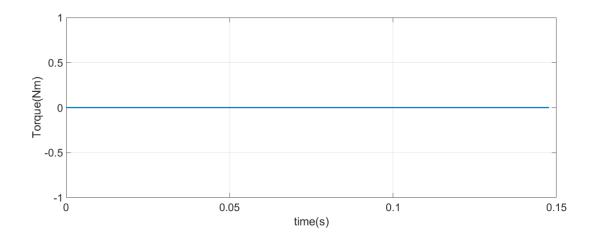

| Fig 4.19: Simulation of torque                                                    |       |

| Fig 4.20: Illustration of measurement circuit on inverter                         |       |

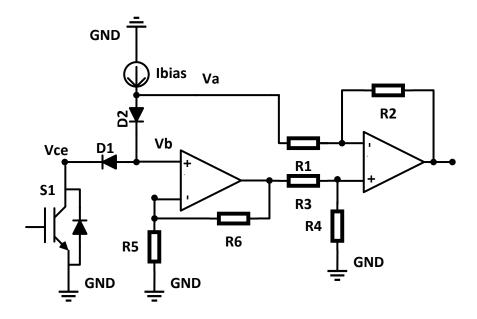

| Fig 4.21: Desaturation protection circuit                                         |       |

| Fig 4.22: Vce measurement                                                         | 77    |

| Fig 4.23: V <sub>ce</sub> calculation using operational amplifiers                | 78    |

|                                                                                   |       |

|                                                                                   |       |

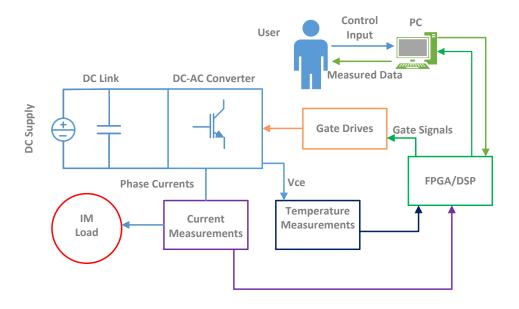

| Fig 5.1: Overview of experimental set-up                                          |       |

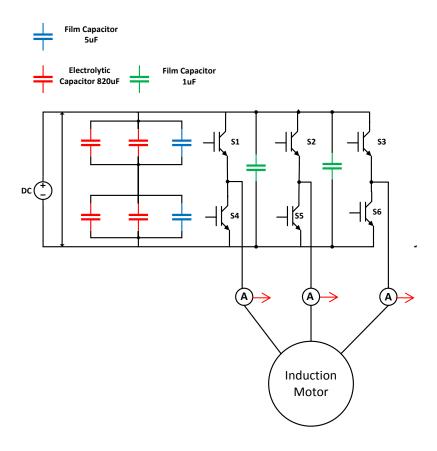

| Fig 5.2: Schematic of the power converter                                         | 83    |

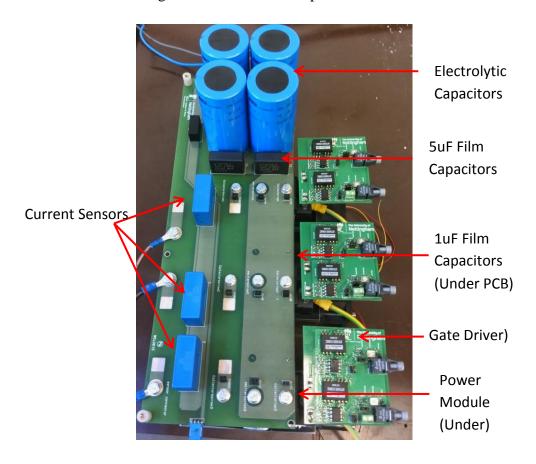

| Fig 5.3: Image of power converter                                                                                                                  | 83  |

|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig 5.4: Space vector diagram                                                                                                                      | 85  |

| Fig 5.5: Block diagram of vector control (IRFO)                                                                                                    | 89  |

| Fig 5.6: Control block                                                                                                                             | 89  |

| Fig 5.7: Plant transfer function                                                                                                                   | 90  |

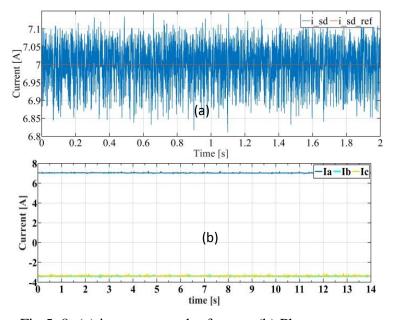

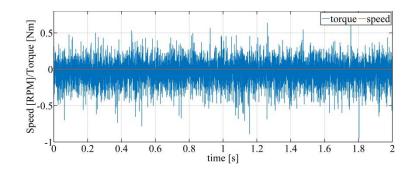

| Fig 5. 8: (a) i <sub>sd</sub> current and reference (b) Phase currents                                                                             | 91  |

| Fig 5.9: Speed and torque of induction motor during heating                                                                                        | 92  |

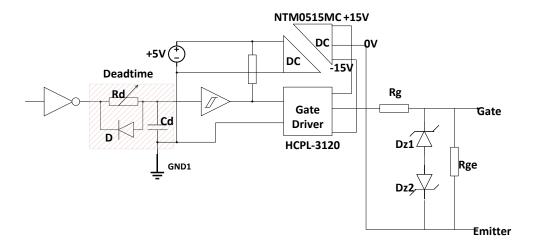

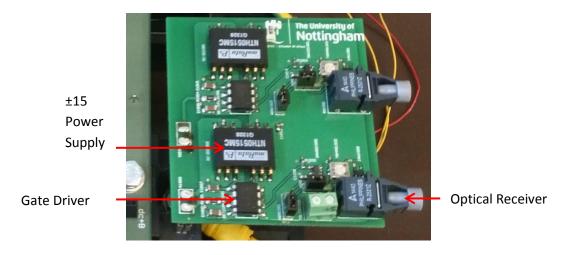

| Fig. 5.10: Gate driver design                                                                                                                      | 92  |

| Fig 5.11: Image of gate driver for 2 IGBTs                                                                                                         | 93  |

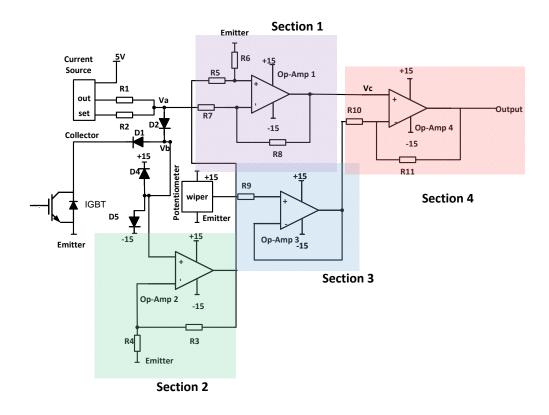

| Fig 5.12: Schematic of the for the top device measurement circuit                                                                                  | 95  |

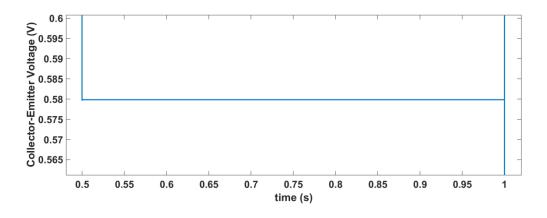

| Fig 5.13: Simulation of collector emitter voltage                                                                                                  |     |

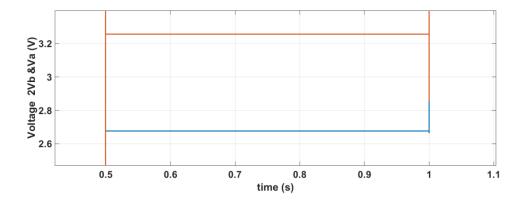

| Fig 5. 14: Voltages at the output of op-amp2 and node Va                                                                                           |     |

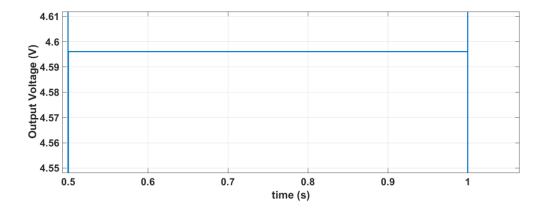

| Fig 5.15: Output of the measurement circuit                                                                                                        |     |

| Fig 5.16: Schematic of the isolation board                                                                                                         |     |

| Fig 5.17: Image of measurement circuit and isolation board                                                                                         |     |

| Fig 5. 18: Constant voltage measurement using digital multimeter and measurement                                                                   |     |

| circuit                                                                                                                                            |     |

| Fig 5. 19: Voltage measurement after the heating pulse                                                                                             |     |

| Fig 5. 20: Temperature change after heating pulse                                                                                                  |     |

|                                                                                                                                                    |     |

| Fig 6.1: (a) Acoustic scan of solder layer (b) camera image                                                                                        | 102 |

| Fig 6.2: Experimental thermal transients for good and bad diode                                                                                    |     |

| Fig 6. 3: Differential structure function of the (a) solder layer (good and bad)                                                                   |     |

| device with difference at the substrate                                                                                                            |     |

| Fig 6.4: Inverter during measurement phase (free-wheeling)                                                                                         |     |

| Fig 6.5: First attempt at measurement                                                                                                              |     |

| Fig 6.6: Current and voltage (collector-emitter) of DUT                                                                                            |     |

| Fig 6.7: Normalized temperature curve                                                                                                              |     |

| Fig 6.8: Measured curves and IV curves using LT1001                                                                                                |     |

| -                                                                                                                                                  |     |

| Fig 6.9: Measurement circuit reference point                                                                                                       |     |

| Fig 6.10: I-v curves and measured device current and voltage (L11300) Fig 6.11: Collector current and collector emitter voltage during measurement |     |

|                                                                                                                                                    | -   |

| vector control                                                                                                                                     |     |

|                                                                                                                                                    |     |

| Fig 6. 13 Differential structure function showing repeatability of this process.                                                                   |     |

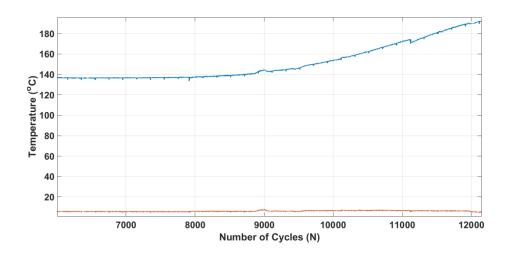

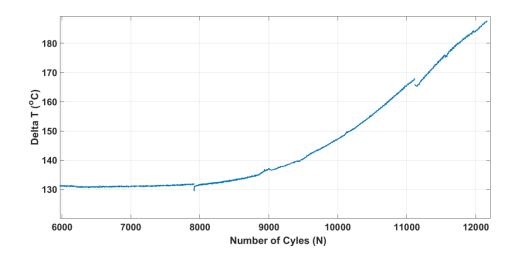

| Fig 6.14: Minimum junction temperature (orange) & maximum junction temp                                                                            |     |

| (blue)                                                                                                                                             |     |

|                                                                                                                                                    | •   |

| Fig 6.16: Differential structure function (a) before cycling with the same mod                                                                     |     |

| including a film between baseplate & heat-sink (b) comparing initial measure                                                                       |     |

| with no film to measurement after cycling                                                                                                          |     |

| Fig 6. 17: (a) Scanning acoustic microscope at time 0 (b) after 10000 cycles                                                                       |     |

| 116 o. 17. (a) beatining acoustic interoscope at time o (b) after 10000 cycles                                                                     | 114 |

|                                                                                                                                                    |     |

| Fig 7.1: Current and Voltage (collector-emitter) of DUT                                                                                            | 118 |

| Fig 7.2: Single phase ANPC inverter                                           | 118 |

|-------------------------------------------------------------------------------|-----|

| Fig 7.3: Switching Sequence and output voltage of a single phase of ANPC [98] | 119 |

| Fig 7.4: Simulation output current ANPC inverter during maintenance routine   | 120 |

| Fig 7.5: Simulation of current through DUT during maintenance routine         | 120 |

#### **List of Tables**

| Table 2.1 Comparison of electrical and thermal quantities            | 12  |

|----------------------------------------------------------------------|-----|

| Table 2.2: Properties of materials used in conventional power module | 14  |

| Table 2.3: IEC standards limits                                      | 34  |

| Table 4.1: Simulation Parameters                                     | 76  |

|                                                                      |     |

| Table 5. 1: List of equipment                                        | 84  |

| Table 5.2: Definition of switching states                            | 88  |

| Table 5.3 Switching states and space vectors                         | 88  |

| Table 5.4: Motor parameters                                          | 92  |

|                                                                      |     |

| Table 6.1: Set-up parameters                                         | 104 |

# **Chapter 1: Introduction**

#### 1.1 Motivation

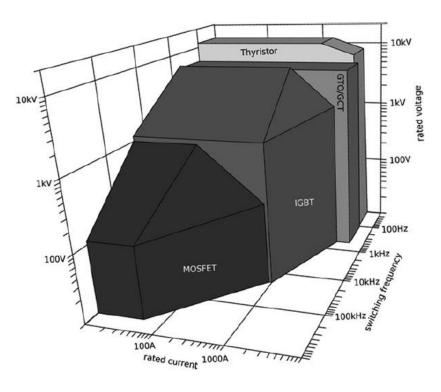

Power semiconductors are the basic building blocks of electrical power conversion applications and are central to a number of key societal infrastructures. Fig 1.1 gives an overview of the various silicon based semiconductor devices used for a wide range of power levels and switching frequencies[1]. Most of these applications are integral to our daily lives. In fact, according to [2], electric motors and the systems they drive are the single largest electrical end-use, consuming more than twice as much as lighting, the next largest end-use. It is estimated that electric motor driven systems account for between 43% and 46% of all global electricity consumption[2]. Over 90 % of this is represented by induction motors. About 25-30% of induction motor drives switched by power converters semiconductors[3]. The number of switched power converters is growing in motor drive applications, automotive, renewable and other applications.

Fig 1.1: Power semiconductor devices and applications (reprinted from[1])

The drive for ever increasing power density in power electronics has led to tougher requirement of reliability and health management/monitoring as devices are exposed to more and more stressful operational conditions in harsher environment. Power converters that use insulated gate bipolar transistors (IGBT) modules are well established in automotive, rail-traction, aerospace, renewable energy and several other applications where the combination of environmental and load-derived thermal cycling can result in large and unpredictable fluctuations in operational temperature [4].

During operation the semiconductor device induces a temperature field inside the IGBT module, which evolves depending on the mission profile. The power module experiences several local thermal cycles defined by the train acceleration and braking processes [5]. In grid connected photo-voltaic (PV) and wind applications, the temperature variation is also dependent on the operating conditions and the unpredictable variation in the wind speed [6].

For the sake of clarity in the previous and subsequent sections, some relevant definitions will be introduced:

- Mission profile- is defined as power processed over time of intended operation.

- Reliability- is defined as the ability of an item to perform required function under stated conditions for a certain period of time, which is often measured by probability of failure (chances that the item will fail) and frequency of failure (the number of times the item fails) [7]

- Availability- is defined as the probability to which an item will function as required when needed during the period of a mission.

Availability is a function of both reliability and maintainability and is relevant to mainly repairable systems.

- Stress- is defined as the result of an applied force which causes a material to deform.

#### 1.1.1 Power Module

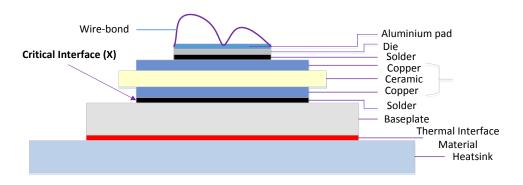

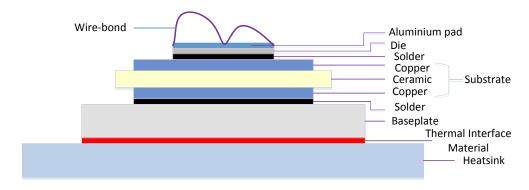

A typical semiconductor power module is made up of different layers and several materials as illustrated in Fig 1.2. This is designed to provide

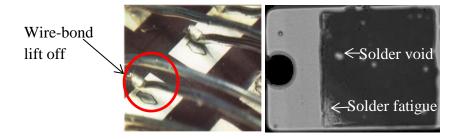

mechanical stability, electrical insulation and thermal conductivity [8]. The coefficient of thermal expansion (CTE) indicates the change of a component's size with a change in temperature. Specifically, it measures the fractional change in size per degree change in temperature at a constant pressure. As the temperatures of components inside the power module increases and decreases, the different materials expand and contract at different rates; this induces mechanical stress in layers between the different materials. A major reason for failures in IGBT modules is mismatched CTE of the various layers of materials used in their construction. The main failure mechanisms are wire-bond cracking, wire-bond lift off, solder joint fatigue, solder voids, aluminium reconstruction [9]. Fig 1.3 shows some of the main failure mechanisms, wire-bond lift off, solder fatigue and solder voids.

As a result of improvements made in wire bond reliability, it was shown in [10, 11] that solder fatigue of the substrate-to-base interface rather than wire bond lift-off is the limiting reliability factor. It has also been discussed in [8] that the substrate-baseplate location (X) features the highest mismatch in the CTE and the maximum temperature swing. For this reason, the focus is on the substrate-baseplate solder as a region of failure in the power module.

Fig 1.2: Illustration of conventional power module cross section

Fig 1.3: (Left) Wire-bond lift off (right) solder fatigue and solder voids[12]

The failure mechanisms need to be detected in order to prevent abrupt destruction of the devices and subsequent risk of system inoperability. The reliability and the availability are improved by monitoring the failure mechanism. The smaller the time it takes for a system to be repaired/maintained the higher its availability. Therefore to increase availability and detect the impending failure, pre-cursors of failure need to be defined. Some parameters related to the device or device structure are related to the failure mechanisms. The thermal response function (cooling or heating curve) as a result of power step excitation contains information of the device structure. Hence by measuring the thermal response function a change in the structure can be detected. The junction temperature then is an important variable to monitor degradation; the power modules are enclosed and provide no opportunity for a direct measurement of the junction temperature.

#### 1.2 Aims and Objectives of the Work

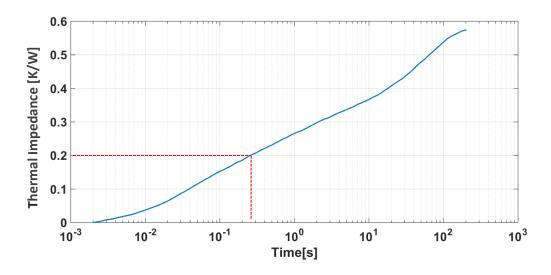

With the prevalence of induction motor drives in power electronics applications and the need for health monitoring for reliability as motivation; this thesis presents the development and proof-of-concept demonstration of an on-board methodology for monitoring the health of power converter modules in induction motor drives. The aim of this thesis is to present a system that can measure the cooling profile of a power module (3 phase 2-level inverter) to derive the structure function during idle times of the equipment. The structure function, presented in detail in chapter 3 is a powerful tool for tracking the extent and location of degradation in power modules. The stated aim is carried out by combining the power device heating technique and the measurement without additional power components [13], except for the measurement circuit

which consists of only analog components and can be integrated into the gate drive board. Single chip, non-punch through (NPT) power modules have been used in this work. The specifics of other technologies such as trench devices have not been considered. The concept in this work however, can be applied to multichip modules and other IGBT technologies.

In order to implement and validate the on-board health monitoring methodology the objectives are as follows:

- I. Identifying the parameter to be used to measure degradation to meet the aims of the project.

- II. Extracting thermal transients, thermal impedance curves, time-constants and structure function

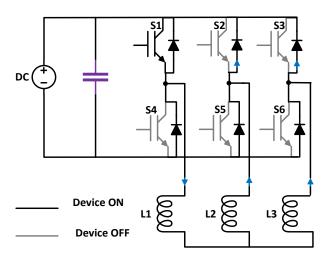

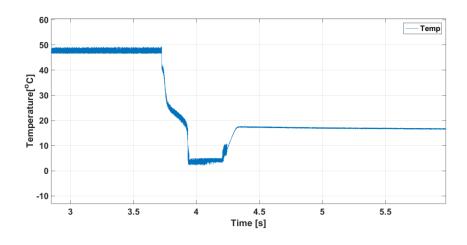

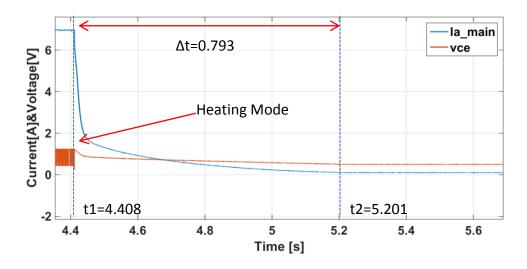

- III. Implementing a control strategy to heat up devices on a 3 phase 2-level inverter without rotating the motor or changing the connections or adding components

- IV. Designing a measurement circuit that will give an accurate temperature measurement without interfering with the converter operation

- V. Presenting a system prototype to validate on-board health monitoring

#### 1.2.1 Background

Similar research in online health monitoring of power devices/modules have been carried out in the past. Prognostic real-time systems in [14, 15] present a method that uses compact thermal models to predict temperatures of inaccessible locations of a power module; the information then obtained is combined with data about the reliability analysis to predict failure mechanisms. Although those methods might be able to predict failure, they give an estimate, hence doesn't provide the actual variation in the quantity of the failure mechanism. Also, as time elapses the aging of the power modules will affect the integrity of the thermal model. Adaptive models for real-time monitoring have been presented in [16-20], which compare physical measurements with a model estimate to accurately track the junction temperature of the device under consideration. The limitations of [16-18] are

that they use the collector emitter voltage, which is noisy and intermittent due to the non-linearity of the I-V characteristic of the IGBT, hence this method is dependent on the operating region. [19] requires extending the turn-on time by making modifications to the gate drive in order to measure the temperature online. In [20] temperature sensors need to be embedded in the baseplate to detect the change in temperature distribution, this method is affected by the positioning of the sensors.

As opposed to the real-time monitoring solutions, which take measurements of the TSEP of the device during operation of the inverter, in the methodology proposed here, measurements are taken when the system is not operation(during maintenance routines). The in-situ method in [21-23] to which this work mainly makes reference to, works by injecting external currents into the power module during idle times. The high current is injected externally to heat the devices. The methods presented in these papers show the ability to successfully measure degradation due to wire-bond lift off and solder fatigue by measuring the voltage at high currents (wire-bonds) and the heating curve (solder fatigue). However, in [21-23] a set of relays need to be inserted to select which device undergoes test, somewhat limiting of the applicability of the solution in some on-board applications. The method in [24] presents a similar control concept of a quasi-real-time prognostic method in simulation, however in practice this will also be subject to noisy and intermittent collector emitter voltage which makes it hard to implement.

The work presented in this thesis provides a system that uses the structure function [25] to measure degradation on-board without making changes to the connections, making use of additional components or dismounting it; it is also able to point out if and where degradation occurred in the structure of the device.

#### 1.3 Thesis outline

In Chapter 2, the power module structure and its reliability are discussed. Chapter 3 entails obtaining the thermal impedance and the theory behind the structure function and how the structure function can be extracted. In Chapter

4, the heating scheme and the measurement circuit design methodologies are introduced. In Chapter 5 the experimental implementation of the heating scheme and measurement system are elaborated. The challenges encountered are presented along with the results validating the on-board measurement methodology in Chapter 6. Conclusions are presented in Chapter 7.

# Chapter 2: Power Modules Structure & Reliability

#### 2.1 Introduction

This chapter presents the theory of heat conduction in the power module. This provides the opportunity of introducing a simplified method of analysing the heat flow path and how the heat flow path is relevant to this work. The structure of power modules and the materials used in a conventional power module will be presented. It will elaborate the benefits of the materials in the power module and how the properties of these materials are susceptible to the failure mechanisms. This chapter will also discuss the failure mechanisms and how they develop in modules. Additionally in this chapter the variables used to determine and evaluate failure mechanisms are elaborated, identified and their functions are discussed. A suitable variable will be chosen for this work and the reason behind this choice will be presented.

#### 2.2 Heat Transfer in Power Devices

Conduction, convection and radiation are the three main mechanisms by means of which heat is transferred. When there is a temperature gradient existing in a solid, heat flows from the higher temperature region to the low temperature region. This process is known as conduction. In this mode, heat transfer is achieved through a complex sub microscopic mechanism in which atoms interact by elastic and inelastic collisions to propagate the energy from regions of higher to regions of lower temperature [26].

Conduction occurs in liquids and gases, but is not the dominant heat transportation mechanism. Convective currents set in motion bring about the transportation of heat in fluids. Hence, transportation of heat on both the microscopic and macroscopic scale. Convection is a more effective way of transporting heat than conduction which is limited to microscopic transport of energy.

The third means of transporting heat from one point to another is radiation. Heat transfer by radiation in solids occurs when the object is transparent or translucent. For the sake of analysis heat conduction and convection is solely considered in power semiconductors because other forms of heat transfer are negligible. Convection happens between the heat sink and its surroundings, and because convection is more effective way of transporting heat, the heat sink is considered to be a constant thermal termination for the heat path in most cases.

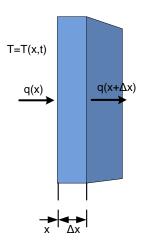

#### 2.2.1 Analysis (Conduction)

Power semiconductor devices have heat transfer in the form of heat conduction. The general equation that describes heat transfer in conduction can be written as [27]:

$$\rho c \frac{\partial T(x, y, z, t)}{\partial t} = \nabla (K \nabla T(x, y, z, t)) + H(x, y, z, t)$$

(2.1)

Where:

$\rho$  = material density

c= specific heat

*K*= *matrix of thermal conductivity coefficients*

*T*=*Temperature*

H=Heat Generation rate

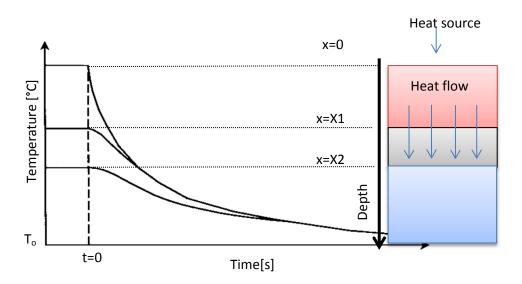

The heat conduction in power device packages can be analysed in a simpler way by considering a thermally isotropic material, where heat conduction in power semiconductor devices can be considered as one-dimensional if the following statements are true:

• Thermal conductivity of silicon is constant (λ). There are some exceptions, silicon has a nonlinear heat conductance at higher temperatures and radiation effects are at higher magnitudes. These effects are not very pronounced in the temperature range used when characterizing the packages.

- Uniform power density and heat generation should occur in a volume with lateral dimensions much bigger than the vertical dimension of the chip, so negligible temperature gradient exists in adjacent cells [27].

- Heat is mainly extracted from the baseplate/heatsink[28]

So for a thermally isotropic material with a constant  $\lambda$  equation (2.1) can be written as:

$$\rho c \frac{\partial T(x, y, z, t)}{\partial t} = \lambda \nabla^2 T(x, y, z, t) + H(x, y, z, t)$$

(2.2)

For one dimensional heat conduction and uniform power density equation (2.2) can be written as:

$$\rho c \frac{\partial T}{\partial t} = \lambda \frac{\partial^2 T}{\partial x^2} + H \tag{2.3}$$

The analytic solution for conduction in a one-dimensional system is presented in Appendix 1.

#### 2.2.1.1 Thermal Resistance/Impedance

Provided there is a temperature gradient in a solid as stated earlier, heat will flow from a high temperature region to a lower temperature. The rate at which the heat is transferred by conduction,  $q_k$  is proportional to the product of the temperature gradient dT/dx and area A through which heat is transferred[26]:

$$q_k \propto A \frac{dT}{dx} \tag{2.4}$$

In the above relation T(x) is the temperature at a given location and x is the distance in the direction of the heat flow. Heat flow is also affected by a constant known as thermal conductivity  $\lambda$ , which is a material property of the medium. The above equation can then be written for a homogeneous as

$$q_k = -\lambda A \frac{dT}{dx} \tag{2.5}$$

The negative sign indicates the slope of the temperature with respect to the distance x. As the rule is that heat will move from the higher temperature to lower as the distance increases, the sign will be negative.

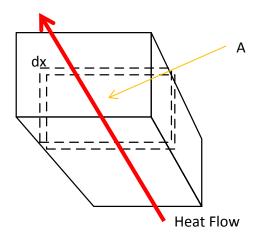

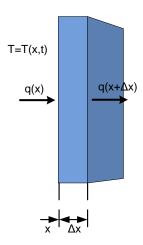

The heat conduction process can be modelled by a circuit diagram, which consists of resistive and capacitive elements R/C elements only. The similarities between electrical and thermal systems are shown in Table 2.1. The thermal resistance can be elaborated by considering (2.5), and the volume presented in Fig 2.1.

Fig 2.1: Illustration of one dimensional heat flow

The starting point x, can be considered as the origin (x=0) in this case and the temperature at the origin is T1 while the temperature at  $\Delta x$  is T2. Equation (2.5) can then be written as

$$\frac{q_k}{A} \int_0^{\Delta x} dx = -\lambda \int_{T_1}^{T_2} dT \tag{2.6}$$

$$\frac{q_k}{A} \left[ x \right]_0^{\Delta x} = -\lambda \left[ T \right]_{T1}^{T2} \tag{2.7}$$

$$q_k = \frac{A\lambda}{\Delta x} (T1 - T2) = \frac{\Delta T}{\frac{\Delta x}{A\lambda}}$$

(2.8)

Table 2.1 Correspondence of electrical and thermal quantities

| Thermal quantities |                  | Unit | Electric<br>quantities |               | unit |

|--------------------|------------------|------|------------------------|---------------|------|

| Т                  | Temperature      | K, C | V                      | Voltage       | V    |

| $q_k$              | Heat flow        | W    | I                      | Current       | A    |

| Rth                | Thermal          | K/W  | R                      | Electric      | ohms |

|                    | resistance       |      |                        | resistance    |      |

| Cth                | Thermal capacity | J/K  | С                      | Capacity      | F    |

| $	au_{th}$         | Time constant    | S    | τ                      | Time constant | S    |

| Zth                | Thermal          | K/W  | Z                      | Impedance     | ohms |

|                    | impedance        |      |                        |               |      |

In the equation above  $\Delta T$ , the temperature difference between two points causes the heat flow. This is the same in electrical circuits where potential difference leads to a current flow. For this reason, current and the heat flow can be considered to be analogous. The electrical equivalent to (2.8) is Ohms law

$$I = \frac{\Delta V}{R} \tag{2.9}$$

It can be observed that  $\Delta x/A\lambda$  is equivalent to the thermal resistance, also inversely proportional to the heat flow, in a similar way the electrical current is inversely proportional to the electrical resistance. This analogy is a convenient tool, especially for visualizing complex situations.

The thermal resistance can be used to visualize situations only during equilibrium. For most applications the use of thermal resistance is sufficient, but for this work, as the aim is to ascertain any changes in the structural integrity, the thermal impedance is needed.

The thermal impedance ( $Z_{th}$ ) is equivalent to RC-network of certain order which represents the physical layers of the system with individual thermal resistances and capacitances; this is explained in more detail in the next

chapter. Generally the transfer function of the thermal system for an arbitrary power profile as suggested in [29, 30], is:

$$\Delta T(t) = \int_{-\infty}^{\infty} Z_{th}(\tau) * \Delta P(t-\tau) d\tau$$

(2. 10)

Where

$$Z_{th}(t) = \frac{dZ_{th}}{dt}(t) \tag{2.11}$$

For constant power dissipation, the thermal impedance in (2.10) can be reduced to

$$Z_{th}(t) = \frac{\Delta T(t)}{\Delta P} \tag{2.12}$$

#### 2.3 Structure of Power Modules

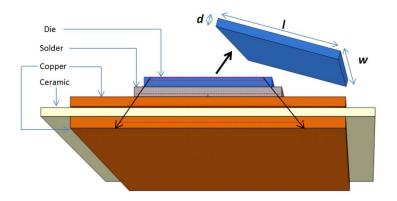

The conventional power module is usually made up of eight layers plus the wire bond as seen in Fig 2.2. The colors are indicative of the material used, as surmarissed in Table 2.2, which also indicates typical thickness and the coefficients of thermal expansion. The coefficient of thermal expansion indicates change of a component's size with a change in temperature. Specifically, it measures the fractional change in size per degree change in temperature at a constant pressure. The purpose of the various layers will be outlined in the following subsections.

Fig 2.2: Cross-section representation of a conventional power module

Table 2.2: Properties of materials used in conventional power module [8]

| No | Material                                                                              | Thickness (μm) | CTE ppm/°C |

|----|---------------------------------------------------------------------------------------|----------------|------------|

| 1  | Aluminium (Al)                                                                        | 4-5            | ~22        |

| 2  | Silicon (Si)-Chip                                                                     | 70-500         | ~3         |

| 3  | Solder                                                                                | 100            | -          |

| 4  | Copper (Cu)-<br>Substrate                                                             | 280            | ~17        |

| 5  | Al <sub>2</sub> O <sub>3</sub> or AlN or<br>Si <sub>3</sub> N <sub>4</sub> -Substrate | 1000           | ~7/4/3.3   |

| 6  | Copper (Cu)-<br>Substrate                                                             | 280            | ~17        |

| 7  | Solder                                                                                | 180            | -          |

| 8  | Cu or AlSiC-<br>Baseplate                                                             | 4000           | ~17/8      |

#### 2.3.1 Die

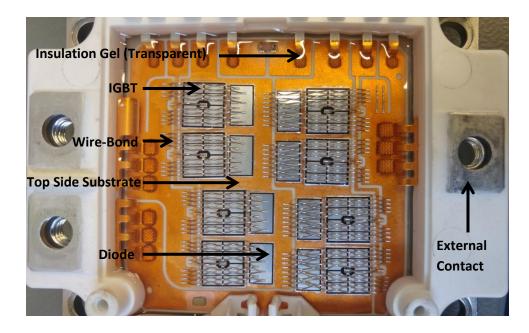

The chip is a silicon semi-conductor device, although other semiconductors have been also introduced (SiC, GaN, AsGa)[12]. The die is usually connected to other chips, gate terminal and power teminal by wire bonds or bump interconnection technology. The wire bond is made up of either aluminium or copper. The wire bonds are attached to the silicon chip via ultra-sound bonding[8]. A conventional commercial power module is presented in Fig 2.3.

Fig 2.3: Conventional half bridge module with devices connected in parallel

Fig 2.3 shows that wire-bonds connect IGBTs and diodes both directly and via the substrate. Both the IGBT and the diodes have two sides to which connection must be made. For the IGBT the top side consists of the gate and the emitter, while the bottom side is the collector. For the diode, the bottom is the cathode and the top side is the anode.

#### 2.3.2 Solder

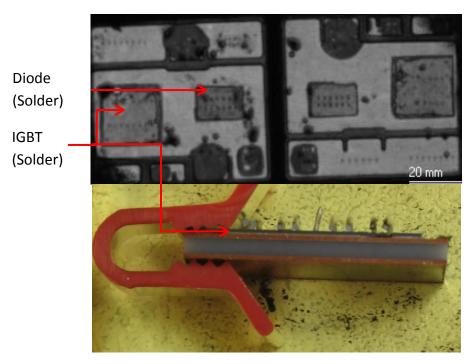

The solder in the power module structure provides a mechanical support for the die to be attached on the substrate, electrical contact for the collector and the cathode and also a thermal path to cool down the device. The solder used is usually an alloy of tin, silver, lead, copper or nickel. In most applications the tin-lead alloy is common. Recently other alloys have been introduced that exclude lead due to its harmful effects and worldwide health and safety regulations. Therefore, tin-silver (Sn-3.5Ag) is a preferable solder in a flux-less reflow soldering process [31, 32]. The acoustic scan of the solder layer of the IGBT and the diode and an image of a cross section showing solder are presented in Fig 2. 4.

Fig 2.4: Scanning acoustic microscope image of IGBT and diode solder & cross-section showing solder layer

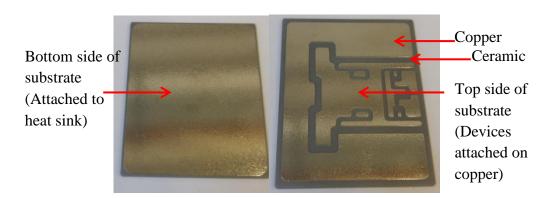

#### 2.3.3 Substrate

The substrate is designed to be electrically insulating and thermally conducting. It consists of two copper layers on its sides (top and bottom) with ceramic inbetween. The copper on the top provides electrical connection between the various chips as mentioned. Typical materials used for substrate manufacturing are Al<sub>2</sub>O<sub>3</sub>, AlN, Si<sub>3</sub>N<sub>4</sub>, BeO. These substrates are coated with copper layer by one of the following methods: copper thick film technology using screen printing, copper on ceramic by electro-less plating, direct copper bonding through eutectic oxide bonding, and active metal braising.

Fig 2.5: Bottom and top side of ceramic substrate

Fig 2.5 shows the photographs of bottom and top side of a DBC substrate. In such a structure the copper layer provides the ability to carry high current and the ceramic tile provides high voltage insulation[33]. AlN has a higher thermal conductivity than  $Si_3N_4$ , resulting in better heat removal from the device attached to it. However,  $Si_3N_4$  has the advantage when considering the thermal expansion and fracture toughness. This is because the CTE of  $Si_3N_4$  is closer to the silicon as it can be seen from Table 2.2 and it has high resistance to brittle fracture during thermal cycle.

#### 2.3.4 Base Plate

The baseplate is the external interface to the heatsink. It is situated between the solder underneath the substrate and the thermal interface material/heatsink. The base plate is based on nickel plated copper slabs. Other materials are metal matrix composites such as copper matrix composites reinforced with diamond, aluminium matrix reinforced with SiC or carbon-reinforced composites. The baseplate provides an effective thermal path that links the substrate to the heatsink or cold plate by spreading the heat. An image of a typical baseplate is presented in Fig 2.6.

Fig 2.6: Baseplate of an IGBT module & plastic housing

#### 2.3.5 Silicone Gel

The devices are covered by an encapsulating silicone gel as shown in Fig 2.3. Silicone gel and a combination of hard epoxy are used to produce this material. The power devices are coated by silicone gel for environmental and mechanical protection. An additional plastic housing shown in Fig 2.6 is used to contain the gel.

#### 2.3.6 Thermal Grease

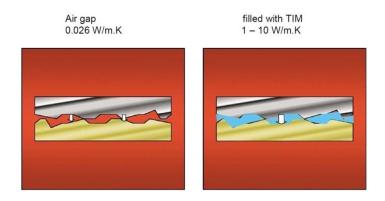

A thermal grease is used to improve the thermal conduction from the baseplate to the heatsink. The thermal grease is used to fill in the air gaps between the baseplate and the hatsink as shown in Fig 2.7. Air has very low thermal conductivity, so thermal grease is used. Heat transfer occurs at a slower rate with the airgaps than with the thermal grease filled gaps.

Fig 2.7: Illustration of thermal grease used to fill air gaps (reprinted from [34])

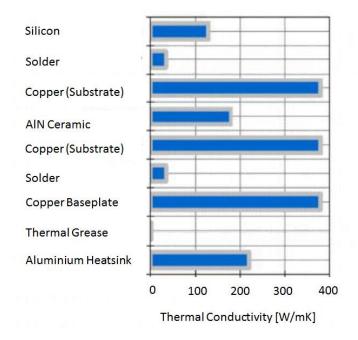

Fig 2.8: Thermal conductivity of materials used in a module compared to thermal grease (reprinted from[34])

It is important to note that, although the thermal grease has a higher heat conductivity than the air gaps, it has a relatively low conductivity compared to the other components used in the power module structure as it can be seen in Fig 2.8. This means that although the thermal grease is needed to fill in the air gaps, an excessive amount will actually increase the thermal resistance. A solution to this is proposed by using an inhomogeneous stencil pattern (Honeycomb shape) to minimise the air being trapped under the module after mounting. A range of thermal foils are also used as thermal interface materials example of these are: thermosilicone foil, thermal wax coated Aluminium foil and carbon foil. Knowledge of the application can aid in choosing the best thermal interface material. The potential for the use of nano-technology has been discussed in [34] to improve thermal conductivity.

#### 2.4 Failure mechanisms

A major reason for failures in IGBT modules is mismatched coefficients of thermal expansion (CTE) of the layers an IGBT consists of. This mismatch causes strains to both the bond wires and the soldering of the IGBT modules thus causing the IGBT modules to fail over time [8, 35]. These failure mechanisms wire-bond cracking, wire-bond lift off, solder joint fatigue, solder voids, aluminzation e.t.c are presented below[9].

#### 2.4.1 Wire-bond Fatigue

Power modules with multichips for high power applications usually include up to 800 wedge bonds. Most of the wire-bonds are located on the active areas of the chips. This means that the wire-bonds experience the full temperature swing due to power dissipation in the power devices and the ohmic self-heating of the wires.

Failure of wire-bonds relate to the stress between the wire bond and point of contact by repeated expansion and contraction. The failure of a single or of multiple bond wires causes a change either in the contact resistance or in the internal distribution of the current, such that it can be traced by monitoring  $V_{ce}$  [36]. The loss of a single wire-bond leads to a cyclic process that leads to the quick destruction of the power module. The loss of wire-bonds means that the remaining wire-bonds need to carry an increased amount of current, which

leads to an increase in the ohmic self-heating of the wire-bonds. Wire-bond fatigue can occur in the form of wire-bond lift off and wire-bond cracking.

#### 2.4.1.1 Wire-bond Lift Off

Wire-bond lift off usually occurs on the bonds present on the chip region. This is due to the fact that the connections made on the copper substrate experience a lower temperature swing than the connecting points on the chip. Moreover the CTE disparity between copper and the aluminium wire-bonds is less than that between aluminium and silicon.

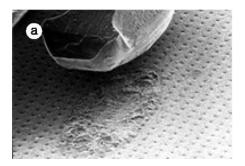

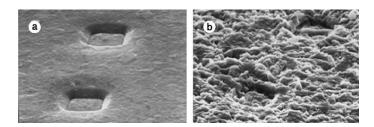

There is experimental evidence that the crack leading to failure is initiated at the tail of the wire-bond and propagates within the material until the wire-bond completely lifts off [8]. Fig 2.9 shows a scanning electron microscope (SEM) image of a single wire-bond lift off.

Fig 2.9: SEM image wire-bond lift off (reprinted from [8])

There are two main methods used in order to dampen the progress of this failure mechanism. Some power modules have a strain buffer on the chip. This is one of the countermeasures employed using a molybdenum plate soldered onto each chip as a strain buffer; the wires are then bonded on the molybdenum plate [37]. The aim of this buffer is to eliminate the thermoelectric stress that occurs by distributing the CTE mismatch across the molybdenum layer. The other solution is covering the wire-bonds with a coating layer. In [8], a comparison between non-coated wire-bonds and coated wire-bonds was carried out. The results indicate that the coated wire-bonds effectively slow down the failure mechanism by a considerable number of cycles.

# 2.4.1.2 Wire-bond Heel Cracking

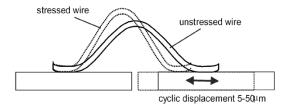

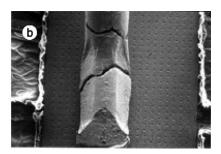

Wire-bond cracking is caused by cyclical lateral bond area displacement as can be seen in Fig 2.10. This can be induced by sinusoidal excitation with 10-20Hz [38]. It is usually experienced when the ultrasonic bonding process is not optimized. This failure mechanism is also due to the thermo-mechanical stress. The wire is exposed to thermal stress as it expands and contracts undergoing fatigue. An SEM image of the wire-bond cracking is shown in Fig 2.11.

Fig 2.10: Wire-bond subjected to thermo-mechanical stress (reprinted from [38])

Fig 2.11: SEM image of wire-bond cracking (reprinted from [8])

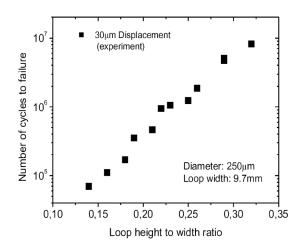

It is important to note that both wire-bond lift-off and wire-bond cracking can occur simultaneously. [38] suggest that the loop height to width ratio has a certain degree of proportionality to the number of cycles to failure as presented in Fig 2.12.

Fig 2.12: Relationship between loop height to width ratio and number of cycles to failure (reprinted from [38])

# 2.4.2 Solder Fatigue and Solder Voids

As a result of improvements made in reliability, it was found that for the module used in [10], solder fatigue of the substrate-to-base interface is one of the limiting reliability factor for power cycling stress, if the duration of a cycle is chosen to be sufficiently large. It has been presented in [8] that in the substrate-baseplate location the worst mismatch in the CTEs, the maximum temperature swing combined with the largest lateral dimensions are present. Also this failure mechanism occurs in the solder layer between the device and the substrate. There are also process induced voids, which can interact with thermal flow and the crack initiation within the solder layer.

#### 2.4.2.1 Solder Voids

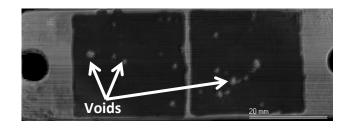

Solder voids increase the junction temperature of the devices which becomes a trigger for other failure mechanisms such as solder fatigue and wire bond fatigue. The heat flow in a power module is considered to be one dimensional; the large solder voids in the heat path makes the heat spread. This incident further inhibits the heat extraction performance. On the contrary, small voids have less impact on the thermal performance of the power module. Fig 2.13 shows a scanning acoustic microscope image (SAM) of the voids in the solder layer between the substrate and the baseplate. Caution is taken in advanced processes for producing the power modules to prevent the formation of voids.

Fig 2.13: SAM image of solder between substrate and baseplate indicating solder voids

## 2.4.2.2 Solder Fatigue

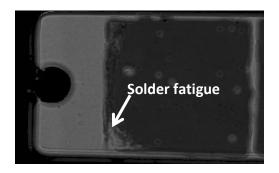

This failure mechanism develops when the solder between the substrate and the baseplate or the solder between the device and the substrate cracks. This mechanism usually propagates from the edges of the solder where shear stress (defined as result of force vector component parallel to the cross section) reaches its maximum and moves towards the centre of the solder until the solder layer is compromised. An acoustic scan of solder fatigue can be observed in Fig 2. 14.

Fig 2.14: Acoustic scan showing solder fatigue

A comparison between two type of baseplates was made in [39]; copper and AlSiC baseplates using the same substrate material (AlN) were compared. The two modules were subjected to thermal cycling; the same temperature swing of 50°C was applied to both samples. From Fig 2.15 it can be observed that the solder on the copper baseplate (module 1) experiences solder fatigue as opposed to the AlSiC (module 2) baseplate. The image of the solder on the copper baseplate was taken after 16,000 cycles while the image of the solder on the AlSiC was taken after 90,000 cycles. This means that under the same

conditions the solder on the copper baseplate degrades much faster than that of the AlSiC baseplate.

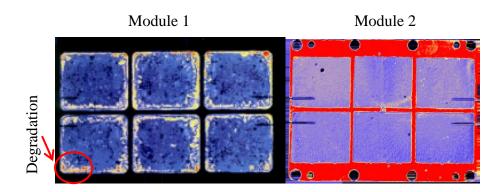

Fig 2.15: SAM images of cycled solder layer of modules using copper(left) and AlSiC(right) baseplates (reprinted from [39])

#### 2.4.3 Aluminium Reconstruction

Aluminium reconstruction occurs due to the large thermo-mechanical mismatch between aluminium and silicon chip and due to the stiffness of the silicon substrate, the stresses, which arise within the aluminium thin film during pulsed operation of the device can be far beyond the elastic limit [40]. The elastic limit is defined as the limit to which a solid may be stretched without permanent alteration of form or size. Surface reconstruction sometimes occurs as a secondary mechanism in conjunction with wire bond lift off. In Fig 2.16 the image on the left side shows the metallization layer before cycling and the image on the right shows the metallization layer after 3.2 million cycles with a temperature swing of 40°C [8].

Fig 2.16: Metallization before power cycling (left) and after (right) (reprinted from [8])

#### 2.4.4 Other Failure Mechanisms

Other failure mechanisms such as cracking, corrosion of the interconnection, latch up and cosmic rays can also affect the power modules. These failure mechanisms are not as common as the aforementioned. Failure mechanisms such as corrosion and cosmic rays depend on the application. For example, corrosion is a considerable failure mechanism in offshore wind turbines or marine applications due to humidity.

#### 2.4.5 Effects of Failure Mechanisms

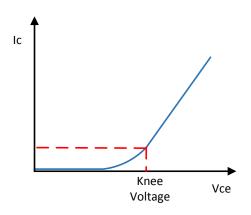

Failure mechanisms are important because they have an effect on the electrical and thermal properties of the module. Increase in electric resistance due to wire bond lift-off as mentioned earlier means that less wire bonds are allowed to carry the same amount of current. An increase in resistance means that there is an increase in Vce for IGBT and forward voltage for diodes. An increase in thermal resistance also occurs due to solder fatigue and solder voids due to a distorted thermal path or thermal conducting area. As these problems develop with time they eventually lead to the destruction of the device. Therefore an effective monitoring of the major failure mechanisms is required.

# 2. 5 Monitoring Degradation

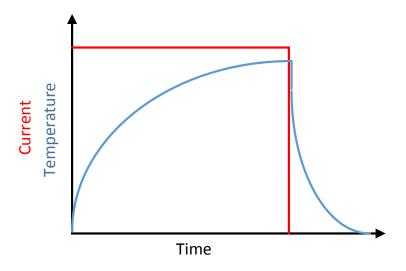

Failures need to be detected in order to prevent abrupt destruction of the devices. Therefore to detect the impending failure, precursors of failure need to be defined. These precursors are temperature, collector emitter voltage (V<sub>ce</sub>), threshold gate voltage  $(V_{ge(th)}),$ gate resistance  $(R_G)$ , resistance/impedance, turn off time and voltage across the parasitic inductance between the power emitter and gate emitter (di/dt). The collector emitter voltage, threshold voltage, gate resistance, V<sub>ge</sub> turn off time and di/dt all have a dependence on temperature and are therefore called temperature sensitive electric parameters (TSEP). There are several TSEPs in addition to the ones mentioned above[41]. TSEPs can either be static (measured at steady state) or dynamic (measured at transients). The thermal resistance and impedance is obtained from the temperature.

The temperature then is an important parameter to monitor degradation; the power modules are enclosed and provide no opportunity for a direct measurement of the junction temperature. The state of the art methods to obtain the junction temperature include the integration of NTC resistors, on – chip diodes and the use of TSEP. The NTC resistors are placed on the substrate and reveal the baseplate temperature with a time constant of a few seconds [42]. The on-chip diodes are integrated within the IGBT and return the local temperature with a time constant of about 1ms [43]. Both types require special consideration during design and manufacturing process to ensure electrical isolation from HV traces on the substrate and require additional external pins and separate copper traces, which might increase manufacturing cost and give rise to additional reliability issues [16]. In the absence of direct measurement, the TSEP is a feasible way of measuring the junction temperature.

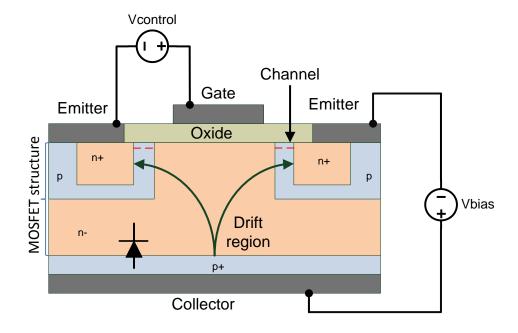

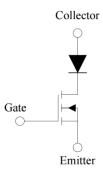

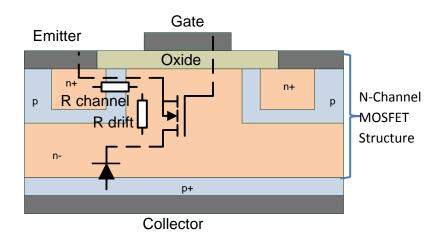

# 2.5.1 IGBT Structure and Operation

In order to gain an understanding of the TSEPs used, the structure and the operation of the IGBT is presented. The IGBT structure is formed by using four (N–P–N–P) alternating semiconductor layers. The basic structure of an N-channel nonpunch-through (NPT) IGBT is presented in Fig 2.17. The nonpunch-through IGBT differs from the punch-through IGBT due to the inclusion of N-buffer layer in N-drift region in the case of PT IGBT. The punch through structure is optimized for DC circuit applications where no reverse bias is applied to the device because it operates exclusively in the first quadrant of the i– $\nu$  characteristics [44].

Fig 2.17: N-channel IGBT (NPT) cross-section

When a positive gate bias (V control) is applied, an inversion channel layer below the gate which connects the emitter to the drift region. When the collector is biased by positive Vbias, electrons flow from the emitter (n+) through the channel creating a connection between emitter and collector.

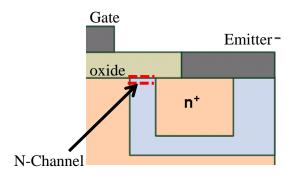

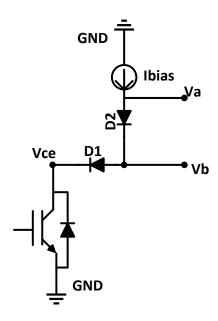

# 2.5.2 Threshold Gate Voltage as TSEP

The threshold voltage for silicon IGBT has a linear relationship with temperature which can be represented by (2.13).

$$V_{th1} = V_{th0} - k \left( T_{j1} - T_{j0} \right) \tag{2.13}$$

Where  $V_{th0}$  is the threshold voltage at room temperature  $(T_{j0})$  and  $V_{th1}$  the threshold voltage at temperature  $(T_{j1})$  in the range of operation. k is the constant of proportionality which is related to the device properties [45]. The threshold voltage is the gate voltage at which the inversion layer forms to produce a conduction path just below the gate oxide. This inversion channel is indicated by the red dotted lines in Fig 2.18. Measuring the threshold voltage is a very sensitive process because it involves switching of the gate control circuit. A basic circuit for the measurement of the threshold voltage can be seen in Fig 2.19. Due to the layout of the conventional power module, there are resistances and inductances related to the wire-bonds and terminals. This

means that if measurement is carried out at the terminals the voltage drop includes the voltage across wire bonds and module terminals. The temperature dependence of the bond wires at low current can be considered negligible [46].

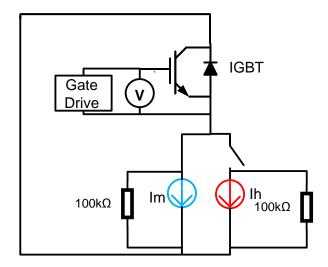

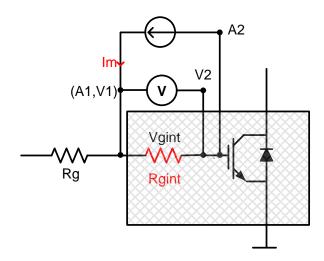

Fig 2.18: Inversion channel IGBT

Threshold voltage is measured after heating current  $I_h$  passes through the device; the measurement is carried out when the measurement current  $I_m$  flows through the DUT by measuring the gate voltage. This measurement system needs to be fast, which is one of the limitations in real operating conditions.

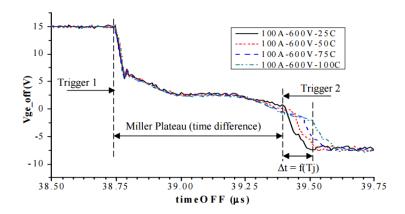

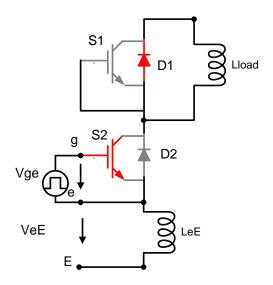

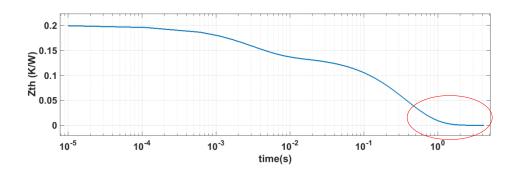

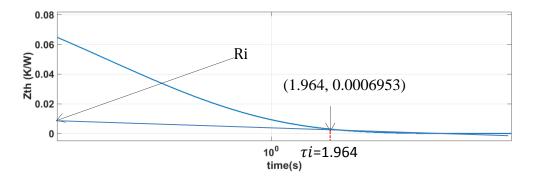

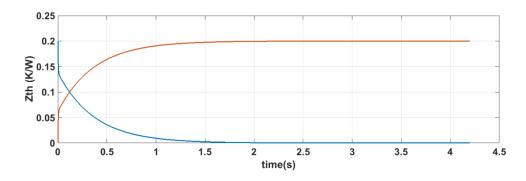

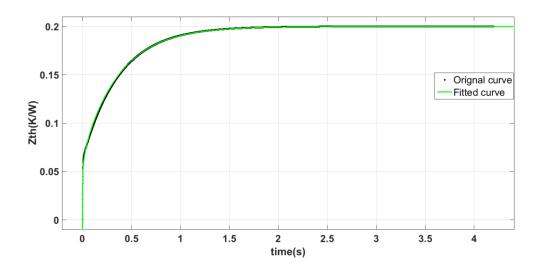

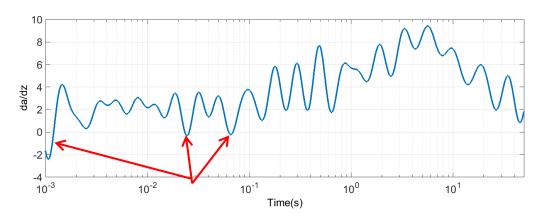

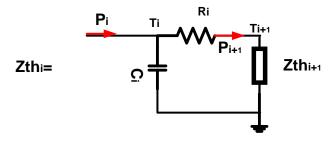

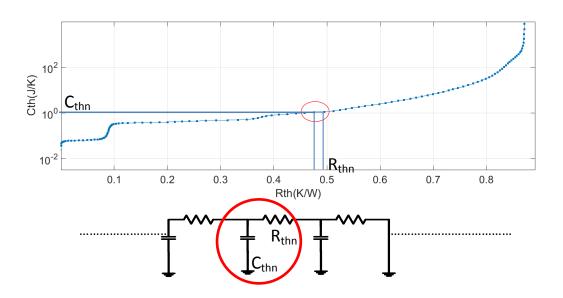

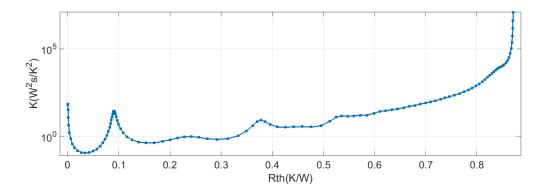

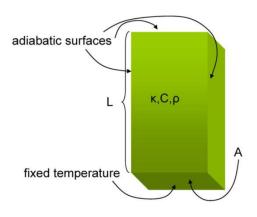

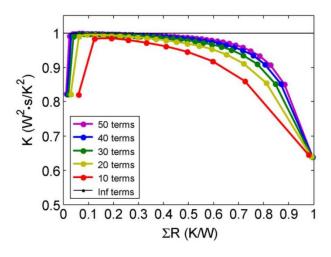

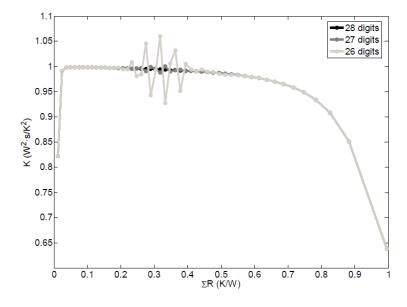

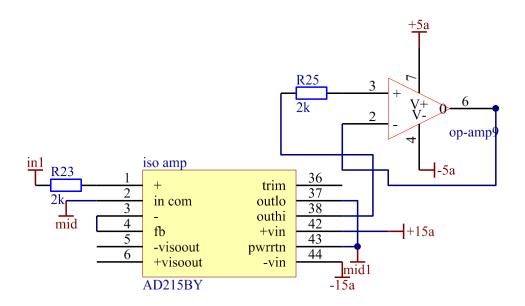

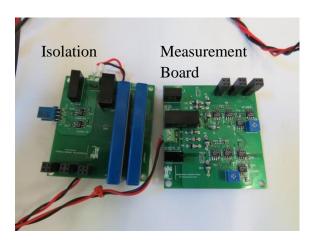

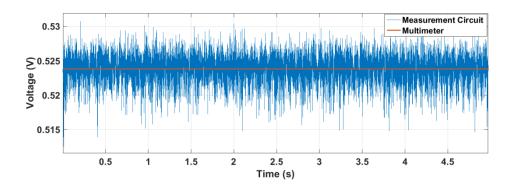

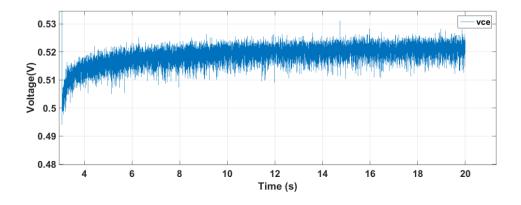

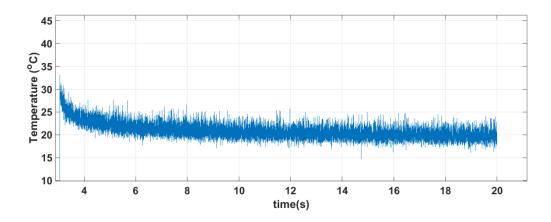

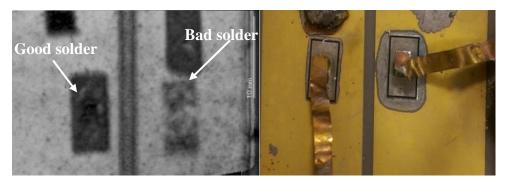

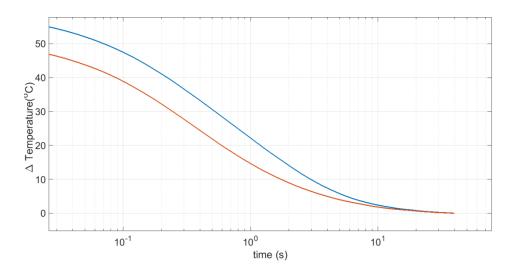

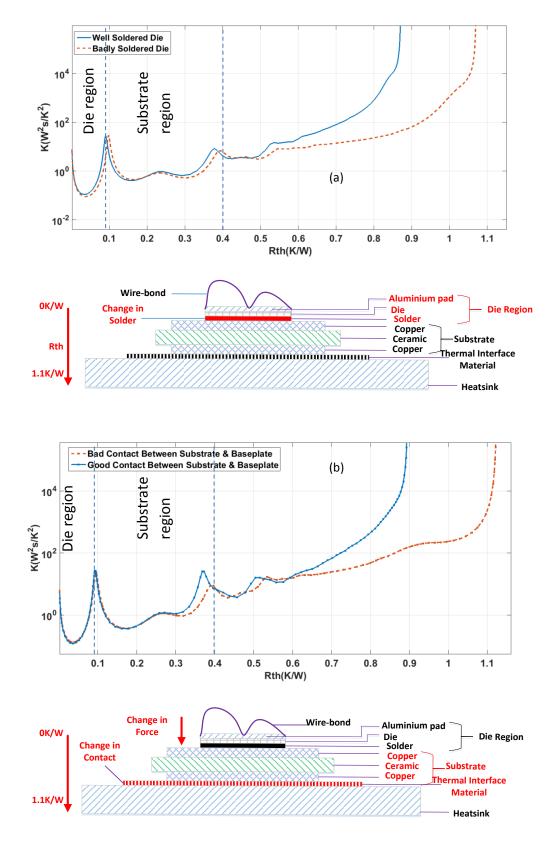

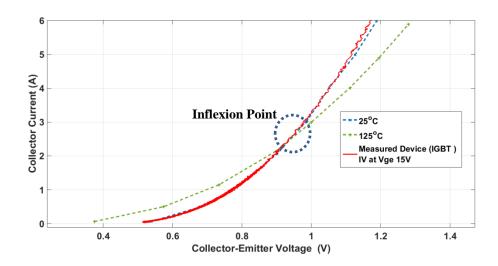

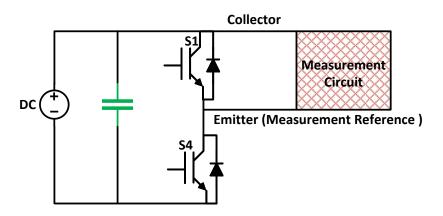

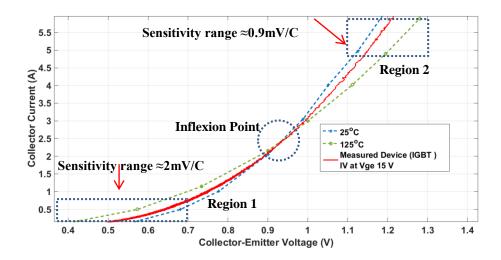

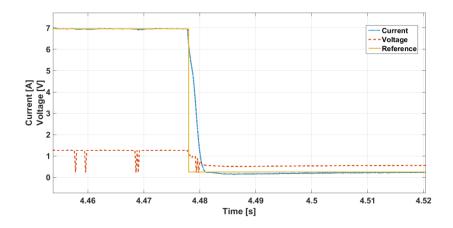

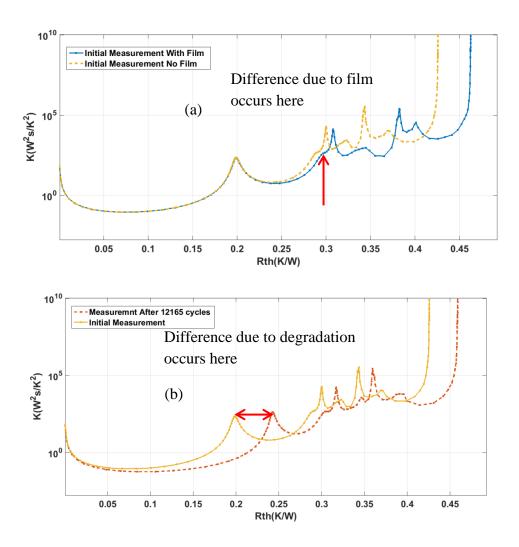

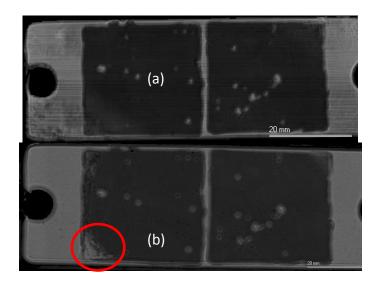

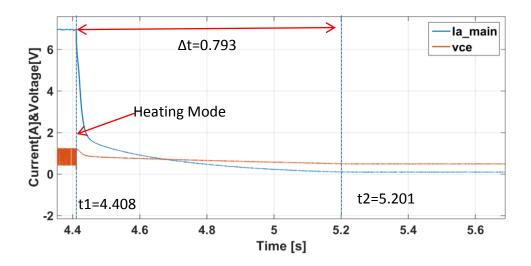

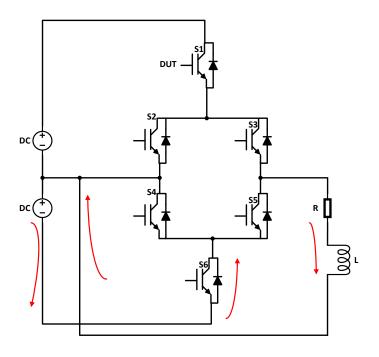

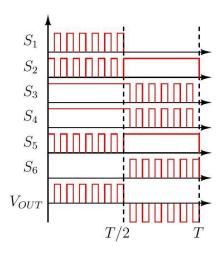

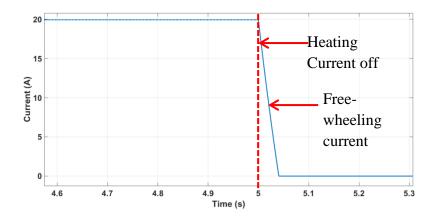

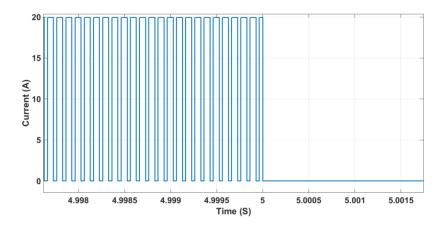

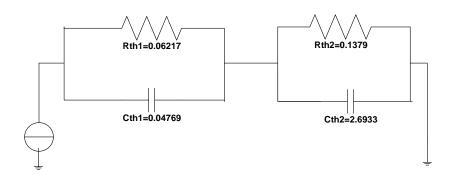

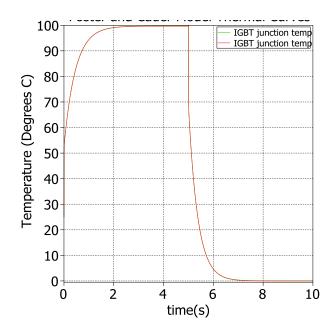

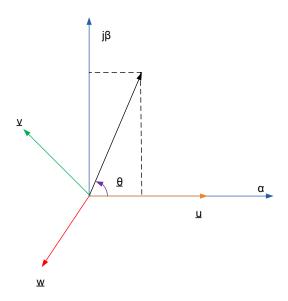

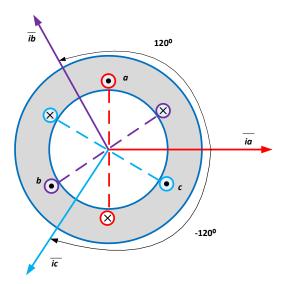

Fig 2.19: Basic schematic for threshold voltage measurement