# High Power Modular Converters for Grid Interface Applications

Marija Jankovic, BSc, MSc

January 2017.

#### Abstract

Scientists at European Organization for Nuclear Research (CERN) are currently conducting feasibility studies for the Compact linear collider (CLIC); their proposed next experimental setup for gathering information on the fundamental particles of matter. This experiment will involve the simultaneous pulsing of 1300 klystron modulators to produce a 140  $\mu$ s, 39 GW pulse with a 50 Hz repetition rate. This proposal presents many demands for the connected power system as an effort is made to "hide" this pulse from the local distribution network - instead drawing only the constant average power of approximately 300 MW. This challenge is considered in this work.

In order to understand the optimal approach both the power system architectures and power electronics interfaces must be considered simultaneously. An approach to the optimisation of the power system architecture is described in this thesis. It is clear from this exercise that the optimum power converter topology for the interface between the electricity distribution network and the klystron modulators is the Modular Multilevel Converter (MMC). This converter is mainly used in modern HVDC transmission circuits as a result of its high efficiency and ability to produce high quality AC waveforms.

Pulsing of the klystron modulators does however create further challenges for the inner control loops of an MMC. The placement of the pulse can create imbalances in the DC capacitors of the MMC submodules which may result in tripping of the converter if not corrected. This thesis proposes three arm balancing solutions to be applied together with the decoupled AC and DC side controller designed for the specified application.

These proposed solutions to the aforementioned problems are successfully validated using simulation work in PLECS and using data from a laboratory scale prototype of one of the MMC interface power converters. To my parents

- whose love travels thousands of miles -

#### Acknowledgements

First of all, I want to thank my supervisors, Prof. Jon Clare, Dr Alan Watson, Dr Alessandro Costabeber and Prof. Pat Wheeler for giving me such a great opportunity to work with them on this interesting project. Thank you for all the advice, support and exchange of ideas. Secondly, I would like to thank Dr Davide Aguglia, for his invaluable input regarding the design practice at CERN. I would also like to thank my assessors, Prof. Paul Mitcheson and Prof. Pericle Zanchetta for taking the time to read my thesis and their constructive advice during my Viva Voce Examination.

I want to thank Prof. Predrag Pejovic for introducing the field of Power electronics to me in a very accessible and appealing way and all the advice before and during my PhD studies.

Many thanks to all the people I have met in Power Electronics, Machines and Control (PEMC) group, on all the absorbing discussions, exchange of experiences and cultural exchanges. Especially, I want to thank to my companions, Manju, Savvas, Attahir, Emre, Sharmila, Shajjad, Shuai and Bilal, for being my international family constantly supporting each other from the first day of our PhDs. You guys together with Stefano, Sara, Luca, Michele, Luca, Alessandro, Mauro, Jordi, Marco, Claudio, Mi and many others made loads of great, memorable, fun-filled moments.

Thanks to Ivana, Natalija, Nikola and many other friends for their support from various countries worldwide.

Many thanks to Milan, who did this journey with me, whose love, support and advice were key at the hard times and who made easy times beautiful.

I would like to give a special thanks to my family for their constant support, love and encouragement. Particularly, to my mum, dad and grandma for believing in me, even when I did not. Thanks to my brother and his family for their cheering and love.

### List of Terms

#### Abbreviations

|                                                       | <b>MMSPC</b> - Modular Multilevel Series Parallel   |

|-------------------------------------------------------|-----------------------------------------------------|

| Nucleaire                                             | Converter                                           |

| ${\bf CLIC}$ - Compact Linear Collider                | $\mathbf{AAC}$ - Alternate Arm Converter            |

| ${\bf RF}$ - Radio Frequency                          | <b>PH-M2C</b> - Parallel Hybrid Modular Multilevel  |

| ${\bf EDF}$ - Electricite de France                   | Converter                                           |

| $\mathbf{MMC}$ - Modular Multilevel Converter         | LV - Low Voltage                                    |

| $\mathbf{NPC}$ - Neutral-Point Clamped                | $\mathbf{MV}$ - Medium Voltage                      |

| <b>CHB</b> - Cascaded H-Bridge                        | $\mathbf{HV}$ - High Voltage                        |

|                                                       | ${\bf SVC}$ - Static VAR Compensator                |

| FC - Flying Capacitor                                 | ${\bf LMV}$ - Lower Medium Voltage                  |

| <b>DCC</b> - Diode-Clamped Converter                  | ${\bf CSA}$ - Cross Section Area                    |

| $\mathbf{VSC}$ - Voltage Source Converter             | $\mathbf{TE}$ - Top Event                           |

| $\mathbf{HVDC}$ - High Voltage Direct Current         | <b>BE</b> - Basic Event                             |

| $\mathbf{LCC}$ - Line-Commutated Converters           | $\mathbf{MCS}$ - Minimum Cut Set                    |

| $\mathbf{XLPE}$ - Cross-Linked Polyethylene           | <b>VDE</b> - Verband der Elektrotechnik, Elektronik |

| $\mathbf{EMI}$ - Electromagnetic Interference         | und Informationstechnik                             |

| ${\bf STATCOM}$ - Static Synchronous Compensator      | ${\bf ESR}$ - Equivalent Series Resistance          |

| <b>AF</b> - Active Filter                             | ${\bf SHE}$ - Selective Harmonic Elimination        |

| ${\bf FACTS}$ - Flexible AC Transmission Systems      | ${\bf NLC}$ - Nearest Level Control                 |

| <b>UNIFLEX-PM</b> - Universal Flexible Power          | ${\bf SVM}$ - Space Vector Modulation               |

| Management system                                     | ${\bf PWM}$ - Pulse Width Modulation                |

| $\mathbf{CMC}$ - Cascaded Matrix Converter            | <b>PD</b> - Phase Disposition                       |

| ${\bf ANPC}$ - Active Neutral-Point Clamped           | <b>POD</b> - Phase Opposite Disposition             |

| $\mathbf{MLC}^2$ - Multilevel-Clamped Multilevel Con- | ${\bf APOD}$ - Alternate Phase Opposite Disposition |

| verter                                                | <b>PLL</b> - Phase Locked Loop                      |

**DDSRF** - Decoupled Double Synchronous Reference Frame

**FLL** - Frequency Locked Loop

**DSOGI** - Decoupled Second-Order Generalised Integrator

**ISR** - Interrupt Service Routine

#### Nomenclature

$V_{DC}$ ,  $v_{DC}$  - Converter DC voltage mean and instantaneous value

$\Delta V, \Delta V^{max}$  - DC voltage droop and its maximum value

$P_{peak}$  - Klystron modulator peak power

$T_{pulse}$  - Pulse duration

- $f_{rep}$  Pulse repetition frequency

- $T_{rep}$  Pulse repetition period

$v_{s\_AC}$  - Grid RMS line to line voltage

$k_{AC}$  - Converter DC to AC voltage ratio

$P_{rated}$ ,  $P_{nominal}$  - Power system component rated and nominal power

n - Number of power system components on a common bus bar

$U_{fault}, U_{nom}$  - Equivalent and nominal voltage at the fault location

$\mathbb{Z}_{0,1,2}\,$  - Impedance towards the grid: 0 - zero, 1- positive, 2 - negative sequence

${I_K}^{\prime\prime}\,$  - Sub-transient fault current

$P_{top}$  - Probability of the top event

${\cal P}_{MCS}\,$  - Probability of the MCS

$E_{stored}$  - Energy stored in all cell capacitors

- $P_{rat}$  Converter rated power

- $E_{arm}$  Energy stored in one arm inductor

- $L_{arm}$  Arm inductance

$i_{DC}$ ,  $I_{DC}$  - Converter DC current instantaneous and mean value

$k_{1,2}$  - Coefficients for the energy stored in the converter arm inductors

$C_{DC}$  - DC link capacitance

- $E_{DC}$  The energy stored in the DC link capacitors

- $N\,$  Number of cells per MMC arm

- $v_{s_A,B,C}$  Grid/source voltage of the phase A, B or C

- $i_{A,B,C}$  Converter and grid current of the phase A, B or C

- $v_{A,B,C}$  Converter AC voltage of the phase A, B or C

- $C_{cell}$  Cell capacitance

- $L_{ph}$  Phase inductance

- $i_{up,A,B,C}$  Upper arm chain-link current of phase A, B or C

- $i_{lo_A,B,C}$  Lower arm chain-link current of phase A, B or C

$v_{up-A,B,C}, v_{up-A,B,C}$  - Upper arm chain-link voltage and its reference of phase A, B or C

- $v_{lo_A,B,C}, v_{lo_A,B,C}$  Lower arm chain-link voltage and its reference of phase A, B or C

- $v_{Cup_{A,B,Ci}}$  Capacitor voltage of  $i^{th}$  cell in the upper arm of phase A, B or C

- $v_{Clo\_A,B,Ci}\,$  Capacitor voltage of  $i^{th}$  cell in the lower arm of phase A, B or C

- $i_{circ\_A,B,C}, i_{circ\_A,B,C}$ <sup>ref</sup> Circulating current and its reference of phase A, B or C

$v_{DC}^+$ ,  $v_{DC}^-$  - DC link positive and negative voltage potential

$v_{AC\_A,B,C}$ ,  $v_{AC\_A,B,C}$ ,  $r^{ef}$  - AC part of the arm voltage and its reference of phase A, B or C  $v_{DC\_A,B,C}$ ,  $v_{DC\_A,B,C}$ ,  $r^{ef}$  - DC part of the arm voltage and its reference of phase A, B or C  $V_{sm}$  - Grid voltage amplitude

- $I_m$  Phase current amplitude

- $\omega\,$  Grid radial frequency

- f Grid frequency

$p_{s\_A,B,C},\,P_{s\_A,B,C}\,$  - Grid/source instantaneous and average power of the phase A, B or C

- $\phi_i$  Phase shift between grid voltage and phase current vector

- $\phi_v\,$  Phase shift between grid voltage and converter AC voltage vector

- $V_m\,$  Converter voltage amplitude

- $p_{AC},\,P_{AC}\,$  Overall grid AC side instantaneous and average (active) power

- $Q_{AC}$  Overall grid AC side reactive power

- $p_{DC}$ ,  $P_{DC}$  Converter DC side instantaneous and average power

- $v_C, V_C$  Average cell capacitor voltage in a chainlink and its nominal value

- $E_{cl}$  Overall energy of a chainlink

- $P_{cl}$  Average chainlink power

- $p_{up_{A},B,C}, P_{up_{A},B,C}$  Upper arm instantaneous and average power

- $p_{lo_{-}A,B,C}$ ,  $P_{lo_{-}A,B,C}$  Lower arm instantaneous and average power

- $EP\,$  Capacitance constant

- $L_{arm\_res}$  Resonance value of arm inductance

- $\alpha\,$  Fault DC current rise rate

- $\theta\,$  Phase angle of the grid voltages

- $v_{s\_\alpha,\beta}$  Grid voltage  $\alpha$  or  $\beta$  component

- $i_{\alpha,\beta}$  Phase current  $\alpha$  or  $\beta$  component

- $v_{AC_{-\alpha,\beta}}$  AC part of the arm (converter) voltage  $\alpha$  or  $\beta$  component

- $v_{s\_d,q}$  Grid voltage d or q component

$i_{d,q}, i_{d,q}^{ref}$  - Phase current d or q component and its reference

- $L_{eq}$  Equivalent phase inductor

- $v_{AC_{-d,q}}$  AC part of the arm (converter) voltage d or q component

- $\tau_i$  Time constant of d, q current controller

- $k_{dq,p}, k_{dq,i}$  Proportional and integral gain of the d, q current controller

- $\tau_{i\_circ}\,$  Time constant of circulating current controllers

- $k_{circ_p}, k_{circ_i}$  Proportional and integral gain of circulating current controllers

- $i_{load}$  Load current

- $v_{tot}, V_{tot}, V_{tot}$  Sum of all cell capacitor voltages, its average value and reference

- $v_{tot_{-}A,B,C}$ ,  $V_{tot_{-}A,B,C}$ ,  $V_{tot_{-}A,B,C}$ <sup>ref</sup> Sum of phase A, B or C cell capacitor voltages, its average value and reference

- $P_{A,B,C}$  Power added to the phase A, B or C

- $\Delta I_{circ_{-}A,B,C}$  Phase balancing correction to the circulating current reference of phase A, B or C

- $\Delta P_{arm_{-}A,B,C}$  Difference between arm powers of phase A, B or C

- $I_{circ50\_A,B,C}$  Circulating current 50 Hz component amplitude of phase A, B or C

- $DEN_{A,B,C}$  Ratio describing how the circulating current amplitude (or x parameter) affects the arm powers difference of phase A, B or C

- $v_{DC50},\,V_{DC50}\,$  DC voltage 50 Hz component ripple and its amplitude

- $\phi_{DC50}$  DC voltage 50 Hz component ripple angle

- $\phi_{circ50-A,B,C}$  Circulating current 50 Hz component angle

- $NUM_{A,B,C}$  The amount of imbalance between arm powers of phase A, B or C

- $x_{A,B,C}$  Parameter x for phase A, B or C

- $Z_{arm}$  Equivalent arm impedance amplitude

- $\Delta \phi_{circ50}$  Equivalent arm impedance angle

- $I_{peak}$  Peak load current

- $T_{s\,}$  Sampling time

- $f_s$  Sampling/switching frequency

- $L_{load}$  Load inductance

- $C_{load}$  Load capacitance

- $R_{load}$  Load resistance

- $v_{out}$  Output load voltage

- $\lambda\,$  Load dumping factor

- $R_M$  Burden resistor

- $T\,$  Grid period

- $I_{load50}$  Load current 50 Hz component amplitude

- $I_{DC50}$  DC current 50 Hz component amplitude

- $\phi_{load50}\,$  Load current 50 Hz component angle

- $\phi_{IDC50}$  DC current 50 Hz component angle

- $t_{start}\,$  Time when the pulse starts with respect to the phase A grid voltage positive gradient zero crossing

### Contents

| 1        | Intr       | Introduction                                                         |         |  |

|----------|------------|----------------------------------------------------------------------|---------|--|

|          | 1.1        | Motivation for the research project                                  | 1       |  |

|          |            | 1.1.1 Compact linear collider                                        | 1       |  |

|          |            | 1.1.2 Requirements for the grid interface to the klystron modulators | 3       |  |

|          | 1.2        | Project objectives                                                   | 6       |  |

|          | 1.3        | Organisation of the thesis                                           | 7       |  |

| <b>2</b> | Mu         | ltilevel converters - Literature review                              | 9       |  |

|          |            |                                                                      |         |  |

|          | 2.1        | Introduction                                                         | 9       |  |

|          | 2.1<br>2.2 | Introduction                                                         | 9<br>11 |  |

|          |            |                                                                      |         |  |

| 3        | 2.2<br>2.3 | Multilevel topologies                                                | 11      |  |

|   | 3.2 | Power system components and nomenclature                  |    |  |  |

|---|-----|-----------------------------------------------------------|----|--|--|

|   | 3.3 | Background on possible power system structures            |    |  |  |

|   | 3.4 | Power system representation                               |    |  |  |

|   |     | 3.4.1 Design rules and CERN specific limitations          | 29 |  |  |

|   |     | 3.4.2 Power system design                                 | 30 |  |  |

|   |     | 3.4.3 Cable models                                        | 34 |  |  |

|   |     | 3.4.4 Transformers                                        | 35 |  |  |

|   |     | 3.4.5 Fault Currents                                      | 36 |  |  |

|   |     | 3.4.6 Availability                                        | 39 |  |  |

|   |     | 3.4.7 Power electronics parameters                        | 41 |  |  |

|   | 3.5 | Power system optimisation                                 |    |  |  |

|   | 3.6 | Summary                                                   |    |  |  |

| 4 | Mo  | dular multilevel converter                                | 53 |  |  |

|   | 4.1 | Introduction                                              | 53 |  |  |

|   | 4.2 | MMC features                                              | 54 |  |  |

|   | 4.3 | Modulation methods                                        | 56 |  |  |

|   |     | 4.3.1 Background on classic multilevel modulation methods | 56 |  |  |

|   |     | 4.3.2 Modulation methods for MMC                          | 60 |  |  |

|   | 4.4 | Converter models                                | 63 |

|---|-----|-------------------------------------------------|----|

|   |     | 4.4.1 Grid connected converter power            | 67 |

|   |     | 4.4.2 Energy stored in converter chainlinks     | 70 |

|   | 4.5 | MMC sizing                                      | 72 |

|   | 4.6 | Summary                                         | 74 |

| 5 | Cor | ntrol of VSC with a pulsed load                 | 77 |

|   | 5.1 | Introduction                                    | 77 |

|   | 5.2 | General background on VSC control               | 78 |

|   | 5.3 | Decoupled AC and DC side control                | 81 |

|   |     | 5.3.1 Control strategy                          | 82 |

|   |     | 5.3.2 Circulating current control               | 85 |

|   | 5.4 | Voltage controllers                             | 88 |

|   |     | 5.4.1 DC voltage controller                     | 88 |

|   |     | 5.4.2 Cell capacitor voltages and their control | 90 |

|   |     | 5.4.2.1 Energy controller                       | 91 |

|   |     | 5.4.2.2 Phase balancing control                 | 92 |

|   |     | 5.4.2.3 Arm balancing control                   | 93 |

|   | 5.5 | Pulsed load effects                             | 94 |

|   | 5.6                               | Arm balancing under pulsed DC load                                                                       |                                                           | 98                        |

|---|-----------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|---------------------------|

|   |                                   | 5.6.1 A                                                                                                  | Analytical solution for the circulating current reference | 98                        |

|   |                                   | 5.6.2 Circulating current reference regardless of DC load type $\ldots$                                  |                                                           | 104                       |

|   |                                   | 5.6.3 Change in the modulation scheme to achieve arm balancing $\ .$                                     |                                                           | 105                       |

|   | 5.7                               | Grid synchronisation                                                                                     |                                                           |                           |

|   | 5.8                               | Control                                                                                                  | algorithms for soft-start and precharge                   | 112                       |

|   |                                   | 5.8.1 P                                                                                                  | Precharge from the DC side                                | 114                       |

|   | 5.9                               | Summar                                                                                                   | у                                                         | 115                       |

| 6 | Sim                               |                                                                                                          |                                                           | 118                       |

|   | 6.1                               |                                                                                                          |                                                           | 118                       |

|   |                                   |                                                                                                          |                                                           |                           |

|   | 6.2                               | Simulati                                                                                                 | on model implementation                                   | 120                       |

|   | 6.2                               |                                                                                                          | on model implementation                                   |                           |

|   | 6.2                               | 6.2.1 C                                                                                                  |                                                           | 120                       |

|   | <ul><li>6.2</li><li>6.3</li></ul> | 6.2.1 C<br>6.2.2 In                                                                                      | Converter and load implementation                         | 120<br>e121               |

|   |                                   | 6.2.1 C<br>6.2.2 In<br>Performa                                                                          | Converter and load implementation                         | 120<br>e121               |

|   | 6.3                               | 6.2.1 C<br>6.2.2 In<br>Performa<br>Validatio                                                             | Converter and load implementation                         | 120<br>e121<br>123        |

|   | 6.3                               | <ul> <li>6.2.1 C</li> <li>6.2.2 In</li> <li>Performation</li> <li>Validation</li> <li>6.4.1 P</li> </ul> | Converter and load implementation                         | 120<br>e121<br>123<br>126 |

$\mathbf{7}$

|     | 6.4.2  | Circulating current controller                                                 |

|-----|--------|--------------------------------------------------------------------------------|

|     |        | 6.4.2.1 Circulating current waveforms                                          |

|     |        | 6.4.2.2 DC voltage controller                                                  |

|     |        | 6.4.2.3 Phase balancing                                                        |

|     |        | $6.4.2.4  \text{Arm balancing}  \dots  \dots  \dots  \dots  \dots  \dots  145$ |

|     | 6.4.3  | Disabling arm balancing controller                                             |

|     | 6.4.4  | General converter waveforms                                                    |

| 6.5 | Perfor | mance of the control system for different pulse positions $\ldots$ 160         |

|     | 6.5.1  | Arm balancing method one 161                                                   |

|     | 6.5.2  | Arm balancing method two 163                                                   |

|     | 6.5.3  | Arm balancing method three                                                     |

| 6.6 | Summ   | ary                                                                            |

| Exp | perime | ntal rig 168                                                                   |

| 7.1 | Introd | uction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $168$             |

| 7.2 | Protot | cype design                                                                    |

|     | 7.2.1  | Converter design                                                               |

|     | 7.2.2  | Pulsed load design                                                             |

|     | 7.2.3  | Precharge circuit                                                              |

|   | 7.3               | Contro                               | ol hardware                                                               | 180                      |

|---|-------------------|--------------------------------------|---------------------------------------------------------------------------|--------------------------|

|   |                   | 7.3.1                                | Data acquisition                                                          | 180                      |

|   |                   |                                      | 7.3.1.1 Voltage and current transducers                                   | 181                      |

|   |                   | 7.3.2                                | Digital control                                                           | 183                      |

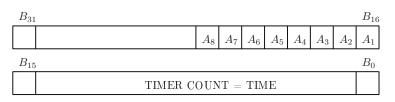

|   |                   |                                      | 7.3.2.1 FPGA board and control signals generation                         | 184                      |

|   |                   |                                      | 7.3.2.2 DSP board                                                         | 187                      |

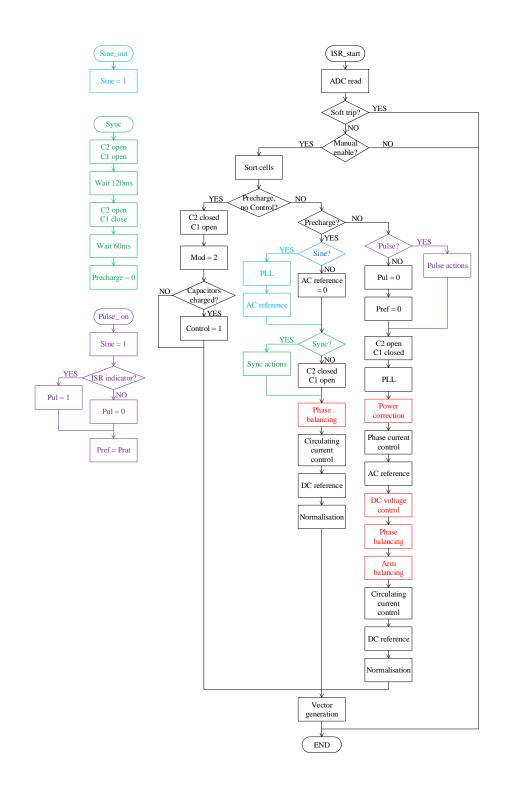

|   | 7.4               | Contro                               | ol software                                                               | 188                      |

|   |                   | 7.4.1                                | Implementation of the control loops                                       | 191                      |

|   | 7.5               | Summ                                 | nary                                                                      | 193                      |

|   |                   |                                      |                                                                           |                          |

| 8 | Exp               | erime                                | ntal results                                                              | 194                      |

| 8 | <b>Exp</b><br>8.1 |                                      | ntal results<br>luction                                                   | -                        |

| 8 | -                 | Introd                               |                                                                           | 194                      |

| 8 | 8.1               | Introd<br>Evalua                     | luction                                                                   | 194<br>196               |

| 8 | 8.1<br>8.2        | Introd<br>Evalua<br>Pulsec           | luction                                                                   | 194<br>196<br>199        |

| 8 | 8.1<br>8.2<br>8.3 | Introd<br>Evalua<br>Pulsec           | luction          ation of the precharge and PLL          l load waveforms | 194<br>196<br>199        |

| 8 | 8.1<br>8.2<br>8.3 | Introd<br>Evalua<br>Pulsed<br>Valida | luction                                                                   | 194<br>196<br>199<br>201 |

|     | 8.4.2  | Circulati  | ing current control                                                      | 211 |

|-----|--------|------------|--------------------------------------------------------------------------|-----|

|     |        | 8.4.2.1    | Circulating current in the cases of different arm bal-<br>ancing methods | 213 |

|     |        | 8.4.2.2    | DC voltage controller                                                    | 216 |

|     |        | 8.4.2.3    | DC current in the cases of different arm balancing methods               | 218 |

|     |        | 8.4.2.4    | Phase balancing                                                          | 221 |

|     |        | 8.4.2.5    | Arm balancing                                                            | 222 |

|     | 8.4.3  | Disablin   | g arm balancing controller                                               | 228 |

|     | 8.4.4  | General    | converter waveforms                                                      | 235 |

| 8.5 | Perfor | mance of   | the control system for different pulse positions $\ldots$ .              | 239 |

|     | 8.5.1  | Arm bal    | ancing method one                                                        | 240 |

|     | 8.5.2  | Arm bal    | ancing method two                                                        | 242 |

|     | 8.5.3  | Arm bal    | ancing method three                                                      | 244 |

| 8.6 | Summ   | ary        |                                                                          | 247 |

| Con | clusio | ns         |                                                                          | 249 |

| 9.1 | Summ   | ary of acl | nievements and contribution                                              | 255 |

| 9.2 | Plans  | for impro  | vement                                                                   | 256 |

9

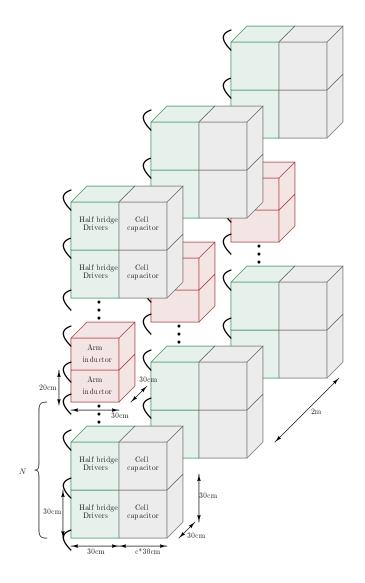

|              | A.1 | Introduction                                                  | 274 |

|--------------|-----|---------------------------------------------------------------|-----|

|              | A.2 | Spatial distribution and estimation of civil engineering cost | 274 |

|              | A.3 | Summary                                                       | 278 |

|              |     |                                                               |     |

| В            | Mo  | delling converter waveforms for different pulse positions     | 279 |

|              | B.1 | Introduction                                                  | 279 |

|              | B.2 | Waveforms modelling                                           | 279 |

|              | B.3 | Summary                                                       | 284 |

|              |     |                                                               |     |

| $\mathbf{C}$ | Pub | lication list                                                 | 286 |

# List of Figures

| 1.1 | Initial CLIC layout overview aimed for 3 TeV centre-of-mass energy.                                          |    |

|-----|--------------------------------------------------------------------------------------------------------------|----|

|     | The figure is taken from $[1]$                                                                               | 2  |

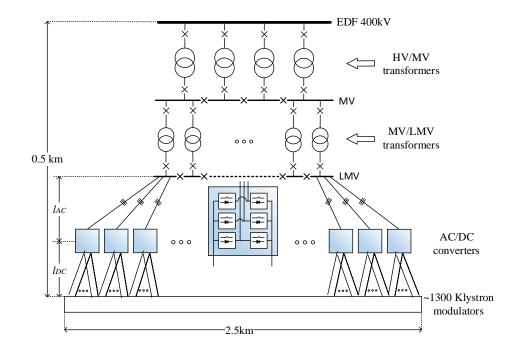

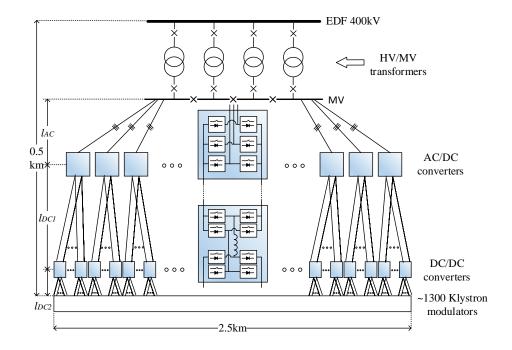

| 1.2 | Grid interface to the drive beam klystron modulators                                                         | 4  |

| 1.3 | From left to right: the expected grid voltage, DC voltage and the final modulator voltage.                   | 4  |

| 2.1 | Phase A representation of the a) 3-level and b) 5-level diode clamped                                        |    |

|     | converter.                                                                                                   | 12 |

| 2.2 | Phase A representation of 7-level cascaded H-bridge converter                                                | 13 |

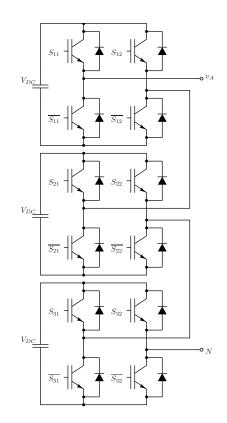

| 2.3 | Phase A representation of the 2 cell per arm a) MMC utilising half bridges and b) AAC utilising full bridges | 16 |

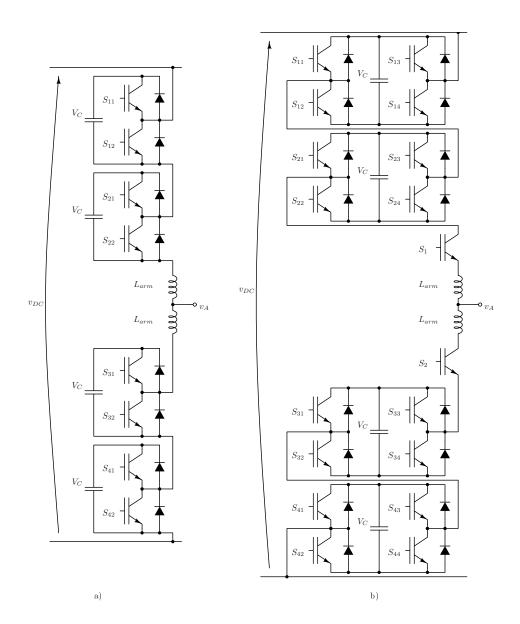

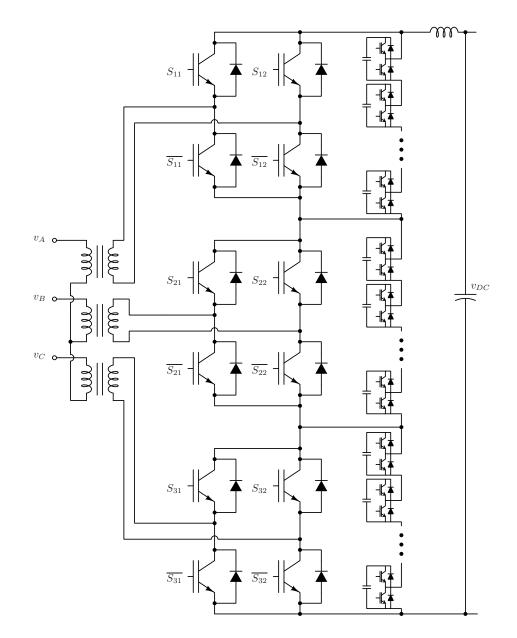

| 2.4 | Three phase parallel hybrid modular multilevel converter with the in-<br>put transformer and DC link filter  | 18 |

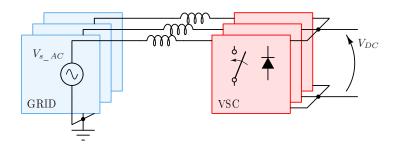

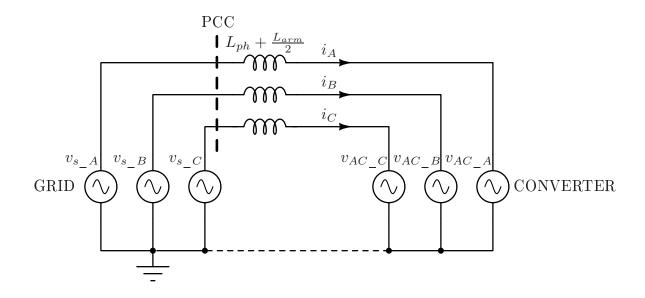

| 3.1 | Grid connected voltage source converter                                                                      | 24 |

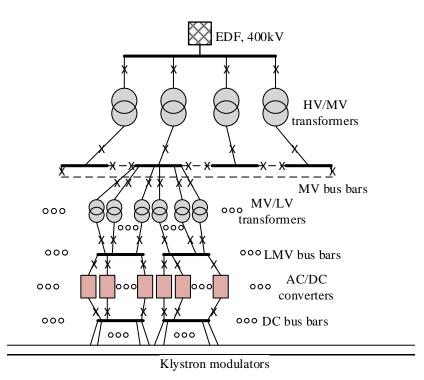

| 3.2 | Single-stage conversion example                                                                              | 25 |

| 3.3  | Double-stage conversion example                                                                                                                                             | 26 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.4  | An example of a power system layout with radially distributed bus bars.                                                                                                     | 31 |

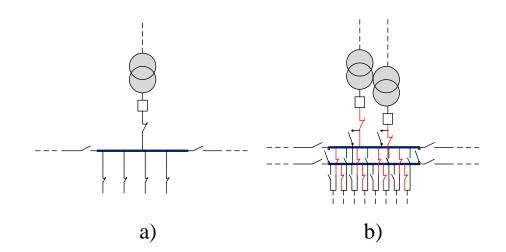

| 3.5  | A comparison of a) single and b) parallel bus bars design principle.                                                                                                        | 32 |

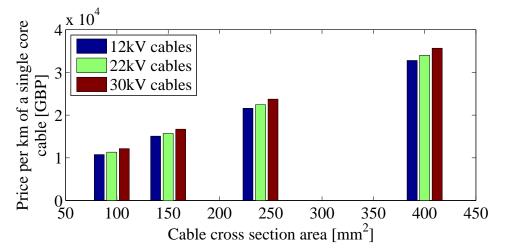

| 3.6  | Cable prices in GBP for the MV cables depending on the voltage rating and conductor cross section.                                                                          | 35 |

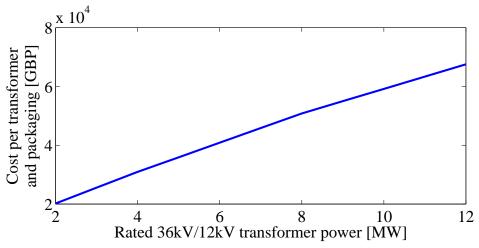

| 3.7  | Transformer (and packaging) price in GBP vs. rated power                                                                                                                    | 36 |

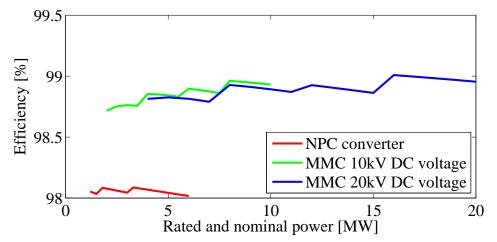

| 3.8  | Converter efficiency vs. rated power for different voltage ratings, esti-<br>mated using the methodology from [2]                                                           | 43 |

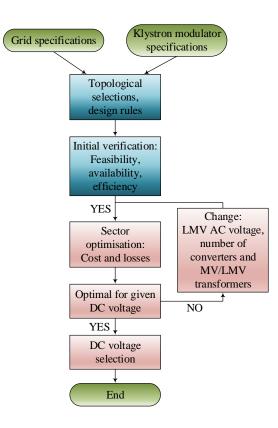

| 3.9  | Power system optimisation diagram.                                                                                                                                          | 45 |

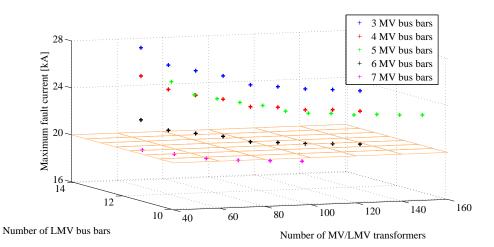

| 3.10 | Maximum fault currents in the case of LMV at $6  kV$ and the final DC voltage about $10  kV$ .                                                                              | 46 |

| 3.11 | Maximum fault currents in the case of LMV at $10  kV$ and the final DC voltage about $20  kV$ .                                                                             | 47 |

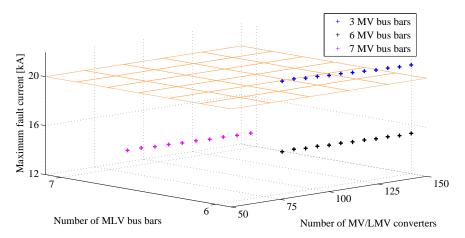

| 3.12 | Two different sector architectures delivering a) $10 \mathrm{kV}$ , b) $20 \mathrm{kV}$ DC voltage                                                                          | 47 |

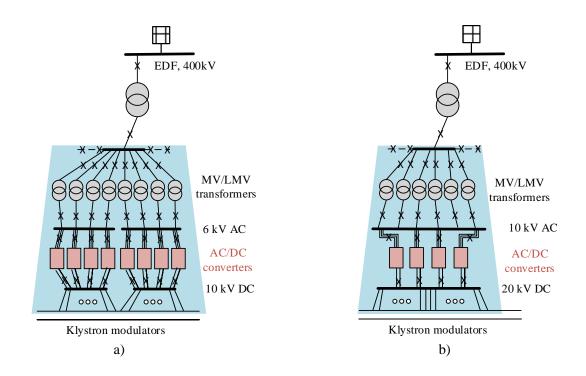

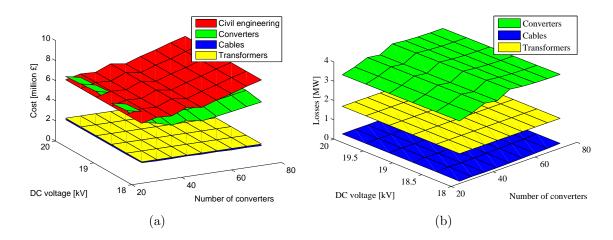

| 3.13 | Total a) cost and b) losses of the 6 sectors optimisied to deliver specified DC voltage belonging to the $10 \mathrm{kV}$ (green) and $20 \mathrm{kV}$ (red) voltage range. | 48 |

| 3.14 | Break down of the total a) cost and b) losses of the 6 sectors vs. the DC voltage and number of converters                                                                  | 49 |

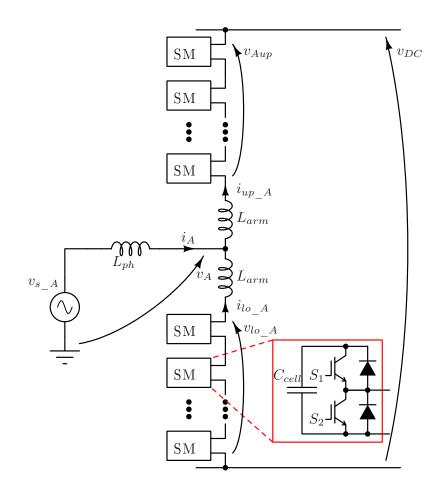

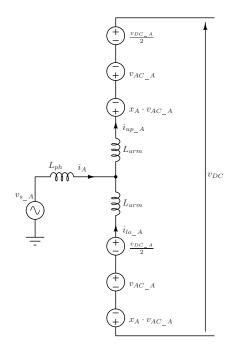

| 4.1  | A single-phase representation of a modular multilevel converter                                                                                                             | 55 |

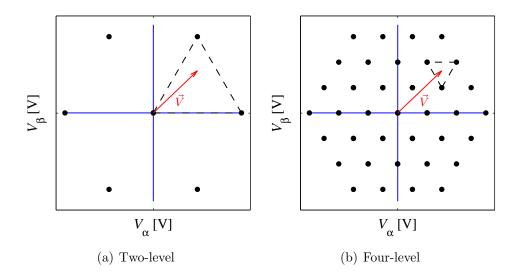

| 4.2  | SVM diagram for three-phase converter.                                                                                                                                      | 57 |

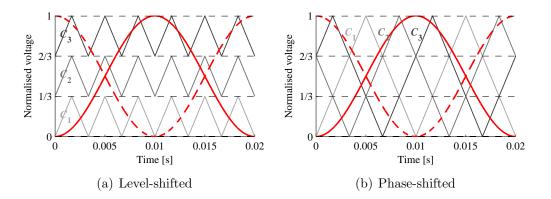

| 4.3  | Carrier based modulation technique for 3 cell per arm MMC, where<br>full line presents the reference for the lower arm, whist the dashed line<br>reference signal is a reference of the upper arm | 59 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

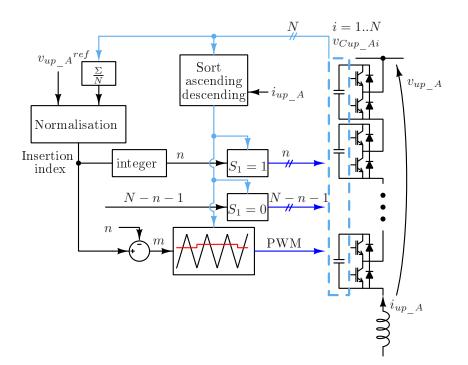

| 4.4  | Modulation algorithm with cell capacitor voltages balancing feature,<br>on the example of the upper arm chainlink of phase A                                                                      | 63 |

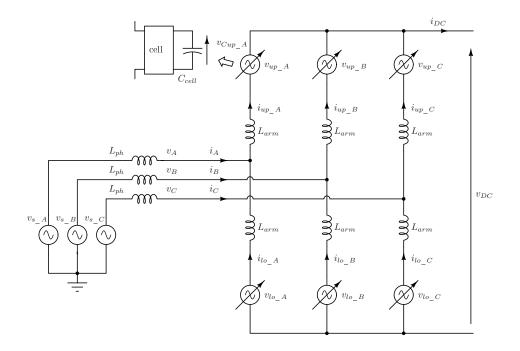

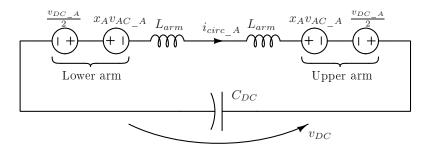

| 4.5  | Grid connected MMC simplified schematics                                                                                                                                                          | 64 |

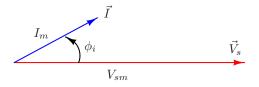

| 4.6  | Voltage and current vector, with the phase shift displacement                                                                                                                                     | 68 |

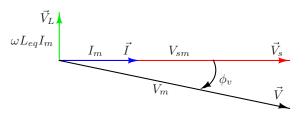

| 4.7  | Phase current and grid and converter voltage vectors                                                                                                                                              | 69 |

| 5.1  | Equivalent AC circuit of grid connected MMC converter                                                                                                                                             | 79 |

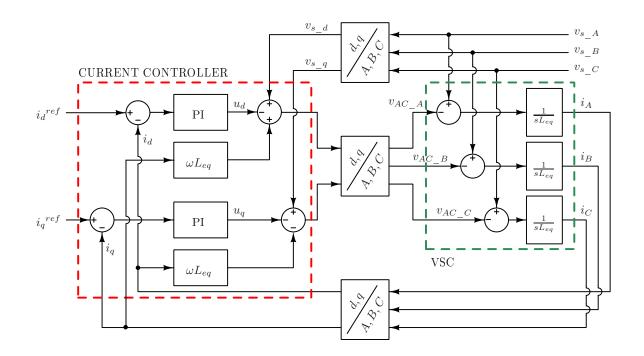

| 5.2  | PI based $d$ , $q$ axis current controller                                                                                                                                                        | 80 |

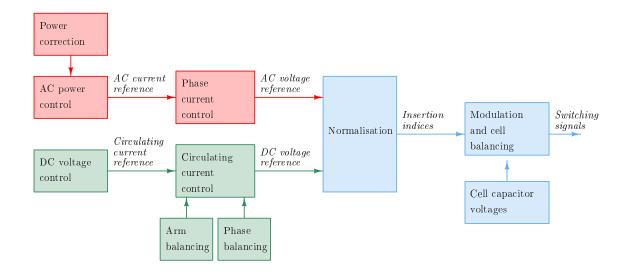

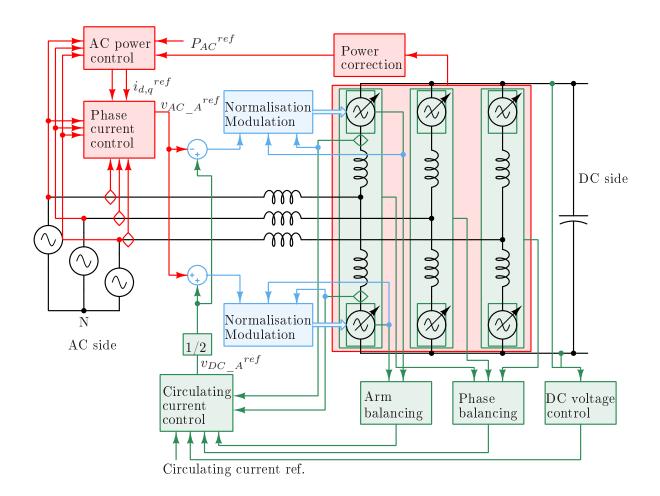

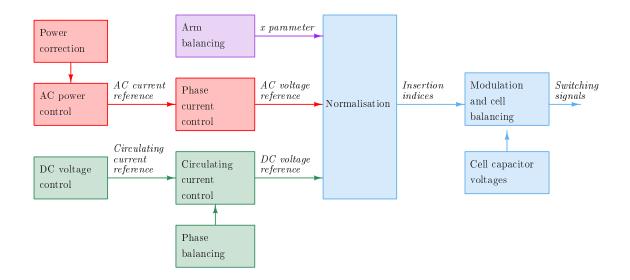

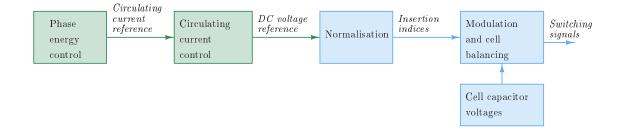

| 5.3  | Decoupled AC and DC side controller strategy for the specified appli-<br>cation                                                                                                                   | 84 |

| 5.4  | The control strategy applied on the MMC converter, with the focus on one converter phase.                                                                                                         | 85 |

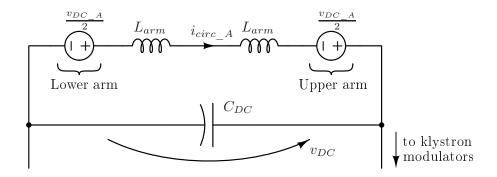

| 5.5  | Equivalent DC side circuit of phase A of an MMC converter                                                                                                                                         | 86 |

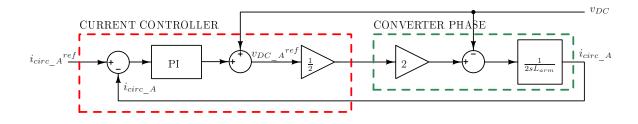

| 5.6  | Circulating current controller for the phase A                                                                                                                                                    | 87 |

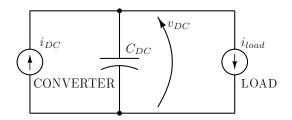

| 5.7  | Equivalent circuit on the DC link side                                                                                                                                                            | 88 |

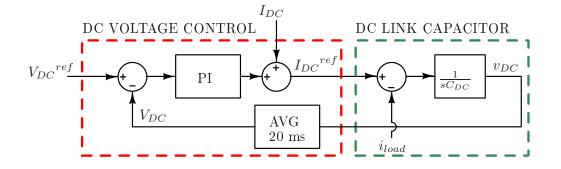

| 5.8  | DC voltage controller used for the DC current reference generation                                                                                                                                | 89 |

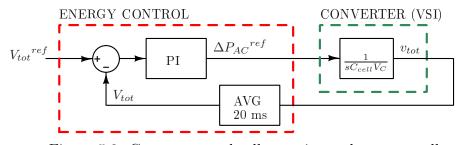

| 5.9  | Converter total cell capacitor voltage controller                                                                                                                                                 | 91 |

| 5.10 | Phase A total cell capacitor voltage controller                                                                                                                                                   | 92 |

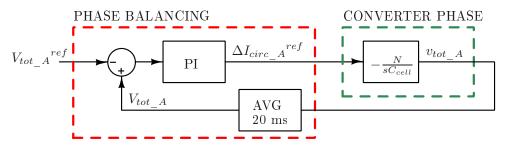

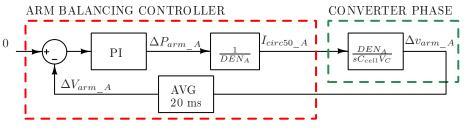

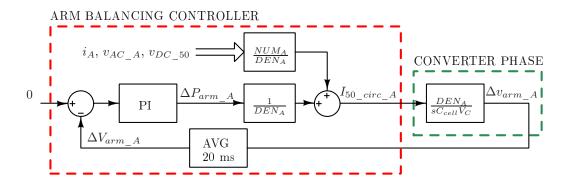

| 5.11 | Arm balancing controller.                                                                                                                                         | 94  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.12 | AC side power of the converter with pulsed DC load and constant circulating currents                                                                              | 96  |

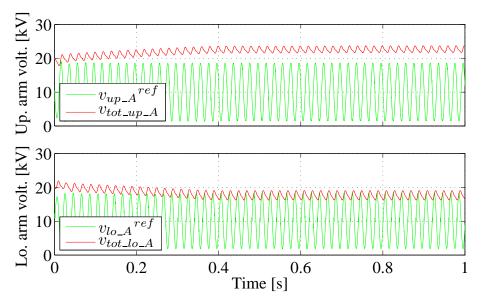

| 5.13 | The modulation signal (green) and total available voltage (red) of up-<br>per (top) and lower (bottom) arm voltages in the imbalanced condition.                  | 97  |

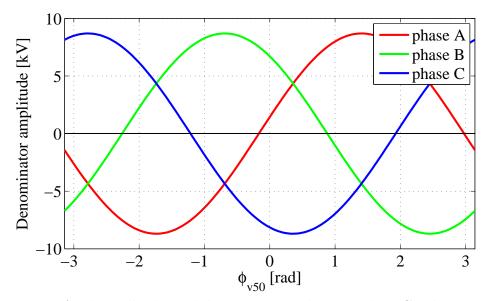

| 5.14 | Analytically derived denominator values vs. the DC voltage ripple phase angle                                                                                     | 101 |

| 5.15 | Arm balancing under pulsed DC load on the example of phase A. $$ .                                                                                                | 102 |

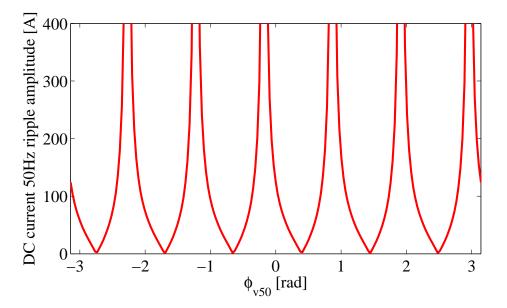

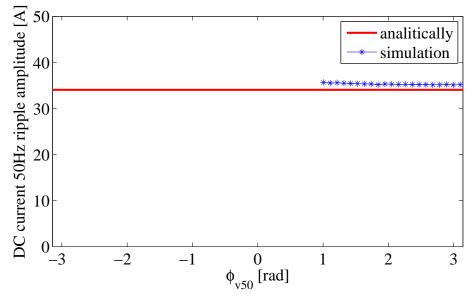

| 5.16 | Analytically derived DC current 50 Hz component amplitude vs. the DC voltage ripple phase angle                                                                   | 103 |

| 5.17 | Simplified schematics of the phase A of an MMC with uneven distri-<br>bution of AC voltage reference.                                                             | 106 |

| 5.18 | Equivalent DC side circuit of phase A of an MMC with uneven AC reference distribution                                                                             | 107 |

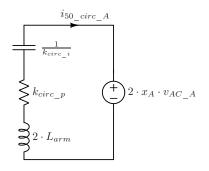

| 5.19 | Circulating current 50 Hz component equivalent circuit in the case of<br>uneven AC reference distribution, assuming PI based circulating cur-<br>rent controller. | 108 |

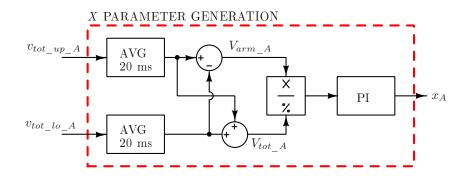

| 5.20 | Parameter $x_A$ generation on the basis of cell capacitor voltages on the example of phase A                                                                      | 109 |

| 5.21 | Controller strategy with the redistributed AC reference for the appli-<br>cation of interest                                                                      | 110 |

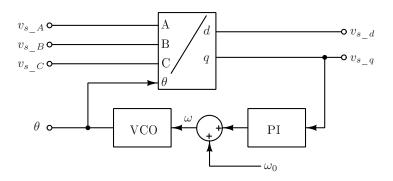

| 5.22 | PLL applied on grid voltages, to provide grid phasor angle                                                                                                        | 111 |

| 5.23 | The grid connected MMC with the precharge circuit attached to the                                                                                            |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | DC side                                                                                                                                                      | 114 |

| 5.24 | Controller strategy for the controlled stage of the precharge regime                                                                                         | 115 |

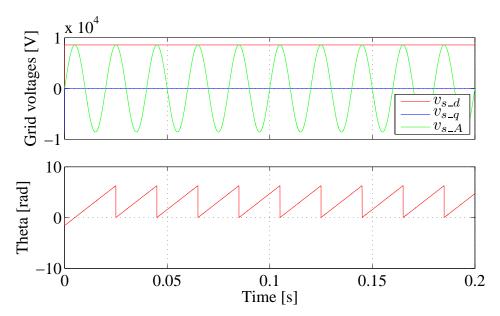

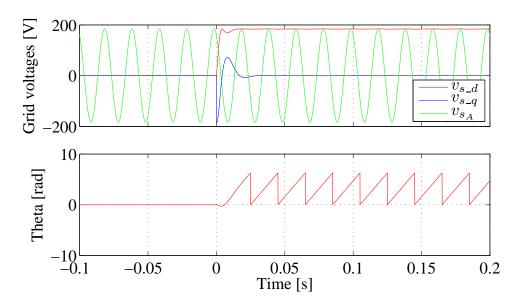

| 6.1  | Grid voltages and phase angle in transient when the simulation starts.                                                                                       | 124 |

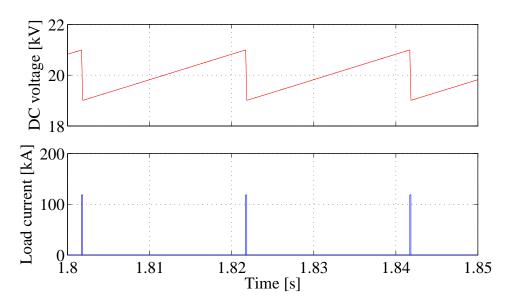

| 6.2  | Pulsed load characteristics: DC voltage and load current under steady state conditions                                                                       | 125 |

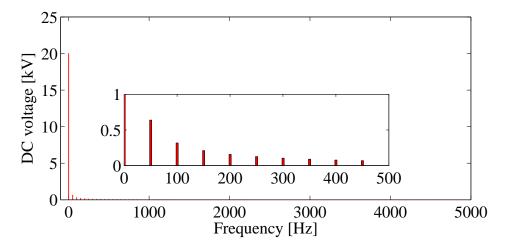

| 6.3  | DC voltage harmonics under steady state conditions when arm balanc-<br>ing method one is applied                                                             | 126 |

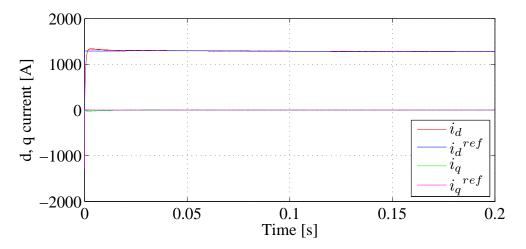

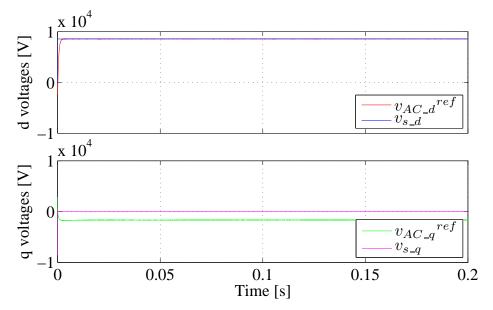

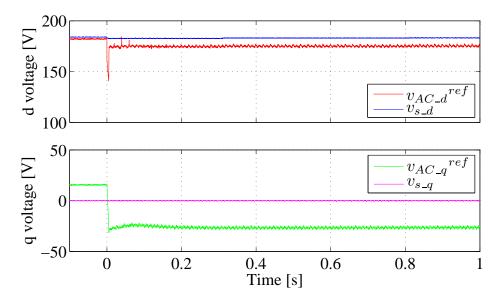

| 6.4  | The $d, q$ current controller reference tracking during transient in the case of arm balancing method one                                                    | 127 |

| 6.5  | Grid voltage and the converter AC voltage $d$ , $q$ components during transient in the case of arm balancing method one                                      | 128 |

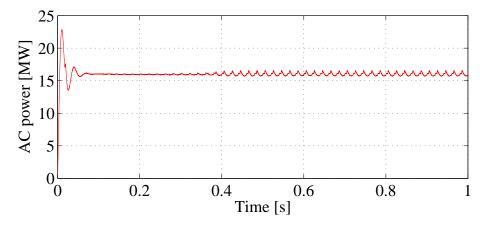

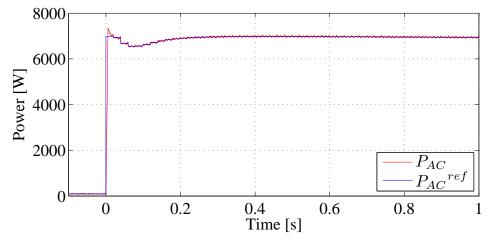

| 6.6  | Grid active power and its reference during transient in the case of arm balancing method one.                                                                | 129 |

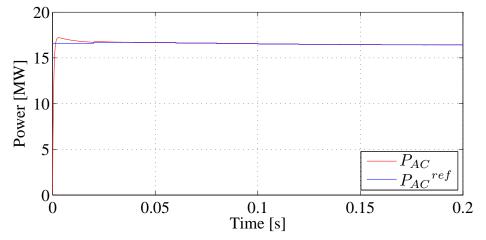

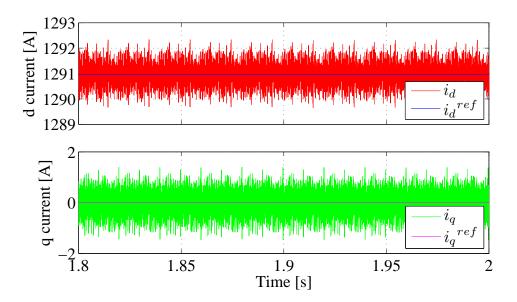

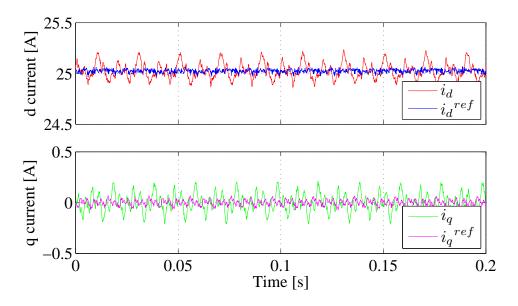

| 6.7  | The $d,q$ current controller reference tracking under steady state conditions with pulsed load when arm balancing method one is applied                      | 129 |

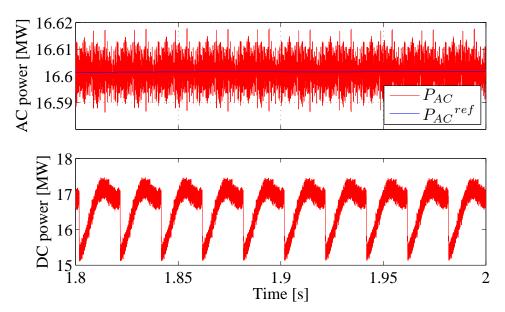

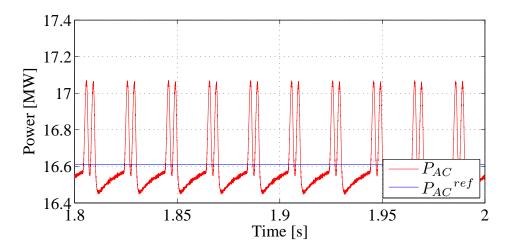

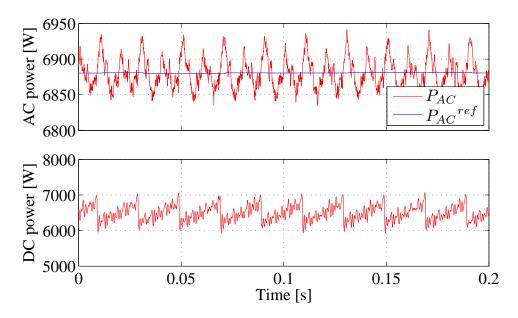

| 6.8  | Grid active power and its reference and the converter DC power under<br>steady state conditions with pulsed load when arm balancing method<br>one is applied | 130 |

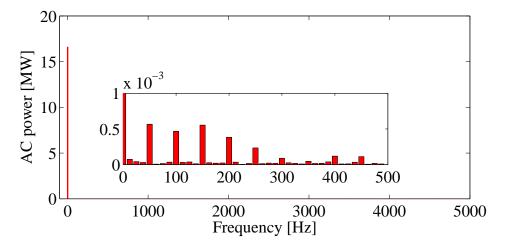

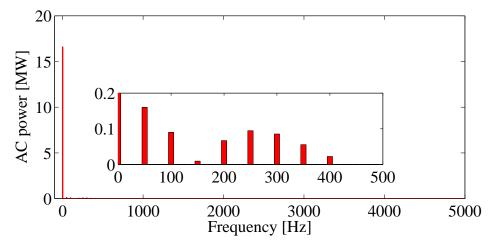

| 6.9  | Grid active power harmonics under steady state conditions with pulsed<br>load when arm balancing method one is applied                                       | 131 |

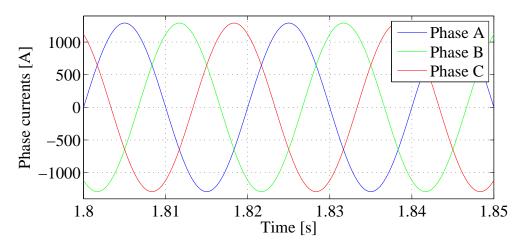

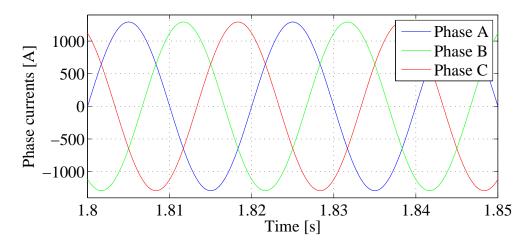

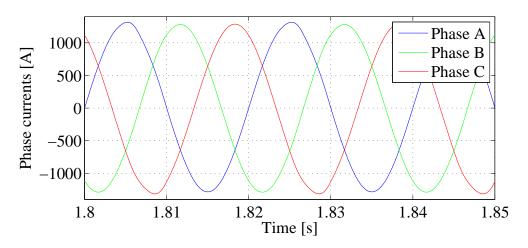

| 6.10 | Phase/grid currents under steady state conditions with pulsed DC load, when arm balancing method one is applied.                                             | 132 |

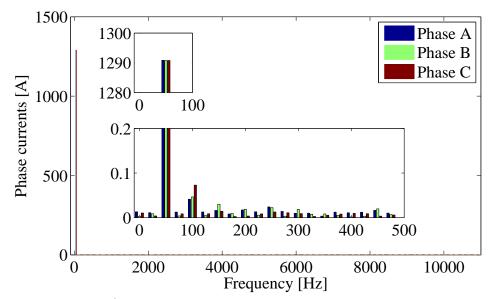

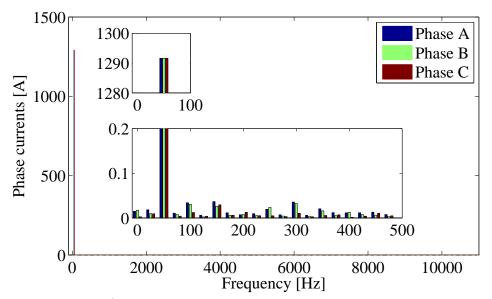

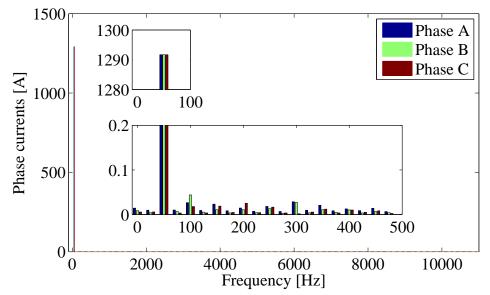

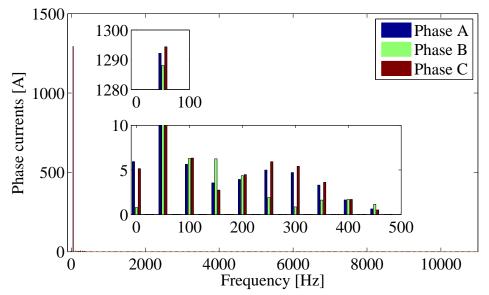

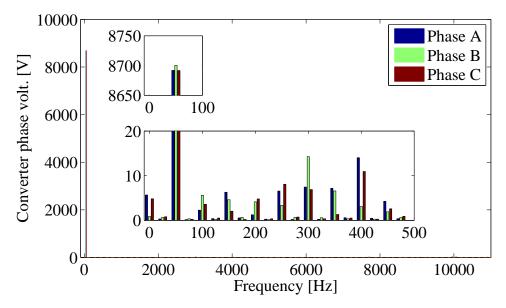

| 6.11 | Phase/grid currents spectrum under steady state conditions with pulsed   |      |

|------|--------------------------------------------------------------------------|------|

|      | DC load, when arm balancing method one is applied. $\ldots$              | 132  |

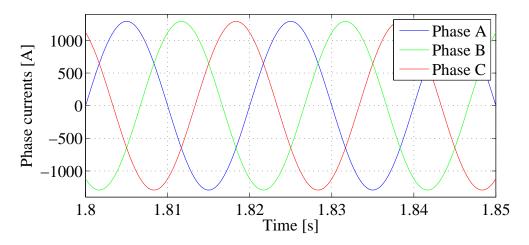

| 6.12 | Phase/grid currents under steady state conditions with pulsed DC load,   |      |

|      | when arm balancing method two is applied.                                | 133  |

| 6.13 | Phase/grid currents spectrum under steady state conditions with pulsed   |      |

|      | DC load, when arm balancing method two is applied                        | 133  |

| 6.14 | Phase/grid currents under steady state conditions with pulsed DC load,   |      |

|      | when arm balancing method three is applied                               | 134  |

| 6.15 | Phase/grid currents spectrum under steady state conditions with pulsed   |      |

|      | DC load, when arm balancing method three is applied. $\ldots$            | 135  |

| 6.16 | The converter energy controller waveforms during transient when the      |      |

|      | simulation starts.                                                       | 136  |

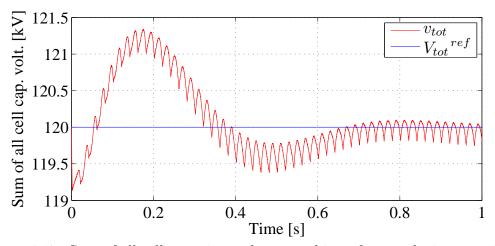

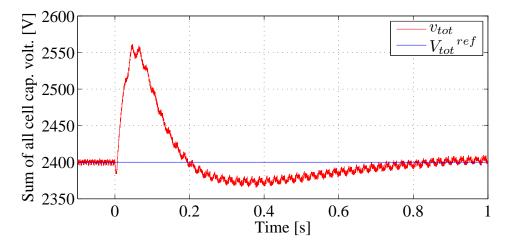

| 6.17 | Sum of all cell capacitor voltages and its reference during transient    |      |

|      | when the simulation starts                                               | 136  |

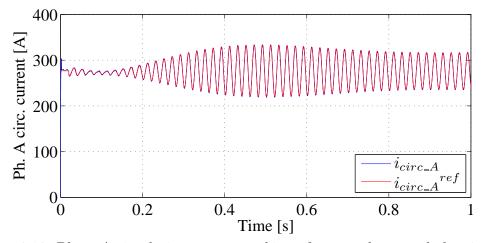

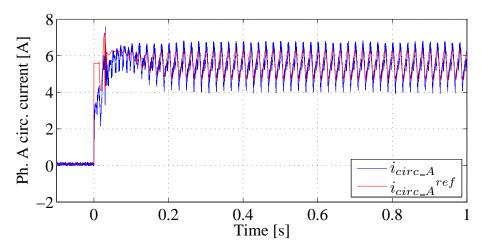

| 6.18 | Phase A circulating current and its reference when arm balancing         |      |

|      | method one is applied during transient when the simulation starts        | 137  |

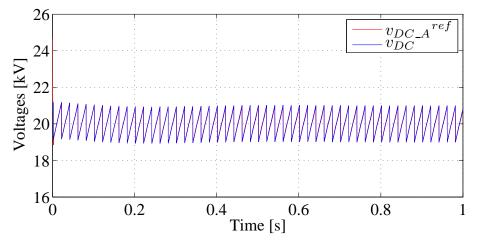

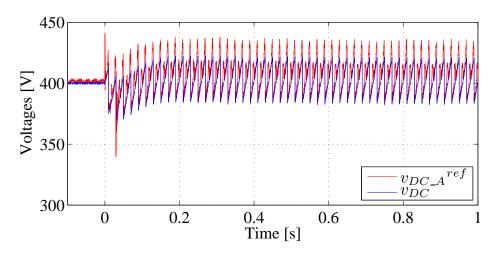

| 6.19 | Phase A DC part of the reference and DC voltage during transient         |      |

|      | when the simulation starts                                               | 138  |

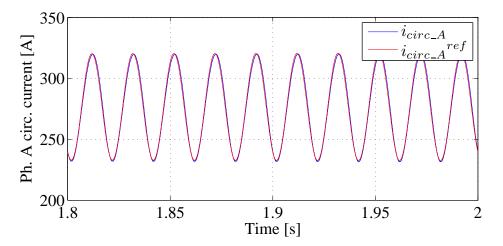

| 6.20 | Phase A circulating current and its reference under steady state con-    |      |

|      | ditions with pulsed DC load when arm balancing method one is applied     | .138 |

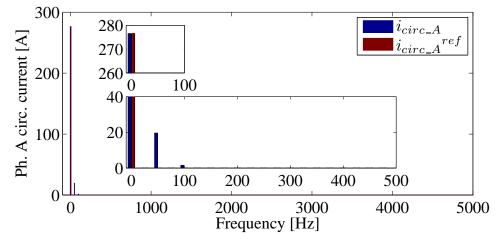

| 6.21 | Spectrum of the circulating current and its reference under steady state |      |

|      | conditions with pulsed DC load when arm balancing method one is applied. | 139  |

|      | аррисч                                                                   | 199  |

| 6.22 | Phase A circulating current and its reference under steady state con-<br>ditions with pulsed DC load when arm balancing method two is applied                                                   | .140 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 6.23 | Spectrum of the circulating current and its reference under steady state conditions with pulsed DC load when arm balancing method two is applied.                                               | 140  |

| 6.24 | Phase A circulating current and its reference under steady state condi-<br>tions with pulsed DC load when arm balancing method three is applied                                                 | .141 |

| 6.25 | Spectrum of the circulating current and its reference under steady state conditions with pulsed DC load when arm balancing method three is applied.                                             | 142  |

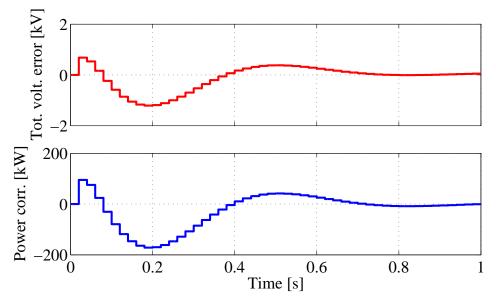

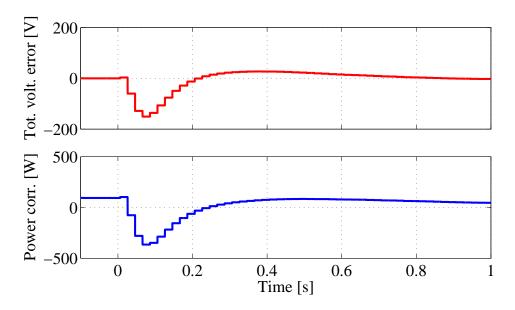

| 6.26 | DC voltage error and controller output correcting DC current reference during transient when simulation starts.                                                                                 | 142  |

| 6.27 | Converter DC voltage and its reference during transient when simula-<br>tion starts                                                                                                             | 143  |

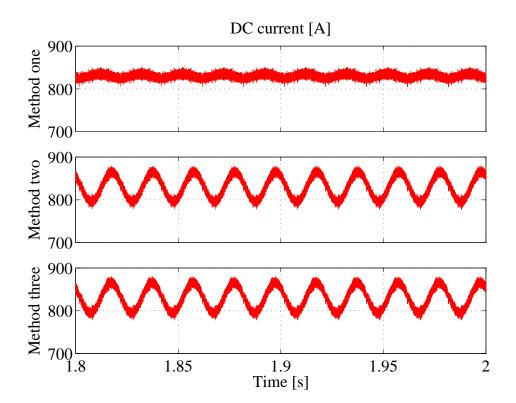

| 6.28 | Converter DC current under steady state conditions for three arm bal-<br>ancing methods                                                                                                         | 144  |

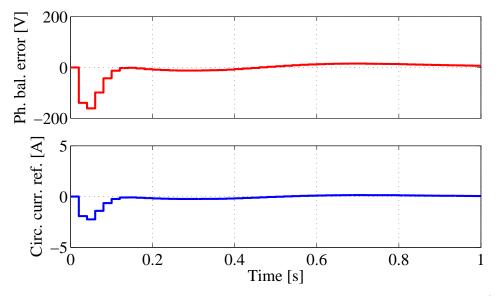

| 6.29 | Phase balancing error and controller output correcting phase A circulating current reference during transient when the simulation starts.                                                       | 145  |

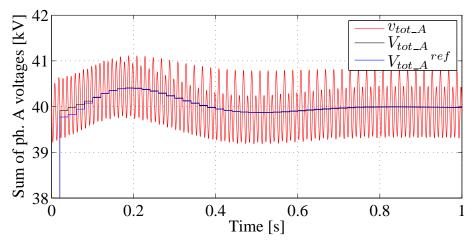

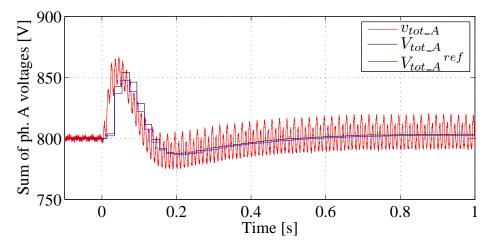

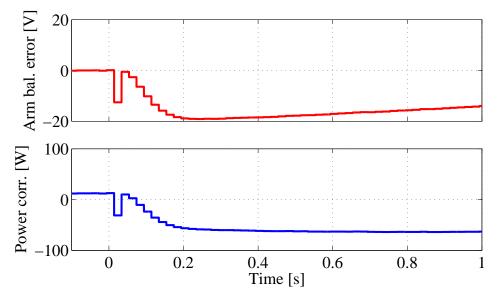

| 6.30 | Sum of the phase A cell capacitor voltages, average value and the reference during transient when the simulation starts                                                                         | 146  |

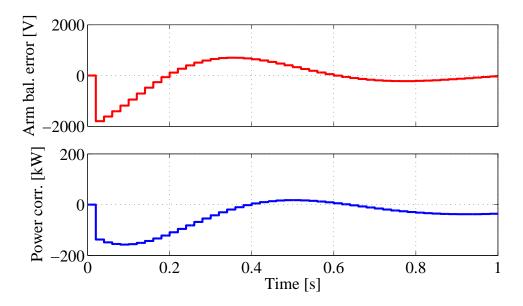

| 6.31 | Arm balancing error and controller output being the compensated<br>power used for generation of circulating current reference 50 Hz com-<br>ponent during transient when the simulation starts. | 146  |

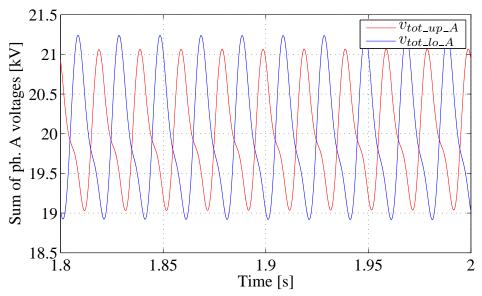

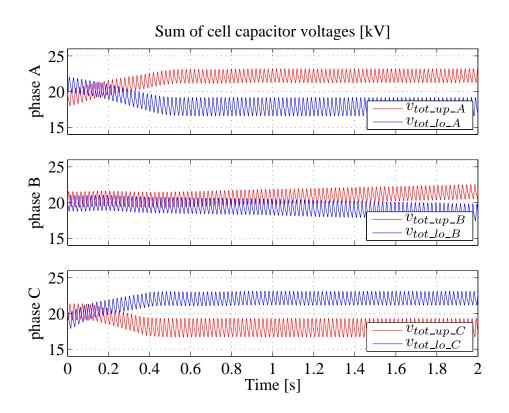

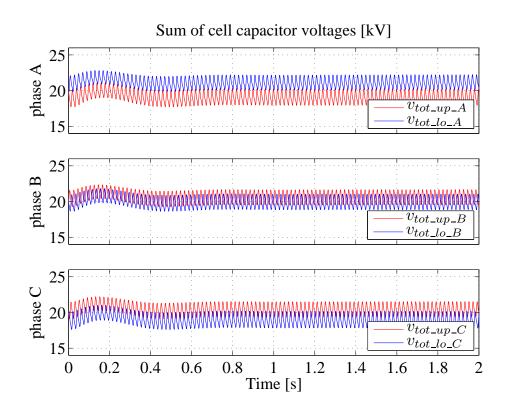

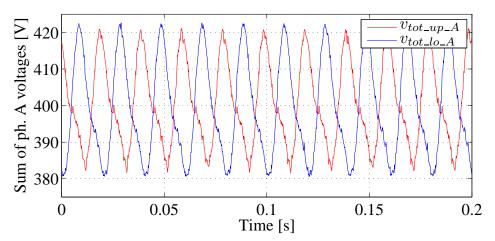

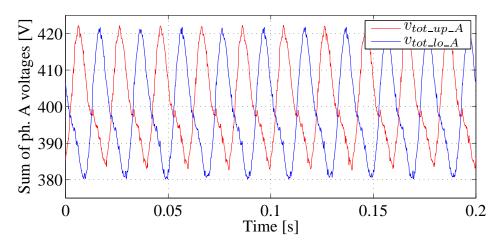

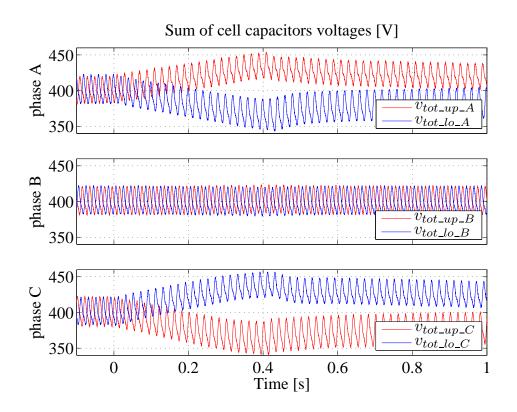

| 6.32 | Sum of the phase A upper arm and lower arm cell capacitor voltages<br>under steady state conditions when method one is applied                   | 147 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|

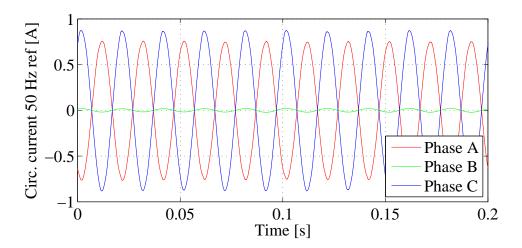

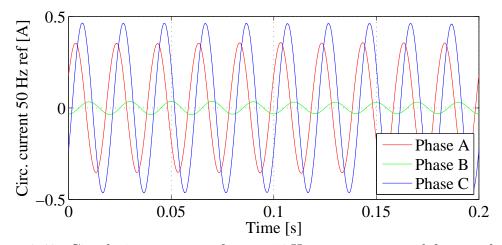

| 6.33 | Circulating current reference 50 Hz component used for arm balancing under steady state conditions when method one is applied. $\ldots$ $\ldots$ | 148 |

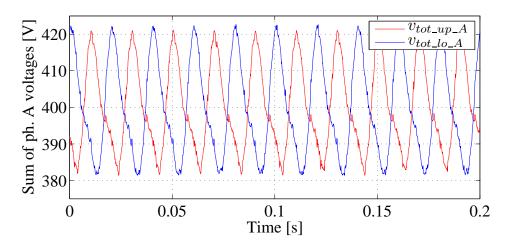

| 6.34 | Sum of the phase A upper arm and lower arm cell capacitor voltages<br>under steady state conditions when method two is applied                   | 149 |

| 6.35 | Circulating current reference 50 Hz component used for arm balancing under steady state conditions when method two is applied                    | 149 |

| 6.36 | Sum of the phase A upper arm and lower arm cell capacitor voltages<br>under steady state conditions when method three is applied                 | 150 |

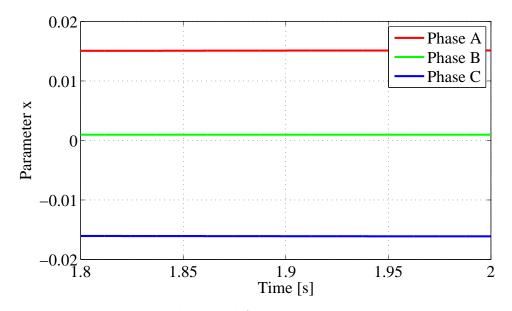

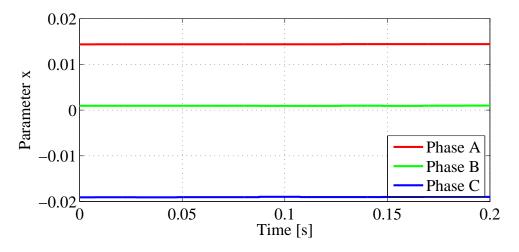

| 6.37 | Paramter $x$ values used for arm balancing in steady state when method three is applied                                                          | 151 |

| 6.38 | The sum of cell capacitor voltages of converter arms when arm balanc-<br>ing controller is disabled                                              | 152 |

| 6.39 | Phase voltages when the arm balancing controller is disabled                                                                                     | 153 |

| 6.40 | Phase voltages spectrum when the arm balancing controller is disabled.                                                                           | 153 |

| 6.41 | Phase/grid currents when the arm balancing controller is disabled                                                                                | 154 |

| 6.42 | Phase/grid currents spectrum when the arm balancing controller is disabled                                                                       | 155 |

| 6.43 | Converter AC power and its reference when arm balancing controller<br>is disabled                                                                | 155 |

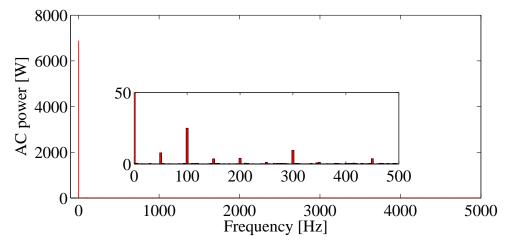

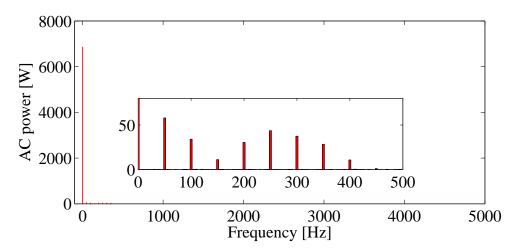

| 6.44 | Converter AC power harmonic spectrum when arm balancing controller is disabled                                                                   | 156 |

| 6.45 | The sum of cell capacitor voltages of converter arms when arm balanc-<br>ing controller is disabled                                                    | 157  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------|

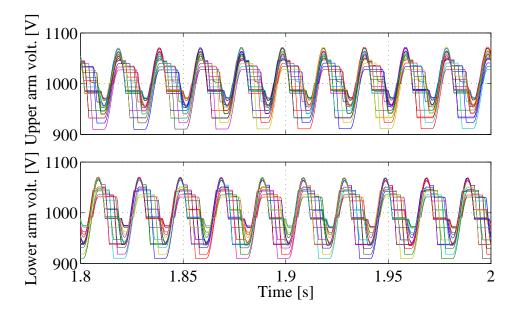

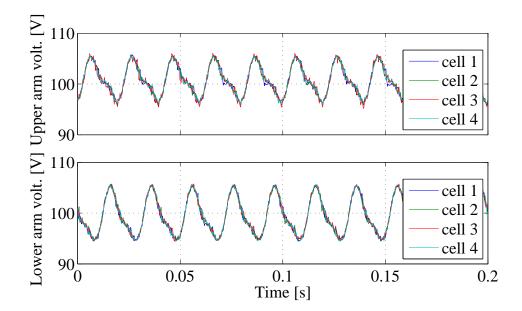

| 6.46 | Phase A cell capacitor voltages under steady state conditions                                                                                          | 158  |

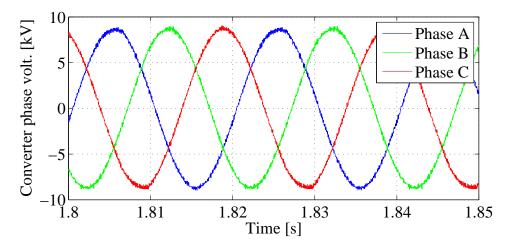

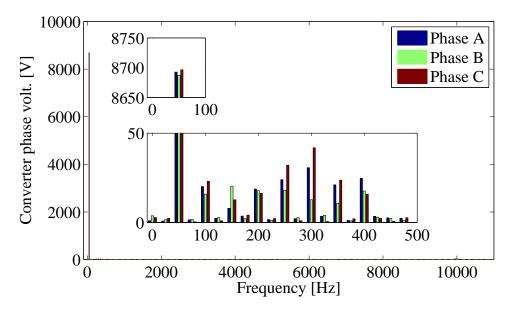

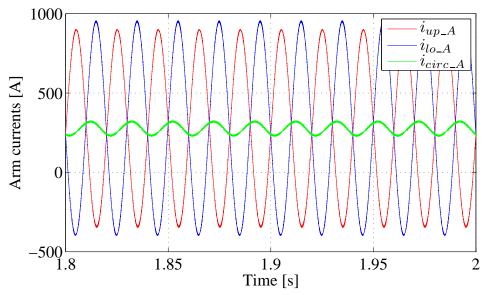

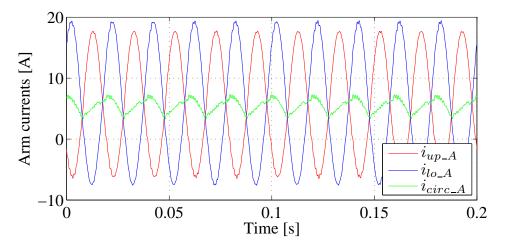

| 6.47 | Phase A arm currents and circulating current under steady state con-<br>ditions when arm balancing method one is applied                               | 159  |

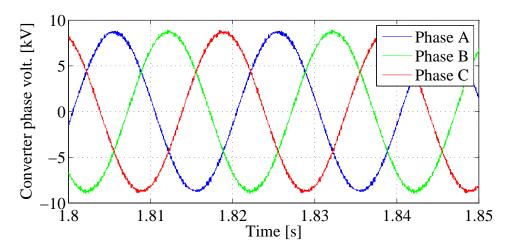

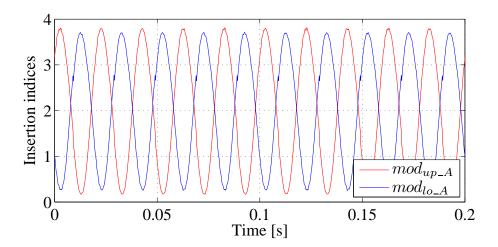

| 6.48 | Phase voltages under steady state conditions, when arm balancing method one is applied                                                                 | 159  |

| 6.49 | Phase voltages spectrum under steady state conditions, when arm bal-<br>ancing method one is applied.                                                  | 160  |

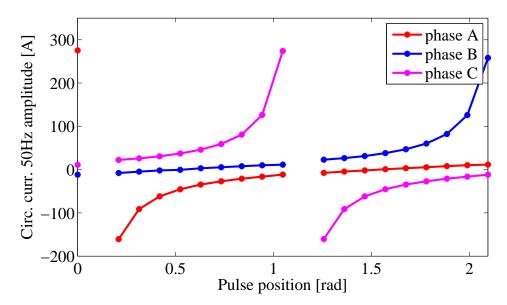

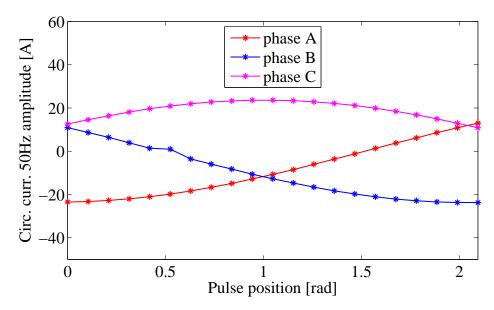

| 6.50 | Amplitude of the circulating current reference (assuming the phase angle lagging $\frac{\pi}{2}$ rad behind DC voltage ripple) vs. the pulse position. | 161  |

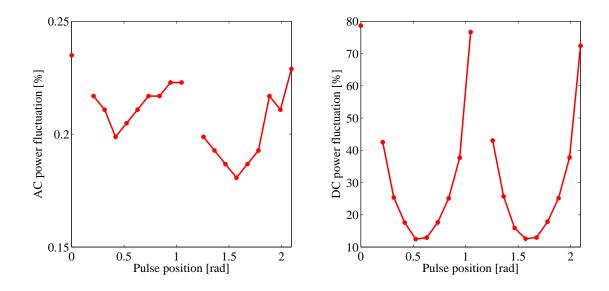

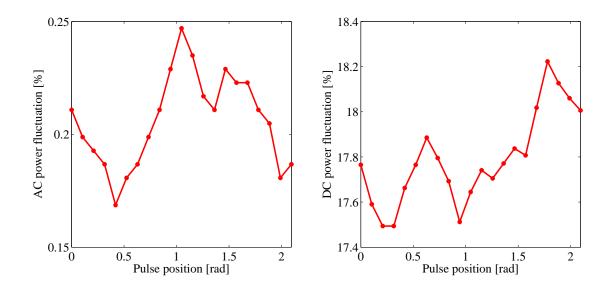

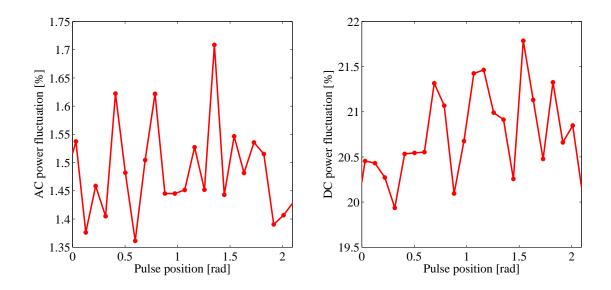

| 6.51 | AC and DC power fluctuation vs. the pulse position when the arm balancing method one is used                                                           | 162  |

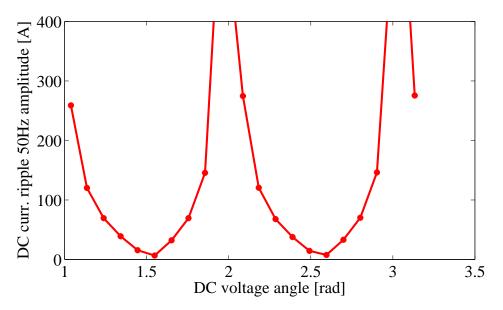

| 6.52 | The DC current ripple 50 Hz component ripple amplitude vs. the DC voltage ripple 50 Hz component angle when the arm balancing method one is applied    | 163  |

| 6.53 | Amplitude of the circulating current reference (assuming the phase<br>angle being the same as the AC voltage reference) vs. the pulse position         | .164 |

| 6.54 | AC and DC power fluctuation vs. the pulse position when the arm balancing method two is used                                                           | 165  |

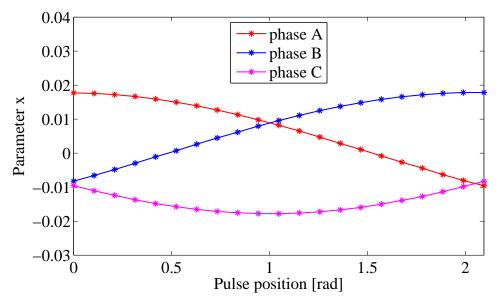

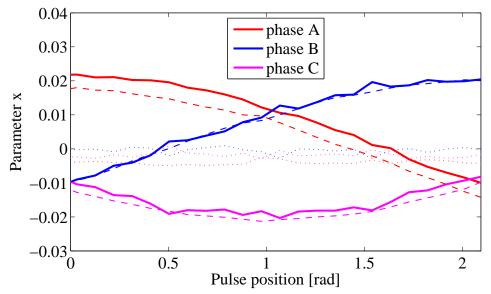

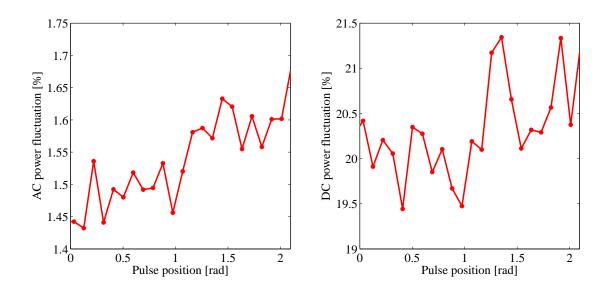

| 6.55 | Parmeter $x_{A,B,C}$ vs. the pulse position                                                                                                            | 165  |

| 6.56 | AC and DC power fluctuation vs. the pulse position when the arm balancing method three is used.                                                        | 166  |

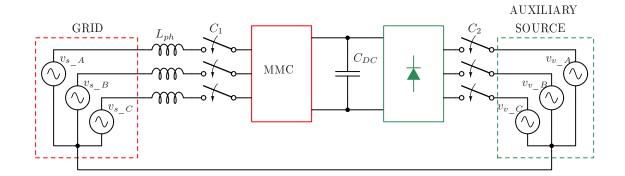

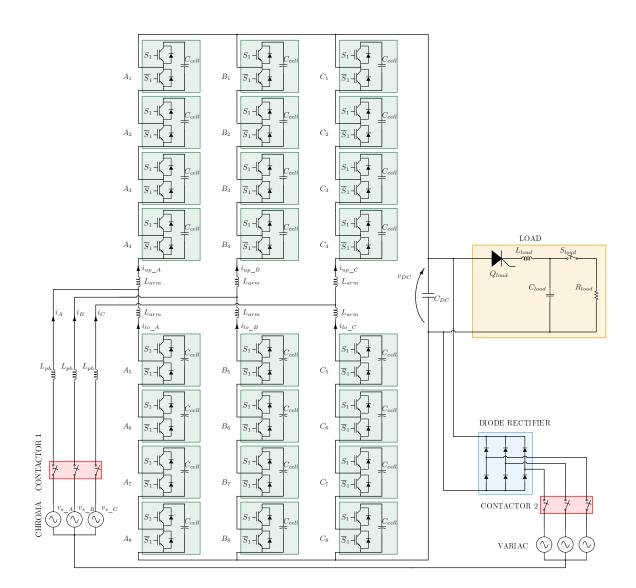

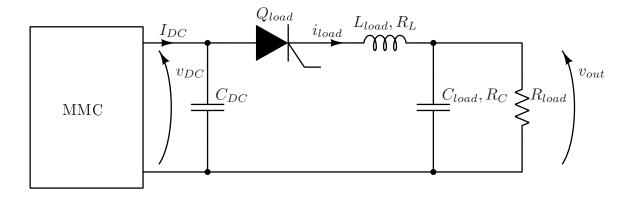

| 7.1  | Schematics of the experimental prototype                                                         | 170 |

|------|--------------------------------------------------------------------------------------------------|-----|

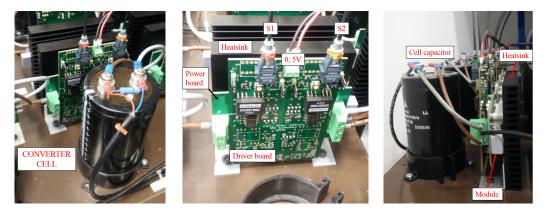

| 7.2  | One half-bridge converter cell                                                                   | 171 |

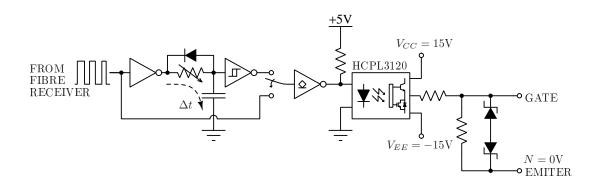

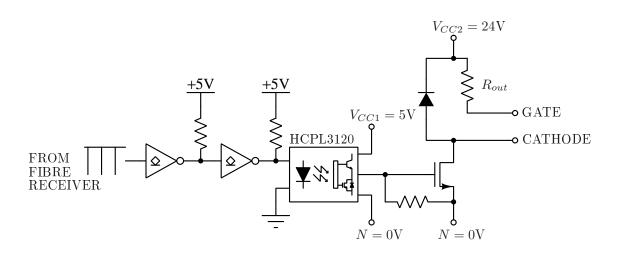

| 7.3  | Gate drive schematics used for gating the cell switches                                          | 172 |

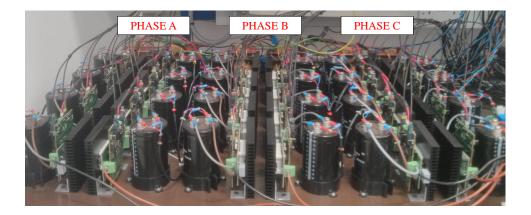

| 7.4  | Photographs of the one converter phase                                                           | 173 |

| 7.5  | Photograph of the three-phase MMC                                                                | 173 |

| 7.6  | Resonant pulsed load design                                                                      | 174 |

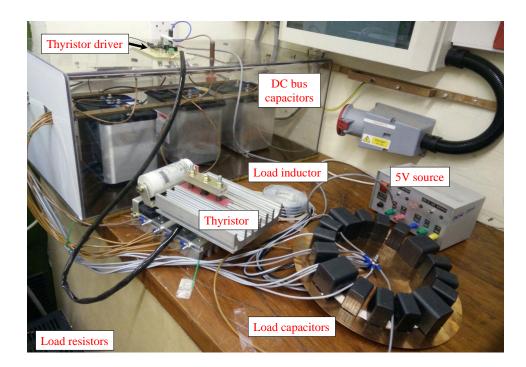

| 7.7  | Pulsed load experimental prototype                                                               | 177 |

| 7.8  | Thyristor gate drive schematics                                                                  | 178 |

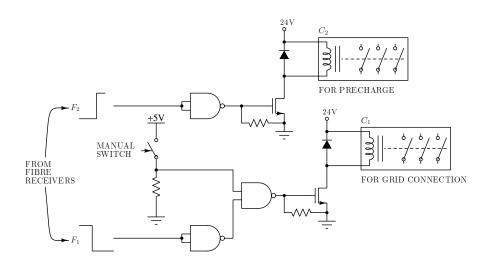

| 7.9  | Contactor control circuit                                                                        | 179 |

| 7.10 | An example of the data acquisition PCB                                                           | 181 |

| 7.11 | LV 25-P voltage transducer application circuit                                                   | 182 |

| 7.12 | LA 55-P current transducer application circuit.                                                  | 183 |

| 7.13 | FPGA board designed within PEMC research group                                                   | 184 |

| 7.14 | FIFO based vector for PWM signal generation in the case of phase A.                              | 185 |

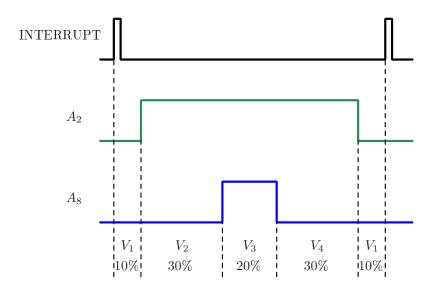

| 7.15 | PWM vectors generation in the case of modulation indices 0.8 and 3.2.                            | 186 |

| 7.16 | DSP board C6713 DSK by Texas Instruments together with the HPI Daughtercard from Educational DSP | 188 |

| 7.17 | Structure of the ISR algorithm.                                                                  | 190 |

| 8.1  | Grid voltages and phase angle when AC waveforms output is enabled<br>in controlled precharge mode.                      | 196 |

|------|-------------------------------------------------------------------------------------------------------------------------|-----|

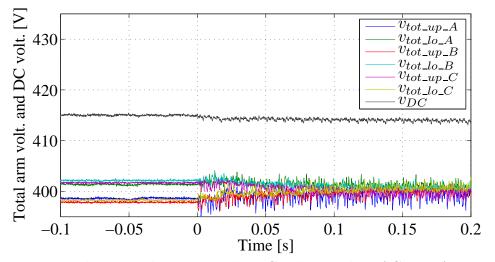

| 8.2  | Total arms voltages and the DC voltage when AC waveforms output<br>is enabled in controlled precharge mode              | 197 |

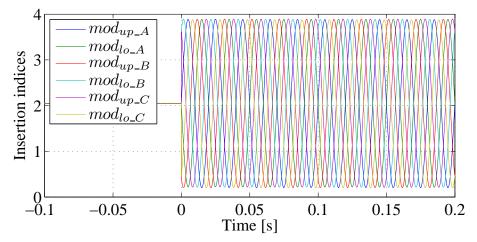

| 8.3  | Insertion indices for all converter arms when AC waveforms output is<br>enabled in controlled precharge mode            | 198 |

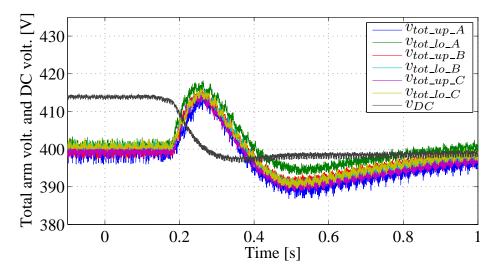

| 8.4  | Total arms voltages and the DC voltage when synchronisation to the grid is enabled.                                     | 198 |

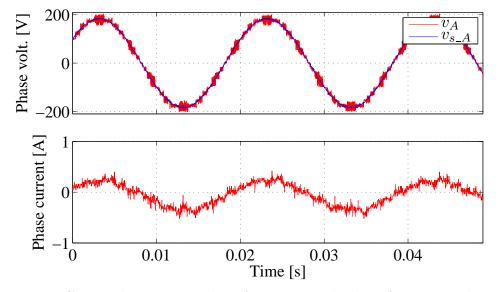

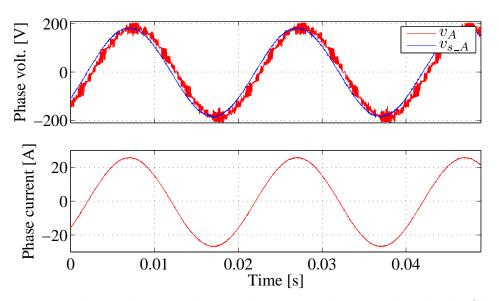

| 8.5  | Grid and converter phase A voltage and phase A current when converter is synchronised to the grid in no-load condition. | 199 |

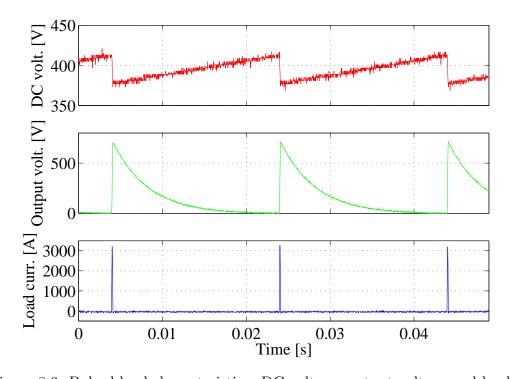

| 8.6  | Pulsed load characteristics: DC voltage, output voltage and load cur-<br>rent under steady state conditions.            | 200 |

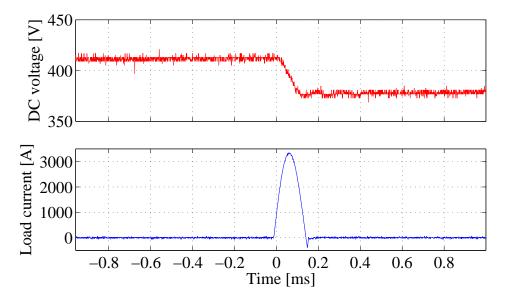

| 8.7  | Pulsed load characteristics: DC voltage and load current, with the focus on one current pulse                           | 200 |

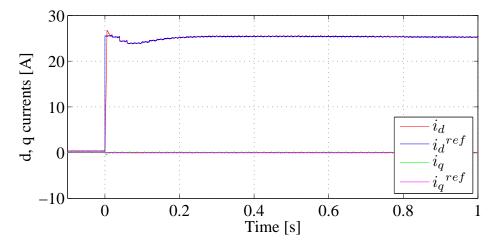

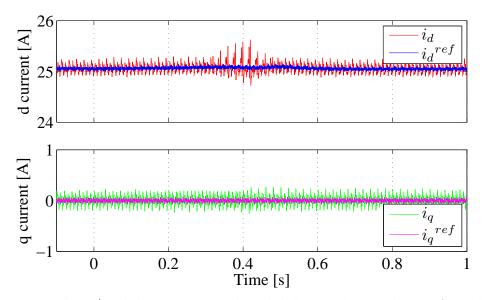

| 8.8  | The $d, q$ current controller reference tracking during transient when pulsed load is enabled                           | 201 |

| 8.9  | Grid voltage and the converter AC voltage $d$ , $q$ components during transient when pulsed load is enabled.            | 202 |

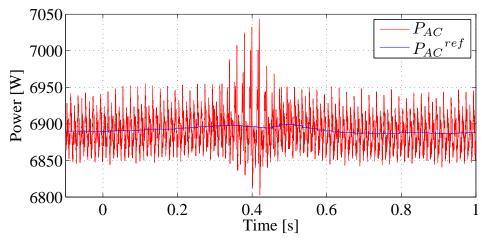

| 8.10 | Grid active power and its reference, during transient when pulsed load is enabled                                       | 203 |

| 8.11 | The $d, q$ current controller reference tracking under steady state con-<br>ditions with pulsed load                    | 203 |

| 8.12 | Grid active power and its reference and the converter DC power under steady state conditions with pulsed load. | 204 |

|------|----------------------------------------------------------------------------------------------------------------|-----|

| 8.13 | Grid active power harmonics under steady state conditions with pulsed load.                                    | 205 |

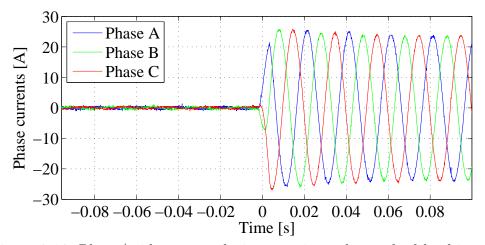

| 8.14 | Phase/grid currents during transient when pulsed load is enabled                                               | 205 |

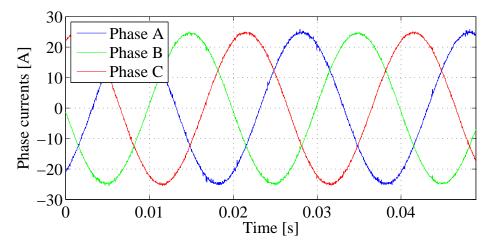

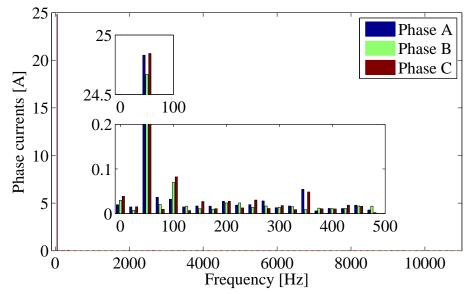

| 8.15 | Phase/grid currents in steady state under pulsed DC load, when arm balancing method one is applied.            | 206 |

| 8.16 | Phase/grid currents spectrum in steady state under pulsed DC load, when arm balancing method one is applied.   | 207 |

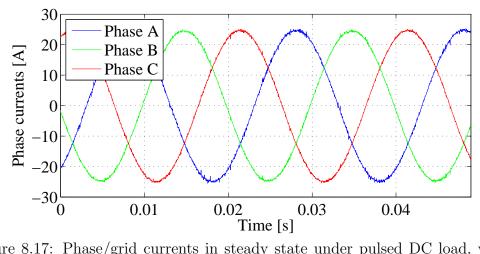

| 8.17 | Phase/grid currents in steady state under pulsed DC load, when arm balancing method two is applied.            | 208 |

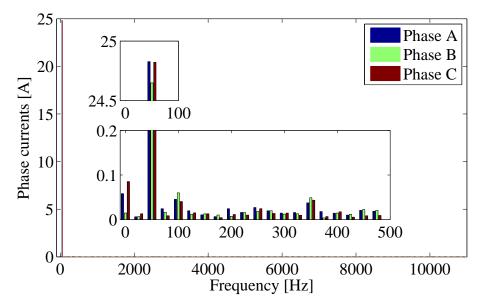

| 8.18 | Phase/grid currents spectrum in steady state under pulsed DC load, when arm balancing method two is applied.   | 208 |

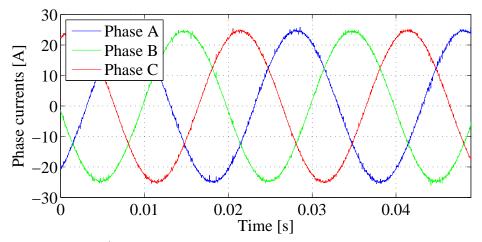

| 8.19 | Phase/grid currents in steady state under pulsed DC load, when arm balancing method three is applied.          | 209 |

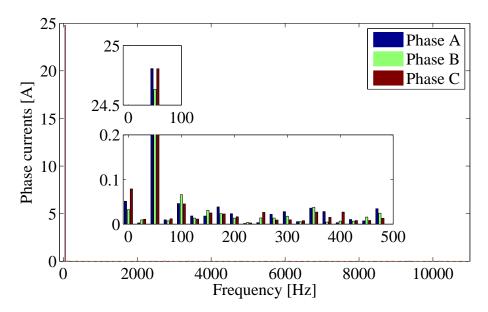

| 8.20 | Phase/grid currents spectrum in steady state under pulsed DC load, when arm balancing method three is applied  | 209 |

| 8.21 | The converter energy controller waveforms during transient when pulsed load is enabled.                        | 210 |

| 8.22 | Sum of all cell capacitor voltages and its reference during transient when pulsed load is enabled              | 211 |

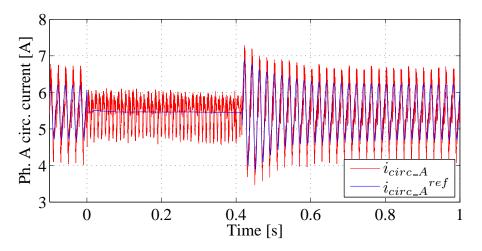

| 8.23 | Phase A circulating current and its reference during transient when pulsed load is enabled.                    | 212 |

| 8.24 | Phase A DC part of the reference and DC voltage during transient<br>when pulsed load is enabled                                                          | 212 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

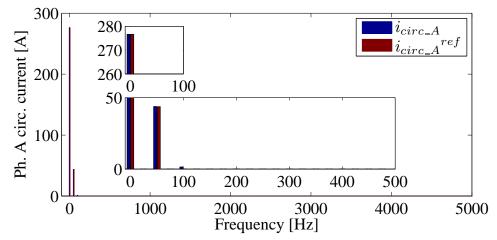

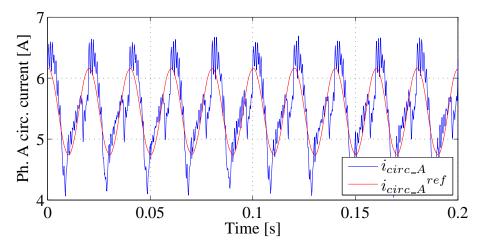

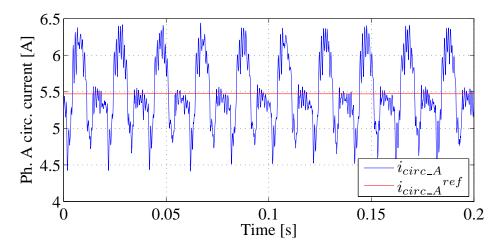

| 8.25 | Phase A circulating current and its reference under steady state con-<br>ditions with pulsed DC load when arm balancing method one is applied.2          | 214 |

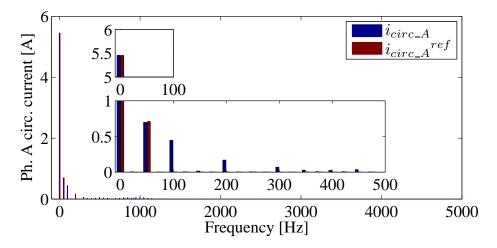

| 8.26 | Spectrum of the circulating current and its reference under steady state conditions with pulsed DC load when arm balancing method one is applied.        | 214 |

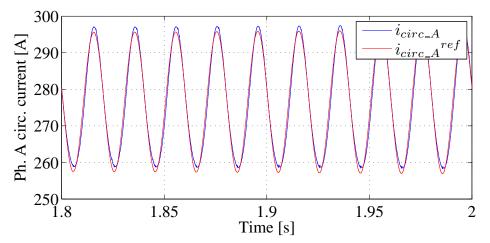

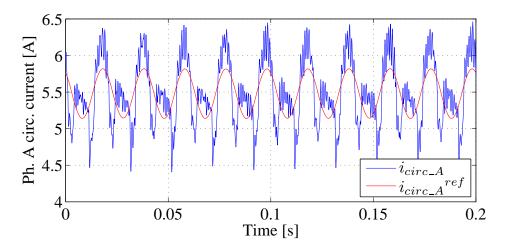

| 8.27 | Phase A circulating current and its reference under steady state con-<br>ditions with pulsed DC load when arm balancing method two is applied.2          | 215 |

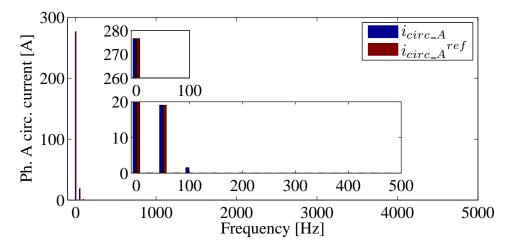

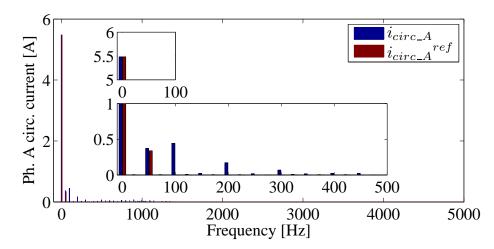

| 8.28 | Spectrum of the circulating current and its reference under steady state<br>conditions with pulsed DC load when arm balancing method two is<br>applied   | 215 |

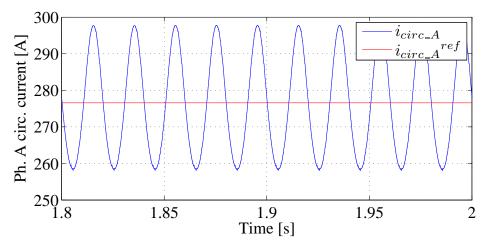

| 8.29 | Phase A circulating current and its reference under steady state condi-<br>tions with pulsed DC load when arm balancing method three is applied.2        | 216 |

| 8.30 | Spectrum of the circulating current and its reference under steady state<br>conditions with pulsed DC load when arm balancing method three is<br>applied | 217 |

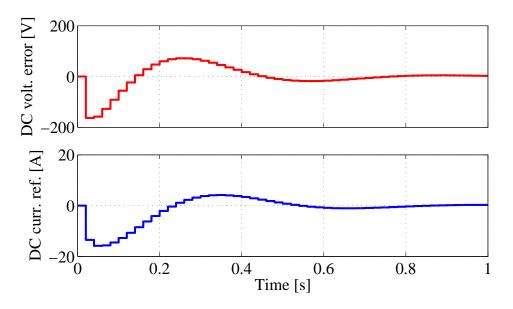

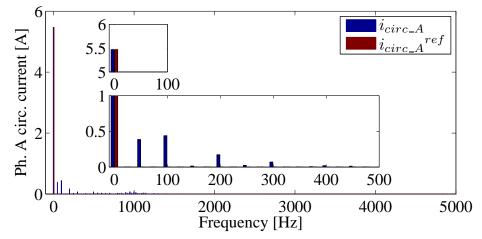

| 8.31 | DC voltage error and controller output correcting DC current reference<br>during transient when pulsed load is enabled.                                  | 217 |

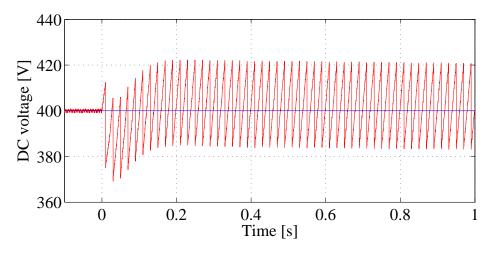

| 8.32 | Converter DC voltage and its reference during transient when pulsed load is enabled                                                                      | 218 |

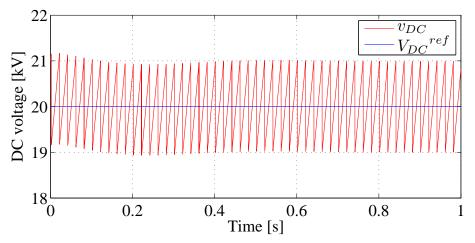

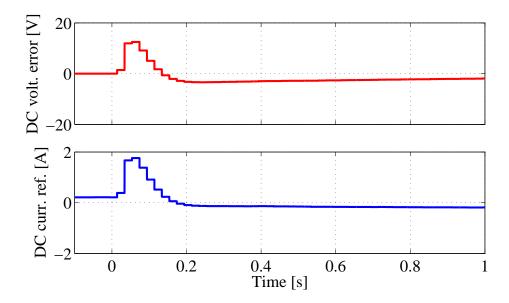

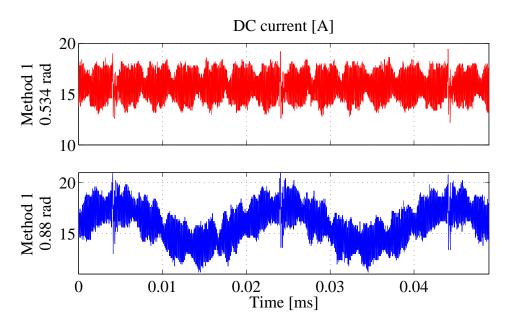

| 8.33 | DC currents under steady state conditions with pulsed load for pulse positions of 0.534 rad and 0.88 rad when arm balacing method one is applied.        | 219 |

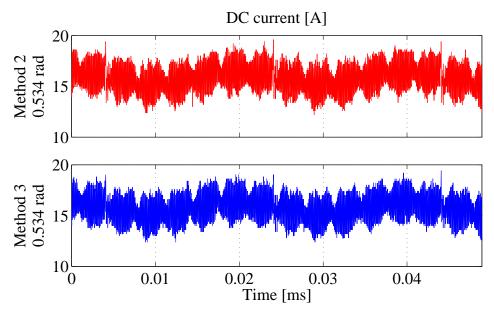

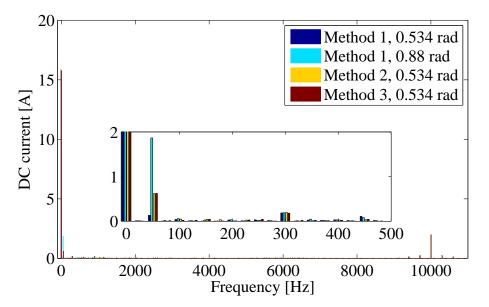

| 8.34 | DC currents under steady state conditions with pulsed load (pulse position is 0.534 rad) for arm balancing methods two and three                | 220 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 8.35 | DC current harmonics comparison for different arm balancing methods.                                                                            | 220 |

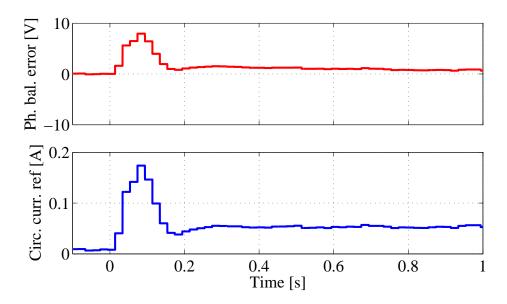

| 8.36 | Phase balancing error and controller output correcting phase A circu-<br>lating current reference during transient when pulsed load is enabled. | 221 |

| 8.37 | Sum of the phase A cell capacitor voltages, average value and a reference during transient when pulsed load is enabled                          | 222 |

| 8.38 | Arm balancing error and controller output being balancing power be-<br>tween arms of phase A during transient when pulsed load is enabled.      | 223 |

| 8.39 | Sum of the phase A upper arm and lower arm cell capacitor voltages<br>under steady state conditions when method one is applied                  | 224 |

| 8.40 | Circulating current reference 50 Hz component used for arm balancing under steady state conditions when method one is applied                   | 225 |

| 8.41 | Sum of the phase A upper arm and lower arm cell capacitor voltages<br>under steady state conditions when method two is applied                  | 225 |

| 8.42 | Circulating current reference 50 Hz component used for arm balancing under steady state conditions when method two is applied. $\ldots$ .       | 226 |

| 8.43 | Sum of the phase A upper arm and lower arm cell capacitor voltages<br>under steady state conditions when method three is applied                | 227 |

| 8.44 | Paramter $x$ values used for arm balancing under steady state conditions<br>when method three is applied                                        | 227 |

| 8.45 | Sum of the upper arm and lower arm cell capacitor voltages when disabling and re-enabling of arm balancing controller is done                   | 229 |

| 8.46 | Phase/grid $d$ , $q$ currents when disabling and re-enabling of arm bal-<br>ancing controller is done                                                        | 230 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 8.47 | AC power and its reference when disabling and re-enabling of arm balancing controller is done                                                                | 231 |

| 8.48 | Phase A circulating current when disabling and re-enabling of arm balancing controller is done                                                               | 231 |

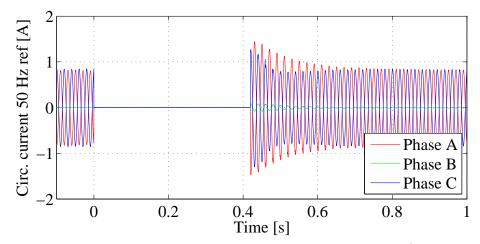

| 8.49 | Circulating currents 50 Hz component references (in the case of arm balancing method one) when disabling and re-enabling of arm balancing controller is done | 232 |

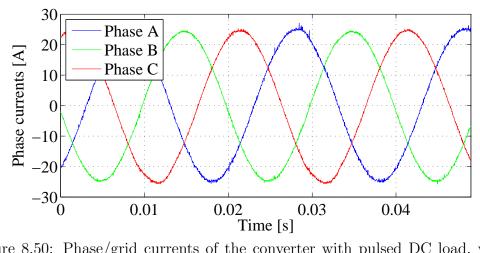

| 8.50 | Phase/grid currents of the converter with pulsed DC load, when arm balancing is disabled                                                                     | 233 |

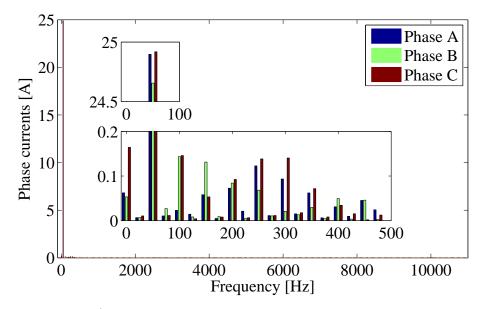

| 8.51 | Phase/grid currents spectrum of the converter with pulsed DC load when arm balancing is disabled                                                             | 233 |

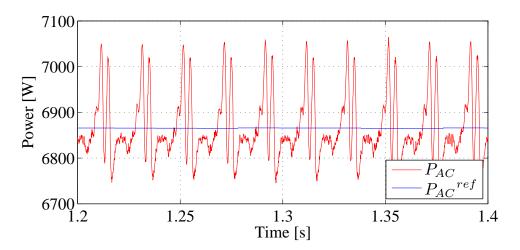

| 8.52 | Grid active power and its reference, under steady state conditions with pulsed load when arm balancing is disabled.                                          | 234 |

| 8.53 | Grid active power harmonics, under steady state conditions with pulsed load when arm balancing is disabled.                                                  | 234 |

| 8.54 | Phase A cell capacitor voltages under steady state conditions                                                                                                | 235 |

| 8.55 | Phase A arm currents and circulating current under steady state con-<br>ditions when arm balancing method one is applied                                     | 236 |

| 8.56 | Phase A upper and lower arm insertion indices under steady state conditions when arm balancing method one is applied                                         | 236 |

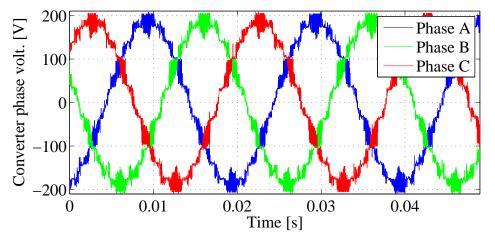

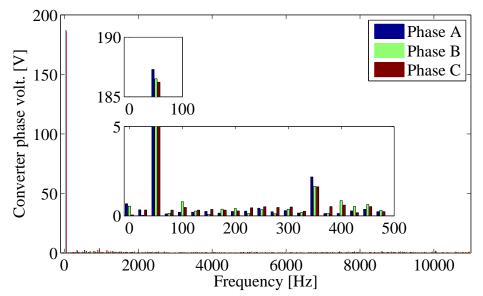

| 8.57 | Phase voltages under steady state conditions with pulsed DC load, when arm balancing method one is applied.                                                                                                   | 237  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 8.58 | Phase voltages spectrum under steady state conditions with pulsed DC load, when arm balancing method one is applied.                                                                                          | 238  |

| 8.59 | Phase voltages under steady state conditions with pulsed DC load, when arm balancing method one is applied.                                                                                                   | 238  |

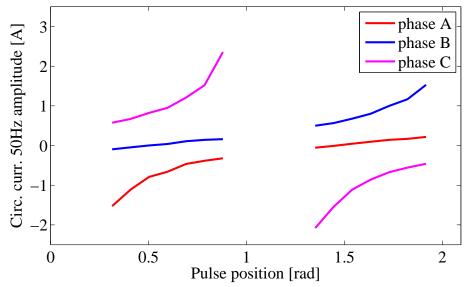

| 8.60 | Amplitude of the circulating current reference (assuming the phase angle lagging $\frac{\pi}{2}$ rad behind DC voltage ripple) vs. the pulse position.                                                        | 241  |

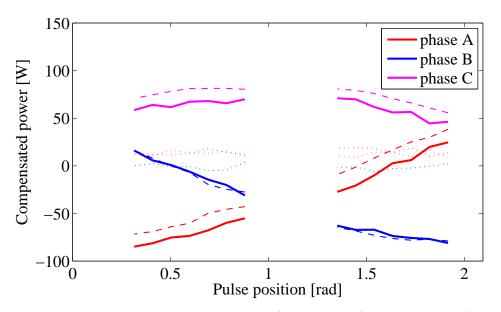

| 8.61 | Balancing power before pulse (dotted lines), during pulse (dashed lines) and the difference (full line associated with the pulsed load only) vs. the pulse position when the arm balancing method one is used | 241  |

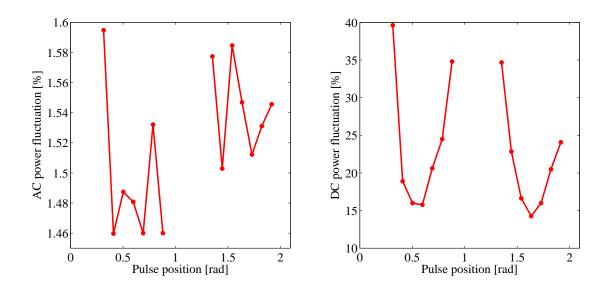

| 8.62 | AC and DC power fluctuation vs. the pulse position when the arm balancing method one is used                                                                                                                  | 242  |

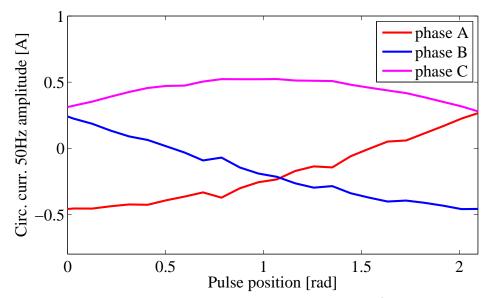

| 8.63 | Amplitude of the circulating current reference (assuming the phase<br>angle being the same as the AC voltage reference) vs. the pulse position                                                                | .243 |

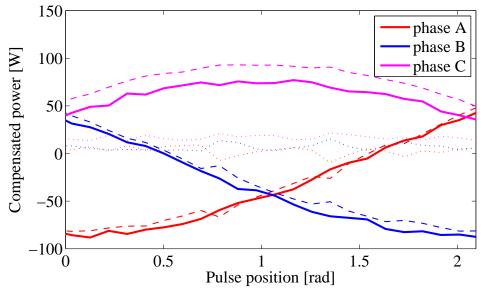

| 8.64 | Balancing power before pulse (dotted lines), during pulse (dashed lines) and the difference (full line associated with the pulsed load only) vs. the pulse position when the arm balancing method two is used | 244  |

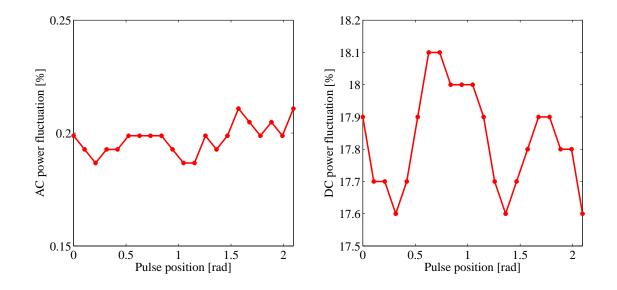

| 8.65 | AC and DC power fluctuation vs. the pulse position when the arm balancing method two is used                                                                                                                  | 245  |

| 8.66 | Parmeter $x_{A,B,C}$ before pulse (dotted lines), during pulse (dashed lines)<br>and the difference (full line associated with the pulsed load only) vs.<br>the pulse position.                               | 246  |

| 8.67 | AC and DC power fluctuation vs. the pulse position when the arm                                                          |     |

|------|--------------------------------------------------------------------------------------------------------------------------|-----|

|      | balancing method three is used                                                                                           | 246 |

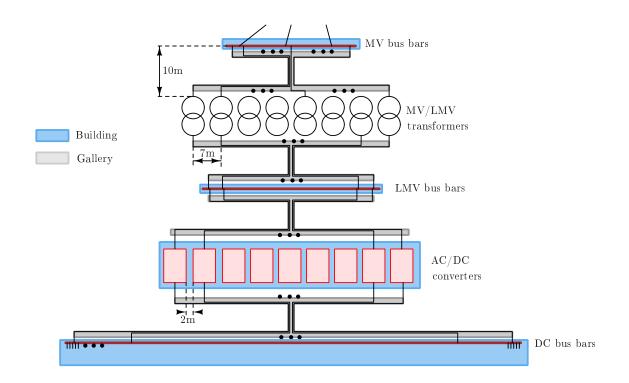

| A.1  | One sector spatial distribution and civil engineering infrastructure                                                     | 275 |

| A.2  | MMC converter physical model                                                                                             | 277 |

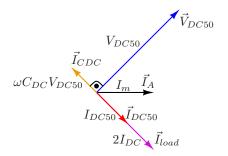

| B.1  | Equivalent vector diagram for the 50 Hz component of the DC link related waveforms when arm balancing method one is used | 281 |

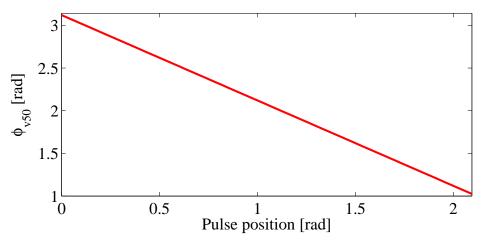

| B.2  | DC voltage ripple 50 Hz component phase angle vs. the pulse position in the case of arm balancing method one             | 282 |

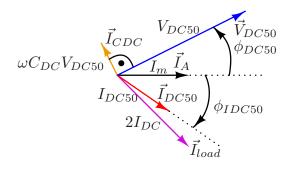

| B.3  | Equivalent vector diagram for the 50 Hz component of the DC link related waveforms when arm balancing method two is used | 283 |

| B.4  | DC current ripple 50 Hz component vs. the DC voltage ripple phase angle in the case of arm balancing method two.         | 284 |

## List of Tables

| 1.1 | Parameters of klystron modulators                                       | 5   |

|-----|-------------------------------------------------------------------------|-----|

| 1.2 | Parameters of the grid (EDF) $\ldots$                                   | 5   |

| 3.1 | Cable and switchgear voltage ratings                                    | 27  |

| 3.2 | Possibilities for the power system voltage ratings                      | 33  |

| 3.3 | Maximum fault currents depending on the fault type                      | 37  |

| 3.4 | Break down of the overal power system losses                            | 49  |

| 3.5 | Modular multilevel converter ratings                                    | 52  |

| 5.1 | Amplitudes and phase angles of 50 Hz components                         | 100 |

| 6.1 | Simulation model parameters                                             | 121 |

| 6.2 | Controller gains used for the purpose of verification by simulation     | 122 |

| 7.1 | Load parameters measured at 1 kHz                                       | 176 |

| 7.2 | Controller gains used for the purpose of the experimental rig control . | 192 |

|     |                                                                         |     |

B.1 Amplitudes and phase angles of AC waveforms and DC voltage. . . . 280

# Chapter 1

# Introduction

### **1.1** Motivation for the research project

Scientists at the European Organization for Nuclear Research (french: Conseil Europeen pour la Recherche Nucleaire, CERN) are aiming to achieve higher energy particle collisions in order to produce the basic constituents of matter - the fundamental particles. This requires building high-luminosity colliders that usually process very high input powers in order to achieve the required centre-off-mass energy collisions. Processing high powers demands very efficient, high availability power electronics. In addition, acceleration cavities often require pulsed power sources, and the grid interface power electronics in that case ideally acts as a firewall, blocking the effect of the pulsed operation from reaching and impacting the electricity network.

#### **1.1.1** Compact linear collider

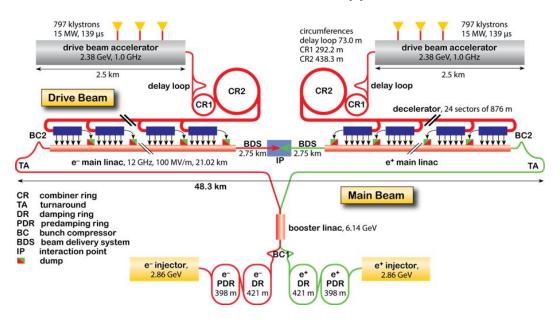

The Compact linear collider (CLIC) is a high energy linear accelerator under feasibility study at CERN [3]. It is aimed for high-luminosity electron-positron collisions reaching the centre-of-mass energy of 3 TeV. Achieving high collision energy requires high acceleration gradients, that are in the case of CLIC provided by a two-beam acceleration principle [3, 4]. This principle requires a drive beam that runs through the power extraction and transfer structures, producing high radio frequency (RF) power pulses used for the main beam acceleration. The drive beam is usually accelerated in a traditional way, i.e. by klystrons, reaching the energies of a couple of GeV. The initial layout of the CLIC is presented in Fig. 1.1. In order to reach the energy of 3 TeV two main beams are placed in approximately 50 km long tunnel, while two drive beams are required for their acceleration. Drive beams are 2 - 2.5 km long and their parallel placement gives an opportunity to place the klystrons used for acceleration of the both beams along 2 - 2.5 km, as suggested in [5].

Figure 1.1: Initial CLIC layout overview aimed for 3 TeV centre-of-mass energy. The figure is taken from [1].

Klystrons are the most efficient linear acceleration tubes, using DC voltage to accelerate electrons that are modulated by an RF sinusoidal signal [6]. In order to reduce the power consumption, klystrons aimed for the drive beam acceleration are operated with a pulsed supply instead of the DC voltage [7]. Therefore, the drive beam klystrons require short, high voltage pulses, with the very tight specifications on the pulse quality (flat top stability, rise and fall times, etc.) as given in [4]. The drive beams acceleration power is therefore pulsed in nature, with a 39 GW peak power for  $140 \,\mu$ s of pulse length and a repetition rate of 50 Hz [4].

Initially, as presented in Fig. 1.1, approximately 1600 klystrons were required to accelerate both drive beams. During the scope of this research, the klystron supply voltage was re-optimised and new pulse parameters [8] were obtained. The new parameters indicate the peak pulse power of nearly 29 MW per klystron, which reduced the required number of klystrons to approximately 13 hundred in total.

Klystron modulators are used to produce a voltage pulse to be applied at each klystron. In the CLIC application the output pulse voltage is approximately 180 kV. The input modulator voltage is usually in the medium voltage range (1-35 kV), requiring a modulator ability to step-up voltage. In [4] various modulator topologies are considered, but considering the pulse rise and fall times, as well as the quality of the flat top, the solutions with a pulsed transformer are the most preferable. This topology comprises a capacitor bank which is discharged through a high voltage pulse transformer via the use of a solid state switch [4].

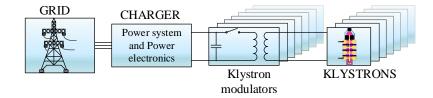

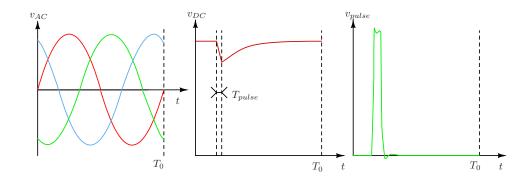

# 1.1.2 Requirements for the grid interface to the klystron modulators

The grid interface of klystron modulators should recharge the capacitor banks between pulses and ensure that a constant average power of approximately 280 MW is drawn from the grid despite the pulsed nature of the klystron modulators. The grid interface (charger) to approximately 1300 klystron modulators is presented in Fig. 1.2. The expected grid voltage, capacitors bank voltage  $v_{DC}$  and the modulator output voltage for the system presented in Fig. 1.2 are shown in Fig. 1.3.

The klystron modulators draw a short high current pulse when the solid state switch is closed and the capacitor voltage is transferred to the primary winding of the pulse

Figure 1.2: Grid interface to the drive beam klystron modulators.

Figure 1.3: From left to right: the expected grid voltage, DC voltage and the final modulator voltage.

transformer. The pulse current causes a voltage droop on the main capacitor bank voltage  $v_{DC}$ , which requires a compensation to avoid the presence of the voltage droop on the transformer secondary side. Without this compensation the droop would have an adverse effect on the output pulse flat top stability. The voltage droop compensation is carried out on the primary side of the transformer, by a high bandwidth active bouncer [9] capable of compensating a maximum voltage droop of 1 kV which is between 5% and 20% of the nominal DC voltage [4]. The parameters of the klystron modulator are given in Table 1.1. The repetition rate of the pulses indicates the presence of the 50 Hz component in the DC voltage ripple.

CERN uses the French electricity provider (french: Electricite de France, EDF) grid connection at the transmission voltage level with the grid parameters given in Table 1.2. The grid connection is approximately 500 m away from the klystron modulators,

| Parameter                  | Label            | Value  |

|----------------------------|------------------|--------|

| Nominal DC voltage [kV]    | $V_{DC}$         | 5 - 20 |

| Maximum voltage droop [kV] | $\Delta V^{max}$ | 1      |

| Peak pulsed power [MW]     | $P_{peak}$       | 29     |

| Pulse duration $[\mu s]$   | $T_{pulse}$      | 140    |

| Repetition rate [Hz]       | $f_{rep}$        | 50     |

Table 1.1: Parameters of klystron modulators

distributed along 2 - 2.5 km. The design of a dedicated power system is required to meet the connection requirements at both grid and modulator side, while maximising the overal efficiency and availability [4, 5].

Achieving low AC power fluctuation (bellow 2%, Table 1.2) is one of the biggest challenges for the power electronics used as a grid interface to the klystron modulators, considering their synchronous pulsation with the total peak power of nearly 39 GW.

Table 1.2: Parameters of the grid (EDF)

| Parameter                     | Value |

|-------------------------------|-------|

| Grid voltage [kV]             | 400   |

| Available power [MW]          | 400   |

| Maximum fault power [MVA]     | 14000 |

| Resistance/reactance ratio    | 0.07  |

| Zero sequence impedance ratio | 0.822 |

| Power fluctuation [%]         | <2    |

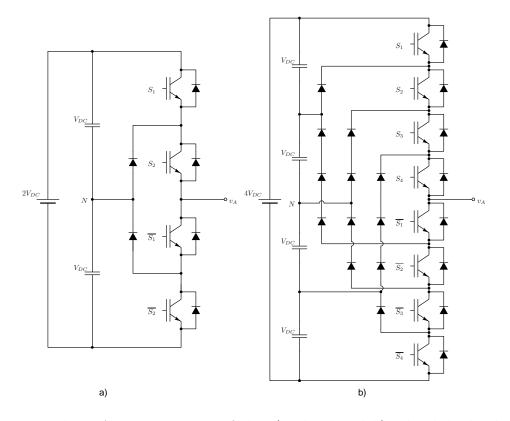

The voltage droop (at the capacitor bank) is limited by selection of the appropriate capacitance of the capacitor bank, which is already attenuating power fluctuation at the DC side by 80-90 % [5]. Grid interface power electronics used as a charger of the capacitor bank should be able to further suppress pulsed effects in order to achieve low AC power fluctuation. Considering the voltage ratings and the requirement for high efficiency and good AC waveform quality, multilevel topologies are foreseen as being more suitable than the standard 2-level topologies [5, 7].

### 1.2 **Project objectives**

Based on the presented challenges from the previous section, the objectives of the research work addressed in this thesis are defined. The main project objectives are following:

- Review existing multilevel topologies and discuss their benefits and drawbacks for the CLIC application. This includes both AC/DC and DC/DC topologies.

- Analyse different power system design architectures in order to meet all the requirements and design practices at CERN. The selection of the power system layout is coupled with the converter topology selection.

- Perform an optimisation of the power system in order to select the most suitable voltage levels, as well as the number of converters and their power and voltage ratings.

- Identify all the possible effects of the klystron modulators, on the selected converter/power system topology.

- Design a closed-loop control strategy to achieve low AC power fluctuation despite the pulsation present on the modulator side, as well as regulating the DC voltage.

- Validate proposed control algorithms on the selected converter topology through simulation modelling.

- Build an experimental prototype including the converter and a pulsed DC load capable of emulating the klystron modulators.

- Verify the proposed control algorithms experimentally.

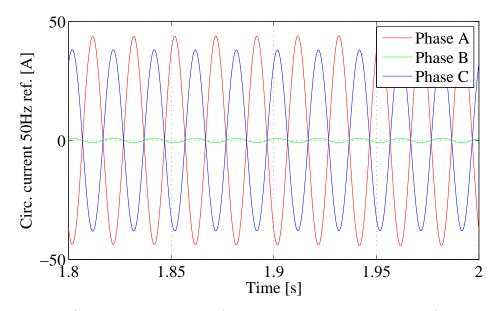

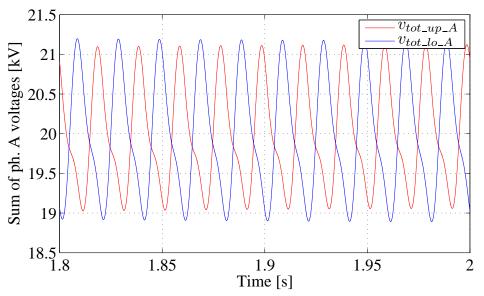

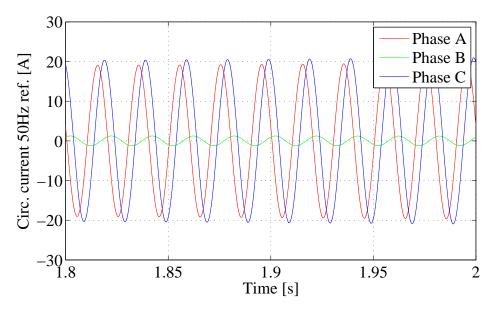

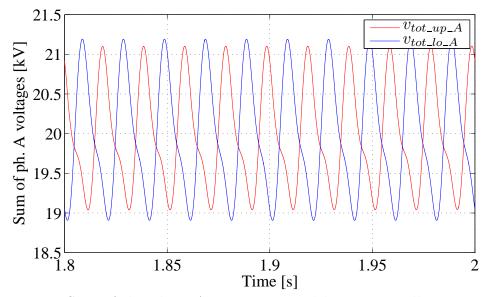

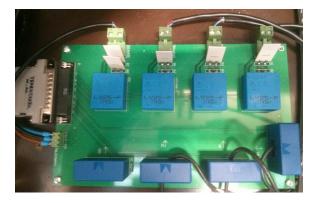

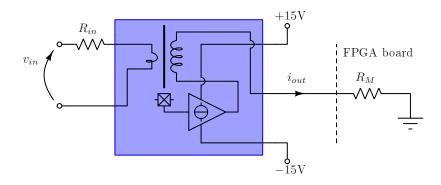

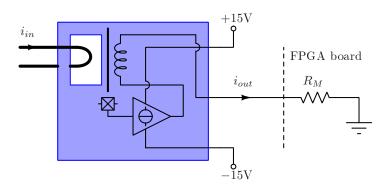

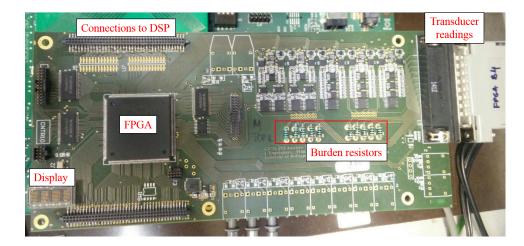

### **1.3** Organisation of the thesis