# DC Fault ride through operation of a Full bridge MMC converter

Yixue Feng MSc.

## Abstract

In recent years the growth of renewable energy has encouraged the development of HVDC grids. One challenge of building HVDC grids is the power converter response to DC side faults. The full-bridge Modular Multilevel Converter (MMC) is a desired power converter topology which is used in HVDC grids due to its scalability, modularity and capability of blocking DC side faults.

Post fault operation of the full-bridge MMC requires the control of power flow, the energy of each sub-module capacitor and the elimination of circulating harmonic current to reduce power loss while DC line-to-ground or DC line-to-line faults exist.

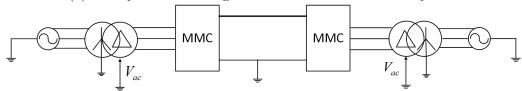

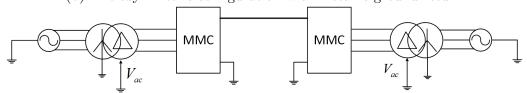

This thesis presents a post fault operation method for a full-bridge MMC in order to transmit partial power after a DC line-to-ground fault and provides reactive power after DC line-to-line fault. Simulated results are provide from a point-to-point HVDC system which consists of two eleven-level full-bridge MMC.

# Acronyms

**HVDC** High Voltage Direct Current. 2

**IPD** In-Phase Disposition. 95

LCC Line Commutated Converter. 2

$\mathbf{MMC}$  Modular Multilevel Converter. 3

**PR** Proportional Resonant. 114

$\mathbf{VSC}$  Voltage Source Converter. 2

# List of Terms

C Sub-module capacitance. 57

$\Delta W_C$  Energy stored in upper arm minus energy stored in lower arm. 62

f Fundamental frequency. 58

$I_{ac}$  AC side current. 56

$i_{cu}$  upper arm capacitor current. 58

$I_{dc}$  DC side current. 56

$I_{diff}$  Circulating current of one phase. 62

$I_l$  Lower arm current. 56

$I_n$  Circulating current. 56

$I_{reactive}$  Reactive current. 71

$I_{real}$  Active current. 71

$I_u$  Upper arm current. 56

$I_{valve}$  Arm current. 101

- $L_c$  Arm inductance. 62, 116

- N Sub-module number in one arm. 54

- $N_c$  Currently inserted sub-module number. 101

- $N_l$  Lower arm inserted sub-module number. 54

- $n_l$  Lower arm insertion index. 54

- $N_s$  Modulation number of inserted sub-module. 98

- $N_u$  Upper arm inserted sub-module number. 54

- $n_u$  Upper arm insertion index. 54

- $P_{CD}$  Conduction power loss of Diode. 81

- $P_{CT}$  Conduction power loss of IGBT. 81

- $P_e$  Real power proportion on the upper arm. 70

- $P_l$  Power flow through lower arm. 61

- $P_u$  Power flow through upper arm. 61

- $R_c$  Arm resistance. 116

- $R_u$  Reactive power proportion on the upper arm. 71

- $\Sigma W_C$  Energy stored in one phase-leg. 62

- $v_0$  Average voltage of sub-module capacitor. 65

$V_{abc}$  Three phase voltage in Cartesian coordinate system. 107

$V_{ac}$  AC side voltage. 54

$v_c$  Sub-module capacitor voltage. 49

$V_{cl}$  Lower arm sub-module capacitor voltage. 55

$V_{cu}$  Upper arm sub-module capacitor voltage. 55

$V_{dc}$  DC side voltage. 54

$V_{diff}$  Voltage across arm inductor. 62

$V_{dq}$  Three phase voltage in dq0 coordinate system. 108

$V_l$  Lower arm voltage. 53, 57

$V_{ph}$  Phase-leg voltage. 57

$V_{sm}$  Sub-module voltage. 49

$V_u$  Upper arm voltage. 53, 57

$W_l$  Energy stored in lower arm. 61

$W_u$  Energy stored in upper arm. 61

# Contents

| 1 | Intr                            | oducti  | on                                                    | 2  |

|---|---------------------------------|---------|-------------------------------------------------------|----|

|   | 1.1                             | Object  | tives and motivation of the thesis                    | 2  |

|   | 1.2                             | Staten  | nent of originality                                   | 5  |

|   | 1.3                             | Outlin  | e of the thesis                                       | 6  |

| 2 | $\operatorname{Lit}_{\epsilon}$ | erature | Review                                                | 8  |

|   | 2.1                             | HVDC    | C grids                                               | 8  |

|   |                                 | 2.1.1   | HVDC system configuration                             | 10 |

|   |                                 | 2.1.2   | HVDC grids topology                                   | 13 |

|   | 2.2                             | Literat | ture review of published power flow control schemes   | 18 |

|   |                                 | 2.2.1   | Device power flow controller                          | 18 |

|   |                                 | 2.2.2   | Master-slave control                                  | 21 |

|   |                                 | 2.2.3   | Voltage margin control                                | 22 |

|   |                                 | 2.2.4   | Voltage droop control                                 | 23 |

|   | 2.3                             | Voltag  | ge source converters                                  | 27 |

|   |                                 | 2.3.1   | Non-Modular Voltage Source Converter (VSC) topologies | 27 |

|   |                                 | 2.3.2   | Modular topologies                                    | 32 |

|   | 2.4                             | HVDC    | C grids DC side faults                                | 39 |

|   |     | 2.4.1 Background to HVDC cables                              | 39 |

|---|-----|--------------------------------------------------------------|----|

|   |     | 2.4.2 DC circuit breaker                                     | 43 |

|   | 2.5 | DC fault management with fault blocking converters           | 45 |

|   | 2.6 | Summary                                                      | 48 |

| 3 | DC  | fault ride through operation of a single full-bridge MMC     |    |

|   | con | verter 5                                                     | 51 |

|   | 3.1 | Introduction                                                 | 51 |

|   | 3.2 | Normal operation of standard MMC converter                   | 54 |

|   |     | 3.2.1 Steady state analysis of MMC converter                 | 59 |

|   |     | 3.2.2 Energy deviation in limb                               | 64 |

|   | 3.3 | Operation with one faulted cable                             | 69 |

|   |     | 3.3.1 Post fault arrangement                                 | 70 |

|   |     | 3.3.2 Operation with extra voltage stress on the transformer | 73 |

|   |     | 3.3.3 Operation with no additional voltage stress            | 77 |

|   |     | 3.3.4 Capacitor voltage estimation                           | 79 |

|   |     | 3.3.5 Best mode for partial power transmission from the      |    |

|   |     | power loss point of view                                     | 83 |

|   | 3.4 | Operation with pole-to-pole fault                            | 91 |

|   | 3.5 | Summary                                                      | 96 |

| 4 | Mo  | dular multi-level converter control scheme                   | 98 |

|   | 4.1 | Introduction                                                 | 98 |

|   | 4.2 | Modulation method level shifted carrier PWM                  | 00 |

|   | 4.3 | Sub-module rotation algorithm                                | )4 |

|   | 4.4 | AC current control                                           | 10 |

|   | 4.5 | Even l   | narmonic elimination                                     | 7  |

|---|-----|----------|----------------------------------------------------------|----|

|   | 4.6 | Contro   | ol of the MMC sub-module capacitor average voltage $$ 12 | 1  |

|   |     | 4.6.1    | Per-phase total capacitor energy control                 | 2  |

|   |     | 4.6.2    | Difference energy of upper and lower arm control 12      | 6  |

|   | 4.7 | DC gr    | id voltage control                                       | 7  |

|   | 4.8 | Summ     | ary                                                      | 9  |

| 5 | Mu  | lti-tern | ninal DC Grid modelling 13                               | 3  |

|   | 5.1 | Introd   | uction                                                   | 3  |

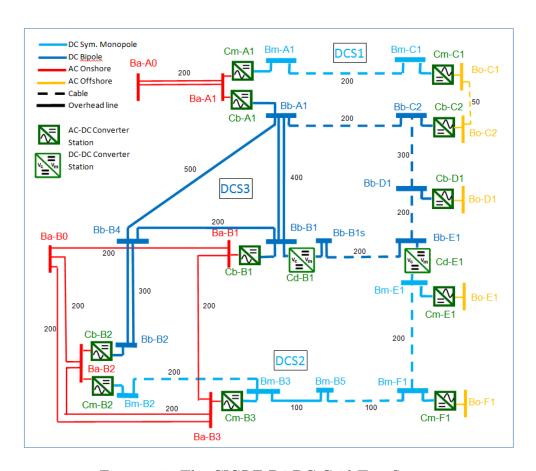

|   | 5.2 | CIGR     | E multi-terminal DC grid test system                     | 4  |

|   | 5.3 | Scaling  | g method                                                 | 6  |

|   | 5.4 | Cable    | modelling methods                                        | 9  |

|   |     | 5.4.1    | PI section transmission line model                       | 9  |

|   |     | 5.4.2    | Distributed Parameter Model/Bergeron Model 14            | :1 |

|   |     | 5.4.3    | Frequency Dependent Model                                | 2  |

|   | 5.5 | Non-sv   | witching model MMC converter                             | 4  |

|   |     | 5.5.1    | Theory of non-switching efficient model of the MMC . 14  | 5  |

|   |     | 5.5.2    | Comparison simulation results of switching model and     |    |

|   |     |          | non-switching model in steady state                      | 8  |

|   |     | 5.5.3    | Non-switching model of MMC when all IGBTs blocked 15     | 1  |

|   | 5.6 | Summ     | ary                                                      | 4  |

| 6 | Sim | ulation  | n results 16                                             | 5  |

|   | 6.1 | Introd   | uction                                                   | 5  |

|   | 6.2 | Simula   | ation circuit and parameters                             | 5  |

|   | 6.3 | Full-bi  | ridge MMC steady state normal operation results 16       | 9  |

|   | 6.4 | Full-bi | ridge MMC steady state operation after line-to-ground     |     |

|---|-----|---------|-----------------------------------------------------------|-----|

|   |     | fault   |                                                           | 170 |

|   | 6.5 | Full-bi | ridge MMC steady state operation for line-to-line fault . | 178 |

|   | 6.6 | Compa   | arison between analysis sub-module capacitor results and  |     |

|   |     | simula  | tion results                                              | 179 |

|   | 6.7 | Summ    | ary                                                       | 184 |

| 7 | Con | clusio  | n and Further Work                                        | 185 |

|   | 7.1 | Summ    | ary of achievements                                       | 188 |

|   | 7.2 | Future  | e work                                                    | 190 |

| A | App | oendix  |                                                           | 192 |

|   | A.1 | Power   | Loss Calculation                                          | 192 |

|   |     | A.1.1   | Conduction loss In Normal Operation for All Full-Bridge   |     |

|   |     |         | Sub-module                                                | 192 |

|   |     | A.1.2   | Switching loss In Normal Operation for All Full-Bridge    |     |

|   |     |         | Sub-module                                                | 195 |

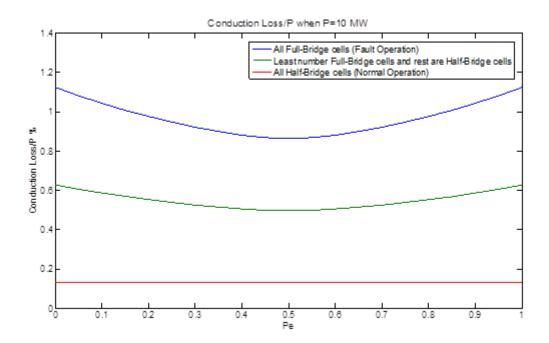

|   |     | A.1.3   | Conduction Loss for different Pe (P=10MW)                 | 200 |

|   |     | A.1.4   | Switching Loss calculation for different Pe (P=10MW)      | 201 |

|   |     | A 15    | Conduction Loss for different Carrier frequency           | 202 |

# List of Figures

| 2.1  | The configuration of Asymmetric monopole HVDC grid with       |    |

|------|---------------------------------------------------------------|----|

|      | earth return                                                  | 10 |

| 2.2  | The configuration of Asymmetric monopole HVDC grid with       |    |

|      | $metallic\ return  .  .  .  .  .  .  .  .  .  $               | 10 |

| 2.3  | The configuration of Symmetric monopole HVDC grid $\ \ .$     | 11 |

| 2.4  | The configuration of Bipole HVDC grid                         | 12 |

| 2.5  | The configuration of Mix HVDC grid                            | 13 |

| 2.6  | Star topology of HVDC grids                                   | 14 |

| 2.7  | Ring topology of HVDC grids                                   | 15 |

| 2.8  | Mesh topology of HVDC grids                                   | 16 |

| 2.9  | The structure of thyristor power flow controller [33]         | 19 |

| 2.10 | The structure of bipolar DC/DC covnerter [34] $\dots$         | 20 |

| 2.11 | The structure of Current Flow Controller [35]                 | 20 |

| 2.12 | An example voltage margin control of HVDC grids [24] $\ .$    | 23 |

| 2.14 | An example voltage droop control of HVDC grids [30]           | 24 |

| 2.13 | An example of Voltage-Power characteristic or Voltage-current |    |

|      | characteristic of one converter                               | 24 |

| 2.15 | Two level Voltage Source Converter                            | 27 |

| 2.16 | Topologies of 3-level converter                                         | 29 |

|------|-------------------------------------------------------------------------|----|

| 2.17 | Topologies of 5-level converter                                         | 31 |

| 2.19 | Three phase hybrid VSC topology [84]                                    | 34 |

| 2.18 | Topologies of MMC converter                                             | 35 |

| 2.20 | Hybrid converter topology [89]                                          | 37 |

| 2.21 | Alternate-Arm Multilevel converter topology                             | 38 |

| 2.22 | The structure of Mass-impregnated (MI) cable [100]                      | 40 |

| 2.23 | Structure of extruded cable [100]                                       | 41 |

| 2.24 | Upper: 1 Bipole HVDC system, 320kV, 1 GW lower: 2 Bipole                |    |

|      | HVDC system, 320kV, 2 GW [98]                                           | 41 |

| 2.25 | Two power and one optical cable in a bundle                             | 42 |

| 2.26 | Submarine cable laying in shallow water [102]                           | 42 |

| 2.27 | Submarine cable laying in deep water [102]                              | 42 |

| 2.28 | Topology of modular hybrid IGBT DC breaker [112]                        | 44 |

| 2.29 | Structure of Clamp-Double Sub-module [66]                               | 46 |

| 2.30 | $Structure\ of\ half-bridge\ with\ double-thyristor-switch\ sub-module$ |    |

|      | [114]                                                                   | 47 |

| 2.31 | Structure of three-level cell [115]                                     | 47 |

| 2.32 | Structure of unipolar-voltage full-bridge sub-module [116]              | 47 |

| 2.33 | Structure of three-level cross-connected sub-module [116] $$            | 48 |

| 3.2  | The structures of Modular Multilevel Converter sub-module .             | 53 |

| 3.1  | Modular Multilevel Converter structure                                  | 53 |

| 3.3  | One single phase MMC structure                                          |    |

| 3.4  | The voltage relations of $V_{dc}$ , $V_{ac}$ , $V_{a}$ and $V_{l}$ ,    | 57 |

| 3.5  | The reconfiguration of symmetric operation to asymmetric op-         |

|------|----------------------------------------------------------------------|

|      | eration                                                              |

| 3.6  | MMC fault operation circuit structure                                |

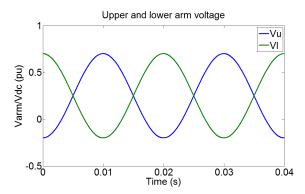

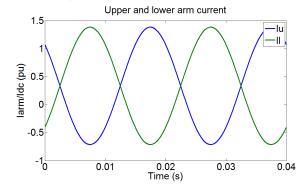

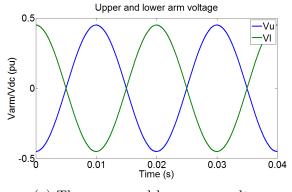

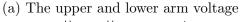

| 3.7  | Arm voltage and current when $P_e=0.5$ , Fault Op2 mode 75           |

| 3.8  | Arm voltage and current when $P_e = 0.5$ and $R_u = 0.5$ 76          |

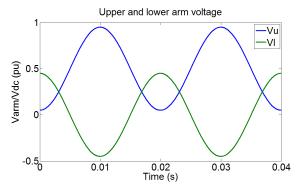

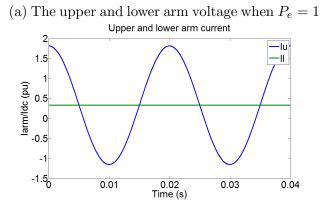

| 3.9  | Arm voltage and current when $P_e = 1$ , Fault Op3 mode 78           |

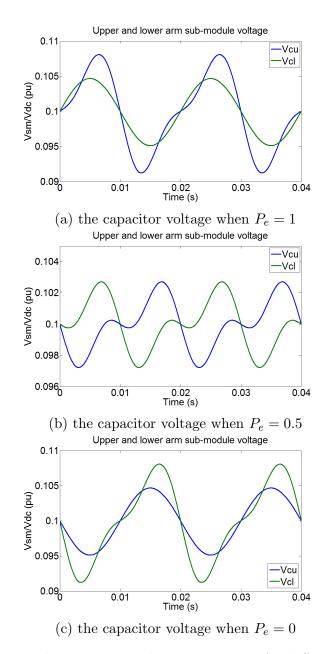

| 3.10 | The capacitor voltage estimation for different $P_e$ value 81        |

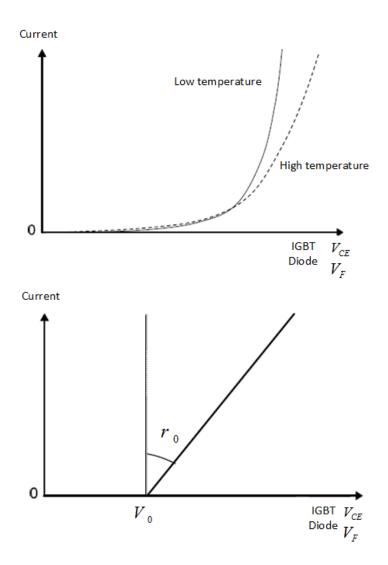

| 3.11 | Typical IGBT and diode on-state characteristics: real (upper)        |

|      | and piecewise-linear approximation (lower) [128] 85                  |

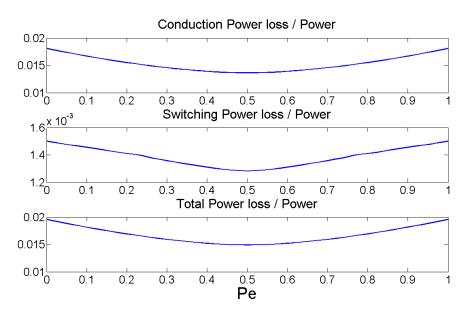

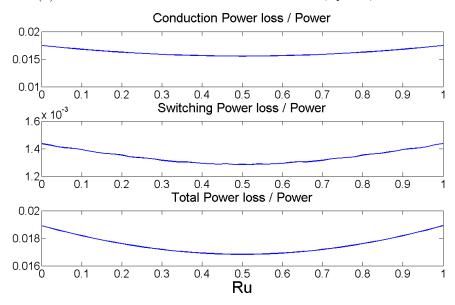

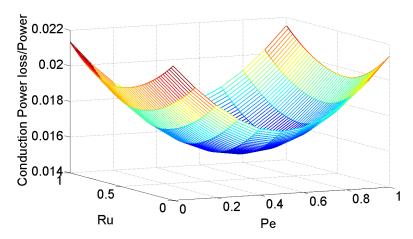

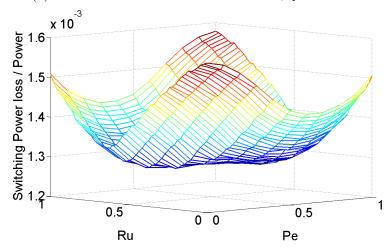

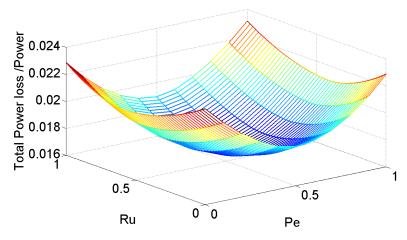

| 3.12 | The power loss calculation                                           |

| 3.13 | The 3D power loss illustration                                       |

| 3.14 | The circuit structure of MMC steady state operation with line-       |

|      | to-line DC side fault                                                |

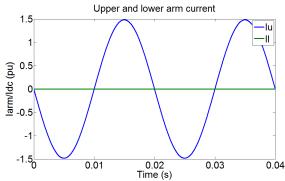

| 3.15 | Arm voltage, current and sub-module voltage when $R_u = 0.5$ . 94    |

| 3.16 | Arm voltage, current and sub-module voltage when $R_u=1$ 95          |

| 4.1  | Control scheme organisation chart                                    |

| 4.2  | Level shifted modulation                                             |

| 4.3  | Level shifted modulation for post-fault operation                    |

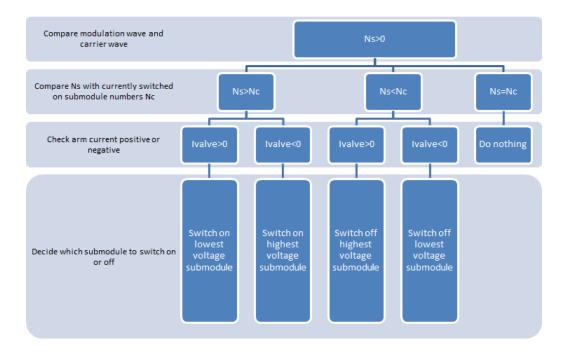

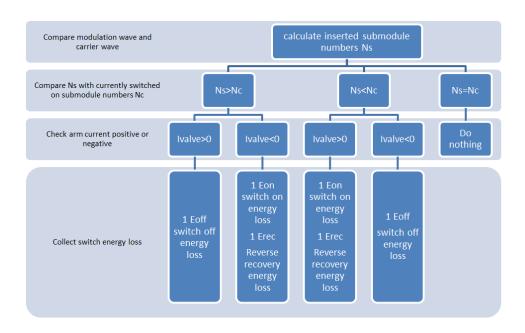

| 4.4  | The flow chart of normal operation rotation algorithm $(N_s > 0)105$ |

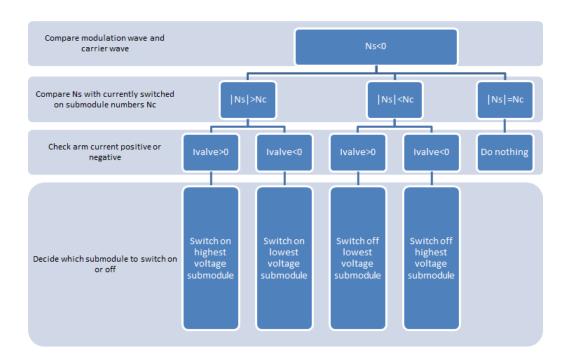

| 4.5  | The flow chart of normal operation rotation algorithm $(N_s < 0)106$ |

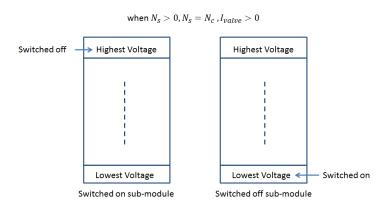

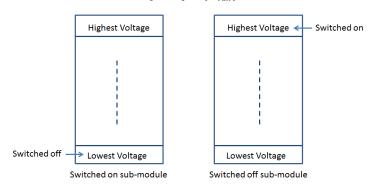

| 4.6  | Increased rotation example when $N_s = N_c > 0 \dots 109$            |

| 4.7  | Three phase system stationary phase coordinate system to ro-         |

|      | tating coordinate system                                             |

| 4.8  | Model of AC side of converter                                        |

| 4.9  | Decoupled vector control scheme for the AC side current 11         | 5  |

|------|--------------------------------------------------------------------|----|

| 4.10 | Block diagram of closed-loop current controller                    | 6  |

| 4.11 | PR control block [139]                                             | 8  |

| 4.12 | Block diagram of standard closed-loop PR controller 11             | 8  |

| 4.13 | Block diagram of closed-loop PR controller                         | 9  |

| 4.14 | The closed-loop controller of total energy from DC side 12         | 3  |

| 4.15 | The closed-loop controller for the dc current                      | 4  |

| 4.16 | The cascaded closed-loop controller of total energy from DC        |    |

|      | side                                                               | :5 |

| 4.17 | The closed-loop controller for the total energy from the AC side12 | 6  |

| 4.18 | The closed-loop controller of arm average voltage difference $12$  | 7  |

| 4.19 | The closed-loop controller of DC voltage                           | 8  |

| 4.20 | The whole control loop of power control terminal                   | 1  |

| 4.21 | The whole control loop of voltage control terminal                 | 2  |

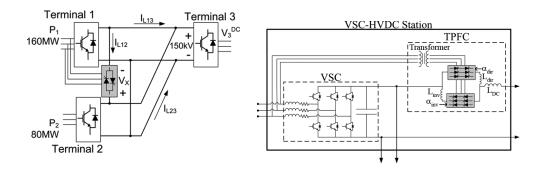

| 5.1  | The CIGRE B4 DC Grid Test System                                   | 4  |

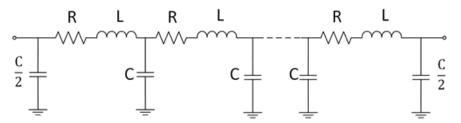

| 5.2  | The configuration of PI model                                      | :0 |

| 5.3  | The configuration of a Distributed Parameter Model 14              | :1 |

| 5.4  | Norton equivalent for transmission line model                      | :3 |

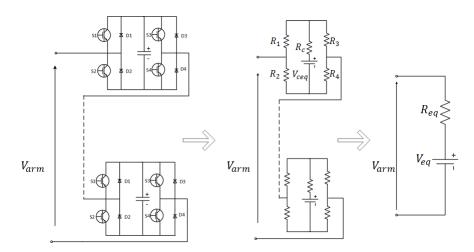

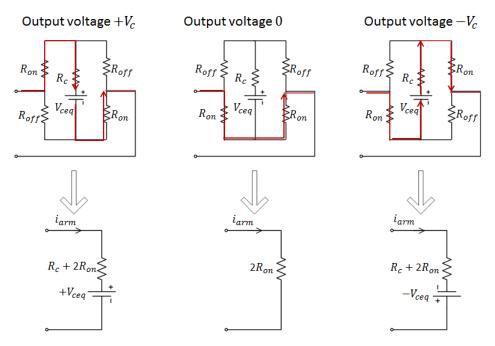

| 5.5  | The venin equivalent circuit for one arm of the MMC 14             | :5 |

| 5.6  | The venin equivalent circuit for one sub-module of MMC 14          | :7 |

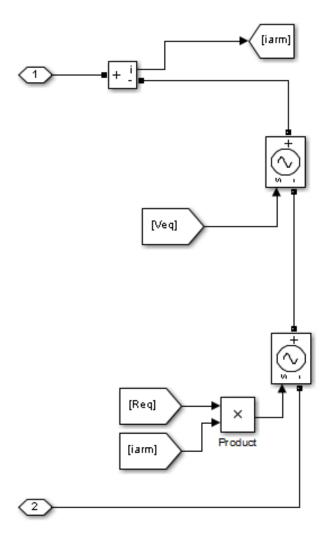

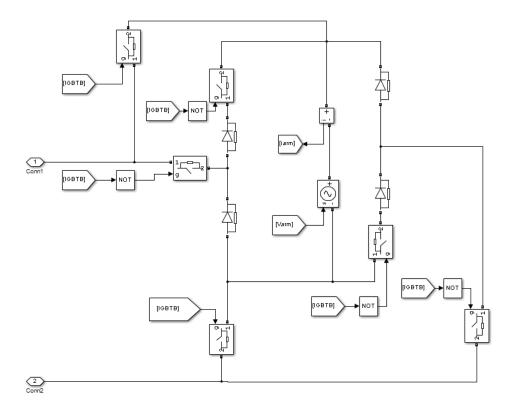

| 5.7  | Non-switching model of one MMC arm                                 | .9 |

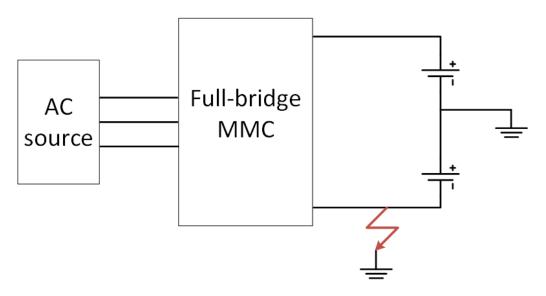

| 5.8  | MMC simulation circuit of switching and non-switching model        |    |

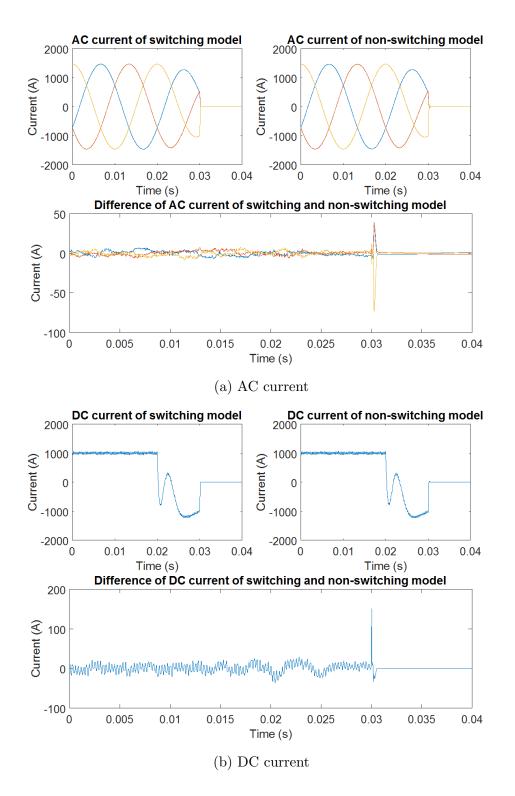

|      | comparison 15                                                      | 'n |

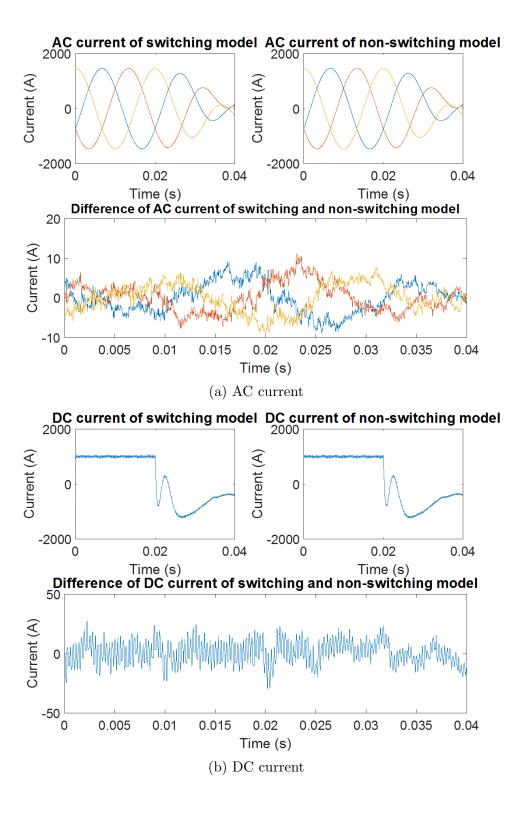

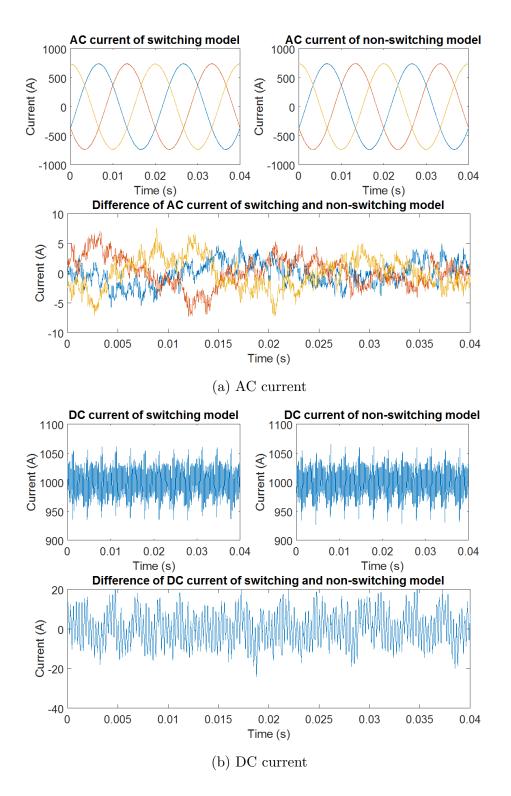

| 5.9  | Simulation results comparison between switching model and      |

|------|----------------------------------------------------------------|

|      | non-switching model in normal operation and after line-to-     |

|      | ground fault                                                   |

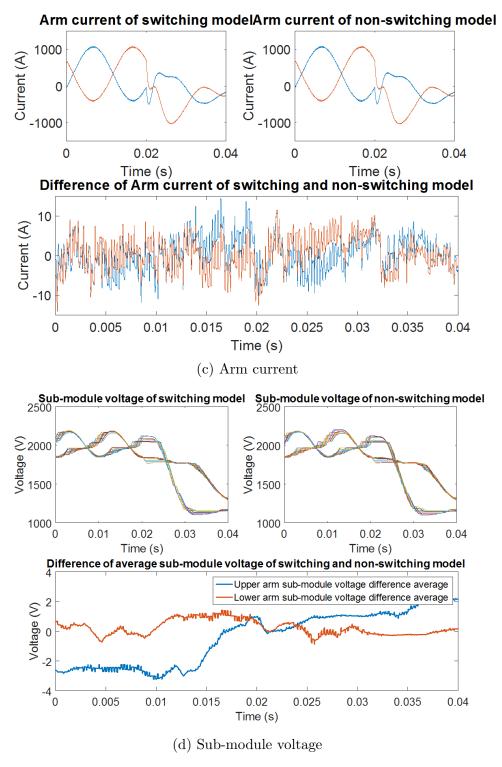

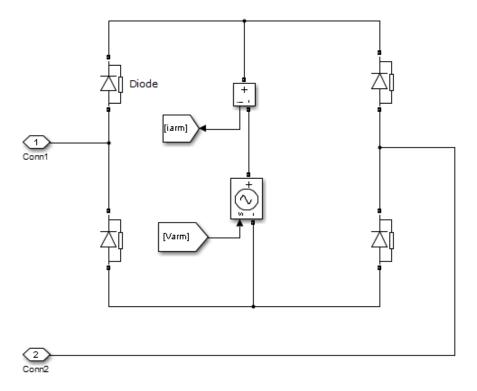

| 5.10 | MMC simulation circuit of switching and non-switching model    |

|      | comparison for post fault operation                            |

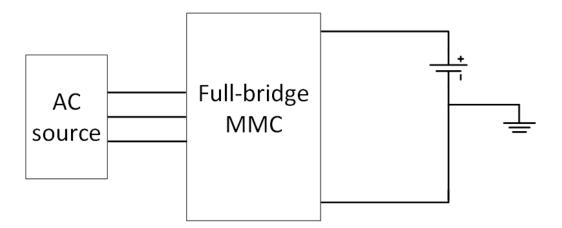

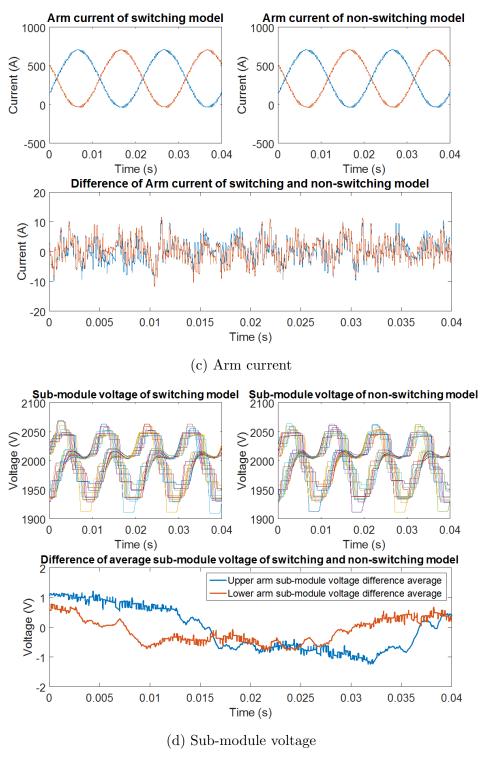

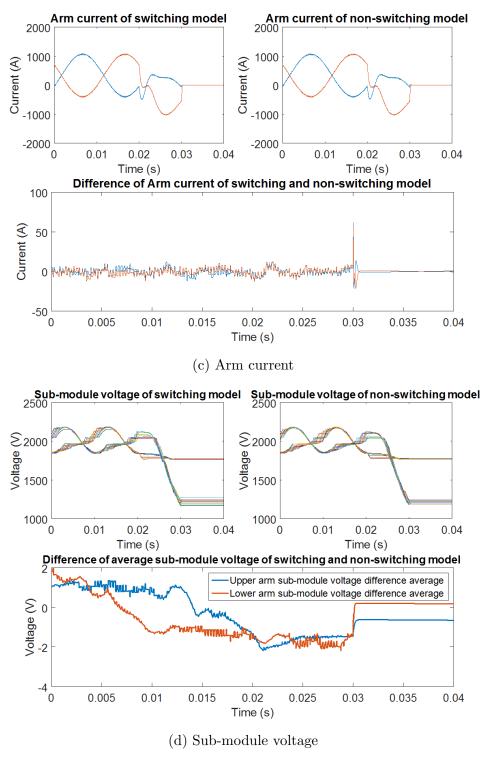

| 5.11 | Simulation results comparison between switching model and      |

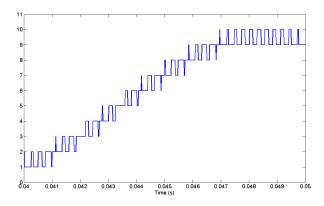

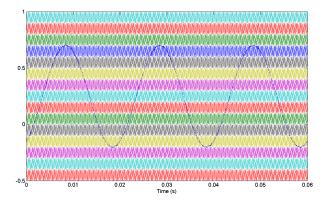

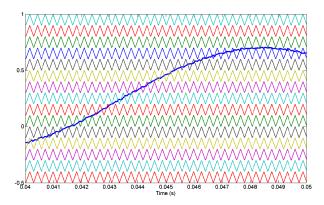

|      | non-switching model in post-fault operation when $P_e=0.5$ 156 |

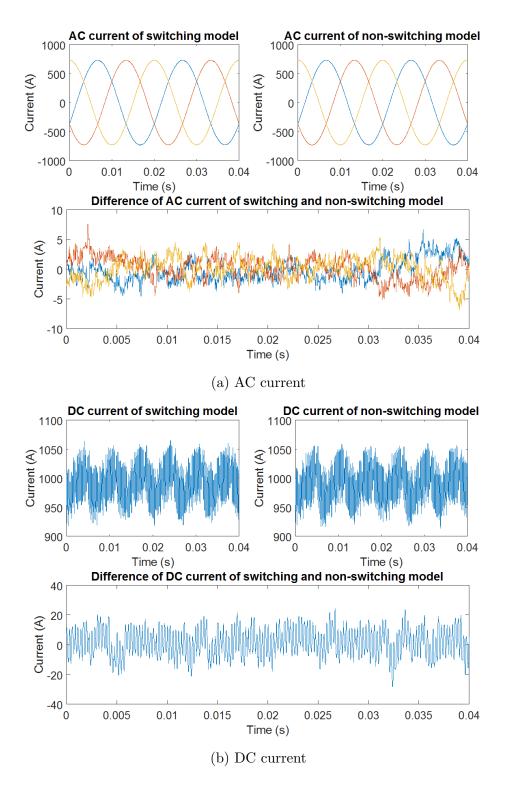

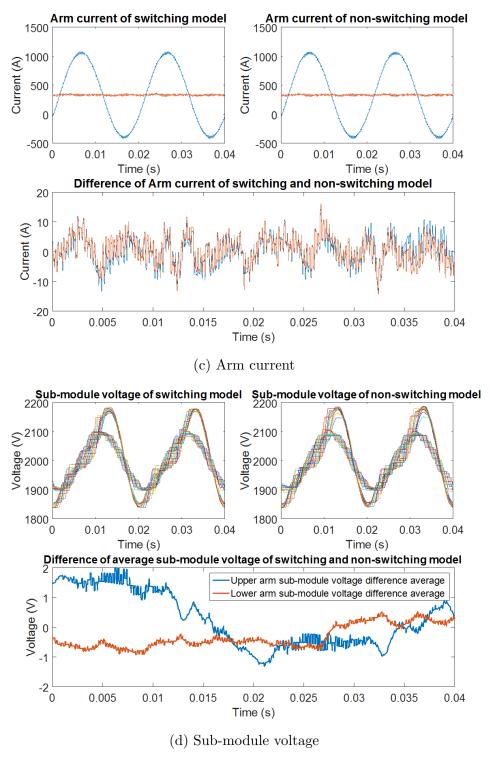

| 5.12 | Simulation results comparison between switching model and      |

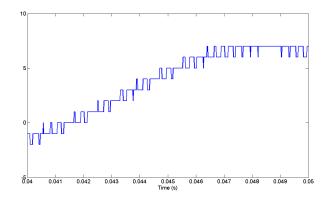

|      | non-switching model in post-fault operation when $P_e=1$ 158   |

| 5.13 | MMC arm simulation circuit of non-switching model with IG-     |

|      | BTs blocked capability                                         |

| 5.14 | MMC arm simulation circuit of non-switching model when all     |

|      | IGBTs opened                                                   |

| 5.15 | Simulation results comparison between switching model and      |

|      | non-switching model with IGBTs blocked capability $162$        |

| 5.16 | MMC arm current of switching and non-switching model zoom      |

|      | in                                                             |

| 6.1  | Simulation circuit of normal operation                         |

| 6.2  | Simulation circuit of post line-to-ground fault operation 167  |

| 6.3  | Simulation circuit of post line-to-line fault operation 167    |

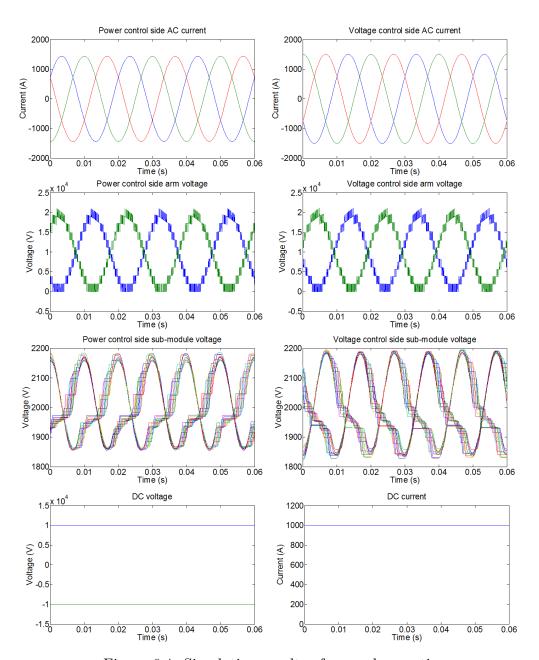

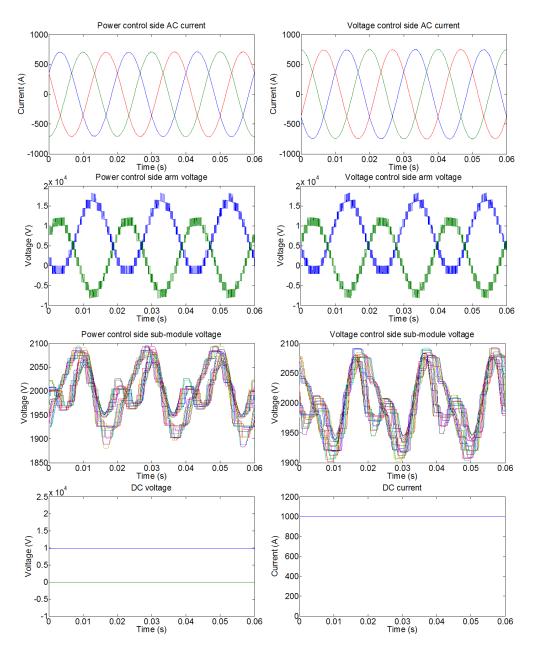

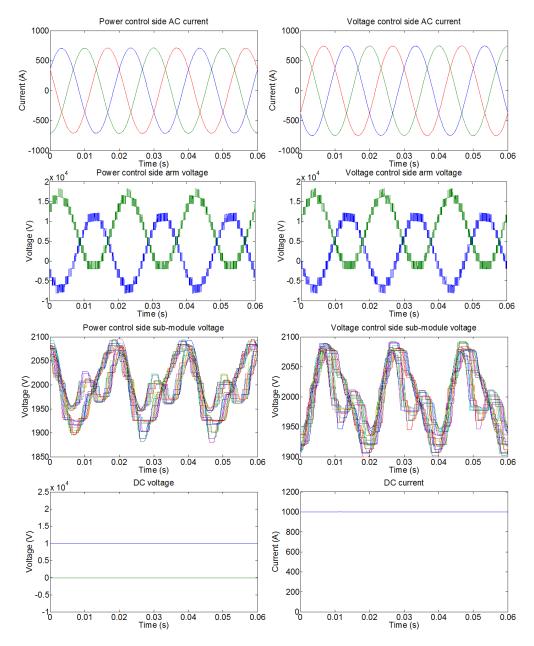

| 6.4  | Simulation results of normal operation                         |

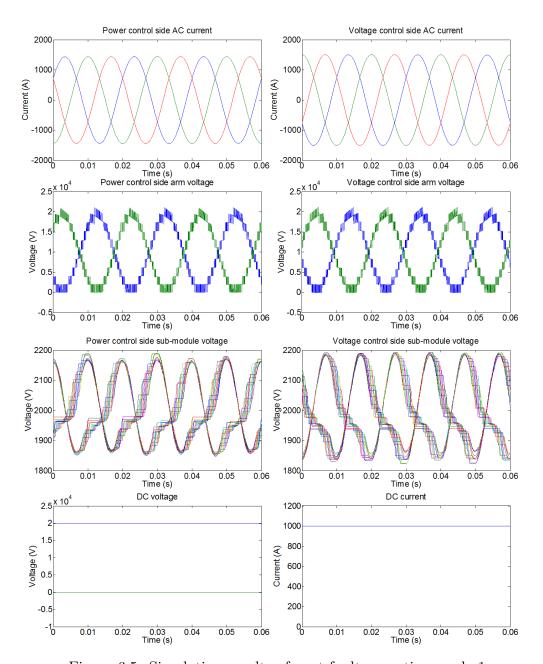

| 6.5  | Simulation results of post fault operation mode 1 172          |

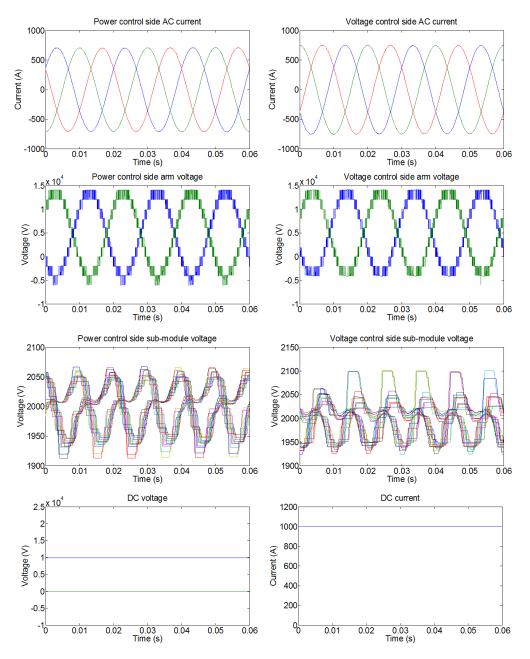

| 6.6  | Simulation results of post fault operation mode 2 174          |

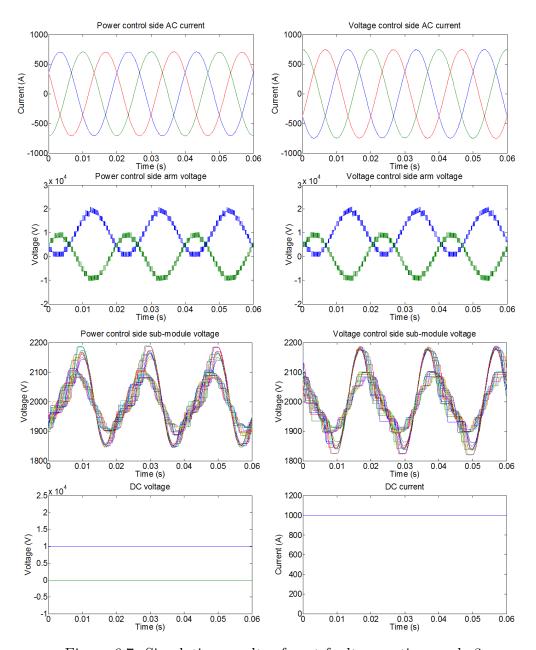

| 6.7  | Simulation results of post fault operation mode 3 175          |

| 6.8  | Simulation results of post fault operation mode 4 176               |

|------|---------------------------------------------------------------------|

| 6.9  | Simulation results of post fault operation mode 5 177               |

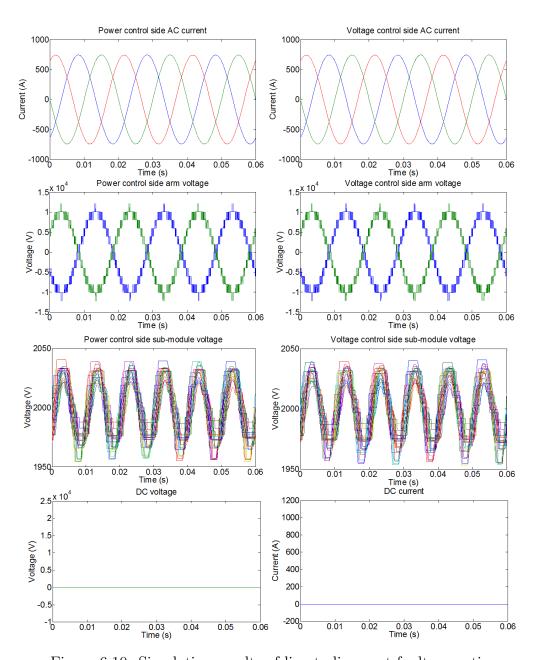

| 6.10 | Simulation results of line-to-line post fault operation 179         |

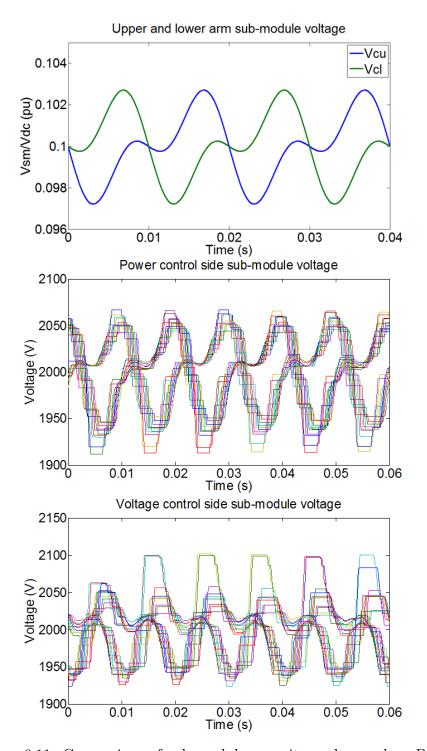

| 6.11 | Comparison of sub-module capacitor voltage when $P_e=0.5$ 182       |

| 6.12 | Comparison of sub-module capacitor voltage when $P_e=1$ 183         |

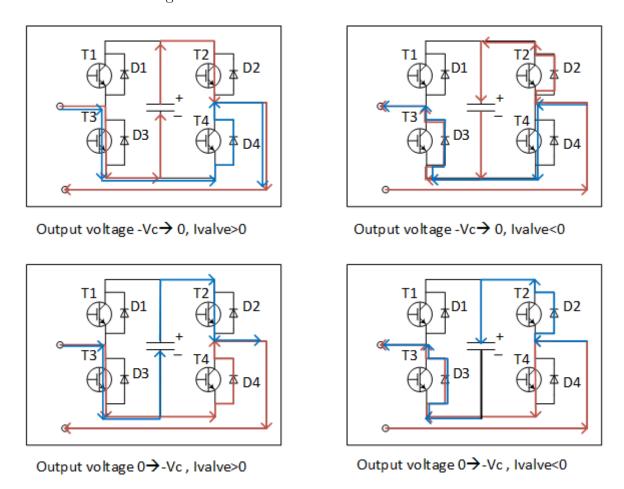

| A.1  | Conduction Path of Full-Bridge sub-module in Normal Oper-           |

|      | ation                                                               |

| A.2  | Switching Path of Full-Bridge sub-module in Normal Opera-           |

|      | tion (red to blue)                                                  |

| A.3  | The flow chart of rotation method                                   |

| A.4  | The flow chart of switching loss calculation                        |

| A.5  | Conduction Path for -Vc output voltage of Full-Bridge Sub-          |

|      | module in Fault Operation                                           |

| A.6  | Conduction Loss VS Pe when P=10MW,Q=0 199                           |

| A.7  | Switching path of Full-Bridge sub-module in Fault Operation . $201$ |

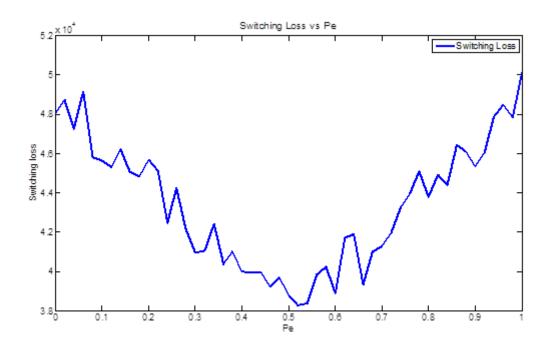

| A.8  | Switching Loss VS Pe when P=10MW,Q=0 203                            |

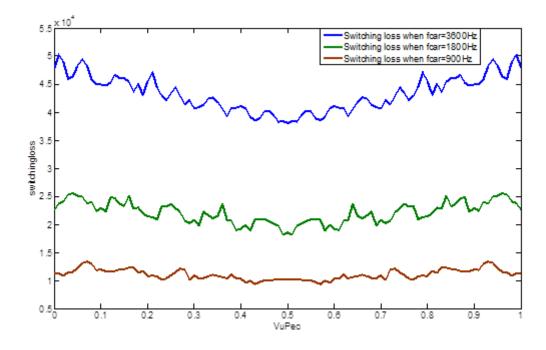

| A.9  | Switching loss comparison when P=10MW, carrier frequency            |

|      | is 3600Hz 1800Hz 900Hz 203                                          |

# List of Tables

| 3.1 | Control states of half-bridge sub-module                      |

|-----|---------------------------------------------------------------|

| 3.2 | Control states of full-bridge sub-module                      |

| 3.3 | Different modes of operation                                  |

| 3.4 | Data used for power loss calculation                          |

| 5.1 | The PU values of converter from CIGRE DC Grid System 136      |

| 5.2 | The parameters for the simulation model                       |

| 5.3 | The energy scaling capacitance                                |

| 5.4 | The CIGRE DC Grid System parameters of $\pm 200kV, 800MVA$    |

|     | DC cable and the scaled $\pm 10kV$ , $20MVA$ parameters 139   |

| 6.1 | Simulation parameters used for MMC converter in point to      |

|     | point scheme                                                  |

| 6.2 | Simulation parameters used for transmission cable in point to |

|     | point scheme                                                  |

| 6.3 | Different modes of operation                                  |

| A.1 | Conducted components of Full-Bridge sub-module in Normal      |

|     | Operation                                                     |

| A.2 | Switching components of Full-Bridge sub-module in Normal |

|-----|----------------------------------------------------------|

|     | Operation                                                |

| A.3 | Conducted components of Full-Bridge sub-module in Fault  |

|     | Operation                                                |

| A.4 | Switching components of Full-Bridge sub-module 202       |

# Chapter 1

## Introduction

### 1.1 Objectives and motivation of the thesis

Multi-terminal high voltage direct current (HVDC) grids are a technically and economically viable solution for future bulk power transmission for the development of large scale renewable energy. By connecting different power sources such as wind, hydro and solar, HVDC grids have advantages of flexibility and reliability. The renewable energy power source such as offshore wind power farms are usually located in remote areas. Compare to an AC system, HVDC is more economic for transmission over long distance, especially when using cable to transmit the power.

Currently HVDC system exist mostly point-to-point systems with Line Commutated Converter (LCC) or Voltage Source Converter (VSC). VSC is more suitable for HVDC grids since it does not need to reverse voltage polarity to change power lower direction. As one of the topologies of VSC, Modular

Multi-level Converters (MMC) could provide high voltage, high performance waveforms with a low switching frequency. Its modularity allows the increase of the voltage rating of converter by adding more sub-modules.

One of the challenge of building a HVDC system is how it would react to a DC side fault. For example, it would take about two month to fix a submarine cable. During the repair time, the transmission between the onshore and offshore system are cut. MMC with full-bridge sub-modules is able to continue to produce the rated AC waveform up to a complete reversal of the DC-Link voltage, as such it has a DC fault blocking response. And after DC fault, full-bridge MMC can partially transmit power.

This project belongs to "Transforming the Top and Tail". It is a collaborative project of eight Universities funded by the EPSRC Grand Challenge Programme.

The main aim of this project is to research full-bridge MMC post DC fault operation. The advantage of the full-bridge sub-module is that it could provide negative voltage and lead to arm voltage range increase to  $[-V_{dc}, V_{dc}]$ . It assumes that in a symmetric monopole point-to-point HVDC system, two full-bridge MMC converters are connected through two power cables. After a DC line-to-ground fault, both converters have one pole connected to ground. One possible operation method is that the faulted pole arm could provide the voltage as AC voltage  $V_{ac}$ , and the other arm provide voltage as  $\frac{1}{2}V_{dc} - V_{ac}$ . Then on DC side the voltage is  $\frac{1}{2}V_{dc}$  so that the point-to-point system could

continue to transfer half rated power. There are also other possible post line-to-line fault operation methods. After DC line-to-line fault, both converters have two pole connected with ground. One arm could provide the voltage as AC voltage  $V_{ac}$ , and the other arm provide voltage as  $-V_{ac}$ . Then on DC side the voltage is 0, but on AC side the converters can still provide reactive power.

The full-bridge modular multilevel converter can only operate correctly when all the sub-module capacitor voltage are controlled. Also, energy inside the sub-modules in one arm have to be evenly distributed. The harmonic circulating which is caused by interaction between arm inductor and sub-module capacitors should be eliminated to reduce power loss.

This thesis provides post fault operation method and the control schemes which include power flow control, energy inside sub-modules control and proportional resonant control. All these methods and control schemes allow the full-bridge MMC continue to transfer half rated power after DC line-to-ground fault, and provide reactive power to each side AC system after DC line-to-line fault.

The objectives of this thesis are:

• To evaluate the current research into full-bridge modular multilevel converters, in an effort to show the advantages of this topology in order to response to DC side fault.

- Research a post fault operation method which enable the HVDC system transmit partial rated power after DC side line-to-ground fault and provide reactive power after line-to-line fault.

- To simulate a point-to-point system with 11-level full-bridge modular multilevel converter to investigate the post fault operation method.

#### 1.2 Statement of originality

The author believes that the originality presented in this thesis lies in the following:

- The new management algorithm for the full-bridge MMC such that it can continue to transmission power with one cable grounded after a dc side line-to-ground fault. The operation can be extended to minimize voltage stress on the ac side transformer. The MMC has to operate asymmetrically to remove voltage stress on transformer, thus the second harmonic circulating current and the sub-module capacitor voltage need to be controlled.

- The new management scheme can eliminate second harmonic arm current for post fault operation.

- The new management scheme can control the total energy of one phase and can control the energy difference in the upper and lower arms, to balance sub-modules energy of the upper and lower arms for asymmetric post fault operation.

#### 1.3 Outline of the thesis

Chapter two provides an overview of the HVDC grids and the DC grid power flow control schemes. An overview of different voltage source converter topologies are then given. The background of HVDC cables and circuit breaker are provided.

Chapter three presents analysis of full-bridge modular multilevel converter in normal operation. The second harmonic circulating current and sub-module capacitor voltage estimation are investigated. The post fault operation modes are presented in order to enable the converter continue operation after DC side line-to-ground fault or line-to-line fault. The best post line-to-ground fault mode is given from the power loss point of view.

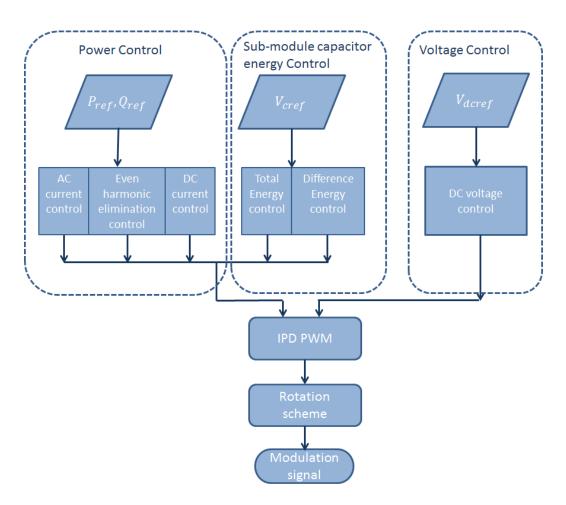

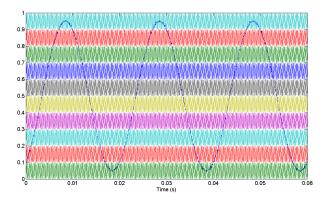

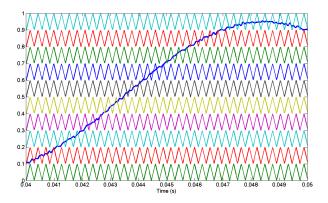

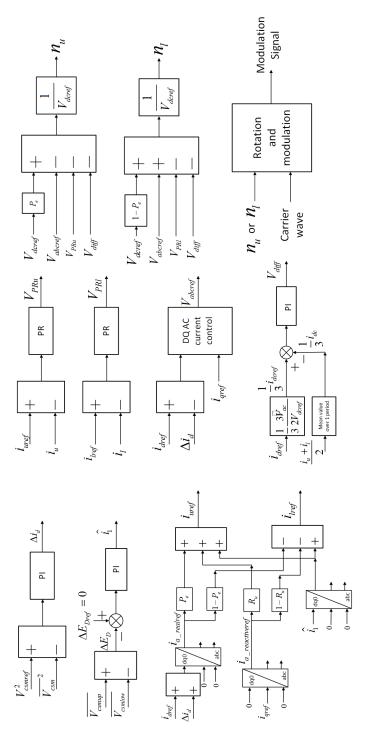

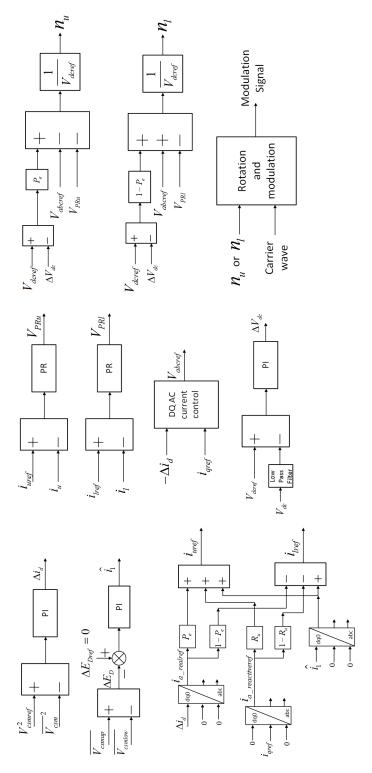

Chapter four presents the control schemes of full-bridge modular multilevel converter in normal and post fault operation condition. The sub-module balancing scheme is based on level-shifted PWM, and the rotation speed depends on the carrier wave frequency. The rest control schemes AC, DC current control, second harmonic circulating current elimination and the energy of sub-module capacitor voltage.

Chapter five presents the overview of CIGRE DC grid system. It provides the reference for the parameters of simulated full-bridge modular multilevel converter. The scaling method for the simulation circuit is also provided. The advantages and disadvantages of different cable modelling methods are presented. A non-switching model of MMC converter is presented in order to reduce the simulation computation time.

Chapter six presents the simulation results obtained by using Matlab/Simulink. Evaluation of the post fault operation schemes and MMC control schemes are presented.

Chapter seven gives the conclusions for the work as a whole and is followed by several appendices containing information on the power loss calculation of post fault operation.

## Chapter 2

## Literature Review

This chapter presents a review of HVDC system grid. The chapter begins with a general introduction to HVDC system configurations and grid topologies. Power flow control schemes are then presented, including the advantages and disadvantages of each scheme. A brief introduction of the available converter topologies is provided, which classified into modular and non-modular structures. Background information on HVDC cables and DC circuit breaker topologies are then presented.

### 2.1 HVDC grids

Multi-terminal high voltage direct current (HVDC) grids are a technically and economically viable solution for future bulk power transmission required due to the development of large renewable energy installation [1–6]. The reason for considering an HVDC system is that it has lower cost for long

distance power transmission compared to an HVAC system. The break-even distance, which is when cost of HVDC system and HVAC system are equal, for an overhead line is 500-800 km [7–9], for a cable is 50 to 80 km [10–13].

HVDC converters can be classified as Line-Commutated Converters (LCC also called Current-source converters) and Voltage-Source Converters (VSC). The LCC, which is thyristor-based, is also known as the classic HVDC or traditional HVDC converter since it has been used from 1972 [14]. The main difference between LCC and VSC is that the VSC uses semiconductor devices such as IGBT, which can be controlled to turn on and turn off. Meanwhile LCC uses thyristor, which can only be controlled to turn on with turn off relies on the external circuit. This freedom gives the VSC advantages such as black start capability and reactive power control [15]. Most importantly, the VSC changes the power flow direction by changing the current direction, maintains the voltage polarity the same. This makes it more suitable for multi-terminal HVDC transmission [16].

Up to now, HVDC systems mainly has been point-to-point connections. Instead of connecting these point-to-point systems, an HVDC grid has less converters, and as a result the investment cost and conversion loss will lower. Moreover, an HVDC-VSC grid is more flexible for power flow and energy trading, and will increase grid security [17]. The configurations of HVDC-VSC system are given in the following subsections.

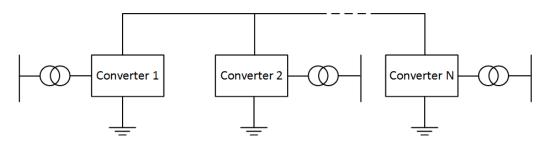

#### 2.1.1 HVDC system configuration

The arrangement of VSC converters for HVDC power transmission can be classified into the following types, asymmetric monopole, symmetric monopole and bipole [15, 18]. Here a brief description of each type of system is presented.

#### Asymmetric monopole configuration

Figure 2.1: The configuration of Asymmetric monopole HVDC grid with earth return

Figure 2.2: The configuration of Asymmetric monopole HVDC grid with metallic return

Figure 2.1 shows the configuration of an asymmetric monopole HVDC grid with earth return. Figure 2.2 shows the configuration of an asymmetric monopole HVDC grid with metal return. The common conception between

them is that they both have a single HVDC converter connected via a single conductor at the full HVDC voltage. The advantages of earth return are reduced cable investment cost and relatively less transmission loss [3]. However, the metallic return is essential when the continuous current flow through earth is not permitted [3].

#### Symmetric monopole configuration

Figure 2.3: The configuration of Symmetric monopole HVDC grid

The configuration of a symmetric monopole HVDC grid is shown in figure 2.3. Unlike the asymmetric monopole, it features a single HVDC converter with two conductors, and the grounding is at the middle of the DC side. This increases the power transmission compare to asymmetric monopole configuration since the DC side voltage doubled, and in normal operation, no current flows through the earth [3].

#### Bipole configuration

As shown in figure 2.4, the configuration of a Bipole HVDC grid consists of two HVDC converters connected in series and grounded in the middle. The

Figure 2.4: The configuration of Bipole HVDC grid

most attractive point about the Bipole configuration is that with one cable fault. It is shall possible to operate the system at reduced power [18].

#### Mixed configuration

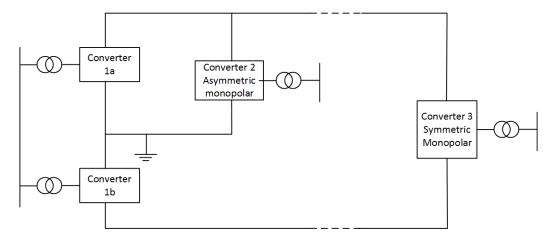

In order to build DC Grids, it is important that all the readily existing HVDC systems can be connected into the grid. As long as the DC voltages are the same, the three types of HVDC system configuration can be connected together. Figure 2.5 shows one example of a configuration mixing three types. Converter 1 is a bipolar structure. Converter 2 is asymmetric monopolar with metallic return, with the grounding point at converter 1. Converter 3 is a symmetric monopole configuration.

If the number of terminals in Figure 2.5 is increased, there are many possibilities for interconnection between the terminals. The topology of the

Figure 2.5: The configuration of Mix HVDC grid

multi-terminal HVDC grid has an impact on the steady state system losses and grid reliability [19]. Different topologies of HVDC grid are discussed in the next subsection.

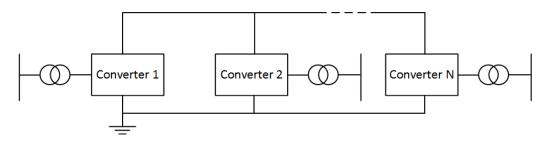

#### 2.1.2 HVDC grids topology

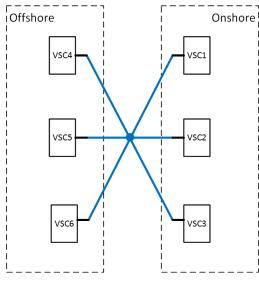

There are three HVDC grid topologies are considered here: star topology, ring topology and meshed topology [19–21]. We take a 6 terminal HVDC system as an example, assuming 3 of them are onshore substations and the other 3 are offshore wind farms. The pros and cons of each topology are demonstrated below.

#### Star topology

Two star topologies are shown in Figure 2.6. The central point could be on an offshore platform or on an onshore substations, respectively as illustrated

(a) Star topology with central node

Offshore

vsc4

vsc5

(b) Star topology with central substation

Figure 2.6: Star topology of HVDC grids

in 2.6a and 2.6b. Either way the terminals are connected at one central node.

The advantages of star topology are: first, the topology structure is simple; second, the cost of this topology is low since the cable rating of the transmission lines is same as the rating of the corresponding terminal. The disadvantage is that if a fault occurs at the central node the whole grid goes down. When a DC fault occurs on a cable, and if the DC fault is permanent, which is highly possible, the corresponding wind farm or substation is lost. This causes the reliability of the star topology to be low [19, 20].

#### Ring topology

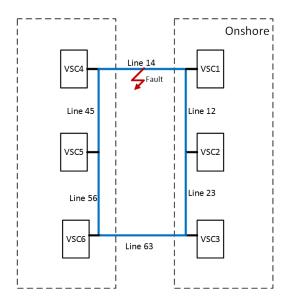

Figure 2.7: Ring topology of HVDC grids

Figure 2.7 shows a ring topology HVDC grid. The terminals are connected as a closed loop. This topology has more reliability and flexibility

Figure 2.8: Mesh topology of HVDC grids

than the star topology [19, 20].

The absence of a central node avoids the whole grid to go off due to a simple fault. Also when a DC fault occurs, for example at line 14, the open loop is able to operate without losing wind farm 4. However, this also lead to a disadvantage of the ring topology which is that the cable rating need to be higher than in a star topology. In the above example, after line 14 is disconnected, the power from wind farm 4 has to go through line 45, line 56 and line 63 to be transferred to onshore. As a result, the rating of line 63 is at least the sum of the power rating of wind farm 4,5 and 6. This increases the investment cost [20].

#### Meshed topology

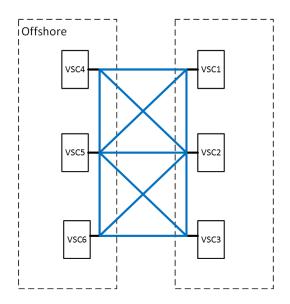

The mesh topology is presented in figure 2.8. It is an extreme case in that all terminals are connected with each other. The purpose is to show the advantages and disadvantages of the mesh topology clearly.

The benefits of a meshed topology is that the reliability and flexibility is increased [19]. If the line between terminal 1 and 4 is disconnected as in the ring topology example, the power from wind farm 4 has more choices to be transferred onshore. The drawback is that the increased connections use more cables than the star or ring topologies. As stated before, connecting all terminals with each other may not be necessary in practice, so the cost will a trade off between reliability and cable cost. Anyhow, the high reliability and flexibility make the mesh topology more suitable to meet future HVDC grids requirements than the others [19].

The topology of an HVDC grid can be a mix of the above. For example, the wind farms could be connected to onshore first, with a subsequent increase in connections from a star or ring to a mesh by adding cables. The grid building could be a gradually growing process. The optimal topology depends on the terminal locations and power flow scenarios. The power flow control methods of multi-terminal HVDC grids is introduced next.

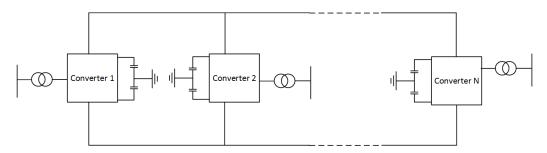

# 2.2 Literature review of published power flow control schemes

There are two types of methods to control multi-terminal HVDC grid power flow: by adding a device such as a voltage source at the end of lines, and by power flow control schemes. The published power flow control schemes can be classified into three types: Master-slave control [16, 22, 23], voltage margin control [24–26] and voltage droop control [27–31].

#### 2.2.1 Device power flow controller

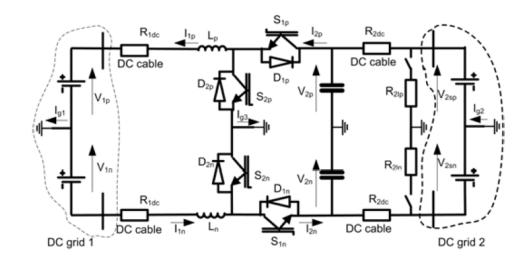

In multi-terminal HVDC VSC grids, the flow of current in the transmission lines depend on the voltage difference of the two ends and the impedance. Although in theory the line current can be controlled by adding resistance, steady state loss would be increased significantly. On the other hand, if an auxiliary dc voltage controller is added on one end of the line, the power flow on the line can be controlled by introducing a voltage source [32]. The loss then will then depend on the efficiency of this device. Up to now, three topologies of device are proposed: Thyristor power flow controller [33], DC/DC device [34] and current flow controller [35].

Figure 2.9: The structure of thyristor power flow controller [33]

#### Thyristor power flow controller

The structure of a thyristor power flow controller is shown in figure 2.9. It is inserted in series in the dc transmission line and it consists of two 6-pulse thyristor bridges to have four-quadrant operation. The rating of this thyristor controller is expected to be 10% of the connected VSC converter [33].

#### DC/DC device

Since a DC/DC converter can produce a voltage difference, it can be placed at the end of line to control current flow. There are many topologies for a DC/DC converter which could be used to connect different HVDC grids [36–38]. Figure 2.10 shows the structure of a bipolar DC/DC converter. In [34], a voltage control ratio 1% - 20% for the DC/DC device when used in power flow control is considered to be optimal.

Figure 2.10: The structure of bipolar DC/DC covnerter [34]

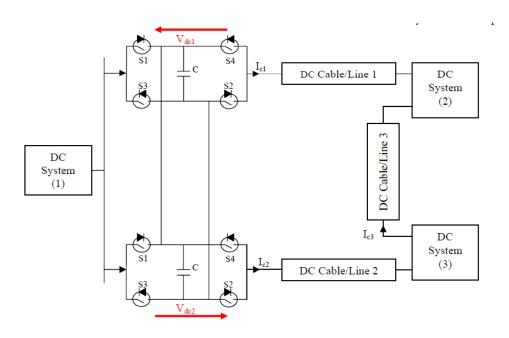

Figure 2.11: The structure of Current Flow Controller [35]

#### Current flow controller

Figure 2.11 illustrates the structure of a current flow controller. Both the thyristor power flow controller and this CFC are connected in series with

cables. The difference is that in order to reduce power loss, the thyristor PFC transfers the power draw from the DC cable to an AC side through a transformer, while the CFC transfers this power to another cable. As a result, the AC transformer rating of the thyristor PFC has to be the DC system voltage, meanwhile the rating of this CFC can be the insertion voltage which is much smaller than DC system voltage [35].

All three devices introduced above are theoretically able to control the power flow of HVDC grids. They could increase the DC grid power flow flexibility by assisting the other multi-terminal HVDC power flow control schemes which are discussed next. However, the investment cost and efficiency of these devices still need to be investigated [35].

#### 2.2.2 Master-slave control

In point-to-point HVDC systems, one converter controls the DC voltage and the other converter controls the power flow. The same control can be used in a multi-terminal system, where one converter controls the DC voltage and the others control the power flows [22]. The converter controlling the DC voltage acts as master controller, and its power flow depends on the rest of the converters.

The master converter has to be able to provide and absorb a large power when necessary. For example, when a converter is lost or there is an increased demand from one terminal. The worst case happens when the master converter fails since the whole system will go off. Consequently, for a mesh HVDC grid, master-slave control is not very suitable [23].

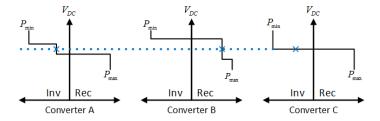

#### 2.2.3 Voltage margin control

In voltage margin control, each converter is given a DC voltage offset. The difference between the converter offsets is defined as the voltage margin [24, 25]. The DC voltage offset can be set in 2-stages to reduce the reliance on the communications between terminals [26].

Compared to Master-slave control, the advantage of Voltage margin control is that when the converter controlling the DC voltage is lost, a new equilibrium point (power balance point) will be reached automatically and another converter will regulating the DC voltage.

Figure 2.12 shows an example of 2-stage voltage margin control of three terminals A,B and C. When all the three converters are in operation as in figure 2.12a, terminal C controls the DC voltage. After terminal C is lost, as shown in figure 2.12b, the system reaches a new balance where terminal A controls the DC voltage.

(a) An example voltage margin control of HVDC grids with three terminals

(b) An example voltage margin control of HVDC grids with three terminals while terminal C is outage

Figure 2.12: An example voltage margin control of HVDC grids [24]

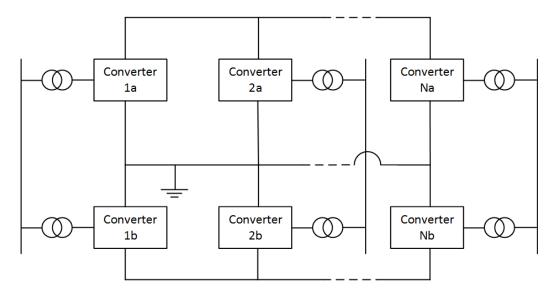

#### 2.2.4 Voltage droop control

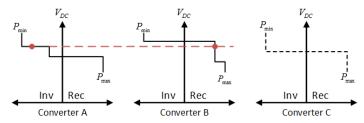

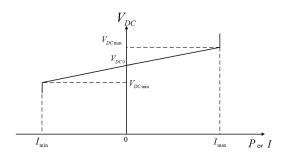

Another control method is named voltage droop control. It regulates the DC voltage based on the relation between voltage and power or current. An example of the Voltage-Power characteristic or Voltage-current characteristic of one converter is illustrated in Figure 2.13 [16, 27, 29]. The limits on voltage and current are determined by the terminal converter. The DC voltage reference will be calculated according to the droop characteristics.

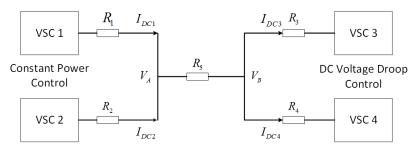

(a) An example of HVDC grids with four terminals

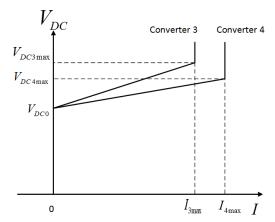

(b) Voltage droop control characteristics of terminal 3 and 4

Figure 2.14: An example voltage droop control of HVDC grids [30]

Figure 2.13: An example of Voltage-Power characteristic or Voltage-current characteristic of one converter

Simplified four terminal HVDC grid is shown in Figure 2.14a. Assume VSC 1 and 2 are offshore wind farms and they are provide constant power; VSC 3 and 4 are onshore substations and they both implement voltage droop

control. The resistors represent the impedance of the cables. Define the V/I characteristic slope of VSC 3 as  $k_3 = \frac{V_{DC3max} - V_{DC0}}{I_{DC3max}}$  and the slope of VSC 4 as  $k_4 = \frac{V_{DC4max} - V_{DC0}}{I_{DC4max}}$ . Then the DC voltages of VSC 3 and 4 are:

$$V_{DC3} = V_{DC0} + k_3 I_{DC3}$$

$$V_{DC4} = V_{DC0} + k_4 I_{DC4}$$

(2.1)

According to the grid structure, the voltage at  $V_B$  is:

$$V_{DC3} + R_3 I_{DC3} = V_{DC4} + R_4 I_{DC4} (2.2)$$

Substituting (2.1) to (2.2) yields

$$k_3 I_{DC3} + R_3 I_{DC3} = k_4 I_{DC4} + R_4 I_{DC4}$$

$$\frac{I_{DC3}}{I_{DC4}} = \frac{k_4 + R_4}{k_3 + R_3}$$

(2.3)

If we assume the voltage increase is small compared to nominal voltage, and the magnitude of  $k_3$ ,  $k_4$  are much greater than  $R_3$ ,  $R_4$ , then the power sharing between VSC 3 and 4 is

$$\frac{P_{DC3}}{P_{DC4}} = \frac{V_{DC3}I_{DC3}}{V_{DC4}I_{DC4}}

\approx \frac{I_{DC3}}{I_{DC4}}

= \frac{k_4}{k_3}$$

(2.4)

Equation (2.4) illustrates that the slope of the voltage droop characteristic will determine the power sharing between terminals [30, 39]. The droop gain also influences the DC voltage disturbance and grid stability [31, 40, 41]. Different from voltage margin control, in which only one terminal controls the DC voltage at a time, voltage droop control enables any number of terminals to adjust the DC voltage to reach the desired steady state condition.

An appropriate multi-terminal HVDC grid control scheme should be able to maintain at steady state when a DC side fault occurs. The next section gives review of voltage source converters topologies and then types of possible DC side fault are discussed.

# 2.3 Voltage source converters

# 2.3.1 Non-Modular Voltage Source Converter (VSC) topologies

This section contains a literature review of VSC topologies proposed for HVDC systems. Discussion is provided on the advantages and disadvantages of each topology for HVDC power transmission and the ability of each converter to withstand DC faults. The discussion is limited to comparison of VSC topologies and not on the comparison with line commutated alternatives.

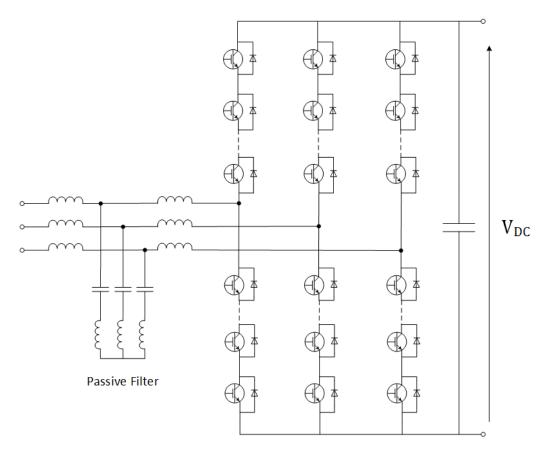

Figure 2.15: Two level Voltage Source Converter

#### Two level converter topology

In Figure 2.15, a two level converter is shown [42]; for HVDC applications a high number (greater than 100) of series connected IGBTs are required to achieve the necessary voltage rating. The advantage of the two-level VSC for HVDC power transmission is it is a relatively simple circuit to control with techniques well published in the literature [43–50]. The disadvantages of this converter when used for this application arise from the requirement to use PWM to decouple the AC voltage from the DC voltage magnitude [51, 52]. This requires that the series string of IGBTs are hard switched introducing additional switching loss as well as extra complexity required to dynamically share the device voltage during the switching event. The PWM switching pattern will also introduce harmonics into the output voltage; which require bulky passive filters to mitigate them to acceptable levels defined by the grid codes [53, 54].

Further disadvantages include poor DC side fault performance; when the DC voltage is depressed, such that when the AC voltage exceeds that of the over-modulation region permitted by triple harmonic injection, then the AC voltage causes the two-level converter to rectify into DC grid and the AC breaker must be opened. Additionally when the DC grid voltage is fully reversed the IGBT diodes will begin to conduct regardless of the state of the IGBTs and the AC side breaker [55, 56].

(a) 3-level diode clamped topology

(b) 5-level diode clamped topology

Figure 2.16: Topologies of 3-level converter

#### Non-Modular Multilevel topologies

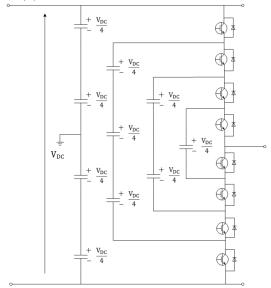

In Figure 2.16a, one phase of a three-level diode-clamped converter is shown [57]. It is a three-level inverter it has available voltage outputs of  $+V_{dc}$ , 0 and  $-V_{dc}$ . The advantages are relatively low switching loss and a good basic AC waveform compared to the two level converter [51]. If the converter is extended to further levels additional clamping diode pairs need to be introduced as shown for the five level case in Figure 2.16b. The total number of diode pairs increases rapidly with the number of levels [58]. For one phase of N-level diode clamping inverter requires (N-1) capacitors, 2(N-1) switches and (N-1)(N-2) clamping diode [59]. The non-modular nature of the topology also means that the clamping diodes do not have a common voltage rating; i.e. some clamping diodes need to be rated for the full DC bus and others do not . Assuming series connected devices are used to achieve this voltage rating, it can be observed that for each extra level many more components are required. Additionally the split DC-Link capacitors introduces complexity in voltage balancing [60, 61].

In Figure 2.17a, one phase of three-level floating capacitor topology is shown. It is also called "capacitor clamped" and "flying capacitor" [62–64]. Instead of adding diodes as in Figure 2.16a, floating DC capacitors,  $C_f$ , are added. The advantages are low switching loss, good AC waveform compared to the two-level inverter, and the switches (have the same duty) are at the same rating. Similarly to the diode clamped-topology, when the number of levels is increased, the number of added capacitors increases rapidly. For one

(a) 3-level floating capcitor topology

(b) 5-level floating capcitor topology

Figure 2.17: Topologies of 5-level converter

phase of an N-level flying-capacitor converter, (N-1)(N-2)/2 flying capacitors and (N-1) main dc bus capacitors are required [60]. This large number of capacitors also leads to a large footprint [51].

As with the two-level voltage source inverter a reversal of the DC bus causes the diodes in both the diode-camped and floating capacitor topology to conduct, thus it is not suitable for use in multi-terminal HVDC systems relying on the converter to provide the fault blocking capability.

#### 2.3.2 Modular topologies

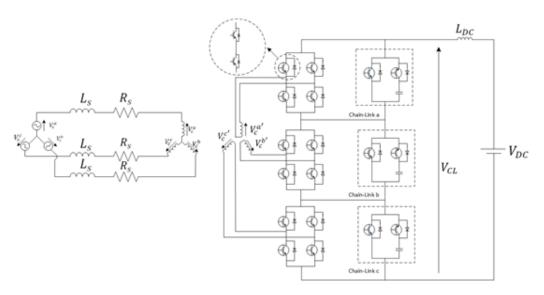

#### Modular multilevel converter (MMC) converter

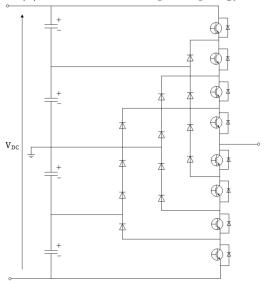

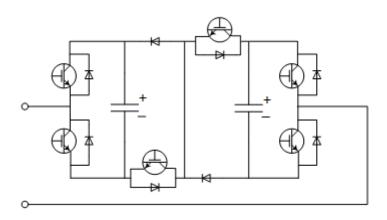

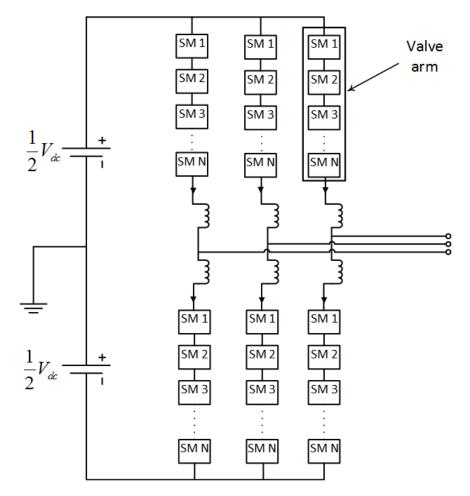

The modular multilevel converter was first proposed in 2003 [65]. The MMC converter shown in Figure 2.18a (half-bridge variant shown) is constructed from a number of series connected sub-modules [42, 66, 67]. The advantages of this topology include scalability, modularity, and low switching losses [68–70].

The modular nature of the converter means that the same building blocks can be used to expand the converter to higher voltages with more levels. This has benefits for commercialization such as reducing development costs and reduction in spares holding requirements [68, 71].

Each sub-module, used as a power electronics building block, includes a self-contained DC-Link which allows at least a two-level output and at the same time restricts the voltage seen across the semiconductors. The consequence of this is that the required high voltage rating can be achieved, while semiconductor voltage sharing issues are mitigated, switching losses are reduced. Additionally the high number or output levels means the converter is able to produce a cleaner output voltage reducing passive filter requirements [72–75].

The disadvantage, of what is essentially taking the bulk energy storage components and distributing them in a smart way around the converter, is that additional complexity is required in the way that energy is managed [76–83].

The MMC as classically proposed is formed from half-bridge sub-modules as shown in Figure 2.18a. The half-bridge sub-module MMC suffers from poor fault performance for similar reasons to the two-level inverter; the IGBT anti parallel diode starts to conduct if the DC bus voltage is reversed. Additionally as each sub-module cannot produce a negative output, over-modulation is only possible via triple harmonic injection, as a consequence a DC voltage depression limits the output AC voltage such that converter will need to be disconnected via opening of the AC circuit breaker.

Variants of the traditional MMC can be constructed using alternative sub-modules. Figure 2.18b shows proposed sub-module topologies [66]. The full-bridge sub-module is able to an output produce voltage of  $+V_c$ , 0 and  $-V_c$ . The ability to be able to produce a negative voltage means that the

converter is able operate even during a full reversal of the DC bus voltage [67]. However, the use of additional semiconductors increases the losses. For the Clamp-Double Sub-Module, it acts as two half-bridge sub-modules in normal condition. When a fault occurs, the IGBT T5 is able to cut off the fault current. Modular High Frequency is used for low power range.

#### Parallel hybrid Converter

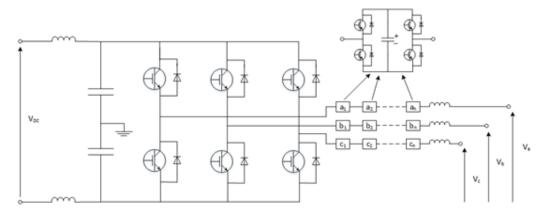

Figure 2.19: Three phase hybrid VSC topology [84]

Figure 2.19 shows the VSC, referred to here as The Parallel Hybrid Converter, first published in [84]. Each phase of the converter is constructed from an H-bridge in parallel with half-bridge sub-modules. The series-string of half-bridges are operated as to produce the rectified target AC voltage, this waveform is then unfolded using the H-Bridge valves which are soft

(a) One phase of MMC with half-bridge sub-module [65]

(b) sub-module of Full-Bridge and Clamp-Double [66, 67]

Figure 2.18: Topologies of MMC converter

switched at fundamental frequency. On the DC side, the three phases are connected in series such that rectified phase voltage sums. The addition of triplen harmonics can be used to decouple the AC and DC side voltage to avoid PWM of the H-Bridge valve which sits in the main power path [84, 85]. The summation of the rectified sinusoids results in 6n harmonics on the DC bus, further injection of triplen harmonics can be used to eliminate these harmonics [86]. This technique has been extended in [87] to produce a smooth DC output voltage.

The advantages of this topology are that the loss is very low, between 0.85 to 1.2% [85, 88], and reduced sub-module size and number.

The IGBT reverse blocking diodes in both the sub-modules and the H-Bridge mean DC-Link voltage reversal will result in the conduction of these devices. Additionally the published triplen harmonic injection technique that allows decoupling of the AC and DC side magnitudes has a maximum range that would be exceeded in DC voltage depressions.

#### Two level inverter with Multi-Level Series Active Filter

The topology depicted in Figure 2.20 was first proposed for HVDC applications in [89] and further published in [90].

Figure 2.20: Hybrid converter topology [89]

The converter is operated by low frequency hard switching of the inverter IGBTs. The output is then actively filtered using full-bridge sub-modules [90].

Advantages of this topology include, AC fault ride through, both symmetrical and asymmetrical AC faults [90], it has been proposed in literature that a smaller size sub-module capacitance could be used than in the MMC [90].

The inclusion of AC full bridge sub-modules allow DC fault ride through of depressed DC bus voltages without conduction of the two level inverter anti-parallel diodes [90]. In the case of negative DC voltages the inverter diodes still begin to conduct for the duration of the negative fault. However unlike a standard 2-level inverter the full bridge modules allow the AC network to be decoupled from the DC fault.

Figure 2.21: Alternate-Arm Multilevel converter topology

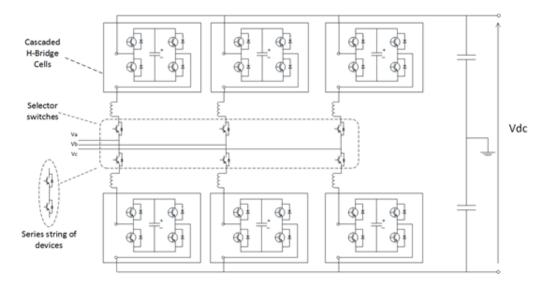

#### Alternate-Arm Multilevel (AAC) converter

The Alternate-Arm Multilevel converter (AAC) was first proposed in [89] and more extensively published in [91–96], is depicted in Figure 2.21. In this hybrid topology, a series string of IGBTs are connected in series with a series string of full-bridge sub-modules to form a converter arm. The addition of the series string of IGBTs, referred to as the director switch, enables the arm to be switched off for approximately half of a fundamental period. Doing so allows the positive and negative half cycles to be generated by the upper and lower arm respectively, such that the available voltage requirement for the arm is approximately halved with respect to the MMC, thus the number of sub-modules required is reduced [93].

The action of switching each arm in and out at fundamental frequency has the effect of rectifying the current into the DC-Link such that a DC filter is required to prevent un-wanted DC current harmonics [91, 93]. Additionally the circuit must be operated around a sweet spot for optimal performance [93]. This sweet spot voltage requires the converter to over-modulate such that full-bridge sub-modules are required. The use of full-bridge sub-modules gives the circuit inherent DC fault blocking capability and allows it operate during DC faults [91].

## 2.4 HVDC grids DC side faults

DC side faults management is critical for HVDC grid transmission. DC faults can be classified as temporary and permanent dependent on the fault clearance time. Temporary faults usually happen on overhead lines due to lightning, the converter can recover after the DC fault is cleared. Permanent faults usually happen to cables as them need a long time to repair. Since this thesis focuses on converter operation after a permanent DC side fault occurs, the background of HVDC cables and proposed fault management schemes will be briefly introduced.

## 2.4.1 Background to HVDC cables

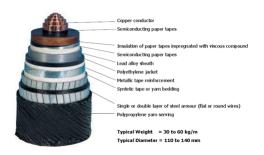

HVDC cable systems include three parts: cable, joint and end terminations. The joint is used to connect cables to reach the desired length. The end termination is used to reduce the electrical stress at the end of the cable to provide adequate electrical and mechanical properties [97]. Presently there are

mainly two types of cable used for HVDC VSC systems: Mass-impregnated HVDC cables and Extruded HVDC Cable such as XLPE (self-contained fluid filled SCFF is also available, but not widely in use) [98, 99].

Figure 2.22: The structure of Mass-impregnated (MI) cable [100]

Mass-impregnated (MI) cable is also known as paper lapped cable. Figure 2.22 shows the structure of Mass-Impregnated cable. It uses paper tapes as the insulation [97, 101]. Currently this type of cable is mostly used because they have been in service for 40 years and are highly reliable. At present the rating is up to  $\pm 600kV$  and 1800ADC [102]. The conductor size is typically up to  $2500mm^2$ .

Extruded cable is also known as polymeric cable. Figure 2.23 shows the structure of extruded cable. Extruded cables such as Cross-Linked Polyethylene (XLPE) cables are mainly used in Voltage Source Converter applications that allow the power flow to reverse without reversing the polarity [101, 103]. To date, this technology has been applied at voltages up to  $\pm 320kV$  (in service with a power capacity of 800 MW) [104], and up to 525 kV, 2.6 GW extruded HVDC cable system has been developed [105].

Figure 2.23: Structure of extruded cable [100]

Figure 2.24: Upper: 1 Bipole HVDC system, 320kV, 1 GW lower: 2 Bipole HVDC system, 320kV, 2 GW [98]

Where HVDC cables are buried underground the cables are buried usually 1-1.5 meter deep and 1 meter wide, as shown in Figure 2.24 [98].

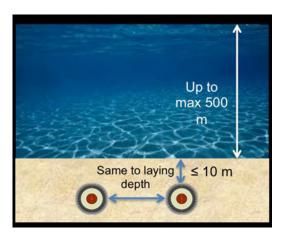

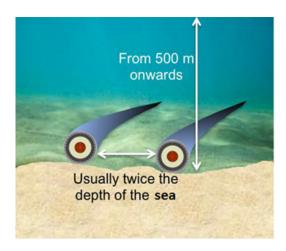

In submarine cable installations a distinction is made between shallow

Figure 2.25: Two power and one optical cable in a bundle

Figure 2.26: Submarine cable laying in shallow water [102]

Figure 2.27: Submarine cable laying in deep water [102]

water cable lying (i.e. up to a maximum depth of 500m) and deep water cable lying. For cable systems in shallow waters, burial is mandatory to protect

the cable against the risk of damage from fishing gear and anchors [106–108]. The cable can be buried in bundle configuration (as shown in Figure 2.25) or individually. When buried individually, the distance between the cables will be at least the water depth (Figure 2.26). In deep water, the threat of anchors is no longer exist, so a burial operation can be omitted. The distance between the cables is usually as great as twice the sea depth. As shown in Figure 2.27. The purpose of the large distance is avoiding overlapping when recover the cable from damage [102, 106].

#### 2.4.2 DC circuit breaker

In order to manage DC side faults, various DC circuit breaker topologies have been proposed [109]. The difficulty for DC circuit breakers compared to AC circuit breakers is due to the absence of natural current zero crossings. The HVDC circuit breakers reported in the literature can be classified as resonant breaker, solid-state breaker and hybrid breaker [110, 111].

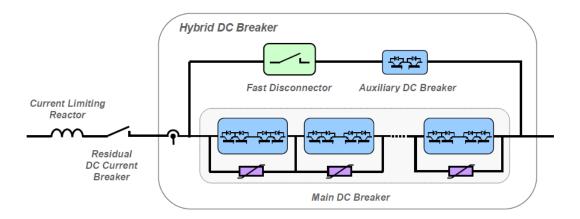

The resonant breaker has the advantage of low cost and low on state loss, but the drawback is that it is not fast enough [109, 110]. On the other hand, the solid-state breaker is fast enough however the on state loss is significant [110]. The hybrid breaker combines the merits of fast switching speed and comparatively low on state loss and appears to be more attractive than the other two [111].

Figure 2.28 shows the topology of a modular hybrid IGBT DC breaker. It was first proposed in 2011 [112]. In normal operation, all the current flows through a fast disconnector and auxiliary DC breaker. Since there is no current in main DC breaker, there is no power loss from the main breaker. After the DC fault occurs, there are three steps to stop the fault current.

Figure 2.28: Topology of modular hybrid IGBT DC breaker [112]

**First** After the DC side fault is detected, the auxiliary DC breaker opens to direct the fault current flow through the main DC breaker.

**Second** The fast disconnector will open after the current flow through it is low enough.

Third the main DC breaker opens to cut-off the fault current

The DC circuit breaker breaks the current by generating a counter voltage larger than the system voltage. In [112], the main DC breaker is designed for larger than 1.5pu system DC voltage. As shown in figure 2.28, the main

DC breaker consists a large number of IGBTs due to the voltage rating requirement. This leads to high economic cost.

Besides DC circuit breakers, the converters with fault ride through capability are also able to block a DC side fault.

# 2.5 DC fault management with fault blocking converters

The DC side fault can be divided as temporary fault and permanent fault. The DC fault type depends on the transmission line. For cable transmission, the fault usually are permanent and require some time to repair. For overhead line transmission, most DC fault due to lightning strike or flash-over is temporary. So it is possible to bring the HVDC system back to operation quickly with reverse blocking converters.

The DC fault that occurs on overhead line is usually caused by lightning strikes. For this type of fault, the full-bridge sub-module can cut off the current by insert reversing voltage [113]. As stated before in section 2.3, some VSC topologies have the DC fault blocking capability. The converter will attempts restart multiple times (typically three times according to SIEMENS) after provide reverse voltage. As a result, the system availability can be increased.

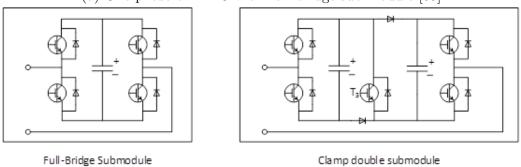

The DC fault right through capability of AAC has been investigated in [93], where the simulation results shows that the AAC behave as a STAT-COM during a temporary DC side fault and back to operation after the fault is cleared. In [90] the temporary solid pole-to-pole DC fault right through capability of Two level inverter with multi-level series active filter has been presented. Besides these two converter topologies, there are some new submodule topologies has been proposed. In [66], a Clamp-Double Sub-module structure is given, as shown in figure 2.29; in [114], a half-bridge with double-thyristor-switch sub-module is presented, as shown in figure 2.30; in [115], a novel three-level cell topology is proposed, as shown in figure 2.31; in [116], a unipolar-voltage full-bridge sub-module and a three-level cross-connected sub-module are proposed, as shown in figure 2.32 and 2.33.

Figure 2.29: Structure of Clamp-Double Sub-module [66]

Figure 2.30: Structure of half-bridge with double-thyristor-switch submodule [114]

Figure 2.31: Structure of three-level cell [115]

Figure 2.32: Structure of unipolar-voltage full-bridge sub-module [116]

Figure 2.33: Structure of three-level cross-connected sub-module [116]

The above research mainly focus on the DC fault handling capability. The converters with fault blocking capability are able to back to operation after the fault is cleared. However, when the DC fault is permanent which is highly possible for cable transmission, it takes a long time to clear the fault. It would be an advantage if HVDC system can continue to operate under DC fault. [117] proposed a method to ensure the healthy DC network continue to operate by using additional DC passive components and novel converter control combined with mechanical DCCBs. In this thesis, the author proposes another method to keep the point-to-point HVDC system continue to operation under DC fault.

## 2.6 Summary

HVDC VSC system grid provides a viable solution for future bulk power transmission required due to the development of large renewable energy installation. The configuration of VSC converters can be classified into the following types, asymmetric monopole, symmetric monopole and bipole. The three types of HVDC system configuration can be connected together.

The topology of HVDC grid can be a mix of star, ring and mesh. The optimal topology depends on the terminal locations and power flow scenarios. Power flow of multi-terminal HVDC grid can be controlled by device or power flow control schemes. Published device power flow controller include thyristor power flow controller, DC/DC device and current flow controller. Published power flow control schemes include master-slave control, voltage margin control and voltage droop control.

Voltage Source Converter topologies consist of non-modular topology including two level converter, diode-clamped converter, floating capacitor converter; and modular topology including modular multilevel converter (MMC), parallel hybrid converter, two level inverter with multi-level series active filter and alternate arm multilevel converter (AAC). There are mainly two types of cable used for HVDC VSC systems: Mass-impregnated HVDC cables and Extruded HVDC cables such as XLPE. Hybrid IGBT DC breaker combines the merits of fast switching speed and comparatively low on state loss appears to be more attractive among various proposed HVDC circuit breaker topologies.

For temporary DC fault occurs on point-to-point or radical HVDC system, the converter with fault blocking capability could back to normal operation after the DC side fault is cleared. If the DC fault is permanent, which is usually happened on cable transmission, one method of continuous operation of HVDC system is proposed in [117] with additional devices. For the point-to-point HVDC system with full-bridge MMC, it is possible to continue to operation under DC fault without additional components. In the following of this thesis, the operation methods of the point-to-point HVDC system continuous operation with the dc side fault is presented.

# Chapter 3

# DC fault ride through operation of a single full-bridge MMC converter

## 3.1 Introduction

The Modular Multilevel Converter (MMC) was first proposed by Prof. R. Marquardt in 2001 [118]. Since this time the topology has been adopted for commercial application by Siemens, ABB and Alstom Grid. The MMC has the following advantages over the two level inverter used in previous generation HVDC voltage source converters:

• Scalability, the modular structure of the MMC enables high voltages to be designed for by inserting large number of sub-modules;

- High power quality, the large number of sub-modules leads to a great number of voltage levels, therefore, the output voltage has low harmonic distortion and is able to meet the grid code without large AC harmonic filters;

- Low switching frequency, the modulation strategy for the MMC enables high quality waveforms to be produced while switching each submodule close to fundamental frequency, reducing switching losses;

- High availability, due to the modular construction, MMC is able to insert redundant sub-modules in the converter arms, providing faulted sub-modules can be bypassed the MMC can continue to operate even if there is a sub-module failure.

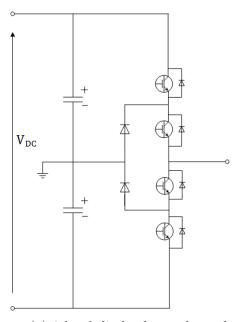

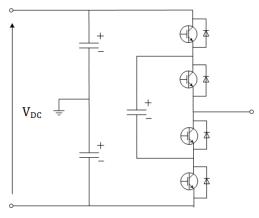

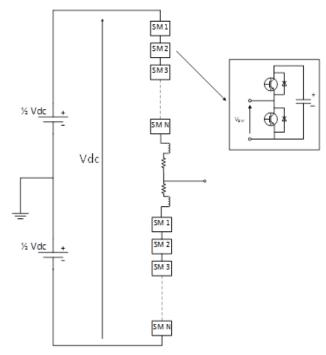

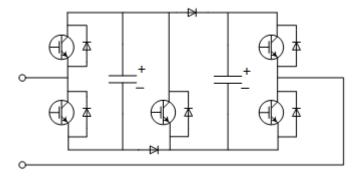

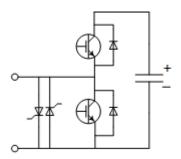

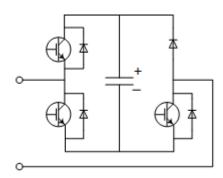

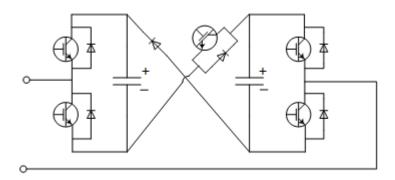

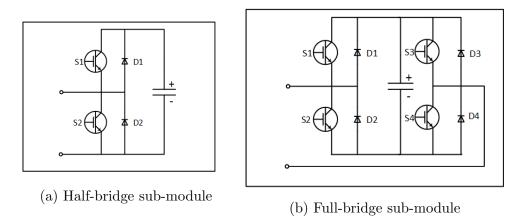

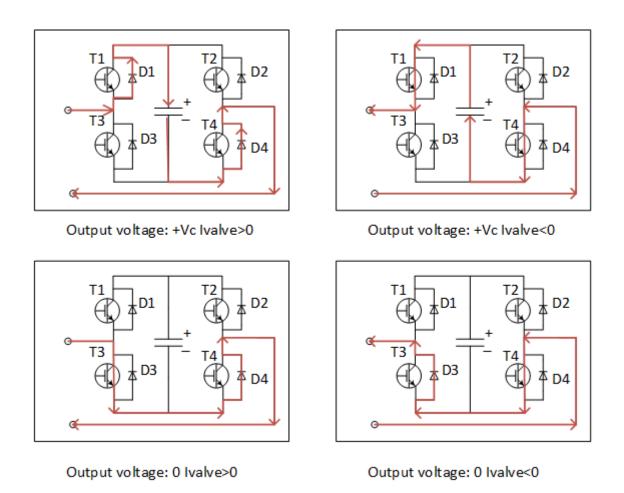

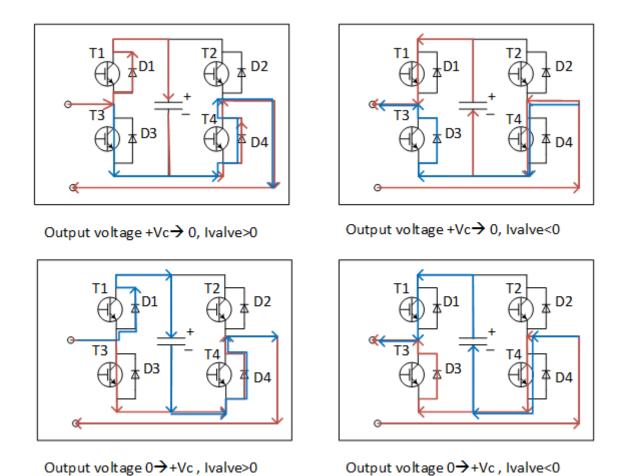

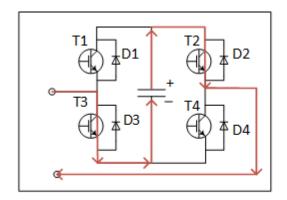

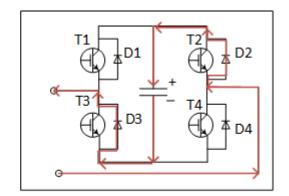

There have been several variants of the MMC proposed, utilising alternative sub-modules. One approach is to use the half-bridge sub-module shown in Figure 3.2a. This sub-module voltage  $V_{sm}$  is able to produce two levels  $v_c$  and 0, where  $V_c$  is the sub-module capacitor voltage, thus an arm populated with just half bridge sub-modules is only able to produce a unipolar waveform and cannot respond to DC faults. Another approach uses the full-bridge sub-module shown in Figure 3.2b. This sub-module is able to produce 3 levels  $V_c$ ,0 and  $-V_c$ . An MMC converter populated with full-bridge sub-modules is able to continue to produce the rated AC waveform for up to a complete reversal of the DC-Link voltage and as such it has a DC fault blocking response.

Figure 3.2: The structures of Modular Multilevel Converter sub-module

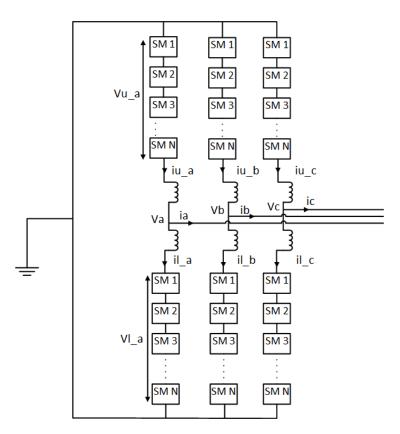

Figure 3.1: Modular Multilevel Converter structure

This chapter presents an analysis of DC fault responses for the MMC converter, initially normal operation is considered showing the approach needed to complete the analysis.

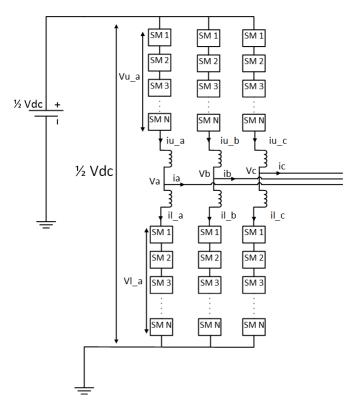

# 3.2 Normal operation of standard MMC converter

The MMC converter topology is shown in figure 3.1. It uses a modular structure where each arm is populated with sub-modules. In this thesis only the half-bridge and full-bridge sub-modules variants are considered; the structure of these sub-modules are shown in figure 3.2a and 3.2b respectively. Alternative sub-modules have been proposed in [66, 67], but are not considered in this work. The available states of the sub-module are shown in table 3.1 and 3.2; by correct modulation of these sub-module states the converter can be controlled to produce both an AC waveform at the AC terminals of the converter and a DC voltage at the DC bus.

Table 3.1: Control states of half-bridge sub-module

| S1  | S2  | $V_{sm}$ | operating state |

|-----|-----|----------|-----------------|

| ON  | OFF | $+V_c$   | 1               |

| OFF | ON  | 0        | 2               |

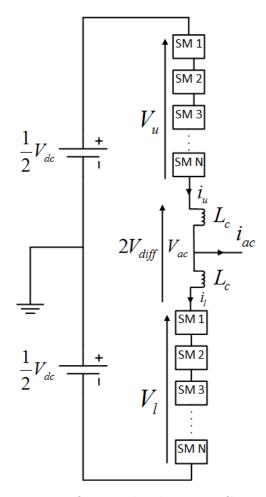

Figure 3.3: One single phase MMC structure  $\frac{1}{2}$

Table 3.2: Control states of full-bridge sub-module

| S1  | S2  | S3  | S4  | $V_{sm}$ | operating state |

|-----|-----|-----|-----|----------|-----------------|

| ON  | OFF | OFF | ON  | $+V_c$   | 1               |

| ON  | OFF | ON  | OFF | 0        | 2               |

| OFF | ON  | OFF | ON  | 0        | 3               |

| OFF | ON  | ON  | OFF | $-V_c$   | 4               |

$$V_{u} = \frac{1}{2}V_{dc} - V_{ac} - L_{c}\frac{di_{u}}{dt}$$

(3.1)

$$V_l = \frac{1}{2}V_{dc} + V_{ac} - L_c \frac{di_l}{dt} \tag{3.2}$$

$$V_{dc} = V_u + V_l + L_c \frac{di_u}{dt} + L_c \frac{di_l}{dt}$$

(3.3)

$$V_{ac} = \frac{1}{2}(V_l - V_u) \tag{3.4}$$

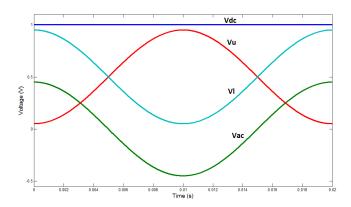

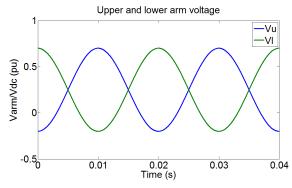

The DC converter voltage is produced by the sum of inserted sub-modules in both the upper and lower arms; conversely the target AC voltage is given by the difference in upper and lower arm voltage. Thus equations (3.1) to (3.4) can be used to derive the required upper and lower arm voltages  $V_u$ ,  $V_l$

Figure 3.4: The voltage relations of  $V_{dc}$ ,  $V_{ac}$ ,  $V_u$  and  $V_l$

as shown in figure 3.3. The voltage and current in the equations are instantaneous value. Figure 3.4 illustrates these characteristics. It shows that the maximum arm voltage will be the DC voltage  $V_{dc}$ , so that if there are N submodules in one arm, the capacitor voltage  $V_c$  should be at least be  $V_{dc}/N$ . It also shows that the amplitude of AC voltage  $V_{ac}$  can not be larger than  $\frac{V_{dc}}{2}$ .

The target inserted voltage can be achieved using a modulation technique such as in-phase disposition (IPD) level shifted modulation or phase shift modulation [77, 82, 119–121] to control the number of inserted sub-modules. An insertion index of the upper and lower arms,  $n_u, n_l$ , between -1 and 1 is defined here, to describe the number of inserted sub-module numbers  $N_u, N_l$  as a fraction of the total number available, N; negative numbers are used to represent sub-modules producing negative voltages. Although only a discrete number of levels are available it is assumed here that the number of sub-modules and so available levels of the converter is great enough that this index can be considered continuous.

$$n_u = N_u/N$$

$$n_l = N_l/N$$

Ideally, the sum of inserted upper and lower arm capacitors voltages should be equal to DC voltage, assuming that the ripple of capacitor voltage is small, then

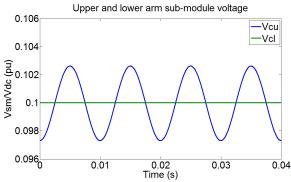

$$\sum V_{cu} \approx \sum V_{cl} \approx V_{dc}$$

Where  $V_{cu}, V_{cl}$  are the upper and lower arm sub-module capacitor voltage.

The power pulsation in each of the arms, arising from the interaction of the arm voltage and the arm current, results in a deviation in the bulk energy stored in the sub-module capacitors. In order that there is sufficient available voltage to meet the target required voltage demand, the capacitors must be selected appropriately based on the inequality shown in (3.5). As will be discussed in the next section this energy deviation can result in DC harmonic circulation if the insertion index of upper and lower arm  $n_u$ ,  $n_l$  are not compensated for appropriately.

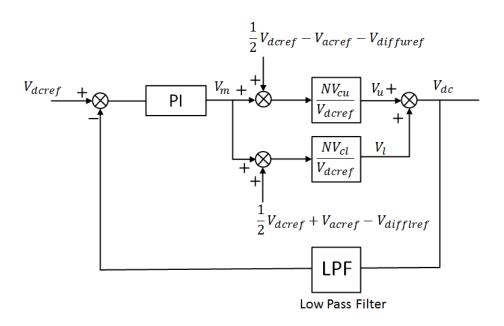

$$n_{u} = \frac{\frac{1}{2}V_{dc} - V_{ac}^{ref} - V_{diff}^{ref}}{\sum V_{cu}}$$

$$\approx \frac{\frac{1}{2}V_{dc} - V_{ac}^{ref} - V_{diff}^{ref}}{V_{dc}}$$

$$n_{l} = \frac{\frac{1}{2}V_{dc} + V_{ac}^{ref} - V_{diff}^{ref}}{\sum V_{cl}}$$

$$\approx \frac{\frac{1}{2}V_{dc} + V_{ac}^{ref} - V_{diff}^{ref}}{V_{dc}}$$

$$(3.5)$$

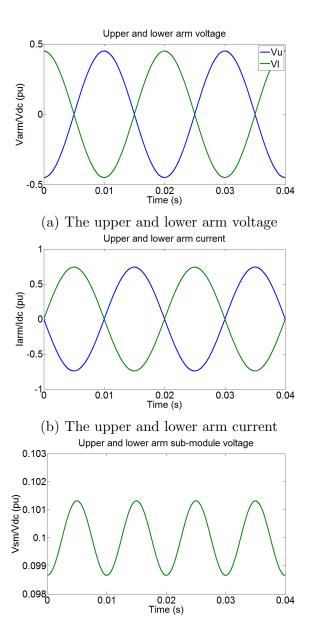

### 3.2.1 Steady state analysis of MMC converter

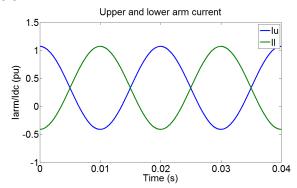

Analysis of the limb current in the MMC converter is not trivial and there are several published methods for doing so [122–124]. Here methods of estimating the arm current are discussed assuming harmonic suppression techniques are not used. These methods can be classified into two types based on the assumptions used. The first approach [122] assumes all the limb current harmonics exist. The second method [123] assumes the second harmonic in the limb current is fixed to a particular value; this can be achieved by appropriate control of the insertion index. It is a reasonable assumption since the second harmonic is the most significant component [78, 122, 125, 126].

The first method [122] assumes that the arm currents  $I_u, I_l$  contain one third dc current  $I_{dc}$ , half ac current  $I_{ac}$  and all orders of harmonics  $I_n$ , also the switching function only contains dc and fundamental frequency components, as shown in equation (3.6)(3.7). Under the ideal situation, where all the

sub-modules capacitor voltage in one arm are the same, the upper and lower arm voltage  $V_u, V_l$  can be calculated as the multiplication of the switching function, sub-module numbers in one arm and sub-module voltage as shown in equation (3.8).

$$I_{u} = \frac{1}{3}I_{dc} + \frac{1}{2}I_{ac} + \sum_{n=1}^{\infty} I_{n}$$

$$I_{l} = \frac{1}{3}I_{dc} - \frac{1}{2}I_{ac} + \sum_{n=1}^{\infty} I_{n}$$

(3.6)

where  $I_n = \hat{i_n} \cos(n\omega t + \phi_n)$ ,  $I_{ac} = \hat{i_{ac}} \cos(\omega t + \phi_{ac})$

$$n_u = \frac{1}{2}(1 - m\cos(\omega t))$$

$$n_l = \frac{1}{2}(1 + m\cos(\omega t))$$

(3.7)

$$V_{u} = n_{u} \times N \times V_{cu}$$

$$= Nn_{u} \frac{1}{C} \int i_{cu} dt$$

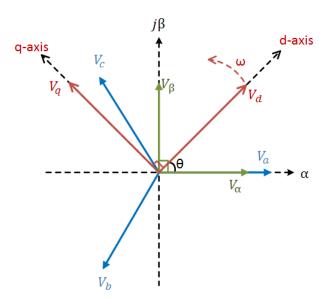

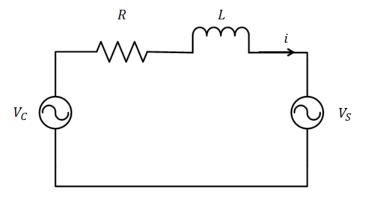

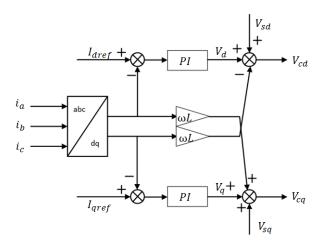

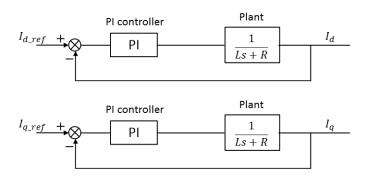

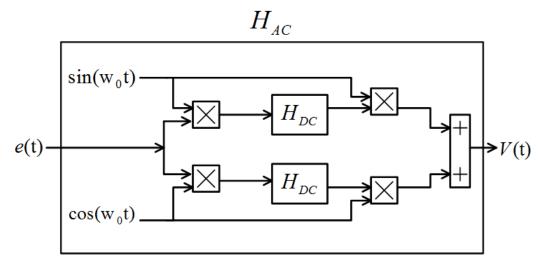

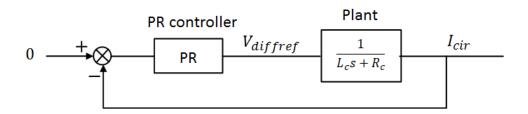

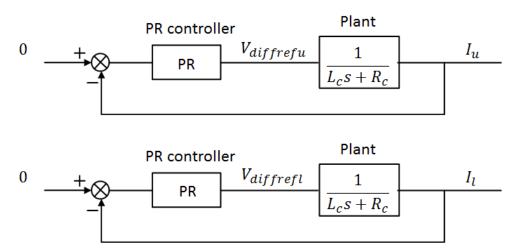

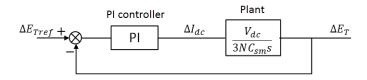

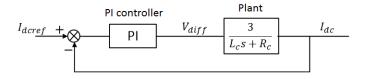

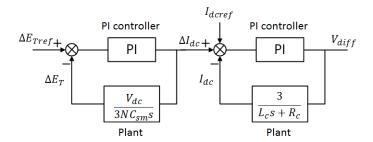

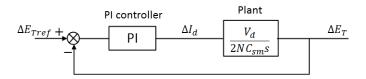

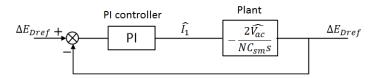

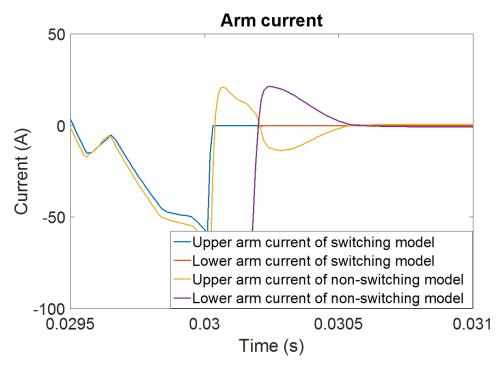

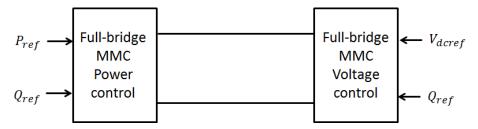

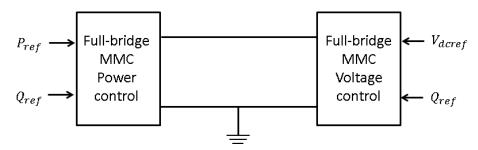

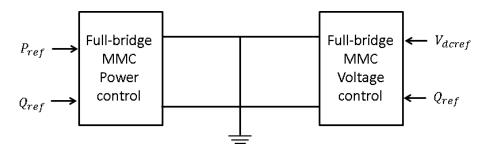

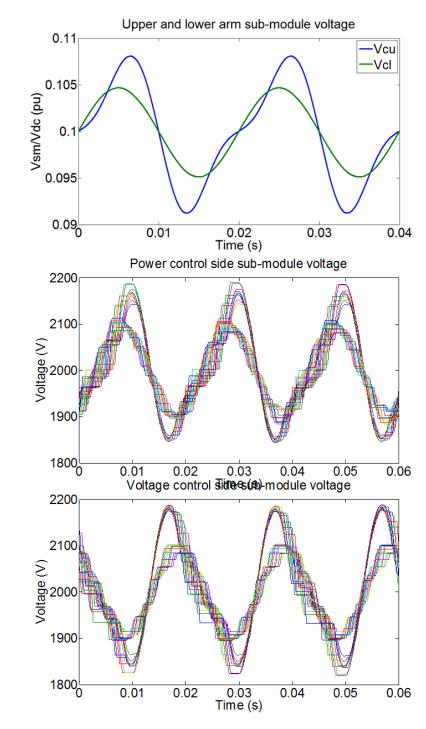

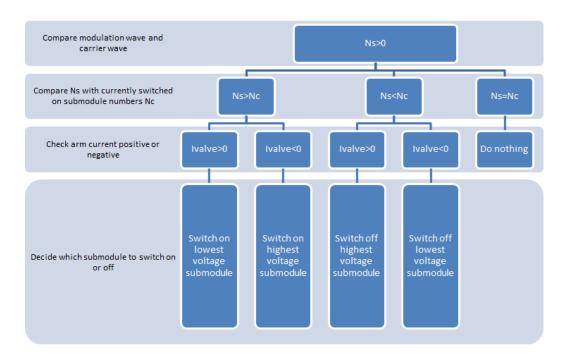

$$= Nn_{u} \frac{1}{C} \int n_{u} I_{u} dt$$