## University of Arkansas, Fayetteville ScholarWorks@UARK

Graduate Theses and Dissertations

8-2022

## **Etching Process Development for SiC CMOS**

Weston Reed Renfrow University of Arkansas, Fayetteville

Follow this and additional works at: https://scholarworks.uark.edu/etd

Part of the Electronic Devices and Semiconductor Manufacturing Commons, Engineering Mechanics Commons, and the Semiconductor and Optical Materials Commons

### Citation

Renfrow, W. R. (2022). Etching Process Development for SiC CMOS. *Graduate Theses and Dissertations* Retrieved from https://scholarworks.uark.edu/etd/4636

This Thesis is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu.

Etching Process Module Development for SiC CMOS

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Materials Science

by

Weston Reed Renfrow Missouri State University Bachelor of Science in Physics/Engineering & Applied Physics, 2019

### August 2022 University of Arkansas

This thesis is approved for recommendation to the Graduate Council.

H. Alan Mantooth, Ph.D. Dissertation Director

Zhong Chen, Ph.D. Committee Member Greg Salamo, Ph.D. Committee Member

Matthew Leftwich, Ph.D. Ex-Officio Member The following signatories attest that all software used in this thesis was legally licensed for use by Weston Renfrow for research purposes and publication.

Mr. Weston Renfrow, Student

Dr. H. Alan Mantooth, Thesis Director

This thesis was submitted to http://www.turnitin.com for plagiarism review by the TurnItIn company's software. The signatories have examined the report on this thesis that was returned by TurnItIn and attest that, in their opinion, the items highlighted by the software are incidental to common usage and are not plagiarized material.

Dr. Matthew Leftwich, Program Director

Dr. H. Alan Mantooth, Thesis Director

List of Published and Planned Papers Used in this Dissertation

Part of Chapter 1, Chapter 3, and Chapter 4 is planned to be published in:

"ICP Etching of Intrinsic and Doped SiC With Chlorine-Based Gas Compositions" Renfrow R., Di Mauro A., Rice T., Chen K, Mantooth H. A., Chen Z., (2022)

### Abstract

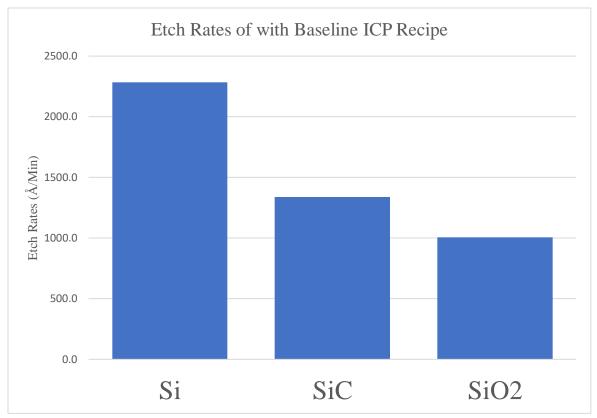

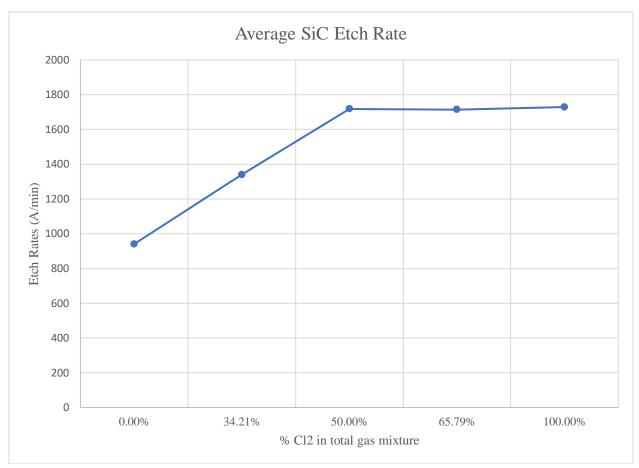

Silicon Carbide (SiC) is an exciting material that is growing in popularity for having qualities that make it a helpful semiconductor in extreme environments where silicon devices fail. The development of a SiC CMOS is in its infancy. There are many improvements that need to be made to develop this technology further. Photolithography is the most significant bottleneck in the etching process; it was studied and improved upon. Etching SiC can be a challenge with its reinforced crystal structure. Chlorine-based inductively coupled plasma (ICP) etching of intrinsic SiC and doped SiC, SiO<sub>2</sub>, and Silicon has been studied. A baseline chlorine gas recipe containing Cl<sub>2</sub> and BCl<sub>3</sub> was studied and characterized. The average SiC etch rate of this recipe was found to be 1330 Å/min. The Cl<sub>2</sub> concentration was then varied to over five total experimental recipes. The results show that Cl-based gas produces little change in etch rates between intrinsic SiC and doped SiC except for the recipe containing 66% Cl<sub>2</sub>. This recipe provided etch rates that were proportional to doping concentration but independent of the dopant species. These results also showed a high critical dimension bias due to sidewall passivation. Buffered oxide etching (BOE) was conducted on SiO<sub>2</sub> for the purposed of etching field oxide, gate oxide, and hardmasks. The studies of BOE were inconsistent with the results found in the literature. Instead, an ICP method and a liftoff method was used on SiO<sub>2</sub> as an alternative. Results from this study found that the desired  $SiO_2$  etching can be achieved without the use of BOE, which can be hazardous. The ICP etch rate of SiO2 was 1006 Å/min. Both ICP and liftoff had higher quality pattern transfer than BOE. The future works of these results have also been described.

Acknowledgments

I would like to acknowledge my advisor, Dr. H. Alan Mantooth, for giving me this opportunity to research with his team and for giving me a summer off to intern with a company called Ten-Nine Technologies. Both have been incredible experiences. I have grown so much in the last two and a half years.

I would like to acknowledge Dr. Zhong Chen for his weekly advisement meetings. His patience, direction, and experience were beneficial in the moments of confusion and frustration.

I would like to thank Murtadha Alher for stepping in to manage the Nanofab lab when no one else was willing. There were times I didn't know if I would have access to a lab again. I didn't think it was possible to graduate. Murtadha took on the responsibility and made the research possible for me. This thesis would be blank pages if it wasn't for him.

I would like to thank the members of my research group, Kevin, Tanner, Anthony, and Hayden. They were always there to help me and answer questions when I needed them. I asked too much of them sometimes, yet they were always there to assist me with long days in the lab. Photolithography would have been a nightmare without these men.

Lastly, I would like to thank John Ransom. His fabrication expertise was particularly helpful near the end of my research. He was under no obligation to answer my questions, yet our discussions were enlightening and enjoyable.

### Dedication

This thesis is dedicated to my parents, Bill and Carol Renfrow. These last two and a half years have been difficult. There have been the highest highs and lowest lows. Their unconditional love and support were the only things I could count on during this time. I owe everything to them.

### Table of Contents

| Chapter 1.  | Introduction                                   |

|-------------|------------------------------------------------|

| Chapter 2.  | Background and Literature Review               |

| Chapter 3.  | Etching Process Methods                        |

| 3.          | 1 Photolithography24                           |

| 3.          | 2 Inductively Coupled Plasma                   |

| 3.          | 3 Buffered Oxide Etching                       |

| Chapter 4.  | Etching Process Module Development and Results |

| 4.          | 1 Photolithography                             |

| 4.          | 2 Inductively Coupled Plasma                   |

|             | 4.2.1 ICP Characterization Study               |

|             | 4.2.2 ICP Gas Flow Composition                 |

| 4.          | 3 Oxide Etching Development                    |

|             | 4.3.1 Buffered Oxide Etching                   |

|             | 4.3.2 Oxide Etching with ICP                   |

| Chapter 5.  | Conclusion                                     |

| 5.          | 1 Summery73                                    |

| 5.          | 2 Conclusion and Future Outlook                |

| Bibliograph | y                                              |

| Appendix A Description of Research for Popular Publication                                | 85 |

|-------------------------------------------------------------------------------------------|----|

| Appendix B Executive Summary of Newly Created Intellectual Property                       | 86 |

| Appendix C Potential Patent and Commercialization Aspects of Listed Intellectual Property |    |

| Items                                                                                     | 87 |

| Appendix D Broader Impact of Research                                                     | 88 |

| Appendix E Microsoft Project for MS Material Science Degree Plan                          | 90 |

| Appendix F Identification of All Software used In Research and Thesis Generation          | 92 |

| Appendix G All Publications Published, Submitted, and Planned                             | 93 |

| Appendix H Photolithography Traveler                                                      | 94 |

| Appendix I ICP Procedure                                                                  | 98 |

# Table of Figures

| Figure 2.1 NMOS Enhancement Mode                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.2 SiC CMOS                                                                                                                  |

| Figure 2.3 Anisotropic etch profile vs. Isotropic etch profile                                                                       |

| Figure 2.4 RF Waveform at bottom electrode (Nojiri, 2012)                                                                            |

| Figure 2.5 Illustration of the 5 parameters to measure for evaluating an etch (Nojiri, 2012) 21                                      |

| Figure 3.1 AutoCAD generated image of photomask design that will be used                                                             |

| Figure 3.2 Photomask being loaded into aligner                                                                                       |

| Figure 3.3 Photoresist on Si wafer using original photolithography process                                                           |

| Figure 3.4 High magnification image of photoresist on Si wafer                                                                       |

| Figure 3.5 SiC etch using the baseline ICP recipe with red line indicating the path of profilometer measurements                     |

| Figure 3.6 Etch depth for intrinsic SiC etching with the baseline recipe                                                             |

| Figure 3.7 Si Substrate with SiO2 etched with BOE for 20 s, 40 s, and 60 s                                                           |

| Figure 3.8 Detail image of the Si substrate with an SiO2 layer that had been etched for 60 s 37                                      |

| Figure 4.1 Photoresist that was developed with AZ 300 MIF for 120 s 41                                                               |

| Figure 4.2 Photoresist that was developed with AZ 726 MIF for 35 s 41                                                                |

| Figure 4.3 Average etch rates of the baseline ICP recipe                                                                             |

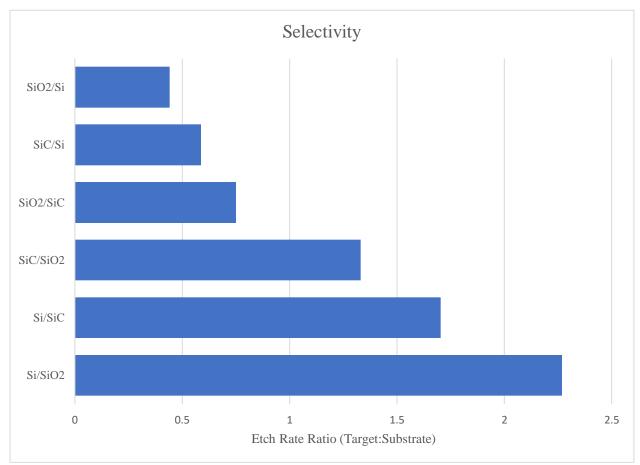

| Figure 4.4 Selectivity between SiC, Si, and SiO <sub>2</sub>                                                                         |

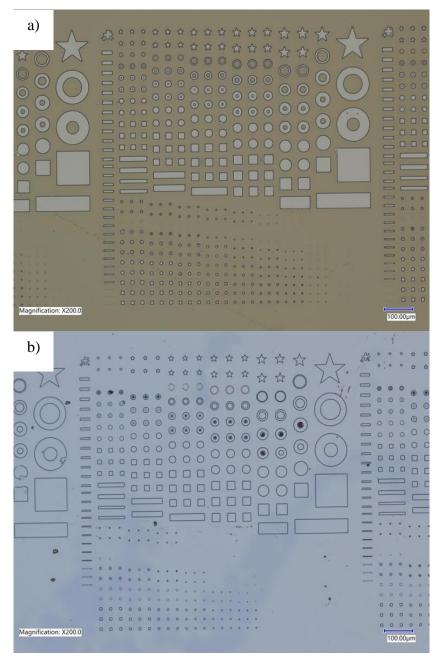

| Figure 4.5a) SiC with photoresist applied before an ICP etch. b) the same SiC sample after the ICP etch with the photoresist removed |

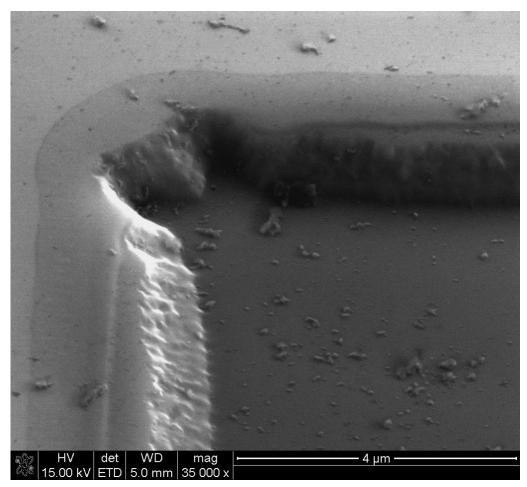

| Figure 4.6 SEM image N+ SiC etched with the baseline ICP recipe shown a 52° angle 49                                                 |

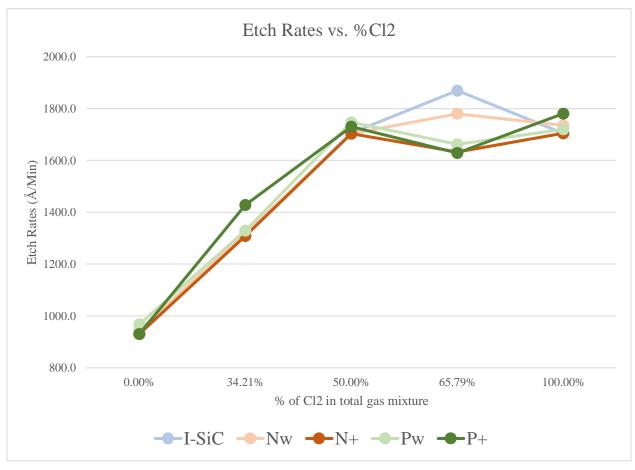

| Figure 4.7 Average SiC etch rate by chlorine percentage                                                                              |

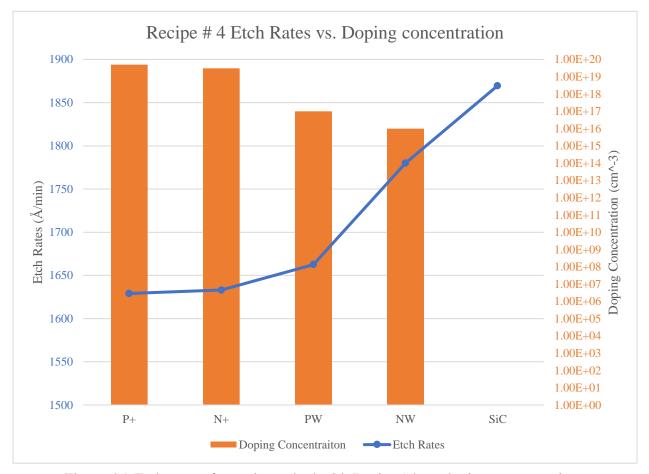

| Figure 4.8 Average SiC etch rates                                                                                                    |

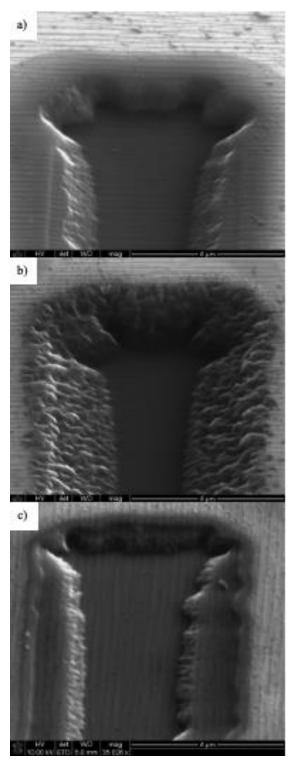

| Figure 4.11 SEM images of the etch profile of P+ SiC samples etched with a) Recipe #2 b)<br>Recipe #3 and c) Recipe #4                                                                                                                                                                                                                             |

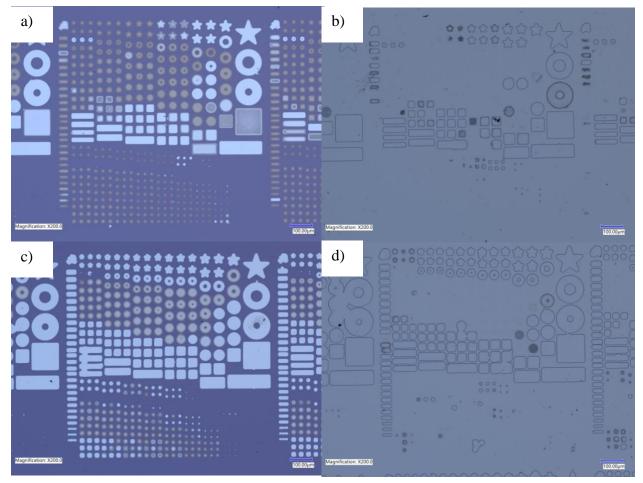

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4.12 a) Si substrate with an SiO2 layer that had been etched with BOE for 40 s. b) the same sample that had been etched with ICP for 30 s then the SiO2 hardmask was removed. c) a Si substrate with an SiO <sub>2</sub> layer that had been etched with BOE for 60s. d) the same sample after a 30 s ICP etch and the hardmask was removed |

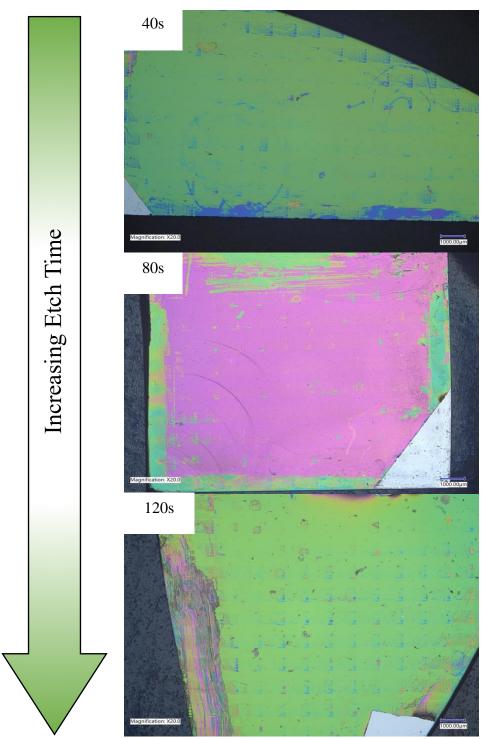

| Figure 4.13 Oxide samples that were etched in 10% BOE solution for 40s, 80s, and 120s 64                                                                                                                                                                                                                                                           |

| Figure 4.14 Oxide samples that were etched in 10% BOE solution for 40s, 80s, and 120s 64                                                                                                                                                                                                                                                           |

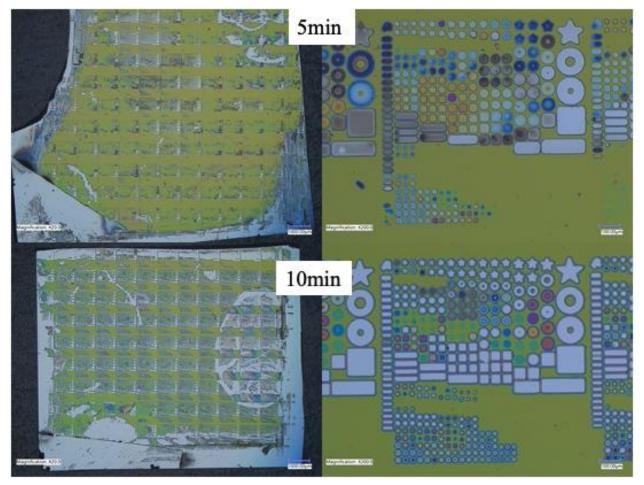

| Figure 4.15 The two samples that were etched with the 10% solution for 5 min and 10 min 66                                                                                                                                                                                                                                                         |

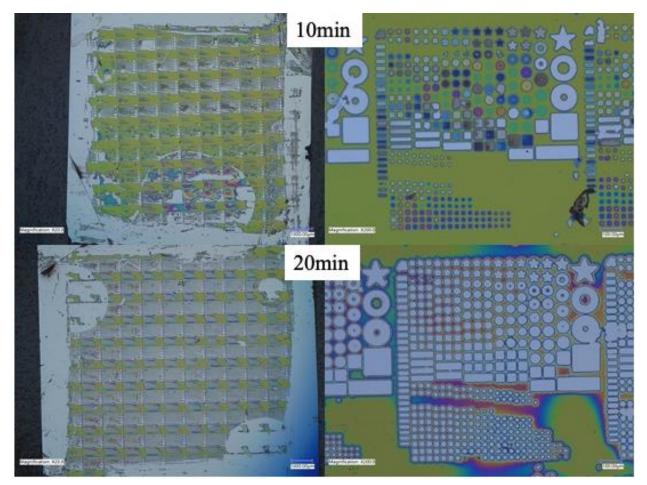

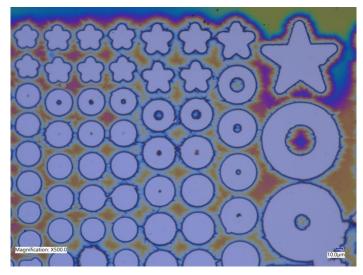

| Figure 4.16 Detail image of the pattern transfer from the 20 min etch with 5% BOE solution 68                                                                                                                                                                                                                                                      |

| Figure 4.17 The two samples that were etched with the 5% BOE solution for 10 min and 20 min                                                                                                                                                                                                                                                        |

| Figure 4.18 Oxide etched with ICP baseline recipe                                                                                                                                                                                                                                                                                                  |

| Figure 4.19 a) Si substrate with layer of SiO2 etched with ICP after the etch with photoresist removed. b) The same Si substrate after the SiO2 layer was removed                                                                                                                                                                                  |

| Figure 4.20 a) Si substrate with photoresist and SiO2 deposited. b) the same substrate after liftoff                                                                                                                                                                                                                                               |

### Chapter 1. Introduction

In 1906, J. C. Bose patented his design for the first form of radio wave communication. Cat's-whisker crystal radio detectors were the first commercial use of silicon as a semiconductor (Emerson, 1998). The first transistor was invented in 1947 by J. Bardeen, W. Brattain, and W. Shockley at Bell Labs. It was about the size of a thumbnail. Only 50 years later, over 9 million could be made on a single silicon wafer (Cressler, Siliocn Earth, 2009). Silicon is the most common element in the galaxy and the second most common on earth. It makes up over 27% of the earth's crust and is found in rocks and soils. It can also be found naturally in plants and animals (Silicon, n.d.). Silicon has become one of the most important electronic materials on earth for several different reasons: It is cheap, nontoxic, mechanically stable, has good thermal properties, and insulating SiO<sub>2</sub> can easily be grown on silicon substrates. For these reasons, the number of silicon transistors has grown to over ten quintillions in only 70 years since the invention of the first transistor (Cressler, Siliocn Earth, 2009). Silicon may be a miracle material for everyday use on earth, but silicon has limitations when brought to extreme conditions.

There are few conditions that are too harsh for silicon-based electronics. Developing electronics that can function in these harsh environments is essential. Consider satellites that are operating in earth's orbit where there is a high level of radiation, or a spacecraft designed to travel to the surface of Venus where temperatures reach 460°C and pressures of 9.4MPa (Neudeck, et al., 2016). These extreme environments are rare, but electronic devices that can withstand extreme environments are necessary for scientific research and development.

There are many extreme conditions that should be considered when designing electronics. The material used should be able to maintain functionality met with these conditions: high radiation or magnetic fields, high temperatures, low temperatures, and corrosive chemicals.

Radiation can ionize the material or displace the atomic lattice, changing its structure. These environments are common in both earth's orbit and deep space. Communication satellites and spaceships are commonly met with radiation-rich environments.

Commercial operating temperatures for electronics are between 0°C to 85°C. Some commercial applications call for -55°C to 125°C. The material should be able to function well outside those ranges. The surface of Mars can get as low as -143° C and deep space can reach - 146°C. The automotive and aerospace industry requires operation at high temperatures up to 300°C on earth, while the surface of Venus can reach up to 600°C (Cressler & Mantooth, Extreme Environment Electronics, 2013). All electronic materials and packaging used in the device should handle these temperatures together without expanding or contracting to the point of destruction.

Consider a chemical sensor that is designed to be ingested by a human. The chemicals in the body are corrosive and can dissolve electronics. The packaging of the device cannot protect it because the sensor must be in contact with the chemical. In this situation, the material in the device must be able to withstand the corrosive material while also being non-toxic (Cressler & Mantooth, Extreme Environment Electronics, 2013). Many of these conditions exist simultaneously in a single environment. The electronic device must be durable to withstand many of these conditions at once. A different material must be used in situations where silicon will not function properly. One material that is gaining interest is Silicon Carbide.

Silicon carbide (SiC) has grown in popularity for being a promising material in hightemperature and extreme environment devices. SiC is a wide bandgap group IV semiconductor material with a low intrinsic carrier concentration compared to silicon. SiC has high thermal conductivity, allowing for quicker heat removal. Having a high drift saturation velocity allows SiC devices to have higher switching speeds with less loss of power. SiC has a higher critical electric field than silicon; therefore, a much higher doping concentration can be achieved. High doping concentrations cause the on-resistance to improve in SiC devices, which means a SiC power device has lower conduction losses and higher efficiency. These properties allow SiC devices to be used in extreme conditions where silicon devices would lose functionality. For relatively short time durations, many SiC devices have been shown to function at temperatures as high as 600°C. Theoretically, SiC devices could function as hot as 800°C (Cressler & Mantooth, Extreme Environment Electronics, 2013). These devices have applications in a wide range of industries, such as aerospace, power generation, and transportation. Although SiC has many unique benefits that make it a suitable material for extreme environment electronics, there are many drawbacks to using SiC.

SiC can be expensive. A single 6-inch wafer of high-quality SiC can cost as much as \$1,500 (Kulu, 2020). This can make prototyping SiC power devices a costly endeavor. They are expensive compared to the low price of \$2 per square inch of Silicon wafers (Mulay, 2022). SiC can also be a difficult material to work with. SiC is the third hardest composite material in the world. This means SiC requires more energy and higher temperatures during the manufacturing process (Lovati, 2021). This makes it one of the most fragile as well. Silicon carbide wafers shatter easily if not taken care of. SiC is more difficult to etch than other semiconductor materials. Its etch rates are slower, making it too slow for deep etching (Tadjer, et al., 2017).

Most published studies on plasma etching SiC deal with fluorinated gas mixtures such as SF<sub>6</sub>, NF<sub>3</sub>, CHF3, and CF<sub>4</sub> (Yih & Steckl, 1995; Kim, et al., 2004; Osipov, et al., 2020; Camara & Zekentes, 1959-1963; Tadjer, et al., 2017; Khan & Adesida, 1999; Ozgur & Huff, 2017; Wang, et al., 1998; Ruixue, Yintang, & Ru, 2009; Pan & Steckl, 1990). SiC etching studies using chlorine-based gases, especially Cl<sub>2</sub>/BCl<sub>3</sub> mixtures, have been less studied (Ekinci, et al., 2014). This thesis aims to understand the etching mechanisms of SiC with Cl<sub>2</sub>/BCl<sub>3</sub> plasmas. This thesis aims to improve the etching process modules involved with SiC CMOS fabrication. These topics include photolithography development, inductively coupled plasma etch characterization, buffered oxide etching, and other methods to etch silicon dioxide.

### Chapter 2. Background and Literature Review

Intrinsic semiconductors cannot conduct electricity by themselves. In order for semiconductor devices to function properly, the device must contain a combination of doped semiconductor materials, which are crystals that intentionally have added impurities. N-type semiconductors contain impurities that displace the crystal atoms for new atoms that give the crystal extra electrons. In the case of SiC, nitrogen is used. P-type semiconductors are given impurities that contain holes, which are atoms that can easily take on an additional electron. SiC is given Al. Both electrons and holes are considered charge carriers, meaning both can flow throw the crystal to carry chare, creating an electrical current. Holes are thought of as a moving species, but electrons are the only species that flow. When a P/N junction is formed, the interface between the two materials becomes a depletion region which is a region that lacks charge carriers. Under the right conditions, a doped semiconductor can invert to become the opposite type. A P-type can act like an N-type, for example. This is known as an inversion region (Shroder, 2006).

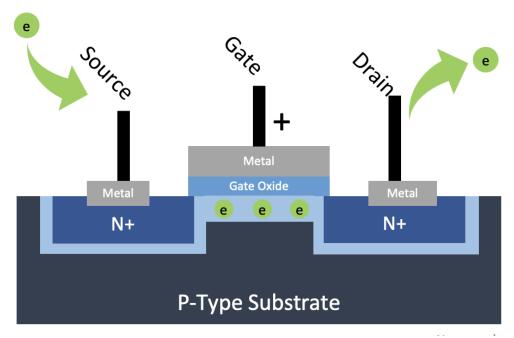

To understand a SiC CMOS, first, a MOSFET must be understood. A MOSFET, metaloxide-semiconductor field-effect transistor, can be an N-channel MOSFET (NMOS) or a P-Channel MOSFET (PMOS). An NMOS in enhancement mode is designed with a P-type substrate and two heavily doped N+ regions making up the source and drain terminals. The P/N junction naturally forms the depletion region. Between the two terminals, a layer of oxide and a layer of metal is deposited to form the gate terminal. When a positive voltage greater than the threshold voltage is applied to the gate terminal, a capacitance effect takes place that pushes the holes in the substrate away from the surface. A depletion region is formed that spans both N+ regions. When the source voltage is great enough, an inversion region then spans through the depletion region. Now, electrons can flow through the source terminal to the drain terminal (Bishop, 2020). Figure 2.1 illustrates this.

Figure 2.1 NMOS Enhancement Mode

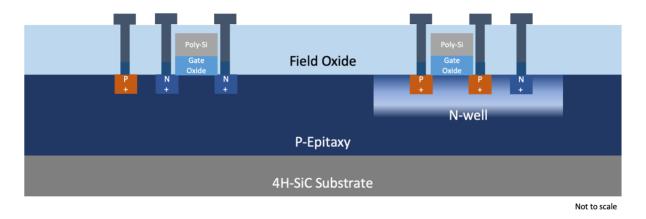

When a positive voltage greater than the threshold voltage is applied to the gate terminal, the current can flow. When there is not a high enough voltage current cannot. This transistor is essentially a switch with no moving parts. Enough transistors organized in specific patterns can be used for digital computations. A PMOS transistor is designed to be the opposite. The gate terminal requires a negative voltage for current to flow, but the charge carriers are holes, not electrons. A CMOS (Complementary MOSFET) is an NMOS and PMOS fabricated together on the same substrate. A CMOS adds body terminals to allow for the capacitance effect in the gate terminals, as well as field oxide to insulate the entire circuit. Figure 2.2 shows the layout of the SiC CMOS.

Figure 2.2 SiC CMOS

The fabrication of the SiC CMOS requires various materials to be etched. One example is etching through the field oxide to the surface of the substrate. In an ideal situation, the etch would be perfectly anisotropic and stop at the surface. However, with plasma etching, there is a probability of over-etching to the SiC surface. So, the etch profile of SiC must also be studied. The etching process modules that this thesis will help develop are the photolithography process, the chlorine-based ICP etch recipe characterization, and oxide etching for the purpose of field oxide, gate oxide, and hardmask deposition. Photolithography is an essential step in semiconductor fabrication. It is repeated between 10 and 40 times in the process of fabricating a single circuit. For large fabs owned by major semiconductor companies, photolithography makes up approximately 30% of the manufacturing cost (Mack, 2007). Photolithography is used for ion implantation, film deposition, and etching. Having an accurate and reliable photolithography process is critical in IC fabrication. Improving this was the first step in developing the etching process modules. The features and resolution of a mask is determined by the photolithography process. A higher resolution allows for smaller feature sizes which can reduce the size of the device. Moore's law predicts that devices reduce in size by half every year. As Moore's law progresses, there is a demand for a more refined photolithography process. The resolution and accuracy of the photolithography process must continue to improve.

The photolithography process varies by types of photoresists, exposure method, and process module requirements, but the general process follows these main steps. Clean substrate, spin coat, post-apply bake (PAB), exposure, post-exposure bake (PEB), then development. Once the photoresist is successfully applied and developed, the substrate undergoes the next fabrication step, etching, implantation, etc., then the photoresist is removed, and, if needed, the entire process is repeated.

Photolithography uses a light-sensitive polymer called photoresist to develop a threedimensional mask that is then used to protect areas on the substrate from being etched. The photoresist reacts to intense UV light and becomes soluble in a developer solution. There are three main ways that this is done: contact lithography, proximity lithography, and projection lithography.

Contact lithography is the most rudimentary method of lithography and is the method that will be described further in the experimental portion of this thesis. It involves pressing a photomask tightly to the substrate to ensure there are no gaps. It is then shining an intense light through the photomask and developing the image that is printed on the photomask. Other methods include proximity lithography, which has a gap between the substrate and photomask. And projection lithography, which is far more popular (Mack, 2007). It uses a lens between the photomask and the substrate that can focus the light to form a sharper image.

Contact aligners use a photomask which is a transparent screen that is printed with a pattern. The wafer is placed on the loading tray and can be finely adjusted to ensure precise alignment. Once the wafer is placed, contact is initiated. The photomask comes in direct contact with the wafer, and pressure is applied to ensure there is no space between the photomask and the wafer. Then an intense light is shined for a desired amount of time. Contact alignment produces a high resolution depending on the wavelength of the light (Mack, 2007).

Projection alignment uses a lens between the photomask and the wafer that focuses the light to a much higher resolution. There are two types of projection alignment: scanners and steppers. Scanners use a photomask that contains the entire pattern to be used over the whole wafer but scans through portions of the wafer at a single time. It can expose small areas of the wafer at once. Stepping uses a similar process, but the photomask only contains a small fraction of the entire mask. It then steps through each section of the wafer, repeating the same pattern until the entire mask is exposed. A hybrid, step-and-scan method has become the choice method for lithography today. This method uses a stepper mask and scans the mask in one direction before moving to a new location on the wafer and repeating the scan (Mack, 2007).

The photolithography process uses a photoresist, a light-sensitive polymer, to coat the surface of a semiconductor wafer. The wafer is uniformly coated using a spin coat method, where the rotational speed of the wafer determines the thickness of the photoresist. As the wafer spins, the photoresist is added. The centrifugal force pushes the liquid photoresist to the edges of the wafer. Excess photoresist flies from the substrate. The centrifugal forces, relative to the speed of rotation and mass of the photoresist, are met with frictional forces relative to the surface of the substrate and viscosity of the liquid. Once the forces reach an equilibrium, the photoresist ceases to spread, and a uniform layer of photoresist is applied. The thickness of the photoresist can be controlled by changing the rotational speed of the wafer. (1) shows the relationship of thickness to viscosity ( $\nu$ ) and spin speed ( $\omega$ ) (Mack, 2007).

thickness

$$\propto \frac{v^{0.4}}{\omega^{0.5}}$$

(Equation 1)

Photoresist comes in two varieties, positive and negative. For a positive photoresist, the light exposure reacts with the photoresist, causing it to be soluble in a developer solution. The product is washed away in the developer solution leaving behind the three-dimensional pattern. A negative photoresist reacts with the light exposure to become insoluble in a developer solution. The photoresist is washed away by the developer, while the product remains to leave behind the three-dimensional pattern.

Determining the proper exposure time is essential for accurate pattern transfer with a high resolution. Exposure time that is too short will not fully develop the features. Not enough carboxylic acid will be produced, and the photoresist will not be soluble in the developer solution. Exposure time that is too long will over-develop the mask. Features will not be accurately transferred. Edges will be rounded, and images will be distorted. To determine the proper exposure time, we must consider the optical absorption properties of the material.

As light passes through a material, the intensity of the light (or photon flux) decreases. This is described in Lambert's law shown in equation two, where  $\alpha$  is the absorption coefficient for the material, *x* is the direction light is traveling, and *I* am the intensity or photon flux of light (Mack, 2007; Kasap, 2018).

$$\frac{dI}{dx} = -\alpha I \tag{Equation 2}$$

A positive photoresist is made up of three different parts: novolac resin (*R*), a sensitizer (*M*), and a liquid solvent (*S*). The novolac resin is used to increase the structural properties and etch resistance of the mask. The solvent is a photoactive compound (PAC), typically diazonaphthoquinone (DNQ). It reacts with the UV light, g-line (436nm) or i-line (365nm), to create a carboxylic acid (P) which is soluble in the developer solution. As the concentration of DNQ is converted to a carboxylic acid, concentration P grows while concentration M reduces. Equation 3 shows the total concentration remains constant. The liquid solvent is in place to assist with spin coat application. A liquid is much easier to apply in a uniform thickness. Most of the solvent is baked out during the post-apply bake. The result is a hardened mask that is resistant to etching. Each of these parts determines how light is absorbed into the material.

$$P = M_0 - M \tag{Equation 3}$$

The Beer law for the absorption coefficient of absorbing material in a nonadsorbing solvent is shown to be proportional to the sum of each of the concentrations of the absorbing materials times the material's absorption coefficient (Mack, 2007). Beer's law for N number of

solvents is shown in equation 4, where  $a_i$  is material *i*'s absorption coefficient, and  $C_i$  is material *i*'s concentration. It can be applied to the three parts in a photoresist shown in equation 5, which can be written as equation 6.

$$\alpha_{solution} = \sum_{i=1}^{N} a_i C_i$$

(Equation 4)

$$\alpha_{solution} = a_M M + a_P P + a_R R + a_S S$$

(Equation 5)

$\alpha_{solution} = Am + B$  (Equation 6)

#### Where,

$$A = (a_M - a_P)M_0$$

(Equation 7)

$$B = (a_P M_0) + a_R R + a_s S$$

(Equation 8)

$$m = \frac{M}{M_0}$$

(Equation 9)

A and B are two very important parameters for determining the absorption of light for photoresists. They are known as the bleachable (A) and nonbleachable (B) absorption coefficients. The bleachable absorption coefficient tells how the color of the photoresist changes with exposure. If A is positive, the photoresist will get lighter. If A is negative, the photoresist will get darker. This seemingly insignificant detail has a large impact on determining the exposure rate of the photoresist. Because the photoresist changes color as it is being exposed, it also changes its exposure absorption coefficients. These parameters must be known to determine the exposure rate of the material.

These two parameters are not all that are needed to understand the absorption of the photoresist. To further understand the full picture, we must shift from the macroscopic scale to the microscopic scale. We see that while DNQ is being converted to a carboxylic acid, there is a short-lived intermediate chemical that is formed. The concentration of which is denoted as  $M^*$ .

The new chemical reaction is shown in equation 10. Where  $k_1$ ,  $k_2$ , and  $k_3$  are rate constants for each reaction.

$$M \underset{k_1}{\overset{k_2}{\leftarrow}} M^* \xrightarrow{k_3} P$$

(Equation 10)

Now, a set of differential equations can be written to describe how the concentrations change with time in equation 11. Some initial conditions can be written in equation 14, and one assumption can be made dealing with the concentration of the intermediate chemical in equation 16. Because the intermediate chemical is short-lived (only 10<sup>-8</sup>s or less (Mack, 2007)), each molecule exists for only a short time before being converted to a carboxylic acid. Therefore, the concentration remains mostly constant throughout the entire reaction. Solving these equations gives equation 17.

$$\frac{dM}{dt} = k_2 M^* - k_1 M \qquad (Equation 11)$$

$$\frac{dM^*}{dt} = k_1 M - (k_2 + k_3) M^*$$

(Equation 12)

$$\frac{dP}{dt} = k_2 M^* \tag{Equation 13}$$

$$M(t=0) = M_0$$

(Equation 14)

$$M^*(t=0) = P(t=0) = 0$$

(Equation 15)

$$\frac{dM^*}{dt} = 0$$

(Equation 16)

$$\frac{dM}{dt} = -\frac{k_1 k_3}{k_2 + k_3} M = -KM$$

(Equation 17)

The variable K is the overall rate constant. K is proportional to the intensity of radiation. By the Grotthus-Draper law, only the light that is absorbed into the material can create a chemical change in the material (Rennie & Law, 2016). The amount of that that is absorbed is proportional to the energy flux or intensity of light and the surface area that is absorbing light. Intensity can be written in terms of photon flux and energy per photon  $(hc/\lambda)$ , shown in equation 18. Where  $\varphi_M$  is the density of photons being absorbed by material M, and v is the velocity the photons are traveling (the speed of light). The amount of light that is absorbed by material M is also dependent on the molecular absorption cross-section of material M,  $\sigma_M$ . So, equation 17 can now be re-written as dm/dt in terms of Intensity, the absorption cross-section, and photon flux,  $\Phi$ , equation 19. Solving equation 20 for *m* leads to equation 21, which reveals an exponential relationship between *m* and *t*. equation 19 can be simplified to equation 20 with the addition of the constant C. By relating the absorption cross-section to molar absorptivity, C can be made more useful in terms of the absorption coefficient,  $a_M$ , and Avogadro's number, N<sub>A</sub>.

$$I = v\phi_M\left(\frac{hc}{\lambda}\right)$$

(Equation 18)

$$\frac{dm}{dt} = -\Phi \sigma_M \left(\frac{\lambda}{hc}\right) Im = -\frac{\Phi a_M}{N_A} \left(\frac{\lambda}{hc}\right) Im \qquad (\text{Equation 19})$$

$$\frac{dm}{dt} = -CIm \tag{Equation 20}$$

$$m = e^{-Clt}$$

(Equation 21)

$$C = \Phi \sigma_M \left(\frac{\lambda}{hc}\right) = \frac{\Phi a_M}{N_A} \left(\frac{\lambda}{hc}\right)$$

(Equation 22)

The constant C in equation 20 is known as the exposure rate constant. It tells how the photoresist changes with time. It is the third and final parameter for photoabsorption in a photoresist. These are known as the Dill parameters or ABC parameters. These three parameters are needed to fully understand how light is absorbed into the photoresist.

The amount of exposure needed to complete the reaction is determined by the exposure dose and the thickness of the photoresist. Exposure dose can be found by integrating equation 21 to give equation 23. The exposure dose is equivalent to the intensity of the light times time. For a given light intensity, the exposure dose can be easily calibrated by adjusting the time the photoresist is exposed to the intense light. Since the photoresist changes color in relationship to the bleachable absorption coefficient, the light passing through the photoresist changes intensity as the material changes. The concentration in the sensitizer changes at different rates throughout the material. Thus the difference in intensity at the top layer of photoresist I(0), and the bottom layer of photoresist I(x) must be determined. To do this, we apply Beer's law equation 6 to Lambert's law equation 2 to give equation 24 and solve it analytically. The result shown in equation 25 shows the relationship between the intensity at the top layer of the photoresist and the bottom layer of the photoresist. As can be expected, the difference in intensity is dependent on photoresist thickness and the bleachable coefficient.

$$Dose = \int_0^t I dt = It$$

(Equation 23)

$$\frac{dI}{dx} = -(Am + B)I$$

(Equation 24)

$$\frac{I(z)}{I(0)} = \left(\frac{m(z)}{m(0)}\right) e^{-Az}$$

(Equation 25)

With these equations derived from Lambert's law of absorption and Beer's law, the rate at which the DNQ-based photoresist changes with exposure can be calculated. Parameter A tells the bleachable coefficient and how the photoresist lightens or darkens during exposure. B tells nonbleachable coefficient, how solvents react to exposure. C tells exposure rate and how the fraction of reactant and product change with time. With a given light intensity and photoresist thickness, the exposure time can be calculated.

For negative photoresists, the areas that are in contact with the light are the areas that remain after the development process. The areas that were not in contact with the light are the areas that are washed away. This is because a carboxylic acid is formed during the post-exposure bake. It cross-links with the resin. Therefore, it is soluble in the developer solution and can be washed away (Mack, 2007). The proper exposure time can be determined for a specific photoresist and used to create a high-resolution mask for etching.

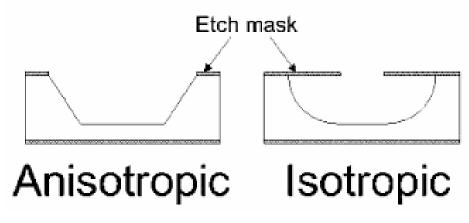

When etching semiconductor devices, the device's functionality will depend on the quality of the etch. Anisotropic etch means that the etch rate is constant in all directions. The result is a rounded profile. An anisotropic etch means the etch rate is higher in one direction and, ideally, zero in all other directions. These two etch profiles are represented in

Etching can be done in two ways, wet etching or dry etching. Wet etching uses liquid chemicals such as hydrazine (N<sub>2</sub>H<sub>4</sub>), potassium hydroxide (KOH), or Tetramethylammonium hydroxide (N(CH<sub>3</sub>)<sub>4</sub>OH, TMAH). to etch SiO<sub>2</sub>, BOE, buffered oxide etching, uses ammonium fluoride (NH<sub>4</sub>F) mixed with hydrofluoric acid (HF) to etch isotropic profile (Ekström, 2019). Wet etching is used to remove trace layers of oxide from the surface of the substrate. BOE can be used to etch the insulating SiO<sub>2</sub> layer. Currently, there is no conventional way of using room temperature wet chemicals for etching patterns into SiC. Dry etching can be done using reactive ion etching (RIE). Variations of RIE exist as inductively coupled plasma (ICP) or magnetically

Figure 2.3 Anisotropic etch profile vs. Isotropic etch profile

enhanced reactive ion etching (MERIE). These use plasma to pattern the material and allow for etching high aspect ratios and deep vias. Plasma etching works by three main mechanisms: first, electrons are dissociated from the gas mixture into a plasma. Second, a high etch rate is achieved by ion bombardment, which breaks bonds at the top monolayers of the substrate. Third and most advantageous, an anisotropic etch is achieved by the electric field of the ion sheath in the chamber (d'Agostino, et al., 2008).

RIE etching is a more common method for etching SiC that uses both physical and chemical components. It uses RF current to induce a magnetic field which creates a plasma. The magnetic field forces the plasma in a singular direction toward the substrate, where the ions react with the surface of the material and create an anisotropic etch profile. RIE uses a combination of F-, Cl-, or Br- based chemicals for both Si and SiC. F- based plasmas give a higher etch rate and more isotropic profile, while Cl- based plasmas give a more anisotropic profile. (Ekström, 2019)

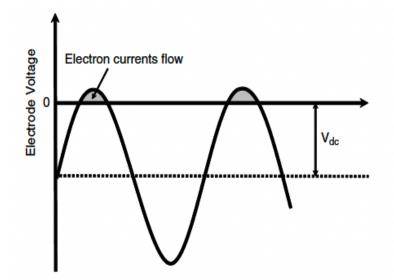

Parallel plate RIE is designed with a top electrode that is grounded and an opposing bottom electrode, where the wafer sits. RF current is applied to the bottom electrode through a

Figure 2.4 RF Waveform at bottom electrode (Nojiri, 2012)

blocking capacitor at a frequency of 13.56MHz. The capacitor causes the electrode to gradually shift towards a negative potential. This is known as a direct current bias ( $V_{dc}$ ). The resulting RF current at the bottom electrode is shifted in the negative direction. The potential is only positive for a short time each cycle while mostly staying negative. Figure 2.4 shows the voltage at the lower electrode given by the RF power through the blocking capacitor. The top portion of the etching chamber is fitted with a showerhead that releases the etching gases. The RF power causes an acceleration in the electrons that ionizes the gas. A plasma is created containing cations, electrons, neutral atoms, and sometimes radicals if the energy is high enough. Electrons, being 100,000 times smaller than ions, can change directions quickly and follow the RF oscillation provided by the electric field. They can flow in both directions towards both electrodes. Ions have much more mass than electrons. They do not have enough time to oscillate directions and are therefore continuously moving in a single direction towards the bottom electrode. Electrons are pushed away from the bottom electrode when the electrode has a negative potential. Because of V<sub>dc</sub>, very few electrons are in the region near the electrode at any given time. This region is known as the ion sheath because there are few ion-electron collisions in this region; thus, no light is emitted (Nojiri, 2012). The plasma is at equipotential, meaning ions flow randomly throughout. At the ion sheath region, the reactive ions move in a single direction without interference from elections, allowing the wafer to be etched anisotropically.

Inductively coupled plasma (ICP) etching is a type of RIE where the plasma is generated independently from the RF power of the bottom electrode. An induction coil is added around the etch chamber to induce a magnetic field vertically through the chamber. This magnetic field is what induces an electric field inside the chamber, which produces the plasma. The RF power from the electrode is what directs the motion of the ions. This added induction allows for

independent control of the plasma creation. A higher density plasma can be created using ICP (Nojiri, 2012). ICP allows for the operator to control many different parameters for the etch. Various types of materials or etch demands may require changes in the etch recipe. The etch can be adjusted to fit specific needs by changing various parameters of the etch recipes, such as chemical composition, chamber pressure, and RF power.

Chemical composition in the chamber can affect the etch profile. As the name implies, reactive ion etching is made up of ions traveling in a single direction and hitting the surface of the material, which causes a reaction, and the wafer material is removed. Ion-assisted etching makes up a large percentage of the total etching mechanism. Etching also occurs by radical atoms and physical sputtering by ions, but these mechanisms contribute little to the overall etch rate. Ion-assisted etching is what gives the etch an anisotropic etch profile. This mechanism depends on the target material and the gasses used. The ion-assisted reaction can change etch characterization based on the configuration of gasses used in the chamber (Zhou, Cao, & Liu, 2010; Ekinci, et al., 2014; Y. H. Lee, Yeom, Lee, Yoo, & Kim, 1998; Wang, et al., 1998; J. K. Sheu, 1999; Lin Sha, 2003). For silicon wafers, Cl<sup>+</sup> ions and Br<sup>+</sup> have a higher ion-assisted etch percentage than F<sup>+</sup> ions (Nojiri, 2012). This means that using the gasses chlorine and bromine-based gases such as Cl<sub>2</sub> and HBr can give a more anisotropic etch than fluorine-based gases for silicon wafers.

Chamber pressure is another important etching parameter to consider because it can also influence the etch profile. As mentioned before, the ion sheath is a region in the chamber where the ions can flow in a single direction without interference from electrons. With lower pressure, there will be fewer particles colliding with the ion flow. The lack of interference allows the ions to flow without scattering. The term for this is the mean free path. The mean free path is the

average distance the ion can travel without colliding with another particle, and it is inversely proportional to the chamber pressure. If the mean free path is adequately larger than the ion sheath, the ions will be able to travel in a straight line directly to the wafer. If the mean free path is smaller than the ion sheath, the ions will be more likely to scatter and travel at random angles. This will cause the sidewalls of the etch profile to be contacted by ions. The etch profile is more isotropic. In the case of an ICP etcher, the plasma density is much higher, while the ion sheath is much shorter. Thus, the mean free path can be longer than the ion sheath, so ion scattering is rate. ICP creates a more anisotropic etch than RIE.

The average amplitude of the RF voltage  $(\overline{V_{rf}})$  determines the thickness and potential of the ion sheath. This comes from the V<sub>dc</sub>, which is dependent on the difference in electrode voltage and surface area of the electrodes  $\left(\frac{V_1}{V_2} = \left(\frac{S_2}{S_1}\right)^4\right)$  (Nojiri, 2012; Bogdanova, Lopaev, & Zyryanov, 2016). Using a modified version of the Child-Lagmuir in equation 26, the thickness of the ion sheath (s) can be calculated, where  $\varepsilon_0$  is the dielectric constant,  $\overline{J_i}$  is the mean current Ion density, and M is ion mass. This shows how V<sub>rf</sub> is related to the ion sheath thickness. Thus RF power can determine the etching profile (Nojiri, 2012) (Bogdanova, Lopaev, & Zyryanov, 2016).

$$s = \left(\frac{0.82\varepsilon_0}{\overline{J_l}}\right)^{\frac{1}{2}} \left(\frac{2e}{M}\right)^{\frac{1}{4}} \left(\frac{1}{2}\left(\overline{V_{rf}} - V_{dc}\right)\right)^{\frac{3}{4}}$$

(Equation 26)

According to (Nojiri, 2012), there are five parameters used to evaluate the quality of an etching procedure. The parameters help compare etches and look for improvements among different recipes. The first is etch rate (ER). This is the rate at which the material is removed while being etched. Consider a substrate of a certain material with a thin film of another material deposited with a known thickness on top. Then a photoresist mask is deposited with a known

thickness on the top layer. The goal of the etch is to etch through the thin film entirely without etching away the underlying substrate. The ER for the photoresist, target film, and underlying substrate must all be known when performing an etch. This is to determine the proper etch time and ensure that the etch reaches a targeted depth without going too far into the underlying substrate. Next is selectivity. This is the ratio of etch rates between two different materials. The ER of photoresist/target film (ER<sub>1</sub>/ER<sub>2</sub>) must be known, and the ER of target film/Underlying substrate (ER<sub>2</sub>/ER<sub>3</sub>) must also be known. This means the photoresist has a lower etch rate than the target film. Therefore the film can be etched quickly while the photoresist remains to act as a mask. The selectivity of ER<sub>2</sub>/ER<sub>3</sub> must be higher. This ensures that the etch time is calibrated in such a way that it will stop the etch at the exact moment when the film is etched entirely through, and the etch on the underlying substrate is minimized.

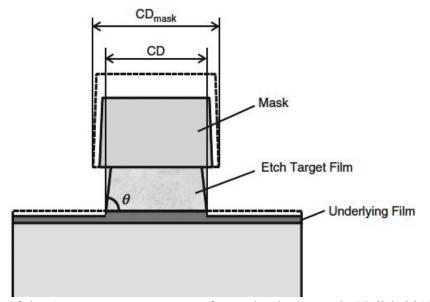

The third parameter to measure is the critical dimension (CD) after etching. This is the small change in feature size after the etch is complete. This small difference must be accounted for with each process step in fabrication. The light shines through a mask that is printed with features. It is impossible for the features on the photoresist to be the exact same size as the mask. There is going to be a small change in size. This small change is known as the critical dimension (Mack, 2007; Nojiri, 2012). When the substrate is then brought to be etched, the final etch is going to have a small change in size from the photoresist mask. The compounding change in size is known as the CD shift and is the fourth parameter to measure  $\Delta CD = CD_{mask} - CD$ . The CD has a direct influence on the transistor performance. It can determine the threshold voltage. If the CD is nonuniform across the wafer, the threshold voltage will also be nonuniform.

The last parameter to measure is the etch profile. The etch profile is the cross-section of the etch, generally viewed with an electron microscope. This can be used to measure the isotropy of the etch. The etch profile can be measured by measuring the interior angle of the standing structure. This can tell how tapered the etch profile is. The ideal etch profile will have a  $90^{\circ}$ , angle, while greater than  $90^{\circ}$  is a reverse taper and must be avoided. A reverse taper can cast a shadow during ion implantation where areas will not be implanted. Figure 2.5 illustrates the five parameters that must be measured.

Figure 2.5 Illustration of the 5 parameters to measure for evaluating an etch (Nojiri, 2012).

Certain materials require a more durable mask, such as oxide (Nakamura, Iizuka, & Yano, 1989). A more durable mask can increase the selectivity between the target material and the masking material, although it can cause sidewall passivation, which can decrease the profile angle (Tseng & Tsui, 2016; Tseng & Tsui, 2016). When etching polysilicon, a photoresist does not provide a high enough selectivity. Therefore a hardmask such as SiO<sub>2</sub> can be used (Ekström, 2019). Creating a hardmask is a more complicated process than a photoresist mask. The mask must be deposited or grown and then patterned with a liftoff process or etching process. The result is a layer of material that is patterned, similar to a photoresist mask. After the plasma etching is finished, the mask must then be removed in order to reveal the etched substrate. This is often done using a wet etching method.

At various stages during the IC fabrication process, it is not necessary to use plasma etching. Wet etching is often a better method. When cleaning the wafer from an oxidized surface or patterning an insulating SiO<sub>2</sub> layer, BOE can be used.

In a CMOS device, insulating SiO<sub>2</sub> is used to isolate the IC from the bulk substrate. There are three reasons why this is required. This reduces leakage current, which improves operation temperature. It reduces capacitance, so the speed is increased, and power requirements are reduced. Noise is reduced for sensitive systems (Honeywell International Inc., 2022). An aqueous solution with hydrofluoric acid is commonly used to pattern SiO<sub>2</sub>. The chemical reaction is shown in (Equation 27). The reaction is made up of several steps. Because the reaction rate is independent of agitation, the reaction rate of the slowest reaction will determine the overall reaction rate (Spierings, 1993).

$$SiO_2 + 6HF \rightarrow H_2SiF_6 + 2H_2O$$

(Equation 27)

The HF solution is made up of the following species, H<sup>+</sup>, F<sup>-</sup>, HF<sub>2</sub><sup>-</sup>, HF, and H<sub>2</sub>O. Oxide reactions in NaF and NH<sub>4</sub>F do not etch SiO<sub>2</sub> (Judge, 1971; Tso & Pask, 1982), so it can be concluded that F<sup>-</sup> ions do not contribute to the reaction rate. The reaction rate is described by the concentration of HF<sub>2</sub><sup>-</sup>, and HF in the solution, though it is disputed which one has a larger impact. The H<sup>+</sup> ions act as a catalyst for the reaction that is described in (Spierings, 1993). The etch rate of the solution is determined by the reactivity of HF, HF<sub>2</sub><sup>-</sup>, and H<sup>+</sup>. The solution can be adjusted by adding strong acids or fluorides to the mixture. Higher HF concentrations give higher etch rates. Strong acids that can be added to the HF solution are HCl, HNO<sub>3</sub>, and H<sub>2</sub>SO<sub>4</sub>.

For a buffered oxide etch (also known as buffered HF), NH<sub>4</sub>F is added to HF. This is exclusively used for etching SiO<sub>2</sub> in the IC fabrication process. BOE solutions are typically a mixture of 40 wt % NH<sub>4</sub>F solution with 49 wt % HF solution in various ratios with water added. NH<sub>4</sub>F is added to dilute the solution and reduce the etch rate and attack the photoresist. At high NH<sub>4</sub>F concentrations, the HF<sub>2</sub><sup>-</sup> become inactive due to complications with NH<sub>4</sub><sup>+</sup> ions (Spierings, 1993).

BOE can be applied in several ways: stirring, bubbling, and ultrasonic agitation can be used to increase the effectiveness of the etch. The solution can be sprayed on a flat wafer as it rotates to increase uniformity. An aerosol BOE solution can be used to increase the anisotropy of the etch. Wax can be applied manually to the surface to protect regions from the etchant. For smaller dimensions that are commonly found in IC design, the photoresist is used. Pure HF can remove the adhesion of the photoresist from the surface. This can be a problem with high HF concentrations or long etch times. NH<sub>4</sub>F has been shown to reduce the attack on photoresists (Spierings, 1993). Increased temperatures can also be used to increase etch rate, therefore, reducing etch time and the attack on a photoresist (Burham, Sugandi, Nor, & Majlis, 2016). In some cases where a deep etch is required, an HF-resistant film is required, such as chromium that is patterned with a photolithographic process.

Aqueous HF solutions provide isotropic etch profiles. When a masking material such as photoresist or chromium is used, the mask has strong adhesion to the surface of the substrate. This creates rounded sidewalls. Delamination of the mask can cause the material to have a tapered sidewall. The tapered sidewall can also be done intentionally by using a second film below the mask that has a higher etch rate than the oxide. The selectivity between these two materials determines the slope of the etch profile (Spierings, 1993).

The photolithography and etching mechanisms described above will need to be studied. To understand how these methods can be used in SiC CMOS fabrication, these methods must be recreated in our lab. The following chapter will discuss the methods used to recreate state-of-theart using the facilities available at the University of Arkansas. The results of these initial studies will be described in the following section as well. Then, in chapter 4, the experiments will be conducted to improve these results so that they may be utilized in CMOS fabrication.

### Chapter 3. Etching Process Methods

This chapter will discuss the initial experiments that were conducted to recreate state-ofthe-art. Methods for photolithography, ICP, and BOE will be attempted. The methods and results will be described in detail. In chapter 4, changes to the original methods will be made. The same equipment and facilities will be used throughout the following chapters.

### 3.1 Photolithography

With any etching process in IC fabrication, the resolution can only be as precise as the preceding photoresist resolution. A photolithography mask recipe capable of depositing a high-resolution mask must be developed before any etching studies can commence.

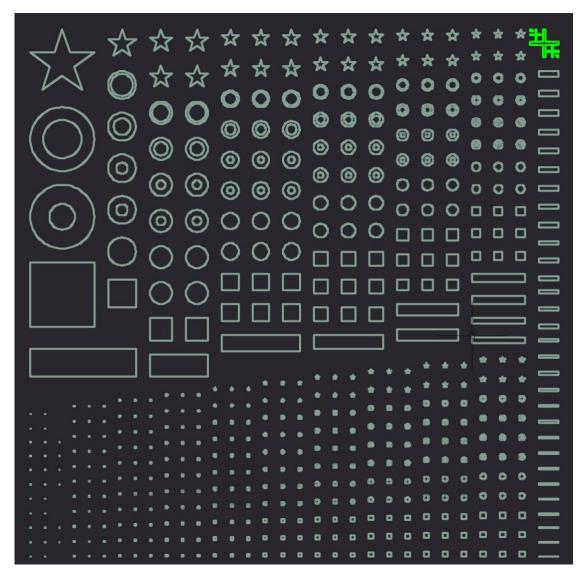

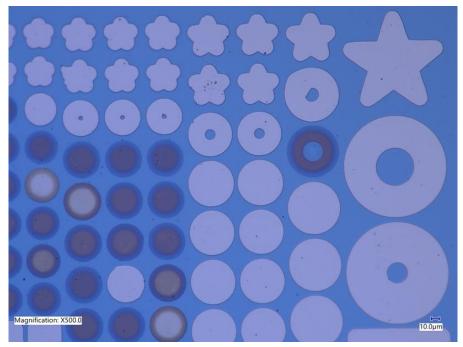

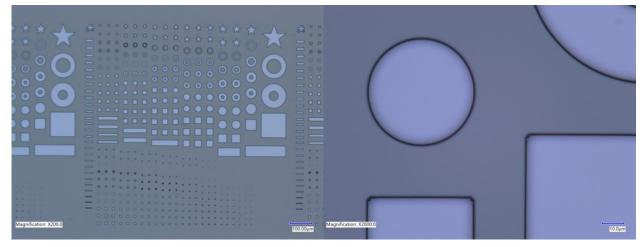

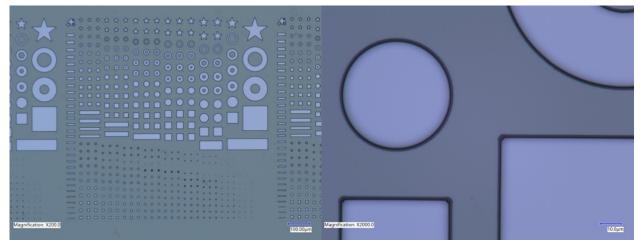

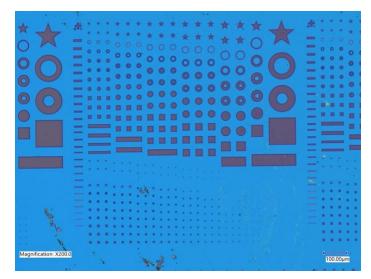

First, a photomask was designed for the purposes of calibration. The goal of this mask was to determine the minimum feature size that the photolithography process could create accurately. To test the accuracy of pattern transfer, different shapes with various angles were used. The shapes that were used were: squares, circles, donuts (varying thicknesses), and 5-point stars. Each shape was repeated and re-sized to fit inside a square with the following side lengths: 1-10µm, 15µm, 20µm, 25µm, 30µm, 40µm, 50µm, and 115µm. Rectangles of various sizes were

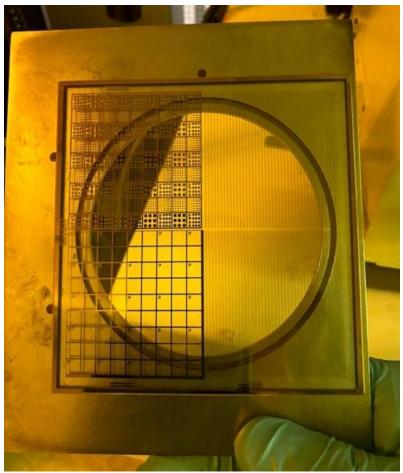

used to fill up empty space on the mask. Cross-shaped alignment marks were added in the corner of each 1cm x 1cm pattern to help with alignment. The 1cm x 1cm pattern was repeated on a 10x10 array to complete the mask. An AutoCAD blueprint image of the 1cm x 1cm pattern is shown in Figure 3.1.

Once the photomask was designed and manufactured, photolithography procedures could commence. The standard photolithography procedure for the University of Arkansas facilities was performed. The general process goes as follows: clean wafer, spin coat photoresist, post-

Figure 3.1 AutoCAD generated image of photomask design that will be used.

Apply bake (PAB), alignment and exposure, post-exposure bake, flood exposure, and development. The exact specifications of the procedure for this control experiment are described in the original traveler shown in Appendix A. The traveler recommends each sample undergoes a 9-step sample cleaning process that involves 3-5 minutes of sonication steps in acetone, methanol, and IPA. In this experiment, we shortened this cleaning process to a 5-minutes acetone sonication, IPA rinse, DI water bath, N<sub>2</sub> blow-dry, and 2-minute dry bake at 100°C. This was to save time when processing many samples, and given the condition of the cleanroom, small particles interfering with our results were inevitable.

A spin coater was used to spread the photoresist across the sample. First, HMDS was coated on the sample to promote adhesion. This was applied with a small amount of chemicals and a rotation speed of 4000 rpm. The excess HMDS was removed during the rotation, and an even layer of HMDS was left across the entire sample. HMDS is indented to be entirely evaporated before moving on to the next step. The next step was adding a photoresist in a similar fashion. The photoresist used was AZ nLOF 2035, a negative resist. The rotation speed used was 3000rpm, which, according to the datasheet (Merk KGaA, 2021)leaves a layer of photoresist with a thickness of  $3.5\mu m$ . The physics behind the spin coat process is described in (Mack, 2007). During the spin coat process, the centrifugal force pushes the photoresist away from the center of rotation. The opposing frictional force pushes the photoresist towards the center of rotation. Initially, the centrifugal force, proportional to the mass of the liquid, is greater than the frictional force. Therefore, some amount of photoresist is flung off the sample. This continues until the centrifugal and frictional forces are balanced, then no more photoresist is removed. The result is an even layer of photoresist across the sample. After the photoresist is applied, a soft bake is required to adhere the photoresist to the sample. The photoresist is now ready for

exposure. However,, this is one negative result of this spin coat process. Due to the shape of the sample, there is a higher amount of surface tension along the edge during the rotation time. This results in a thicker amount of liquid building along the edges of the sample. This is referred to as the edge bead. If the edge bead is left on the sample, the contact aligner will not be able to make an even contact, and exposure will not be accurate. To remove the edge bead, the datasheet (Merk KGaA, 2021) and (Mack, 2007) recommend using edge bead remover, which thins the photoresist without removing the photoresist entirely. However, for experimental purposes, acetone, which removes the photoresist entirely and leaves a rough edge, is acceptable. The sample is now ready to be loaded unto the contact aligner.

The aligner that was used is a Karl Suss MJB-3 contact aligner. The first step is loading the photomask. The photomask is designed so that the pattern is printed on one side of a transparent pane of plastic. The other side of the mask does not have an image printed on it. The sample is intended to be in as close contact with the pattern as possible. Therefore, the side that has the image printed on it is the side that must be in contact with the sample. This is to reduce any refraction that may occur as the light passes through the mask. Visual observation of the mask will show that one side of the mask is mirrored while the other has a chrome look. The chrome side is the side required to be in contact with the sample. When placing the photomask in the vacuum holder, the mask must cover all vacuum holes so that a proper vacuum hold can be established. Chrome, or contact, the side must be facing up. The aligner that was used has a problem that results in only one quadrant of the loading area receiving proper exposure. This requires that the photomask must be designed in four quadrants, with each quadrant being a different pattern. The photomask must be orientated so that the intended pattern is in the right quadrant. Figure 3.2 shows the proper mask setup. Once the vacuum hold is initiated, the entire

apparatus is then flipped at a 180° turn so that the side that was once facing up is now facing down. The apparatus is then inserted into the contact aligner, and the sample is ready to be loaded for exposure.

The sample can now be placed on the wafer chuck. This is done by sliding the chuck out to its loading position, placing the sample in the lower right-hand quadrant, then closing the tray. To ensure proper alignment, the adjustment knobs are used to change the X, Y, and rotational axis. Once alignment is exactly as indented, it is time to initiate contact. Once there has been contact between the mask and the sample, no more alignment adjustments can be made, and contact cannot be broken. Although the sample and mask are in contact, there is still space between the sample and mask. The Z-axis dial must be turned until it cannot rotate anymore. This raises the wafer chuck so that the sample is pressed against the mask with a higher pressure than before. Full contact is now being made with the sample. It is time to expose the sample.

Assuming an exposure time of 17.7 seconds, adjust the time dial to approximately 18 seconds and expose the sample. A post-exposure bake (PEB) is required at 110°C for 60 seconds. Although not specified in the traveler, our early trials used a flood exposure step of 60 seconds without the photomask in place. For the flood exposure, there is no need to initiate contact, simply place the sample on the chuck and expose it for 60 seconds. The final step in the photolithography process is to develop the photoresist.

Figure 3.2 Photomask being loaded into aligner

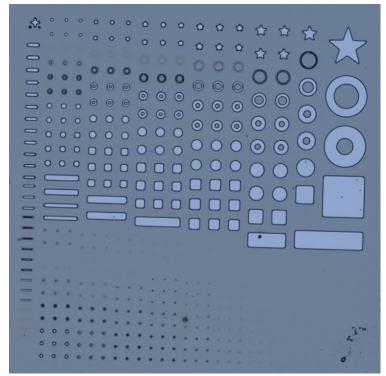

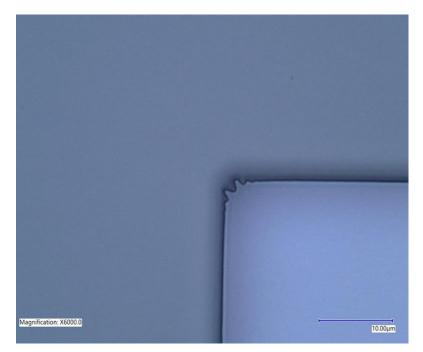

To do this, the sample is held in a beaker with developer liquid for a specified amount of time, then immediately removed and placed in a water bath to stop development. The sample is then dried with N<sub>2</sub> blow-drier. The developer used in early trials was AZ 726 MIF for 35 seconds. The Keysight microscope was used to view the results shown in Figure 3.3 and Figure 3.4. The results show that this photolithography procedure was unable to accurately transfer the features of the photomask to the photoresist. The smallest features were not transferred at all, while the larger features were not accurately represented. It should also be noted that circular features were transferred with high accuracy. This is because circular objects do not require a high resolution to be transferred with photolithography. 3.2 shows the same sample at a higher magnification. It shows a feature that is intended to be a perfect square with right angles. This

shows that the angles are not, in fact, rounded but have a jagged or wavey edge. This wave resembles that of a light wave. This implies that the high-intensity light from the exposure lamp may be refracting at the corners. A higher resolution is needed to obtain sharper corners and smaller feature sizes.

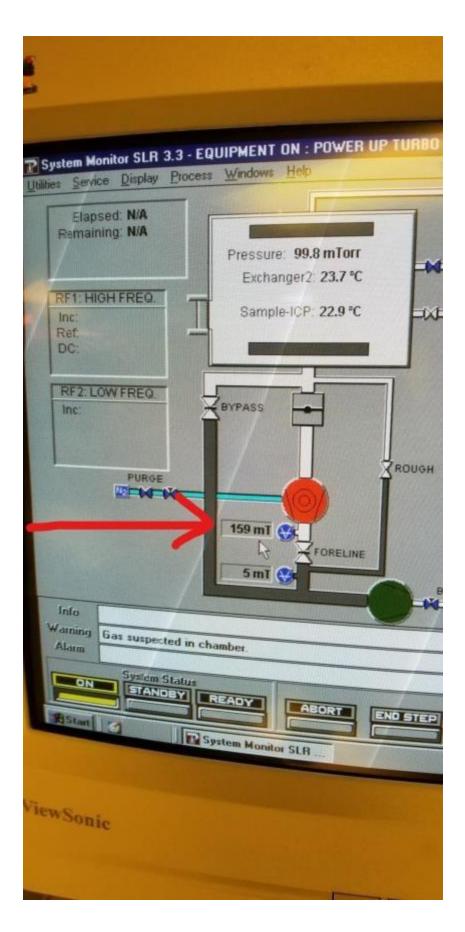

# 3.2 Inductively Coupled Plasma

When etching a CMOS device, it is critical that the etch is calibrated so that it etches the desired depth without over-etching. When layers of varying materials are deposited on a substrate, the different materials could have different etch rates. These values must be known for calibration. As described in the previous section, etch rate and selectivity are measurements that must be taken to help calibrate the etching procedure. At the time of this study, the ICP etcher has only access to Cl<sub>2</sub>, BCl<sub>3</sub>, NF<sub>3</sub>, and N<sub>2</sub>. A reliable value for the etch rate of SiC must be determined at an ICP recipe that is known to work.

To do this, gas chemistry in this baseline recipe that has been known to work with GaN (Lee, et al., 1998; Kim, Yeom, Lee, & Kim, 1999) was used for SiC. The photoresist was applied using the photolithography process described previously. The same calibration mask was used for all etching experiments to directly compare critical dimensions between photolithography and etching. The detailed procedure for ICP etching in the Nanofab lab is shown in Appendix I.

| Exchanger 2 Temp: 35°C | Cl <sub>2</sub> : 13 sccm  | Time: XX:XX     |

|------------------------|----------------------------|-----------------|

| Sample-ICP Temp: 40°C  | BCl <sub>3</sub> : 25 sccm | RF1 Power: 300W |

Table 3.1 shows the temperatures, chamber pressure, flow rates, etch time, and RF power that was used for the baseline recipe. RF1 is the power at the bottom electrode where the wafer sits, and RF2 is the power at the induction coil that generates the plasma. The total flow rate for the gases was 38 sccm, where Cl<sub>2</sub> made up approximately 34%.

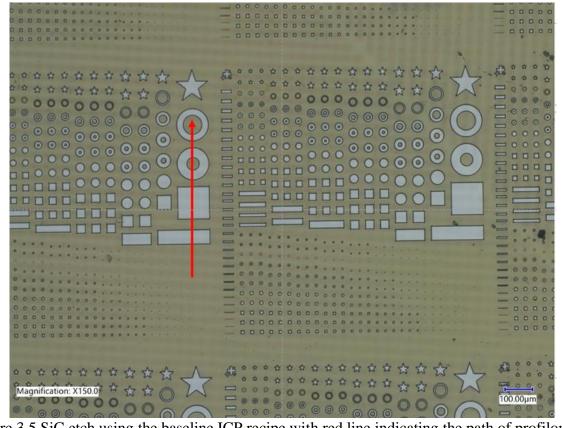

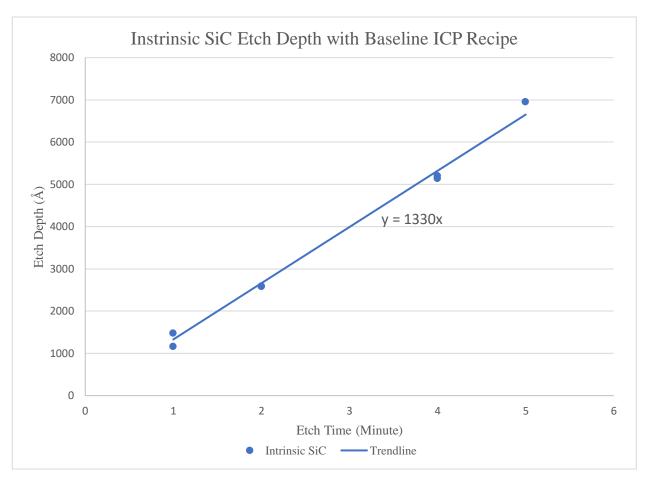

Using a Dektek 3030 profilometer, the etch depth was measured. The photoresist was removed with acetone before etching depths were measured. Figure 3.5 shows the path of the stylist on the etched SiC sample after the photoresist was removed. The red line shows the path and direction the stylist traveled on the sample. This path was chosen because the larger features made for easier measurements and more repeatable results. The etch depth was measured at various points across the substrate and then averaged together to get a reliable estimate for the depth of the etch. This measurement is then divided by the etch time to give the average etch rate across the sample. The first two samples that were etched using the baseline ICP recipe shown in Table 3.1 for one minute had an average depth of 137.1 nm. The same recipe was then used to etch SiC samples for 1-5 mins. The data shown in Figure 3.6 shows a linear relationship with a slope of 1330 Å/min. Data was collected for a three min etch, but the gas lines in the ICP needed to be cleaned. The collected data was unreliable and thrown out

There is little known about the etching performance of SiC with Chlorine based gases. To design the plasma etching process modules for the SiC CMOS, more needs to be understood. The five parameters need to be measured. Etch rate, selectivity, CD, CD shift, and etch profile need to be measured for SiC, doped SiC, polysilicon, SiO<sub>2</sub>, and photoresist. New gas ratios must also be experimented with to determine how the selectivity changes with the gas recipe. The next section will discuss the procedure used to study the plasma etching performance of SiC.

Figure 3.3 Photoresist on Si wafer using original photolithography process.

Figure 3.4 High magnification image of photoresist on Si wafer

| Exchanger 2 Temp: 35°C | Cl <sub>2</sub> : 13 sccm  | Time: XX:XX      |

|------------------------|----------------------------|------------------|

| Sample-ICP Temp: 40°C  | BCl <sub>3</sub> : 25 sccm | RF1 Power: 300W  |

| Chamber Pressure: 10mT | N <sub>2</sub> : 00 sccm   | RF2 Power: 1000W |

Table 3.1 Baseline ICP Recipe

Figure 3.5 SiC etch using the baseline ICP recipe with red line indicating the path of profilometer measurements.

Figure 3.6 Etch depth for intrinsic SiC etching with the baseline recipe

# 3.3 Buffered Oxide Etching

As described in previous sections, buffered oxide etching is a wet etching method for etching silicon dioxide from the surface of a silicon wafer. This method can be used to remove the oxidation layer from the surface of a substrate. It can be used to pattern oxide for the use of an insulating field oxide or gate oxide in a CMOS device or a hardmask layer that can be used for high selectivity plasma etching.

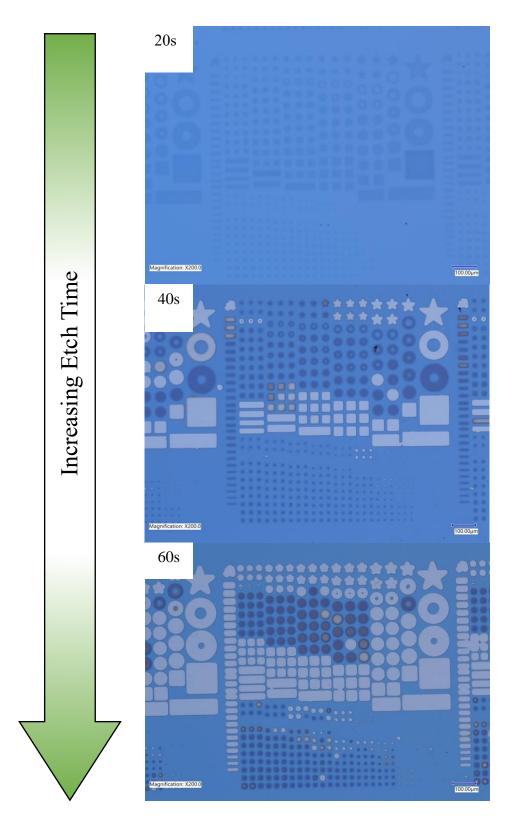

Like the method for calibrating a plasma etch, a baseline etch recipe is used before improvements to the recipe can be made. The baseline recipe used a BOE solution that was premixed 5:1 ratio. This is one part by weight hydrofluoric acid (HF) and five parts by weight ammonium fluoride (NH4F). This was mixed with water in a 20% by vol BOE solution in a 100 mL total volume. A single silicon sample was deposited with a layer SiO<sub>2</sub> by sputtering. Using ellipsometry, the approximate thickness of the oxide layer was 136nm for this first sample. The sample was then deposited with a photoresist mask identical to the mask used for photolithography calibration. Then it was cleaved into three separate samples. Each sample was submerged in the solution 60s, 40s, and 20s, respectively. The solution was not agitated during the etching time. The only agitation comes from submerging the sample and removing it from the solution Figure 3.7 shows the three samples that were etching using this BOE solution. It can be seen from Figure 3.7 that the longer the sample was submerged in the solution, the more oxide was etched. The oxide will continue to be etched until the underlying Si substrate is revealed. The etching does not appear to be consistent throughout the entire sample.

It appears the larger features are etched more quickly than the smaller features. This is likely due to the larger surface area that is in contact with the etching solution. Figure 3.8 shows a close-up view of the sample that was etched for the 60s. The sharp points on the star have become more rounded, and the inner circles of the donut shapes have disappeared. This is likely due to the isotropic etch profile that etches in all directions.

Figure 3.7 Si Substrate with SiO2 etched with BOE for 20 s, 40 s, and 60 s.

Figure 3.8 Detail image of the Si substrate with an SiO2 layer that had been etched for 60 s.

In some cases, silicon dioxide can be used as a hardmask for plasma etching. When etching polysilicon with plasma, high selectivity is required to reduce over-etching and microtrenching. Photoresist tends to add carbon to the gas inside the plasma chamber and then redeposit that carbon onto the substrate, causing micromasking. This will reduce the etch rate. Silicon dioxide has a high selectivity to polysilicon without the micromasking effect of photoresist. For this reason, silicon dioxide is preferred for etching polysilicon (Ekström, 2019; Bell, Joubert, & Vallier, 1996). For an oxide hardmask to be effective, it must have a high resolution and be etched entirely through to the target material. This can be a difficult task considering the nature of wet etching and the isotropic etch profile it gives. A possible solution to this problem is using a lift-off method to pattern the silicon dioxide. This will be described in later sections.

A method for depositing a silicon dioxide hardmask from sputter deposition that can be used for polysilicon plasma etching must be developed. The resolution of the mask will need to be improved, and the etch must be more consistent. The wet etches rate will need to be determined to create a method for depositing a hardmask. The plasma etches rates for silicon dioxide and polysilicon will be measured to verify if silicon dioxide will make a suitable hardmask.

There are many improvements that need to be made to the etching process modules of the SiC CMOS. The photolithography recipe must be improved to increase resolution and pattern transfer accuracy. This will be done by analyzing the photolithography process to determine areas for improvement. The critical dimension of the photoresist will be determined by measuring the resolution of images of the photoresist and comparing them to the photomask. The plasma etching recipe will need to be calibrated for the various materials that will be etched. This will be done by varying the gas mixtures that are used to etch the material. To determine the quality of the etch, the five parameters mentioned before will be measured for these materials and gas combinations. Lastly, the hardmask deposition process will be determined by using various BOE recipes and attempting an oxide liftoff attempt. Then that hardmask will be tested with polysilicon in an ICP etcher. These methods for improving the process modules will be described in greater detail in the following chapters.

#### Chapter 4. Etching Process Module Development and Results

This chapter will discuss the experiment design and results that have been conducted to improve the methods that have been described in the previous chapter. These experiments aim to improve the accuracy of pattern transfer from the mask. The selectivity of different etch chemistries have also been studied to characterize chlorine-based ICP etches with SiC. SiO<sub>2</sub> etching with ICP and BOE has been studied along with an alternative to etching, liftoff.

#### 4.1 Photolithography

The initial resolution for the mask was not sufficient to perform etching experiments. It would be too difficult to make observations on the quality of the etch if the mask was poor quality. To improve the quality of the photoresist mask, the photolithography procedure had to be changed.

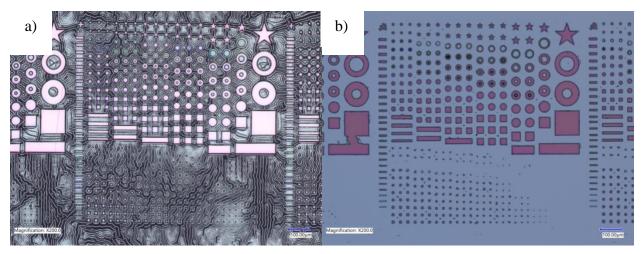

The first change that was made to the procedure was the exposure time. The original instruction was to expose the photoresist for 17.7 seconds. There was no explanation of where that exposure time came from. A more accurate exposure time can be calculated from equation 23. The exposure time is equal to the exposure dose of a given photoresist at a certain thickness divided by the intensity of the lamp in the aligner, which can change as the bulb ages. For our given photoresist, AZ nLOF 2035, at a thickness of 3.5µm, is 80 mJ/cm<sup>2</sup>. To calculate the exposure dose for a different thickness becomes a difficult math problem involving analytical calculus (Mack, 2007). So it is better to keep the thickness at 3.5 µm and use the given exposure dose. Now the proper exposure time can be calculated for the measured lamp intensity. A higher resolution was achieved by changing the photolithography procedure. The datasheet (Merk KGaA, 2021) recommended AZ 726 MIF developer for a development time of 35 s or AZ 300 MIF for a development time of 120 s. To test if this new developer was an improvement, two identical Si samples were processed in photolithography simultaneously. Photolithography processes were identical (described in Appendix A). The only change in the two procedures is the developer and development time. Sample one used the AZ 726 MIF for 35 s. Sample two used AZ 300 MIF for 120s. The higher quality procedure would be used for the etching studies. The results are shown below in Figure 4.2 and Figure 4.1.

The figures above show a subtle difference in photoresist quality. It is most noticeable when looking at the small features and at the sharp edges of the features. There appear to be more small features being developed with the AZ 300 MIF developer. The quality of the image transfer is also higher. By looking closely at the sharp edges of the square features, the corners appear more rounded, and less of the wave pattern appears. There also appears to be a thicker parameter around the features that were developed with AZ 300 MIF. This indicates that there may be more of a tapered sidewall in the photoresist.