# Expressive and Efficient Memory Representation for Bounded Model Checking of C programs

by

### Xiang Zhou

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Master of Applied Science in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2022

© Xiang Zhou 2022

#### Author's Declaration

This thesis consists of material all of which I authored or co-authored: see Statement of Contributions included in the thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### **Statement of Contributions**

Some figures and formulations are taken from Bounded Model Checking for LLVM paper [29] with contributions from Siddharth Priya, Yusen Su, Prof. Yakir Vizel, Dr. Yuyan Bao and Prof. Arie Gurfinkel.

Some of the features in SEABMC, which SEAM depends on were implemented by Siddharth Priya and Prof. Arie Gurfinkel.

The benchmark Verify-C-Common project [28] contains contributions from Siddharth Priya, Yusen Su, Prof. Yakir Vizel, Dr. Yuyan Bao and Prof. Arie Gurfinkel.

#### Abstract

Ensuring memory safety in programs has been an important yet difficult topic of research. Most static analysis approaches rely on the theory of arrays to model memory access. The limitation of the theory of arrays in terms of scalability and compatibility with SAT/SMT solvers is well-known, and there has been many attempts at optimizing either the theory itself or memory encodings based on theory of arrays.

In this thesis, we demonstrate that existing arrays-based memory encodings miss potential optimization opportunities by omitting language specific properties such as alignment and pointer arithmetic in C. We present SEAM, a new memory representation for C programs built around a more expressive First-order Theory: the Theory of Memory. We show that by preserving more C language specific rules and properties, the Theory of Memory allows for more thorough optimization methods during eager rewriting of sequences of stores. We introduce two such optimization methods in this thesis. First, we over-approximate pointer comparison with an abstract interpretation-like approach called AddressRangeMap. Second, we compress sequences of stores with STORE-MAP for faster address offset look-ups.

The new memory representation is implemented in SEABMC, a new BMC tool for LLVM. We evaluate our approach on real-world bounded model checking tasks from the aws-c-common library and SV-COMP benchmarks and compare it against two existing memory representations in SEABMC. Our results show that SEAM outperforms the theory of array based representation and is comparable with the  $\lambda$  based representation.

#### Acknowledgements

I would like to thank my supervisor Professor Arie Gurfinkel for guiding me in every step of my research projects. I would like to thank my colleagues for aiding me with their domain specific expertise. Lastly I would like to thank my readers Prof. Mahesh Tripunitara and Prof. Meng Xu for their insightful feedback.

#### Dedication

This is dedicated to my family, friends and Lulu the cat, who are with me during my MASc journey.

# Table of Contents

| Li                  | List of Figures |                                                                                                      |           |  |  |  |

|---------------------|-----------------|------------------------------------------------------------------------------------------------------|-----------|--|--|--|

| Li                  | st of           | Tables                                                                                               | xii       |  |  |  |

| 1                   | 1 Introduction  |                                                                                                      |           |  |  |  |

| 2                   | Bac             | kground                                                                                              | 4         |  |  |  |

|                     | 2.1             | Basic rewrite rules                                                                                  | 4         |  |  |  |

|                     | 2.2             | Theory of Arrays                                                                                     | 7         |  |  |  |

|                     | 2.3             | Encoding set/copy memory operations $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 9         |  |  |  |

|                     | 2.4             | Encoding Arrays with $\lambda$ -expressions                                                          | 11        |  |  |  |

|                     | 2.5             | SeaBMC                                                                                               | 11        |  |  |  |

| 3                   | Ove             | erview                                                                                               | 16        |  |  |  |

| 4                   | The             | eory of Memory                                                                                       | <b>21</b> |  |  |  |

| 5 Address Range Map |                 |                                                                                                      |           |  |  |  |

|                     | 5.1             | Offset Intervals                                                                                     | 28        |  |  |  |

|                     | 5.2             | Address Range Map                                                                                    | 32        |  |  |  |

| 6                   | Cor             | npressing write with STORE-MAP                                                                       | 40        |  |  |  |

|                     | 6.1             | STORE-MAP data structure                                                                             | 41        |  |  |  |

| 7  | Implementation 4 |                                    |    |  |  |  |

|----|------------------|------------------------------------|----|--|--|--|

|    | 7.1              | Multi-step rewriter                | 46 |  |  |  |

|    | 7.2              | Cached ordered maps for STORE-MAP. | 51 |  |  |  |

| 8  | Eva              | luations                           | 54 |  |  |  |

|    | 8.1              | Overall performance                | 55 |  |  |  |

|    | 8.2              | Simplification with ARM            | 59 |  |  |  |

|    | 8.3              | Overhead reduction with STORE-MAP  | 63 |  |  |  |

|    | 8.4              | Conclusion                         | 66 |  |  |  |

| 9  | Rela             | ated Work                          | 68 |  |  |  |

| 10 | 10 Conclusion    |                                    |    |  |  |  |

| Re | References 7     |                                    |    |  |  |  |

# List of Figures

| 2.1  | Rewrite rules for $ite$ terms                                                                                                                                                   |  |  |  |  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 2.2  | Example rewrite rules for comparison terms                                                                                                                                      |  |  |  |  |

| 2.3  | Example rewrite rules for Boolean terms                                                                                                                                         |  |  |  |  |

| 2.4  | Rewrite rules for addition arithmetic terms                                                                                                                                     |  |  |  |  |

| 2.5  | Term formation rules of $\mathcal{T}_{\mathcal{A}}$ , <i>a</i> is an $\sigma_A$ constant                                                                                        |  |  |  |  |

| 2.6  | Rewrite rules for $\mathcal{T}_{\mathcal{A}}$ read-over-write expressions                                                                                                       |  |  |  |  |

| 2.7  | Term formation rules of $\mathcal{T}_{ASC}$                                                                                                                                     |  |  |  |  |

| 2.8  | Rewrite rules for <i>read</i> -over-set                                                                                                                                         |  |  |  |  |

| 2.9  | Rewrite rules for <i>read</i> -over-copy                                                                                                                                        |  |  |  |  |

| 2.10 | Simplified grammar of SEA-IR, where E, L R, P and M are expressions, labels, scalar registers, pointer registers and memory registers, respectively. Credit to Siddharth Priya. |  |  |  |  |

| 2.11 | Definition of some <i>sym</i> semantics for translating parts of <b>VC</b> , <b>RDEF</b> and <b>MDEF</b>                                                                        |  |  |  |  |

| 2.12 | sym translation of memory operations in LAMBDAS and ARRAYS 15                                                                                                                   |  |  |  |  |

| 3.1  | Sample C program containing memory operations $P_1$ 16                                                                                                                          |  |  |  |  |

| 3.2  | Memory state of $P_1$ after line 17 encoded in $\mathcal{T}_A$                                                                                                                  |  |  |  |  |

| 3.3  | $\mathcal{T}_{\mathcal{A}}$ expression of <i>read</i> -over- <i>write</i> operation *num                                                                                        |  |  |  |  |

| 3.4  | $\mathcal{T}_{\mathcal{A}}$ expression of <i>read</i> -over- <i>write</i> operation $\mathtt{st}$ ->b                                                                           |  |  |  |  |

| 3.5  | Sample C program $P_2$ containing multiple memory operations on same ad-<br>dresses                                                                                             |  |  |  |  |

| 3.6 | Memory state of $P_2$ after line 10 encoded in $\mathcal{T}_A$                                                                                                                                                       |    |  |  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|

| 4.1 | Term formation rules of $\mathcal{T}_{\mathcal{M}}$ for programs with 8-bit byte size, 32-bit word size. Operations between pointer and scalar terms are differentiated with subscripts $p$ and $s$ .                | 23 |  |  |

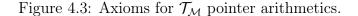

| 4.2 | Axioms for $\mathcal{T}_{\mathcal{M}}$ pointer comparison.                                                                                                                                                           | 24 |  |  |

| 4.3 | Axioms for $\mathcal{T}_{\mathcal{M}}$ pointer arithmetics                                                                                                                                                           | 24 |  |  |

| 4.4 | $\mathcal{T}_{\mathcal{M}}$ word-sized <i>read</i> -over- <i>write</i> axioms                                                                                                                                        | 25 |  |  |

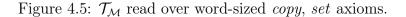

| 4.5 | $\mathcal{T}_{\mathcal{M}}$ read over word-sized <i>copy</i> , <i>set</i> axioms                                                                                                                                     | 25 |  |  |

| 4.6 | read-over-write rewrite rules for word-sized memory stores                                                                                                                                                           | 25 |  |  |

| 4.7 | read-over-write rewrite rules for word-sized memset and memcpy                                                                                                                                                       | 26 |  |  |

| 4.8 | sym translation of memory operations in SEAM                                                                                                                                                                         | 26 |  |  |

| 5.1 | Concrete semantics in domain $\mathcal{D}_s$                                                                                                                                                                         | 28 |  |  |

| 5.2 | $\alpha$ and $\gamma$ between $\mathcal{D}_s$ and $\hat{\mathcal{D}}_s$ . min $S_{i\in\mathbb{N}}$ and max $S_{i\in\mathbb{N}}$ returns the maximum and minimum element of a set $S$ respectively.                   | 29 |  |  |

| 5.3 | Abstract semantics of itv abstract operators $\sqcup, \sqcap$ and $\hat{+}$ . $min(a, b)$ , $max(a, b)$ returns the smaller and larger of $a$ and $b$ ; $ite(c, a, b)$ returns $a$ if $c$ is True and $b$ otherwise. | 29 |  |  |

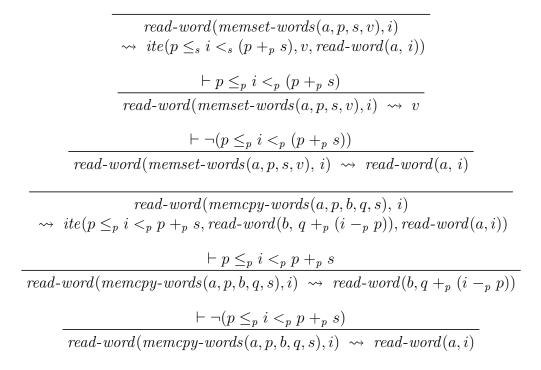

| 5.4 | Example $t_{\mathcal{S}} s_1$ representing a set of scalar numbers $nums(s_1)$ , with abstract value $\alpha(nums(s_1))$ . ITE(i) node represents expression $ite(i,)$ .                                             | 30 |  |  |

| 5.5 | Inference rules for numeric offset inclusion in Offset itv.                                                                                                                                                          | 32 |  |  |

| 5.6 | Concrete semantics in domain $\mathcal{D}_p$ . Note <i>nums</i> from <b>itv</b> domain                                                                                                                               | 33 |  |  |

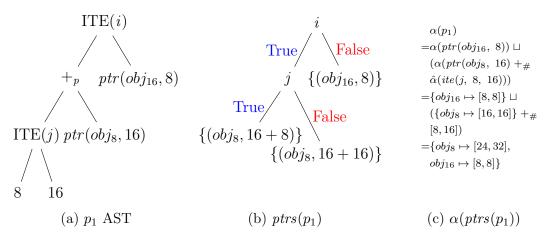

| 5.7 | Example $t_{\mathcal{P}} p_1$ representing set of pointers $ptrs(p_1)$ , with abstract value $\alpha(ptrs(p_1))$ . ITE(i) node represents expression $ite(i,)$ .                                                     | 33 |  |  |

| 5.8 | $\gamma$ and $\alpha$ functions between ARM and pointers                                                                                                                                                             | 34 |  |  |

| 5.9 | Abstract semantics for <b>ARM</b> $\sqcup$ , $\sqcap$ , $\sqsubseteq$ and $+_{\#}$ . Accent $$ denotes values and operators of itv.                                                                                  | 34 |  |  |

| 6.1 | Memory write sequence represented as a linked-list                                                                                                                                                                   | 41 |  |  |

| 6.2 | Part of a memory write sequence represented as a map                                                                                                                                                                 | 41 |  |  |

|     |                                                                                                                                                                                                                      |    |  |  |

| 6.3  | Memory write sequence represented as a linked list with a STORE-MAP node.                       | 42 |

|------|-------------------------------------------------------------------------------------------------|----|

| 6.4  | $write\ensuremath{\text{-over-write}}$ rewrite rules related to creating and updating store-map | 43 |

| 6.5  | Rewrite rules for reading store-map                                                             | 44 |

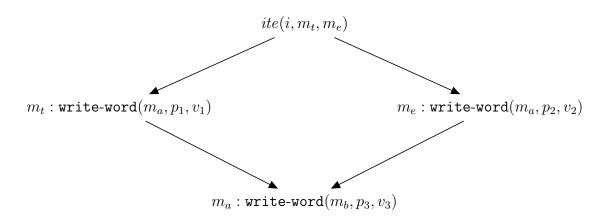

| 7.1  | Example Expr of a $t_{\mathcal{M}}$ under rewrite.                                              | 50 |

| 7.2  | Insertion process with OCL and cached stl map                                                   | 53 |

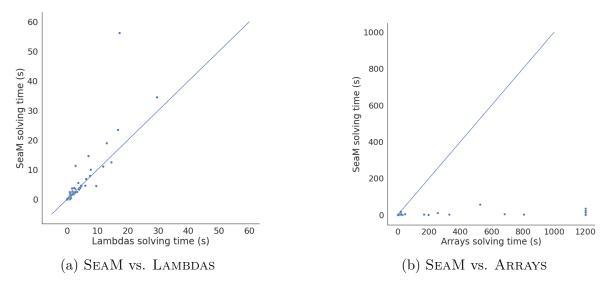

| 8.1  | Per task solving time using Z3                                                                  | 57 |

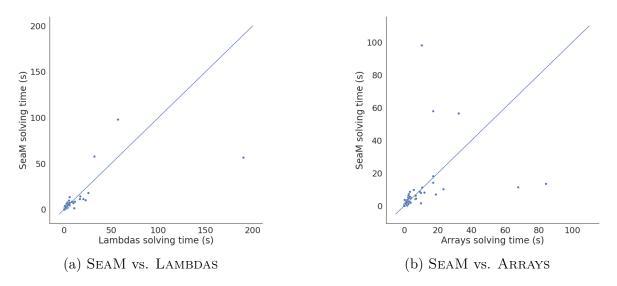

| 8.2  | Per task solving time using Yices2                                                              | 58 |

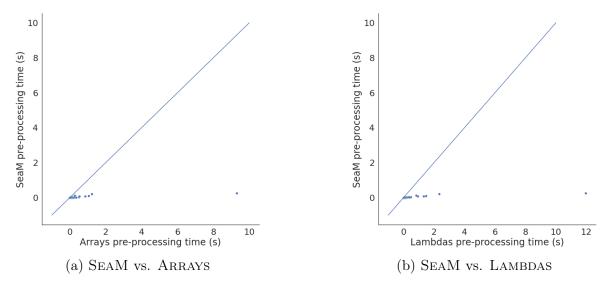

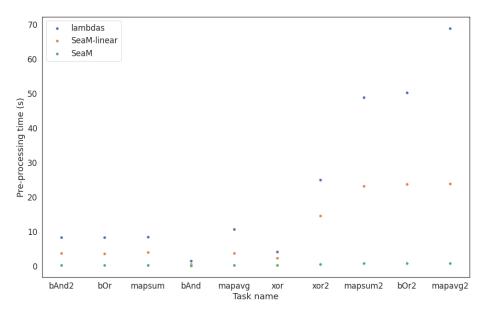

| 8.3  | Per task pre-processing comparison                                                              | 59 |

| 8.4  | Semantically equivalent expressions                                                             | 60 |

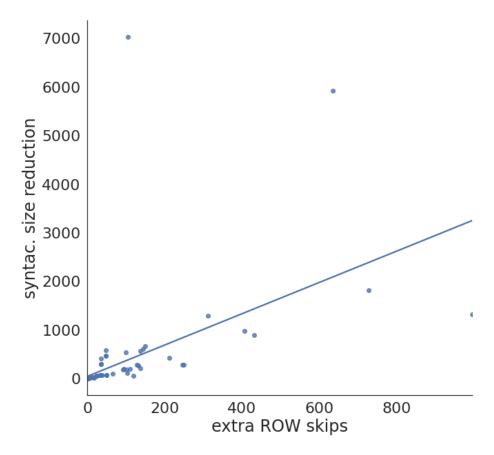

| 8.5  | $\#$ of extra ROW skips vs. reduction in syntactic size. $\ldots$ . $\ldots$ . $\ldots$         | 61 |

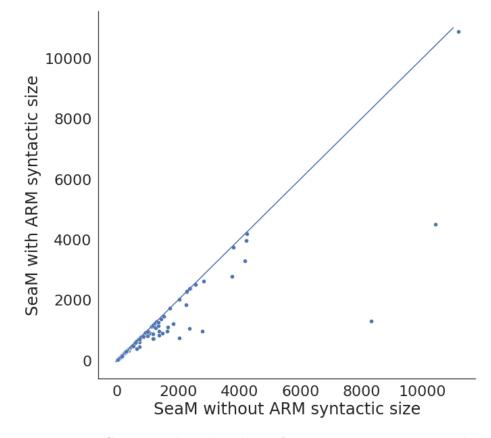

| 8.6  | SEAM with and without ARM syntactic size per task.                                              | 62 |

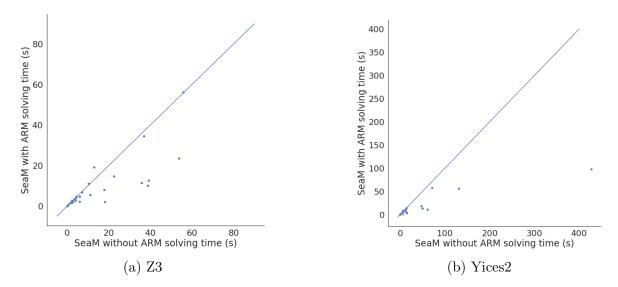

| 8.7  | SEAM with and without ARM solving time per task                                                 | 63 |

| 8.8  | Pre-processing time on SV-COMP tasks.                                                           | 65 |

| 8.9  | bAnd program source code                                                                        | 66 |

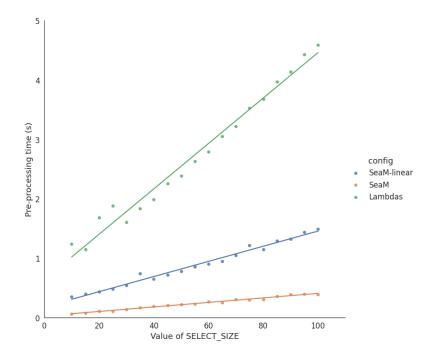

| 8.10 | Pre-processing time of SEAM configurations with increasing SELECT_SIZE.                         | 67 |

# List of Tables

| 8.1 | Overall BMC performance of SEAM, ARRAYS and LAMBDAS on aws-c-comm<br>benchmark with Z3. cnt, fld and to measures number of total tasks,<br>failed tasks and timeouts per category respectively. Timeout threshold                                                                                                                |    |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | is $1,200$ seconds                                                                                                                                                                                                                                                                                                               | 56 |

| 8.2 | Overall BMC performance of <b>SEAM</b> , <b>ARRAYS</b> and <b>LAMBDAS</b> on <b>aws-c-comm</b> benchmark with <b>Yices2</b> solver. <b>cnt</b> , <b>fld</b> and <b>to</b> measures number of <b>to-tal tasks</b> , <b>failed tasks</b> and <b>timeouts</b> per category respectively. Timeout threshold is set to 1,200 seconds. |    |

| 8.3 | BMC performance of <b>SEAM</b> with and without ARM on aws-c-common benchmark with <b>Z3</b> and <b>Yices2</b> . Timeout threshold is 1,200 seconds                                                                                                                                                                              | 61 |

| 8.4 | BMC performance on 10 SV-COMP programs.                                                                                                                                                                                                                                                                                          | 64 |

| 8.5 | BMC performance summary on bAnd.                                                                                                                                                                                                                                                                                                 | 65 |

# Chapter 1

## Introduction

Ensuring memory safety has always been one of the most crucial yet tricky aspects of any programming language that manipulates memory. Some high-level programming languages like Java [20] assist programmers with built-in runtime checks against certain memory faults like null pointer dereference and out-of-bound memory access. More recent development in programming language like Rust [23] attempt to achieve balance between high-level memory safety and low-level control with its *ownership* type system, where pointer aliasing is tracked *statically* to prevent direct mutation of aliased state. However, low-level languages often lack built-in memory safety mechanisms like those possessed by Java and Rust. The C language, for example, gives programmers low-level control of memory operations, yet features like arbitrary pointer arithmetic and manual memory management can take years to master, and can lead to catastrophic memory errors if used incorrectly. The lack of built-in compile-time or runtime checking means severe security exploits like *Heartbleed* [21] can go unnoticed for years in some of the most trusted software libraries like OpenSSL.

Over the years, C programmers have gained access to a plethora of 3rd-party tools for avoiding and detecting memory errors. Dynamic Binary Instrumentation (DBI) tools like Valgrind [26] check memory errors at runtime by executing instrumented binary under emulated environment. DBI tools allow for analysis of programs without the source code, yet often suffer from heavy overhead in terms of running time. Memory checks instrumented at compile-time alleviate running-time overhead by executing natively instead of under emulation. One of the most commonly used compile-time instrumentation tools is LLVM's **AddressSanitizer** [32]. The drawback of compile-time instrumentation tools is that they require the source code of program under analysis in order to re-compile under special configurations. The main drawback of all dynamic analysis tools is that their effectiveness rely on the quality of test suites executed. Even with a great test suite, it is still nearly impossible for dynamic analysis to explore all program states of any complex program. An alternative approach to ensure memory safety is through static analysis techniques like Bounded Model Checking (BMC) and Symbolic Execution (SE) [7]. Many static analysis approaches reduce the problem of program verification to Satisfiability Modulo Theories (SMT) [2] and then eventually to satisfiability (SAT) solving, which allows them to explore more of the program states without handcrafting as many test cases. To verify programs manipulating memory then, we need an expressive SMT theory that can model memory operations as well as efficient decision procedures that reduces the theory to simpler form.

The theory of arrays  $(\mathcal{T}_{\mathcal{A}})$  ([24], [1], [22]) is a common choice for modeling memory. An Array sort is defined by its *index* sort  $\sigma_I$  and *element* sort  $\sigma_E$ . An array can be seen as an infinite map from indices of  $\sigma_I$  to elements of  $\sigma_E$ . A write to memory is modeled by the  $\mathcal{T}_{\mathcal{A}}$  write (store in SMT-LIB2) operation: write :  $\sigma_A \times \sigma_I \times \sigma_E \to \sigma_A$ ; while a read from memory is modeled by the  $\mathcal{T}_{\mathcal{A}}$  read (select in SMT-LIB2) operation: read :  $\sigma_A \times \sigma_I \to \sigma_E$ . The reduction of formulas with  $\mathcal{T}_{\mathcal{A}}$  terms to equivalent formulas with only underlying theories of  $\sigma_I$  and  $\sigma_E$  along with if-then-else (*ite*) terms.

The basic form of  $\mathcal{T}_{\mathcal{A}}$  still has a few missing pieces for sufficiently modeling real-world C programs. **First**, the transformation of long sequences of *read*-over-*write* (ROW) terms can lead to large nested case-splits. [19] introduced a variety of preprocessing techniques that eliminates ROW terms, including *lazily* delaying the transformation of *read* terms by substituting them with new variables. Similarly, [6] replaces reads with variables of another theory (like uninterpreted functions) and tries to solve the formula *lazily*, only adding lemmas when inconsistencies occur between indices equality and read variables equality. A more recent work [18] further reduced the overhead of ROW elimination by grouping writes with *comparable* indices together. Note that [18] inspired much of our work in Chapter 6. Second, common memory operations over a range of indices like memcpy and memset cannot be represented succinctly by  $\mathcal{T}_{\mathcal{A}}$  read and write operations alone. Sinz et al. ([33], [17], [16]) addressed this issue by extending  $\mathcal{T}_{\mathcal{A}}$  to better model memcpy and memset operations. In their BMC tool LLBMC ([25], [15]), operations like memcpy and memset are directly modeled with succinct  $\lambda$ -terms instead of sequences of chained writes. Similar efforts have also been applied on the SMT solver side. Boolector [5], for example, matches patterns representing array operations over a range of consecutive indices and extracts  $\lambda$ -terms from the patterns [27].

Existing optimizations drastically improved the performance of array-based memory encodings. However, few has taken account C-specific memory rules. Specifically, C standard implies that given two *distinct* memory objects  $o_a$  and  $o_b$ , and two corresponding *legal* pointer arithmetic terms  $o_a + x$  and  $o_b + y$ , then  $o_a + x \neq o_b + y$  must hold. We hypothesize that by omitting C language specific properties like such, existing memory encodings could

miss certain simplification opportunities only applicable under C memory model.

In this thesis, we present SEAM, a more expressive memory representation preserving more features of the C language. The first component of the new memory representation is an expressive First-Order Theory called Theory of Memory  $\mathcal{T}_{\mathcal{M}}$  based on ROW axioms similar to those in  $\mathcal{T}_{\mathcal{A}}$ .  $\mathcal{T}_{\mathcal{M}}$  preserves features of C language source code such as rules for legal pointer arithmetic.  $\mathcal{T}_{\mathcal{M}}$  also contains succinct encoding of batch memory operations like **memcpy** and **memset** based on the extended  $\mathcal{T}_{\mathcal{A}}$  in [33]. We also present the rewrite rules for transforming formulas with  $\mathcal{T}_{\mathcal{M}}$  terms present to formulas containing only *ite* and underlying theory terms.

With memory operations encoded in  $\mathcal{T}_{\mathcal{M}}$ , we next showcase two optimization techniques enabled by  $\mathcal{T}_{\mathcal{M}}$ . **First**, we observe that one of the more expensive operations during ROW simplification is the resolution of (dis-)equalities between nested pointer expressions. If left to the SMT/SAT solver, these (dis-)equalities would require expensive ite-pull and ite-push transformations (see Chapter 2 for detail). For faster resolution of pointer (dis-)equality, we over-approximate pointer expressions with an Abstract Interpretation-inspired approach called Address Range Map (ARM), and apply comparisons between abstract values where possible.

**Second**, we make the observation that pre-processing each ROW term is an operation with *linear* time complexity. With  $\mathcal{T}_{\mathcal{M}}$ , memory *write* operations into addresses with different unique base address can be safely commuted since they are guaranteed to be disjoint; conversely, *writes* with identical unique base address can be grouped together for faster lookup. We introduce the STORE-MAP data structure to compress consecutive store operations, and present rewrite rules for *read-over-store-map* with *logarithmic* in best-case scenario.

SEAM is implemented as part of the Verification Engine of SeaBMC, a BMC tool that targets LLVM IR compatible languages like C. We evaluate our approach against existing basic array-based memory representation and lambda-based memory representation in SeaBMC, on the BMC tasks targeting real-world C code from the Verify-C-Common benchmark. Our current results show that  $\mathcal{T}_{\mathcal{M}}$ -based memory representation drastically outperforms array based approach in terms of verification time. We further observe that over-approximating pointer comparisons with ARM resulted in more pointer (dis-)equality resolutions, effectively reducing formula size and verification time. We also evaluate SEAM on selected verification tasks from SV-COMP that contain longer sequences of ROW terms. This set of experiments show that SEAM achieves similar level of simplification as  $\lambda$ -based encoding with lower overhead in terms of pre-processing time. The reduction in preprocessing overhead is even more pronounced with store compression using STORE-MAP.

### Chapter 2

## Background

This chapter serves as a basis for understanding the rest of the thesis. In this chapter, we first summarize rewrite rules and procedures for ite-terms, comparison terms and Boolean terms. This chapter describes the axoims and rules that establishes the basic form of the Theory of Arrays. Next, we present an extension of  $\mathcal{T}_A$  that allows for more succinct representation of batch memory operations like **memcpy** and **memset**. SEAM is implemented in SEABMC, a BMC tools for LLVM IR. We briefly summarize the design and features of SEABMC for modeling memory and verifying memory safety properties.

### 2.1 Basic rewrite rules

In this thesis, we frequently use *rewrite rules* to define semantics and simplification rules. For rest of the thesis, we use the notation  $\vdash_P \varphi$  to indicate that the formula  $\varphi$  is deduced to be valid by some proof system P, and  $\vdash \varphi$  when the proof system P is irrelevant. We write  $\models \varphi$  to indicate that  $\varphi$  is valid (but not necessarily provable). A rewrite rule

$$\frac{\vdash a}{t_1 \rightsquigarrow t_2}$$

means if a is proved to be valid, then the term  $t_1$  can be rewritten to  $t_2$ . This means that any formula  $\phi$  containing  $t_1$  is equivalent to the formula  $\phi[t_1/t_2]$ . For the rest of this thesis, when presenting axioms and rewrite rules, we assume that all free variables are implicitly universally quantified. For example, we write  $\psi(a)$  to mean  $\forall a \cdot \psi(a)$ .

Figure 2.1: Rewrite rules for *ite* terms.

In the rest of this thesis, we use *ite*-terms in the form of ite(c, a, b) as a shorthand for *if* c then a else b. Figure 2.1 defines the semantics of ite-terms with rewrite rules. Given an arbitrary function f, **ITE-PUSH** pushes f into an ite-term, and **ITE-PULL** lifts f from an ite-term. While the rewrite rules are shown for unary functions only, they easily extend to functions and predicates of arbitrary arity. As an example, we show rewrite rules for equality (a binary predicate) over ite-terms in **ITE-EQ** rules.

**Reducing ite-terms** A common problem in compiling expressions down to satisfiability solvers is to reduce the formulas to simpler expressions that can be represented effectively in CNF. Here, we describe the procedure for ite-terms.

Let  $\varphi$  be a formula containing an ite-term t of the form f(ite(c, x, y)). Construct a formula  $\psi$  as follows:  $\psi = (\varphi[t \mapsto f(w)] \land (c \Rightarrow w = x) \land (\neg c \Rightarrow w = y))$ , where w is a fresh variable not used in  $\varphi$ . Then,  $\varphi$  is SAT iff  $\psi$  is SAT, and  $\psi$  is approximately same size as  $\varphi$ :  $|\varphi| \approx |\psi|$ . The encoding is similar to Tseytin transformation [34] commonly used to encode arbitrary formulas to equisatisfiable CNF. The transformation is formalized by

the following rewrite rule:

$$\frac{t = f(ite(c, x, y)) \quad w \text{ fresh in } \varphi}{\varphi[t] \quad \rightsquigarrow \quad (\varphi[t \mapsto f(w)] \land (c \Rightarrow w = x) \land (\neg c \Rightarrow w = y))}$$

(2.1)

Note that while the transformation does not increase the size of the formula, it does introduce additional variables (namely w). This, in turn, complicates potential simplifications.

Comparison  $(=, \leq)$  terms are crucial for representing array operations with *ite*-terms by forming *index comparison*. The details are covered in Sec. 2.2. Figure 2.2 presents some basic rewrite rules for comparison terms.

$$\begin{array}{c|c} \vdash a = b & \bowtie \in \{\leq, =\} \\ \hline (a \ op \ p) \Join (b \ op \ q) & \rightsquigarrow \ p \Join q \\ \hline \hline a = b & \rightsquigarrow \ \top & \hline \hline a = b & \rightsquigarrow \ \bot \\ \hline \hline a \neq b & \rightsquigarrow \ \neg(a = b) \end{array}$$

Figure 2.2: Example rewrite rules for comparison terms.

In order to perform simplifications on *ite*-terms, it is necessary to first perform simplifications on the Boolean terms forming the *condition* part. Figure 2.3 presents some example rewrite rules for Boolean terms containing negations. Note that the rule **NEG-PUSH** is a variation of **ITE-PUSH**.

$$\overline{\neg(\neg(a))} \rightsquigarrow a \qquad \overline{\neg(ite(c, x, y))} \rightsquigarrow ite(c, \neg x, \neg y)$$

NEG-PUSH

$$\underbrace{\vdash a = \top}_{\neg(a) \rightsquigarrow \bot} \qquad \underbrace{\vdash a = \bot}_{\neg(a) \rightsquigarrow \top}$$

Figure 2.3: Example rewrite rules for Boolean terms.

Arithmetic (+, -) terms are also important for representing index arithmetics. Sec. 2.2 also shows index arithmetics representing the *range* of batch array operations. Figure 2.4 shows two rewrite rules for arithmetics containing addition (+) operation.

$$\frac{\vdash +(b,c) = d}{+(a,b,c) \iff +(a,d)} \text{ADD-COMPRESS}$$

$$\frac{}{+(a,+(b,c)) \iff +(a,b,c)} \text{ADD-FLATTEN}$$

Figure 2.4: Rewrite rules for addition arithmetic terms.

Note that apart from the purely syntactic rules, most of the rewrite rules presented above require certain assumption(s) to be true under some proof system. One of the more common assumptions take the form of (dis-)equality  $(=, \neq)$ . In Sec. 2.2 we show the importance of (dis-)equality between array indices. In Chapter 4 we show how preserving C memory semantics can serve as a proof system for deciding array-like index (dis-)equality checks. Furthermore, in Chapter 5 we show another proof system for index (dis-)equality checks based on abstract interpretation.

### 2.2 Theory of Arrays

Theory of arrays  $(\mathcal{T}_{\mathcal{A}})$  is commonly used to represent memory operations. The classic theory of arrays was first introduced by McCarthy [24] with the following signature:

$\Sigma_{\mathcal{A}} = \{read, write, =\}$ read :  $\sigma_A \times \sigma_I \to \sigma_E$ write :  $\sigma_A \times \sigma_I \times \sigma_E \to \sigma_A$

note that the binary function equality (=) is only defined between element terms and index terms in non-extensional  $\mathcal{T}_{\mathcal{A}}$ .  $\mathcal{T}_{\mathcal{A}}$  defines an array sort  $\sigma_{\mathcal{A}}$  with the element sort  $\sigma_{\mathcal{E}}$  and the index sort  $\sigma_{\mathcal{I}}$  of the array. The formation rules of terms in  $\mathcal{T}_{\mathcal{A}}$  and syntax of read and write are defined in Figure 2.5, where the detailed formation rules of index terms  $t_{\mathcal{I}}$  and element terms  $t_{\mathcal{E}}$  are determined by the underlying theories  $\mathcal{T}_{\mathcal{E}}$  and  $\mathcal{T}_{\mathcal{I}}$ .

| $t_{\mathcal{I}}$ | ::= |          |                                                            | index terms   |

|-------------------|-----|----------|------------------------------------------------------------|---------------|

| $t_{\mathcal{E}}$ | ::= |          | $read(t_{\mathcal{A}}, t_{\mathcal{I}})$                   | element terms |

| $t_{\mathcal{A}}$ | ::= | $a \mid$ | $write(t_{\mathcal{A}}, t_{\mathcal{I}}, t_{\mathcal{E}})$ | array terms   |

Figure 2.5: Term formation rules of  $\mathcal{T}_{\mathcal{A}}$ , *a* is an  $\sigma_A$  constant.

The semantics of *read* and *write* is defined by the following axioms:

$$\forall i, j \, . \, i = j \Rightarrow read(a, i) = read(a, j) \tag{A1}$$

$$\forall i, j \, . \, i = j \Rightarrow read(write(a, j, v), i) = v \tag{A2}$$

$$\forall i, j : i \neq j \Rightarrow read(write(a, j, v), i) = read(a, i)$$

(A3)

Axoim (A1) states that reading from the same array a at the same index shall yield the same element. Axoims (A2) and (A3) assert the rules for *read*-over-*write*. Given a modified array *write*(a, j, v), (A2) states that if a *read* over the same index as the previous *write*, then the *read* yields the written element; if the *read* is over a different index as the previous modification, the *read* shall always yield the element at index i of the unmodified array a.

**Extensionality** Note that with the above three axioms, it is only possible to compare the equality between *elements* of arrays. To compare equality between arrays themselves, we need to add the axiom of extensionality:

$$\forall a, b, i \, . \, a = b \Leftrightarrow read(a, i) = read(b, i) \tag{A4}$$

SEABMC, the BMC tools in which the new memory representation is implemented, uses only non-extensional theory of arrays. For the rest of this thesis, we write  $\mathcal{T}_{\mathcal{A}}$  to refer to the *non-extensional* theory of arrays.

Based on the *read*-over-*write* axioms, Figure 2.6 shows rewrite rules for  $\mathcal{T}_{\mathcal{A}}$  read-overwrite expressions that replace write terms with ites.

With the basic form of  $\mathcal{T}_{\mathcal{A}}$  presented above, each *write* operation can only represent modification of array contents one index at a time. Given consecutive writes to memory or batch memory operations such as **memset** and **memcpy** over *n* indices then,  $\mathcal{T}_{\mathcal{A}}$ represents the operations with sequences of *writes* with size growing linearly to *n*. This behaviour creates a significant performance bottleneck at both the simplification stage and the SMT/SAT solving stage. Furthermore, it would be impossible to accurately represent batch memory operations with *n* of *variable* (symbolic) value. In the next section, we present an alternative way to encode batch memory operations with  $\lambda$ -expressions. Chapter 6 also presents a potential approach to compress consecutive writes to memory.

$$\begin{array}{c} \hline read(write(a,i,v),j) & \rightsquigarrow ite(i=j,v,read(a,j)) \\ \hline \hline ead(write(a,i,v),j) & \rightsquigarrow ite(i=j,v,read(a,j)) \\ \hline \hline read(write(a,i,v),j) & \rightsquigarrow read(a,j) \\ \hline \end{array}$$

Figure 2.6: Rewrite rules for  $\mathcal{T}_{\mathcal{A}}$  read-over-write expressions.

### 2.3 Encoding set/copy memory operations

Work from Falke ([17], [16]) introduced theory of arrays with set and copy operations  $(\mathcal{T}_{ASC})$ .  $\mathcal{T}_{ASC}$  extends  $\mathcal{T}_A$  with additional signatures that describe array operations over a range of size term  $t_S$  with sort  $\sigma_S$ :

$$\begin{split} \Sigma_{\mathcal{ASC}} &= \Sigma_{\mathcal{A}} \cup \{ copy, set, +, -, \leq, < \} \\ set : \sigma_A \times \sigma_I \times \sigma_E \times \sigma_S \to \sigma_A \\ copy : \sigma_A \times \sigma_I \times \sigma_A \times \sigma_I \times \sigma_S \to \sigma_A \end{split}$$

Note the addition of arithmetic operations (+, -) and comparison operations  $(\leq, <)$  to the signature. They are defined between terms of  $\sigma_I$  and  $\sigma_S$  sorts to represent contiguous range of indices. The underlying theories of  $\sigma_I$  and  $\sigma_S$  are therefore numeric such as the theory of BitVectors  $(\mathcal{T}_{\mathcal{BV}})$ .

The term formation rule of  $\mathcal{T}_{ASC}$  is also expanded, shown in Figure 2.7

| $t_{\mathcal{I}}$ | ::= |                                                                                             | index terms   |

|-------------------|-----|---------------------------------------------------------------------------------------------|---------------|

| $t_{\mathcal{S}}$ | ::= |                                                                                             | size terms    |

| $t_{\mathcal{E}}$ | ::= | $  read(t_{\mathcal{A}}, t_{\mathcal{I}})$                                                  | element terms |

| $t_{\mathcal{A}}$ | ::= | $a \mid write(t_{\mathcal{A}}, t_{\mathcal{I}}, t_{\mathcal{E}})$                           | array terms   |

|                   |     | $set(t_{\mathcal{A}}, t_{\mathcal{I}}, t_{\mathcal{E}}, t_{\mathcal{S}})$                   |               |

|                   |     | $copy(t_{\mathcal{A}}, t_{\mathcal{I}}, t_{\mathcal{A}}, t_{\mathcal{I}}, t_{\mathcal{S}})$ |               |

Figure 2.7: Term formation rules of  $\mathcal{T}_{ASC}$

Informally, a set(a, p, v, s) operation sets all elements of a with indices in the range between p and p + s - 1 to the value v; a copy(a, p, b, q, s) writes the values of elements in array b with indices between q and q + s - 1 to elements in array a with indices between p and p + s - 1. Formally, the semantics of a *read* over **set/copy** is defined by the following axioms:

$$\forall p, i, s \, . \, p \le i$$

$$\forall p, i, s . \neg (p \le i

(A6)$$

$$\forall p, i, s \, . \, p \le i$$

$$\forall p, i, s . \neg (p \le i

(A8)$$

Based on axioms A5-A8, we can devise rewrite rules for *read*-over-set (Figure 2.8) and *read*-over-copy (Figure 2.9) that eliminate set and copy terms.

Figure 2.8: Rewrite rules for *read*-over-set

$$read(copy(a, p, b, q, s), i) \rightsquigarrow ite(p \le i < (p + s), read(b, q + (i - p)), read(a, i))$$

$$\begin{split} & \vdash p \leq i < (p+s) \\ \hline read(copy(a,p,b,q,s),i) & \rightsquigarrow \ read(b,q+(i-p)) \\ \\ & \frac{ \vdash \neg (p \leq i < (p+s)) }{ read(copy(a,p,b,q,s),i) & \rightsquigarrow \ read(a,i) } \end{split}$$

#### Figure 2.9: Rewrite rules for *read*-over-copy

$\mathcal{T}_{ASC}$  enables more succinct and precise encoding of memory state of programs containing batch memory operations like set and copy. The improvement is especially crucial for applications like BMC, which alternatively treats set and copy like iterations with basic  $\mathcal{T}_{A}$ encoding. With a finite limit on unrolling, soundness of the verification is compromised when the size of address range is symbolic.

### 2.4 Encoding Arrays with $\lambda$ -expressions

Instead of eagerly rewriting *read*-over-array expressions, it is also possible to simulate array operations using  $\lambda$ -expressions. In fact, all  $\sigma_A$  terms can be expressed using a  $\lambda$ -expression  $\lambda i.s$ , where *i* is a bound variable of sort  $\sigma_I$  and *s* is an expression of sort  $\sigma_E$ .

Based on *read*-over-*write* axioms, write(a, j, v) can be simulated with a  $\lambda$ -term:

$write(a, j, v) \rightsquigarrow \lambda i.ite(i = j, v, read(a, j))$

Similarly, set and copy can also be rewritten:

$$set(a, p, v, s) \rightsquigarrow \lambda i.ite(p \le i < (p + s), v, read(a, i))$$

$$copy(a, p, b, q, s) \rightsquigarrow \lambda i.ite(p \le i < (p + s), read(b, q + (i - p)), read(a, i))$$

A read over  $\sigma_A$  term is then just applying  $\beta$ -reduction over  $\lambda i.s$ :

$read(\lambda i.s, r) = s[i/r]$

The  $\lambda$ -based encoding allows for aggressive simplification of memory state expressions through beta-reduction during the *creation* / *update* stage of arrays.

In our new memory representation, the new theory of memory  $\mathcal{T}_{\mathcal{M}}$  handles set and copy operations in C programs (memcpy, memset) largely the same as  $\mathcal{T}_{\mathcal{ASC}}$ . Improving upon  $\mathcal{T}_{\mathcal{A}}$  and  $\mathcal{T}_{\mathcal{ASC}}$ , however,  $\mathcal{T}_{\mathcal{M}}$  preserves C memory semantics to enable more conclusive index comparisons and creates possibility for techniques like ARM and STORE-MAP.

### 2.5 SEABMC

In this section, we provide an overview of SEABMC, with a focus on how it models memory operations.

**SEA-IR** SEABMC is a BMC tool developed for LLVM-based languages; input programs under verification are first translated into the intermediate representation (IR) of LLVM called *bitcode*. Next, SEABMC extends raw LLVM *bitcode* input into an IR with explicit dependency information between memory operations called SEA-IR. A simplified subset of the SEA-IR grammar is defined in Figure 2.10.

A well-formed SEA-IR program (PR) must contain a single entry function named main. A main function must contain one or more basic blocks (BB). Each BB consists of a label (L), zero or more PHI-statements which represents control flow, one or more statements (S) and ends with a branch (br) statement or halt. The last BB must end with halt marking program termination. Registers are separated into three types: scalar registers R, pointer registers P and memory registers M. Scalar registers store primitive data type values like integers. Pointer registers store pointer values returned by memory allocations or by reading from memory (pointer to pointer). Memory registers represent memory states returned by either fresh allocations or writing to existing memory. For encoding C programs, SEA-IR also includes the signatures memcpy :  $\mathbf{P}, \mathbf{P}, \mathbf{R}, \mathbf{M}, \mathbf{M} \to \mathbf{M}$  and memset :  $\mathbf{P}, \mathbf{R}, \mathbf{R}, \mathbf{M} \to \mathbf{M}$  for representing C memcpy, memset functions. Verification users can define constraints on scalar values with assume and express assertions with assert.

Memory model in SEABMC It is common practice for software verification tools to use a single *flat* array to represent the memory state of a program. However, many language semantics treat memory objects from different allocation site as disjoint regions in memory. Instead of the *flat* memory model, SEABMC partitions all memory objects into disjoint sets of memory regions using alias analysis. To aid program analysis, SEA-IR follows the MemorySSA [8] scheme in which memory operations are *pure*. Allocating a fresh object (alloca / malloc) or writing to existing memory (store) defines new memory registers; in other words, memory write operations have no *side effects* on existing defined memory registers. Read statements (load) are also annoted with the source memory registers.

**Verification Condition Generation (VCGen)** After performing a series of further transformations on the input SEA-IR program SEABMC produces program with following features:

- single assertion: only contains one **assert** statement at the end of the last basic block;

- single assumption: only contains one **assume** statement before the sole **assert** statement;

- pure data flow: PHI branching statements are replaced with select statements (semantic same as ITE), the program contains a single basic block with all branching paths merged with select (ITE) statements

| $\mathbf{PR}$  | ::= | $\texttt{fun main}()\{\mathbf{BB}^+\}$                                                                                                                       |

|----------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BB             | ::= | $\mathbf{L}$ : $\mathbf{PHI}^*$ $\mathbf{S}^+$ $(\mathbf{BR} \mid \texttt{halt})$                                                                            |

| $\mathbf{BR}$  | ::= | br $\mathbf{E}, \ \mathbf{L}, \ \mathbf{L} \ \mid \ $ br $\mathbf{L}$                                                                                        |

| $\mathbf{PHI}$ | ::= | $\mathbf{R}=	ext{phi} \ [\mathbf{R}, \ \mathbf{L}](, \ [\mathbf{R}, \ \mathbf{L}])^*$                                                                        |

|                |     | $\mathbf{M}=	t{phi}\;[\mathbf{M},\;\mathbf{L}](,\;[\mathbf{M},\;\mathbf{L}])^{*}$                                                                            |

|                | Ì   | $\mathbf{P}=	extsf{phi}\;[\mathbf{P},\;\mathbf{L}](,\;[\mathbf{P},\;\mathbf{L}])^{*}$                                                                        |

| $\mathbf{S}$   | ::= | $RDEF \mid MDEF \mid VS$                                                                                                                                     |

| RDEF           | ::= | $\mathbf{R} = \mathbf{E} \hspace{0.1 in}   \hspace{0.1 in} \mathbf{P}, \mathbf{M} = 	textsf{alloca} \hspace{0.1 in} \mathbf{R}, \mathbf{M}$                  |

|                |     | $\mathbf{P}, \mathbf{M} = \texttt{malloc} \ \mathbf{R}, \ \mathbf{M}     \mathbf{R} = \texttt{load} \ \mathbf{P}, \ \mathbf{M}$                              |

|                |     | $\mathbf{P} = \texttt{load} \; \mathbf{P}, \; \mathbf{M} \; \mid \; \mathbf{M} = \texttt{free} \; \mathbf{P}, \; \mathbf{M}$                                 |

| MDEF           | ::= | $\mathbf{M} = \mathtt{store} \; \mathbf{R}, \; \mathbf{P}, \; \mathbf{M} \; \mid \; \mathbf{M} = \mathtt{store} \; \mathbf{P}, \; \mathbf{P}, \; \mathbf{M}$ |

|                |     | $\mathbf{M} = \texttt{memset} \ \mathbf{P}, \ \mathbf{R}, \ \mathbf{R}, \ \mathbf{M}$                                                                        |

|                | Ì   | $\mathbf{M} = \texttt{memset} \; \mathbf{P}, \; \mathbf{R}, \; \mathbf{P}, \; \mathbf{M}$                                                                    |

|                | Ì   | $\mathbf{M} = \texttt{memcpy} \; \mathbf{P}, \; \mathbf{P}, \; \mathbf{R}, \; \mathbf{M}, \; \mathbf{M}$                                                     |

| $\mathbf{VS}$  | ::= | assume $\mathbf{R}^{-}$   asssert $\mathbf{R}$                                                                                                               |

Figure 2.10: Simplified grammar of SEA-IR, where E, L R, P and M are expressions, labels, scalar registers, pointer registers and memory registers, respectively. Credit to Siddharth Priya.

The transformed SEA-IR program is then translated into verification conditions (VC) in SMT-LIB2 with a function  $sym : IR \to VC$ . We use *scalr* and *ptrs* to represent the sorts of variables translated from SEA-IR scalar and pointer registers. The underlying sort of *scalr* and *ptrs* are usually BitVectors (*bv*). The sort of translated memory registers is defined as *mems* : *ptrs*  $\to$  *bv*(*n*), where *n* is the same as underlying BitVector of *ptrs*. *sym* encodes the SEA-IR AST in bottom up fashion. First, SEA-IR registers Mn, Rn or Pn are translated to variables or constants of corresponding sort  $m_n$ ,  $r_n$  or  $p_n$ . Second, each expression E is translated into a SMT-LIB2 expression sym(E). The details of expressionwise translation are omitted since most of them are trivial. Each statement S is translated into a Boolean SMT-LIB2 formula, the most common form being an equality(=) predicate. Finally, a single SMT-LIB2 formula is produced from the conjunction of *sym* results of all statements. Some of the statement-wise semantics of *sym* is presented in Figure 2.11.

Memory allocation The sym translation of stack allocation (alloca) and heap allocation (malloc) returns a conjunction of equality predicates each defining contraints on new pointer and new memory. The constraint on the new pointer depends on the implementation of *memory allocator* denoted by function *alloc*, which takes allocation type  $sym(\mathbf{R} = \mathbf{E}) \triangleq r = e \qquad sym(\texttt{assume } \mathbf{R}) \triangleq r \qquad sym(\texttt{assert } \mathbf{R}) \triangleq \neg r$  $sym(\mathbf{M1} = \texttt{store } \mathbf{R1}, \mathbf{P2}, \mathbf{M0}) \triangleq m_1 = write(m_0, r_1, p_2)$  $sym(\mathbf{M1} = \texttt{memset } \mathbf{P1}, \mathbf{R1}, \mathbf{R2}, \mathbf{M0}) \triangleq m_1 = memset(m_0, p_1, r_1, r_2)$  $sym(\mathbf{M1} = \texttt{memset } \mathbf{P1}, \mathbf{R1}, \mathbf{P2}, \mathbf{M0}) \triangleq m_1 = memset(m_0, p_1, r_1, p_2)$  $sym(\mathbf{M2} = \texttt{memcpy } \mathbf{P1}, \mathbf{P2}, \mathbf{R1}, \mathbf{M0}, \mathbf{M1}) \triangleq m_2 = memcpy(m_0, p_1, m_1, p_2, r_1)$  $sym(\mathbf{R1} = \texttt{load } \mathbf{P0}, \mathbf{M}) \triangleq p_1 = read(m, p_0)$  $sym(\mathbf{P1}, \mathbf{M1} = \texttt{allocc} \mathbf{R0}, \mathbf{M0}) \triangleq p_1 = alloc(\texttt{alloca } \mathbf{R0}, \mathbf{M0}) \land m_1 = m_0$  $sym(\mathbf{P1}, \mathbf{M1} = \texttt{malloc } \mathbf{R0}, \mathbf{M0}) \triangleq p_1 = alloc(\texttt{malloc } \mathbf{R0}, \mathbf{M0}) \land m_1 = m_0$

Figure 2.11: Definition of some *sym* semantics for translating parts of VC, **RDEF** and **MDEF**.

(heap, stack), allocation size and source memory register and returns a pointer. *Memory allocator* places important language specific constraints on freshly allocated pointers. For example, pointer addresses are aligned to word bit width; heap addresses and stack addresses are disjoint, etc.

**Memory representations in SEABMC** Note that in Figure 2.11, the detail semantics of *sym* on memory operations **store**, **select**, **memset** and **memcpy** are abstracted in functions *read*, *write*, *memset* and *memcpy* respectively. The detailed semantics of *sym* on these memory operations are encapsulated in *memory representations*. In SEABMC, currently there are two memory representations:

1. ARRAYS: Memories are modeled after  $\mathcal{T}_{\mathcal{A}}$  as described in Sec. 2.2. SEA-IR expressions memory operations are translated to  $\mathcal{T}_{\mathcal{A}}$  expressions following signatures of ArrayEx<sup>1</sup>. ARRAYS handles wide memory operations like *memset* and *memcpy*, with nested Array **stores** as shown in Figure 2.12. This is not sound when BMC unroll bound is insufficient or when range of operation is *symbolic*.

<sup>&</sup>lt;sup>1</sup>http://smtlib.cs.uiowa.edu/theories-ArraysEx.shtml

|                                   | ARRAYS                                                                                                                                                  | LAMBDAS                                  |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| $read(m, p_0)$                    | select $m p_0$                                                                                                                                          | $m(p_0)$                                 |

| $write(m_0, r_1, p_2)$            | store $m_0 \; r_1 \; p_2$                                                                                                                               | $\lambda x.ite(x = p_2, r_1, m_0(x))$    |

| $memset(m_0, p_1, r_1, r_2)$      | (store                                                                                                                                                  | $\lambda x.ite(p_1 \le x < (p_1 + r_1),$ |

|                                   | (store                                                                                                                                                  | $r_2, m_0(x))$                           |

|                                   | $(\text{store } m_0 \ r_2 \\ (+ \ p_1 \ (- \ r_1 \ 1))) \\ \dots \\ r_2 \ (+ \ p_1 \ 1)) \\ r_2 \ p_1)$                                                 |                                          |

| $memcpy(m_0, p_1, m_1, p_2, r_1)$ | (store<br>(store<br><br>(store $m_0$<br>(select $m_1$ (+ $p_1$<br>(+ $p_1$ (- $r_1$ 1)))<br><br>(select $m_1$ (+ $p_2$<br>(select $m_1$ $p_2$ ) $p_1$ ) |                                          |

Figure 2.12: sym translation of memory operations in LAMBDAS and ARRAYS.

2. LAMBDAS: Memories are modeled with  $\lambda$ -functions as described in Sec. 2.4. As shown in Figure 2.12, writing to memory  $write(m_0, r_1, p_2)$  is simulated with a  $\lambda$  function  $\lambda x.ite(x = p_2, r_1, m_0(x))$ ; reading from memory  $read(m, p_0)$  is translated by applying a pointer value as argument to a  $\lambda$  function  $m(p_0)$ . Formulas can be simplified with  $\beta$ reduction, resulting in final VC containing *ites* only, eliminating the need of ArrayEx support in SMT solver.  $\lambda$ -functions provide *sound* encoding for *memset* and *memcpy*.

SEABMC also applies techniques like shadow memory and fat pointers to verify both temporal and spatial memory safety, detailed in [29]. These techniques are applied at a higher level than memory representation and are thus out of the scope of this thesis. Neither of the existing memory representations in SEABMC retain much information from C memory semantics, as detailed in Chapter 3 and Chapter 4. The contributions in this thesis presents an alternative memory representation SEAM for SEABMC. SEAM explores possibilities for improving VC simplification performance by preserving C semantics and implementing custom optimization techniques during VCGen.

### Chapter 3

## Overview

This chapter provides an overview of the approaches used in SEAM using a series of examples. Consider sample C program  $P_1$  in Figure 3.1.

```

typedef struct { int a; int b; } s;

int main() {

int *num = malloc(sizeof(int)); // obj<sub>8</sub>

*num = 4;

s *st = malloc(sizeof(s)); // obj<sub>16</sub>

st->a = 21, st->b = 42;

int *p = nd_bool() ? &(st->a) : &(st->b);

*p = 4;

assert(*num == st->b); // read-over-write

return 0;

}

```

Figure 3.1: Sample C program containing memory operations  $P_1$ .

The program initializes an integer num and a structure st containing two integer fields. It non-deterministically writes the same value in num into one of the fields in st. Figure 3.2 shows the memory state of  $P_1$  denoted by mem<sub>1</sub> encoded with  $\mathcal{T}_A$  after the execution of line 17. For demonstration, we use a fresh variable  $obj_n$  to represent a pointer to allocated memory objects.

Note that the final assertion on line 18 depends on two reads on  $mem_1$ : first read (\*num) is on the address  $obj_8$ ; second read is on the address  $obj_{16} + 8$ . According to the *read*-over-*write* axioms (A2), (A3) and rewrite rules in Figure 2.6, the two *read*-over-*write* expressions can be eagerly rewritten into *ite*-expressions in Figure 3.3a and Figure 3.4a.

```

(select mem_1 obj_8) =

(select mem_1 obj_8) =

(ite false 4 4) = 4

(ite

(=

obj<sub>8</sub>

(ite bool<sub>a</sub> obj_{16} (+ obj_{16} 8)))

4

(ite

(= obj_8 (+ obj_{16} 8))

42

(ite

(= obj_8 obj_{16})

21

(ite

(= obj_8 obj_8)

(select mem<sub>0</sub> obj<sub>8</sub>)

)

)

)

)

(a) Full expression of after rewrite into ite.

(b) Simplified expression.

```

Figure 3.3:  $\mathcal{T}_{\mathcal{A}}$  expression of *read*-over-*write* operation \*num.

```

(select mem_1 (+obj<sub>16</sub> 8))

(select mem_1 (+obj_{16} 8))

(ite

(ite

(=

(ite

(+obj<sub>16</sub> 8)

bool<sub>a</sub>

(ite bool<sub>a</sub> obj<sub>16</sub> (+ obj<sub>16</sub> 8)))

(= (+obj_{16} \ 8) \ obj_{16})

4

(= (+obj_{16} 8) (+obj_{16} 8)))

4

(ite

(= (+obj_{16} 8) (+ obj_{16} 8))

42)

42

=

(ite

(ite

(= (+obj_{16} \ 8) \ obj_{16})

(ite bool<sub>a</sub> false true)

21

(ite

42)

(= (+obj_{16} \ 8) \ obj_8)

= (ite (not bool_a) 4 42)

(select mem_0 (+obj<sub>16</sub> 8))

)

)

(b) Simplified expression.

```

(a) Full expression of after rewrite into *ite*.

Figure 3.4:  $\mathcal{T}_{\mathcal{A}}$  expression of *read*-over-*write* operation st->b.

Any reasoning or simplification on the rewritten *ite*-expressions depend heavily on (dis-)equality checks between each pair of *read* (select) and *write* (store) indices. Certain checks can be resolved with trivial syntactic check, for example  $obj_8 = obj_8$  is True and  $obj_16+8 = obj_{16}+8$  is *False*. However, (dis-)equality checks like  $obj_8 = (obj_{16}+8)$  would be *inconclusive* if address bases like  $obj_8$  and  $obj_{16}$  are *symbolic* variables. SEABMC optionally uses concrete numbers to represent address bases instead, which can result in more conclusive (dis-)equality checks. Still, this approach would fail to resolve (dis-)equalities where offsets are symbolic: consider the (dis-)equality check  $(obj_8 + x) = (obj_{16} + y)$ . Also, using concrete numbers for address bases result in loss of generality in terms of allocation schemes. However, such (dis-)equality check should be conclusive if C semantics is taken into consideration: any legal pointer arithmetic operations on pointers from different objects will never be equal. Hence  $(obj_8 + x) = (obj_{16} + y)$  is always false. In Chapter 4, we introduce Theory of Memory  $(\mathcal{T}_{\mathcal{M}})$  which preserves key C semantics to enable more simplification opportunities.

Next, consider (dis-)equality checks involving *ite*-expressions such as  $obj_8 = ite(bool_a, obj_{16}, (obj_{16}+8))$ . A typical strategy for reasoning over such expressions is to perform an ITE-PUSH rewrite:  $ite(bool_a, obj_{16} = obj_8, (obj_{16} + 8) = obj_8)$ , and try to resolve equalities at leave nodes of *ite*-expressions. This approach could be expensive as the size of rewritten expression grows significantly, especially when both *lhs* and *rhs* of the equality contain nested *ite*-expressions. However, from the example equality check one can make the observation that the *lhs* of the equality can possibly resolve to the set of addresses  $A_L = \{obj_8\}$ , while the *rhs* can resolve to  $A_R = \{obj_{16}, obj_{16} + 8\}$ . With C memory semantics in mind, we can prove  $A_R \cap A_L = \emptyset$  since they do not contain any address from the same memory object, hence the equality check is conclusively *False*. In the above demonstration, notice that  $A_L$  and  $A_R$  can be extracted individually from the *lhs* and *rhs* parts without performing **ITE-PUSH**. Similarly, in Chapter 5, we show that certain pointer dis-equalities can be resolved more efficiently by reasoning over the *abstract value* of the pointer expressions. We show that the *abstract values* can be computed *in place* without performing expensive **ITE-PUSH** rewrites.

Applying all aforementioned simplifications, it is possible to simplify the two read-overwrite expressions into shorter versions in Figure 3.3b and Figure 3.4b. However, notice the number of read-over-write simplifications for each read grows linearly to the number of writes. When analysing larger programs with large number of writes, simplification at pre-process could become a bottleneck. Consider another C program  $P_2$  in Figure 3.5 with multiple memory writes to same memory locations.

```

typedef struct { int a; int b; } s;

int main() {

2

int *num = malloc(sizeof(int)); // obj8

3

s *st = malloc(sizeof(s));

// obj<sub>16</sub>

4

st -> a = 21;

5

*num = 4;

6

st -> b = 42;

7

st -> a = 42;

*num = 8;

9

st -> b = 21;

assert(*num < st->b); // read-over-write

return 0;

12

}

```

$^{14}$  Figure 3.5: Sample C program  $P_{\mathcal{Z}}$  containing multiple memory operations on same addresses.

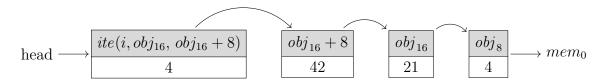

Neglecting compiler optimizations, the memory state of  $P_2$  is shown in Figure 3.6a.

```

mem_2 =

mem_2 =

(store

(store

(store

(store

(store

(store mem<sub>0</sub> obj<sub>16</sub> 42)

(+ obj<sub>16</sub> 8) 21)

(store

(store

obj<sub>8</sub> 8)

(store mem_0 obj<sub>16</sub> 21)

obj<sub>8</sub> 4)

(+ obj<sub>16</sub> 8) 42)

obj<sub>1</sub>6 42)

obj<sub>8</sub> 8)

(+ obj<sub>16</sub> 8) 21)

(a) Unsimplified full expression.

(b) Simplified expression.

```

Figure 3.6: Memory state of  $P_2$  after line 10 encoded in  $\mathcal{T}_A$ .

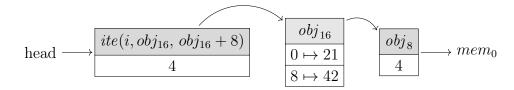

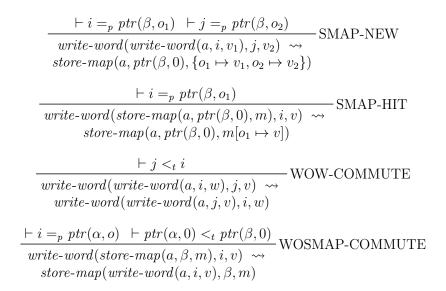

Considering C memory semantics once again, it is easy to see that after line 10 of  $P_2$ , although there have been 6 memory writes, only 3 distinct addresses have been written to. The first 3 writes are effectively overwritten and can be erased from the memory state. Figure 3.6b shows the simplified expression representing memory state after line 10. Also note that the addresses  $obj_{16}$  and  $obj_{16} + 8$  are *comparable*: the predicate < is defined between them. Addresses like such can be grouped in a sorted fashion such that *binary search* can be done on them instead of *linear search* during *read*-over-*write* simplifications.

In Chapter 6, we introduce an approach that compresses *writes* in a fashion similar to the example shown in Figure 3.6. Repeating writes to the same address are compressed; writes to addresses with the *same base* are grouped in dedicated data structure in order to improve the time complexity of *read*-over-*write* simplification from linear to logarithmic in best case scenario.

## Chapter 4

## Theory of Memory

In Figure 2.12, we introduced how SEABMC translates statements in SEA-IR into VCs with sym under currently implemented memory representations. The ARRAYS memory representation essentially models memory with arrays of BitVectors, and leverages existing syntax and semantics of ArrayEx theory, which is widely supported by most modern SMT-solvers. The LAMBDAS also models memory with arrays of BitVectors, but simulates array operations with  $\lambda$ -functions. This enables more efficient and precise representation of ranged memory operations like memory and memset in C, as well as enabling eager simplification through  $\beta$  reduction. Note that while there are careful distinctions between memory, pointer and scalar registers in SEA-IR, sym with LAMBDAS and ARRAYS loses such distinctions in translation. For example, pointer registers and scalar registers would both be translated into BitVectors in final VC. Language specific semantics are also not properly modeled by existing memory representations. As demonstrated in Chapter 3, we believe such loss of language-specific information would lead to loss of simplification opportunities, thus worsening the burden of SMT solvers.

In this chapter, we introduce the theory of memory  $\mathcal{T}_{\mathcal{M}}$  with signatures

$$\begin{split} \Sigma_{\mathcal{M}} &= \{\circ_{s}, \circ_{p}, \bowtie_{s}, \bowtie_{p}, write-word, read-word, write-byte, read-byte, memset-words, memcpy-words\} \\ ptr: \sigma_{S}^{word} \times \sigma_{S}^{word} \rightarrow \sigma_{P} \\ write-word: \sigma_{M} \times \sigma_{P} \times \sigma_{S}^{word} \rightarrow \sigma_{M} \\ read-word: \sigma_{M} \times \sigma_{P} \rightarrow \sigma_{S}^{word} \\ write-byte: \sigma_{M} \times \sigma_{P} \times \sigma_{S}^{byte} \rightarrow \sigma_{M} \\ read-byte: \sigma_{M} \times \sigma_{P} \rightarrow \sigma_{S}^{byte} \\ memset-words: \sigma_{M} \times \sigma_{P} \times \sigma_{S}^{word} \times \sigma_{S}^{word} \rightarrow \sigma_{M} \\ memcpy-words: \sigma_{M} \times \sigma_{P} \times \sigma_{M} \times \sigma_{P} \times \sigma_{S}^{word} \rightarrow \sigma_{M} \end{split}$$

$\mathcal{T}_{\mathcal{M}}$  aims to present a precise and efficient encoding of C programs that deal with memory by preserving certain C memory semantics in its axioms.  $\mathcal{T}_{\mathcal{M}}$  is parameterized by scalar theory  $\mathcal{T}_{\mathcal{S}}$ , pointer theory  $\mathcal{T}_{\mathcal{P}}$  and condition theory  $\mathcal{T}_{\mathcal{C}}$ .  $\mathcal{T}_{\mathcal{S}}$  and  $\mathcal{T}_{\mathcal{C}}$  are both single-sorted theories of sort  $\sigma_S$  and  $\sigma_C$  respectively.  $\mathcal{T}_{\mathcal{S}}$  models scalar values and needs to support linear arithmetic operators  $+, -, =, \leq, <; \mathcal{T}_{\mathcal{C}}$  models Boolean values and needs to support Boolean operators and  $(\wedge)$ , or  $(\vee)$ . In practice, both  $\mathcal{T}_{\mathcal{S}}$  and  $\mathcal{T}_{\mathcal{C}}$  are implemented with theory of BitVectors  $(\mathcal{T}_{\mathcal{BV}})$ . Note that in order to represent the bit width difference between bytes and words,  $\sigma_S$  needs to be parameterized by bit width. This is also handled by  $\mathcal{T}_{\mathcal{BV}}$ . We use  $\sigma_S^n$  to denote a scalar sort of bit width n, and  $t_S^n$  to denote an n-bit scalar term. The term formation rules of  $\mathcal{T}_{\mathcal{M}}$  are defined in Figure 4.1.

A pointer term  $t_{\mathcal{P}}$  is defined by the function  $ptr : \sigma_S \times \sigma_S \to \sigma_P$ . The first scalar term *b* represents *base* and the second scalar term *o* represents *offset*. A *base* represents the starting address of a C memory object. Note a similar set of *compare* operations are defined for scalar terms and pointer terms. We use different subscripts differentiate the two sets of operations ( $\bowtie_s$  and  $\bowtie_p$ ). The semantics of pointer comparison in  $\mathcal{T}_{\mathcal{M}}$  are defined by axioms in Figure 4.2. Two  $t_{\mathcal{P}}$ s with different *base* are not equal. This preserves the C semantics that two pointers from two different *objects* cannot be equal. Note that two  $t_{\mathcal{P}}$ s are only comparable (operators  $\leq_p$ ,  $<_p$  defined) if and only if their *bases* are identical. Semantics of pointer arithmetics in  $\mathcal{T}_{\mathcal{M}}$  are defined by axioms in Figure 4.3. Pointer term can also be formed by performing pointer addition  $+_p$  between a pointer term and a scalar offset; performing pointer subtraction  $-_p$  between pointers with same base would yield the scalar difference in offsets between them.

With new pointer syntax and semantics, we now also need to modify the semantics of allocation in *sym*. The behaviour of *memory allocator* remains unchanged: *alloc* now

Figure 4.1: Term formation rules of  $\mathcal{T}_{\mathcal{M}}$  for programs with 8-bit byte size, 32-bit word size. Operations between pointer and scalar terms are differentiated with subscripts p and s.

places constraints on newly created  $t_{\mathcal{P}}$  terms as side conditions.

$$\begin{split} sym(\texttt{P1}, \ \texttt{M1} = \texttt{alloca } \texttt{R0}, \ \texttt{M0}) &\triangleq p_1 = ptr(obj_n, 0) \land \\ ptr(obj_n, 0) = alloc(\texttt{alloca } \texttt{R0}, \ \texttt{M0}) \land m_1 = m_0 \\ sym(\texttt{P1}, \ \texttt{M1} = \texttt{malloc } \texttt{R0}, \ \texttt{M0}) &\triangleq p_1 = ptr(obj_n, 0) \land \\ ptr(obj_n, 0) = alloc(\texttt{malloc } \texttt{R0}, \ \texttt{M0}) \land m_1 = m_0 \end{split}$$

The new base  $obj_n$  created at each allocation site is a fresh scalar variable that is greater than all previous allocation bases to denote *temporal* order of allocation. This would be useful later in Chapter 6.

mem-identifier denotes a symbol or constant of memory sort  $\sigma_M$ . A memory term  $t_{\mathcal{M}}$  represent a mapping from a pointer to either a byte or a word. Writing a byte or a word to memory is represented by write-byte :  $\sigma_M \times \sigma_P \times \sigma_S^b \to \sigma_M$  and write-word :  $\sigma_M \times \sigma_P \times \sigma_S^w \to \sigma_M$  respectively, where b and w are the bit widths of a byte and a word. Reading a byte or a word from memory is represented by read-byte :  $\sigma_M \times \sigma_P \to \sigma_S^b$  and read-word :  $\sigma_M \times \sigma_P \to \sigma_S^w$ . Without loss of generality, we discuss word-sized memory operations only in the rest of this chapter. The semantics of word-sized memory operations are similar to  $\mathcal{T}_{\mathcal{A}}$  ROW axioms, as shown in Figure 4.4.

$$\begin{aligned} \forall b_1, b_2 . b_1 \neq_s b_2 \Rightarrow ptr(b_1, o_1) \neq_p ptr(b_2, o_2) \\ \forall b_1, b_2, o_1, o_2 . b_1 =_s b_2 \land o_1 =_s o_2 \iff ptr(b_1, o_1) =_p ptr(b_2, o_2) \\ \forall b_1, b_2, o_1, o_2 . b_1 =_s b_2 \land o_1 <_s o_2 \iff ptr(b_1, o_1) <_p ptr(b_2, o_2) \\ \forall b_1, b_2, o_1, o_2 . b_1 =_s b_2 \land o_1 \leq_s o_2 \iff ptr(b_1, o_1) \leq_p ptr(b_2, o_2) \end{aligned}$$

Figure 4.2: Axioms for  $\mathcal{T}_{\mathcal{M}}$  pointer comparison.

$\begin{aligned} \forall b, o_1, o_2 . \ ptr(b, o_1) +_p o_2 &= ptr(b, o_1 +_s o_2) \\ \forall b_1, b_2 . \ b_1 =_s b_2 \Rightarrow ptr(b_1, o_1) -_p \ ptr(b_2, o_2) &= o_1 -_s o_2 \end{aligned}$

Ranged memory operations are represented by memset-words :  $\sigma_M \times \sigma_P \times \sigma_S^w \times \sigma_S^w \to \sigma_M$  and memory-words :  $\sigma_M \times \sigma_P \times \sigma_M \times \sigma_P \times \sigma_S^w \to \sigma_M$ . The semantics of word-sized ranged memory operations are similar to the semantics of set and copy in  $\mathcal{T}_{ASC}$ , as shown in Figure 4.5.

With semantics of word-sized memory operations defined in Figure 4.4 and Figure 4.5, we define rules for eagerly rewriting word-sized *reads* over  $t_{\mathcal{M}}$  into formulas with only *ite*-terms and terminal *mem-identifier* symbols. The rewrite rules are shown in Figure 4.6 and Figure 4.7 for *read* over word-sized **stores** and word-sized **memset**, **memcpy** respectively.

$\mathcal{T}_{\mathcal{M}}$  defines sym VCGen semantics for SEAM memory representation. We expand sym memory operations translation semantics (previous shown in Figure 2.12) with SEAM shown in Figure 4.8. Note that VC in SEABMC is non-extensional, so final VC from SEAM would not contain any write-word, memset-words and memcpy-words after eager rewriting.

In the rewrite rules of  $\mathcal{T}_{\mathcal{M}}$  memory operations, notice that most of the simplifications depend on resolution of pointer term (dis)-equalities. In the next chapter, we introduce an efficient technique for pointer comparison based on Abstract Interpretation.

$\forall i, j . i =_p j \Rightarrow read-word(a, i) = read-word(a, j)$  $\forall i, j . i =_p j \Rightarrow read-word(write-word(a, j, v), i) = v$  $\forall i, j . i \neq_p j \Rightarrow read-word(write-word(a, j, v), i) = read-word(a, i)$

Figure 4.4:  $\mathcal{T}_{\mathcal{M}}$  word-sized *read*-over-*write* axioms.

$$\begin{split} \forall p, i, s \ . \ p \leq_p i <_p p +_p s \Rightarrow read-word(memset-words(a, p, v, s), i) = v \\ \forall p, i, s \ . \ \neg(p \leq_p i <_p p +_p s) \Rightarrow read-word(memset-words(a, p, v, s), i) = read-word(a, i) \\ \forall p, i, s \ . \ p \leq_p i <_p p +_p s \Rightarrow read-word(memcpy-words(a, p, b, q, s), i) = read-word(b, q +_p (i -_p p)) \\ \forall p, i, s \ . \ \neg(p \leq_p i <_p p +_p s) \Rightarrow read-word(memcpy-words(a, p, b, q, s), i) = read-word(a, i) \end{split}$$

$read-word(write-word(a, i, v), j) \rightsquigarrow ite(i =_p j, v, read-word(a, j))$  ROW

$\frac{\vdash i =_{p} j}{read-word(write-word(a, i, v), j) \rightsquigarrow v} \text{ ROW-HIT}$   $\frac{\vdash i \neq_{p} j}{read-word(write-word(a, i, v), j) \rightsquigarrow read-word(a, j)} \text{ ROW-SKIP}$

Figure 4.6: read-over-write rewrite rules for word-sized memory stores.

Figure 4.7: *read*-over-*write* rewrite rules for word-sized memset and memcpy.

|                                              | SeaM                                                     |

|----------------------------------------------|----------------------------------------------------------|

| $\overline{write(m_0,r_1,p_2)}$              | write-word $m_0 \; r_1 \; p_2$                           |

| $memset(m_0, \ p_1, \ r_1, \ r_2)$           | $	extsf{memset-words}(m_0, \ p_1, \ r_1, \ r_2)$         |

| $memcpy(m_0, p_1, m_1, p_2, r_1)$            | $\texttt{memcpy-words}(m_0, \ p_1, \ m_1, \ p_2, \ r_1)$ |

| $read(write(m_0, r_1, p_2), p_1)$            | $ite(p_1 =_p p_2, r_1, \texttt{read-word}(m_0, p_1))$    |

| $read(memset(m_0, p_1, r_1, r_2), p_2)$      | $ite(p_1 \leq_p p_2 <_p (p_1 +_p r_1), r_2,$             |

|                                              | $\texttt{read-word}(m_0,\ p_2))$                         |

| $read(memcpy(m_0, p_1, m_1, p_2, r_1), p_3)$ | $ite(p_1 \leq_p p_3 <_p (p_1 +_p r_1)),$                 |

|                                              | $read-word(m_1, p_2 +_p (p_3p p_1)),$                    |

|                                              | $\texttt{read-word}(m_0,\ p_3))$                         |

Figure 4.8: sym translation of memory operations in SEAM.

# Chapter 5

## Address Range Map

In C programs translated to SEA-IR, it is common to represent control flow with PHI statements, which is further translated to *ite*-terms during VCGen to represent different possible values based on condition. As a result, it is possible for pointer terms  $t_{\mathcal{P}}$  in  $\mathcal{T}_{\mathcal{M}}$  expressions to contain *ite*-expressions, as described in Figure 4.1. Precise comparison between  $t_{\mathcal{P}}$  terms containing nested *ites* can be exponential when done with **ITE-PULL** and **ITE-PUSH** rewrites. In this chapter, we introduce Address Range Map (ARM), an Abstract Interpretation [11] based technique that results in more efficient pointer comparisons by over-approximating  $t_{\mathcal{P}}$  pointer terms.