#### Luís Fernando Arcaro

# INCREASING THE RELIABILITY AND APPLICABILITY OF MEASUREMENT-BASED PROBABILISTIC TIMING ANALYSIS

Tese submetida ao Programa de Pós-Graduação em Engenharia de Automação e Sistemas para a obtenção do Grau de Doutor em Engenharia de Automação e Sistemas.

Orientador: Prof. Dr. Rômulo Silva de Oliveira

Florianópolis

2019

# Ficha de identificação da obra elaborada pelo autor, através do Programa de Geração Automática da Biblioteca Universitária da UFSC.

Arcaro, Luís Fernando Increasing the Reliability and Applicability of Measurement-Based Probabilistic Timing Analysis / Luís Fernando Arcaro; orientador, Rômulo Silva de Oliveira, 2019. 245 p.

Tese (doutorado) - Universidade Federal de Santa Catarina, Centro Tecnológico, Programa de Pós Graduação em Engenharia de Automação e Sistemas, Florianópolis, 2019.

Inclui referências.

1. Engenharia de Automação e Sistemas. 2. Sistemas de Tempo Real. 3. Análise Temporal Probabilística Baseada em Medições. 4. Confiabilidade. 5. Aleatorização Temporal. I. Oliveira, Rômulo Silva de. II. Universidade Federal de Santa Catarina. Programa de Pós-Graduação em Engenharia de Automação e Sistemas. III. Título.

#### Luís Fernando Arcaro

### INCREASING THE RELIABILITY AND APPLICABILITY OF MEASUREMENT-BASED PROBABILISTIC TIMING ANALYSIS

Esta Tese foi julgada aprovada para a obtenção do Título de "Doutor em Engenharia de Automação e Sistemas", e aprovada em sua forma final pelo Programa de Pós-Graduação em Engenharia de Automação e Sistemas.

Florianópolis, 8 de Abril 2019.

Prof. Dr. Rômulo Silva de Oliveira

Orientador

Prof. Dr. Werner Kraus Junior

Coordenador do Programa de Pós-Graduação em

Engenharia de Automação e Sistemas

Banca Examinadora:

Prof. Dr. Rômulo Silva de Oliveira

Presidente

Prof. Dr. Sandro Rigo

Universidade Estadual de Campinas (UNICAMP)

Prof. Dr. Luiz Cláudio Villar dos Santos

Universidade Federal de Santa Catarina (UFSC)

Prof. Dr. Eduardo Augusto Bezerra Universidade Federal de Santa Catarina (UFSC)

À minha família. Ao Bibinho.

#### AGRADECIMENTOS

Agradeco inicialmente a meus grandes pais, Lourenco e Izabel, pela vida, pela motivação e pela segurança familiar que permitiram minha dedicação à formação acadêmica. À minha irmã, Katia, pelos cuidados, pelos valiosos ensinamentos, e pela companhia durante toda nossa vida. À minha parceira de toda hora, Vanessa, pela companhia, paciência e compreensão no nosso movimentado dia-a-dia. Ao meu cunhado, Guilherme, por ser membro ativo e presente na nossa família e pela ótima companhia regada a cerveja e café. Aos nossos bichinhos, Mini (Bibi), Blu e Horácio, pela alegria que representam em nossas vidas. Ao meu orientador e exemplar profissional, Rômulo, agradeço grandemente pelo trabalho realizado e pela paciência em me orientar ao longo dos últimos seis anos. À minha irmã de doutorado, Karila, por compartilhar todas as dificuldades e glórias da pós-graduação – foi e continua sendo ótimo trabalhar com você! Á minha também irmã de Belém. Rejane, pela grande amizade e pelos valiosos ensinamentos que levarei certamente para a vida toda. Aos amigos Jonatas, Carol e Wilson, pela amizade que permanece forte apesar da distância e dos compromissos. Aos amigos Alexandre, Flávio, Leonardo Assis, Leonardo Martins, Sidney e Thayse Christine, pela companhia diária dentro e fora da universidade e pelas discussões aleatórias regadas a chimarrão e café. Ao hermano colombiano Carlos González Aguilera, pela grande amizade e pelo boné do Cusco Voador. À amiga gaúcha Stephanie, pelos chimarrões e conversas sobre esse e outros gauchismos. Aos amigos e ciclistas incansáveis Carlise e Ruan, pelas trips insanas envolvendo grandes distâncias, inclinações, e cercas elétricas. Aos amigos Priscila, Guilherme e Gael, pelos fantásticos cafés com bolo e conversa. Aos demais amigos e colegas do PPGEAS, da Sala dos Doutorandos e além, por serem como uma grande família que adora café, biscoito, cerveja e churrasco. Aos professores do PPGEAS, pelo conhecimento e experiência compartilhados incansavelmente ao longo dos cursos. E, finalmente mas com igual importância, a todas as pessoas que não citei explicitamente, mas que participaram de alguma forma desses seis anos de aprendizado acadêmico, profissional e principalmente existencial. Obrigado!

#### RESUMO

Conforme a complexidade das arquiteturas computacionais aumenta para melhorar desempenho ou reduzir custos, o uso de processadores modernos em Sistemas de Tempo Real (STRs) é prejudicado cada vez mais pelo surgimento de efeitos temporais que dificultam a obtenção de limites confiáveis e precisos para os Worst-Case Execution Times (WCETs) de tarefas. A Análise Temporal Probabilística Baseada em Medicões (ATPBM) visa determinar limites probabilísticos de WCET (i.e. pWCETs) aplicando a Teoria de Valores Extremos (TVE) sobre medições de tempos de execução, e é portanto promissora no tratamento da complexidade de hardware no projeto de STRs. Processadores temporalmente aleatorizados foram recentemente propostos para tornar o comportamento temporal de sistemas computacionais mais facilmente analisável através de ferramental probabilístico, e são projetados substituindo informações internas determinísticas ou especulativas por números (pseudo-) aleatórios. A pesquisa cujos resultados são apresentados nesta tese produziu contribuições em duas frentes distintas. Em primeiro lugar, foram propostos e aplicados métodos para avaliar a confiabilidade dos pWCETs produzidos pela ATPBM, baseados na coleta de grandes amostras de tempos de execução e na comparação (1) dos pWCETs com os maiores tempos de execução observados, e (2) das densidades de excedência dos pWCETs com seus valores esperados. Essas avaliações indicaram que modelos probabilísticos da TVE projetados para gerar margens mais precisas podem muitas vezes levar a subestimativas de pWCETs, e recomendou-se então que modelos sobrestimadores devem ser utilizados para obter-se pWCETs mais confiáveis. Em segundo lugar, avaliou-se a hipótese de que técnicas de escalonamento aleatorizado podem beneficiar a análise temporal de tarefas executadas em pipelines multithread através da ATPBM, por levarem os tempos de execução produzidos a atenderem às premissas básicas de aplicabilidade da técnica. Para tal, foram considerados tanto (A) um escalonador puramente aleatório, quanto (B) um escalonador aleatorizado capaz de limitar os efeitos temporais da interferência entre threads, sem comprometer sua analisabilidade pela ATPBM, através de um mecanismo de regulação de elegibilidade baseado em créditos.

Palavras-chave: Sistemas de Tempo Real. Análise Temporal Probabilística Baseada em Medições. Confiabilidade. Aleatorização Temporal.

#### RESUMO EXPANDIDO

### Introdução

Sistemas de Tempo Real (STRs) são sistemas computacionais sujeitos tanto a requisitos de natureza lógica quanto de natureza temporal, ou seja, seus resultados precisam não apenas estar logicamente corretos mas devem também ser gerados respeitando prazos (deadlines) estritos. Tais sistemas são classificados de acordo com a criticalidade de seus requisitos temporais. A ausência de corretude temporal em STRs críticos pode resultar em consequências catastróficas, tanto do ponto de vista econômico quanto no sentido de poder causar a perda de vidas. Garantias precisam ser fornecidas, portanto, de que seus deadlines não serão perdidos – mesmo no pior caso. O Worst-Case Execution Time (WCET) de tarefas de software representa o tempo mais longo que a plataforma-alvo de hardware pode possivelmente levar para executá-las. O WCET de uma tarefa varia em função de múltiplos fatores que precisam ser levados em conta para a determinação de seu valor exato, o que geralmente prova-se extremamente complexo, ou para estabelecer limites superiores confiáveis para seu valor. Especialmente em relação a STRs críticos, estimativas de WCET precisam ser seguras, i.e. o valor real nunca deve ser subestimado, e razoavelmente apertadas, i.e. sua sobrestimação deve ser minimizada a fim de reduzir o desperdício de recursos. A determinação de limites para WCETs é geralmente realizada através de métodos estáticos, que empregam análises conjuntas detalhadas do software e do hardware, ou baseados em medições, que analisam amostras do tempo efetivamente consumido para executar a tarefa analisada na plataforma-alvo. Este trabalho desenvolve-se no contexto da Análise Temporal Probabilística Baseada em Medições (ATPBM), que visa determinar limites probabilísticos para os WCETs de tarefas que compõem STRs. Esses limites, conhecidos como pWCETs, são compostos de um valor-limite e de uma probabilidade associada à excedência desse valor em qualquer execução da tarefa. A aplicação da ATPBM baseia-se na análise estatística dos maiores tempos de execução produzidos pelas tarefas, medidos quando de sua execução na plataforma de hardware real sob condições adequadas. A principal ferramenta atualmente utilizada pela ATPBM é a Teoria de Valores Extremos (TVE), um ramo da estatística destinado a estimar a probabilidade de eventos extremos raros. Através do ajuste de modelos estatísticos aos maiores valores observados de uma variável associada a

um determinado fenômeno, a TVE é capaz de determinar margens de seguranca com probabilidades arbitrariamente baixas de excedência. No contexto da ATPBM, a TVE é promissora para a determinação de estimativas de pWCET associadas a probabilidades de excedência comparáveis, ou até mesmo mais baixas, que aquelas associadas a outros tipos de falha que precisam ser levadas em consideração no projeto de STRs críticos (e.g. falhas estruturais). A aleatorização temporal em hardware foi proposta recentemente como um meio para projetar processadores cujo comportamento temporal é influenciado por leis probabilísticas, podendo assim facilitar a análise temporal de STRs através de métodos baseados em ferramentas estatísticas como a ATPBM. O princípio básico da aleatorização temporal é a substituição de informações tipicamente especulativas utilizadas para tomar ações que influenciam o tempo de execução de tarefas por números (pseudo-)aleatórios. Consequentemente, a aleatorização temporal também desacopla parcialmente o comportamento temporal do hardware do histórico de execução, mitigando o surgimento sistemático de padrões patológicos associados a tempos de execução extremos. Apesar de não fornecer garantias quanto à analisabilidade dos tempos de execução produzidos, processadores temporalmente aleatorizados frequentemente mostram-se adequados para análise através da ATPBM.

### Objetivos

Esta tese possui dois objetivos: (A) investigar métodos empíricos para evidenciar ou contra-provar a confiabilidade de estimativas de pWCET produzidas utilizando a TVE no contexto da ATPBM, e (B) investigar abordagens para o projeto de pipelines multithread temporalmente aleatorizados adequados para a aplicação da ATPBM. Mais especificamente, a tese a ser demonstrada em (A) é que a confiabilidade das estimativas de pWCET produzidas utilizando a ATPBM pode ser avaliada utilizando grandes amostras de validação e comparando seu comportamento com expectativas em relação à delimitação (bounding) dos maiores valores e das densidades de cauda observadas, e em (B) é que aleatorização temporal pode ser utilizada para permitir a utilização de pipelines multithread em STRs por produzir tempos de execução adequados à aplicação da ATPBM.

### Contribuições

Duas principais contribuições são fornecidas neste trabalho. Em primeiro lugar, foi realizada uma avaliação empírica da confiabilidade de estimativas de pWCET produzidas com base na ATPBM através

da TVE utilizando grandes amostras de validação (por exemplo, de tamanho 10<sup>8</sup>), considerando diferentes abordagens para aplicação da TVE e realizando um grande conjunto de replicações utilizando diferentes condições e métodos. A confiabilidade das estimativas de pWCET foram avaliadas com base na efetiva delimitação (1) dos maiores tempos de execução observados e (2) das densidades de excedência das caudas das distribuições empíricas de tempos de execução observadas em amostras de validação. Em segundo lugar, foi avaliada a hipótese de que técnicas de escalonamento aleatorizado de threads podem beneficiar a aplicação da ATPBM em múltiplas tarefas executadas simultaneamente em pipelines multithread (neste trabalho foi considerado apenas o caso dual-thread). Para isso, foram avaliados tanto (1) um escalonador puramente aleatório, que leva ao atendimento dos requisitos da ATPBM mas que não balanceia atrasos devido a interferências, e (2) um escalonador capaz de limitar os efeitos temporais de pior caso da interferência entre threads, utilizando para isso um mecanismo de regulação de elegibilidade baseado em créditos.

### Considerações Finais

Esta tese fornece contribuições relevantes no contexto da ATPBM, tanto por avaliar e aumentar a confiabilidade de seus resultados quanto em relação à introdução de aleatorização no nível de hardware para facilitar sua aplicação. Em particular, os métodos de avaliação de confiabilidade propostos mostraram que a ATPBM precisa que seus modelos probabilísticos sejam utilizados de forma que as estimativas de pWCET potencialmente superestimem (e não apenas estimem) os máximos tempos de execução possivelmente observáveis. Além disso, o trabalho apresentado explorou caminhos originais de pesquisa envolvendo multithreading, uma técnica que é frequentemente evitada no projeto de STRs por potencialmente (1) levar a grande pessimismo na estimação de WCETs através de métodos estáticos, ou (2) requerer que garantias temporais sejam fornecidas apenas para uma thread, cuja execução é geralmente priorizada. Pode-se portanto considerar que o trabalho apresentado fornece contribuições relevantes que aumentam a aplicabilidade confiável da ATPBM, também promovendo portanto sua usabilidade na análise temporal de STRs críticos.

Palavras-chave: Sistemas de Tempo Real. Análise Temporal Probabilística Baseada em Medições. Confiabilidade. Aleatorização Temporal.

#### ABSTRACT

As the complexity of computer architectures grows in order to improve performance and/or to reduce costs, the use of modern processors in the design of Real-Time Systems (RTSs) is increasingly hampered by the emergence of timing effects that challenge determining reliable and tight bounds for tasks' Worst-Case Execution Times (WCETs). The Measurement-Based Probabilistic Timing Analysis (MBPTA) technique aims determining probabilistic WCET bounds (i.e. pWCETs) by applying Extreme Value Theory (EVT) on tasks' execution time measurements, and is hence promising in handling hardware complexity issues within RTSs' design. Hardware-level time-randomized processors were recently proposed as a means to cause computing systems' timing behaviour to become more easily analysable through probabilistic tools, and are designed replacing deterministic or speculative internal information with (pseudo-)random numbers. The scientific research whose outcomes are presented in this thesis produced contributions on two distinct fronts. In first place, we proposed and applied methods for evaluating the reliability of pWCET estimates produced using MBPTA, based on collecting large execution time samples and then comparing (1) the pWCETs against the largest observed execution times, and (2) pWCETs' exceedance densities against their expected values. These evaluations led us to conclude that EVT probabilistic models intended to yield more precise bounds may often lead to pWCET underestimations, and we hence recommended that upper-bounding models should instead be used for deriving pWCETs with increased reliability. In second place, we evaluated the hypothesis that randomized scheduling techniques can benefit the timing analysis of tasks executed on multithread pipelines through MBPTA, by causing the yielded execution times to meet the technique's basic application requirements. For that, we considered both (A) a scheduler that employs a purely random policy, and (B) a randomized scheduler capable of limiting the timing effects of inter-thread interference, without compromising analysability, by using a credit-based eligibility regulation mechanism.

**Keywords:** Real-Time Systems. Measurement-Based Probabilistic Timing Analysis. Reliability. Time-Randomization.

# LIST OF FIGURES

| Figure 1  | Block Maxima (BM) approach 42                                |

|-----------|--------------------------------------------------------------|

| Figure 2  | Peaks Over Threshold (POT) approach                          |

| Figure 3  | Hypothesis tests' decision approaches                        |

| Figure 4  | KS test p-value distribution comparison                      |

| Figure 5  | Quantile plot comparison                                     |

| Figure 6  | Platform illustration                                        |

| Figure 7  | Raw data histogram                                           |

| Figure 8  | I.i.d. tests' p-values                                       |

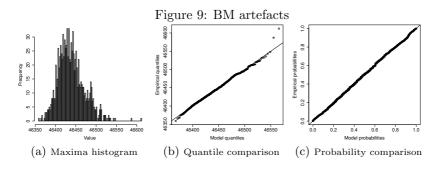

| Figure 9  | BM artefacts                                                 |

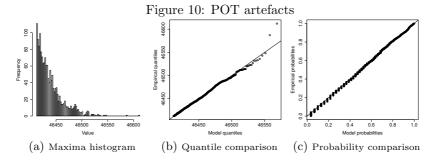

| Figure 10 | POT artefacts                                                |

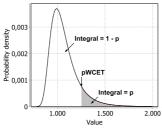

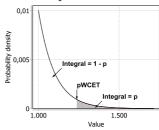

| Figure 11 | pWCET derivation process                                     |

| Figure 12 | Synthetic samples' distributions                             |

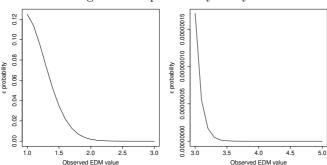

| Figure 13 | $\varepsilon$ probability analysis                           |

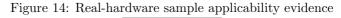

| Figure 14 | Real-hardware sample applicability evidence 93               |

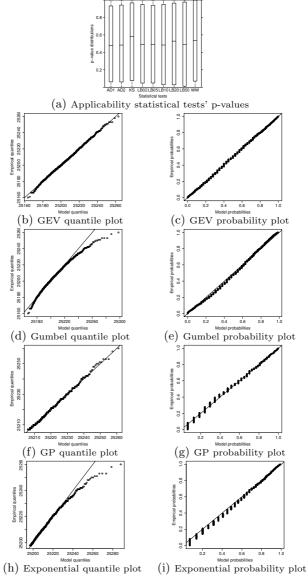

| Figure 15 | Real-hardware pWCET HWM reliability 95                       |

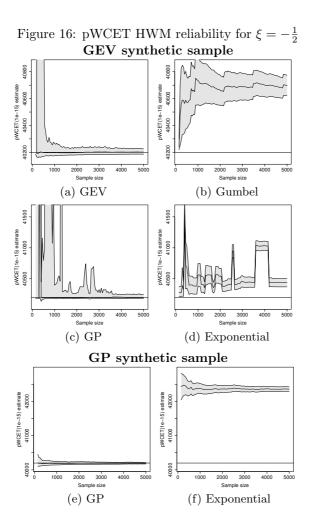

| Figure 16 | pWCET HWM reliability for $\xi = -\frac{1}{2}$               |

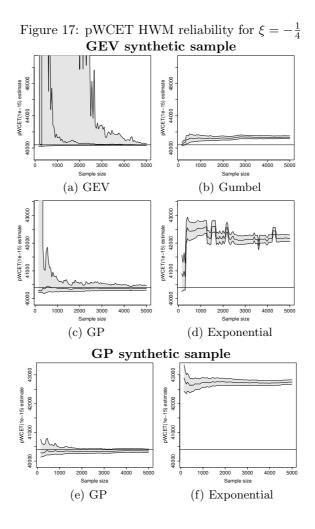

| Figure 17 | pWCET HWM reliability for $\xi = -\frac{1}{4}$               |

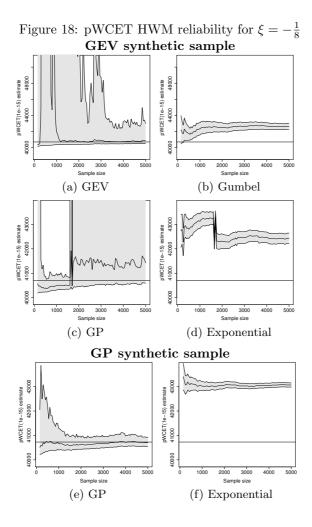

| Figure 18 | pWCET HWM reliability for $\xi = -\frac{1}{8}$               |

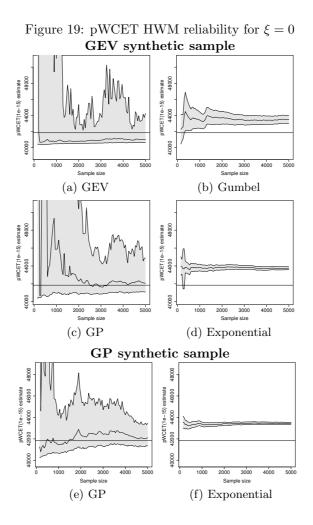

| Figure 19 | pWCET HWM reliability for $\xi = 0 \dots 99$                 |

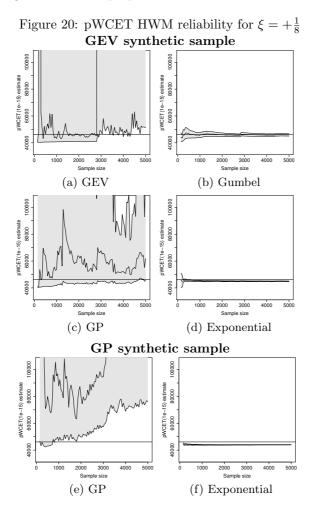

| Figure 20 | pWCET HWM reliability for $\xi = +\frac{1}{8} \dots 100$     |

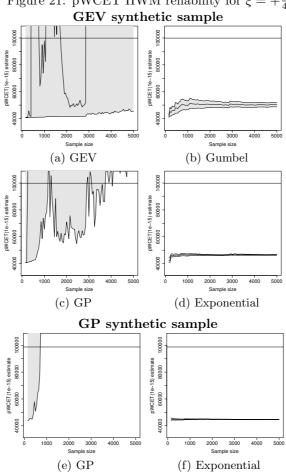

| Figure 21 | pWCET HWM reliability for $\xi = +\frac{1}{4} \dots 101$     |

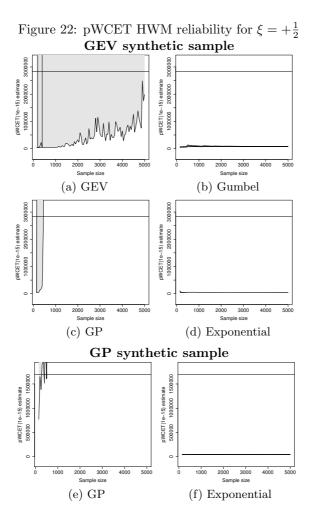

| Figure 22 | pWCET HWM reliability for $\xi = +\frac{1}{2} \dots 102$     |

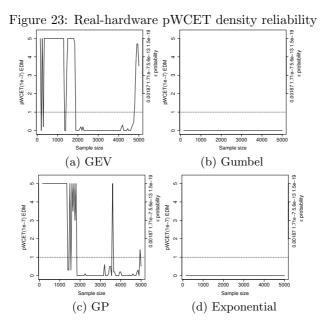

| Figure 23 | Real-hardware pWCET density reliability104                   |

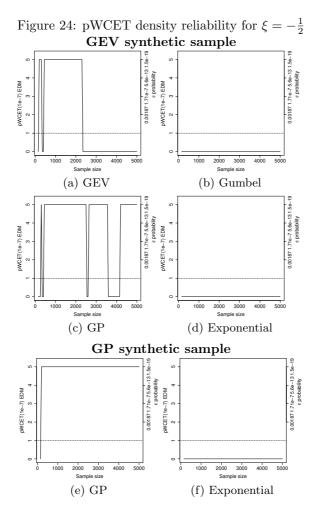

| Figure 24 | pWCET density reliability for $\xi = -\frac{1}{2} \dots 106$ |

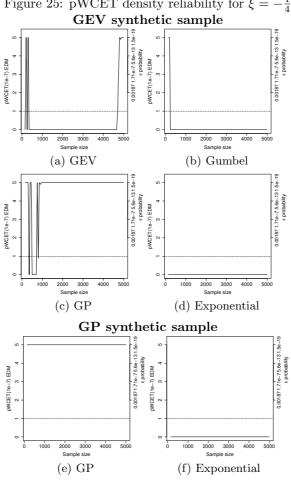

| Figure 25 | pWCET density reliability for $\xi = -\frac{1}{4} \dots 107$ |

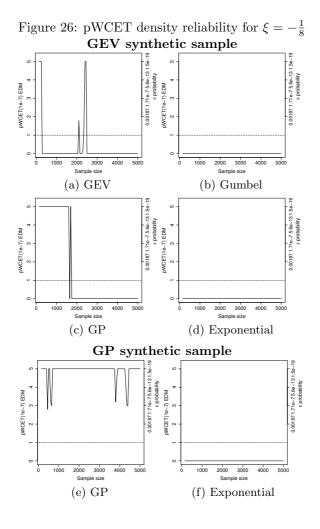

| Figure 26 | pWCET density reliability for $\xi = -\frac{1}{8} \dots 108$ |

| Figure 27 | pWCET density reliability for $\xi = 0 \dots 109$            |

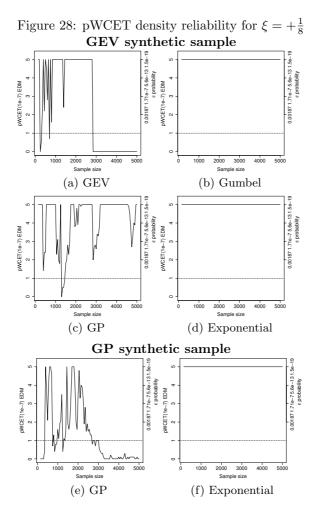

| Figure 28 | pWCET density reliability for $\xi = +\frac{1}{8} \dots 110$ |

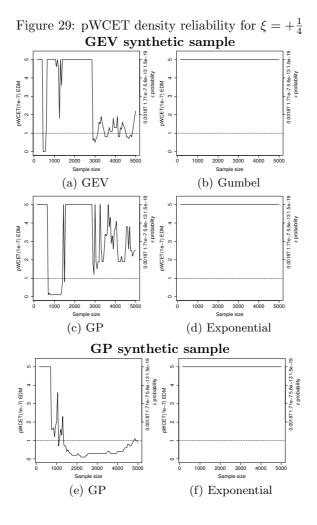

| Figure 29 | pWCET density reliability for $\xi = +\frac{1}{4}$           |

| Figure 30 | pWCET density reliability for $\xi = +\frac{1}{2} \dots 112$ |

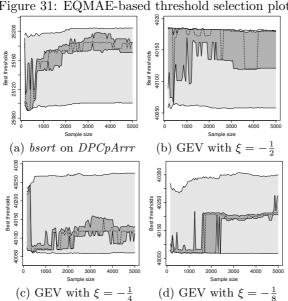

| Figure 31 | EQMAE-based threshold selection plots                        |

| Figure 32 | Simple pipeline design                                       |

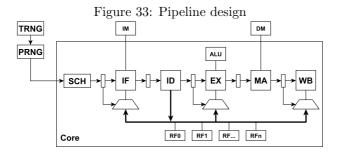

| Figure 33 | Pipeline design                                                     |

|-----------|---------------------------------------------------------------------|

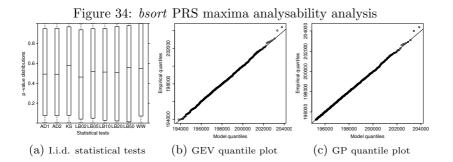

| Figure 34 | bsort PRS maxima analysability analysis                             |

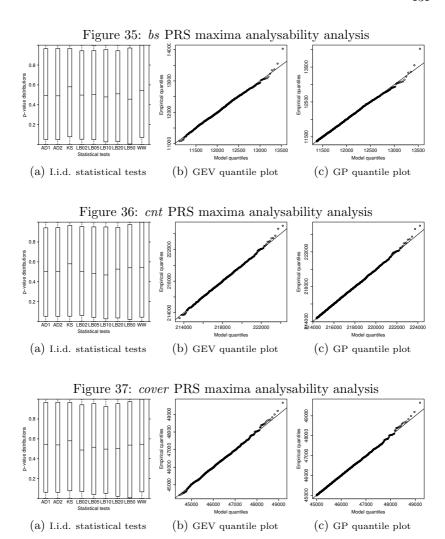

| Figure 35 | bs PRS maxima analysability analysis                                |

| Figure 36 | cnt PRS maxima analysability analysis                               |

| Figure 37 | cover PRS maxima analysability analysis                             |

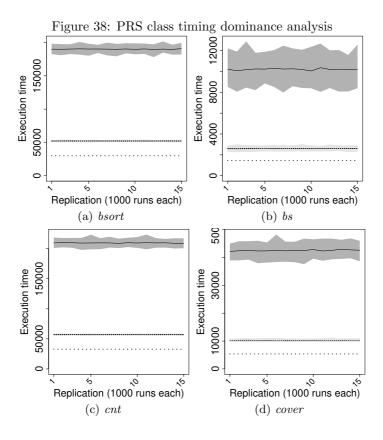

| Figure 38 | PRS class timing dominance analysis                                 |

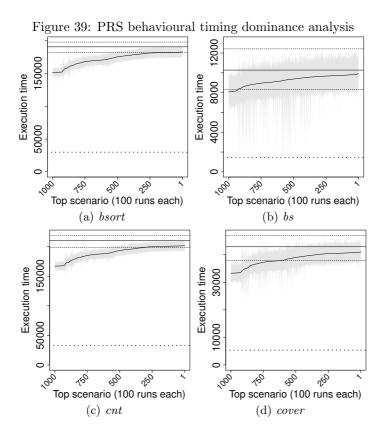

| Figure 39 | PRS behavioural timing dominance analysis 134                       |

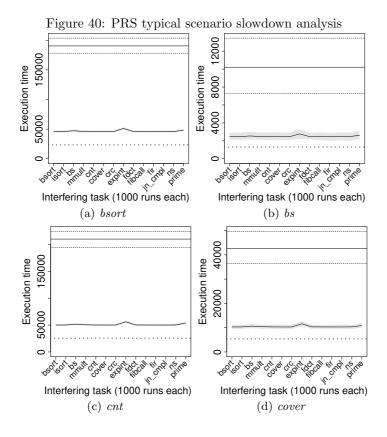

| Figure 40 | PRS typical scenario slowdown analysis136                           |

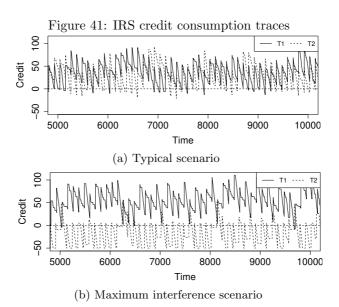

| Figure 41 | IRS credit consumption traces                                       |

| Figure 42 | bsort IRS maxima analysability analysis                             |

| Figure 43 | bs IRS maxima analysability analysis                                |

| Figure 44 | cnt IRS maxima analysability analysis142                            |

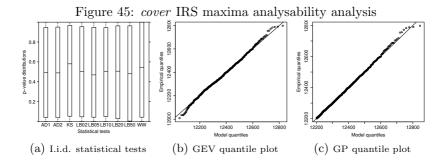

| Figure 45 | cover IRS maxima analysability analysis143                          |

| Figure 46 | IRS class timing dominance analysis                                 |

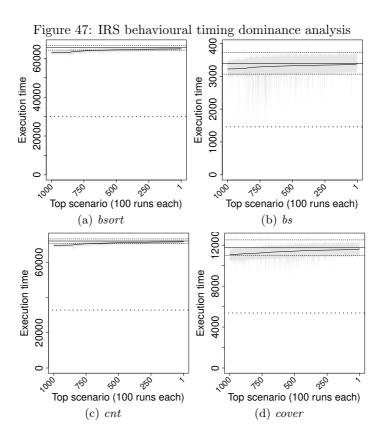

| Figure 47 | IRS behavioural timing dominance analysis 145                       |

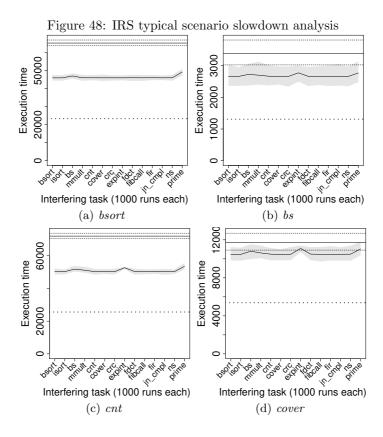

| Figure 48 | IRS typical scenario slowdown analysis 147                          |

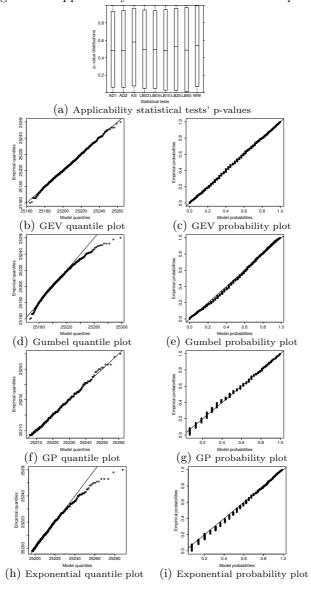

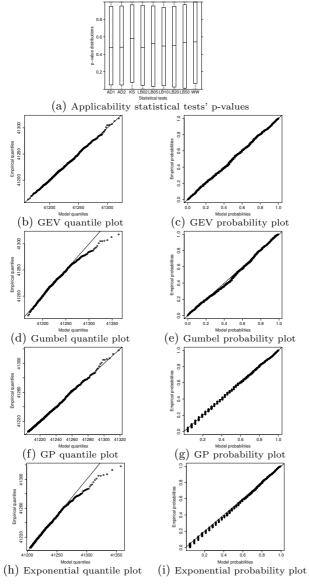

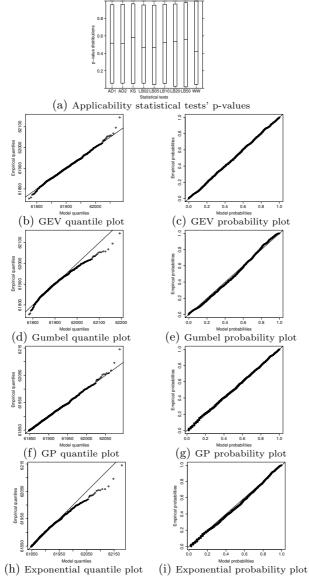

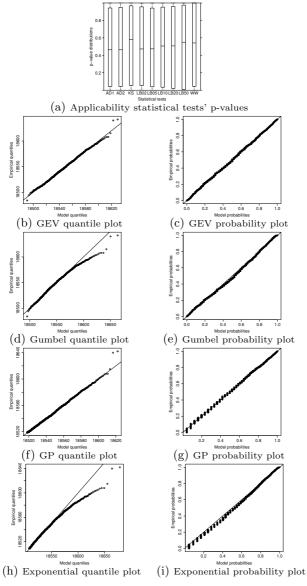

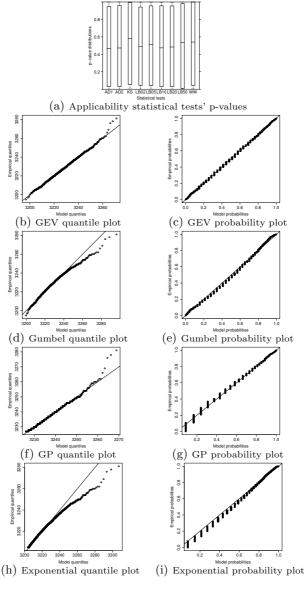

| Figure 49 | Applicability evidence for bsort on DPCpArrr 181                    |

| Figure 50 | Applicability evidence for bsort on DPArptdm 182                    |

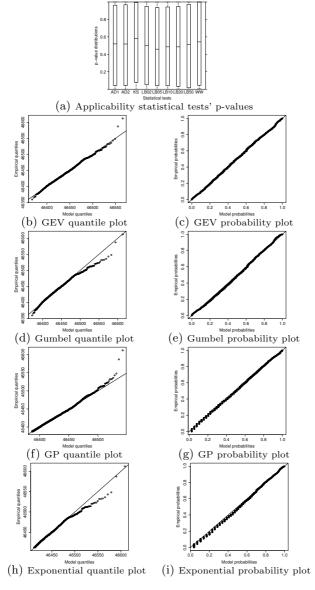

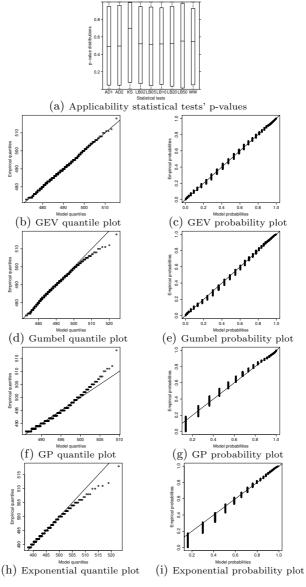

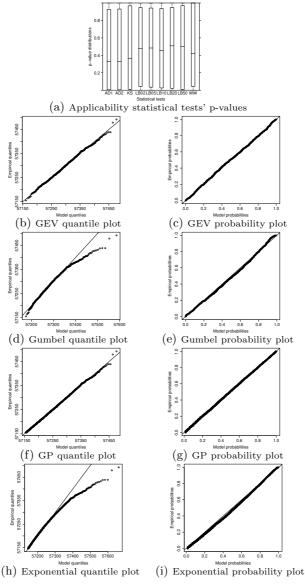

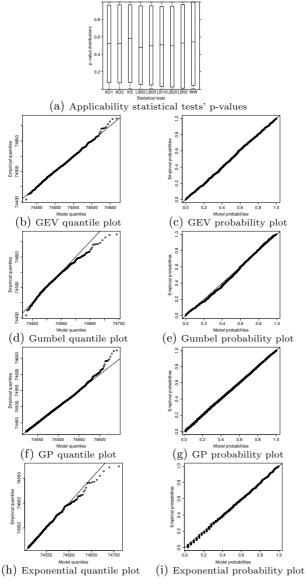

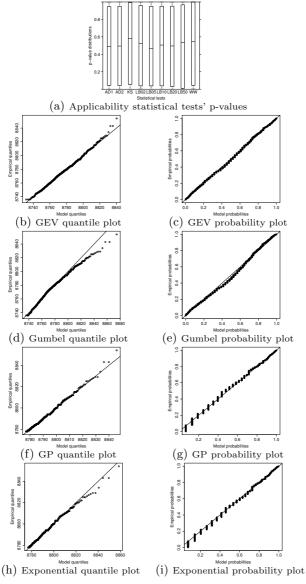

| Figure 51 | Applicability evidence for <i>insertsort</i> on <i>DPCpArrr</i> 183 |

| Figure 52 | Applicability evidence for <i>insertsort</i> on <i>DPArptdm</i> 184 |

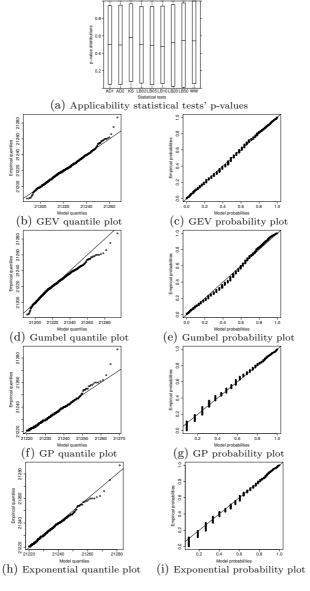

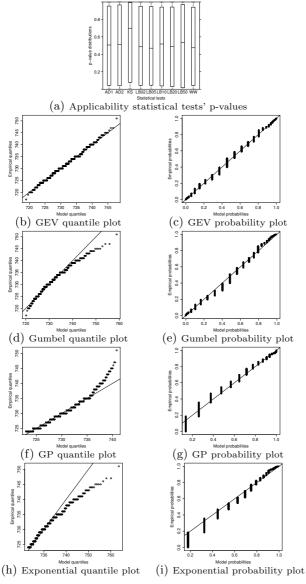

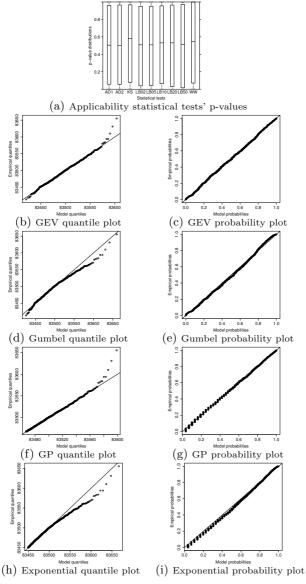

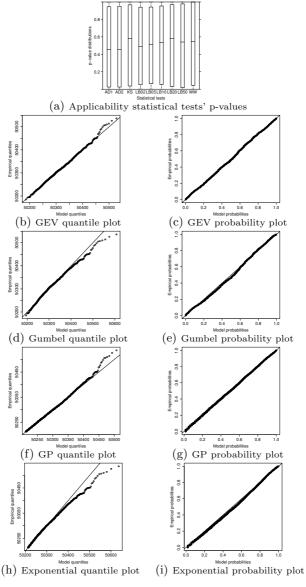

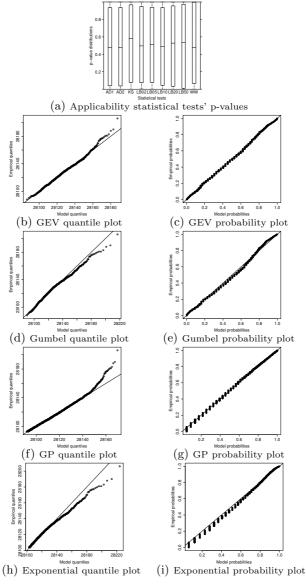

| Figure 53 | Applicability evidence for bs on DPCpArrr185                        |

| Figure 54 | Applicability evidence for bs on DPArptdm 186                       |

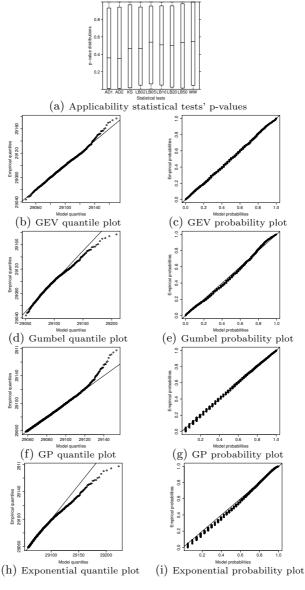

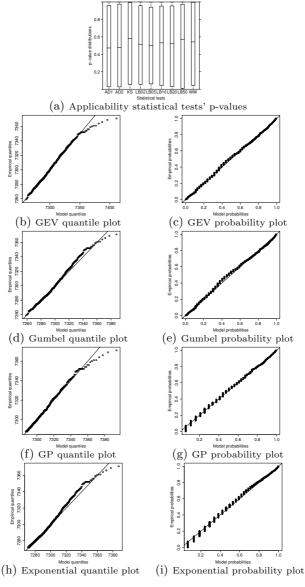

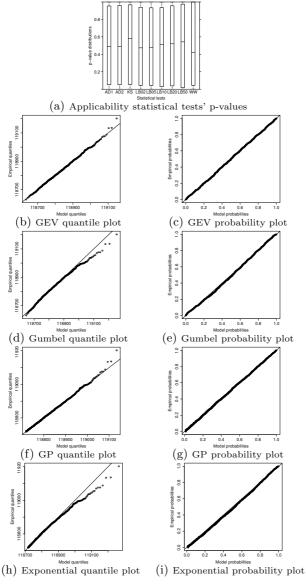

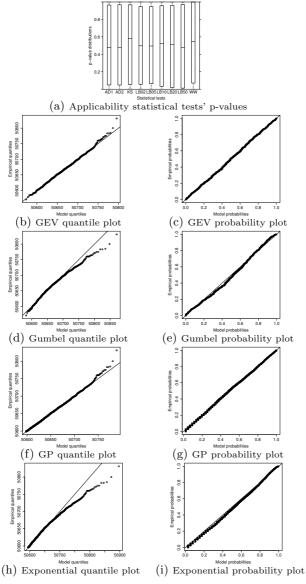

| Figure 55 | Applicability evidence for expirt on DPCpArrr 187                   |

| Figure 56 | Applicability evidence for expirt on DPArptdm 188                   |

| Figure 57 | Applicability evidence for fdct on DPCpArrr 189                     |

| Figure 58 | Applicability evidence for fdct on DPArptdm 190                     |

| Figure 59 | Applicability evidence for crc on DPCpArrr 191                      |

| Figure 60 | Applicability evidence for <i>crc</i> on <i>DPArptdm</i> 192        |

| Figure 61 | Applicability evidence for matmult on DPCpArrr193                   |

| Figure 62 | Applicability evidence for matmult on DPArptdm 194                  |

| Figure 63 | Applicability evidence for fir on DPCpArrr195                       |

| Figure 64 | Applicability evidence for fir on DPArptdm196                       |

| Figure 65 | Applicability evidence for fibrall on DPCpArrr 197                  |

| Figure 66 | Applicability evidence for $fibcall$ on $DPArptdm$ 198              |

|           |                                                                     |

| Figure 67  | Applicability evidence for <i>cnt</i> on <i>DPCpArrr</i> 199                   |

|------------|--------------------------------------------------------------------------------|

| Figure 68  | Applicability evidence for <i>cnt</i> on <i>DPArptdm</i> 200                   |

| Figure 69  | pWCET HWM reliability for bsort on DPCpArrr201                                 |

| Figure 70  | pWCET HWM reliability for bsort on DPArptdm 201                                |

| Figure 71  | pWCET HWM reliability for insertsort on DPCpArrr 202                           |

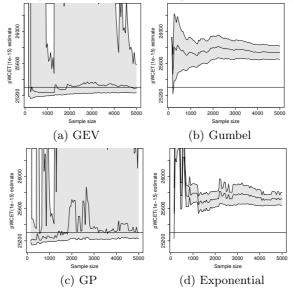

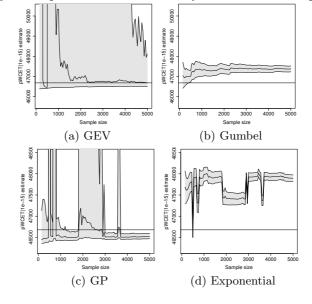

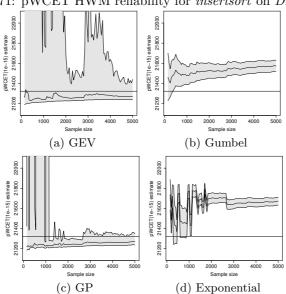

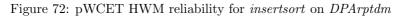

| Figure 72  | pWCET HWM reliability for insertsort on DPArptdm 202                           |

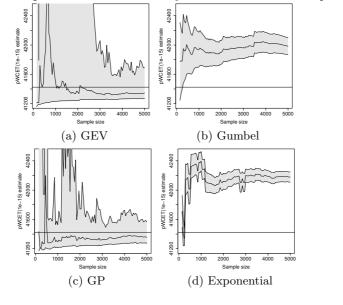

| Figure 73  | pWCET HWM reliability for bs on DPCpArrr203                                    |

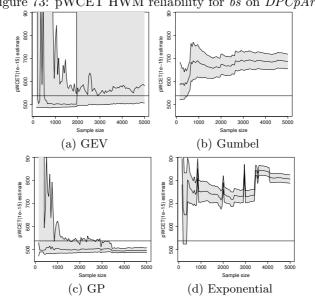

| Figure 74  | pWCET HWM reliability for $bs$ on $DPArptdm203$                                |

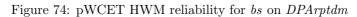

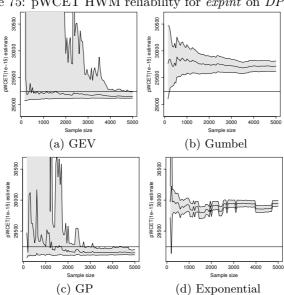

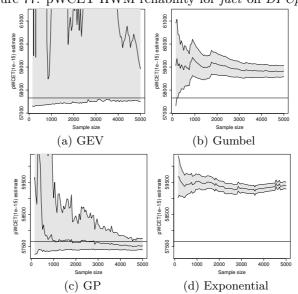

| Figure 75  | pWCET HWM reliability for expint on DPCpArrr204                                |

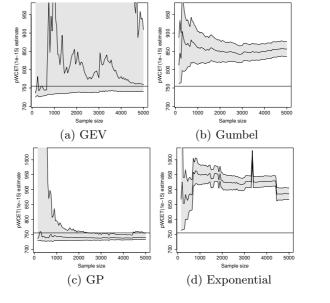

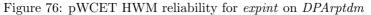

| Figure 76  | pWCET HWM reliability for expint on DPArptdm204                                |

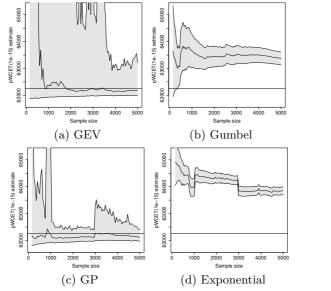

| Figure 77  | pWCET HWM reliability for fdct on DPCpArrr205                                  |

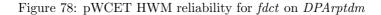

| Figure 78  | pWCET HWM reliability for fdct on DPArptdm 205                                 |

| Figure 79  | pWCET HWM reliability for crc on DPCpArrr206                                   |

| Figure 80  | pWCET HWM reliability for crc on DPArptdm206                                   |

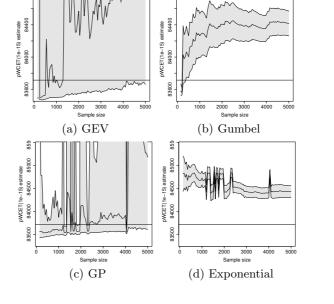

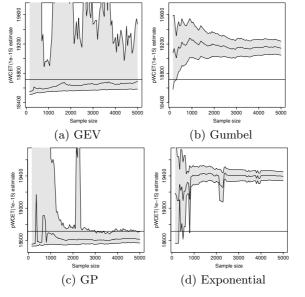

| Figure 81  | pWCET HWM reliability for $matmult$ on $DPCpArrr$ . 207                        |

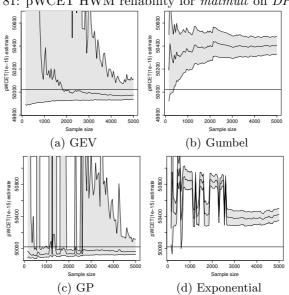

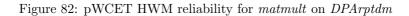

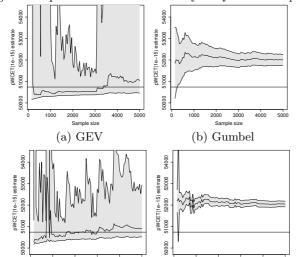

| Figure 82  | pWCET HWM reliability for $\mathit{matmult}$ on $\mathit{DPArptdm}$ . 207      |

| Figure 83  | pWCET HWM reliability for fir on DPCpArrr 208                                  |

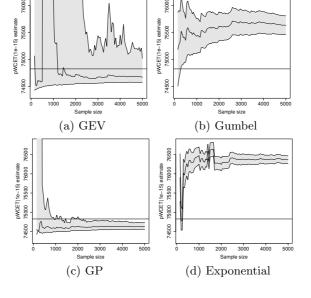

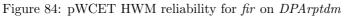

| Figure 84  | pWCET HWM reliability for $fir$ on $DPArptdm$ 208                              |

| Figure 85  | pWCET HWM reliability for fibrall on $DPCpArrr209$                             |

| Figure 86  | pWCET HWM reliability for $\mathit{fibcall}$ on $\mathit{DPArptdm} \ldots 209$ |

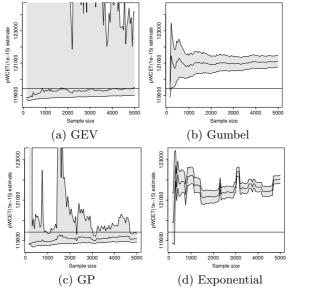

| Figure 87  | pWCET HWM reliability for <i>cnt</i> on <i>DPCpArrr</i> 210                    |

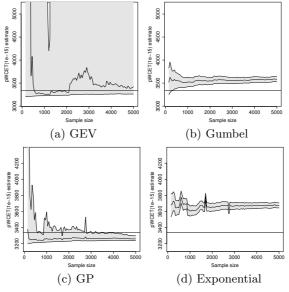

| Figure 88  | pWCET HWM reliability for cnt on DPArptdm 210                                  |

| Figure 89  | pWCET density reliability for $bsort$ on $DPCpArrr211$                         |

| Figure 90  | pWCET density reliability for $bsort$ on $DPArptdm \dots 211$                  |

| Figure 91  | pWCET density reliability for $insertsort$ on $DPCpArrr212$                    |

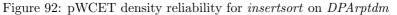

| Figure 92  | pWCET density reliability for $insertsort$ on $DPArptdm212$                    |

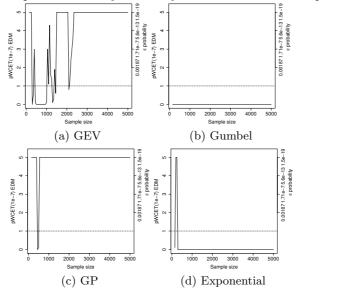

| Figure 93  | pWCET density reliability for $bs$ on $DPCpArrr213$                            |

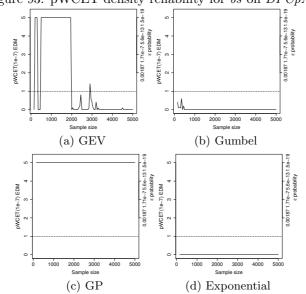

| Figure 94  | pWCET density reliability for $bs$ on $DPArptdm213$                            |

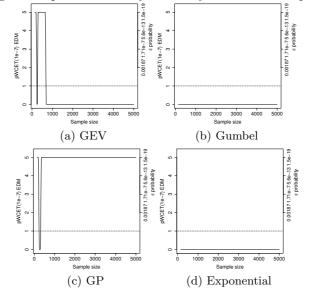

| Figure 95  | pWCET density reliability for $expint$ on $DPCpArrr214$                        |

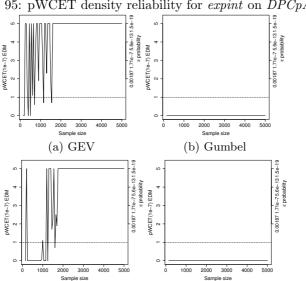

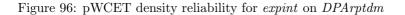

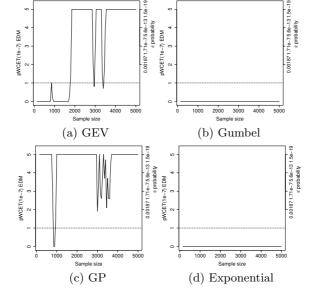

| Figure 96  | pWCET density reliability for $expint$ on $DPArptdm214$                        |

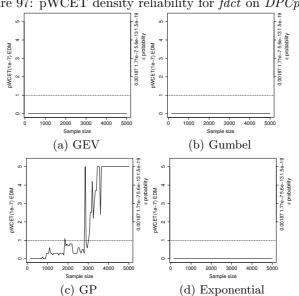

| Figure 97  | pWCET density reliability for fdct on DPCpArrr215                              |

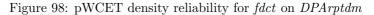

| Figure 98  | pWCET density reliability for $fdct$ on $DPArptdm \dots 215$                   |

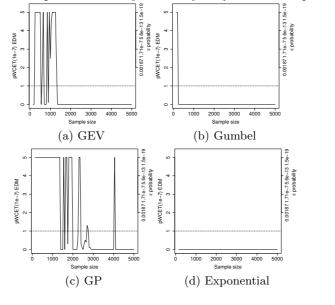

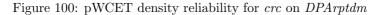

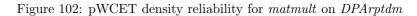

| Figure 99  | pWCET density reliability for crc on DPCpArrr216                               |

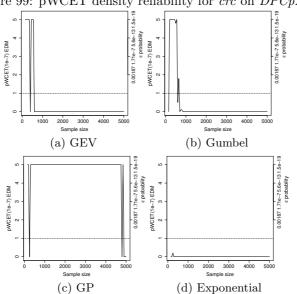

| Figure 100 | pWCET density reliability for crc on DPArptdm216                               |

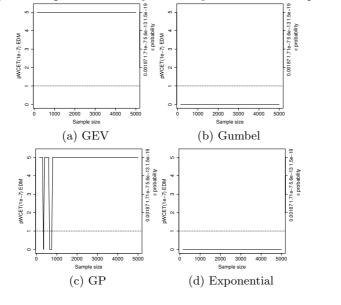

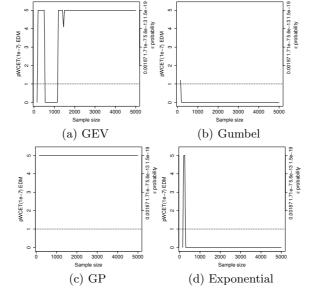

| Figure 101 | pWCET density reliability for $matmult$ on $DPCpArrr\ 217$                             |

|------------|----------------------------------------------------------------------------------------|

| Figure 102 | pWCET density reliability for $matmult$ on $DPArptdm\ 217$                             |

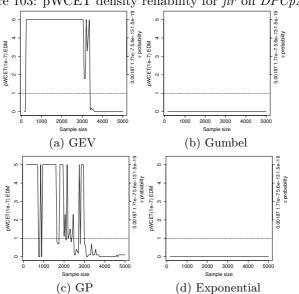

| Figure 103 | pWCET density reliability for $\mathit{fir}$ on $\mathit{DPCpArrr}$ 218                |

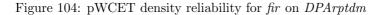

| Figure 104 | pWCET density reliability for $\mathit{fir}$ on $\mathit{DPArptdm}$ $\ldots\ldots$ 218 |

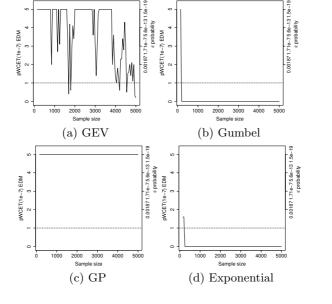

| Figure 105 | pWCET density reliability for $\mathit{fibcall}$ on $\mathit{DPCpArrr} \dots 219$      |

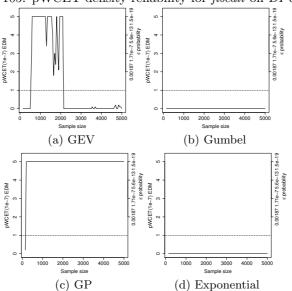

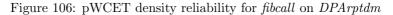

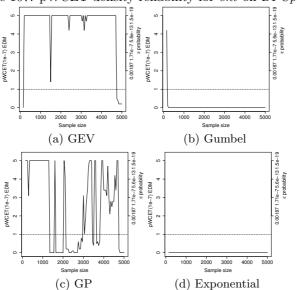

| Figure 106 | pWCET density reliability for $\mathit{fibcall}$ on $\mathit{DPArptdm} \dots 219$      |

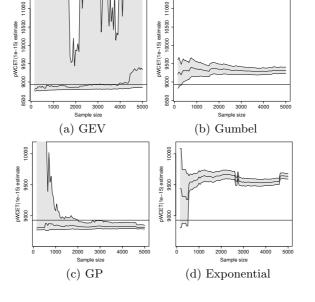

| Figure 107 | pWCET density reliability for $cnt$ on $DPCpArrr$ $$ 220                               |

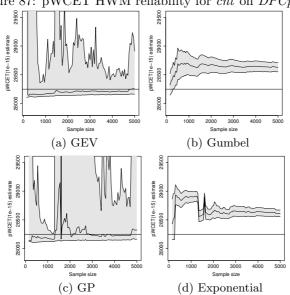

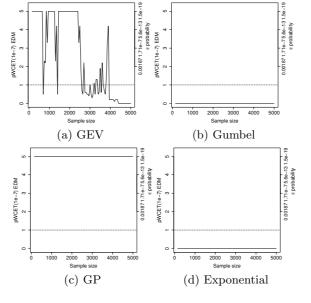

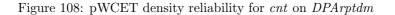

| Figure 108 | pWCET density reliability for $cnt$ on $DPArptdm$ $$ 220                               |

| Figure 109 | crc PRS maxima analysability analysis                                                  |

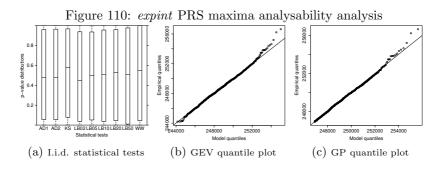

| Figure 110 | expint PRS maxima analysability analysis                                               |

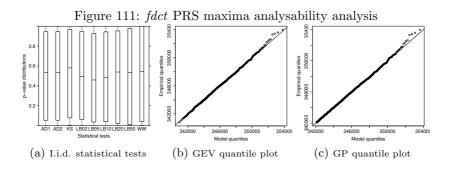

| Figure 111 | fdct PRS maxima analysability analysis                                                 |

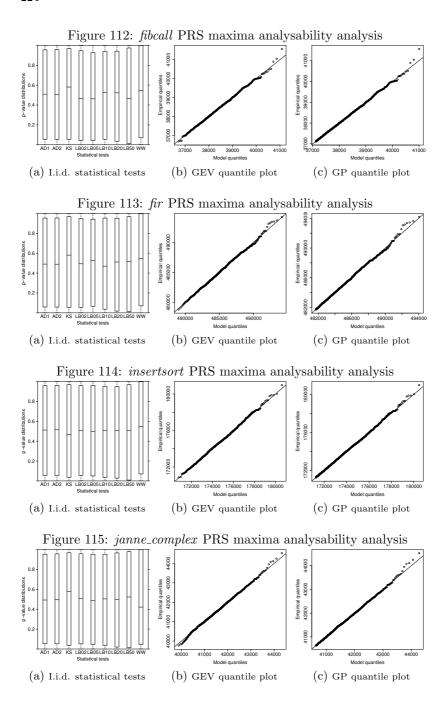

| Figure 112 | $\mathit{fibcall}$ PRS maxima analysability analysis224                                |

| Figure 113 | $\mathit{fir}$ PRS maxima analysability analysis                                       |

| Figure 114 | insertsort PRS maxima analysability analysis                                           |

| Figure 115 | $janne\_complex$ PRS maxima analysability analysis 224                                 |

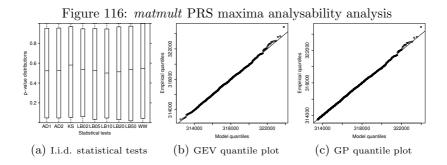

| Figure 116 | matmult PRS maxima analysability analysis                                              |

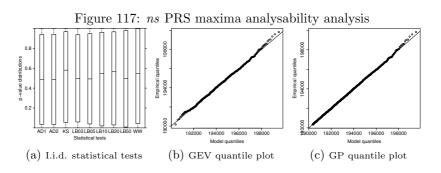

| Figure 117 | ns PRS maxima analysability analysis                                                   |

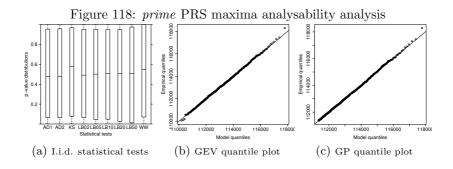

| Figure 118 | prime PRS maxima analysability analysis                                                |

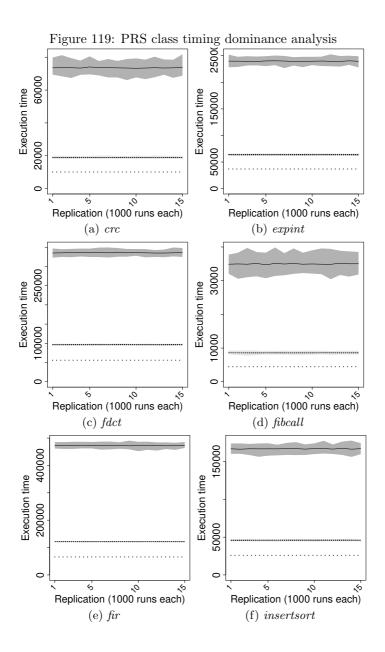

| Figure 119 | PRS class timing dominance analysis                                                    |

| Figure 120 | PRS class timing dominance analysis                                                    |

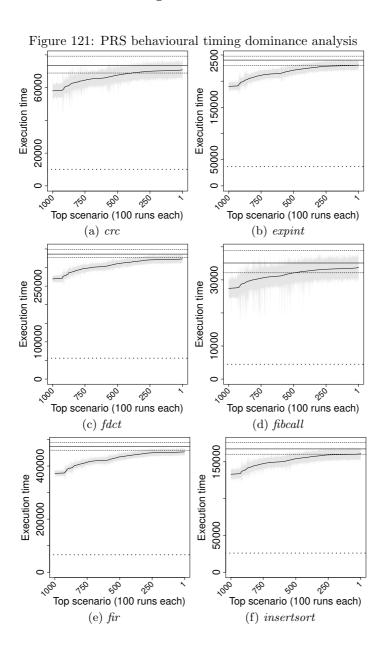

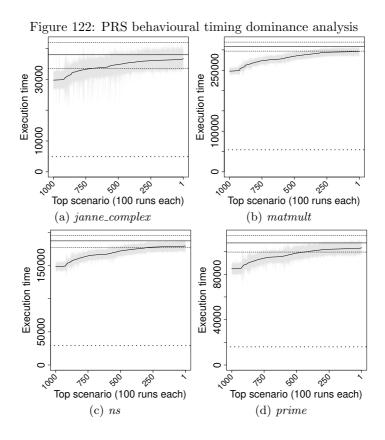

| Figure 121 | PRS behavioural timing dominance analysis                                              |

| Figure 122 | PRS behavioural timing dominance analysis                                              |

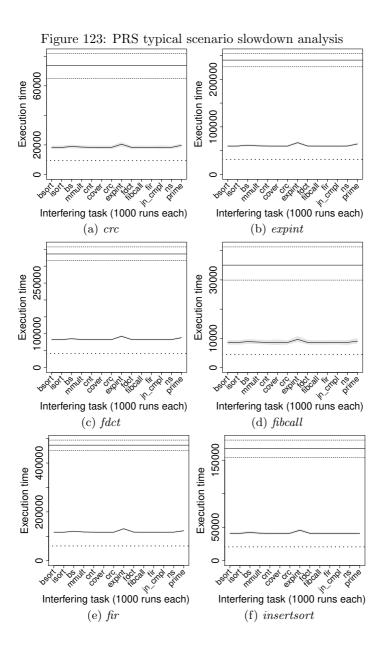

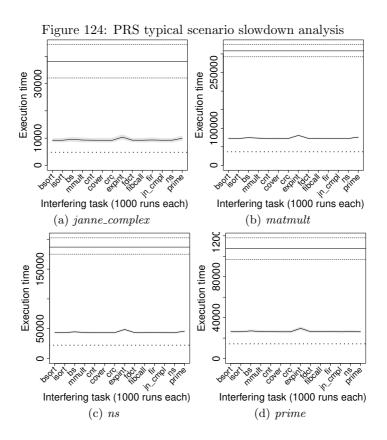

| Figure 123 | PRS typical scenario slowdown analysis                                                 |

| Figure 124 | PRS typical scenario slowdown analysis                                                 |

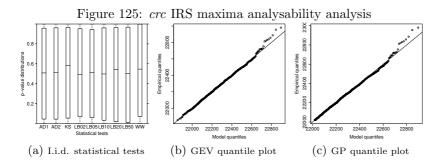

| Figure 125 | crc IRS maxima analysability analysis                                                  |

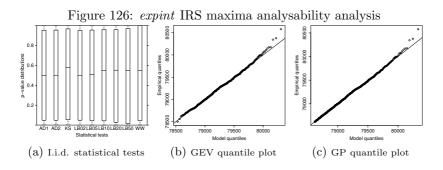

| Figure 126 | expint IRS maxima analysability analysis                                               |

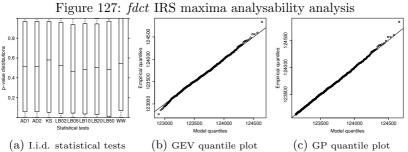

| Figure 127 | $\mathit{fdct}$ IRS maxima analysability analysis                                      |

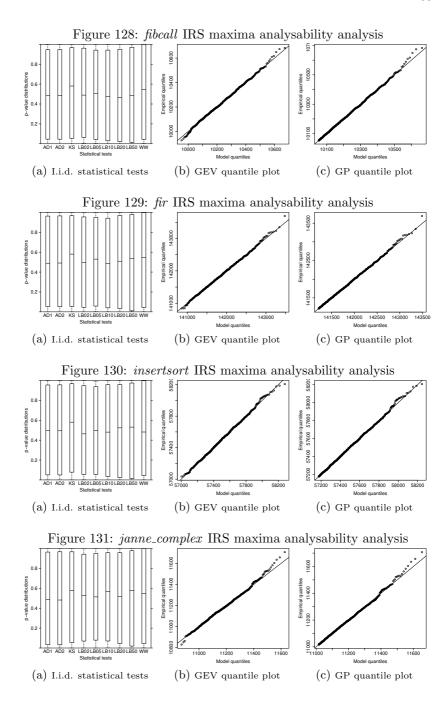

| Figure 128 | $\mathit{fibcall}$ IRS maxima analysability analysis                                   |

| Figure 129 | fir IRS maxima analysability analysis                                                  |

| Figure 130 | insertsort IRS maxima analysability analysis 233                                       |

| Figure 131 | $janne\_complex$ IRS maxima analysability analysis 233                                 |

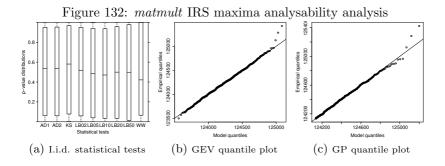

| Figure 132 | $matmult \ {\it IRS} \ {\it maxima} \ {\it analysability} \ {\it analysis}234$         |

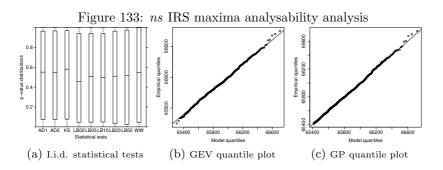

| Figure 133 | ns IRS maxima analysability analysis                                                   |

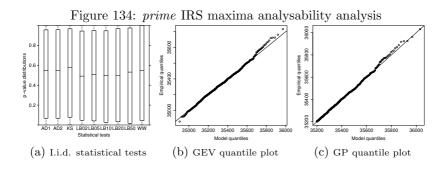

| Figure 134 | prime IRS maxima analysability analysis                                                |

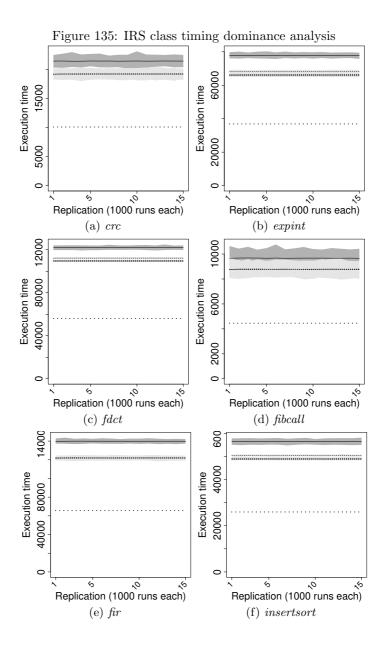

| Figure 135 IRS class timing dominance analysis          | 35 |

|---------------------------------------------------------|----|

| Figure 136 IRS class timing dominance analysis          | 36 |

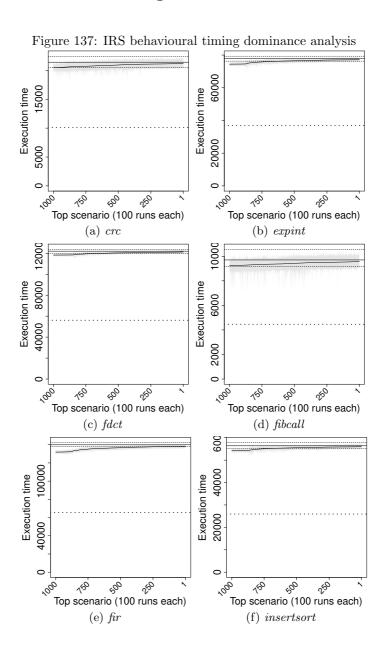

| Figure 137 IRS behavioural timing dominance analysis    | 37 |

| Figure 138 IRS behavioural timing dominance analysis 23 | 38 |

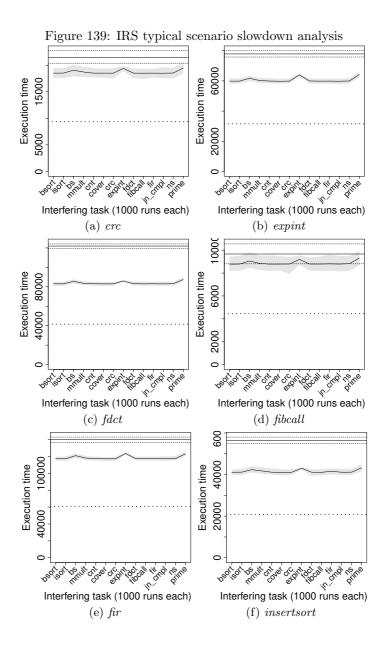

| Figure 139 IRS typical scenario slowdown analysis       | 39 |

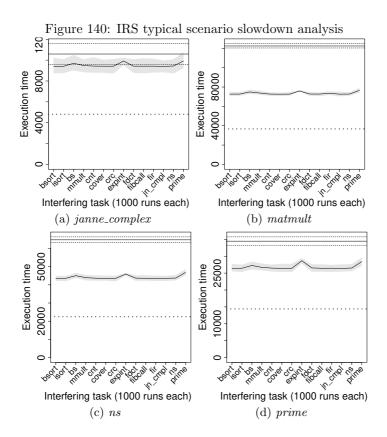

| Figure 140 IRS typical scenario slowdown analysis       | 10 |

# LIST OF TABLES

| Table 1 | MBPTA results                         | 68 |

|---------|---------------------------------------|----|

| Table 2 | PRS maximum slowdown                  | 35 |

| Table 3 | PRS typical slowdown                  | 37 |

| Table 4 | IRS maximum slowdown14                | 46 |

| Table 5 | IRS typical slowdown14                | 48 |

| Table 6 | Raw dataset analysis                  | 50 |

| Table 7 | BM timing analysis                    | 51 |

| Table 8 | POT timing analysis                   | 52 |

| Table 9 | Schedulers' hardware complexity/cost1 | 53 |

|         |                                       |    |

#### LIST OF ACRONYMS

**AD** Anderson-Darling

ALU Arithmetic Logic Unit

BM Block Maxima

BTB Branch Target Buffer

**CAN** Controller Area Network

CASR Cellular Automata Shift Register

**DMA** Direct Memory Access

**DRAM** Dynamic Random Access Memory

**EDM** Exceedance Density Metric

**EQMAE** Estimated Quantiles' Mean Absolute Error

**EVT** Extreme Value Theory

FIFO First-In First-Out

**FPU** Floating-Point Unit

FPGA Field-Programmable Gate Array

FSB Front-Side Bus

GMLE Generalized Maximum Likelihood Estimation

**GEV** Generalized Extreme Value

**GP** Generalized Pareto

**IoT** Internet of Things

**HWM** High Water Mark

**IEEE** Institute of Electrical and Electronics Engineers

I/O Input/Output

IP Intellectual Property

IRS Interference-Regulated Scheduler

ISA Instruction Set Architecture

KS Kolmogorov-Smirnov

LB Ljung-Box

LFSR Linear Feedback Shift Register

LRU Least Recently Used

MBDTA Measurement-Based Deterministic Timing Analysis

MBPTA Measurement-Based Probabilistic Timing Analysis

MIPS Microprocessor without Interlocked Pipeline Stages

MLE Maximum Likelihood Estimation

**NoC** Network-on-Chip

PC Program Counter

PCI Peripheral Component Interconnect

PRNG Pseudo-Random Number Generator

POT Peaks Over Threshold

PRS Purely Random Scheduler

**pWCET** Probabilistic Worst-Case Execution Time

RAM Random Access Memory

RISC Reduced Instruction Set Computer

**RF** Register File

RR Round-Robin

RTS Real-Time System

SDTA Static Deterministic Timing Analysis

SPTA Static Probabilistic Timing Analysis

**TDM** Time Division Multiplexing

**TRNG** True Random Number Generator

WCEP Worst-Case Execution Path

WCET Worst-Case Execution Time

**WW** Wald-Wolfowitz

# CONTENTS

| INTRODUCTION                    | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOTIVATION                      | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| OBJECTIVES                      | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CONTRIBUTIONS                   | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DOCUMENT ORGANIZATION           | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| EXTREME VALUE THEORY            | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

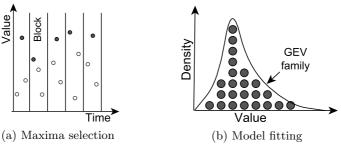

| APPLICATION APPROACHES          | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| MODEL FITTING                   | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| BM BLOCK SIZE SELECTION         | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| POT THRESHOLD SELECTION         | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

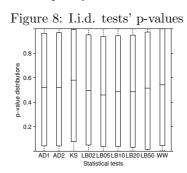

| APPLICABILITY REQUIREMENTS      | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Applicability Statistical Tests | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

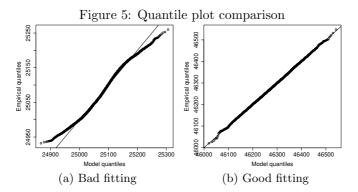

| Applicability Plots             | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Conclusion                      | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| MEASUREMENT-BASED PROBABILISTIC |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TIMING ANALYSIS                 | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| APPLICATION                     | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| APPLICABILITY REQUIREMENTS      | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SAMPLE SIZE                     | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| MODEL FITNESS                   | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| EXECUTION PATHS                 | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TEMPORAL ISOLATION              | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RELATED WORK                    | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| APPLICATION EXAMPLE             | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CONCLUSION                      | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TIME-RANDOMIZED PROCESSORS      | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RELATED WORK                    | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

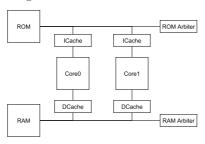

| CACHE MEMORIES                  | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| BRANCH PREDICTORS               | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| BUS ARBITERS                    | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                 | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RANDOMNESS SOURCES              | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                 | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| -                               | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RELATED WORK                    | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                 | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Real-Hardware Samples           | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                 | MOTIVATION OBJECTIVES CONTRIBUTIONS DOCUMENT ORGANIZATION EXTREME VALUE THEORY APPLICATION APPROACHES MODEL FITTING BM BLOCK SIZE SELECTION POT THRESHOLD SELECTION APPLICABILITY REQUIREMENTS Applicability Statistical Tests Applicability Plots Conclusion MEASUREMENT-BASED PROBABILISTIC TIMING ANALYSIS APPLICATION APPLICABILITY REQUIREMENTS SAMPLE SIZE MODEL FITNESS EXECUTION PATHS TEMPORAL ISOLATION RELATED WORK APPLICATION EXAMPLE CONCLUSION TIME-RANDOMIZED PROCESSORS RELATED WORK CACHE MEMORIES BRANCH PREDICTORS BUS ARBITERS NETWORKS-ON-CHIP RANDOMNESS SOURCES CONCLUSION pWCET RELIABILITY EVALUATION RELATED WORK EXPERIMENT DESIGN |

| 5.2.2   | Synthetic Samples                       | 85  |

|---------|-----------------------------------------|-----|

| 5.3     | EXPERIMENT OBJECTIVES                   | 87  |

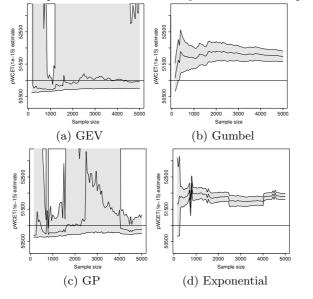

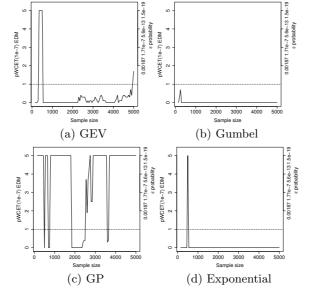

| 5.3.1   | pWCET HWM Reliability                   | 87  |

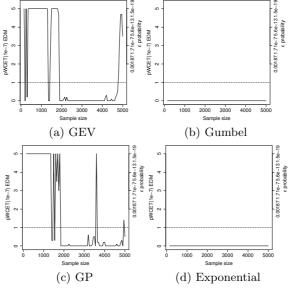

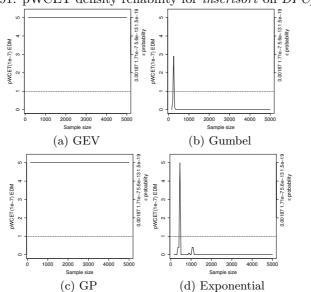

| 5.3.2   | pWCET Density Reliability               | 87  |

| 5.4     | THE PROBABILITY OF REJECTING A RELIABLE |     |

|         | pWCET                                   | 90  |

| 5.4.1   | HWM-based method                        | 91  |

| 5.4.2   | EDM-based method                        | 91  |

| 5.5     | APPLICABILITY EVIDENCE                  | 92  |

| 5.6     | pWCET HWM RELIABILITY                   | 94  |

| 5.6.1   | Real-Hardware Samples                   | 94  |

| 5.6.2   | Synthetic Samples                       | 95  |

| 5.7     | pWCET DENSITY RELIABILITY               | 103 |

| 5.7.1   | Real-Hardware Samples                   |     |

| 5.7.2   | Synthetic Samples                       | 104 |

| 5.8     | EQMAE-BASED POT THRESHOLD SELECTION     |     |

| 5.9     | RECOMMENDATIONS                         |     |

| 5.10    | CONCLUSION                              |     |

| 6       | EVALUATING RANDOMIZED SCHEDULING        |     |

|         | ON MULTITHREAD PIPELINES TO BENEFIT     |     |

|         | MBPTA                                   | 119 |

| 6.1     | PIPELINING                              | 119 |

| 6.2     | MULTITHREADING                          | 121 |

| 6.3     | MULTITHREAD PIPELINE DESIGN             |     |

| 6.4     | MAXIMUM INTERFERENCE SCENARIO           |     |

| 6.5     | EVALUATION METHOD                       |     |

| 6.6     | PURELY RANDOM SCHEDULER (PRS)           |     |

| 6.6.1   | Evaluation                              |     |

| 6.6.1.1 | Maxima Analysability                    |     |

|         | Class Timing Dominance                  |     |

|         | Behavioural Timing Dominance            |     |

|         | Interference Balancing                  |     |

|         | Typical Scenario Slowdown               |     |

| 6.7     | INTERFERENCE-REGULATED SCHEDULER (IRS)  |     |

| 6.7.1   | Thread States                           |     |

| 6.7.2   | Inter-Thread Interference Detection     |     |

| 6.7.3   | Credit-Based Schedulability Regulator   |     |

| 6.7.4   | Evaluation                              |     |

|         | Maxima Analysability                    |     |

|         | Class Timing Dominance                  |     |

|         | Behavioural Timing Dominance            |     |

| 5.1.1.0 |                                         | 110 |

| Interference Balancing                        |

|-----------------------------------------------|

| Typical Scenario Slowdown                     |

| TIMING ANALYSIS COMPARISON                    |

| ${\tt IMPLEMENTATION\ EFFORT\$                |

| CONCLUSION                                    |

| <b>FINAL REMARKS</b>                          |

| GENERAL CONSIDERATIONS                        |

| PUBLICATIONS                                  |

| FUTURE WORK                                   |

| ${\bf ACKNOWLEDGEMENT} \ \dots \ 160$         |

| <b>REFERENCES</b>                             |

| APPENDIX A - pWCET Reliability Evaluation181  |

| APPENDIX B - Evaluating Randomized Scheduling |

| on Multithread Pipelines to Benefit MBPTA 223 |

| APPENDIX C - Experimentation Platforms 243    |

|                                               |

#### 1 INTRODUCTION

Real-Time Systems (RTSs) are computer systems that are subject both to logical and temporal requirements, which means the produced results must not only be correct from a logical point of view but must also be generated at the correct time. Applications with real-time requirements are becoming increasingly common and greatly vary in size, complexity and criticality, ranging from the simple embedded controllers for household appliances to complex and critical avionics systems, for example. RTSs are classified according to the criticality of their temporal requirements. In critical or hard real-time systems, the lack of timing correctness may result in catastrophic consequences, both from the economic point of view and in the sense of potentially causing the loss of life. In non-critical or soft real-time systems the temporal requirements describe the desired behaviour, but if not met they do not invalidate the results nor have catastrophic consequences, although the application's utility is significantly reduced (LIU, 2000).

The temporal requirements to which RTSs are subject are expressed in terms of the deadlines in which the results must be generated. For critical RTSs it is necessary to build strong evidence that these deadlines are not missed, and for this purpose schedulability tests are often employed that demonstrate they are met even in the worst-case scenario. These tests are based on temporal parameters that are either imposed upon the tasks by the operation context, for example their periods  $T_i$  and deadlines  $D_i$ , or that must be derived from the software and hardware that implement them, such as their maximum execution times  $C_i$  – which are estimated considering tasks are executed continuously and exclusively on a single-core processor –, and their response times  $R_i$  – determined by taking into account interference such as the concurrent execution of other tasks, the use of resource locks (e.g. semaphores), and the occurrence of release jitter (e.g. due to disabled interrupts) (LIU, 2000; WILHELM et al., 2008).

The  $C_i$  parameters, also known as the tasks' Worst-Case Execution Times (WCETs), represent the longest time possibly taken by the target hardware platform to execute the software that implements them. A task's WCET varies depending on a multitude of factors that must be taken into account for the determination of its exact value, which can be extremely complex, or for establishing reliable bounds for it. Especially when related to critical RTSs, the WCET estimates must be safe, i.e. the real value must never be underestimated, and should

be tight, i.e. its overestimation must be minimized in order to reduce resource wasting. The methods employed in deriving these estimates must be (1) sound, to allow providing reliable guarantees, (2) efficient, to be useful in practical environments, and (3) as precise as possible regarding the yielded results. The determination of WCET bounds is usually performed through methods that fit one of the following classes, although hybrid approaches are also increasingly common (LIU, 2000; WILHELM et al., 2008, 2009; ABELLA et al., 2015):

- Static methods are based on a detailed analysis of the task's code taking into account the architecture of the hardware platform in which it will be executed, thus generally leading to large efforts and/or computational costs but also to results known to be safe (WILHELM et al., 2008; CAZORLA et al., 2013a).

- Deterministic: Static Deterministic Timing Analysis (SDTA) comprises the traditional static timing analysis methods, in which WCET bounds are derived by jointly analysing the task's code and an abstract but temporally trustworthy model of the hardware on which it will be executed. Such methods typically provide safe results by considering or being conservative regarding every possible execution condition, but (1) hardware model abstractions that are often necessary to ensure computational feasibility can lead to large WCET overestimations, and (2) even small changes in the processor architecture may require large efforts to properly adjust the hardware models employed in the timing analysis. Moreover, such methods generally lack composability characteristics needed for handling large systems that use modern processors (WILHELM et al., 2008).

- Probabilistic: Static Probabilistic Timing Analysis (SPTA) determines probability density functions for timing events of the underlying hardware platform through a careful analysis of their behaviour, and progressively combines them through convolution operations in order to obtain upper-bounding densities for the execution of instruction sequences. This leads to reliable results, since the global density function is known to be valid as long as the local ones are, but potentially leads to large computational efforts for the analysis of complex applications, even if executed on simple processor architectures (ABELLA et al., 2014).

- Measurement-based methods perform the analysis of measurements of the task's execution times taken on the target hardware platform, which significantly reduces the hardware architecture analysis efforts but requires the determination of safety margins to account for possibly unmeasured effects.

- **Deterministic**: Measurement-Based Deterministic Timing Analysis (MBDTA) analyses the task's code and execution environment for determining the inputs that are expected to exercise the Worst-Case Execution Paths (WCEPs), execution paths that are candidate to produce the Measurements are then taken on the target WCET. hardware to obtain these paths' execution times, whose low variability is expected to provide reasonable confidence that their real WCETs are not far from the measured values. Since the conditions for the occurrence of the task's real WCET are generally very hard to predict and reproduce, margins typically still need to be added to the maximum measured time in order to attain higher safety in relation to unwitnessed timing effects. On top of that, acceleration hardware elements capable of inducing worst-case timing effects that are hardly observable (e.g. cache memories) must be avoided or used with care (ABELLA et al., 2014).

- **Probabilistic**: Measurement-Based Probabilistic Timing Analysis (MBPTA) produces probabilistic WCET estimates, i.e. WCET estimates associated to non-null but sufficiently small exceedance probabilities, by fitting statistical models to measurements of the analysed task's maximum execution times (CUCU-GROSJEAN et al., 2012). Such methods can in principle produce bounds with confidence levels that can be high enough even for systems requiring certification, but for that proper evidence must be supplied that the task's measured execution times (1) are representative regarding the task's worst possible timing behaviour, (2) meet the requirements of the employed statistical tools, and (3) present maxima that in fact adhere to the probability distributions used. This poses strict requirements both on the measurement collection process and on the timing behaviour of the hardware platform used (COLES, 2001; CAZORLA et al., 2016; KOSMIDIS et al., 2016).

This work focuses on the Measurement-Based Probabilistic Timing Analysis (MBPTA) technique, which targets determining probabilistic bounds for the WCETs of tasks that compose RTSs. These bounds, known as Probabilistic Worst-Case Execution Times (pWCETs), are composed of both a limiting value and an associated probability that the value is exceeded at any individual execution of the task. The application of MBPTA is based on the statistical analysis of the tasks' maximum execution times, measured while they are executed on the real target hardware platform under carefully determined conditions (CAZORLA et al., 2013a, 2016). The main tool currently employed by MBPTA is Extreme Value Theory (EVT), a branch of statistics designed to estimate the probability of rare extreme events. Through the adjustment of statistical models to the largest values observed for the outcomes of a target phenomenon, EVT is capable of determining values expected to be exceeded with a maximum probability that can (in principle) be set to arbitrarily low values (COLES, 2001; CUCU-GROSJEAN et al., 2012). Within MBPTA, EVT is promising in enabling the determination of pWCET estimates associated with exceedance probabilities comparable, or even lower, than those associated to other kinds of failures that must be considered in designing critical RTSs (e.g. structural failures) (CAZORLA et al., 2016).

Time-randomization at hardware level was recently proposed as a means for designing processors whose timing behaviour is influenced by probabilistic laws, hence potentially improving RTSs' timing analysability through methods based on statistical frameworks – such as MBPTA. The main principle of time-randomization is the replacement of speculative information typically employed in taking actions that influence execution times with (pseudo-)random numbers. Consequently, time-randomization also partially decouples hardware elements' timing behaviour from execution history, mitigating the systematic emergence of pathological patterns that could lead to extreme execution times (TRILLA et al., 2017b; AGIRRE et al., 2018). Time-randomization have been recently applied in related work, e.g., for designing cache memories (KOSMIDIS et al., 2013a), bus arbiters (JALLE et al., 2014) and Networks-on-Chip (NoCs) (SLIJEPCEVIC et al., 2016, 2017a). Despite no guarantees on execution times' analysability can be effectively provided (LIMA; DIAS; BARROS, 2016), time-randomized processors often prove suitable to be used in the context of MBPTA (CAZORLA et al., 2013a; KOSMIDIS et al., 2016; CAZORLA et al., 2016).

The determination of strict bounds for the WCETs of RTSs' tasks, with the objective of guaranteeing that their timing constraints are met,

is becoming increasingly challenging as computer architectures evolve. This is so either due to the large effort and complexity of modelling modern processors' constructive details for applying static methods (WILHELM et al., 2008) or due to difficulties in reliably associating variable execution times with tasks' worst-case behaviour through measurement-based techniques (KOSMIDIS et al., 2016). At the same time, many modern applications – such as autonomous cars and devices composing the so-called Internet of Things (IoT) – are emerging which tend to increase the demand for computer architectures capable of delivering processing capacity with both scalability and affordable timing analysability characteristics. In this context, the associated application of MBPTA and of hardware-level time-randomization techniques is promising in enabling the timing analysis of RTSs' tasks executed on complex computer processors, for which traditional methods would potentially produce pessimistic results, by abstracting constructive details of the underlying hardware (KOSMIDIS et al., 2016).

# 1.1 MOTIVATION

Static WCET analysis techniques have known limitations regarding the complexity of processor architectures that can be handled in feasible time, for inherently lacking of composability characteristics. The continuous introduction of increasingly complex acceleration hardware elements in processors, mainly for improving performance, is resulting in architectures which are far from being analysable through static methods. Even a small set of such elements can cause static timing analysis to become intractable, due both to the complexity of modelling their behaviour (especially when different elements are combined) and to the computational efforts demanded by the analysis. The introduction of multi-core processors have especially contributed in making static analysis infeasible in modern architectures: the existence of shared hardware elements and the uncertainty regarding the behaviour of tasks lead to a situation in which either (1) unrealistically pessimistic cases must be assumed, inducing pessimism that can be large enough to negate a significant fraction of the processing capacity (NÉLIS; YOMSI; PINHO, 2016; KIM et al., 2016), or (2) all possibilities must be tested, which easily proves intractable (WILHELM et al., 2008; LIU; REINEKE; LEE, 2010; CULLMANN et al., 2010).

At the same time, industry has an increasing demand for WCET analysis, which is often met by either (1) employing simpler architectures

to which timing analysis is safe and feasible (e.g. for critical systems), or (2) relying on measurements taken on a "bad-case" environment added with safety margins defined based solely on experience (e.g. for non-critical systems) (CAZORLA et al., 2016).

There is a strong tendency that the market of processors targeting RTSs will witness a fast demand increase during the next years, which is especially true assuming the autonomous cars' and IoT devices' markets keep growing. Whenever this speculation proves right, so will grow the demand for increased processing capacity, and for affordable and reliable timing analysis of tasks executed on such processors (KINNAN, 2009; NÉLIS et al., 2014; SAIDI et al., 2015). In this scenario, the timing analysis solutions currently employed in the industry tend to prove not applicable, since (1) simple processors generally do not allow large sets of tasks being integrated into single hardware platforms, and (2) the pessimism of multi-/many-core processors' analysis through traditional methods tends to prove unacceptable (KIM et al., 2016).

These trends point out that, in a near future, complex hardware platforms will be necessary for executing modern RTSs in order to cope with their increasing processing demands, and that therefore MBPTA approaches will possibly play an important role in enabling industry to derive WCET bounds in a safe and cost-effective manner. Still, there are many open questions associated with the fundamental requirements that must be met in collecting and analysing measurements for applying MBPTA, and especially regarding how reliable are the pWCET estimates it is capable of yielding. Time-randomization is a candidate technique to leverage timing analysability on increasingly complex processors, for being promising in benefiting MBPTA application.

Considering the mentioned open questions and design opportunities, this thesis tackles MBPTA-related issues in two fronts: (A) performing empirical evaluations of the reliability of pWCET estimates derived through MBPTA, and (B) evaluating the suitability for MBPTA of processors equipped with randomly-scheduled multithread pipelines.

# 1.2 OBJECTIVES

The objectives of this thesis are twofold: (A) investigating empirical methods for evidencing or counter-proving the reliability of pWCET estimates produced using EVT within MBPTA, and (B) investigating approaches for designing time-randomized multithread pipelines suitable for the application of MBPTA. More specifically,

the thesis to be demonstrated within (A) is that the reliability of pWCET estimates produced using MBPTA can be evaluated using large validation samples and comparing their behaviour against expectations on the bounding of maximum values and of tail densities, and within (B) is that scheduling-level time-randomization can be employed to enable the use of multithread pipelines on RTSs – a design often regarded as harmful to static timing analysis – by causing yielded execution times to meet the applicability requirements of MBPTA.

# 1.3 CONTRIBUTIONS

The main contributions provided in this work are twofold:

Firstly, we perform an empirical evaluation of the reliability of pWCET estimates produced based on MBPTA through EVT using large validation samples (e.g. of size 10<sup>8</sup>), considering distinct EVT application approaches and performing a large set of replications using different conditions and methods. We evaluate pWCET estimates' reliability based on the effective upper-bounding of large validation samples' (1) maximum observed execution times and (2) densities of execution time empirical distributions' tails. These contributions are covered in the following published papers: