# A Bidirectional ASIC for Active Microchannel Neural Interfaces

Maryam Habibollahi<sup>1</sup>, Dai Jiang<sup>1</sup>, Henry Lancashire<sup>2</sup>, Andreas Demosthenous<sup>1</sup>

<sup>1</sup> Department of Electronic and Electrical Engineering, University College London, United Kingdom

<sup>2</sup> Department of Medical Physics and Biomedical Engineering, University College London, United Kingdom email: maryam.habibollahi.15@ucl.ac.uk; a.demosthenous@ucl.ac.uk

Abstract—Closed-loop neural prostheses have been widely used as a therapeutic strategy for a range of neurological, inflammatory, and cardiac disorders. Vagus nerve stimulation has shown promising results for the monitoring and treatment of post-operation symptoms of heart transplant recipients. A prime candidate for selective control of vagal fibres is the microchannel neural interface (MNI), which provides a suitable environment for neural growth and enables effective control of the neural activity in a bidirectional system. This paper presents the design and simulation of an ASIC in 180nm high-voltage CMOS technology, capable of concurrent stimulation and neural recording with artifact reduction in a seven-channel MNI. The analog front-end amplifies action potentials with a gain of 40 dB, presenting a common-mode rejection ratio of 81 dB at 1 kHz and a noise efficiency factor of 5.13 over the 300 Hz to 5 kHz recording bandwidth. A 42-Vcompliant stimulation module operates concurrently and independently across the seven channels.

Keywords—Bidirectional neural interface, biomedical electronics, high-voltage stimulation, microchannel electrodes, neural recording, vagus nerve stimulation.

## I. INTRODUCTION

Denervation of the autonomic fibres following a heart transplant results in severe limitations in exercise capacity for patients suffering from heart failure due to chronotropic incompetence, which restricts the ability of appropriately increasing the heart rate to meet metabolic needs [1]. A recent approach to improve the quality of life of posttransplant patients includes electrical stimulation of the vagus nerve (CN X), that has shown benefits in correcting autonomic imbalance [2]. However, effective modulation of the vagus nerve requires a highly selective interface that provides concurrent stimulation and acquisition of neural activity for a truly bidirectional system. The measurement of meaningful signals from the nervous fibres poses several challenges for the design of a closed-loop implantable bioelectronic system.

The trade-off between the selectivity and invasiveness of neural interfaces demands various considerations for the selection of the appropriate structure. Regenerative electrodes have shown promising results in providing a selective interface while guiding neural growth. In particular, the microchannel electrodes, which enclose groups of axons within insulating tubes, have enabled effective stimulation and recording of neural fibres independently from the position of the nodes of Ranvier. The increased extracellular resistance requires smaller stimulus amplitudes and results in larger recorded signals (neural spikes or action potentials). Typically, microchannels range up to 5 mm in length and 200 µm in diameter to minimise channel blockage while providing adequate space for vascularisation of the nerve [3]. High-density microchannel neural interfaces (MNIs) can overcome the limitations of electrode interconnects via multiplexed, on-chip contacts that access the channels more

This work was supported in part by the European Commission under H2020- EU.1.2.2. – FET Proactive (Agreement ID: 824071; project NeuHeart; <u>http://www.neuhearth2020.eu/</u>) and in part by the Engineering and Physical Sciences Research Council (EPSRC).

easily and limit device complexity. Moreover, on-site electronic circuits capable of stimulation and recording of the neural signals would allow concurrent multi-channel operation and high-quality acquisition of action potentials, while the structure of the MNI enables scaling of the system by stacking multiple units [4].

Action potentials recorded extracellularly are orders of magnitude smaller than the surrounding noise. Collecting meaningful data requires a common-mode rejection ratio (CMRR) in excess of 80 dB [5] via analog signal processing through in-situ amplification to minimise sensitivity to artifacts. Due to the high contact impedance of the microchannel electrodes, a large voltage compliance is necessary to deliver the required stimulus currents. This results in artifacts that can be detected by adjacent recording channels, causing distortion in the measured signal, or completely masking the biosignals. A method that carries out automatic detection and reduction of the stimulus artifacts was developed using a comparator and an adjustable bandpass filter [6], forming a closed loop to apply pole shifting upon detecion of artifacts. High-voltage (HV) stimulus currents are necessary to safely deliver balanced, biphasic pulses with varying frequencies to elicit or inhibit neural activity.

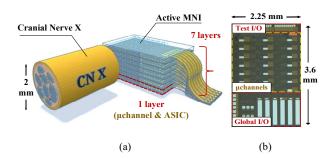

This paper presents the design and simulation of an ASIC for a bidirectional active MNI. The concept diagram shown in Fig. 1(a) represents seven stacked devices, each containing seven 300-µm-pitch microchannels with tripolar electrodes on the ASIC shown in Fig. 1(b). The interface aims to enclose sections of the thoracic branch of the vagus nerve within 49 channels. Section II outlines the system requirements for a multi-channel bidirectional interface with artifact reduction. Section III describes the top-level architecture and the system sub-blocks. Post-layout simulation results are presented in Section V.

## II. SYSTEM REQUIREMENTS

Modulation of the vagus nerve fibres requires a biocompatible neural interface capable of safely delivering stimulus currents whilst adequately measuring neural signals to form a closed loop system. The safety of the implant must be ensured to avoid any toxic effects on the tissue or corrosive impacts on the electrodes.

Figure 1. Active MNI; (a) conceptual view, and (b) ASIC micrograph.

# A. Neural Excitation

Electrical stimulation of the neural fibres in miniaturised interfaces requires electrode voltages above 10 V to deliver the necessary currents, which range from 5  $\mu$ A to 25  $\mu$ A in microchannels [4]. As the channel impedances reach 1.24 M $\Omega$  [3], activation of the fibres requires a voltage compliance exceeding 30 V. Restrictions in the maximum drain-to-source (V<sub>ds</sub>) and gate-to-source (V<sub>gs</sub>) voltages of standard CMOS transistors require advanced methods such as transistor stacking [7] or HV shielding [8] to operate safely and integrate the HV output stage with the LV circuits. Furthermore, the device should be capable of providing balanced stimulus pulses with a reliable control over the programmed current. A tripolar electrode configuration is preferable to deliver focused stimulus pulses [9].

A high-output-impedance current driver is required to limit the effects of load variation on the delivered charge and provide the necessary precision and sensitivity within a limited circuit footprint. Current-mode digital-to-analog converters (I-DAC) are typically implemented in conjunction with a high-voltage output driver that consists of current mirrors for a stable stimulus current [10]. Additionally, charge imbalance must be minimised by passive or active charge balancing to prevent the build-up of residual charge at the electrode.

## B. Feedback Acquisition

Closed-loop interfaces have been widely developed for the peripheral nerves to provide advanced performance. Feedback can be obtained as biomarkers from the vagus nerve via measured action potentials, which range above 100 Hz in frequency with amplitudes varying from approximately 30 µV to 200 µV in silicone microchannels of the proposed dimensions [3]. Careful amplifier design is required to adequately record neural signals in the presence of noise sources that exceed 10 mV. Several techniques for low-noise amplifier (LNA) design have been developed to filter out-of-band noise sources and limit in-band sources such as the 1/f noise to limit contribution to the inputreferred noise (IRN) and the noise efficiency factor (NEF), which highlights the noise-power trade-off [11]. Operational transconductance amplifiers (OTA) are a common element of neural recording systems, with cascode topologies achieving a high gain within a limited front-end area.

Concurrent neural stimulation and recording requires appropriate methods for the detection and mitigation of the resulting stimulation artifacts. Such techniques can be applied to prevent the recording of artifacts, to improve the resilience of the recording front-end for a linear response, or to reconstruct the measured signal at the cost of increased complexity and circuit area. Although the preventative measures cannot provide complete removal of the artifacts, they are often used to ease the requirements on the recording amplifier [12].

## **III. ASIC ARCHITECTURE**

## A. Overal Structure

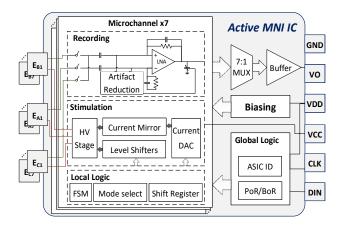

The active MNI chip has seven channels, each comprising stimulation and recording modules with independent control over the channel functions according to the received commands. Fig. 2 shows the system block

diagram. It shows the circuits local to each microchannel comprising the stimulation module, recording front-end, and the local logic, as well as circuits global to the chip, including voltage and current biasing, an analog output stage comprising a 7-to-1 multiplexer and buffer for the measured signal, a power-on reset signal source with brown-out detection, and a global ID storage unit to identify one of seven ICs in a stacked interface.

The system is provided with six main I/O pads, which carry the ground line, the LV (1.8 V) and HV (42 V) supply voltages, a 1 MHz clock signal and a digital input line for communication, and an analog output for the recorded neural signal. Although multiple channels can stimulate at the same time, the system I/O pads enable single-channel recording with swift transitions across the seven IC channels. A pseudo-tripolar electrode arrangement is implemented via the three electrode pads ( $E_{A,B,C}$ ) in each channel to limit the effects of interference on the recorded signal and achieve a more focused electric field during stimulation.

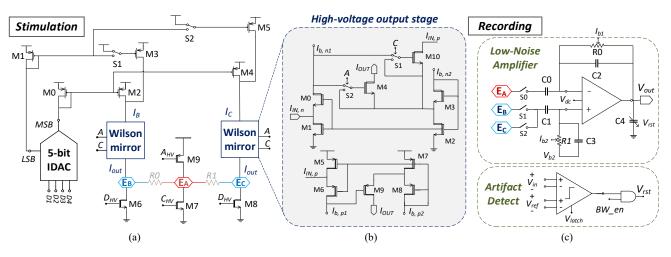

#### B. Stimulation Module

The high-voltage biphasic stimulus pulses are provided by current drivers local to each channel. These mirror the signal generated by a 5-bit I-DAC through two high-swing super-Wilson current mirrors at the outer electrode nodes  $E_B$ and  $E_C$  to achieve current steering. Each current mirror is supplied with two separate paths that determine the pulse polarity based on the digital signals for the cathodic ( $\Phi_C$ ) and anodic ( $\Phi_A$ ) phases. The I-DAC is designed using a binaryweighted topology to supply an output current ranging from 2  $\mu A$  to 62  $\mu A$  at each outer node, providing a maximum stimulus current of 124  $\mu A$  through the central electrode pad. The output of the I-DAC is mirrored through a simple current mirror that enables a least significant bit (LSB) calibration at the outer pads. An overview of the HV stimulator output stage is shown in Fig. 3(a).

Thick-oxide transistors were selected for the output stage to ensure safe operation with a high voltage compliance; level shifters apply the pulse control signals  $\Phi_C$  and  $\Phi_A$  at the necessary voltage to ensure safe operation of the HV transistors and switches, which also provide a path to ground for passive charge balancing following a biphasic pulse. The high-swing super-Wilson current mirror at each outer branch is shown in Fig. 3(b).

Figure 2. System block diagram of the active MNI IC (modified from [6]).

# C. Recording Module

An LNA was designed using the ac-coupled capacitive network structure with a telescopic cascode OTA to achieve a high output impedance with a gain of 40 dB over the bandwidth of 300 Hz to 5 kHz. High-voltage blanking switches at each electrode pad provide protection from the HV pulses during same-channel stimulation. To achieve a small channel area and power with minimum PVT variation, the LNA feedback pseudo-resistors were designed using the parallel-NMOS architecture with optimum control over their equivalent resistance via a stable control current that is generated globally [6]. The OTA transistor parameters were selected to reduce the noise introduced by the input and load transistors while also achieving a trade-off between power consumption and open-loop parameters of the circuit for a stable response.

Two differential comparators and D flip-flops that detect the absolute value of the input signal exceeding a pre-defined threshold form the artifact detection unit. The resulting output pole shifts the amplifier's low-pass response by adjusting the output capacitor accordingly. Fig. 3(c) shows the neural recording module, which includes an AND gate to enable the pole shifting operation. This user-specified  $BW\_en$  signal is extracted from the control command transmitted to all channels.

# D. Digital Control

A 32-bit command frame can be received by the channel logic blocks to determine the state of the control switches that define the channel's operating mode, phase, and parameters. The stimulation modes provide low-frequency (LF, 10 Hz to 50 Hz) pulses to elicit neural activity, highfrequency (HF, 10 kHz to 20 kHz) pulses to block neural signals and chopped (500 kHz packets within a LF envelope) pulses [13] using a finite-state machine. The recording settings enable pole shifting. As the command signal is broadcast to all the channels on every chip, initial ID checks are carried out to determine the intended channel via three pull-up/down resistors at each channel that specify its local address along with the programmable global ID blocks that locate the desired ASIC. In addition to the stimulation and recording functionalities of the channel, the system can be commanded to read and store the three-bit global ID upon power-up and to carry out electrode pad electroplating for ASIC post-processing.

# IV. SIMULATION RESULTS

Post-layout simulations of the analog blocks have verified their performance. Parametric and transient analyses of the stimulus pulses were used to model the accuracy and matching of the biphasic pulses, while the quality of the recorded signal was determined via frequency analysis. The performance of the overall system was observed in a mixed-signal environment via a top-level digital testbench that cycles through the operating modes. The ASIC draws 0.49 mW during the idle state with 13.3% (64.9  $\mu$ W) in each channel (43.4  $\mu$ W for stimulation, 5.1  $\mu$ W for recording, and 16.5  $\mu$ W for logic) and 6.5% (32  $\mu$ W) in the global region.

### A. Electrical Stimulation

Rectangular stimulus pulses of varying settings were generated according to the logic control switches. The current steering outputs were modelled with unequal intensities via the individual LSB control bits. Monte Carlo analyses of the largest output (62  $\mu$ A) setting showed an average value of 62.3 ± 0.5  $\mu$ A, which can be calibrated prior to implantation.

A maximum phase mismatch of 3.4% was observed on the low-frequency 2  $\mu$ A current setting, which can be accounted for with discharge phase duration. Fig. 4(a) illustrates the stimulus current (I<sub>STIM</sub>) during the three modes, programmed to supply one cycle of LF pulses at 2  $\mu$ A, followed by HF and chopped pulses at 22  $\mu$ A.

# B. Neural Recording

Initial frequency analyses on the amplifier were carried out during the optimisation process, resulting in an IRN of 6.3  $\mu V_{rms}$  [Fig. 4(b)] and an NEF of 5.13, which are sufficiently low to detect the smallest predicted biopotential markers (30  $\mu$ V). Further simulations confirmed a closed-loop amplifier gain of 40 dB [Fig. 4(c)] and a CMRR of 81 dB at 1 kHz [Fig. 4(d)], which exceeds the necessary performance. Monte Carlo analyses of the pseudo-resistor with 200 runs showed a standard deviation of 1.5% with PVT variations, which corresponds to approximately 23 Hz of variation in the frequency domain.

In addition to the sinusoidal input signals generated at varying frequencies to model the action potentials, composite forms of the signals with rectangular stimulus pulse artifacts

Figure 3. Schematics of the channel; (a) stimulation output, (b) super-Wilson current mirror, and (c) recording blocks [6].

Figure 4. Simulated results of (a) stimulation modes, (b) recording path input-referred noise, (c) amplifier gain, and (d) amplifier CMRR.

were also provided to the inputs of the LNA and passed through an additional filtering stage at the output, providing a 54 dB artifact attenuation ratio. Table I provides a comparison with other work.

|                                                                   | [14]                        | [15]                      | [16]                                 | This work                              |

|-------------------------------------------------------------------|-----------------------------|---------------------------|--------------------------------------|----------------------------------------|

| Technology                                                        | 130 nm                      | 180 nm                    | 65 nm                                | 180 nm                                 |

| Channel<br>count                                                  | 32 sense & stimulation      | 8 sense, 4<br>stimulation | 64 sense, 4<br>stimulation           | 7 sense & stimulation                  |

| Electrode<br>setup                                                | Bipolar                     | Bipolar                   | Bipolar                              | Tripolar                               |

| Stimulation<br>Compliance<br>Amplitude<br>Frequency               | 3.3 V<br>3 mA<br>5 Hz       | -<br>600 μΑ<br>12 Hz      | ±11 V<br>10 μA –<br>10.2 mA<br>10 Hz | 42 V<br>2–124 μA<br>7.4 Hz – 20<br>kHz |

| <b>Recording</b><br>Bandwidth<br>CMRR<br>IRN (µV <sub>rms</sub> ) | 1– 500 Hz<br>> 70 dB<br>1.6 | 1 Hz – 2<br>kHz<br>5      | 10 Hz – 1<br>kHz<br>-<br>2.9         | 300 Hz – 5<br>kHz<br>81 dB<br>6.3      |

| Artifact<br>attenuation                                           | Yes                         | 42 dB                     | 60 dB                                | 54 dB                                  |

| Die size                                                          | 10.9 mm <sup>2</sup>        | 1.4 mm <sup>2</sup>       | $4 \text{ mm}^2$                     | 8.1 mm <sup>2</sup>                    |

| Power draw                                                        | 54.4 μW                     | 3.96 µW                   | 0.62 mW                              | 0.49 mW                                |

TABLE I. COMPARATIVE SUMMARY OF PERFORMANCE

## V. CONCLUSION

This paper has presented the design and simulation of an active microchannel neural interface that provides concurrent stimulation and recording of regenerated neural fibres. The system is intended for the vagus nerve for the treatment of post-operative symptoms of heart transplant patients. However, it can be implemented for a wider range of applications. Post-layout simulations of the ASIC have shown a amplifier response with a CMRR of 81 dB at 1 kHz and an overall NEF of 5.13. High-voltage stimulus pulses were observed at various frequencies with a 54 dB artifact attenuation within a total chip area of 8.1 mm<sup>2</sup>.

#### REFERENCES

- A. Zweerink, A. L. C. van der Lingen, M. L. Handoko, A. C. van Rossum and C. P. Allaart, "Chronotropic incompetence in chronic heart failure," *Circulation: Heart failure*, vol. 11, no. 8, pp. 1-14, 2018.

- [2] H. Klein and G. M. U. De Ferrari, "Vagus nerve stimulation: A new approach to reduce heart failure," *Cardiology Journal*, vol. 17, no. 6, pp. 638-643, 2010.

- [3] J. J. FitzGerald et al., "A regenerative microchannel neural interface for recording from and stimulating peripheral axons in vivo," J. *Neural Eng.*, vol. 9, no. 1, p. 016010, Feb. 2012.

- [4] H. T. Lancashire, D. Jiang, A. Demosthenous and N. Donaldson, "An ASIC for recording and stimulation in stacked microchannel neural interfaces," *IEEE Trans. on Biomed. Circuits Syst.*, vol. 13, no. 2, pp. 259-270, 2019.

- [5] T. Denison, K. Consoer, W. Santa, A. T. Avestruz, J. Cooley and A. Kelly, "A2 μw 100 nV/rtHz chopper-stabilized instrumentation amplifier for chronic measurement of neural field potentials," *IEEE J. Solid-State Circuits*, vol. 42, no. 12, pp. 2934-2945, 2007.

- [6] M. Habibollahi, F. F. Hanzaee, D. Jiang, H. Lancashire and A. Demosthenous, "An active microchannel neural interface with artifact reduction," in *IEEE Int. Symp. Circuits Syst. (ISCAS)*, Daegu, Korea, 2021.

- [7] M. Monge et al., "A fully intraocular high-density self-calibrating epiretinal prosthesis," *IEEE Trans. Biomed. Circuits Syst.*, vol. 7, no. 6, pp. 747-760, 2013.

- [8] J. Charthad et al., "A mm-sized wireless implantable device for electrical stimulation of peripheral nerves," *IEEE Trans. Biomed. Circuits Syst.*, vol. 12, no. 2, pp. 257-270, 2018.

- [9] V. Valente, A. Demosthenous and R. Bayford, "A tripolar currentsteering stimulator ASIC for field shaping in deep brain stimulation," *IEEE Trans. Biomed. Circuits Syst.*, vol. 6, no. 3, pp. 197-207, 2012.

- [10] K. Sooksood, E. Noorsal, U. Bihr and M. Ortmanns, "Recent advances in power efficient output stage for high density implantable stimulators," in *Proc. Annu. Int. Conf. IEEE Eng. Med. Bio. Soc. EMBS*, 2012.

- [11] F. H. Noshahr, M. Nabavi and M. Sawan, "Multi-channel neural recording implants: A review," *Sensors (Switzerland)*, vol. 20, no. 3, pp. 1-29, 2020.

- [12] A. Zhou, B. C. Johnson and R. Muller, "Toward true closed-loop neuromodulation: artifact-free recording during stimulation," *Current Opinion in Neurobiology*, vol. 50, pp. 119-127, 2018.

- [13] D. Jiang and A. Demosthenous, "A multichannel high-frequency power-isolated neural stimulator with crosstalk reduction," *IEEE Trans. Biomed. Circuits Syst.*, vol. 12, no. 4, pp. 940-953, 2018.

- [14] M. R. Pazhouhandeh, M. Chang, T. A. Valiante and R. Genov, "Track-and-zoom neural analog-to-digital artifact rejection," *IEEE J. Solid-State Circuits*, vol. 55, no. 7, pp. 1984-1997, 2020.

- [15] A. E. Mendrela et al., "A bidirectional neural interface circuit with active stimulation artifact cancellation and cross-channel commonmode noise suppression," *IEEE J. Soulid-State Circuits*, vol. 51, no. 4, pp. 955-965, 2016.

- [16] J. P. Uehlin et al, "A single-chip bidirectional neural interface with high-voltage stimulation and adaptive artifact cancellation in standard CMOS," *IEEE J. Solid-State Circuits*, vol. 55, no. 7, p. 1-13, 2020.