# Design and Development of High Voltage High Pulse Power Supply using FPGA for **Dynamic Impedance Matching**

Krishna Kumar Rai,<sup>#,\*</sup> A.V. Giridhar,<sup>§</sup> D.R. Jahagirdhar<sup>%</sup> and Ashish Rai<sup>^</sup>

#DRDO - Center for High Energy Systems and Sciences (CHESS), Hyderabad - 500 069, India <sup>%</sup>DRDO - Research Centre Imarat (RCI), Hyderabad - 500 069, India ^DRDO – SF Complex (SFC), Hyderabad - 494 001, India <sup>§</sup>National Institute of Technology Warangal, Hyderabad - 506 004, India \*Email: kkrai.chess@gov.in

#### ABSTRACT

High Voltage High Pulse Power Supply (HVHPPS) is designed with the goal to match fixed load, so that precise pulse output can be achieved. Generally the loads involve magnetron, klystron, and particle accelerators etc. The HVHPPS output pulse shape changes with load impedance variation due to various reasons. Due to changes in impedance, the performance of Pulse Power Supply degrades and reflects the power at the source end which causes component failure and system shut down. To overcome such problems, a scale down High Voltage High Pulse Power is designed and developed to match the dynamic impedance variations upto 25 % of mismatch. In earlier days, all HVHPPS were designed using microcontrollers where the problem of pulse to pulse monitoring and computational speed was compromised. The availability of variable and self-defined, Field Programmable Gate Array (FPGA) controller, which provided flexibility to design the pulse to pulse shaping and various vital parameter monitoring, made it possible. This paper presents the design and implementation of HVHPPS over an FPGA platform to meet the fast response requirement. This paper provides a solution for impedance mismatch problems associated with such types of power supply, and also presents specifications for major components in a high voltage pulse power system for various types of load ranges. An experimental test hardware was designed and developed for HVHPPS to implement dynamic impedance algorithm and validate the results.

Keywords: FPGA; High voltage high pulse power supply; Impedance mismatch; Pulse shaping; Pulse forming network; Klystron

#### NOMENCLATURE

- Pulse Width

- $t_p Z_o L_n C_n T_q I_{in} I_{avg} V_o$ Characteristic Impedance

- Line Inductance

- Line Capacitance

- Time constant

- Peak Current

- Average Current

- Initial Voltage

# 1. INTRODUCTION

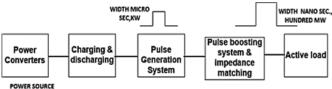

There are a wide range of applications of HVHPPS in commercial, industrial and defence sectors. There are two domains of application, one at low voltage low pulse power level and another at high voltage high pulse power. Basically, low voltage low pulse power is used in commercial and some sectors in industry whereas all military applications require High Voltage High Pulse Power Supply. HVHPPS uses a range of load (impedance) such as Magnetron, Klystron, Linear Accelerator, etc. Thus, efficient HVHPPS design and development is very essential.<sup>1</sup> The change in length of transmission line (Impedance) is due to temperature effect on microwave oscillator cavity dimensions, and dynamic Impedance characteristics of Amplifiers /oscillators. Impedance change in load will have an impact on the performance of HVHPPS i.e. back reflection & power loss. HVHPPS design is based on voltage fed series resonance pulse forming network which contains five blocks, as illustrated in Fig. 1.

#### Figure 1. Block diagram of high voltage high pulse power supply.

The HVPPS begins with power converters and ends at the interface with the active load. There may be more blocks of pulse formation based on the requirement of pulse width amplitude. HVHPPS in a compact form is always desirable for defense, space and commercial applications. High Voltage High Pulse Power System generates peak power for very short duration as a single pulse at a particular Pulse Repetition Frequency (PRF).2-3

Received : 11 May 2022, Revised : 28 October 2022

Accepted : 10 November 2022, Online published : 6 December 2022

# 2. DESIGN OF HIGH VOLTAGE HIGH PULSE POWER SYSTEM

All High Voltage High Pulse Power Supply systems have the problem of impedance mismatch. Hardware was therefore designed and developed to simulate the impedance mismatch and implement dynamic impedance matching.

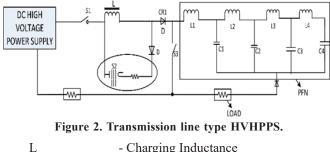

# 2.1 Transmission Line Type HVHPPS

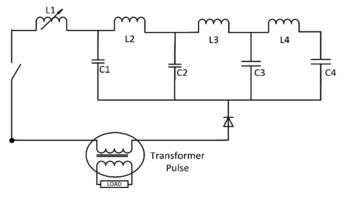

For proper pulse definition i.e., Pulse width, Pulse shape and pulse repetition frequency control, transmission line type of HVPPS is used and considered for design and development. As per the configuration shown in Fig. 2 the energy storage device is a lumped constant transmission line. These devices not only act as a source of electrical energy but also work as pulse shaping element i.e. Pulse Forming Network (PFN).<sup>4</sup>

| L              | - Charging Inductance           |

|----------------|---------------------------------|

| L1, L2, L3, L4 | - PFN Inductor                  |

| C1, C2, C3, C4 | - PFN Capacitor                 |

| S1             | - Controlled Switch             |

| S2             | - DeQ Switch                    |

| S3             | - Main Pulse discharging switch |

| L              | - Controlled Inductance         |

| C1             | - Capacitor                     |

| CR1            | - Diode                         |

| PFN            | - Pulse Forming Network         |

Table 1 represents the specification for hardware designed and developed as to implement impedance matching algorithm on FPGA.

Table 1. Specification of high voltage high pulse power supply

| Parameter                  | Value    |

|----------------------------|----------|

| Pulse Output Voltage       | 15kV     |

| Output Current             | 10A      |

| Pulse width (Variable)     | 4-10µsec |

| Pulse width (nominal)      | 6 µsec   |

| Repetition rate (Variable) | 10-400Hz |

| Load impedance( $R_1$ )    | 1500Ω    |

| Turns Ratio                | 1:11     |

# 2.2 Charging Circuit and Charging Inductor

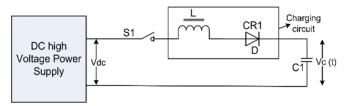

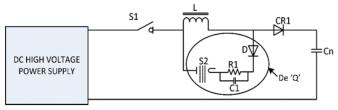

As per Fig. 3, when switch S is closed, current flows and charge the capacitor C1.

Due to resonance, a damped oscillation of current flows between L and C1.

Resonant time is  $T_c = 2\pi\sqrt{L1C1}$

Resonance charging transfers the stored energy in charging

inductor through CR1 (block the reverse flow of current) to capacitor C1 at voltage equal to twice that of DC High voltage supply.<sup>5</sup>

Figure 3. Resonance charging circuit.

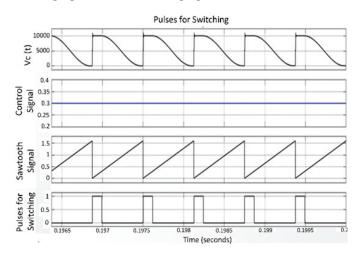

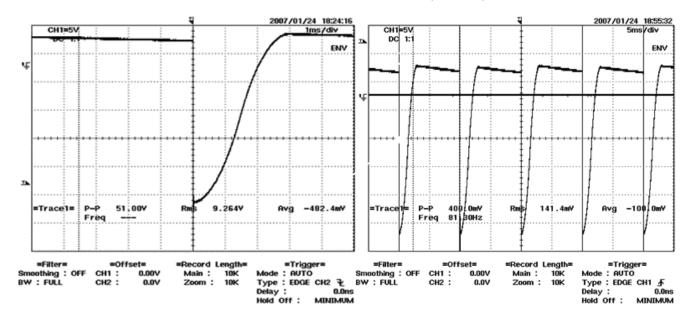

The maximum Pulse Repetition Frequency is the deciding factor for quiescent duration between two pulses. As per Fig. 4, once the charging inductor charges twice the input DC voltage, the main switches ON based on a comparison with sawtooth waveform and control signal. The main switch switches ON accordingly and energy stored in capacitor discharges as pulse across the load.

Charging time = period of resonance/2

Charging time,

$$T = \pi \sqrt{LC}$$

where, L is inductance of charging choke and C is capacitance of pulse forming network.<sup>6</sup>

We consider a charging time = 1.5msec, and Charging Inductor = 0.808H at 3kV.

Higher inductance of the charging choke causes slow rate of charging, thus inductor charging time increases.

Figure 4. Waveforms obtained from the controlling circuit.

### 2.3 Charging Diode

The main purpose of charging diode is to block the reverse flow of current which is connected in series as shown in Fig. 3. The number of diodes will be decided based on the requirement of reverse blocking voltage.

In this case, 6 fast recovery diodes each having a 500V reverse blocking voltage are considered to meet 3kV reverse blocking voltage capacity.

# 2.4 Novel Pulse Forming Network

In PFN system architecture, as shown in Fig. 5, we have to make assumption about the load nature i.e. whether it is static or dynamic and the required pulse power generation voltage.

(Primary Impedance)

$$Z_p = \frac{Z_s (\text{Seconday Load Impedance})}{N^2}$$

Pulse current of pulse transformer =  $\left(\frac{v}{R}\right)$

Thus the maximum transformer power is calculated by matching the pulse transmission line impedance to load impedance. The nature of pulse changes with the length of the transmission cable.<sup>7</sup>

Figure 5. Novel pulse forming network design.

The novel requisite pulse width for load is the deciding factor for the calculation of pulse forming network (PFN) parameters.

Thus, total capacitance of PFN,  $C_n = \frac{t_p}{2Z}$

where,  $t_p$  is pulse width; A, N and B should meet  $L_n$ . Normally

$Z_{o} = \text{Load Impedance which is already known, } Z_{o} = \sqrt{\frac{L_{n}}{C_{n}}}$  is the characteristic impedance of PFN.

To achieve dynamic impedance variance compensation of transmission line, the value of pulse forming network capacitance will always be 5-10 % higher than the calculated value.

The inductance required,  $L_n = Z_0^2 \times C_n$ . In case of air wound,

Inductance

$$L_n = \frac{0.2 \times A^2 \times N^2}{3A + 9B}$$

where, L= Inductance in  $\mu$ H, A= Mean dia of coil, B= length of coil, and N = number of turns.

Table 2. Calculated value of network parameters

| Network Parameter                         | Calculated Value |

|-------------------------------------------|------------------|

| Network Capacitance (Cn)                  | 0.24 µF          |

| C1 to C6                                  | 0.047 µF         |

| No. of capacitance                        | 06 Nos           |

| Network Inductance                        | 43.75 μH         |

| Mean dia of coil (A)                      | 2.75 Inch        |

| Length of coil (B)<br>Number of turns (N) | 24.5 Inch<br>82  |

As shown in Table 2, for all the calculated value of network parameters, the total number of section of L and C banks calculated on the basis of flatness percentage required for pulse shape is shown.

#### 2.5 Modified Decreasing Quality Factor

Pulse regulation achieved through DeQing switch S2 (Decreasing Q Factor) connected through RC network in Fig. 6.

Figure 6. DeQing switch circuit.

DeQ switching operation takes place when charging inductor voltage crosses the set charging value (user defined). During switching operation, excess energy stored in the inductor is dissipated in DeQ resistor.<sup>8</sup>

Decay time constant,

$$T_q = \frac{L_{charging choke}}{R_{deca}}$$

.

Pulse charging average current is represented as,  $I_{av} = \frac{CV}{T}$ .

Hence, Peak current I<sub>av</sub> through charging choke is represented

$I_{in} = \frac{\pi}{2} \times I_{av}.$

DC current flowing through the choke is represented as  $I_{d_0} = I_{u_0} \times dutyratio$ .

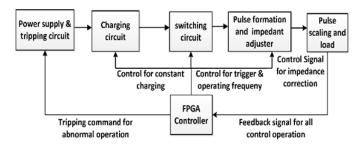

FPGA based controllers are always compact, more reliable, simpler and are part of emerging technology. FPGA based controller works in shielded environment for EMI and EMC protection. The block diagram of control architecture, power flow and logical operation of high voltage high pulse power system is shown in Figure 7. FPGA controls the charging requirement of the pulse forming network and the main switch operation. Further it controls the impedance matching and logical flow of power.

# Figure 7. Control architecture, power flow and logical operation.

To implement the control and impedance matching, pulse to pulse voltage is monitored through voltage compensation network and the same is used as a feedback for comparison with ideal pulse shape defined in the reference.<sup>9</sup> When pulse shape deteriorates due to positive and negative impedance mismatch beyond 10 % (acceptable limit defined by the user), a trip command is issued by the controller to stop output voltage generation.

# 2.6 Impedance Matching Algorithm Implementation

Pulse Forming Network has multiple sections of LC tank based on pulse width requirement. A novel technique is introduced to create an option for impedance matching at the source end. In this technique more numbers of inductance coils are created to meet the impedance matching requirement. The source voltage is sensed with the help of voltage sensor circuit. The sensed source voltage is given as the analog input to ADC of Virtex 6 FPGA board of Xilinx.

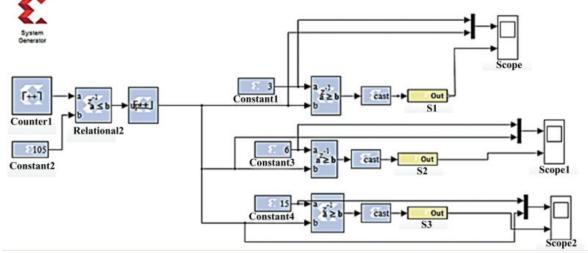

FPGA controller is of importance because it is used to provide gate pulses for switching MOSFET. The gate pulse of required width, which is found from simulation, is developed using FPGA controller that is used for generating the gate pulses for switching on MOSFET at a high frequency. Here the recurrence frequency used is of 1.6 kHz.

To develop the pulses of required width, the control scheme is developed in MATLAB using Xilinx blocks as in Figure 8. Counter gives either sawtooth or triangular waveforms by using up or up–down operational mode. The expression for selecting count value is shown in Eq.1 below:

$$Count value = \frac{f_{clock}}{f_{desired} x explicit period}$$

(1)

But the count value is limited by the number of bits with the relation  $2^{nbits}$  > count value. For example, if the count value is 210, then the minimum number of bits selected should be 8. The explicit period normally is very small. 1.6 kHz count frequency of saw tooth waveform generation with explicit value of approximately 10-6 is around 210. The clock frequency is made 1 when using system generator to match MATLAB simulation period. A constant value of half of the count value is compared to the saw tooth waveform obtained from the up counter block is of discrete type. So as to get 50% duty cycle of rectangular wave. Now it is applied to up-down counter saw tooth wave for which the signal increases linearly for high value and decreases linearly for low value. The up-down counter block a triangular signal was obtained. This was compared with a constant value selected based on the percentage of duty cycle needed to get the required gate pulse.

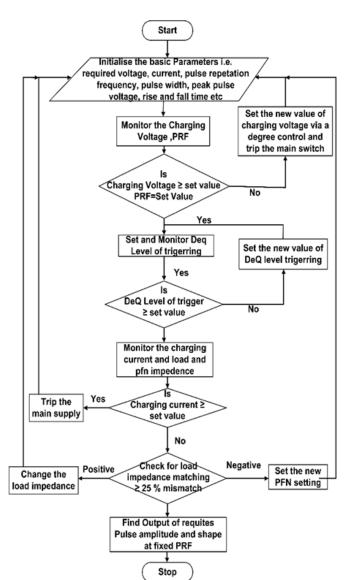

The generated reference signal was compared with a set value of requirement and switching signals were given to the devices through pulse amplification and isolation circuits. The flow chart in Fig. 9 indicates the algorithm implemented in FPGA working. The control signal varies based on the level of faults and level of impedance mismatch.

#### **Condition I: Negative Mismatch**

Case 1: if

$$Z_1 < Z_0$$

and  $Z_1 \approx 80$  % to 90 % of  $Z_0$

then  $V_{output} = 50$  % of  $V_{rated value}$

$PRF_{set} = 50\%$  of  $PRF_{max}$

- Case 2: if  $Z_1 < Z_0$  and  $Z_1 \approx 80\%$  to 75% of  $Z_0$ then  $V_{output} = 10\%$  of  $V_{rated value}$  $PRF_{set} = 10\%$  of  $PRF_{max}$

- Case 3: if  $Z_1 < Z_0$  and  $Z_1 > 75\% Z_0$ then trip command will be sent.

#### **Condition II: Positive Mismatch**

Case 1: if

$$Z_1 > Z_0$$

and  $Z_1 \approx 1.10$  to 1.20 of  $Z_0$

then  $V_{output} = 50\%$  of  $V_{rated value}$

PRF<sub>eet</sub> = 50% of PRF<sub>max</sub>

Case 2: if

$$Z_1 > Z_0$$

and  $Z_1 \approx 1.20$  to 1.25 of  $Z_0$

then  $V_{output} = 10\%$  of  $V_{rated value}$

PRF<sub>set</sub> = 10% of PRF<sub>max</sub>

Case 3: if  $Z_1 > Z_0$  and  $Z_1 > 1.25$  of  $Z_0$ then trip command will be sent.

There will be two conditions of mismatch problem i.e. Positive and Negative. In negative mismatch power will reflect back to source, which may cause system failure. To protect the vital components, the set high voltage and PRF should be reduced as per conditions mentioned above.

Figure 8. Simulink model to generate required pulses using FPGA.

Figure 9. Flow chart of FPGA programming.

# 3. PROTOTYPE HARDWARE OF HVHPPS AND ANALYSIS

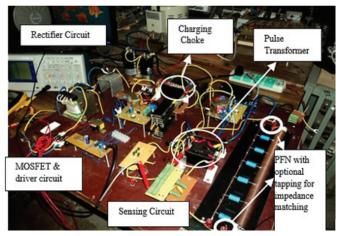

HVHPPS hardware created for 1.5 K $\Omega$  resistor connected through triple shielded cable impedance of 12.5  $\Omega$ .

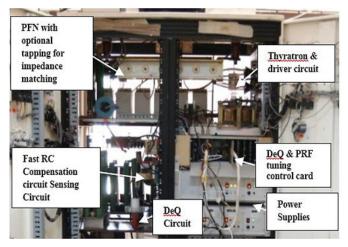

The detailed specifications of HVHPPS is given in Table 1. A scale down proof of concept hardware model was developed and control algorithm on FPGA implemented in High Voltage High Pulse Power generation for impedance matching. The same experiment has been proven on actual hardware was shown in Fig. 10 and the result was validated for establishing the functionality of the system.

Charging voltage produce due to resonance is observed through RC sensing circuit as shown in Fig. 11.

DeQ RC Network will not have more than 20 % power dissipation accordingly DeQ switching level adjusted. Thus constant charging voltage is maintained for each pulse to achieve the pulse regulation.<sup>10</sup>

PRF is controlled based on mismatch and fault conditions depending upon severity of fault, the PRF will automatically reduce from 50 % to 20 % of rated value.

Figure 10. Hardware of High Voltage High Pulse Power Supply (HVHPPS).

Figure 11. Charging voltage waveform.

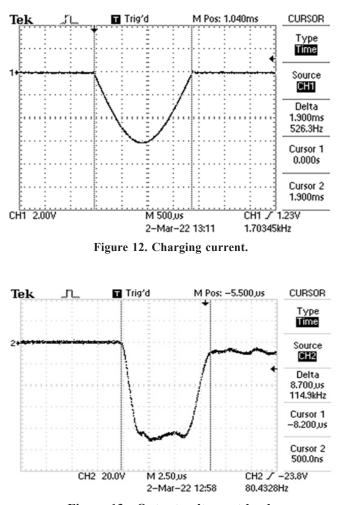

Figure 12 shows the charging current which is sensed by  $1\Omega$  resistor assembly. If output current rapidly increases due to arc, then overcurrent protection circuit turns off EHT supply.

The ferrite core pulse transformer is conservatively designed with bifilar winding.

Designed Prototype hardware gives 15kV pulse output voltage at secondary of pulse transformer (1:11) where primary voltage is 1.3kV. Figure 13 shows output voltage across resistive load of  $1.5k\Omega$ .

Figure 13. Output voltage at load.

The achieved output pulse is having two overshoots and one undershoot on flat top which will be due to mismatch of the load. In such cases flat pulse top can be achieved after PFN adjustment/ tuning.

#### 4. EXPERIMENTAL RESULTS AND ANALYSIS

Figure 14 shows the hardware of the High Voltage High Pulse Power Supply developed for implementation of impedance matching offline which delivers 15 kV, 10 - 400 Hz (selectable) frequency, approximately 10 A current (Primary of Pulse transformer) with 6 micro sec pulse duration for primary of pulse transformer, when the load is klystron microwave amplifier.

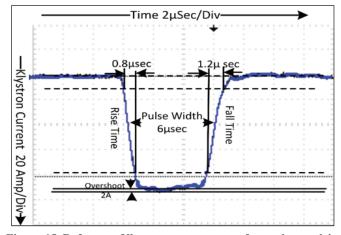

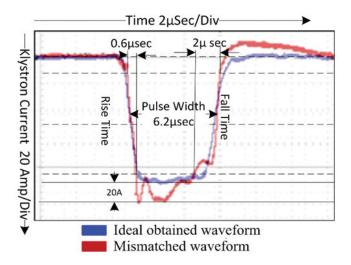

As shown in Fig. 15, a perfectly impedance matched klystron current waveform was observed during the experiment with manual taped change option created for impedance matching.

Figure 14. Actual hardware of High Voltage High Pulse Power Supply (HVHPPS).

Figure 15. Reference Klystron current waveform observed in perfectly matched condition.

The rise time, pulse width, fall time and overshoot of 8  $\mu$ sec, 6  $\mu$ sec, 1.2  $\mu$ sec and over shoot of 2A obtained respectively.

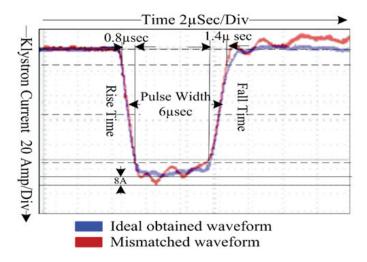

As per Fig. 16, overshoot of 8A was observed and 1.4  $\mu$ sec of fall time was obtained which was due to positive mismatch  $(Z_1 > Z_2)$  of PFN.

For pulse generated by PFN will be

$${}_{i(t)=\frac{V_0}{Z_0+R_1}} \begin{cases} 1-U(t-2\delta)-\frac{Z_0-R_1}{Z_0+R_1} [U(t-2\delta)-U(t-4\delta)] - \\ \frac{Z_0-R_1}{Z_0+R_1} [U(t-2\delta)-U(t-4\delta)] + \\ \left(\frac{Z_0-R_1}{Z_0+R_1}\right)^2 [U(t-4\delta)-U(t-6\delta)] + ..... \end{cases}$$

where,  $U(\Delta t) = 1$  for  $\Delta t > 0$  and  $U(\Delta t) = 0$  for  $\Delta t < 0$  $\Delta t = (t - n\delta), n = 2, 4, 6...$

Initial tapping of PFN increased i.e. line inductance was enhanced to compensate positive mismatch by adding the number of turns (Ln) to obtain the reference waveform for klystron.

Figure 16. Klystron current waveform with +ve mismatch.

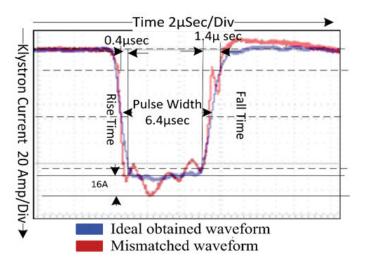

As per Fig. 17, Klystron output current showed negative mismatch ( $Z_1 < Z_o$ ) of upto 18 % of the reference value. This negative mismatch was detected and measured to give a suitable command for output voltage amplitude and frequency correction.

To compensate the overshoot, pulse width, fall time and rise time, PFN tapping at the trailing edge was done in such a way that some of the air wound coils (Ln) were eliminated from the PFN.

Figure 17. Klystron current waveform with -ve mismatch.

Figure 18 shows that when impedance mismatch is high the controller will work in time domain and issue corrective command based on deterioration of the output voltage pulse parameters.

After observation and comparative analysis with reference waveform, tripping command is issued by FPGA controller. Based on the mismatch condition the developed hardware option for impedance matching correction is utilized offline and impedance matching of PFN at the source end and finally ideal pulse as shown in Figure.15 is achieved, which is a perfectly impedance matched condition.

Figure 18. Klystron current waveform with highly mismatch.

# 5. CONCLUSION

A concept hardware was developed for compact high voltage high pulse power system which delivered 15kV and 10 amp pulse with a sharp fall and rise time in micro seconds. Sharp fall and rise time are achieved by using MOSFET and ferrite core pulse transformer. With appropriate control using Virtex FPGA controller, the output pulse can vary pulse repetition frequency from 10 Hz to 400 Hz and voltage can be achieved from 1 kV to 15 kV.

Impedance matching mechanism and algorithm were tested in scale down model. The same was implemented in actual hardware as klystron load (klystron amplifier of 6MW, 6 micro sec, and 0.001 duty cycle) and impedance matching tested. Offline impedance matching tuning mechanism was achieved.

In future, dynamic impedance matching can be thought of using servo control mechanism for online PFN tuning. Servo control mechanism will enable the HVHPPS to work in wide band as universal power supply.

# REFERENCES

- Akiyama, H.; Sakai, S.; Sakugawa, T. & Namihira, T. Invited Paper - Environmental applications of repetitive pulsed power. *IEEE TDEI*, 2007, 14(4), 825-833. doi: 10.1109/TDEI.2007.4286513.

- Li, H.; Yan, Z.; Zhang, C.; Wang, Y.; Gao, M. & Zou, G. Experimental study of inductive pulsed power supply based on multiple HTSPPT modules. *IEEE TPS*, 2016, 44(6), 950-956.

doi: 10.1109/TPS.2016.2558663.

- Carleto, N. & Motta, C.C. Design, construction and characterization of a line-type pulse modulator for driving high power magnetron. *In* SBMO/IEEE MTT-S International Conference on Microwave and Optoelectronics, 2005, pp. 330-333. doi: 10.1109/IMOC.2005.1580011.

- Rai, K.K.; Giridhar, A.V.; Jahagirdhar, D.R.; Rai, A. & Paul, A.K. Mathematical modelling and analysis of high voltage high pulse power supply performance on various loads. *In* 1st International Conference on Power

Electronics and Energy (ICPEE), 2021, pp. 1-5. doi: 10.1109/ICPEE50452.2021.9358787.

Wang, Y., *et al.* Design of series resonant high-voltage constant current power supply. *In* IEEE 4th Advanced Information Management, Communicates, Electronic and Automation Control Conference (IMCEC), 2021, pp. 471-475.

doi:10.1109/IMCEC51613.2021.9482281

- Wang, Q.; Gao, Y.; Liang, C. & Zhao, J. Design of series resonant high voltage capacitor charging power supply. *In* 16th IET International Conference on AC and DC Power Transmission (ACDC 2020), 2020, pp. 1294-1297. doi: 10.1049/icp.2020.0309.

- Ponomarev, A.; Korzhenevskiy, S.; Komarskiy, A.; Krasniy, O. & Chepusov, A. Power Supply for powerful generators with high pulse repetition rate. *In* 7th International Congress on Energy Fluxes and Radiation Effects (EFRE), 2020, pp. 315-316. doi: 10.1109/EFRE47760.2020.9242016

- Kim, J.H.; Park, C.G.; Ryoo, M.H.; Shenderey, S. J.; Kim, S. & Rim, G.H. IGBT stacks based pulse power generator for PIII&D. *In* IEEE Pulsed Power Conference, 2005, pp. 1065-1068.

doi: 10.1109/PPC.2005.300503

9. Jin, S.; Chen, J.; Li, Z.; Zhang, C.; Zhao, Y. & Fang, Z. Novel RDD pulse shaping method for high-power highvoltage pulse current power supply in DBD application. *IEEE TIE*, 2022, 1-1.

doi: 10.1109/TIE.2022.3140515

10. Zhou, L., *et al.* High overload power supply system and its energy synchronization control method for short-term

high-energy pulse load, *IEEE TSG*, 2022, **13**(2), 849-860.

doi: 10.1109/TSG.2021.3122442

# CONTRIBUTORS

**Mr Krishna Kumar Rai** is working as a Scientist in Center for High Energy Systems and Sciences, (DRDO), Hyderabad. He completed his MTech from IIT Rourkee.

In the current study he carried out literature survey, identified problem and carried out experiments and analysed the results.

**Dr Giridhar A.V.** received his doctorate from Indian Institute of Technology, Madras. Presently, he is Assistant Professor in the Department of Electrical Engineering.

In the current study, he carried out literature survey, identified the problem and validated results based on experiments.

**Dr D.R. Jahagirdhar** received his doctorate degree from Department of Electronics and Computer Science, University of Southampton, UK. He is working as a Scientist in Research Centre Imarat, DRDO, Hyderabad.

In the current study, he carried out experiments based on the problem identified for solving. He analysed the results.

**Mr Ashish Rai** completed his MTech (Microwave Electronics) from IIT (BHU). Presently he is working as a Scientist at Defence Research and Development Organization.

In the current study, he has designed the hardware, experimental test set up, and obtained the results and analysed them.