Samaneh Ammari

# NEURAL NETWORK ACCELERATOR DESIGN FOR SYSTEM ON CHIP

Master of Science Thesis Faculty of Information Technology and Communication Sciences Examiners: Prof. Timo D. Hämäläinen, Saman Payvar, M.Sc. October 2022

## ABSTRACT

Samaneh Ammari: Neural Network Accelerator Design for System on Chip Master of Science Thesis Tampere University Master's degree October 2022

ML is vastly utilized in a variety of applications such as voice recognition, computer vision, image classification, object detection, and plenty of other use cases. Protecting data privacy and the importance of preventing latency in different applications and saving the network bandwidth to process data locally without the need to transfer it to the cloud. The approach is called edge computing. It is challenging to design a deep learning accelerator suitable for edge devices. Two main factors affect the chip design. On-chip memory is the first and the most power and area-consuming unit. The second one is multipliers. In this thesis, we are focusing on the latter.

Most machine learning algorithms use convolution, which is calculated by multiplying and accumulating input feature maps and weights. Most of the deep learning accelerators use the precision scalable Multiply and Accumulate (MAC) architecture and an array of MAC units. Most of the chip's area is taken up by the array of MAC units, especially multipliers, which also use a lot of power.

This master's thesis consists of two parts. First, a new deep learning accelerator architecture is proposed. Second, different multiplier algorithms are explored. These algorithms were implemented in the SystemVerilog language and synthesized via Cadence tools. The aim was to find a smaller area and lower power consumption multiplier with higher performance. In this work, the Braun multiplier, the Booth multiplier, the Baugh-Wooley array multiplier, the Wallace multiplier, the Parallel prefix Vedic multiplier, and the Modified-Booth multiplier are implemented. The power consumption, chip area usage, and performance of the multipliers at different clock frequencies are measured and considered to select the optimal multiplier. Then the precision flexibility feature is added to the selected multiplier algorithms to perform one 8-bit\*8-bit, two 4-bit\*4-bit, or four 2-bit\*2-bit multiplication. It is worth mentioning that both data (multiplicand) and weight (multiplier) can be in different bit width ranges, such as 1,2,4,8. In the proposed deep learning accelerator, the area and power of the systolic array are measured and reported. Among all other multipliers, the signed flexible Modified Booth multiplier which can calculate 2,4, and 8-bits is selected. It occupies 866.461 um<sup>2</sup>, and consumes 0.653 mW power at 1 GHz. The area and power of the systolic array with bit precision flexible are 283,564 mm<sup>2</sup> and 223,156 mW power at 1 GHz, respectively.

Keywords: System on Chip, Embedded Systems, FPGA, ASIC, Machine Learning, Deep learning, Neural Network, Hardware accelerator, Deep learning accelerator

The originality of this thesis has been checked using the Turnitin Originality Check service.

## PREFACE

This work was done by a collaboration of Nokia Networks, and SoC-HUB, directed by Tampere University. It was my honor to be a part of this collaboration and work with wonderful people. I would like to thank all the people around me who helped me during my studies and work. Without your strong support, I couldn't have achieved this level of successful work.

I sincerely express my gratitude to my Professor Timo Hämäläinen for his advice, guidance, and support not only during my thesis work but also during my master's studies. A special thanks to Saman Payvar; you were always available regardless of your own deadlines. Thanks for providing valuable feedback on my thesis.

I want to thank my manager, Petri Uusi-Äijö who trusted in me and supported me during my studies and work. A huge thanks to my colleagues Tero Lehtinen, Tapio Mujunen and Tanja Viiru. Without your wonderful support and help, it would have been extremely difficult.

At the end, I would like to thank my family, who encouraged me with their love, and a big thanks to Reza Allahyarzadeh who was there for me during all the ups and downs of my studies.

Tampere, 1st October 2022

Samaneh Ammari

## CONTENTS

| 1. | Introduction                                                   |

|----|----------------------------------------------------------------|

| 2. | Background and motivation                                      |

|    | 2.1 Machine learning                                           |

|    | 2.1.1 Convolution                                              |

|    | 2.1.2 Training and inference                                   |

|    | 2.2 System on Chip and Embedded systems                        |

|    | 2.3 Relationship between System on Chip and Machine Learning 9 |

| 3. | Related work                                                   |

|    | 3.1 Deep Learning Accelerators                                 |

|    | 3.2 Multipliers                                                |

| 4. | Design principles of deep learning accelerator architectures   |

|    | 4.1 Data Movement                                              |

|    | 4.1.1 Data flow of the systolic array                          |

|    | 4.1.2 Dimension of the systolic array                          |

|    | 4.2 The network on chip of the systolic array                  |

|    | 4.3 Post processing                                            |

| 5. | Proposed deep learning accelerator architecture                |

|    | 5.1 CNN/RNN Core                                               |

|    | 5.1.1 MAC Unit: Multiplier and Adder                           |

|    | 5.1.2 Data Movement                                            |

|    | 5.2 DMA                                                        |

|    | 5.3 Control Unit                                               |

|    | 5.4 Global Buffer                                              |

|    | 5.5 Aggregation core                                           |

| 6. | Methodology                                                    |

|    | 6.1 Procedure                                                  |

|    | 6.2 Evaluation                                                 |

| 7. | Implementation of multipliers                                  |

|    | 7.1 Adders                                                     |

|    | 7.2 Multipliers                                                |

| 8. | Results and analysis                                           |

|    | 8.1 Multipliers and Adders                                     |

|    | 8.2 Exploring different Vedic multiplier implementations       |

|    | 8.3 Performance analysis of proposed deep learning accelerator |

|    |                                                                |

|      | 8.4 Comp    | arison of | f this v | work | w | ith | re | lat | ed | wo | ork | S | • |   | • | • | • |  | • |   |   | 49 |

|------|-------------|-----------|----------|------|---|-----|----|-----|----|----|-----|---|---|---|---|---|---|--|---|---|---|----|

| 9.   | Conclusion  | ns        |          |      |   |     |    |     |    | •  |     |   |   |   |   |   |   |  | • | • | • | 50 |

| Refe | erences     |           |          |      |   |     |    |     |    | •  |     | • |   | • |   |   |   |  | • |   |   | 51 |

| Арр  | endix A: Ap | opendix   |          |      |   |     |    |     |    | •  |     | • | • |   |   |   |   |  | • |   |   | 58 |

|      | A.1 Syste   | mVerilog  | Code     | es.  | • |     |    |     |    | •  |     | • |   |   |   |   |   |  | • |   |   | 58 |

|      | A.1.1       | Modified  | d Boo    | th.  | • |     |    |     |    | •  |     | • |   |   |   |   |   |  | • |   |   | 58 |

|      | A.1.2       | Vedic m   | ultipli  | er.  |   |     |    |     |    | •  |     | • | • |   |   |   |   |  | • |   |   | 65 |

## LIST OF FIGURES

| 1.1 | Ballast SoC with proposed deep learning accelerator design | 2  |

|-----|------------------------------------------------------------|----|

| 2.1 | Taxonomy of Artificial intelligence                        | 4  |

| 2.2 | Deep CNN Example of classification application             | 5  |

| 2.3 | Two common platform structures for ML                      | 11 |

| 3.1 | Visual comparison of Table 3.1                             | 14 |

| 4.1 | Roofline Model for selecting the number of MAC operation   | 20 |

| 4.2 | Common Network on Chip                                     | 21 |

| 4.3 | Different layers of Neural Network                         | 22 |

| 5.1 | Top level overview of proposed the DL accelerator          | 23 |

| 5.2 | MAC unit structure                                         | 24 |

| 5.3 | Data movements between major blocks                        | 26 |

| 6.1 | Methodology flow                                           | 30 |

| 7.1 | Multiplication of two 4-bit number                         | 32 |

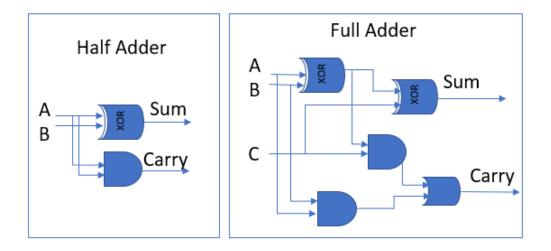

| 7.2 | Logic circuit diagram of Half adder and full adder         | 33 |

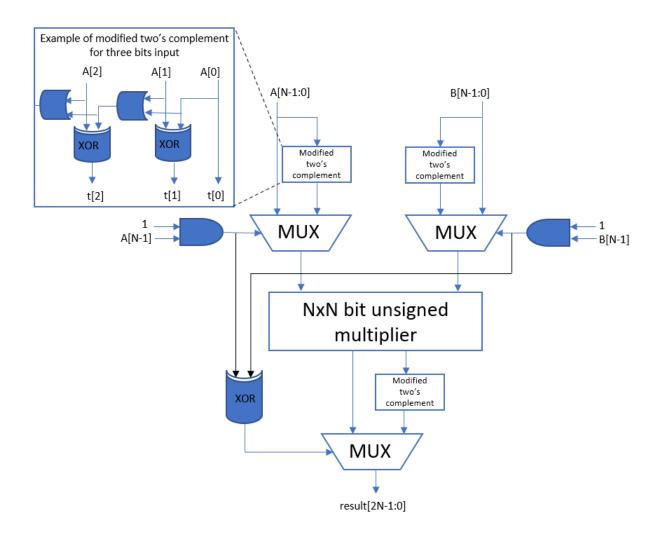

| 7.3 | Signed multiplication                                      | 35 |

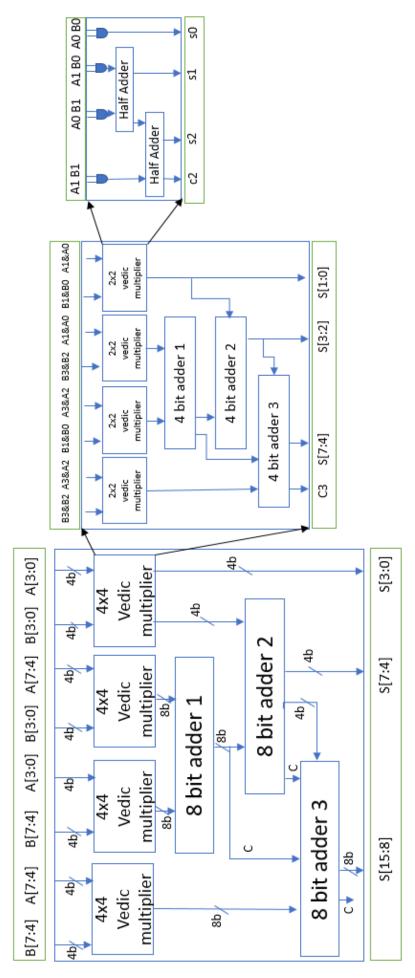

| 7.4 | Vedic multiplier                                           | 36 |

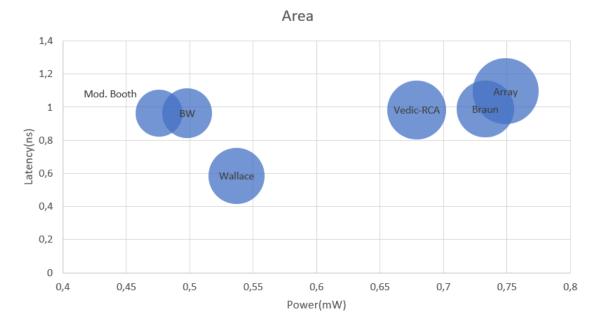

| 8.1 | Area, Power, and Latency of Table 8.1 visualized           | 38 |

| 8.2 | Area, Power, Latency, and Fan-out of Table 8.2 normalized  | 39 |

| 8.3 | Maximum clock frequency that a multiplier can perform      | 40 |

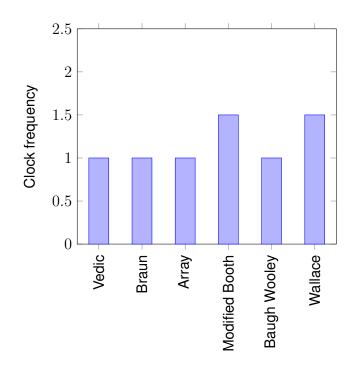

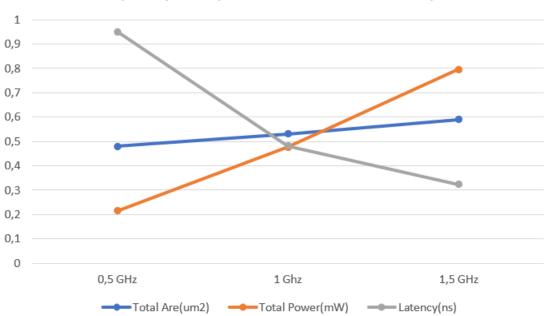

| 8.4 | Normalized values of Table 8.7                             | 43 |

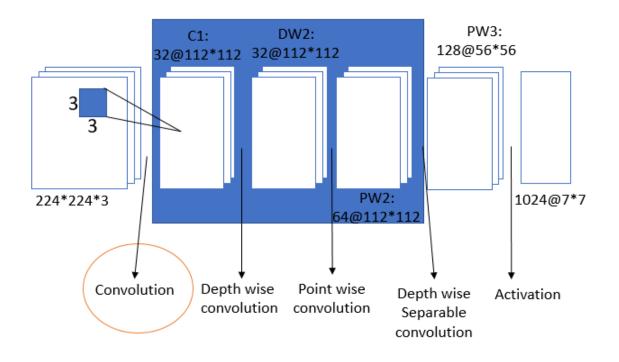

| 8.5 | Basic illustration of simple MobileNet layer               | 44 |

| 8.6 | Data movements between IPs for MobileNet NN model          | 46 |

| 8.7 | The latency to execute one layer                           | 47 |

## LIST OF TABLES

| 2.1 | Neural networks and some of their common use cases                            | 6  |

|-----|-------------------------------------------------------------------------------|----|

| 2.2 | Summary of popular neural network models in ImageNet-1k only                  | 6  |

| 2.3 | Comparison of various chip platforms                                          | 9  |

| 3.1 | The comparison of DNN accelerators                                            | 12 |

| 3.2 | Sorting Table 3.1 by Performance per power consumption                        | 14 |

| 3.3 | Related works with CNN-RNN architecture at 200 MHz frequency                  | 15 |

| 3.4 | Computation requirements                                                      | 16 |

| 3.5 | Comparison in the number of MAC/PE, area; ASIC platform                       | 17 |

| 8.1 | Area, Power, Latency, and average Fan-out of 8-bit signed multipliers         | 37 |

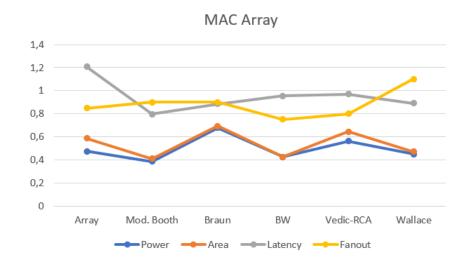

| 8.2 | Area, Power, Latency, and average Fan-out of various MAC array                | 38 |

| 8.3 | Area, Power, Latency, and average Fan-out of flexible bit width multipliers . | 40 |

| 8.4 | Comparison of 8-bit implementation of adders                                  | 41 |

| 8.5 | Area consumption of 8-bit signed Vedic multipliers                            | 42 |

| 8.6 | Performance and power consumption of 8-bit signed Vedic multipliers           | 42 |

| 8.7 | Area and power of Modified Booth multiplier at different frequency            | 43 |

| 8.8 | The comparison of proposed DL Accelerator with other                          | 49 |

## LISTINGS

| 2.1  | Standard convolution                          | 7           |

|------|-----------------------------------------------|-------------|

| 2.2  | Depth-wise convolution                        | 7           |

| 2.3  | Point-wise convolution                        | 7           |

| 4.1  | Weight stationary                             | 9           |

| 4.2  | Output stationary                             | 9           |

| 4.3  | Input stationary                              | 9           |

| 8.1  | Python code of a simple MobileNet model       | 15          |

| A.1  | Modified Booth multiplication                 | 58          |

| A.2  | 4-bit Modified Booth multiplication           | ;2          |

| A.3  | 2-bit Modified Booth multiplication           | 33          |

| A.4  | Flexible Modified Booth signed multiplication | ;4          |

| A.5  | Example of signed multiplication              | 35          |

| A.6  | 8-bit Vedic multiplier                        | <b>\$</b> 7 |

| A.7  | 4-bit Vedic multiplier                        | 38          |

| A.8  | 2-bit Vedic multiplier                        | '0          |

| A.9  | Ripple carry adder                            | '1          |

| A.10 | Flexible Vedic multiplier                     | '2          |

## ABBREVIATIONS

- AI Artificial Intelligence

- APU AI Processing Unit

- ASIC Application Specific Integrated Circuit

- AXI Advanced eXtensible Interface

- BK Brent-Kung

- BN Batch Normalization

- CLA Carry Look Ahead adder

- CLK clock

- CNN Convolutional Neural Network

- CPU Central Processing Unit

- CSA Carry Select Adder

- DDR Double Data Rate

- DL Deep Learning

- DLA Deep Learning Accelerator

- DMA Direct Memory Access

- DNN Deep Neural Network

- DRAM Dynamic Random Access Memory

- DWC Depth-Wise Convolution

- FC Fully Connected

- FPGA Field Programmable Gate Array

- GAN Generative Adversarial Networks

- GOPS Giga Operation Per Seconds

- GPU Graphics Processing Unit

- IDE Integrated Development Environment

- ILSVRC Large-Scale Visual Recognition Challenge

- IoT Internet of Things

- IP Intellectual Property

| KS   | Kogge-stone                         |

|------|-------------------------------------|

| LSTM | Long Short-Term Memory              |

| LTU  | Linear Threshold Unit               |

| MAC  | Multiply and Accumulate             |

| ML   | Machine Learning                    |

| MLP  | Multi-Layer Perceptron              |

| MSB  | most significant bit                |

| MSIC | ML-specific Integrated Circuit      |

| NN   | Neural Network                      |

| NoC  | Network on Chip                     |

| NPU  | Neural Processing Unit              |

| OPS  | Operation Per Seconds               |

| PE   | Processing Element                  |

| PPA  | Parallel Prefix Adder               |

| PWC  | Point-Wise Convolution              |

| RCA  | Ripple Carry Adder                  |

| RELU | Rectified Linear Unit               |

| RNN  | Recurrent Neural Network            |

| RTL  | Register Transfer Level             |

| SIMD | Single Instruction, Multiple Data   |

| SMVM | Sparse Matrix Vector Multiplication |

| SRAM | Static Random Access Memory         |

| TOPS | Tera Operation Per Seconds          |

| TPU  | Tensor Processing Unit              |

|      |                                     |

- UNPU Unified Neural Processing Unit

- VLSI Very Large Scale Integration

- WNS Worst Negative Slack

## 1. INTRODUCTION

Recent studies indicate that Machine Learning (ML) algorithms provide considerable benefits, especially in the internet of things (IoT) and edge devices (low-power mobile applications). Edge devices have sensors or actuators that gather data, and instead of transmitting data to the data center for processing and analysis, all the computation could be conducted at the edge. The power and memory capacity of edge devices are limited. Thus, it is challenging to use ML algorithms on edge devices. However, due to data privacy and latency concerns, the demand on using Deep Learning (DL) algorithms on edge devices is increasing.

Several studies have been conducted on designing efficient hardware accelerators. As in ML, especially DL, there is a set of repetitive computations. A collection of specialized hardware is used to do these computations faster and more energy efficient. This set of hardware is generally called a Deep Learning Accelerator (DLA), Neural Processing Unit (NPU), or AI Processing Unit (APU). They are optimized for performing a specific task. There are three aspects to DLA: data reuse ability, fixed computational patterns, and fast memory access. For these reasons, the DL Accelerator designs are moving towards non-von Neuman architectures. It enables the increase of parallelism with the high number of Processing Elements (PEs) utilization.

The goal of this master's thesis is to study and propose the most effective Very Large-Scale Integration (VLSI)-based DL accelerator. The suggested DL accelerator is one of the subsystems in a larger System on Chip (SoC) named Ballast [1]. The proposed DL accelerator will replace the Ballast chip's current DL accelerator. The objective is to introduce a novel DL accelerator that consumes less area footprint and reduces power consumption, while improving performance. Our design strives to be suited for edge devices. The aim of this master's thesis is to investigate the design principles of the DL accelerator and improve every aspect of the design that can be optimized. The focus is on the arithmetic part of the DL subsystem, as it is the bottleneck of the main process. For that reason, different types of multipliers are implemented and compared. The aim is to select the multipliers that are as fast as the critical path of the whole chip. The final hardware architecture should be able to do both standard convolutions and depth-wise separable convolutions.

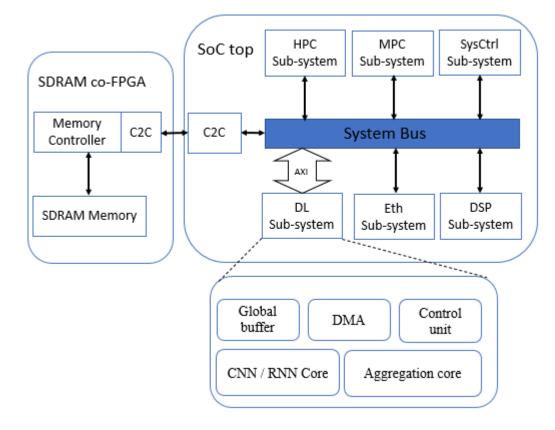

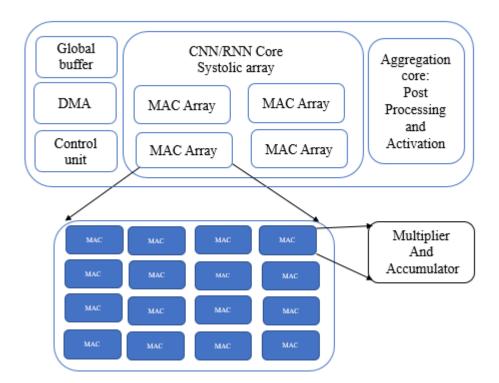

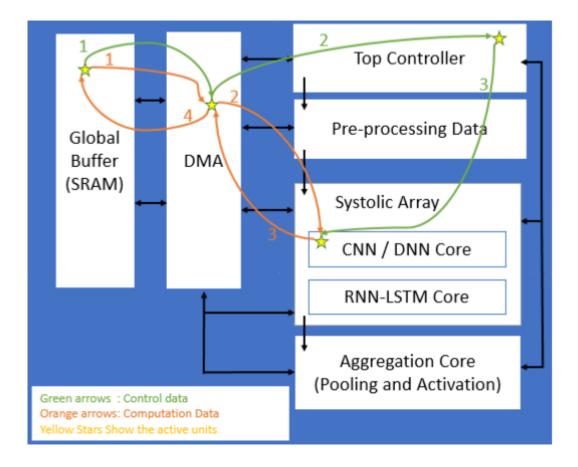

Figure 1.1 demonstrates a general overview of the Ballast SoC. Besides that, it illustrates the structure of the proposed DL architecture. It consists of Direct Memory Access (DMA), a global buffer, a control unit, a systolic array, and an aggregation core. Other members of the team implement certain components of the DLA. This thesis work focuses on selecting the needed components for the DL accelerator and discussing the reasons behind the selection of different features. Furthermore, it discusses the arithmetic part of DL and how to do the convolution. Finally, it evaluates the different multipliers to determine a fast, energy-efficient, and area-efficient way to do these computations.

Figure 1.1. Ballast SoC with proposed deep learning accelerator design

The thesis work comprises nine chapters. The second Chapter 2 explains the basic concepts that readers with different backgrounds might need. The third Chapter 3 evaluates related works. This thesis consists of two main parts. First, Chapter 4 defines the deep learning design principle, followed by Chapter 5, which proposes a hardware accelerator for edge computing use cases, enabling specific deep learning algorithms. It explains the different parts of the proposed deep learning accelerators and the reason for implementation. Second, Chapter 6 and 7 describe the procedure, techniques, and implementation of different multipliers and adders, respectively. Chapter 8 compares and evaluates different multipliers in terms of the area and power consumption of the DL subsystem. In the last Chapter, 9 the conclusion is discussed.

## 2. BACKGROUND AND MOTIVATION

This chapter provides a concise explanation of the fundamental principles necessary to comprehend the context. The first segment focuses on machine learning. The second part briefly introduces SoC and embedded systems, followed by a discussion of the significance of the link between ML and SoC in the third section.

#### 2.1 Machine learning

Neural Network (NN) refers to the approach used to design a computer to function similarly to human brains. The name of the NN was inspired by neurons in the human brain. ML is a branch of AI focused on building models and training them with sample data for specific tasks without being explicitly programmed. Supervised and unsupervised learning are the two main types of machine learning. In a nutshell, supervised learning is suitable when the data source is structured, and the model is known. Regression and classification are techniques for supervised learning. Classification can predict a label, whereas regression can predict a quantity.

It is important to specify the following usage cases. The examples of regression would be the agricultural industry for predicting the effect of fertilizers and water on plants, house pricing prediction, and medicine to predict the relationship between blood pressure and drug dosage. In addition, examples of classification applications include the categorization of spam and non-spam emails and the classification of soil and crops. In contrast, unsupervised learning is used for unstructured source of data to discover hidden structures in the data. Products or customer segmentation, and similarity detection are some of the common use cases [2].

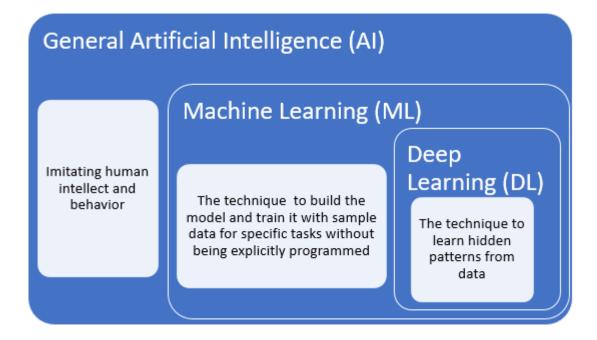

Deep learning is one of the most effective machine learning techniques. It uses a neural network to execute complex calculations on big data. Figure 2.1 illustrates the hierarchy between AI, ML, and DL. It is part of ML while it is a subset of AI. Having several layers of neural networks has a significant improvement in ML. There are various types of DL methods, such as Deep Neural Networks (DNNs), Convolutional Neural networks (CNN), Recurrent Neural networks (RNN), Multi-Layer Perceptron (MLP), Linear Threshold Unit (LTU), Generative Adversarial Networks (GAN), Autoencoder, Distributed Learning, Transformer, Deep Feedforward Network, Training Feedforward Network, etc.

Figure 2.1. Taxonomy of Artificial intelligence (AI)

Brief descriptions of the three most prevalent neural networks are provided below.

CNN is among the most prominent NN models. It is derived from the mathematical idea of convolution, which is the process of computing the integral of two functions while the shape of one of them is modified and shifted. CNN can extract specific features or patterns. Briefly, in each convolution, the filter slides over the input to detect special patterns such as corners, edges, lines, objects, texture, shape, etc. For instance, a filter that can identify objects is known as an object detector. A CNN comprises of three main layers: an input layer, hidden layers, and an output layer. All layers between an input layer and output layer are called hidden layers. Typically, it also has a Fully Connected (FC) layer and a pooling layer. Each layer contains a set of neurons that have specific weights and biases. The convolution layer applies the filter to an input. As a result, a feature map is produced. If the same filter is applied repeatedly to the input, it will produce the feature map. The ability to learn many filters in parallel is the most important innovation of CNN. LeNet [3], AlexNet [4], VGGNet [5], GoogLeNet [6], ResNet [7], and ZFNet [8] are famous variation of CNN models. These kinds of models are mostly applied to computer vision applications.

Remembering the past states is a unique feature of RNN. These memories are stored in special nodes. Each node gets the data and the previous state as inputs. In addition, the output relies on the input and the previous computation. One of the most well-known RNNs is Long Short-Term Memory (LSTM). This kind of network is efficient when historical characteristics are crucial for making a choice. It dominates predictive

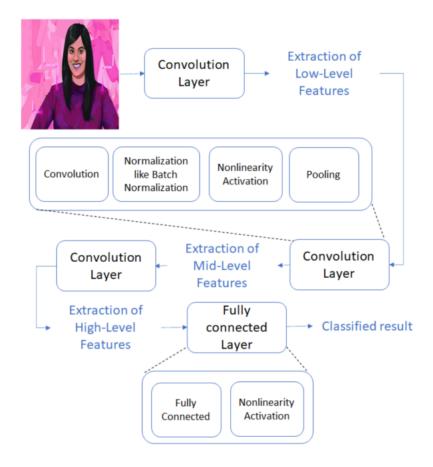

Figure 2.2. Deep CNN Example of classification application

applications like as the stock market, speech recognition, and language modeling.

DNNs have more than one layer between input and output. It extracts features from the huge amounts of data available without human interaction. Collective layers are cascaded to extract the feature. The most common NN layers are convolution, FC, activation function, and pooling. Figure 2.2 demonstrates the general process of DL neural networks as an example in image classification. Usually, the input is an image with a dimension of 256\*256 pixels, 128\*128 pixels, or sometimes a reduced size to save some calculations. The ML model trains with the available datasets to produce weights or kernels. In other words, a filter is created during the training. Filters can be programmed to detect features like straight edges, simple colors, and curves. The kernel convolves over the entire area of input image features to extract the features.

Each of these techniques is suitable for specific applications. Generally, ML utilization shows considerable improvement in computer vision tasks, speech recognition, robotics, self-driving cars, detecting cancer, playing complex games, and so on. NN algorithms may be suitable for more than one application. In these cases, insightful evaluation of NN algorithms determines which of them would be most suitable and provides the highest accuracy for a given application. Some of the applications for different NNs are shown

| CNN-DNN                     | RNN-LSTM                               |  |  |  |  |

|-----------------------------|----------------------------------------|--|--|--|--|

| Image segmentation          | Trend Forecasting                      |  |  |  |  |

| Image classification        | Detecting Anomalies                    |  |  |  |  |

| Medical image analysis      | Generating Image Descriptions          |  |  |  |  |

| Image and video recognition | Language Modelling and Generating Text |  |  |  |  |

| Natural Language processing | Speech Recognition                     |  |  |  |  |

| Search engine               | Video Tagging                          |  |  |  |  |

Table 2.1. Neural Networks (NN) and some of their common use cases

in the table 2.1 below. The focus of this master's thesis is mostly on supporting the DNN. The main reason is that it can widely support so many applications.

Table 2.2 demonstrates the comparison of the different NN models in terms of the number of parameters and top-1 accuracy based on the ImageNet dataset [9]. The top-1 accuracy rate is a factor for the ground truth against the first predicted class. Another good factor for comparison is the top-5 error rate, which compares the ground truth against the first five predicted classes. According to the table 2.2, the MobileNet model gives high accuracy, despite the low number of parameters. MobileNet is suitable for computer vision tasks and requires less computation.

| Model                  | Number of parameters | Top-1 Acc ImageNet (%) | Year |

|------------------------|----------------------|------------------------|------|

| AlexNet [10]           | 60M                  | 63.3                   | 2012 |

| VGG16 [5]              | 138M                 | 74.4                   | 2014 |

| GoogLeNet [6] [11]     | 4M                   | 68.3                   | 2015 |

| ResNeXt-101(64x4) [12] | 83.6M                | 80.9                   | 2017 |

| Xception [13]          | 23M                  | 79                     | 2017 |

| MobileNetV3 [14]       | 5.4M                 | 75.2                   | 2019 |

| InceptionV3 [15]       | 24M                  | 78.95                  | 2020 |

Table 2.2. Summary of popular NN models in ImageNet-1k only

## 2.1.1 Convolution

Convolution is the heart of CNN and DNN; It extracts features by convolving the trained filters on input feature maps. There are different types of convolutions, for example, direct convolution, 1D convolution, and depth-wise separable convolution. To illustrate the mathematical complexity of convolution, let's examine the definition of direct convolution. As the equation 2.1 standard convolution demonstrates, there is very much multiplication. The input feature map (i) has height (H), width (W), and the filter (f) is

represented with height (R), width (S). The number of input channels as parameters (C) is the same in both input activation and filter. The output feature map (o) has height (P), width (Q), and biases (b), batch size (n) and given stride size (U) are the parameters used to show the convolution. Standard convolution [9]:

$$O_{[p][q][m][n]} = \left(\sum_{c=0}^{C-1} \sum_{r=0}^{R-1} \sum_{s=0}^{S=0} i[n][c][U_p + r][U_q + s] * f[m][c][r][s]\right) + b[m]$$

$$0 \le n < N, \quad 0 \le m < M, \quad 0 \le p < P, \quad 0 \le q < Q,$$

$$P = (H - R + U)/U, \quad Q = (W - S + U)/U$$

$$(2.1)$$

A simple pseudo code in Listing 2.1 depicts how standard convolution works.

```

for r = [0:R]:

for s = [0:S]:

for p = [0:P]:

for q = [0:Q]:

for c = [0:C]:

for m = [0:M]:

for n = [0:N]:

output[p][q][m][n] += Weight[r][s][m][c] * Input[p+r][q+s][c][n];

Listing 2.1. Standard convolution

```

Corresponding for loops in listing 2.2 illustrate depth-wise separable convolution, which consists of Depth-Wise Convolution (DWC) and Point-Wise Convolution (PWC), in other words, the filtering stage and combination stage. It is the feature of the MobileNet NN [16].

```

for n = [0:N]:

for c = [0:C]:

for r = [0:R]:

for s = [0:S]:

for p = [0:P]:

for q = [0:Q]:

output[p][q][c][n] += Weight[r][s][1][c] * Input[p+r][q+s][c][n];

Listing 2.2. Depth-wise convolution

```

```

for p = [0:P]:

for q = [0:Q]:

for m = [0:M]:

for c = [0:C]:

for n = [0:N]:

output[p][q][m][n] += Weight[1][1][m][c] * Input[p][q][c][n];

Listing 2.3. Point-wise convolution

```

#### 2.1.2 Training and inference

Training and inference are two fundamental concepts in ML. Training indicates the process of producing the NN model. In this process, a DNN learns how to analyze a set of data and make decisions. Inference, on the other hand, applies the generated ML model to novel data to anticipate the outcomes [17].

It is noteworthy to mention some well-known datasets and DNN algorithms. Usually, these datasets are used to train a NN model. The three most available datasets are MNIST, CIFAR-10, and ImageNet. Their complexities increase in the same order. ALexNet [4], GoogLeNet [6], ResNet [7], are popular DNNs that won the Large-Scale Visual Recognition Challenge (ILSVRC) in image classification in 2012, 2014, and 2015, respectively.

There are some open source ML frameworks for training and inferences, such as TensorFlow [18], Pytorch [19], Keras [20], Caffe [21] and Microsoft Cognitive toolkit. These mentioned frameworks are used to train the NN Model.

#### 2.2 System on Chip and Embedded systems

Embedded systems play an essential role in our lives. There is a good chance we are already using multiple embedded systems in our daily lives, and they can be found in cars, home appliances, digital watches, etc. In general, an embedded system is a term describing a computer system combining both hardware and software designed to perform a dedicated function, which can be part of a larger system, hence embedded in it. This system can utilize multiple embedded processors, such as a System on Chip (SoC), Field Programmable Gate Array (FPGA), microcontrollers, and some electronic components.

An SoC is an integrated circuit (IC) that combines many components of an electronic system into one chip, such as the Central Processing Unit (CPU), Graphics Processing Units (GPU), memory interfaces, input/output interfaces, and may contain digital, analog, or mixed signals and often signal processing units. An SoC could be designed for special use cases or functions such as fast data processing or edge computing and may include special accelerator units such as Tensor processing units (TPU) [18].

An Application Specific Integrated Circuits (ASIC) and a FPGA are the ideal choices when designing hardware for a particular task. The significant advantage of them is customization for specific needs. In contrast to ASIC, FPGA allows clients or users to change designs after manufacturing.

However, Custom ASIC has many advantages to mention compared to the CPU, GPU, FPGA, and other types of computing systems. ASICs, on the other hand, have a

few drawbacks, including a long time to market due to the lengthy design, research, and development process, whereas FPGA is appropriate when time to market is critical. However, the power consumption of FPGA products is much higher than ASICs, especially on edge devices and mass-produced IoT. Table 2.3 compares the characteristics of different kinds of computing systems.

| Characteristic    | CPU   | GPU       | ASIC | FPGA      |

|-------------------|-------|-----------|------|-----------|

| Development cost  | Low   | Low       | High | Medium    |

| Unit cost         | High  | High      | Low  | High      |

| Time to Market    | Short | Medium    | Long | Medium    |

| Flexibility       | High  | Medium    | Low  | Very High |

| Power consumption | High  | Very High | Low  | Medium    |

Table 2.3. Comparison of various chip platforms

It is essential to remember that the appropriate hardware solution is chosen in accordance with the application, time to market, and design criteria. It is possible to categorize most DL accelerator designs between general-purpose architectures like GPUs and CPUs and neuromorphic architectures like [22].

With the development of technology, the need for smart, portable gadgets increases. In edge devices, local memory processing and power consumption are bottlenecks. Hence, there is a need to develop either specific hardware for each unique task or flexible hardware. Thus, it is possible to have optimal hardware that can perform the same assignment much faster. It is recommended to design specific hardware to get the best performance and accelerate the speed of computation.

### 2.3 Relationship between System on Chip and Machine Learning

With the most recent breakthroughs in information technology, ML has found opportunities to expand in several technologies. Nowadays, ML is being applied extensively in industrial and edge processing, such as speech recognition, computer vision, image classification, object detection, and many other use cases. There are numerous ML algorithms, like state-of-the-art DNNs. Even though DNNs predict the results with high accuracy, they introduce high computational complexity. It is possible to deploy ML algorithms on different hardware platforms; the cloud, GPUs, CPUs, FPGAs, and ASICs are the most famous hardware platforms.

SoCs and ML can become related in two ways. Either ML is used to design an SoC or design an SoC for a specific ML application. The emphasis here is on the latter. There is a tradeoff among various hardware platforms. The platform is selected based on the application requirements.

However, the tendency to process data locally is increasing to protect data privacy, especially in edge applications. In some use cases to prevent fraudulent activities, hacking, phishing, and identity theft, the cloud is not a viable option. On the other hand, CPUbased platforms are insufficient for parallel computing, which DNNs need. They support several instructions sets, and multiple access to external memory per instruction has a negative effect on power consumption, although there are only a few repetitive instruction sets needed for specific tasks.

GPUs are commonly utilized for accelerating ML algorithms. GPU-based platforms are much better than CPUs at deploying DL. GPU's multiple cores provide astonishingly fast, highly parallel computations. GPU-based platforms can have high throughput, but they use too much power to be useful for edge devices. [23] has compared FPGAs against other hardware platforms. According to their research, FPGAs and ASICs surpass GPUs and CPUs in terms of energy efficiency and performance. Moreover, ASICs rise above all of them.

[24] compares hardware options for neural network acceleration in terms of power efficiency and the number of processing units. According to the book, ASICs and FPGAs with customized compute logic have higher power efficiency than GPUs with single instruction, multiple data executed for general-purpose computing. And the CPU with a few cores for mobile/edge has the lowest power efficiency.

The DNN algorithms on GPUs with the Von-Neumann architecture are computationally more costly than the ASIC's design. Nowadays, the trend is to use the ASIC platform for ML, especially for DNNs. As the number of weight parameters is high in the DNN algorithms, it demands data movement between the processing unit and memory, which is expensive due to latency and energy consumption caused by the memory wall. DLA's design is shifting toward Non-von Neumann architecture to support parallelism. As a result, it enables fixed memory access and computational patterns with deterministic data reuse-ability, and it is easy to increase parallelism with more PE utilization.

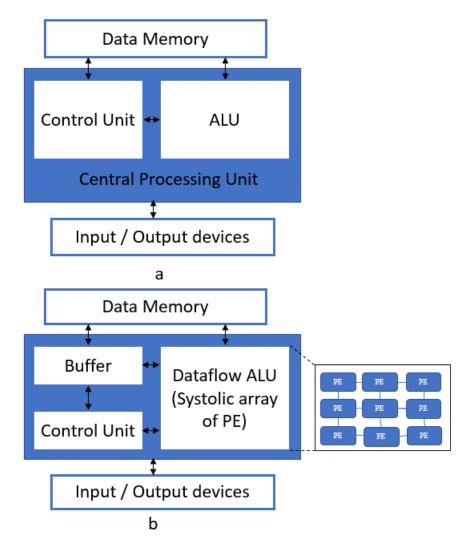

General purpose processors such as CPU and GPU have Von Neumann architecture like figure a in 2.3. These kinds of processors consume a considerable amount of power, and they are not suitable for low-power edge devices. On the other side, by implementing the non-von Neumann architecture or even computing in memory, it is possible to carry out higher performance, energy efficiency, and cost-effective platforms. As a result, DL accelerators designed by FPGAs or ASICs follow a semi-spatial structure like in figure b 2.3. Therefore, as ML develops quickly, hardware architecture should be designed to support ML computation. There is a need for a hardware architecture to execute the highly computational neural network algorithms fast. The spatial hardware architecture helps to increase the speed of computations. This can happen by bringing memory near the computation unit or inside it. Thus, there will be less latency for transferring the data

*Figure 2.3.* Two common platform structures for ML: a) General purpose processors b) Common spatial architecture

between different units.

ML is all about computation, and it consumes considerable amounts of power. But the power source is limited to edge devices. Thus, it is challenging to design an ML accelerator that consumes a smaller amount of energy. According to [25], Moore's law is going toward the end. Power becomes a key factor. Therefore, to have a faster processor instead of a general-purpose processor, build a more heterogeneous architecture that only does one specific task. The software-centric, hardware-centric, and combination approaches are the ones suggested. So, there is a need to employ domain-specific hardware in a computing system and use the hardware and software co-design to boost performance. In other words, to do co-design, the proposed DL accelerator is designed for a specific NN algorithm. In this thesis, the MobileNet algorithm [16] is selected as it can cover many applications of ML.

## 3. RELATED WORK

### 3.1 Deep Learning Accelerators

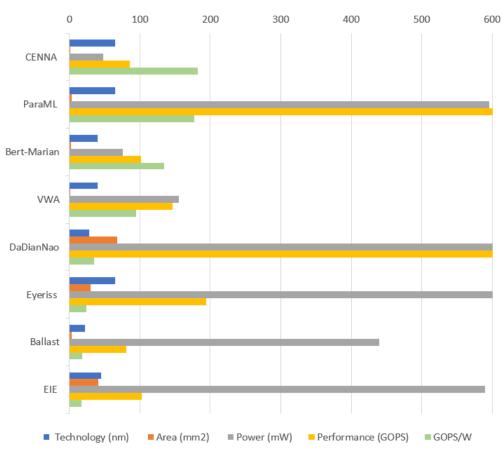

In recent years, DNNs and other domain-specific ML accelerators have gained a lot of attention in the computer architecture community. The amount of literature available on DL accelerators is growing quickly. Table 3.1 demonstrates several deep learning accelerators and compares them based on their technology, chip area, power consumption, and overall performance.

| Platform         | Technology (nm) | Area (mm <sup>2</sup> ) | Power (mW) | Performance (GOPS) |

|------------------|-----------------|-------------------------|------------|--------------------|

| Ballast [1]      | 22              | 2,63                    | 439,3      | 80.80              |

| Eyeriss V2 [26]  | 65              | $\approx 30^{1}$        | -          | 193.7              |

| CENNA [28]       | 65              | 1.38                    | 47.34      | 86                 |

| EIE [29]         | 45              | 40.8                    | 590        | 102.4              |

| VWA [30]         | 40              | 1.56                    | 154.98     | 146.33             |

| DaDianNao [31]   | 28              | 67.7329                 | 15970      | 5580               |

| ParaML [32]      | 65              | 3.51                    | 596        | 1056               |

| Bert-Marian [33] | 40              | 2.4                     | 76         | 102                |

Table 3.1. The comparison of DNN accelerators

Ballast [1] has an AI-subsystem based on NVDLA [34]. It has 32x8 bit MAC units and operates at a 750 MHz clock frequency. Eyeriss version 2 [26] reports the throughput and energy efficiency of their designed DL accelerator with four different DNN algorithms. The values in Table 3.1 are for the MobileNet neural network inferences on their DL accelerator. CENNA [28] is the 16-bit CNN accelerator which uses matrix multiplication for

<sup>&</sup>lt;sup>1</sup>Eyeriss v1 area is 1394k NAND-2 gate reported in [26] which is also reported 16  $\text{um}^2$  in [27]. Therefore, Eyeriss v2 area which is reported 2695k NAND-2 gate in [26] is estimated  $\approx$  30  $\text{um}^2$ .

doing the convolution. As shown in Table 3.1, it produces good results.

Chen et al. [35] focus on different approaches to reduce data movements such as Weight stationery, Output Stationery, No local Reuse (NLR), Row Stationary (RS). Then claim that the RS is the best in power and energy consumption. Calculating the 1D Row Convolution in PE is named row stationary.

State-of-the-art, EIE [29] is an efficient inference engine that supports sparsity. It utilized a dedicated accelerator, performing Sparse Matrix Vector Multiplication (SMVM) and handling weight sharing. EIE saves a considerable amount of energy with four actions: moving the data from Dynamic Random Access Memory (DRAM) to Static Random Access Memory (SRAM), then using sparsity, sharing weights, and finally, skipping zeros caused by activation. Another AI accelerator that supports sparsity is NullHop [36]. The authors claim that an efficiency of 368 percent is possible because of its zero-skipping pipeline and high MAC utilization.

VWA [30] is a hardware-efficient CNN accelerator that can implement different convolution filters with good results. It combines systolic array architecture with vector-wise input and weight data to preserve regular structure. As a result, they manage to reduce expenses while still satisfying the aforementioned requirements for flexibility.

Another well-known DLA is DaDianNao [31]. It stores all the computation-related data in local memory to reduce the number of memory accesses. The author claims accomplishments in both high performance and low power consumption.

ParaML [32] or Polyvalent Multi-core Accelerator for ML is an architecture that supports ten different ML techniques (k-NN, k-means, linear regression, SVM, DNN, naive bayes, classification tree, LVQ, parzen window, PCA) and is a flexible design that can accommodate for increased data size and is energy efficient for different ML scenarios. Bert-Marian [33] is a low-power precision-scalable processor for CNN which has 256 parallel PU and runs at 204MHz, it uses the sparsity of convolutions and implements dynamic scalability, it utilizes 16x16 MAC array.

Table 3.2 shows all these different accelerators sorted by their performance per power consumption (GOPS/W). Because these are implemented with different technologies ranging from 22 to 65nm, comparing the area or power is not a one-to-one comparison, so sorting them by their respective performance per power consumption is a better way to demonstrate their efficiency. Figure 3.1 visualizes the results, and as some implementations have power consumption on a scale of thousands more than others, the X axis is cropped at 600 to be able to view the smaller values. CENNA [28] has the best GOPS/W result, followed by ParaML [32], even though both are implemented in 65nm technology. Although DaDianNao [31] had the highest performance, we can see that it has very medium GOPS/W compared to other accelerators. As there is no other 22nm

| Platform         | GOPS/W  |  |  |

|------------------|---------|--|--|

| CENNA [28]       | 1816,65 |  |  |

| ParaML [32]      | 1771,81 |  |  |

| Bert-Marian [33] | 1342,11 |  |  |

| VWA [30]         | 944,186 |  |  |

| DaDianNao [31]   | 349,405 |  |  |

| Eyeriss V2 [26]  | 243,036 |  |  |

| Ballast [1]      | 183,929 |  |  |

| EIE [29]         | 173,559 |  |  |

accelerator, we can't compare Ballast in more detail with others correctly.

Table 3.2. Sorting Table 3.1 by Performance per power consumption

DNN Accelerators

Figure 3.1. Visual comparison of Table 3.1

Chen et al. [26] explore sparsity and architectural design for sparse DNN models. By using Rectified Linear Unit (Relu), the decoder layer and pruning sparsity happen to DNNs. It is possible to use this sparsity to improve energy efficiency and the speed of processing. These can happen in two ways: either skipping, gating the MAC computation, or compressing the weights and activations. The latter helps to decrease data movement and storage. However, it is not as easy as it sounds. There are two main challenges: first, access pattern irregularity, and second, a different PE has an uneven workload. It is noteworthy to mention that Eyeriss V2, in contrast with other versions, supports sparsity. Eyeriss v1 [27] does not support sparsity and it has 1394k NAND-2 gate area, while Eyeriss v2 [by supporting sparsity] consumes 2695k NAND-2 gate area, approximately two times more. It vividly shows that supporting sparsity increases area. Sparsity is not the only reason for the increase in area; another reason is the use of Single Instruction, Multiple Data (SIMD), which doubles the MAC operations.

Bing et al. [37] is the FPGA based DL accelerator, which supports depth-wise separable convolution. It consists of depth-wise convolution and point-wise convolution. MobileNet and ShuffleNet are examples of ML models which use depth-wise separable convolution. The MobileNet architecture introduces depth-wise separable convolution layers [16]. In this architecture, 2D convolution is replaced by 1D convolution along with depthwise convolution. Reducing the number of parameters as well as calculations are the reasons for using this kind of convolution, while keeping the loss of precision limited.

Table 3.3 demonstrates three convolution-recurrent neural networks (CNN-RNN), and compares them in terms of area, power, and throughput. Because of the space and power requirements, there are few designs for the combined CNN-RNN accelerator. Shin et al [38], [39] propose a heterogeneous ML-specific integrated circuits (MSICs) architecture called DNPU. There is a top controller, the MLP-RNNs processor, and a CNNs processor inside the DNPU in order to support gesture and action recognition as well as image captioning. As a consequence of supporting CNN and RNN at the same time, this accelerator consumes more areas. Furthermore, the Unified Neural Processing Unit (UNPU) [40] accelerator employs CNN-RNN cores. It is designed specifically for dialogue generation and emotion recognition tasks. An interesting point about UNPU is that weight and input features are concatenated into a 1D vector.

| CNN-RNN   | Technology (nm) | Area (mm <sup>2</sup> ) | Power (mW) | Performance (GOPS) |

|-----------|-----------------|-------------------------|------------|--------------------|

| UNPU [40] | 65              | 16                      | 279        | 691.2              |

| YIN [41]  | 65              | 19,36                   | 447        | 409.6              |

| Zeng [42] | FPGA-ZU5EG      | N/A                     | 8000       | 690.76             |

Table 3.3. Related works with CNN-RNN architecture at 200 MHz frequency.

#### 3.2 Multipliers

Convolution is calculated by multiplying and accumulating input feature maps and weights. Billions of MAC operations are required, which results in intensive data movements. Table 3.4 shows the number of MACs for different DL algorithms.

In most DLA designs, the terms MAC and PE are mentioned a lot. A PE can contain MAC units, a small memory buffer, and a control unit. For example, [43] uses four RISC-V processors as PEs, and each RISC-V core has a buffer, controller, and MAC. Consequently, these terms are sometimes used instead of each other. When PE is mentioned, the focus is on the number of MAC units it contains.

| Deep Learning Algorithms | Num of PE/MAC units | Num Weights |

|--------------------------|---------------------|-------------|

| MobileNet [16]           | 569 M               | 13 M        |

| Inception [44]           | 5.74 B              | 52 M        |

| AlexNet [4]              | 724 M               | 61 M        |

| VGG16 [5]                | 15.5 G              | 138 M       |

| ResNet-50 [7]            | 3.9 G               | 25.5 M      |

| GoogLeNet [6]            | 1.43 G              | 7 M         |

Table 3.4. Computation requirements MACs and weights of various deep neural networks

Table 3.5 shows the number of MAC/PE units of various deep learning accelerators. According to [26] MAC units consume around 65 percent chip area of their work, which is the similar situation in most of the DL accelerator designs. Moreover, it indicates that the number of MACs that contain multipliers is high in each DLA. Thus, it is important to have a multiplier that consumes less chip area and power. For example, the systolic array in Eyeriss [27] architecture consists of 168 MAC units. It's interesting to note that in Eyeriss V2 [26], the bit width has been reduced from 16 to 8 bits. The array of MAC unit structures, in particular multipliers, will occupy a vast chip area and consume a considerable amount of power.

Camus et al [45] evaluate the implementation of MAC units in various DL accelerators. Using the precision-scalable MAC architecture is one of the common ways, such as the Deep Neural Processing Unit (DNPU) [46], Unified Deep Neural Network (UNPU) accelerator [40].

| Platform         | Num of PE/MAC units | Area (mm <sup>2</sup> ) | Bit Width |

|------------------|---------------------|-------------------------|-----------|

| Ballast [1]      | 256                 | 2.63                    | 8-bit     |

| Eyeriss v1 [27]  | 168                 | 16                      | 16-bit    |

| Eyeriss v2 [26]  | 192                 | pprox 30                | 8-bit     |

| Bert-Marian [33] | 256                 | 2.4                     | 1-16 bits |

| EIE [29]         | 64                  | 63.8                    | 4-bit     |

| VWA [30]         | 168                 | 1.56                    | 16-bit    |

Table 3.5. Comparison in the number of MAC/PE, area; ASIC platform.

## 4. DESIGN PRINCIPLES OF DEEP LEARNING ACCELERATOR ARCHITECTURES

This chapter discusses some principles of designing a DLA. Figure 2.3 demonstrates how DLAs adhere to spatial architecture. It enables the increase of parallelism with the high number of PEs utilized, because there are fixed computational patterns, memory access, and data reusability in them.

### 4.1 Data Movement

Training and inference of each ML algorithm require abundant amount of data. Only considering the inference, each layer of ML needs a tremendous amount of data transfer across distinct blocks. The transmission of data can become a bottleneck in execution. Data movement and memory data structures influence overall performance, such as energy consumption and throughput, especially in memory-bound systems. According to [47], transferring the data from DRAM (external memory) to ALU consumes 200 times more energy than transferring the data from the register file (RF) to ALU, and data movement between the global buffer (internal memory) and ALU spends six times more energy.

One of the ways to reduce data movement overhead is the use of Direct Memory Access (DMA). While the main processing unit is occupied by other tasks such as reading from external inputs and generating control signals, another part of the system called DMA can enable certain hardware subsystems to access main system memory independently of the CPU. DMA makes the design faster by reducing the time required for data movement. However, even after utilizing the DMA, data movements in the DL accelerator are noticeable, time-consuming operations.

It is critical to remember that enabling sparsity minimizes data movement. Because the sparse weight is no longer in memory, and when the input data is 0, MAC operations are omitted.

### 4.1.1 Data flow of the systolic array

Going toward the spatial architecture enables data reuse, which reduces data movements. It is noteworthy to highlight that it is necessary to exploit spatial reuse. Otherwise, it leads to the underutilization of parallelism. Multiple MAC units align together to form a systolic array. Hence, since convolution doesn't have ordering constraints, alternative data flows can be implemented. Usually, the connection of MAC units follows one of the data flow structures listed below. The weight stationary is the most popular among others. Notably, there are methods for transferring data across MACs and reducing data movements. The most well-known ones are mentioned by the listing. To understand each item in the for loop, consider I[w] to be the input activations, F[s] to be the filter weights, and O[q] to be the output activations.

• Weight stationary like NVDLA [48], TPU [49], Origami [50] and UltraTrail [51]. Weights are stationary and are obtained once from memory. The connection in the pseudo code in section 2.1.1 has this kind of connection. It can also be represented as:

for s = [0:s]:

for q = [0:q]:

w = q + s

O[q] += I[w] \* F[s];

Listing 4.1. Weight stationary

• Output stationary like ShiDianNao [52], DaDianNao [31]. In this kind of data flow, intermediate results known as partial sum are stationary.

for q = [0:q]:

for s = [0:s]:

w = q + s

O[q] += I[w] \* F[s];

Listing 4.2. Output stationary

• Input stationary like SCNN [53], This kind of data flow to reduce the data movement, keeps the input feature maps stationary.

```

for w = [0:w]:

for s = [0:s]:

q = w - s

O[q] += I[w] * F[s];

Listing 4.3. Input stationary

```

- No local reuse like DianNao [54], as it is obvious from its name there is no data reuse in any local register.

- Row stationary 1D Row Convolution in PE) like Eyeriss Version 1 and version 2 [27]. In this data flow, a row of a kernel and a row of one channel of the input fea-

ture map are stationary.

Based on the findings of [27], the row stationary is much more efficient than the other mentioned data flow. The comparison was between different data flows of the same design of 256 PEs and a batch size of 16 based on the ALexNet convolutional layer.

### 4.1.2 Dimension of the systolic array

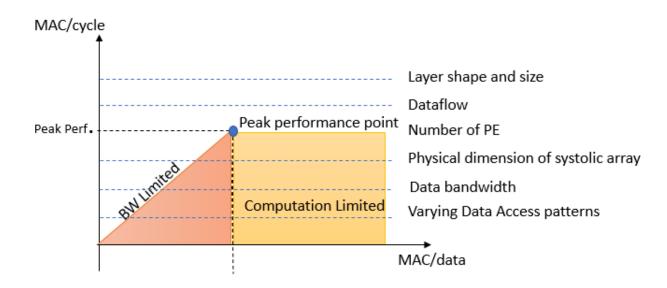

With regards to [55] a roofline model tells how to improve the performance. It is used to figure out the appropriate number of MAC units and the dimension of the systolic array. According to the roofline model, the number of MACs/PEs cannot exceed a certain amount since having an unnecessary number of MACs/PEs wastes resources. Hence, finding the suitable dimension of the systolic array is the most challenging part. A suitable number of MAC units should be chosen so that the DL accelerator performs optimally.

Figure 4.1 depicts the factors influence the number of PEs/MACs. There are seven steps to determining an adequate number of MAC units [56]. These seven steps are the layer shape and size, data flow; predefining the number of PEs/MACs to check the impact of the architecture, dimension of the systolic array, memory capacity by considering the global buffer size, data bandwidth, and various data access patterns.

Figure 4.1. Roofline Model for selecting the number of MAC operation [55]

## 4.2 The network on chip of the systolic array

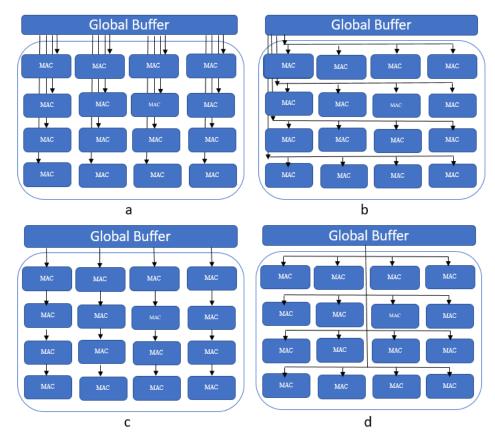

As explained in 4.1.1, a Network on Chip (NoC) should have three features to support data flow: processing with high parallelism by efficiently delivering data between storage and data path; Moreover, it should exploit data reuse to minimize the bandwidth requirement and improve energy efficiency. Finally, it is scalable at a reasonable implementation cost.

Figure 4.2 illustrates four NoC structures suitable for DL accelerators. Unicast networks are represented by a, 1D Multicast networks by b, 1D Systolic networks by c, and broadcast networks by d. Each NoC implementation has pros and cons. As an example, Unicast Network has low reuse and high bandwidth, while broadcast Network is vice versa.

Figure 4.2. Common Network on Chip

It must be pointed out how the results data flow would be. According to [57] the results of each MAC unit can either sum apart or sum together. [57] proposed two MAC engines, with different implementation of sum separate and sum together suitable for DNN inferences. Sum separate means that the intermediate results from each PE are apart from each other while sum together means the results form one single output.

#### 4.3 Post processing

Post-processing is the final step of the computational pipeline. Depending on the layer, it may include pooling, activation, Batch Normalization (BN), etc. Here, briefly, some of them are discussed.

There are two types of nonlinear activations: conventional and contemporary. Classical nonlinear activations include the sigmoid and hyperbolic tangent, while current nonlinear activations include the Rectified Linear Unit (Relu), Leaky Relu, and Parametric Relu. The three most popular activation functions are Sigmoid, Tanh, and Relu. The first two are well-known for their mathematical analysis, while the third is well-known for their simplicity. These functions improve the DNN's linearity.

Pooling or more generic downsampling helps to resize the feature map. It is usually executed after the activation. The ability to extract aspects of a picture, such as sharp and smooth characteristics, is the ability of pooling. Maximum, Minimum, and Average are different pooling operations. On the other hand, there is also unpooling/upsampling which increases the resolution of the feature map.

BN is executed between convolution and a fully connected layer or nonlinear activation. In the design of CNNs, batch normalization has become the norm.

Equation of the batch normalization:

$$y = \gamma * \frac{x - \mu}{\sqrt{\delta^2 + \epsilon}} + \beta$$

(4.1)

$\gamma$  : Scale value,  $\beta$  : Shift value,  $\epsilon$  : Constant,  $\delta$  : Diviation,  $\mu$  : Mean, x : input

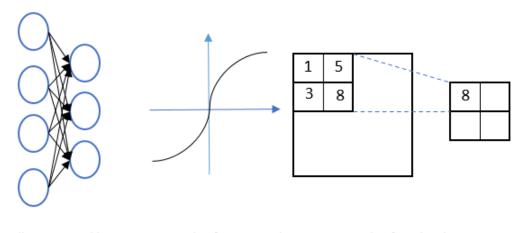

Figure 4.3 illustrates some of the layers. Convolution extract features by convolving the trained filters on input feature maps. In the convolution, when the the filters are the same size of the input feature map is a special situation, called fully connected layer.

Fully connected layer Example of activation layer Example of pooling layer

Figure 4.3. Different layers of Neural Network

## 5. PROPOSED DEEP LEARNING ACCELERATOR ARCHITECTURE

This chapter briefly explains the elements of the proposed deep learning accelerator and the reasoning behind them. Figure 5.1 depicts the structure of the proposed DL accelerator. It has five important Intellectual Properties (IPs): the Global Buffer, the DMA, the Control Unit, the CNN/RNN core, and the Aggregation Core.

Figure 5.1. Top level overview of proposed the DL accelerator

## 5.1 CNN/RNN Core

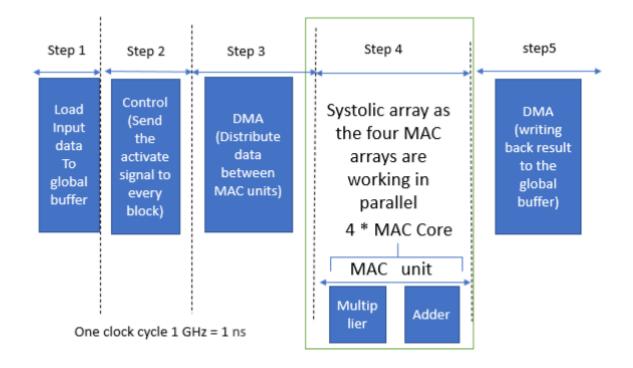

To keep the design highly flexible, the architecture should be configurable so that it can perform on both CNN and RNN. This subsystem is constructed of four MAC arrays.

Each MAC array consists of 64 MAC units which in total there 4\*64 = 256 MAC units. Figure 5.1 only illustrates 16 of them. In addition, each MAC unit has a multiplier and an adder.

The number if MAC units is selected based on the roofline model 4.1.2. The first constraints would be the layer size and shape. This affects the maximum workload parallelism, which is based on the selected NN model. The second step, the dataflow loop nest will limit the maximum data flow parallelism. For example, here we would like to have weight stationary dataflow, this means that each MAC stores one weight. Then in the third step, the finite number of MACs is defined, based on theoretical peak performance and evaluating different scenarios we conclude that based on our use cases if 512 MAC units is selected we will end up with multiple idle MACs at the processing time which reduces the overall performance therefore reducing that to 256 we reach our peak performance, 128 MAC units result in under performance and increased latency, this constraint the number of maximum MAC parallelism to 256 units. The dimension of the MAC array and fixed storage capacity for intermediate data will bound the number of active MAC units.

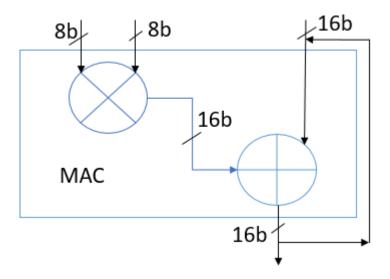

### 5.1.1 MAC Unit: Multiplier and Adder

The MAC unit is the smallest unit in the whole DL submodule. There are different ways to implement MAC units. Here, a simplistic MAC unit is considered. It consists of an adder and a multiplier. Figure 5.2 demonstrates the inputs and outputs of each MAC unit as well as the relationship between multipliers and adders. For building the MAC unit different multiplier and adder algorithms are implemented and compared. Chapter 7 explains more about it. Here is a brief primer on multipliers and adders.

Figure 5.2. MAC unit structure

As illustrated in section 2.1.1 multiplication and addition operations are at the heart of

convolution. The multiplier is one of the critical parts of the DL subsystem since it's both repeated multiple times and consumes a tremendous amount of chip area and power. Therefore, designing an efficient multiplier has a great impact on the overall performance of the subsystem. On the other hand, the bandwidth that the multiplier can handle will affect the on-chip buffer size. For these two main reasons, it is valuable to implement the multiplier with logic gates that can calculate 2-bit, 4-bit, and 8-bit values. Similarly, addition is repeated several times. Although they do not consume too much area, the multipliers and adders' goal are to perform convolution. There are several different ways to do the convolution, such as Toeplitz, Gauss's complex multiplication transform, and Strassen's Matrix Multiplication Transform [58], [59].

Another notable factor is that the bit width of the outputs of multiplication is twice the bit width of the input. For example, the output of 8-bit multiplication is 16 bits. As a result, it should be truncated to 8 bits consequently some values will be lost. This affects the accuracy of the ML result. The truncation should occur before being written back to the memory.

This DL accelerator also supports the characteristic of sparsity. This feature minimizes MAC operations by bypassing the MAC units when the input data is zero. The sparse weight will no longer be saved in the memory. However, additional zero values may be formed during some process like Relu activation. Therefore, it is feasible to filter out these needless MAC operations by placing one flip flop before the MAC units and skipping MAC operation if the input is zero.

#### 5.1.2 Data Movement

Another way to reduce the data movement is to decrease the bit width of the weights and input features. Hence, in the proposed design, input features and weight data are packed in any 2, 4, or 8-bit format. The designed equivalent multiplier can perform the 2,4,8-bit computation. As a result, there is no need for data manipulation inside the DL accelerator. The [60] is an excellent example of limiting weights and activation to 4 and 8 bits, respectively. It is important to highlight that reducing the precision will decrease memory bandwidth, storage costs, energy per MAC operation, and memory access. However, it will have an impact on accuracy. Then, it is critical to be careful to maintain accuracy.

The proposed DL accelerator supports depth-wise separable and normal convolution. Thus, the connections between the MAC units are important. They should be connected in such a way that both computations are feasible with one systolic array. The key rationale is that this method of operation will save area while increasing efficiency. Furthermore, because we will be doing the calculation layer by layer in each NN model, there will be no requirement for concurrent computation of normal and depth-wise convolution. There is a significant challenge in selecting the suitable NoC due to various layers and models. Each model requires a different amount of data reuse. Considering the MobileNet model, the DL accelerator's proposed NoC would be a row-stationary data flow with a broadcast NoC.

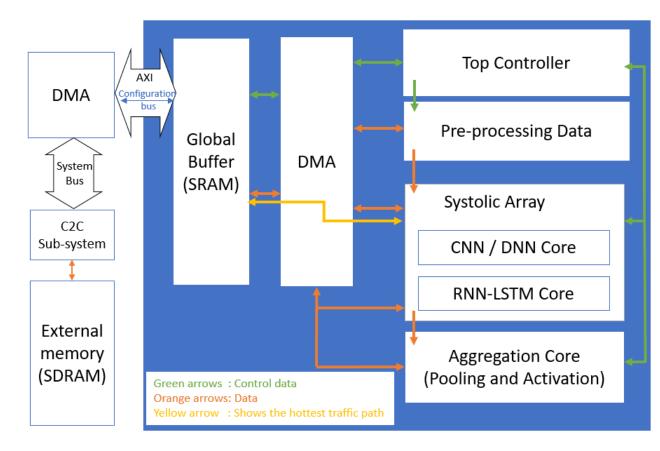

## 5.2 DMA

To decrease the data movement, data is read once from the external memory and stored in the internal memory. The data is then distributed across other units, particularly systolic arrays, via DMA. Figure 5.3 depicts the data path of deep learning accelerators. A control bus links the top controller with other IPs. And between DMA and other IPs, there is a data bus.

Figure 5.3. Data movements between major blocks

In hardware design, it is always important to specify the input and output of intellectual property (IP). In the proposed deep learning accelerator, data transfer occurs through the AXI protocol and DMA. DMA has a configurable interface to transfer the data. It maximizes the amount of data that can be transferred between external and internal memory. One of the critical roles of a DMA is to remove the requirement for a processing unit to transfer data. It should sync with other relevant components to be utilized effectively. Interrupt signals are sufficient for initiating the data transfer.

## 5.3 Control Unit

The control unit is a component that oversees the operation of the accelerator. It interacts with different parts of the design through control signals and interconnects [61]. The resources are managed by the control unit, and it directs the flow of data between each part of the design. To make the design simpler, there is one main/top controller which activates other units. The top controller is responsible for configuring the units that are needed in each layer. DMA can move the necessary control data to and from the control unit and can effectively transfer higher levels of data flow control commands while the control unit can manage each resource at a lower level of control.

There is a configuration bus which is responsible for communicating with the main CPU and DL Accelerator. And there are several other control units which are invoked by the configurable bus controller. The control unit has multiple internal counters dividing the data into sections, controlling the flow. Each layer of the neural network algorithm calculation needs its own operations. There are a series of calculations and convolutions done on the data based on the coefficients respective of their widths, heights, and channel numbers, and then there are different kernel numbers, kernel heights, and kernel widths, which further require configuring the resources accordingly. The pooling and activation stages of the data flow also need a control unit to decide. This is done by controlling the signals to stimulate the inputs of different units and latching the outputs.

The dynamic kernel size is utilized to simplify the control unit and decrease the number of various kernels. In this work, the kernel size is 3\*3 by default. And, if the kernel size is smaller than the default size, then zero-padding should be added. In other cases, if the kernel size is bigger than the default size, it should be divided into multiple 3\*3 matrices.

There are multiple configuration registers inside the control unit which can be configured to control this flow, and as they are being configured through DMA, the control unit communicates with several other smaller control units inside each part of the design, handshaking the data to the next phase and activating them at the right moment. And as this is a time-critical task, there is a dedicated configuration bus for all the control communications.

### 5.4 Global Buffer

To process multiple neural network layers, there is a need to provide neurons output values from previous layers, therefore the global buffer is allocated to store the input data and weight data. The global DMA transfers the required data from external memory into the global buffer. As this is the most time-consuming process of the accelerator, it reduces

the data movement by storing the data inside the buffer. On other hand, as a trade-off Memory on chip consumes huge amount of area and it is costly.

The output of each layer will be the input of the next iteration, and this process is repeated until the last layer, to take advantage of this periodic operation, the result of first computation will be stored in the global buffer and it will be used for the next iteration, it is possible to use the memory page mirroring technique for this multi-step computation. In the final layer the result will be stored in the output buffer. It should be truncated and packed accordingly to be suitable for the next iteration.

The buffers should be designed in the ping pong method to save the time and reduce the latency. The concept is a way to move the data back and forth so that all the resources can use the data without colliding each other's transaction. Using DMA and indicator signals such as data ready, data is transferred without losing any part and the receiving unit will only take the data into use only if the previous unit is done writing to it.

## 5.5 Aggregation core

The aggregation core consists of an activation and pooling core. Considering that each ML model does something specific, for example, it may be a sequential NN model with five layers that may be a combination of convolution layer, pooling layer, recurrent layer, and so on. We would like to have several to support for different NN models. Therefore, suggested DL accelerator supports linear and nonlinear activation such as Relu, as well as providing support for maximum, minimum, average pooling.

For example, if adapts the design to the MobileNet NN model. The Basic MobileNet model doesn't have the pooling layer, however according to the [62], using the pooling layer in the MobileNet model with a kernel size of 3x3 and stride 2 provides more accuracy and reduces the size of the hidden layer more than common pooling. Furthermore, this feature reduces parameters and the cost of computation. Pooling exists in our proposed architecture because it encapsulates the image to one label which is needed in some applications such as image classification applications.

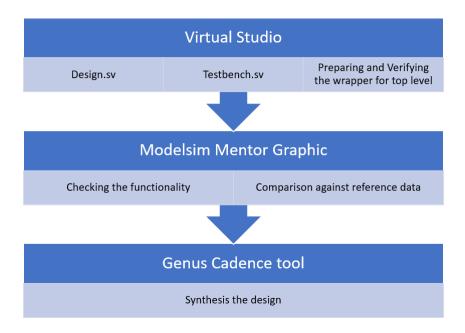

## 6. METHODOLOGY

This chapter explains the methods and tools used in this thesis work. The 22 nm ASIC technology is used for implementation. The tools utilized are Visual Studio [63] for writing and editing the code. Modelsim [64] is used for the RTL simulation and finally Cadence [65] tools for ASIC synthesis. Figure 6.1 demonstrates the whole process of doing the work.

### 6.1 Procedure

This thesis tries to find which algorithm and RTL implementation is better regarding different parameters such as area, power, and performance for the proposed DL accelerator subsystem. Various approaches proposed in other thesis works and literature are compared, to come up with a conclusion on which algorithm is performing better. Different hardware implementation algorithms were implemented and then ran the simulation and synthesis to come up with the conclusion table of the results.

In this thesis work, multipliers and adders are written in SystemVerilog hardware description language. The Visual Studio Code Integrated Development Environment (IDE) with the SystemVerilog extension is very convenient to write and debug the code. After preparing the Hardware Description Language (HDL) known as Register Transfer Level (RTL) code, there is a need to check the functionality of the design. For this reason, the design is simulated by Modelsim, one of the Mentor graphics tools. Various verification methods are used to ensure that the designed hardware is behaviorally correct according to the models which are written in SystemVerilog as well.

The next step after the simulation and verifying the functionality of the design is the actual hardware implementation at a low level and generating the netlist file and back-end tools for the physical implementation. To do the synthesis, a wrapper file is prepared to hold the top-level design and creates two registers in the input and output of the design, and then by running the synthesis flow. Some features of the design are given in the results, which are compared here.

The data is collected from the synthesis tool summary report. Then it is attempted to use different scenarios to collect multiple varying data and then compare them and list

Figure 6.1. Methodology flow

them in the corresponding table and sort each algorithm based on each feature that has preferred results.

The methodologies used in this thesis follow industry standards and the most elaborate method to verify and choose different architectural implementations in RTL design. By simulating the observed behavior, which is independent of and unaffected by the implementation method and evaluating each design option against it.

### 6.2 Evaluation

As the field of research is developing and study is carried out related to the ML, DL, NN, and hardware accelerator for specific/general NNs. Therefore, it was important to know how to compare them. These are the metrics for comparing a DLA.

Operation Per Seconds (OPS) which the unit would be Tera/Giga/Mega operation per second (TOPS, GOPS or MOPs) is the best value for comparing the performance of various DL accelerators. It is possible to include the power into this number and report Operation per second normalized by power consumption (TOPS/W, GOPS/W or MOPs/W). Equation 6.1 demonstrates it.

$$\frac{\text{Operations}}{\text{second}} = (\frac{1}{\frac{\text{cycles}}{\text{operation}}} * \frac{\text{cycle}}{\text{second}}) * \text{Number of MAC units } * \text{Utilization of MAC units}$$

Throughput demonstrates the computational capability of the hardware. There are

effective throughput which obtain in real world conditions, and theoretical throughput that the number of arithmetic units (MAC units) and clock frequency determines

it. The achievable throughput relates to the number of utilized MACs. The overall

system theoretical throughput:

$\label{eq:Utilization of MACs} \text{Utilization of MACs} = \frac{\text{Number of active MACs}}{\text{Number of MACs}} * \text{Utilization of active MACs} \ \ \text{(6.2)}$

- Latency is the amount of time it takes to return results for given inputs. Low latency is one of the essential criteria for real-time applications such as autonomous navigation.

- Accuracy determines the quality of the results for specific task. The difficulty of the task and dataset affects the accuracy. As an example, performing the classification model on MNIST is less complex than on ImageNet. Object detection is more difficult than classification.

- Energy and power are one of the most critical variables in edge devices. It determines the quality of an edge accelerator.

- Hardware cost such as area of the chip and memory bandwidth

- Flexibility, which refers to the DL accelerator's ability to perform a variety of tasks.

- Scalability refers to the number of different DNN models supported by the DL accelerator.

The accelerator design that can handle multiple NN with the least amount of area and power consumption is preferred. There is a trade-off between throughput, power consumption, precision of weights and activation, and inference accuracy. For example, reducing the power consumption will reduce the inference accuracy as well [24].

## 7. IMPLEMENTATION OF MULTIPLIERS

There is one multiplier in every MAC unit of the proposed DL architecture. There are four MAC arrays in the proposed DL accelerator. Each MAC array consists of 64 MAC units. Thus, there would be 256 multipliers in total.

Figure 7.1 demonstrates the 4-bit multiplication calculation on pen and paper. The most traditional way of doing multiplication is with addition and shift. The partial products are generated by using AND gate. Then, the result is the addition of the partial products. Thus, it is possible to say that multiplication is repeated addition. The various multiplier algorithms have their unique structure to generate partial products, and they might use special adders to make the computation more optimized.

| Multiplicand:<br>Multiplier: |      |      |      |      |      | A3 A2 A1<br>B3 B2 B1 |                |

|------------------------------|------|------|------|------|------|----------------------|----------------|

|                              | _    |      |      | B0A3 | B0A2 | B0A1                 | BOAO           |

| Partial                      |      |      | B1A3 | B1A2 | B1A1 | B1A0                 | 0              |

| Product                      |      | B2A3 | B2A2 | B2A1 | B2A0 | 0                    | 0              |

|                              | B3A3 | B3A2 | B3A1 | B3A0 | 0    | 0                    | <sup>0</sup> 🔶 |

| Product - Sum7               | Sum6 | Sum5 | Sum4 | Sum3 | Sum2 | Sum1                 | Sum0           |

Figure 7.1. Multiplication of two 4-bit number

### 7.1 Adders