# Channel doping concentration and cell program state dependence on random telegraph noise spatial and statistical distribution in 30 nm NAND flash memory

Toshihiro Tomita and Kousuke Miyaji

Department of Electrical and Electronic Engineering, Shinshu University, Nagano 380-8553, Japan

E-mail: kmiyaji@shinshu-u.ac.jp

#### Abstract

The dependence of spatial and statistical distribution of random telegraph noise (RTN) in a 30 nm NAND flash memory on channel doping concentration  $N_A$  and cell program state  $V_{th}$  is comprehensively investigated using three-dimensional Monte Carlo device simulation considering random dopant fluctuation (RDF). It is found that single trap RTN amplitude  $\Delta V_{th}$  is larger at the center of the channel region in the NAND flash memory, which is closer to the jellium (uniform) doping results since  $N_A$  is relatively low to suppress junction leakage current. In addition,  $\Delta V_{th}$  peak at the center of the channel decreases in the higher  $V_{th}$  state due to the current concentration at the shallow trench isolation (STI) edges induced by the high vertical electrical field through the fringing capacitance between the channel and control gate. In such cases,  $\Delta V_{th}$  distribution slope  $\lambda$ cannot be determined by only considering RDF and single trap.

## 1. Introduction

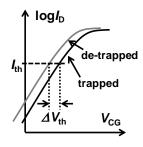

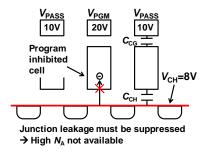

Random telegraph noise (RTN) is considered to be one of the major error/noise sources in ultra-scaled flash memory technology.<sup>1-8)</sup> RTN is induced by capture/emission of single electron in a gate oxide trap, which is generated by fabrication process or program/erase cycling stress. Therefore, RTN results in threshold voltage  $(V_{\rm th})$  fluctuation as shown in Figure 1. RTN characteristics in the floating gate (FG) type NOR flash memories have been already extensively studied.<sup>2-8)</sup> In these works, it is found that threshold voltage shift  $\Delta V_{\rm th}$  (RTN amplitude) depends on the channel doping profiles as well as the trap position and density at the gate oxide interface using three-dimensional (3D) Monte Carlo device simulation with random dopant fluctuation (RDF).9-12) Also, assuming uniform doping profile with relatively high channel doping concentration  $N_{\rm A}$  beyond  $1 \times 10^{18}$  cm<sup>-3</sup>,  $\Delta V_{\rm th}$ exhibits exponential distribution whose slope value is  $\lambda$  and standard deviation is proportional to the square root of  $N_{\rm A}$ .<sup>1,3-5)</sup> Meanwhile, in FG type NAND flash memory, the cell design and operation are totally different from NOR in terms of the channel profiles and operating voltage as shown in Table I.  $N_A$  is expected to be kept as low as possible (<  $1 \times 10^{18}$  cm<sup>-3</sup>) to suppress junction leakage current unless the short channel effect (SCE) becomes too significant.<sup>13-17)</sup> Otherwise, the channel voltage ( $V_{CH}$ ) cannot be maintained sufficiently high (~8 V) at the unselected cell during program inhibit operation using channel self-boosting technique<sup>18,19</sup> as shown in Figure 2. In this scheme, the NAND string channel potential is boosted utilizing capacitive coupling between the control gate (CG) and channel by turning off select gates. During channel self-boosting, the channel voltage drop by the leakage current at p-n junction results in unwanted electron injection to the floating gate (FG) called program disturbance.

On the other hand, there are also reports that focusing on RTN effects in NAND flash memories.<sup>20-26)</sup> However in these reports, analyses are mainly based on measurement results, which are derived from macroscopic physical values. In other words, microscopic physics obtained from statistical 3D Monte Carlo device simulation would provide further understandings to the RTN in ultra-scaled NAND flash memory.

In this work, RTN characteristics in 30 nm NAND flash memory are analyzed through 3D Monte Carlo device simulation considering RDF. Two points are focused. First, single trap RTN amplitude  $\Delta V_{\text{th}}$  and its distribution  $\lambda$  are evaluated by widely varying  $N_{\text{A}}$  from

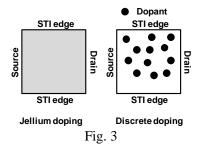

$1 \times 10^{17}$  to  $3 \times 10^{18}$  cm<sup>-3</sup>. Cases for jellium and discrete doping are also compared. Figure 3 shows the differences between the jellium and discrete doping case. In the jellium doping case, dopants are uniformly distributed (no atomistic effect) while the discrete doping considers atomistic effect of the dopants. The results reveal that in NAND flash memory (low  $N_A$ ), RTN characteristics are more like the jellium doping case where drain current  $I_D$  flows at the center of the channel. Second,  $\Delta V_{\text{th}}$  and its distribution ( $\lambda$ ) are evaluated with varying cell program state ( $V_{\text{th}}$ ) by changing charge amount in FG assuming 2 bit/cell multi-level cell (MLC) architecture. Simulations are also performed for different  $N_A$ . As cell  $V_{\text{th}}$  increases in high  $V_{\text{th}}$  program state,  $I_D$  concentrates at the shallow trench isolation (STI) edges due to the high vertical electrical field by fringing capacitance resulting in different trends for both low and high  $N_A$ .

This paper is organized as follows. In Sect. 2, device simulation conditions are explained. Sect. 3 shows and discusses the results of the  $N_A$  dependence of  $\Delta V_{th}$  distribution for discrete doping and jellium case. Sect. 4 shows cell program state dependence of  $\Delta V_{th}$  distribution. Finally, conclusions are given in Sect. 5.

#### 2. 3D device simulation conditions

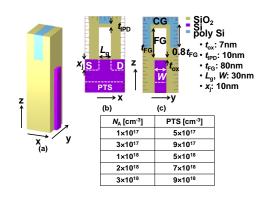

Figure 4(a) shows the 30 nm 2 bit/cell NAND flash memory cell structure for 3D device simulation used in this work. Figures 4(b) and 4(c) show the cross section view for x-z plane and y-z plane, respectively. SiO<sub>2</sub> tunnel oxide thickness  $t_{ox}$ , inter-poly dielectric thickness  $t_{IPD}$ , and FG height  $t_{FG}$  are 7, 10, and 80 nm, respectively. Both channel width W and length  $L_g$  are set to 30 nm, and source/drain junction depth  $x_j$  is set to 10 nm. In this work,  $N_A$  is widely varied from  $1 \times 10^{17}$  to  $3 \times 10^{18}$  cm<sup>-3</sup> while punch-through stopper (PTS) layer is adopted at 30 nm below the source/drain junction to suppress excess SCE. PTS doping concentration is increased as  $N_A$  is increased.

Monte Carlo simulations over 100 NAND flash cells are performed including RDF effect. The threshold voltage difference between trapped and de-trapped states is extracted as  $\Delta V_{\text{th}}$  for each NAND cell having different discrete doping profiles based on methods in references.<sup>2,4-8)</sup> Threshold voltage  $V_{\text{th}}$  is defined as the  $V_{\text{CG}}$  value when  $I_{\text{D}}$  reaches  $W/L_{\text{g}} \times 10^{-7}$  A. To emulate the trapped states, 1 nm<sup>2</sup> square negative surface charge is randomly placed at the channel surface (tunnel oxide/substrate interface) whose charge

amount equals to single electron. In this work, trap energy levels are not considered for simplicity.<sup>2)</sup> Therefore, channel potential dependence on time constants and  $\Delta V_{\text{th}}$  of the trap/de-trap phenomenon are not included. For changing cell program states, charge amount in the FG is changed to adjust the  $V_{\text{th}}$  to the desired value for MLC operation, which will be explained in detail at Sect. 4.

## 3. $N_A$ dependence of $\Delta V_{\rm th}$ distribution

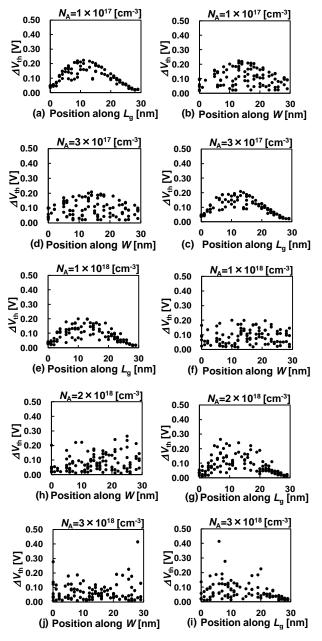

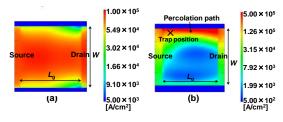

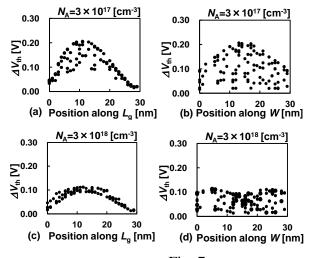

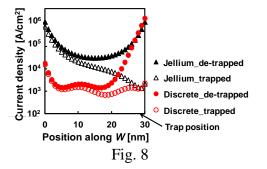

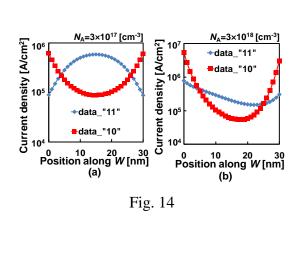

Simulation results of  $\Delta V_{\text{th}}$  spatial distributions ( $\Delta V_{\text{th}}$  against trap position along  $L_{\text{g}}$  and Wfor each  $N_A$ ) are shown in Figures 5(a)-5(j). At low  $N_A$  (1×10<sup>17</sup> and 3×10<sup>17</sup> cm<sup>-3</sup>), it is found that  $\Delta V_{\rm th}$  is large at the center of the channel for both  $L_{\rm g}$  and W direction.  $\Delta V_{\rm th}$ distribution peak for position along  $L_g$  slightly locates near the source side since the drain voltage  $V_D$  of 0.5 V induces weak electrostatic potential asymmetry by drain-induced barrier lowering (DIBL).<sup>8)</sup> However, as  $N_A$  increases,  $\Delta V_{th}$  distribution peak along W moves slightly towards the channel STI edges. Furthermore, extremely large  $\Delta V_{\rm th}$  is observed at the highest  $N_A$  case. Figures 6(a) and 6(b) show current density distributions of the channel surface near  $V_{\rm th}$  for the low and high  $N_{\rm A}$  devices, respectively. For the low  $N_{\rm A}$ case [Fig. 6(a)], current widely flows at the center of the channel, corresponding to the  $\Delta V_{\rm th}$ spatial distribution in Figures 5(b) and 5(d). On the other hand, in the high  $N_A$  case [Fig. 6(b)], huge RTN is observed when the trap locates above the percolation current path formed by the random discrete dopants.<sup>2,9,10)</sup> Figures 7(a)-7(d) show  $\Delta V_{\text{th}}$  spatial distribution in jellium doping case. When  $N_A$  is low, the  $\Delta V_{th}$  spatial distribution of the discrete doping case [Figs. 5(c) and 5(d)] is nearly the same as the jellium doping case [Figs. 7(a) and 7(b)] indicating that very few dopants locate at the channel surface and hardly create percolation path. Considering 30 nm cubic area, only 2 ~ 3 dopants exist on average in the region when  $N_{\rm A} = 1 \times 10^{17}$  cm<sup>-3</sup>. As for the high  $N_{\rm A}$  case [Figs. 7(c) and 7(d)], slight  $\Delta V_{\text{th}}$  peaks near the STI edges are also observed in the jellium case [Fig. 7(d)]. However, outlier sample is not observed in this case. It is also found that  $\Delta V_{\text{th}}$  at high  $N_{\text{A}}$  is smaller than that at low  $N_A$  [Figs. 7(b) and 7(d)]. In order to clarify the origin of this difference, channel surface current density distributions along W for the huge  $\Delta V_{\rm th}$  outlier sample in discrete dopant case and jellium case are extracted and compared as shown in Figure 8. Both trapped and de-trapped states are shown for the discrete and jellium doping

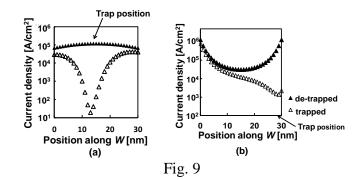

simulation results. From the current density distribution in the jellium case, current crowding is observed at the both sides of the STI edge, which is considered to be the electric field concentration by the corner effect at high  $N_{\rm A}$  doping.<sup>27, 28)</sup> The slight  $\Delta V_{\rm th}$ peak shift towards the STI edge can be explained from this phenomenon for both jellium and discrete doping simulation results. However, two current peaks are symmetrical in the jellium case while in the outlier sample, the current peak only locates on one (the right) side. Since single trap is considered in this simulation, current can still flow at the opposite edge even when the trap locates at the either side of the STI edge in the jellium case. Therefore,  $\Delta V_{\text{th}}$  is not huge compared to the outlier case where the current path is completely blocked when the trap site exactly locates above the single current path. The reason for smaller  $\Delta V_{\text{th}}$  at higher  $N_{\text{A}}$  in the jellium doping case can be also explained from the current density distribution profiles along W as shown in Figure 9. From Figures 9(a) and 9(b),  $\Delta V_{\rm th}$  would be larger in the lower N<sub>A</sub> case since the large portion of the current path is blocked and the maximum current density is reduced when the trap site locates above the channel center at low  $N_{\rm A}$ . It should be noted that the discussion is valid in the single trap case handled in this work and the result would be different in the multiple trap case. If two traps locate on both edges, the results above imply that large RTN would appear even in the jellium case.

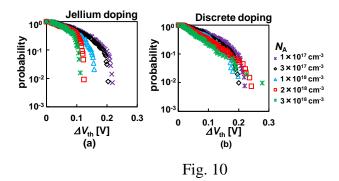

Figures 10(a) and 10(b) show  $\Delta V_{\text{th}}$  probability distributions for the jellium and discrete doping case, respectively. Distribution slope  $\lambda$  cannot be determined below  $N_{\text{A}} = 2 \times 10^{18}$ cm<sup>-3</sup> [Fig. 10(b)] as well as in the jellium case [Fig. 10(a)], since  $\Delta V_{\text{th}}$  tail bits do not exist due to the absence of the percolation path. Other physical origins should be considered such as multiple trap sites<sup>2,20,21)</sup> or line edge roughness<sup>29-31)</sup> to account for the  $\Delta V_{\text{th}}$  tail bits found in the NAND flash memory measurement results in the other reports.<sup>20-26)</sup> Figures 11(a) and 11(b) show  $N_{\text{A}}$  dependence of the average and standard deviation of  $\Delta V_{\text{th}}$ , respectively. Average  $\Delta V_{\text{th}}$  of the discrete doping case agrees well with the jellium, and continues to decrease as  $N_{\text{A}}$  increases. This is because channel current broadly flows in the low  $N_{\text{A}}$  cells and the current peak gradually becomes sharp as  $N_{\text{A}}$  increases by the electric field concentration at the STI edge (note that channel also becomes percolative in the discrete doping case). On the other hand, standard deviation of  $\Delta V_{\text{th}}$  starts to increase above  $N_{\text{A}} = 1 \times 10^{18}$  cm<sup>-3</sup> in the discrete doping case as the percolation path starts to appear in the channel.

#### 4. Effect of cell program state

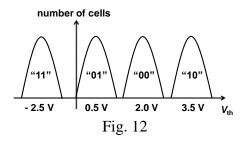

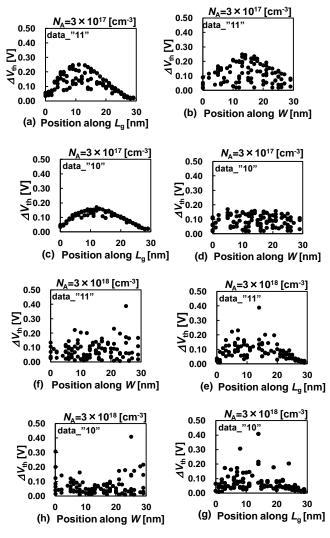

In this section,  $\Delta V_{\rm th}$  distribution is evaluated with varying cell program state by changing the charge amount in the FG. Figure 12 shows  $V_{\rm th}$  distribution and corresponding data symbols in MLC NAND flash memory.<sup>32)</sup>  $N_A$  is also varied where its value are 1×10<sup>17</sup>,  $3 \times 10^{17}$ , and  $3 \times 10^{18}$  cm<sup>-3</sup>, respectively. Here, fluctuation of the charge amount in the FG within each program state is not considered for simplicity. Figures 13(a)-13(d) show  $\Delta V_{\rm th}$ distribution along  $L_g$  and W with cell data symbol for "11" (the lowest  $V_{th}$  state corresponding to the erase state) and "10" (the highest  $V_{\rm th}$  state) when  $N_{\rm A} = 3 \times 10^{17}$  cm<sup>-3</sup>. Figures 13(e)-13(h) are those when  $N_{\rm A} = 3 \times 10^{18}$  cm<sup>-3</sup>. At low  $N_{\rm A} (3 \times 10^{17} \text{ cm}^{-3})$ ,  $\Delta V_{\rm th}$ distribution of Figures 13(a) and 13(b) are basically the same as Figures 5(c) and 5(d) when data symbol is "11". However, as Vth increases (data symbol "10"), maximum and minimum  $\Delta V_{\text{th}}$  near the center of channel along  $L_{\text{g}}$  direction decreases [Fig. 13(c)]. Furthermore,  $\Delta V_{\text{th}}$  peak along W direction is diminished [Fig. 13(d)]. On the other hand, at high  $N_A$  (3×10<sup>18</sup> cm<sup>-3</sup>) in Figures 13(e)-13(h),  $\Delta V_{\text{th}}$  distribution shape is less dependent on data symbols compared to the low  $N_A$  case, although  $\Delta V_{\rm th}$  peak slightly moves toward the channel STI edges along W direction in Figure 13(h). Also, extremely large  $\Delta V_{\text{th}}$  is observed for both "11" and "10" data symbols. Figures 14(a) and 14(b) show channel surface current distribution at the center of the channel for low and high  $N_A$  in typical samples with discrete doping, respectively. As shown in Figure 14(a), when  $N_A$  is low, the current distribution shape is completely inverted for two program states. The current peak is at the center of the channel for the low  $V_{\rm th}$  state "11" while it is at the channel STI edges for the high V<sub>th</sub> state "10". The reason for the current crowding at the STI edges at "10" state is due to the fringing electrical field from CG to channel, since higher voltage is applied to the CG to invert the channel.<sup>22)</sup> Therefore,  $\Delta V_{\text{th}}$  at the center of the channel is reduced in "10" state in Figure 13(d). Also, the reason why high  $\Delta V_{\text{th}}$  is not observed at the STI edge in "10" state in Figure 13(d) can be explained by the same mechanism discussed in Figure 8 jellium case, where two current peaks existing in single trap simulations. On the other hand, at high  $N_A$ , current path concentrates at the STI edge region for both "11" and "10" state but not symmetry as shown in Figure 14(b). In particular, this trend is more

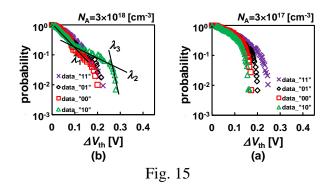

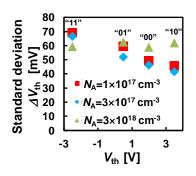

prominent in "10", where the maximum current density surpasses 5×10<sup>6</sup> A/cm<sup>2</sup>. Figures 15(a) and 15(b) show  $\Delta V_{\text{th}}$  probability distributions for four data symbols at  $N_{\text{A}} = 3 \times 10^{17}$ and  $3 \times 10^{18}$  cm<sup>-3</sup>, respectively. Figure. 16 shows standard deviation of  $\Delta V_{\text{th}}$  as a function of  $V_{\rm th}$  of the program state. Distribution slope  $\lambda$  is still not available at low  $N_{\rm A}$  even if the program state changes. Furthermore,  $\Delta V_{\text{th}}$  tail bits are reduced at "10" state, which can be seen from Figure 15(a) and the decrease in  $\Delta V_{\rm th}$  standard deviation in Figure 16. This is due to the current concentration at the both STI edges in the single trap condition as discussed before. On the other hand,  $\lambda$  can be extracted at the high  $N_A$  case except for the "10" state due to the RDF induced percolation path as shown in Figure 15(b). It is interesting that three distribution tendencies are found in the "10" state according to the  $\Delta V_{\text{th}}$  range as indicated by  $\lambda_1$ ,  $\lambda_2$  and  $\lambda_3$  lines in Figure 15(b). The tail distribution  $\lambda_2$  of 250 mV/dec is larger than  $\lambda_1$  of 145 mV/dec, since strong current concentration by the fringing electrical field and RDF induces large  $\Delta V_{\text{th}}$  when a trap locates above the current path. However,  $\lambda$  significantly reduces to  $\lambda_3$  of 45 mV/dec for even higher  $\Delta V_{\text{th}}$ . This is because the fringing electrical field from the CG tries to induce two current paths at the STI edges and  $\Delta V_{\text{th}}$  is suppressed in the single trap condition.

From these results, the amplitude and distribution of RTN in NAND flash memory with low  $N_A$  strongly depends on the cell program state. The results also indicate that the number of trap sites would significantly affect the NAND flash memory RTN characteristics.

### 5. Conclusions

The spatial and statistical distributions of RTN in a 30 nm node NAND flash memory in terms of  $N_A$  and cell program state  $V_{th}$  are studied using 3D Monte Carlo device simulation assuming single trap. Low  $N_A$  and low cell state  $V_{th}$  in NAND flash memory result in large  $\Delta V_{th}$  at the center of the channel region, showing jellium-like characteristics. On the other hand, as the programmed state  $V_{th}$  increases,  $\Delta V_{th}$  peak at the center of the channel decreases because  $I_D$  concentrates at the both STI edges due to the fringing electrical field from CG. Since single trap is considered in this work,  $\Delta V_{th}$  is suppressed in spite of the high current concentration because alternative current path remains even if a trap locates

above either side of the STI edges. Therefore, exponential distribution  $\lambda$  is only observed above  $N_A = 1 \times 10^{18}$  cm<sup>-3</sup> in this work, which is too high for NAND flash memory. In order to explain the  $\Delta V_{\text{th}}$  tail bits in the NAND flash memory measurement results found in other reports, multiple trap sites or other physical origins will play an important role rather than RDF.

# Acknowledgments

This work is partly supported by JSPS KAKENHI Grant Number 25820148. The authors appreciate TCAD academic committee and Professor. Hiramoto for the help and discussions.

## References

- K. Takeuchi, T. Nagumo, S. Yokogawa, K. Imai, Y. Hayashi, Symp. VLSI Tech. Dig., 2009, p. 54.

- A. Ghetti, C. M. Compagnoni, A. S. Spinelli, A. Visconti, IEEE Trans. Electron Devices 56, (2009) 1746.

- S. M. Joe, M. K. Jung, W. Lee, M. S. Lee, B. S. Jo, J. H. Bae, S. K. Park, K. R. Han, J. H. Yi, G. S. Cho, J. H. Lee, Symp. VLSI Tech. Dig., 2011, p. 112.

- C. M. Compagnoni, A. S. Spinelli, S. Beltrami, M. Bonanomi, A. Visconti, IEEE Electron Device Lett. 29, (2008) 941.

- C. M. Compagnoni, R. Gusmeroli, A. S. Spinelli, A. Visconti, IEEE Trans. Electron Devices 55, (2008) 3192.

- A. Ghetti, C. M. Compagnoni, F. biancardi, A. L. Lacaita, S. Beltrami, L. Chiavarone, A. S. Spinelli, A. Visconti, IEDM Tech. Dig., 2008, p. 1.

- 7) A. Ghetti, S. M. Amoroso, A. Mauri, C. M. Compagnoni, IMW Tech. Dig., 2011, p. 1.

- A. Ghetti, S. M. Amoroso, A. Mauri, and C. M. Conpagnoni, IEEE Trans. Electron Devices 59, (2012) 309.

- 9) Y. Li, C. H. Hwang, T. Y. Li, M. H. Han, IEEE Trans. Electron Devices 57, (2010) 437

- 10) Y. Li, S. M. Yu, J. R. Hwang, F. L. Yang, IEEE Trans. Electron Devices 55, (2008) 1449.

- 11) S. Markov, A. S. M. Zain, B. Cheng, A. Asenov, SOI Conf., 2012 p. 1.

- 12) A. Asenov, IEEE Trans. Electron Devices 45, (1998) 2505.

- Y. Taur, G. J. Hu, R. H. Dennand, L. M. Terman, Y. T. Chung, K. E. Petrillo, IEEE Trans. Electron Devices 32, (1985) 203.

- 14) R. R. Troutman, IEEE J. Solid-State Circuits 14, (1979) 383.

- R. H. Dennard, F. H. Gaensslen, V. L. Rideout, E. Bassous, IEEE Solid-State Integrated Circuits 9, (2003) 256.

- D. Hisamoto, W. C. Lee, J. Kedzierski, H. Takeuchi, IEEE Trans. Electron Devices 47, (2002) 2320.

- 17) Z. H. Liu, H. Chenming, J. H. Huang, T. Y. Chan, M. C. Jeng, P. K. Ko, Y. C. Cheng, IEEE Trans. Electron Devices 40, (2002) 86.

- A. Torsi, Y. Zhao, H. Liu, T. Tanzawa, A. Goda, P. Kalavade, K. Parat, IEEE Trans. Electron Devices 58, (2011) 11.

- 19) K. D. Suh, B. H. Suh, Y. H. Lim, J. K. Kim, Y. J. Choi, Y. N. Koh, S. S. Lee, S. C. Kwon, B. S. Choi, J. S. yum, J. H. Choi, J. R. Kim, and H. K. Lim, IEEE J. Solid-State Circuits. 30 (1995) 1149.

- 20) N. Tega, H. Miki, T. Osabe, A. Kotabe, K. Otsuga, H. Kurata, S. Kamohara, K. Tokami, Y. Ikeda, and R. Yamada, IEDM Tech. Dig., 2006, p. 1.

- K. Fukuda, Y. Shimizu, K. Amemiya, M. Kamoshida, and C. Hu, IEDM Tech. Dig., 2007, p. 169.

- 22) T. Kim, D. He, R. Porter, D. Rivers, J. Kessenich, and A. Goda: IEEE Electron Device Lett. **31**, (2010) 153.

- 23) T. Kim, N. Franklin, C. Srinivasan, P. Kalavade, and A. Goda: IEEE Electron Device Lett.

32, (2011) 1183.

- 24) D. Kang, S. Lee, H. M. Park, D. J. Lee, J. Kim, J. Seo, C. Lee, C. Song, C. S. Lee, H. Shin, J. Song, H. Lee, J. H. Choi, and Y. H. Jun: Symp. VLSI Tech. Dig., 2011, p. 206.

- 25) M. K. Jeong, S. M. Joe, H. J. Kang, K. R. Han, G. Cho, S. K. Park, B. G. Park, J. H. Lee: Symp. VLSI Tech. Dig., 2013, p. T154.

- 26) E. Nowak, J. H. Kim, H. Y. Kown, Y. G. Kim, J. S. Sim, S. H. Lim, D. S. Kim, K. H. Lee,

Y. K. Park, J. H. Choi, C. Chung, Symp. VLSI Tech. Dig., 2012, p. 21.

- 27) W. Xiong, J. W. Park, J. P. Colinge, SOI Conf., 2003, p. 111.

- 28) T. Nagumo, and T. Hiramoto, IEEE Trans. Electron Devices 53, (2006) 3025.

- 29) F. L. Yang, J. R. Hwang, and Y. Li, IEEE CICC Tech. Dig., 2006, p. 691.

- H. Fukutome, Y. Momiyama, T. Kubo, E. Yoshida, H. Morioka, M. Tajima, and T. Aoyama: IEDM Tech. Dig., 2006, p. 281.

- 31) A. Asenov, IEEE Trans. Electron Devices **50**, (2003) 1837.

- S. Tanakamaru, C. Hung, A. Esumi, M. Ito, K. Li, and K. Takeuchi, ISSCC Tech. Dig., 2011, p. 204.

## **Figureure Captions**

**Fig. 1** (Color online)  $I_{\rm D}$ - $V_{\rm CG}$  characteristics for trapped and de-trapped states induced by RTN. Threshold voltage shifts by RTN.

**Fig. 2** (Color online) Channel voltage ( $V_{CH}$ ) self-boosting during program inhibit operation in NAND flash memory.  $V_{CH}$  in unselected NAND strings is self-boosted (~8 V) utilizing capacitance  $C_{CG}$  and  $C_{CH}$  by turning off select gates.

**Fig. 3** (Color online) Schematics of dopants in the channel to show the differences between jellium and discrete doping. In jellium doping case, dopants are uniformly distributed while discrete doping considers atomistic effect of dopants.

**Fig.4** (Color online) Simulated 30 nm NAND flash memory cell structure. (a) NAND structure overall view, (b) the cross section view of channel gate length  $L_g$  direction at the center of channel width W, (c) the cross section view of W direction at the center of  $L_g$ .

Fig. 5 (Color online)  $\Delta V_{\text{th}}$  against trap position along  $L_g$  and W for each  $N_A$  in discrete doping case. (a, b)  $N_A = 1 \times 10^{17} \text{ cm}^{-3}$ . (c, d)  $N_A = 3 \times 10^{17} \text{ cm}^{-3}$ . (e, f)  $N_A = 1 \times 10^{18} \text{ cm}^{-3}$ . (g, h)  $N_A = 2 \times 10^{18} \text{ cm}^{-3}$ . (i, j)  $N_A = 3 \times 10^{18} \text{ cm}^{-3}$ . For (a), (c), (e), (g), and (i), source edge is at 0 nm.

Fig. 6 (Color online) Current density distribution at the channel surface of the de-trapped state near  $V_{\text{th}}$ . (a)  $N_{\text{A}} = 1 \times 10^{17} \text{ cm}^{-3}$ ,  $V_{\text{CG}} = -0.3 \text{ V}$  (b)  $N_{\text{A}} = 3 \times 10^{18} \text{ cm}^{-3}$ ,  $V_{\text{CG}} = 1.2 \text{ V}$ .

Fig. 7 (Color online)  $\Delta V_{\text{th}}$  against trap position along  $L_{\text{g}}$  and W for each  $N_{\text{A}}$  in jellium doping case. (a, b)  $N_{\text{A}} = 1 \times 10^{17} \text{ cm}^{-3}$ . (c, d)  $N_{\text{A}} = 3 \times 10^{18} \text{ cm}^{-3}$ .

**Fig. 8** (Color online) Channel surface current density distribution profiles along W for the huge  $\Delta V_{\text{th}}$  outlier sample in the discrete dopant case and the jellium case.  $V_{\text{CG}}$  is 1.2 V for jellium doping case ( $V_{\text{CG}}$  is same for both de-trapped and trapped states) and 1.3 V for discrete doping case.

**Fig. 9** (Color online) Channel surface current density distribution profiles along *W* between trapped and de-trapped state in the jellium doping case at (a) low and (b) high  $N_A$ .  $V_{CG}$  is -0.15 and 1.3 V for low and high  $N_A$ , respectively.

Fig. 10 (Color online) Statistical distribution of  $\Delta V_{\text{th}}$ . (a) Jellium doping and (b) discrete doping case.

**Fig. 11** (Color online) (a) Average and (b) standard deviation of  $\Delta V_{\text{th}}$  as a function of  $N_{\text{A}}$ .

**Fig. 12** (Color online)  $V_{\text{th}}$  distribution and corresponding data symbols in MLC NAND flash memory.<sup>32)</sup>  $V_{\text{th}}$  values for each program state used in this work are also shown.

Fig. 13 (Color online)  $\Delta V_{\text{th}}$  distribution along  $L_{\text{g}}$  and W with cell data symbol for "11" (lowest  $V_{\text{th}}$  state representing erase state) and "10" (highest  $V_{\text{th}}$  state). (a)-(d)  $N_{\text{A}} = 3 \times 10^{17}$  cm<sup>-3</sup>. (e)-(h)  $N_{\text{A}} = 3 \times 10^{18}$  cm<sup>-3</sup>.

Fig. 14 (Color online) Channel surface current distribution at the center of the channel for low and high  $N_A$  in typical samples with discrete doping (a) low  $N_A$  case and (b) high  $N_A$  case.  $V_{CG}$  is implied -2.5 and 3.5 V for data"11" and data "10" respectively.

Fig. 15 (Color online)  $\Delta V_{\text{th}}$  probability distribution for four data symbol in (a)  $N_{\text{A}} = 3 \times 10^{17}$  and (b)  $3 \times 10^{18}$  cm<sup>-3</sup>.

**Fig. 16** (Color online) Standard deviation of  $\Delta V_{\text{th}}$  as a function of  $V_{\text{th}}$  of the program state.

Table I Differences between NOR and NAND flash memory in terms of program voltage  $V_{PGM}$ ,

| NOR                   | NAND                                                                                 |

|-----------------------|--------------------------------------------------------------------------------------|

| 10V                   | 20V                                                                                  |

| 5V                    | 8V                                                                                   |

| (selected             | (inhibited                                                                           |

| cell)                 | cell)                                                                                |

| high                  | low                                                                                  |

| >1 × 10 <sup>18</sup> | ~3 × 10 <sup>17</sup>                                                                |

| cm <sup>-3</sup>      | cm <sup>-3</sup>                                                                     |

| [4-8]                 | This work                                                                            |

|                       | 10V<br>5V<br>(selected<br>cell)<br>high<br>>1 × 10 <sup>18</sup><br>cm <sup>-3</sup> |

max channel voltage  $V_{CH}$  and channel doping concentration  $N_A$ .

Fig. 1

Fig. 2

Fig. 4

Fig. 5

18

Fig. 6

Fig. 7

Fig. 11

Fig. 13

Fig. 16